## Deployment and Debugging of Real-Time Applications on Multicore Architectures

by

## Hany Kashif

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2015

© Hany Kashif 2015

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Statement of Contributions

In what follows is a list of publications which I have co-authored and used their content in this dissertation. For each publication, I present a list of my contributions.

The use of the content, from the listed publications, in this dissertation has been approved by all co-authors.

- 1. Hany Kashif, Hiren D. Patel, and Sebastian Fischmeister. Using Link-level Latency Analysis for Path Selection for Real-time Communication on NoCs. In *Proceedings of the Asia South Pacific Design Automation Conference (ASPDAC)*, Sydney, Australia, February 2012 [67].

- Defined the path selection algorithm

- Defined the heuristics used by the algorithm

- Implemented the algorithm

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 2. Hany Kashif and Sebastian Fischmeister. Program Transformation for Time-aware Instrumentation. In *Proceedings of the 17th IEEE International Conference on Emerging Technologies & Factory Automation (ETFA)*, Krakow, Poland, September 2012 [63].

- Defined the program transformation techniques

- Defined the instrumentable edges detection algorithm

- Defined the solution to the overhead optimization problem

- Implemented the instrumentation tool

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 3. Hany Kashif, Sina Gholamian, Rodolfo Pellizzoni, Hiren D. Patel, and Sebastian Fischmeister. ORTAP:An Offset-based Response Time Analysis for a Pipelined Communication Resource Model. In *IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)*, Philadelphia, USA, April 2013 [65].

- Involved in deriving the offset-based stage-level analysis

- Formalized the the offset-based stage-level analysis

- Derived and formalized the offset-based flow-level analysis

- Implemented the offset-based stage-level analysis

- Involved in writing the article

- 4. Hany Kashif, Pansy Arafa, and Sebastian Fischmeister. INSTEP: A Static Instrumentation Framework for Preserving Extra-functional Properties. In *Proceedings of the 19th IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA)*, Taipei, Taiwan, August 2013 [62].

- Defined the instrumentation flow

- Implemented the instrumentation framework

- Designed the experiments

- Wrote a significant portion of the article

- 5. Hany Kashif and Hiren Patel. Bounding Buffer Space Requirements for Real-Time Priority-Aware Networks. In *Proceedings of the Asia South Pacific Design Automation Conference (ASPDAC)*, SunTec, Singapore, January 2014 [66].

- Defined the problem and the solution

- Defined and formalized the buffer space analysis techniques

- Implemented the buffer space analysis techniques

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 6. Hany Kashif, Sina Gholamian, and Hiren Patel. SLA: A Stage-level Latency Analysis for Real-time Communication in a Pipelined Resource Model. In *IEEE Transactions on Computers*, 64(4), April 2014 [64].

- Defined a solution to analyze communication at the stage-level

- Formalized the stage-level analysis

- Implemented the stage-level analysis

- Designed and executed the experiments

- Analyzed the experimental results

- Wrote a significant portion of the article

- 7. Hany Kashif, Johnson Thomas, Hiren Patel, and Sebastian Fischmeister. Static Slack-Based Instrumentation of Programs. In *Proceedings of the 20th IEEE International Conference on Emerging Technologies & Factory Automation (ETFA)*, Luxembourg, September 2015 [68].

- Involved in designing the algorithm for minimizing instrumentation points

- Defined a solution to the overhead optimization problem

- $\bullet\,$  Implemented the software and hardware solutions

- $\bullet$  Designed and executed the experiments

- $\bullet\,$  Analyzed the experimental results

- Involved in writing the article

#### Abstract

It is essential to enable information extraction from software. Program tracing techniques are an example of information extraction. Program tracing extracts information from the program during execution. Tracing helps with the testing and validation of software to ensure that the software under test is correct. Information extraction is done by instrumenting the program. Logged information can be stored in dedicated logging memories or can be buffered and streamed off-chip to an external monitor. The designer inspects the trace after execution to identify potentially erroneous state information. In addition, the trace can provide the state information that serves as input to generate the erroneous output for reproducibility.

Information extraction can be difficult and expensive due to the increase in size and complexity of modern software systems. For the sub-class of software systems known as real-time systems, these issues are further aggravated. This is because real-time systems demand timing guarantees in addition to functional correctness. Consequently, any instrumentation to the original program code for the purpose of information extraction may affect the temporal behaviors of the program. This perturbation of temporal behaviors can lead to the violation of timing constraints, which may bias the program execution and/or cause the program to miss its deadline. As a result, there is considerable interest in devising techniques to allow for information extraction without missing a program's deadline that is known as time-aware instrumentation. This thesis investigates time-aware instrumentation mechanisms to instrument programs while respecting their timing constraints and functional behavior. Knowledge of the underlying hardware on which the software runs, enables the extraction of more information via the instrumentation process.

Chip-multiprocessors offer a solution to the performance bottleneck on uni-processors. Providing timing guarantees for hard real-time systems, however, on chip-multiprocessors is difficult. This is because conventional communication interconnects are designed to optimize the average-case performance. Therefore, researchers propose interconnects such as the priority-aware networks to satisfy the requirements of hard real-time systems. The priority-aware interconnects, however, lack the proper analysis techniques to facilitate the deployment of real-time systems. This thesis also investigates latency and buffer space analysis techniques for pipelined communication resource models, as well as algorithms for the proper deployment of real-time applications to these platforms.

The analysis techniques proposed in this thesis provide guarantees on the schedulability of real-time systems on chip-multiprocessors. These guarantees are based on reducing contention in the interconnect while simultaneously accurately computing the worst-case communication latencies. While these worst-case latencies provide bounds for computing the overall worst-case execution time of applications on chip-multiprocessors, they also provide means to assigning instrumentation budgets required by time-aware instrumentation. Leveraging these platform-specific analysis techniques for the assignment of instrumentation budgets, allows for extracting more information from the instrumentation process.

#### Acknowledgements

First and foremost, I am grateful to God for bestowing upon me the strength, knowledge, and good health to complete the research for this thesis.

I would like to seize this opportunity to thank my supervisor, Professor Sebastian Fischmeister, for his continuous encouragement, help, and support. His advice, tolerance, and consideration were invaluable. I also thank my co-supervisor, Professor Hiren Patel, for his constant guidance and thoughtfulness.

I would like to thank Professor Rodolfo Pellizzoni for the valuable research discussions and sharp insights. I would like to thank Professor Mahesh Tripunitara for teaching me a mind-set and an approach to solving certain problems. I would like to thank Professor Mark Aagaard for giving me the opportunity to be, on various occasions, the teaching assistant of someone as respectful and decent as he is. I would like to thank Professor Siddharth Garg and Professor Borzoo Bonakdarpour for the numerous interesting research discussions. I would also like to thank my committee members: Professor Bill Cowan, Professor Catherine Gebotys, Professor Lin Tan, and Professor Kees Goossens for taking the time and effort to participate in my examination committee and provide me with valuable feedback.

I would like to thank my friends in the Real-Time Embedded Software Group at the University of Waterloo for all the beautiful moments we shared together. We have been together through thick and thin: Ramy Medhat, Mahmoud Salem, Pansy Arafa, Samaneh Navabpour, Johnson Thomas, Wallace Wu, Aymen Ketata, Augusto Born de Oliveira, Jean-Christophe Petkovic, Akramul Azim, and Sina Gholamian.

I cannot find the words to thank my parents, Ismail and Nahla, for their continuous and endless support throughout my whole life. I thank them for believing in me and for helping me be who I am today. Thanks to my brothers, Mostafa and Ahmed, for the help and support they offer me. Thanks to my young and beautiful sister, Mariam, for representing all the beauty and innocence in this world.

I would like to express my deep gratitude for my wife, Pansy. Thanks for all the sacrifices, support, and endless patience. I also thank my son, Adham, for shining my days with his innocent smiles.

### Dedication

To my lovely wife, Pansy.

To my son, Adham.

To my dear parents, Ismail and Nahla.

To my siblings, Ahmed, Mostafa, and Mariam.

To all those who touched my life.

## Table of Contents

| Li | st of           | Tables                                     | ciii |  |

|----|-----------------|--------------------------------------------|------|--|

| Li | List of Figures |                                            |      |  |

| A  | bbre            | iations                                    | xvi  |  |

| Li | st of           | Symbols                                    | viii |  |

| 1  | Inti            | oduction                                   | 1    |  |

|    | 1.1             | Tracing                                    | 1    |  |

|    |                 | 1.1.1 Tracing of Real-Time Systems         | 2    |  |

|    | 1.2             | Time-Aware Instrumentation                 | 2    |  |

|    |                 | 1.2.1 Goals and Contributions              | 3    |  |

|    | 1.3             | Chip-Multiprocessors for Real-Time Systems | 4    |  |

|    |                 | 1.3.1 Goals and Contributions              | 5    |  |

|    | 1.4             | Organization                               | 7    |  |

| 2  | Ove             | rview                                      | 8    |  |

|    | 2.1             | Information Extraction                     | 8    |  |

|    |                 | 2.1.1 Instrumentation                      | 8    |  |

|    |                 | 2.1.2 Sampling                             | 10   |  |

|    |                 | 2.1.3 Emulation                            | 11   |  |

|    |                 | 2.1.4 Multi-Objective Compilation          | 11   |  |

|    | 2.2             | Chip-Multiprocessors                       | 11   |  |

|    |                 | 2.2.1 Architecture and Operation           | 11   |  |

|    |                 | 2.2.2 Real-Time Communication              | 12   |  |

|    |                 | 2.2.3 Timing Analysis                      | 13   |  |

|   |      | 2.2.4   | Buffer Space Requirements                         | 15 |

|---|------|---------|---------------------------------------------------|----|

|   |      | 2.2.5   | Path Selection                                    | 16 |

| 3 | Inci | reasing | g the Effectiveness of Time-Aware Instrumentation | 17 |

|   | 3.1  | Overv   | riew of Time-Aware Instrumentation                | 17 |

|   | 3.2  | Model   | l and Terminology                                 | 19 |

|   | 3.3  | ETP S   | Shift-Effectiveness Metric                        | 20 |

|   |      | 3.3.1   | Formalized ETPsem                                 | 22 |

|   | 3.4  | Progra  | am Transformation                                 | 24 |

|   |      | 3.4.1   | Edge Detection for Program Transformation         | 24 |

|   |      | 3.4.2   | Branch Block Creation                             | 25 |

|   |      | 3.4.3   | CFG Cloning                                       | 27 |

|   |      | 3.4.4   | Experimentation                                   | 30 |

|   | 3.5  | Slack-  | based Conditional Instrumentation                 | 34 |

|   |      | 3.5.1   | The Underlying Concepts                           | 35 |

|   |      | 3.5.2   | Minimization of CPs on the WCP                    | 38 |

|   |      | 3.5.3   | Constrained Minimization of CPs                   | 39 |

|   |      | 3.5.4   | Implementation Approaches                         | 41 |

|   |      | 3.5.5   | Experimentation                                   | 44 |

|   | 3.6  | Discus  | $\operatorname{ssion}$                            | 50 |

|   | 3.7  | Summ    | nary                                              | 53 |

|   |      |         |                                                   |    |

| 4 | INS  |         | A Static Time-Aware Instrumentation Framework     | 54 |

|   | 4.1  |         | -Functional Instrumentation Overview              | 56 |

|   | 4.2  | Partia  | al Program Derivation                             | 57 |

|   |      | 4.2.1   | The Input Program                                 | 57 |

|   |      | 4.2.2   | The Instrumentation Intent                        | 58 |

|   |      | 4.2.3   | The Derivation of the Partial Program             | 59 |

|   |      | 4.2.4   | The Partial Program                               | 63 |

|   | 4.3  | Deter   | minising the Instrumentation                      | 64 |

|   |      | 4.3.1   | Specifying the Constraints                        | 64 |

|   |      | 4.3.2   | Cost Models                                       | 64 |

|   |      | 4.3.3   | The Formulation                                   | 65 |

|   |      | 4.3.4 The Instrumented Program                | 68         |

|---|------|-----------------------------------------------|------------|

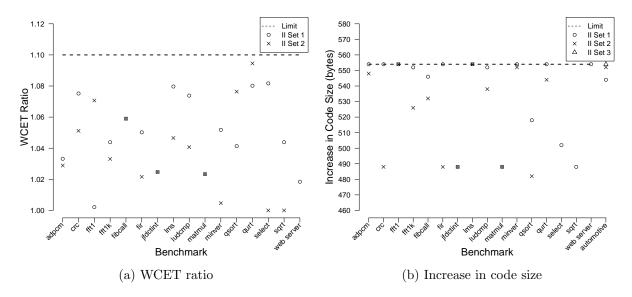

|   | 4.4  | Experimentation                               | 69         |

|   |      | 4.4.1 Experimental Setup                      | 69         |

|   |      | 4.4.2 Experimental Results                    | 71         |

|   | 4.5  | Discussion                                    | 74         |

|   | 4.6  | Summary                                       | 76         |

| 5 | Stag | ge-Level Analysis for CMPs                    | 77         |

|   | 5.1  | Resource Model                                | 77         |

|   | 5.2  | Communication Task Model                      | <b>7</b> 9 |

|   | 5.3  | Direct Interference                           | 80         |

|   | 5.4  | Worst-Case Latency with Direct Interference   | 81         |

|   | 5.5  | Indirect Interference                         | 85         |

|   | 5.6  | Worst-Case Latency with Indirect Interference | 87         |

|   | 5.7  | An Illustrative Example                       | 87         |

|   | 5.8  | Tightness Analysis                            | 88         |

|   | 5.9  | Relaxing the Deadline Restriction             | 89         |

|   | 5.10 | Experimentation                               | 93         |

|   | 5.11 | Summary                                       | 98         |

| 6 | Offs | et-based WCRT Analysis for CMPs               | 99         |

|   | 6.1  | System Model                                  | 00         |

|   |      | 6.1.1 Task Model                              | 00         |

|   |      | 6.1.2 Offsets and Jitters                     | 01         |

|   | 6.2  | Holistic Analysis                             | 03         |

|   |      | 6.2.1 ComputeOffsets: Computing Offsets       | 04         |

|   |      | 6.2.2 Compute Jitters: Computing Jitters      | 05         |

|   | 6.3  | Offset-based Stage-Level Analysis             | 05         |

|   |      | 6.3.1 Direct and Indirect Interference        | 05         |

|   |      | 6.3.2 Derivation of a Response Time Estimate  | 05         |

|   |      | 6.3.3 Critical Activation Patterns            | 12         |

|   |      | 6.3.4 Indirect Interference Jitter            | 14         |

|   |      | 6.3.5 Exponential Analysis                    | 14         |

| $\mathbf{R}$ | e <b>fere</b> : | nces    |                                                 | 173 |

|--------------|-----------------|---------|-------------------------------------------------|-----|

| 9            | Con             | clusio  | n                                               | 170 |

|              | 8.5             | Summ    | ary                                             | 168 |

|              | 8.4             | Set-to: | p Box Application                               | 165 |

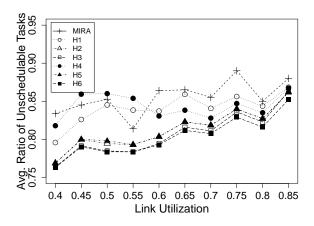

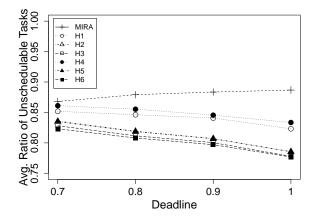

|              |                 | 8.3.1   | Summary of Experimental Results                 | 164 |

|              | 8.3             | Exper   | $imentation \ldots \ldots \ldots \ldots \ldots$ | 159 |

|              |                 | 8.2.2   | Heuristic-based Path Selection Algorithm        | 151 |

|              |                 | 8.2.1   | Optimal Path Selection Algorithm                | 150 |

|              | 8.2             | Path S  | Selection Algorithm                             | 150 |

|              | 8.1             | System  | n Model                                         | 149 |

| 8            | Pat             | h Selec | ction                                           | 149 |

|              | 7.4             | Summ    | ary                                             | 148 |

|              |                 | 7.3.3   | Experimentation                                 | 144 |

|              |                 | 7.3.2   | Allocation Algorithm                            | 142 |

|              |                 | 7.3.1   | Stage-Level Analysis                            | 135 |

|              | 7.3             | Buffer  | Space Allocation                                | 135 |

|              |                 | 7.2.3   | Experimentation                                 | 132 |

|              |                 | 7.2.2   | Flow-Level Buffer-Space Analysis                | 132 |

|              |                 | 7.2.1   | Stage-Level Buffer-Space Analysis               | 129 |

|              | 7.2             | Buffer  | Space Requirements                              | 128 |

|              | 7.1             | System  | m Model                                         | 127 |

| 7            | Buf             | fer Spa | ace Analysis for CMPs                           | 127 |

|              | 6.6             | Summ    | ary                                             | 126 |

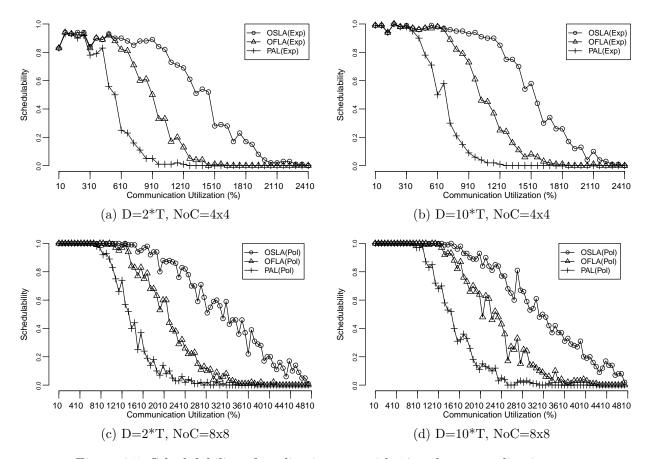

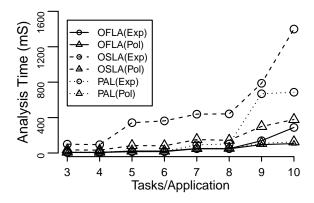

|              | 6.5             | •       | imental Evaluation                              |     |

|              |                 | 6.4.3   | Polynomial Analysis                             |     |

|              |                 | 6.4.2   | Direct and Indirect Interferences               |     |

|              |                 | 6.4.1   | Exponential Analysis                            |     |

|              | 6.4             | Offset- | -based Flow-Level Analysis                      | 119 |

|              |                 | 6.3.6   | Polynomial Analysis                             | 117 |

## List of Tables

| 3.1 | ETPsem and number of retries                                                   | 32  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.2 | The overhead on the WCP and increase in code size                              | 33  |

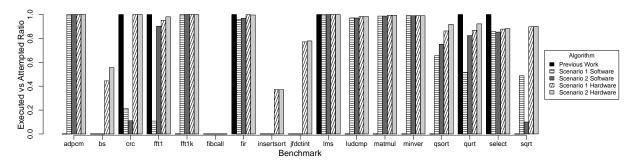

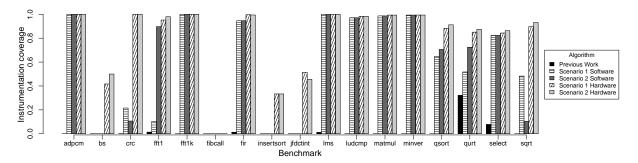

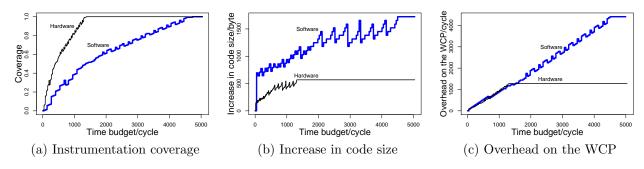

| 3.3 | Instrumentation coverage for the software implementation of Scenario ${\bf 1}$ | 46  |

| 3.4 | Overhead on the WCP and the increase in code size for Scenarios 1 and 2 .      | 48  |

| 4.1 | Experimentation results for INSTEP                                             | 75  |

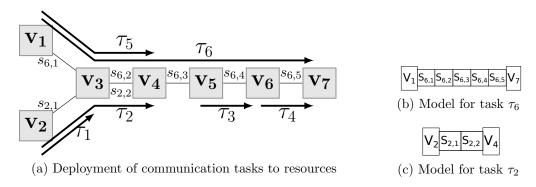

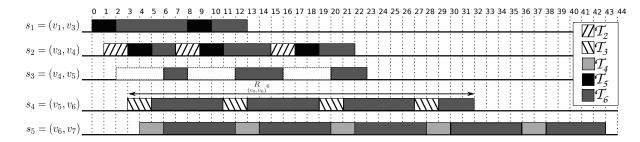

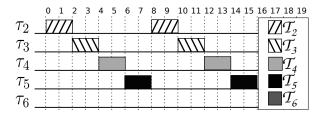

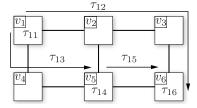

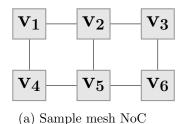

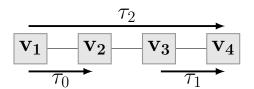

| 5.1 | Data for communication tasks in Figure 5.1a                                    | 80  |

| 5.2 | Results for the example in Figure 5.1a using both SLA and FLA                  | 88  |

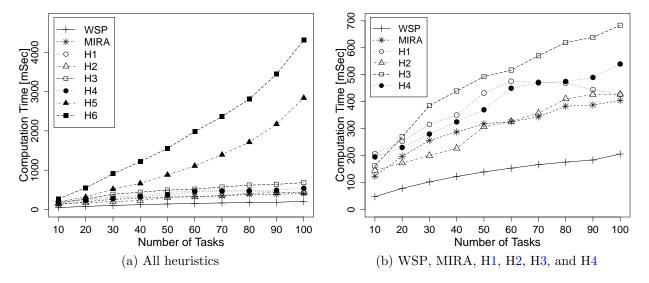

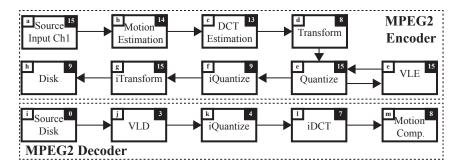

| 8.1 | Complexity of the different heuristics                                         | 159 |

| 8.2 | Summary of experimentation results                                             | 165 |

| 8.3 | Data for set-top box application                                               | 167 |

| 8.4 | Results for the set-top box case study                                         | 167 |

# List of Figures

| 1.1  | Execution time profiles of the OLPC keyboard controller [39]       | 3  |

|------|--------------------------------------------------------------------|----|

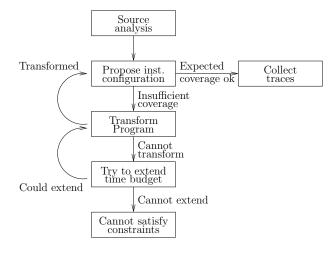

| 3.1  | Work flow for time-aware instrumentation                           | 18 |

| 3.2  | Example of a program's execution time variation                    | 20 |

| 3.3  | Illustrative example of the ETPsem                                 | 22 |

| 3.4  | Execution time profile to prove Theorem 1                          | 22 |

| 3.5  | Example of program transformation                                  | 24 |

| 3.6  | Average instrumentation coverage for program transformation        | 32 |

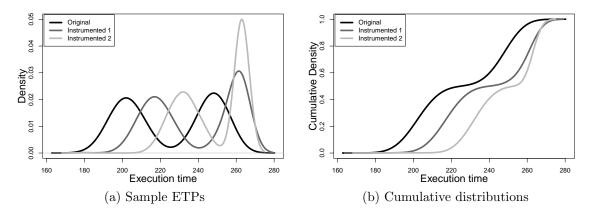

| 3.7  | Execution time profiles for qsort-exam                             | 33 |

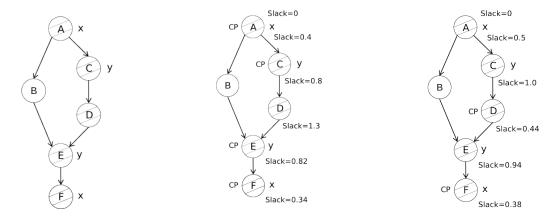

| 3.8  | Original program                                                   | 37 |

| 3.9  | All CPs on WCP                                                     | 37 |

| 3.10 | Minimal CPs on WCP                                                 | 37 |

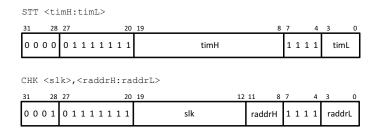

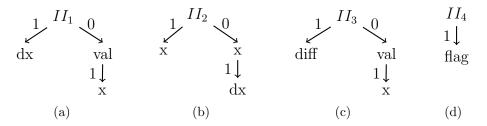

| 3.11 | Instruction encodings of the $stt$ and $chk$ instructions          | 43 |

| 3.12 | Executed vs attempted instrumentation points for Scenarios 1 and 2 | 46 |

| 3.13 | Instrumentation coverage for Scenarios 1 and 2                     | 47 |

| 3.14 | Execution time profiles for the <i>insertsort</i> benchmark        | 49 |

| 3.15 | Constrained minimization of CPs for the matrix inversion algorithm | 50 |

| 4.1  | Extra-functional instrumentation framework                         | 57 |

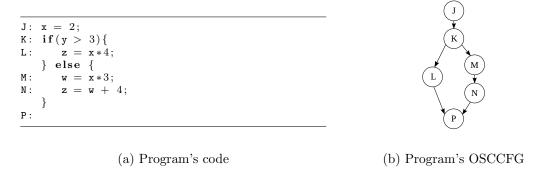

| 4.2  | Input programs                                                     | 58 |

| 4.3  | Instrumentation intents for the input program                      | 59 |

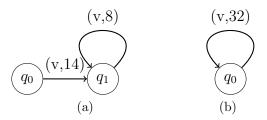

| 4.4  | Example to illustrate instrumentation alternatives                 | 60 |

| 4.5  | Cost models                                                        | 65 |

| 4.6  | WCET ratio and increase in code size of instrumented benchmarks    | 72 |

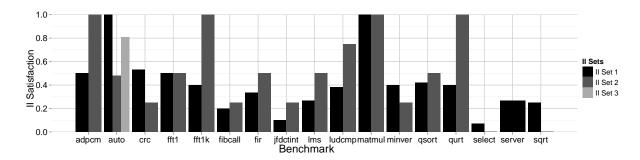

| 4.7  | Satisfaction of instrumentation intents                            | 73 |

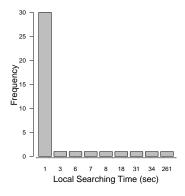

| 4.8  | Local search time                                                  | 73 |

| 5.1 | Motivating example                                                                                         |

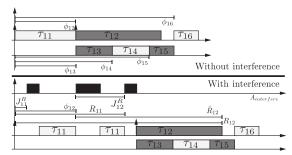

|-----|------------------------------------------------------------------------------------------------------------|

| 5.2 | Timeline of task $\tau_6$ in Figure 5.1a                                                                   |

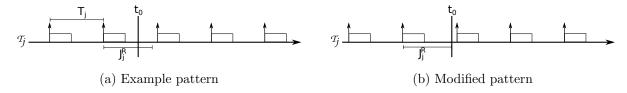

| 5.3 | Activation pattern of task $\tau_j$                                                                        |

| 5.4 | Timeline of task $\tau_6$ in Figure 5.1a using FLA                                                         |

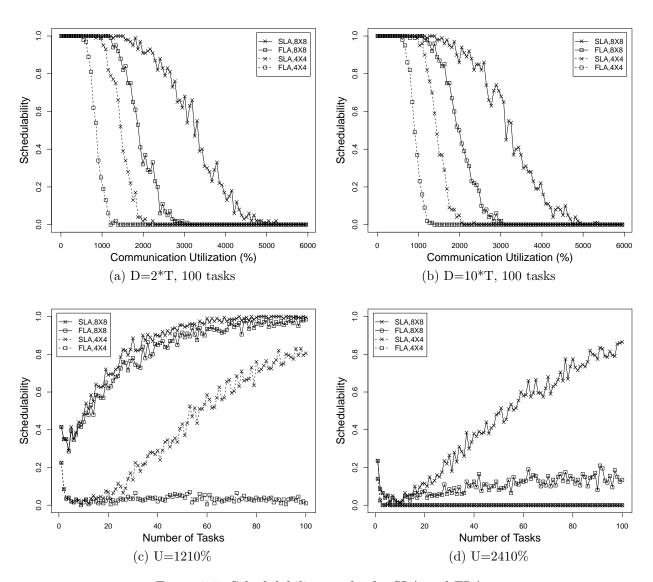

| 5.5 | Schedulability results for SLA and FLA                                                                     |

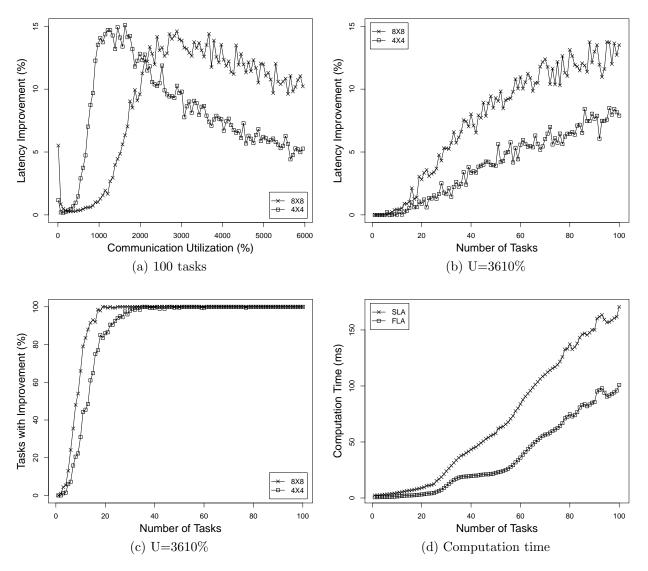

| 5.6 | Latency and computation time results for SLA and FLA                                                       |

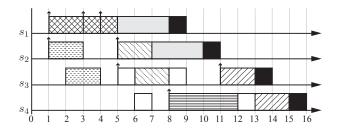

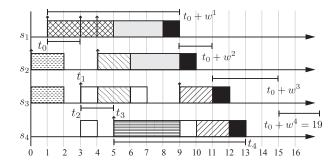

| 6.1 | Illustrative example application $A_1$ : Task graph and its mapping 102                                    |

| 6.2 | An example schedule (up arrows are release times)                                                          |

| 6.3 | An example of the stage-normalized schedule                                                                |

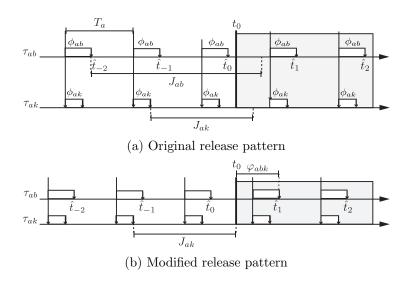

| 6.4 | Release patterns of jobs of application $A_a$                                                              |

| 6.5 | Schedulability of application sets with 10 tasks per application                                           |

| 6.6 | Run time comparison of OSLA, OFLA, and PAL                                                                 |

| 7.1 | Interference scenario S1 on stage $s$                                                                      |

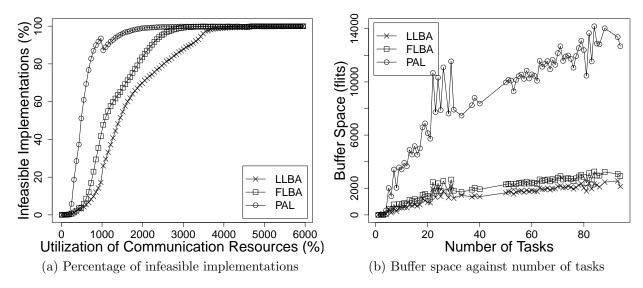

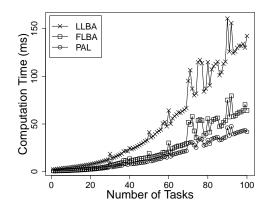

| 7.2 | Infeasible implementations and buffer space requirements                                                   |

| 7.3 | Computation time against number of tasks                                                                   |

| 7.4 | Illustration of Lemma 18                                                                                   |

| 7.5 | Illustrative example of Lemma 21                                                                           |

| 7.6 | Illustration of Lemma 22                                                                                   |

| 7.7 | Schedulability results for SLA and FLA against VC size                                                     |

| 7.8 | Latency and computation time results for SLA and FLA                                                       |

| 7.9 | Results for the buffer space allocation algorithm                                                          |

| 8.1 | An illustrative example for objectives 1 and 2 of PSA                                                      |

| 8.2 | An illustrative example for objective 3 of PSA                                                             |

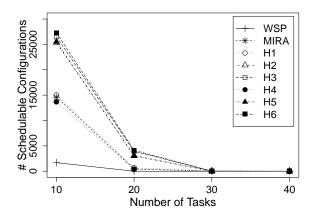

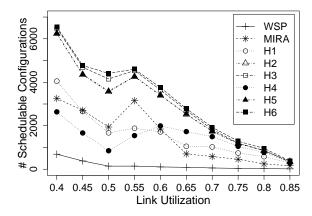

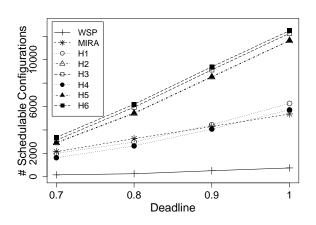

| 8.3 | Schedulability results                                                                                     |

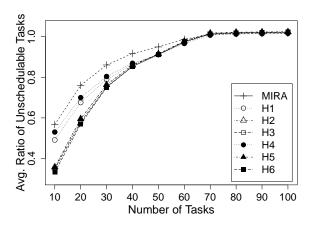

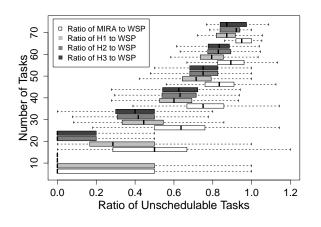

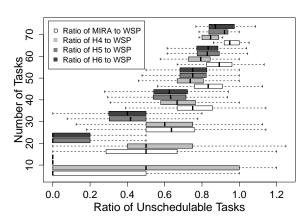

| 8.4 | Ratio of unschedulable tasks against number of tasks for $8 \times 8$ mesh, $U = 0.4$ , $D = 1.0 \dots 16$ |

| 8.5 | Average computation times for the different algorithms against number of tasks                             |

| 8.6 | Set-top box block diagram and mapping                                                                      |

| 8.7 | Routing of the tasks for the different algorithms                                                          |

## Abbreviations

ACK Acknowledgment.

ALU Arithmetic logic unit.

BIP Binary integer programming.

CFG Control-flow graph.

CI Confidence interval.

CMP Chip-multiprocessor.

CP Conditional instrumentation point.

DAG Directed acyclic graph.

DSP Digital signal processing.

DUA Definitive-use association.

ETP Execution time profile.

ETPsem Execution time profile shift-effectiveness metric.

FIFO First in first out. FLA Flow-level analysis.

FLBA Flow-level buffer-space analysis.

GALS Globally asynchronous, locally synchronous.

GCC GNU compiler collection.

II Instrumentation intent.ILP Integer linear programming.IP Instrumentation point.ISA Instruction-set architecture.

LHS Left hand side.

MCU Micro-controller unit.

MIRA Minimum interference routing algorithm.

MUX Multiplexer.

NACK Negative acknowledgment. NLP Non-linear programming.

NoC Network-on-chip.

NP Non-deterministic polynomial time.

OFLA Offset-based flow-level analysis.

OLPC One laptop per child. OSCCFG One-state change CFG.

OSLA Offset-based stage-level analysis.

PAL Palencia and Gonzalez's analyses.

PSA Path selection algorithm.

RHS Right hand side.

SEM Standard error of mean. SLA Stage-level analysis.

SLBA Stage-level buffer-space analysis.

SoC System-on-chip.

SWP Shortest widest path.

TDM Time division multiplexing.

VC Virtual channel.

WCET Worst-case execution time.

WCL Worst-case latency. WCP Worst-case path.

WCRT Worst-case response time.

WSP Widest shortest path.

## List of Symbols

#### Time-Aware Instrumentation

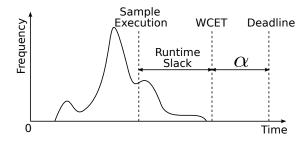

- $\alpha$  The difference between the program's worst-case execution time and deadline.

- $\beta$  The program's debugging time budget.

- O The overhead on the program's worst-case execution time due to instrumentation.

- $\Upsilon(t)$  The execution time profile shift-effectiveness metric.

- $\varrho$  The instrumentation coverage.

#### Stage-Level Analysis

- $\Gamma$  A set of communication tasks deployed on the pipelined resource model.

- $\tau_i$  A communication task i.

- $P_i$  Priority of communication task  $\tau_i$ .

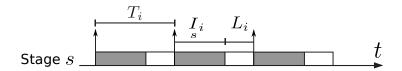

- $T_i$  Period or minimum interarrival time between jobs of communication task  $\tau_i$ .

- $D_i$  Deadline of communication task  $\tau_i$ .

- $J_i^R$  Release jitter of communication task  $\tau_i$ .

- $L_i$  Worst-case latency of communication task  $\tau_i$  on a single communication resource.

- $C_i$  Worst-case latency of communication task  $\tau_i$  along its path of communication resources from source to destination.

- $\delta_i$  A path formed of a series of contiguous communication resources of communication task  $\tau_i$  from a source stage  $s_1$  to a destination stage  $s_{|\delta_i|}$ .

- $\sigma_i(s_l)$  A subsequence of the path  $\delta_i$  of communication task  $\tau_i$  starting with the same source stage  $s_1$  and ending with a stage  $s_l$ ..

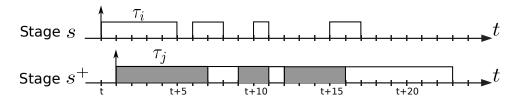

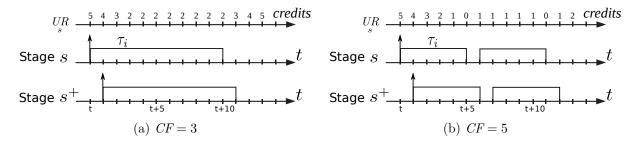

A stage on the path  $\delta_i$  of a communication task  $\tau_i$ .  $s_{i,l}$ s'A stage preceding stage s on the path of a communication task.  $s^+$ A stage succeeding stage s on the path of a communication task.  $(v_i, v_j)$ A communication resource (stage) connecting the two computation resources  $V_i$  and  $V_i$ .  $\mathbb{S}_i^D$ Set of directly interfering tasks with task  $\tau_i$  on stage s of its path  $\delta_i$ .  $\mathbb{S}_i^I$ Set of indirectly interfering tasks with task  $\tau_i$  on stage s of its path  $\delta_i$ .  $J_i^I$ Indirect interference jitter for a task under analysis on stage s through a directly interfering task  $\tau_i$ .  $R_i$ Worst-case latency of communication task  $\tau_i$  along its path  $\delta_i$ .  $R_i$ Worst-case latency of communication task  $\tau_i$  on stage s of its path  $\delta_i$ .  $I_i$ The worst-case interference suffered by communication task  $\tau_i$  from higher priority tasks on stage s of its path  $\delta_i$ .  $B_i$ Busy period on stage s on the path of communication task  $\tau_i$ .  $w_i(p)$ The worst-case completion time of each job p of communication task  $\tau_i$  on stage s from the start of the busy period  $B_i$ .  $I_i(p)$ The worst-case interference suffered by job p of communication task  $\tau_i$  from higher priority tasks on stage s of its path  $\delta_i$ . Maximum value of p for task  $\tau_i$  on stage s.  $p_{B,i}$  $F_i$ The number of flits in one packet of communication task  $\tau_i$ .  $VC_i$ The buffer space in the virtual channel of task  $\tau_i$  in the priority-aware router sending flits on stage s of the task's path  $\delta_i$ . The delay that a data unit of communication task  $\tau_i$  experiences as it moves  $R_{s_{i,l}}$ from one stage  $s_{i,l-1}$  to another stage  $s_{i,l}$ .  $IB_i$ The blockage suffered by task  $\tau_i$  on stage s of its route  $\delta_i$  due to limited buffer space in the downstream router of stage s. CFThe credit feedback delay of the credit-based task control mechanism in the priority-aware network.

The downstream router of stage s.

DR

UR The upstream router of stage s.

#### Offset-based WCRT Analysis

$\mathcal{A}$ A set of n applications deployed on the pipelined resource model.  $A_i$ An application i.  $T_i$ Period or minimum interarrival time for the execution of application  $A_i$ .  $D_i$ Deadline of application  $A_i$ .  $J_i^R$ Release jitter of application  $A_i$ .  $G_{A_i}$ Task graph of application  $A_i$ .  $\Gamma_i^C$ Set of computation tasks in application  $A_i$ .  $\Gamma_i^M$ Set of communication tasks in application  $A_i$ . Task k of application  $A_i$ .  $\tau_{ik}$ The c-th job of task  $\tau_{ik}$ .  $\tau_{ikc}$  $P_{ik}$ Priority of task  $\tau_{ik}$ . A path of communication task  $\tau_{ik}$  formed of a series of contiguous commu- $\delta_{ik}$ nication resources from a source computation resource  $v_{s_{ik}}$  to a destination  $v_{d_{ik}}$ .  $L_{ik}$ Worst-case latency of communication task  $\tau_{ik}$  on a single communication resource.  $C_{ik}$ Worst-case execution time of computation task  $\tau_{ik}$  on a processing resource  $v_{c_{ik}}$  or worst-case latency of communication task  $\tau_{ik}$  along its path of communication resources from source to destination.  $J_{ik}^R$ Release jitter of task  $\tau_{ik}$ .  $\mathbb{S}_i^D(\tau_{ab})$ The set of tasks of application  $A_i$  that directly interfere with task  $\tau_{ab}$  along its path  $\delta_{ab}$ .  $\mathbb{S}_{i}^{D}( au_{ab})$ The set of tasks of application  $A_i$  that directly interfere with task  $\tau_{ab}$  on stage s of its path  $\delta_{ab}$ .  $\mathbb{S}^{I}_{ij}( au_{ab})$ The set of tasks indirectly interfering with task  $\tau_{ab}$  through the intermediate task  $\tau_{ij}$ .  $J_{ij}^{I}(\tau_{ab})$ Indirect interference jitter of task  $\tau_{ij}$  due to the tasks in the indirect inter-

ference set of task  $\tau_{ab}$ .

$\Pi_{ik}$  The set of all paths in the task graph of application  $A_i$ ,  $G_{A_i}$ , starting from  $\tau_{i1}$  to  $\tau_{ik}$ .

$\rho_{ik}$  The set of tasks forming an individual path of  $\Pi_{ik}$ .

$\phi_{ik}$  The offset of task  $\tau_{ik}$  relative to the activation of the root task of application  $A_i$ .

$\bar{\Theta}(t,s)$  A stage-normalized schedule where the transmission schedule  $\Theta(t,s)$  on successive stages is moved earlier in time to account for stage delay so that release times coincide across all stages.

$\Theta(t,s)$  A function schedule that denotes the assignment of a data unit of a job  $\tau_{abc}$  of task  $\tau_{ab}$  to a particular slot t on stage s.

$R_{ab}$  The worst-case response time of task  $\tau_{ab}$  along its route  $\delta_{ab}$  measured from the activation of the root task of application  $A_a$ .

$\hat{R}_{ab}$  The worst-case response time of task  $\tau_{ab}$  along its route  $\delta_{ab}$  measured from the activation of task  $\tau_{ab}$ .

$\bar{R}_{ab}$  The worst-case response time of task  $\tau_{ab}$  measured from the activation of task  $\tau_{ab}$  in a stage-normalized schedule.

$\varphi_{ijk}$  The phase between any task  $\tau_{ij}$  and the beginning of the busy chain of a critical activation pattern created by task  $\tau_{ik}$ .

$p_{0,ab}^v$  The first job instance of task  $\tau_{ab}$  that has enough jitter to be part of the busy chain.

$W_i^{\prime\prime\prime*}(\tau_{ab},s,t)$  An upper bound to the worst-case contribution of an application  $A_i$  to the busy chain of  $\tau_{ab}$  on stage s-1 solely due to tasks that are on stage s-1 but not s, i.e., in the set  $\underset{s-1}{\mathbb{S}}_i^D(\tau_{ab})\backslash \underset{s}{\mathbb{S}}_i^D(\tau_{ab})$ , and by considering each task in  $A_i$  to coincide with the critical instant.

$p_{B,ab}^v$  The largest-numbered job instance of task  $\tau_{ab}$  which exists in the busy chain of  $\tau_{ab}$  up to stage s.

$W_{ik}(\tau_{ab}, s, t)$  The worst-case contribution of an application  $A_i$  to the busy chain of  $\tau_{ab}$  on stage s when the activation of task  $\tau_{ik}$  coincides with the critical instant.

$W'_{ik}(\tau_{ab}, s, t)$  The worst-case contribution of an application  $A_i$  to the busy chain of  $\tau_{ab}$  on stage s-1, when the activation of task  $\tau_{ik}$  coincides with the critical instant, solely due to tasks that are common on stages s-1 and s, i.e., in the set  $\underset{s-1}{\mathbb{S}}_{i}^{D}(\tau_{ab}) \cap \underset{s}{\mathbb{S}}_{i}^{D}(\tau_{ab})$ .

$W_i^*(\tau_{ab}, s, t)$  An upper bound to the worst-case contribution of an application  $A_i$  to the busy chain of  $\tau_{ab}$  on stage s by considering each task in  $A_i$  to coincide with the critical instant.

- $W_{ik}''(\tau_{ab}, s, t)$  The worst-case contribution of an application  $A_i$  to the busy chain of  $\tau_{ab}$  on stage s-1, when the activation of task  $\tau_{ik}$  coincides with the critical instant, solely due to tasks that are on stage s-1 but not s, i.e., in the set  $\underset{s-1}{\mathbb{S}}_{i}^{D}(\tau_{ab}) \setminus \underset{s}{\mathbb{S}}_{i}^{D}(\tau_{ab})$ .

- $w_{ab}^{v}(p)$  The worst-case length of the busy chain for job p of task  $\tau_{ab}$  up to stage s for an activation pattern v.

- $w_{abc}(p)$  The worst-case length of the busy chain for job p of task  $\tau_{ab}$  up to stage s for a critical instant created by tasl  $\tau_{ac}$ .

- $R_{ab}^{v}(p)$  The worst-case response time of job p of task  $\tau_{ab}$  on a stage s for an activation pattern v measured from the activation of application  $A_a$ .

- $R_{abc}(p)$  The worst-case response time of job p of task  $\tau_{ab}$  on a stage s for a critical instant created by task  $\tau_{ac}$  measured from the activation of application  $A_a$ .

## Chapter 1

## Introduction

In this thesis, we address two problems that exist in the field of real-time embedded systems. The first problem is the instrumentation of embedded software. It is essential to take timing constraints into account when instrumenting real-time software. Hence, it is crucial to find new instrumentation techniques that are more suited for real-time systems. The second problem is scalability. Modern chip-multiprocessors (CMPs) connect a large number of embedded processing elements using a pipelined communication interconnect. While the use of CMPs is becoming widespread in general purpose computing, its adoption for hard real-time systems has been cautious at best. This is because of the need to provide provable guarantees that the hard real-time software always meets its timing requirements. Providing tight bounds on the communication latencies between tasks deployed on CMPs can increase the instrumentation budget available for time-aware instrumentation. My main research focus is, thus, (1) providing solutions to instrumentation of real-time embedded software and (2) providing analysis techniques to enable using CMPs as a platform for real-time systems.

### 1.1 Tracing

Program tracing is the extraction of information from a program at runtime during its execution. The tracing technique was developed as early as programming itself [8, 10]. There are various ways for tracing program execution; instrumentation, sampling, and emulation. Instrumentation is the insertion of additional code to the original program to support tracing. The instrumentation process can either be applied to the source code or the binary executable of the program. It can also be a static or a dynamic process. Sampling can also be used to extract information about a running program. The program is unmodified and, at certain intervals, an external monitor interrupts the program to capture some parameters. Emulation as well is recognized as a method for tracing. The reason is that the emulated system can be totally controlled and every single instruction execution is visible for instrumentation.

A common example of tracing program execution is state logging where monitors extract certain critical software state information and program counter locations. Logged

information can be stored in dedicated logging memories or can be buffered and streamed off-chip to an external monitor. The designer inspects the trace after execution to identify potentially erroneous state information. In addition, the trace can provide the state information that serves as input to generate the erroneous output for reproducibility. These techniques are used during the software design process to test, validate, and debug the system, but they are also often used during deployment as well. This is to continue collecting trace information in the event of certain failures that require diagnosis.

### 1.1.1 Tracing of Real-Time Systems

Of all computers, 98% are embedded systems and plenty of those are real-time control systems (DARPA, 2000). This highlights the prevalence of real-time systems in our daily lives including, but not limited to: automotive vehicles, aeroplanes, cellular phones, etc. Real-time applications can be classified into hard real-time and soft real-time applications. For hard real-time applications, it is imperative to meet deadlines. Missing deadlines can lead to system failure which might result in loss of life for instance. Soft real-time applications, on the other hand, can occasionally miss deadlines without causing serious harm. Missing deadlines, however, leads to a degradation in the overall system performance.

While the various real-time applications have different non-functional requirements such as safety and memory consumption, they are all time-sensitive systems. In general, writing correct software is both difficult [71] and expensive [43]. This is further aggravated for real-time systems because in addition to functional correctness, timeliness is important. Tracing is one of the common techniques for debugging real-time systems. The instrumentation process, required to enable tracing, naturally causes perturbation to the system under analysis. Hence, any instrumentations to the original program code may affect the temporal behaviors of the system. Typically, the more tracing code the program executes during the run, the more the perturbation in temporal behaviors. The reason is that, in general, the addition of more tracing code increases the number of instructions the processor executes leading to a longer execution time (except for timing anomalies).

This perturbation of temporal behaviors raises issues during testing and validation in the software design process, and during deployment. In the former, violating the temporal constraints of the program may bias the execution of the program to certain operations, which otherwise would not occur in a real deployment. In the latter, deployment is simply not possible if the program may potentially miss its deadline. As a result, there is considerable interest in devising techniques to allow for program tracing while meeting the program deadlines that is known as time-aware instrumentation [39, 63, 62, 5].

### 1.2 Time-Aware Instrumentation

Time-aware instrumentation tries to preserve logical correctness as well as meeting timing constraints. While a minor influence on execution time maybe be acceptable within a specified timing constraint, naive instrumentation will usually violate such constraints.

Time-aware instrumentation attempts to honor the timing constraints and shifts the execution time profile (ETP) of the program closer to the program's deadline.

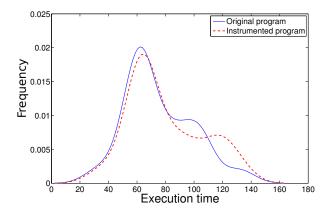

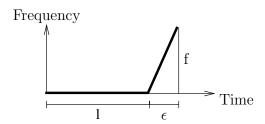

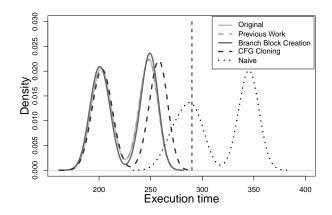

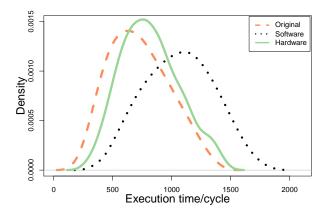

Case studies investigated in related work [39] demonstrate the promise of the general concept but the results revealed new problems. Figure 1.1 shows the ETP of a case study reported in [39] on the one laptop per child (OLPC) keyboard controller. The figure shows the success of time-aware instrumentation in shifting the ETP of the instrumented program. While the shift in the ETP is visible, it is lower than expected. The expectation was a larger shift in the time profile towards longer execution times. Further investigation revealed that, in this example, about 25 percent of the paths share basic blocks with the worst-case path (WCP). This means that large portions of the program are unavailable for instrumentation, because instrumenting them could affect the worst-case execution time (WCET) and thus violate existing timing constraints.

Figure 1.1: Execution time profiles of the OLPC keyboard controller [39]

#### 1.2.1 Goals and Contributions

In this thesis, we investigate different techniques for increasing the effectiveness of timeaware instrumentation. The following is a summary of our contributions:

- 1. Execution time profile shift-effectiveness metric (ETPsem) [63]: We propose the ETPsem to measure the effectiveness of a time-aware instrumentation approach, so that different approaches can be compared against each other. One way to measure the effectiveness of time-aware instrumentation is a visual inspection as seen in Figure 1.1. This involves manual assessment and lacks accuracy. Another way is to calculate the instrumentation coverage as the ratio of extracted information to what is expected or desired. We introduce ETPsem as a more efficient metric for time-aware instrumentation.

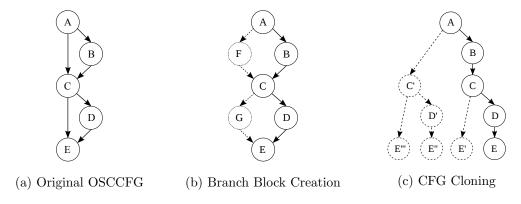

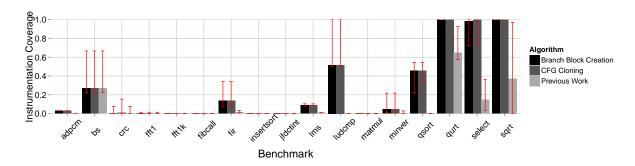

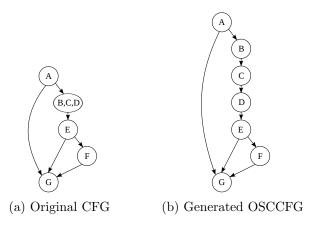

- 2. **Program transformation** [63]: A central element for time-aware instrumentation is to identify regions in the program which can be instrumented. We propose an algorithm that identifies instrumentable edges in a program's control-flow. An instrumentable edge is one that lends itself for time-aware instrumentation. Different

approaches can use these edges for program instrumentation. We demonstrate the utility of this algorithm by introducing Branch Block Creation and CFG Cloning as two such approaches to increase the effectiveness of time-aware instrumentation at the expense of code size.

- 3. Instrumentation on the WCP [68]: We propose a slack-based conditional instrumentation technique for debugging hard real-time programs. This instrumentation technique preserves functional behavior, and temporal behaviors of the original program while allowing the instrumentation of variables on the WCP. Conditional instrumentation allows the instrumented code to execute only when there is sufficient slack in the program. We accomplish this using a timer to record the available slack during execution. This is a run-time approach to check for slack. Then, we address the challenge of selecting points in the program code to insert such conditional instrumentations. We use a purely software technique to implement conditional instrumentation and compare it against a technique that extends the processor with instructions to perform the conditional checks.

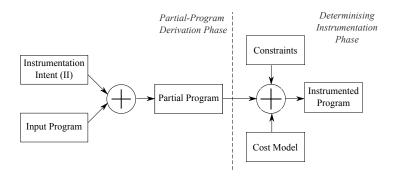

- 4. INSTEP [62]: Software systems are rich in extra-functional (or non-functional [132, 85]) requirements such as timing, code sizes, communication bandwidth, power consumption, and memory consumption. While our work focuses on time-aware instrumentation, other extra-functional properties might exist in the real-time system. Maintaining an extra-functional property during instrumentation is complicated and managing multiple properties simultaneously is even more so. Extra-functional properties can be competing where meeting one property might break another. We present a static instrumentation framework that gives the developer unprecedented control over what to instrument and what to preserve. It thereby presents the first fully-implemented instrumentation mechanism that considers multiple competing extra-functional properties. INSTEP uses trees to represent instrumentation intents and automata to represent cost models.

## 1.3 Chip-Multiprocessors for Real-Time Systems

Real-time embedded applications, and software in general, continue to evolve with increasing complexity. This increasing complexity of real-time applications translates into a need for higher computational power to satisfy their real-time requirements. Due to the limits on power consumption and heat dissipation in processors, increasing their performance is not a viable solution anymore. Multicore architectures pose themselves as a solution to the performance bottleneck. For the correct operation of the real-time system, a guarantee must be provided that the entire system is schedulable. This is done by ensuring that the temporal requirements of all tasks are met, which requires an estimate on the WCET of tasks and the worst-case communication latency between the tasks. Providing timing guarantees for hard real-time systems, however, on multicore interconnects is difficult. This is because conventional communication interconnects are designed to optimize the average-case performance. These, however, are a hindrance to accurately predicting the worst-case

communication time in the interconnects. Therefore, recent research focuses on developing custom network-on-chip (NoC) interconnects to facilitate their adoption as a platform for real-time applications.

Common NoC implementations include resource reservation and run-time arbitration (priority-aware) networks. Time division multiplexing (TDM) is an example of resource reservation networks. Resource reservation networks statically allocate resources to prevent contention between communication tasks in the network at runtime. Priority-aware networks, on the other hand, allow contention between communication tasks. Contention is resolved at runtime using priority-aware arbitration routers. TDM networks guarantee schedulability of tasks as part of their static allocation of resources and have small buffer requirements (one flit for guaranteed services and one packet for best-effort services) [44]. In this type of networks, if there is no data to be transmitted in a certain time slot, the slot will remain empty; thereby, not allowing other tasks to use it resulting in under-utilization of communication resources. For low latency communication, a larger proportion of slots are assigned; thus, causing low latency communication to be intertwined with the bandwidth when using TDM. Moreover, TDM networks do not cleanly support sporadic tasks. This is because sporadic tasks are triggered by external events and, hence, it is unknown at design time when exactly they start.

Priority-aware networks have better resource usage compared to TDM but require a worst-case latency (WCL) analysis to guarantee schedulability of the network tasks [126, 124]. A priority-aware network architecture was proposed by Shi and Burns [126, 124, 125, 127]. This architecture supports wormhole switching and priority arbitration between network messages. Shi and Burns also present a WCL analysis that we call flow-level analysis (FLA) that determines the worst-case communication latency in the priority-aware network [126, 124].

#### 1.3.1 Goals and Contributions

The most recent WCL analysis for priority-aware networks is FLA [126, 124]. This analysis is crucial to determine the schedulability of communication tasks and accordingly the feasibility of deploying a real-time application on a priority-aware network. FLA assumes that the paths taken by communication tasks are indivisible units of communication. Hence, FLA does not incorporate the effects of pipelining and parallel transmission of data in the network. Aspects, other than the WCL analysis, need as well to be considered for the successful deployment of real-time applications on priority-aware networks. These include mapping of tasks to the network cores, path-selection for the communication between tasks, and buffer space assignment to the routers of the network. Our goal is to provide an integrated solution to deploying real-time applications on priority-aware networks while considering pipelining and parallel data transmission in the networks. The following is a summary of our contributions:

1. Stage-level analysis (SLA) [64]: We propose a pipelined communication resource model for analyzing the worst-case latencies for hard real-time systems. This model

supports pipelined and parallel transmission of data over communication resources with fixed priority preemption. We also present an associated stage-level analysis that uses the pipelined communication resource model to produce tight WCL estimates. The model supports communication tasks that are either periodic or sporadic. This analysis is suitable for interconnects that use run-time arbitration such as the priority-aware network proposed by Shi and Burns [126, 124].

- 2. Offset-based worst-case response time (WCRT) analysis [65]: An important challenge in distributing hard real-time systems onto modern computing platforms is in developing WCRT analysis techniques that combine communication and computation execution latencies. Such WCRT analysis techniques must consider the WCL of data transmissions across the communication medium connecting the processing resources, and its effect on any dependent computation tasks to determine accurate WCRT estimates. We present extensions to both FLA and SLA to compute end-to-end worst-case latencies of applications including both computation and communication tasks. We also present a holistic analysis algorithm for computing the dynamic offsets and jitters of tasks.

- 3. Buffer space requirements [66]: To enable the deployment of real-time applications to priority-aware networks, recent research proposes WCL analyses for such networks. Buffer space requirements in priority-aware networks, however, are seldom addressed. Hence, we bound the buffer space required for valid WCL analyses and consequently optimize router design for application specifications by computing the required buffer space in priority-aware routers. In addition to the obvious advantage of bounding buffer space while providing valid WCL bounds, buffer space reduction decreases chip area and saves energy in priority-aware networks. We present a detailed buffer space analysis using each WCL analysis: namely stage-level buffer-space analysis (SLBA) and flow-level buffer-space analysis (FLBA).

- 4. Buffer space allocation in priority-aware routers: Although computing the buffer space bounds required for valid WCL analyses is necessary, it only provides an upper bound to the required buffer space. Further reduction of the buffer space is possible, but might lead to higher worst-case latencies. These higher worst-case latencies are acceptable as long as the deployed applications are schedulable. We extend SLA to incorporate buffer space limits and we present an algorithm for buffer space allocation in the priority-aware routers.

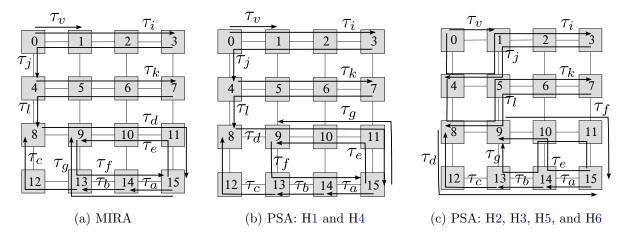

- 5. Path selection [67]: We propose a path selection algorithm (PSA) assisted by SLA that aims to improve the number of schedulable tasks by selecting appropriate paths in the priority-aware network. We use SLA because it considers the pipelining effect of worm-hole switched NoCs, and it provides tight WCET bounds. In particular, we propose an algorithm that utilizes observations from SLA to efficiently select paths in the priority-aware network. To avoid the high complexity of an optimal algorithm, our algorithm uses heuristics to find least interference paths and to consider lower priority tasks while selecting paths for the higher priority ones.

### 1.4 Organization

This thesis is organized as follows. Chapter 2 presents an overview of the related work on the research topics addressed in this thesis. Chapter 3 presents ETPsem and techniques to increase the effectiveness of time-aware instrumentation (time-aware instrumentation contributions 1-3). Chapter 4 presents INSTEP, a static time-aware instrumentation framework (time-aware instrumentation contribution 4). Chapter 5 presents the stage-level WCL analysis (CMPs for real-time systems contribution 1). Chapter 6 presents the offset-based WCRT analyses (CMPs for real-time systems contribution 2). Chapter 7 discusses the buffer space requirements and buffer space allocation in priority-aware routers (CMPs for real-time systems contributions 3 and 4). Chapter 8 discusses the proposed PSA for real-time systems on priority-aware networks (CMPs for real-time systems contributions 5). Chapter 9 concludes this thesis.

## Chapter 2

## Overview

In this chapter, we discuss the related work on the research topics addressed in this thesis. First, we overview related work on information extraction techniques. Next, we overview related work on the different aspects of deploying real-time applications on CMPs.

### 2.1 Information Extraction

We mentioned in Chapter 1 that information extraction techniques include tracing, sampling, and emulation. We review the related work on these topics in this section as well as related work on multi-objective compilation.

#### 2.1.1 Instrumentation

A program can be instrumented at the source code level either automatically or manually. In automatic instrumentation, a tool parses the program, may generate a control-flow graph (CFG), and eventually insert instrumentation points. An example of automatic instrumentation tools is the GNU compiler collection (GCC) profiling and code coverage instrumentation tool. On the other hand, in manual instrumentation, developers are in control, walk through the source code, and insert instrumentation statements whenever they see fit. Traditional debugging is a typical use case for manual instrumentation. Assume that the developer has received a bug report including a test case that causes the bug. Typical behavior is that the developer tries to identify the origin of the bug by manually inserting printf() statements at key points and rerunning the test case [69, 131]. By inserting more printf() statements and removing unnecessary ones, the developers test different bug hypotheses until they find the right one and can proceed with fixing the bug. Obviously, manual instrumentation, while being the most flexible, has the worst characteristics with respect to interference, because developers cannot estimate changes in the WCET [152] or memory consumption for modern computer architectures. This makes it also hard to find timing-related software defects using this method, because the instrumentation might temporarily clobber the defect.

Some instrumentation tools are capable of inserting instrumentation points to binary executables. This can happen either statically or dynamically during program execution. QPT is a program profiler and tracing system that measures the execution frequency of basic blocks and control flow [75]. EEL also provides similar functionalities for analysis and modification of executables for while abstracting details of instruction sets and executable file formats [74]. ATOM is another framework for building customized program analysis tools [134]. Binary static instrumentation tools also include Etch [119] the program performance evaluation and optimization system, and Morph [156] which re-optimizes programs to apply profile-based and other platform specific optimizations. Multiple tools exist that support dynamic binary instrumentation. Dynamic binary instrumentation tools that use code transformation during program execution include Dyninst [21], Kerninst [141], Detours [52], and Vulcan [36]. Most of these instrumentation tools, however, suffer from transparency issues, i.e., they modify native behavior of the program under analysis [20]. Examples of transparent dynamic binary instrumentation tools that have software code caches and dynamically compile binaries include Pin [88], DynamoRIO [19], and Valgrind [103]. Other examples of dynamic binary instrumentation also include DTrace, SystemTAP, Frysk and GDB. These tools overwrite code locations with trap instructions to execute instrumentation code, then after the interrupt handling and instrumentation code execution, the original instructions are restored and executed.

Some instrumentation tools are more oriented towards the analysis of parallel programs. Mellor-Crummey et al. propose a software instruction counter [92] to help debug parallel programs using the integrated approach to parallel program debugging and performance analysis on large-scale shared-memory multiprocessors introduced by Fowler et al. [41]. Thane [143] and Dodd et al. [32] present integrated approaches for monitoring and debugging of real-time systems. Kim et al. uses formal requirements for the monitoring and checking of Java programs at run time [70]. Moore et al. [96] and Omre [107] introduce hardware trace debuggers. Some other examples of hardware trace debuggers include the JTAG and NEXUS trace debugging interfaces. Cargill et al. use dedicated hardware counters to support the debugging and profiling of compiled programs [23]. There also exists work on replay mechanisms in hardware tracing. Replay mechanisms record sufficient information during program execution that later on helps the developer deterministically recreate an equivalent execution. A lot of research has been conducted on hardware supported replay mechanisms for non-deterministic applications [121, 120, 138, 148, 7, 50, 104, 95]. Some work also exists on tracing interrupts during program execution [137, 45]. Although such approaches naturally provide low interference, they can still have a significant impact on performance [97] and behavior and thus warrant research on characterizing interference levels and possible bounds.

All these instrumentation methods are known to affect the behavior of the program including its temporal behavior which is sometimes not acceptable in real-time embedded systems. Partial instrumentation, as a means of ensuring timeliness, can be used to build inductive debugging mechanisms for deployed resource and space constrained systems. Since it is hard to reproduce bugs from user bug reports [15], even having a partial trace can help extract information. Partial traces help extract information and can be input to additional debugging tools [123, 114].

Fischmeister and Lam [39] introduce time-aware instrumentation which honors the programs timing constraints, especially the worst-case behavior. The idea was mainly to instrument programs at code locations that leaves the WCET of the program unmodified. The proposed tool instruments programs, optimizing for code space and instrumentation coverage, while meeting time constraints.

### 2.1.2 Sampling

The goal of execution monitoring is to record an execution trace of the program under test. The external monitor observes the execution of the program and needs to log the program's execution path. In sampling-based tracing, the external monitor periodically examines the state of the program and stores it. It is clear that we can obtain more accurate traces through increasing the sampling frequency at the price of sampling overhead.

Liblit et al. present a sampling infrastructure with low overhead that collects samples from numerous runtime executions [84]. These samples are used for bug isolation in subsequent program executions. Liblit et al. also present a random sampling technique for statistical multiple bug isolation in complex applications [83]. Zheng et al. propose an interactive collective voting scheme for program runs to statistically identify multiple bugs in software [157]. Fischmeister et al. introduce an approach to bound the cost of monitoring program execution through fixed rate sampling [40]. This approach discusses optimal tradeoffs between accuracy and overhead. It also provides a framework for the reconstruction of system state and execution paths. Thomas et al. extends the work in [40] through investigating the expressiveness and efficiency of different marker schemes [145]. This work also proposes and discusses the applicability of two new marker schemes. Gprof, which is part of the GNU binary utilities, uses an operating system virtual timer to sample the program at regular intervals [46]. It can also produce a call graph through the instrumentation of each function entry in the program code. However, the effect of this kind of instrumentation on program execution cannot be estimated.

Another type of sampling involves the usage of performance counters. These counters are used to count instructions, cache misses, branch delays, and other similar metrics. OProfile is an example of a Linux-based performance analysis tool that uses performance counters sampling [81]. Cheung et al. propose Endoscope, a declarative aquisitional software monitoring framework, to monitor the state and performance of program execution [26]. Jiang et al. introduce metric-correlation models for bug detection in software systems and fault localization [58]. Ball et al. present algorithms that optimize the placement of profiling code according to the estimated and measured frequency of each basic block execution in a CFG [9]. Hutchins et al. [53] and Frankl et al. [42] propose branch-based monitoring techniques using definitive-use associations (DUAs). DUA is the association between variable definition (value stored in memory) and variable use (value fetched from memory) which are used for control-flow and data-flow coverage. Santelices et al. present a method to efficiently monitor DUAs based on branch monitoring, and to accurately predict some DUAs from branch coverage information [122].

#### 2.1.3 Emulation

An emulated system can be totally controlled and analyzed during its execution. This increase in flexibility comes at the expense of performance (slower real-time execution). Examples of emulation systems are Unisim [6] and Qemu [11] which emulate different processor architectures. Another example is the Valgrind emulation system [103] which is used for program instrumentation, validation, and performance analysis. Valgrind is a framework for creating dynamic analysis tools for memory debugging, memory leak detection, and cache profiling. Valgrind has tools for the detection of memory and thread bugs, profiling of cache and branch prediction, heap profiling, and overrun detection in heaps, stacks, or arrays. Phillips also presents work on using an emulator with traces [113].

### 2.1.4 Multi-Objective Compilation

Naik and Palsberg [98] present a framework for code-size-aware compilation. They formulate register allocation as an Integer linear programming (ILP) problem. The objective is to minimize target code size under a set of linear constraints. Lee et al. [78] introduce a framework to balance the tradeoffs between code size, execution time, and energy consumption in a real-time embedded system. It minimizes a system's cost function while satisfying the design constraints. They enable a tradeoff between code size and execution time based on a dual instruction set processor. The framework satisfies the design constraints and assigns code/WCET pairs to the tasks to minimize the system cost function.

## 2.2 Chip-Multiprocessors

Buses are the most popular communication architecture between system-on-chip (SoC) components. Buses are widely used due to their flexibility and easy adoption. On the other hand, they are power inefficient and lack scalability [76]. Point-to-point connections offer dedicated communication channels between the SoC components. However, the required number of wires for the point-to-point scheme makes it unscalable [30]. Another architecture alternative is SoC interconnect architecture that model multiprocessor systems. NoC interconnects [30, 13] offer a reusable solution to the limitations of buses and point-to-point connections. In this section, we overview some aspects of the NoC interconnects.

### 2.2.1 Architecture and Operation

The NoC topology determines the layout of the network nodes as well as the connections between the nodes. Mesh [73] and torus [30] interconnects are amongst the most popular NoC topologies.

The way packets traverse the NoC routers is determined by the switching protocol. Circuit switching protocols establish dedicated connections between source and destination

pairs for packet traversal. Packet switching, on the other hand, does not reserve links. Examples of packet switching protocols include store and forward, virtual cut through, and wormhole switching. In store and forward [34], a router must buffer a complete packet before forwarding it to a neighboring router. This increases the transmission latency as well as buffer requirements. In virtual cut through [33], a packet does not have to be buffered and can be directly transmitted to another router. However, if the receiving router is busy, then the complete packet must be buffered. Wormhole switching [105] operates similarly but reduces the buffering requirement to the flit level of the packet. Virtual channels (VCs) [31] can be used to provide multiple buffer queues for the same physical channel. Wormhole switching along with using VCs increases the network utilization by reducing blockage in the NoC.

Routing algorithms define the paths that packets take in the NoC [34]. In deterministic routing, the path selection process is deterministic for any source and destination pair. In adaptive routing, on the other hand, the routes can change dynamically to, for instance, avoid congestion in the network. While adaptive routing increases the network efficiency, it adds a communication overhead and has more complicated logic compared to deterministic routing.

Flow control mechanisms are responsible for controlling the traversal of packets between the network routers and for the prevention of overflow in buffers. The handshake flow control involves the exchange of valid and acknowledgement signals between the sender and the receiver, respectively [155]. While handshaking is simple, it has a high overhead. In the ACK/NACK flow control scheme, the receiving router will respond with an acknowledgment (ACK) signal if it has enough buffer space to accept the incoming flit, otherwise it will reply with a negative acknowledgment (NACK) signal [115]. This scheme is combined with a GO-BACK-N policy in which the sender sends flits continuously without waiting for ACK signals until it receives a NACK. Upon the occasion of receiving a NACK, the sender resends the flit for which the NACK was received as well as all the flits that were sent after it. The ACK/NACK scheme is more efficient than handshaking, but requires expensive buffering for resending purposes. Credit-based flow control uses credits to avoid overflowing full buffers [116]. An upstream router has credits equivalent to the available buffer space at a downstream router. These credits are decremented as the upstream router sends flits downstream and are incremented as the downstream router frees buffer space.

#### 2.2.2 Real-Time Communication

There are several research efforts that enable real-time communication over CMPs [44, 87, 128, 17]. Bjerregaard and Sparso [17] present a clock-less NoC called message passing asynchronous NoC (MANGO) for guaranteed services. They use an asynchronous latency guarantee arbiter, which consists of a set of VCs, and priority selection and arbitration modules to support real-time communication. MANGO combines wormhole switching with virtual circuits and provides guaranteed service in terms of bandwidth and latency [17]. The arbiter used by MANGO ensures that a flit in a virtual channel can block a lower priority flit only once. This is different from the fixed priority scheme used in this work. Wiklund

and Liu [151], and Wolkotte et al. [153] use circuit switching that requires establishing a connection between source and destination before sending data packets.

Millberg et al. [93] and Lu et al. [87] use the TDM approach for communication. TDM divides the link access into equal time slots such that a communication task can use the slot time to transfer its own packets. Æthereal [44] uses TDM to guarantee WCL bounds on real-time communication tasks. In each time slot, the router forwards the data from input to output ports. According to a pre-determined slot table, network adapters inject packets into the routers. Hence, TDM avoids contention between packets in the network, and has no need for arbitration and buffering of packets [133]. The WCL depends on the slot allocation [87], which computes the time for the last flit of a task to reach its destination. Æthereal, like MANGO, combines guaranteed service with best-effort to increase its resource utilization [118]. Hence, the Æthereal router design [44] supports both guaranteed service and best-effort traffic. Each router contains a slot table to control the switching of the guaranteed service traffic.

A light version of Æthereal, aelite [48], is available. It carries the routing information inside packets headers, and only supports guaranteed service traffic. This simplifies the routers by avoiding the use of slot tables. Another version of aelite is called dAElite [136]. It supports multi-cast routing by using slot tables.

In TDM NoCs, a global notion of time is required for the usage of the slot tables in the routers. This can be achieved using a fully-synchronous NoC implementation [133]. This, however, might be practically infeasible due to different operating frequencies on cores as well as difficulties with clock distribution. Alternative implementations of the NoC are, hence, needed. In [48], a mesochronous implementation of aelite is presented. This can be achieved by adding first in first out (FIFO) buffers on the links to compensate for phase differences between clocks.

Shi and Burns [126, 128] propose the use of priority-based routers with wormhole switching to support real-time communication. This approach supports multiple priorities, and their routers ensure that higher priority tasks can preempt lower priority ones.

### 2.2.3 Timing Analysis

The problem of the WCL computation for inter-process communication in real-time systems is addressed in [60, 111, 110]. Authors develop an upper bound on the delivery time of messages. The downsides of these methods are the overhead of the establishment and tear down of channels between source and destination pairs, as well as under utilization of the system's resources. They also store packets at intermediate nodes which leads to expensive buffer capacity for storing early arriving packets and queuing packets in order of arrival [60].

The two common approaches used in customizing interconnects for real-time applications use resource reservation or run-time arbitration. An example of a resource reservation approach is TDM [93, 44, 87]. This approach statically allocates slots to communication tasks such that no other task can use that slot other than the assigned one. In the event

that there is no data to be transmitted in that slot, the slot remains empty; thereby, not allowing other tasks to use it resulting in under-utilization of communication resources. For low latency communication, a larger proportion of slots are assigned; thus, causing low latency communication to be inter-twined with the bandwidth when using TDM. Note also that TDM does not cleanly support sporadic tasks. This is because sporadic tasks are triggered by external events and, hence, it is unknown at design time when exactly they start.

Run-time arbitration, on the other hand, arbitrates access to communication resources at run-time. Hence, contention is expected, and the WCL analysis accounts for these contentions. One such communication architecture was proposed by Shi and Burns [126, 128] that supports wormhole switching with priority-based arbiters that allow higher priority communication to preempt lower ones. Moreover, this approach overcomes the tight coupling of latency and bandwidth suffered by TDM and TDM-like approaches, and it allows for a variety of communication task types with its use of priorities. Shi and Burns also present a WCL analysis, which we call FLA [126, 128] that determines the WCLs between communicating tasks. Their analysis includes direct and indirect interferences from other communications. This analysis is central in determining the schedulability of the communication tasks. However, FLA assumes a model where the tasks are indivisible units of communication. As a consequence, FLA does not incorporate the effects of pipelining and parallel transmission of data in its communication model. This restriction in the model results in higher upper-bounds on the communication latencies.

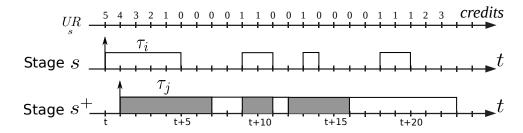

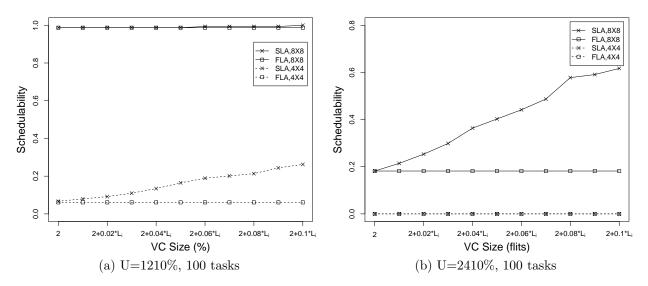

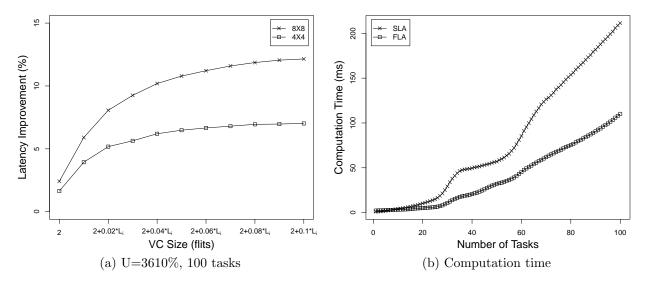

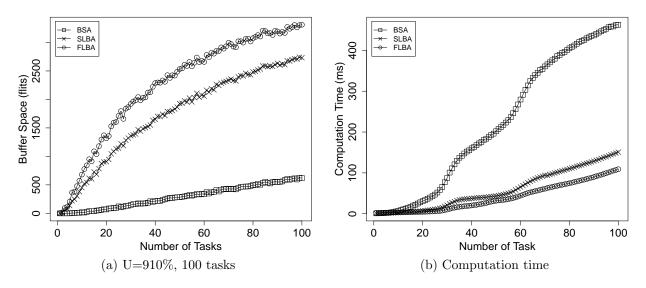

There exists other techniques to compute end-to-end worst-case delays on networks. These include network calculus [154], an extension of network calculus for real-time systems called real-time network calculus [144], holistic analysis [146, 89, 108], and delay calculus [55, 56].