# CMOS Impedance Measurement Array for Cell Sensing

by

Areeb Ali

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2015

© Areeb Ali 2015

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Impedance measurement plays a vital role in determining the physical and chemical properties of live cells under different environmental conditions and aids in the development of cellular models for life science research and new medicines to fight disease. In order to improve the fidelity and spatial resolution of bio-impedance measurement systems, cell sensing platforms are being constructed using silicon chips where live cells interact with integrated microelectronic sensors through an on-chip electrode array. Our proposed complementary metal-oxide-semiconductor (CMOS) sensor array measures the impedance of complex cellular samples using a mixed-signal-based frequency response analysis (FRA) approach to extract and convert the real and imaginary parts of the cell impedance. The system is implemented using a synchronous voltage-to-frequency converter designed to operate over an input frequency range from 0.7 Hz to 2 kHz with a programmable nominal resolution up to 16 bits. Unlike previous work, we apply a switched-capacitor-based offset correction scheme to reduce the effect of multiplying integrator input offset on the sensor interface. The chip features an  $8 \times 6$  surface electrode array of individually-addressable working electrodes connected to four independent impedance extraction channels for parallel data readout. The device is fabricated in a standard 0.18  $\mu$ m CMOS technology, where each sensor channel consumes only 94  $\mu$ W from a 1.8 V supply, and has been experimentally verified to provide linear conversion over an input current amplitude range from 40 pA to 60 nA.

#### Acknowledgments

I would like to express deepest gratitude to my supervisor Dr. Peter Levine for his encouragement, support and expert guidance throughout my graduate study and research. Without his experience, wisdom and patience my thesis work would have been extremely difficult and complicated. My thanks to the thesis readers Professor David Nairn and Professor Chris Backhouse for their constructive feedback.

I would also like to thank Phil Regier and other technical staff at University of Waterloo, who supported and resolved any issues I faced during the entire academic period.

Special thanks to my fellow gradate students Alireza, Mark, and Abdullah, who helped and advised me at various stages of the research work.

In the end I would like to acknowledge the unconditional support and love from my family, without which this thesis would not have been possible.

### Dedication

This thesis is dedicated to my beloved country Pakistan and its brave people.

# **Table of Contents**

| Li | st of          | Tables                                                       | ix |

|----|----------------|--------------------------------------------------------------|----|

| Li | st of          | Figures                                                      | xi |

| 1  | Intr           | roduction                                                    | 1  |

|    | 1.1            | Cell Membrane Impedance Model                                | 6  |

|    | 1.2            | Electrochemical Impedance Spectroscopy (EIS)                 | 9  |

|    |                | 1.2.1 Nyquist Plot                                           | 11 |

|    | 1.3            | CMOS Integrated Circuits for Cellular Impedance Measurements | 12 |

|    |                | 1.3.1 Impedance Extraction Techniques                        | 13 |

| 2  | $\mathbf{Sys}$ | tem Architecture and Modeling                                | 22 |

|    | 2.1            | System Architecture                                          | 22 |

|    | 2.2            | System Specifications                                        | 24 |

|    | 2.3            | Novel Implementation of FRA Algorithm                        | 27 |

|    |                | 2.3.1 Real Part Extraction                                   | 28 |

|   |      | 2.3.2   | Imaginary Part Extraction          | . 29 |

|---|------|---------|------------------------------------|------|

|   | 2.4  | Imped   | lance-to-Digital Converter Design  | . 30 |

|   | 2.5  | Princij | ple of Impedance Extraction        | . 34 |

|   | 2.6  | Resolu  | tion of Impedance Sensor           | . 37 |

|   | 2.7  | Dynan   | nic Range Programmability          | . 37 |

|   | 2.8  | Operat  | tional Amplifier Offset Correction | . 41 |

|   | 2.9  | System  | n Specifications                   | . 43 |

| 3 | Circ | cuit De | esign                              | 44   |

|   | 3.1  | Integra | ator                               | . 44 |

|   |      | 3.1.1   | Integrator Design                  | . 47 |

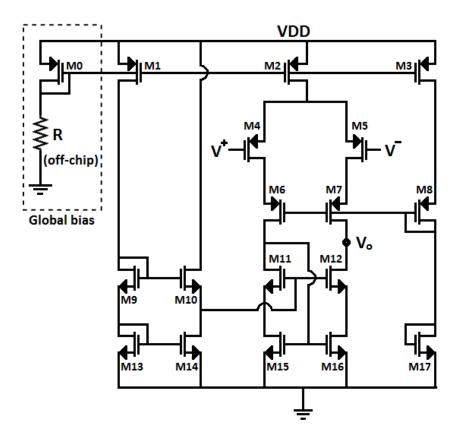

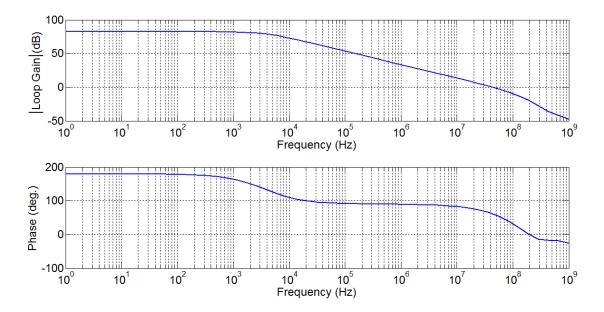

|   |      | 3.1.2   | Operational Amplifier Design       | . 48 |

|   |      | 3.1.3   | Op Amp Output Signal Swing         | . 52 |

|   |      | 3.1.4   | Op Amp Slew Rate                   | . 53 |

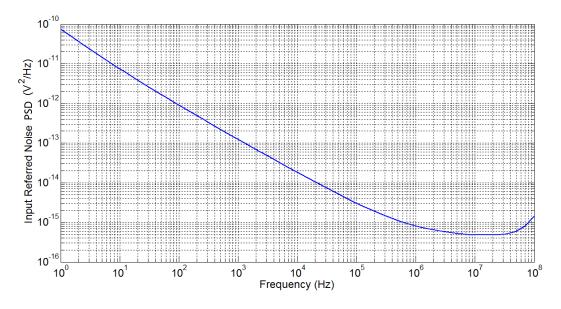

|   |      | 3.1.5   | Telescopic Cascode Amplifier Noise | . 54 |

|   | 3.2  | Compa   | arator Design                      | . 56 |

|   | 3.3  | DC Re   | eference Current Source Design     | . 61 |

|   | 3.4  | Non-ov  | verlapping Clock Generator         | . 64 |

|   | 3.5  | 16-bit  | Bi-directional Counter Design      | . 66 |

|   | 3.6  | Paralle | el-to-Serial Converter             | . 67 |

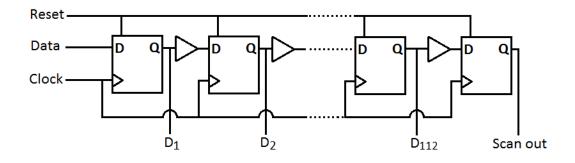

|   | 3.7  | Scan C  | Chain                              | . 68 |

|    | 3.8   | Simula | ation Results                           | 69  |

|----|-------|--------|-----------------------------------------|-----|

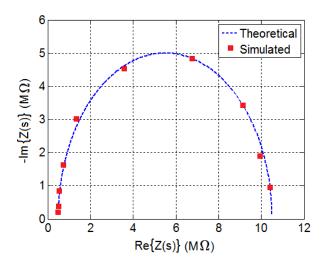

|    |       | 3.8.1  | Nyquist Response                        | 69  |

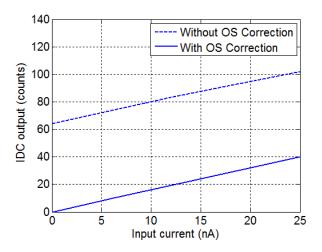

|    |       | 3.8.2  | Offset Correction                       | 70  |

| 4  | Exp   | erime  | ntal Results                            | 71  |

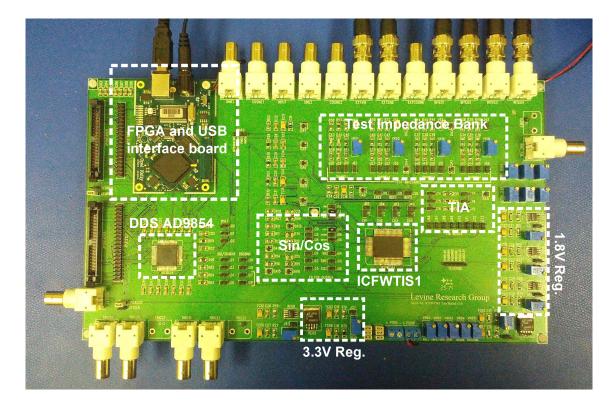

|    | 4.1   | Exper  | imental Setup                           | 73  |

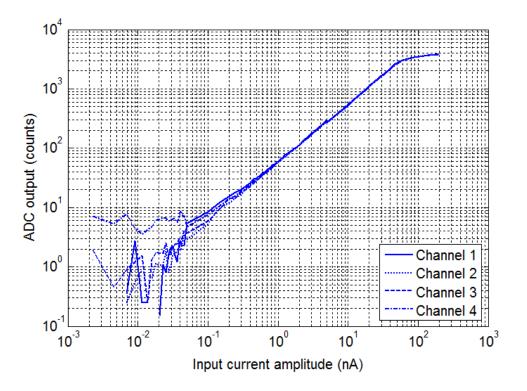

|    |       | 4.1.1  | Amplitude Linearity of Impedance Sensor | 75  |

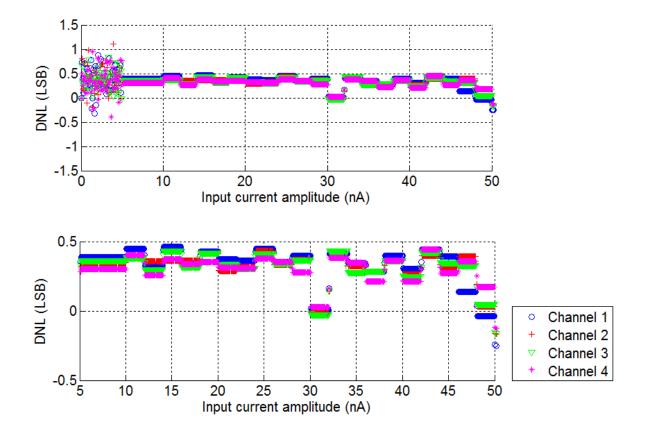

|    |       | 4.1.2  | Differential Nonlinearity Error         | 76  |

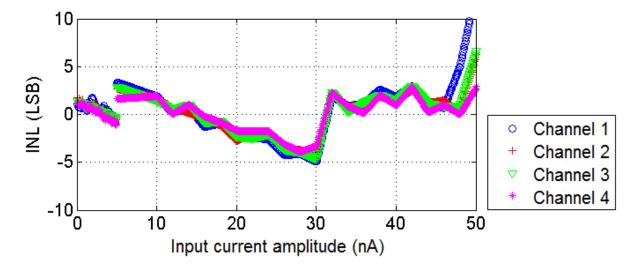

|    |       | 4.1.3  | Integral Nonlinearity Error             | 78  |

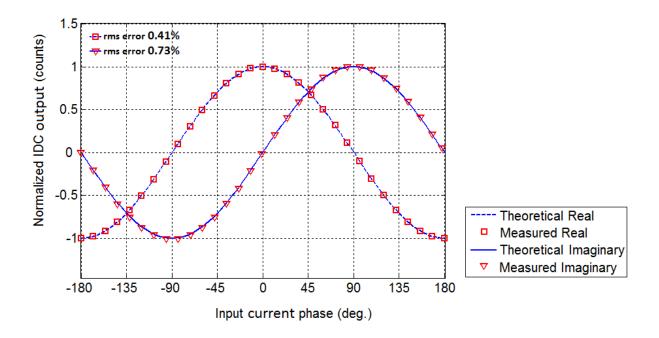

|    |       | 4.1.4  | Phase Linearity of Impedance Sensor     | 79  |

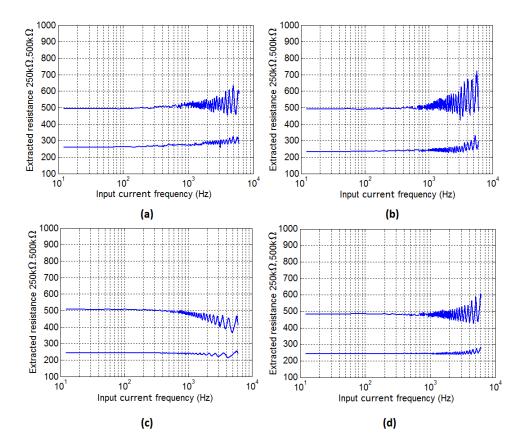

|    |       | 4.1.5  | Frequency Response                      | 80  |

|    |       | 4.1.6  | Signal-to-Noise Ratio and Dynamic Range | 82  |

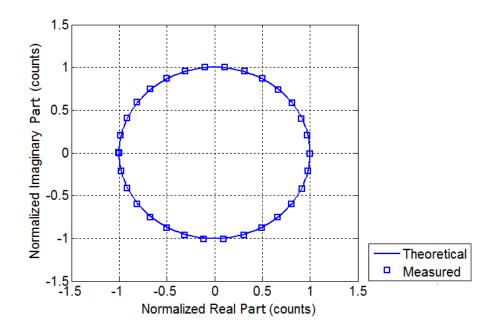

|    |       | 4.1.7  | Nyquist Plot                            | 84  |

|    |       | 4.1.8  | Op Amp Input Offset Correction          | 85  |

|    | 4.2   | Comp   | arison of the IDC channels              | 86  |

| 5  | Con   | clusio | n                                       | 88  |

| A  | PC    | B Desi | gn                                      | 90  |

| в  | Chi   | p Pack | age and Bonding Diagram                 | 96  |

| С  | Sca   | n Chai | in Control Signals                      | 100 |

| Re | efere | nces   |                                         | 103 |

# List of Tables

| 1.1 | Calculated values of membrane resistance and capacitance for different elec-               |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | trode areas covered by a cellular layer                                                    | 8  |

| 1.2 | Performance parameters of the analog coherent detection architecture [7].                  | 16 |

| 1.3 | Measured performance parameters of lock-in IDC [1]                                         | 20 |

| 2.1 | Dynamic range programmability of IDC for 50 nA reference current at 100 kHz clock.         | 38 |

| 2.2 | Dynamic range programmability of IDC for 200 nA reference current at 100 kHz clock.        | 39 |

| 2.3 | Dynamic range programma<br>bility of IDC for 1 $\mu$ A reference current at 100 kHz clock. | 40 |

| 2.4 | System specifications                                                                      | 43 |

| 3.1 | Telescopic cascode amplifier transistor dimensions                                         | 51 |

| 3.2 | Op amp design specifications and simulated results                                         | 55 |

| 3.3 | Comparator device dimensions.                                                              | 58 |

| 3.4 | Comparator design specifications and performance                                                               | 60  |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 3.5 | Cascode current mirror dimensions                                                                              | 63  |

| 3.6 | Simulated non-overlapping clock interval for all corners at standard 1.8 V supply voltage and 27°C temperature | 65  |

| 4.1 | Input voltage and resistor values used to generate test currents                                               | 75  |

| 4.2 | Performance comparison of the IDC channels.                                                                    | 86  |

| 4.3 | Performance comparison with Yang [1].                                                                          | 87  |

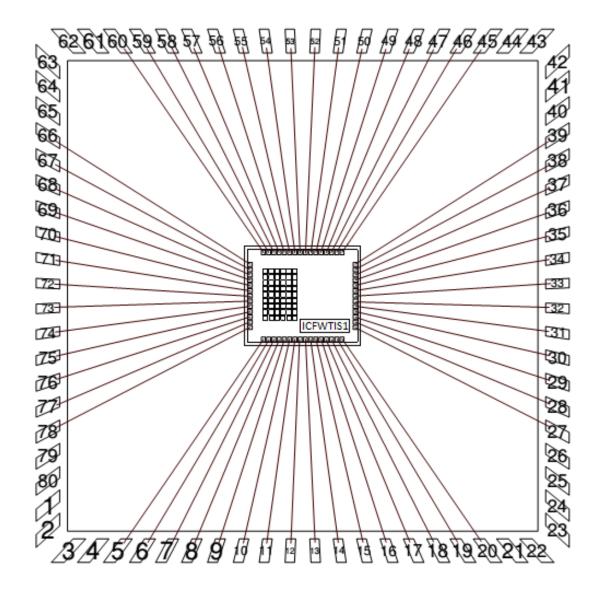

| B.1 | CQFP-80 pin mapping table (contd)                                                                              | 97  |

| B.2 | CQFP-80 pin mapping table.                                                                                     | 98  |

| C.1 | Digital control signals of the scan chain (contd)                                                              | 101 |

| C.2 | Digital control signals of the scan chain.                                                                     | 102 |

| C.3 | Biasing resistor values.                                                                                       | 102 |

# List of Figures

| 1.1  | Impedance measurement system for cell motion detection (adapted from [3]).      | 3  |

|------|---------------------------------------------------------------------------------|----|

| 1.2  | Diagram of cells in tissue culture emphasizing the dimensions at cell-electrode |    |

|      | interface (adapted from [3])                                                    | 4  |

| 1.3  | Basic human cell membrane structure.                                            | 6  |

| 1.4  | Passive circuit model of a cellular sample and electrode-electrolyte interface. | 7  |

| 1.5  | Simplified passive circuit model of a cell membrane                             | 8  |

| 1.6  | Block diagram of a general impedance spectroscopy system                        | 9  |

| 1.7  | General Nyquist plot of the cell impedance for model given in Fig. 1.5          | 12 |

| 1.8  | Block diagram of the FFT approach.                                              | 13 |

| 1.9  | System block diagram for a frequency response analysis approach                 | 14 |

| 1.10 | Analog coherent detection architecture for impedance measurement from [7].      | 15 |

| 1.11 | Principle schematic of a lock-in IDC circuit, adapted from [1]. $\ldots$ .      | 17 |

| 1.12 | Waveform showing $\varphi$ and its multiplication with input ac signal          | 18 |

| 2.1  | Block diagram of the multi-channel impedance measurement system                 | 23 |

| 2.2  | Nyquist plot of typical cellular impedance for 85 $\mu$ m×85 $\mu$ m working electrode area.                                                                                                                                     | 24       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.3  | Effect of 1% increase in $C_m$ value on (a) magnitude (b) phase of input current level.                                                                                                                                          | 25       |

| 2.4  | Change in output current magnitude and phase due to 1% membrane ca-<br>pacitance increase.                                                                                                                                       | 26       |

| 2.5  | Block diagram showing the proposed impedance extraction approach based<br>on the FRA algorithm.                                                                                                                                  | 28       |

| 2.6  | Multiplier signal $\varphi(t)$ definition. (a) In phase with $sin(\omega t)$ (b) in phase with $cos(\omega t)$ .                                                                                                                 | 30       |

| 2.7  | Circuit diagram of impedance-to-digital converter built using an SVFC                                                                                                                                                            | 31       |

| 2.8  | SVFC waveforms when the output current is (a) equal to zero and (b) greater than zero.                                                                                                                                           | 32       |

| 2.9  | Simulation waveforms of the SVFC based impedance sensor for 200 k $\Omega$ resistance at 390.6 Hz input signal frequency. (a) Input ac voltage signal, (b) comparator A output, (c) integrator output, and (d) flip-flop output. | 33       |

| 2 10 | Implementation of the offset correction technique.                                                                                                                                                                               | 33<br>42 |

|      | Offset correction circuit for (a) the first half and (b) the second half of the input period T.                                                                                                                                  | 42       |

| 3.1  | Ideal integrator.                                                                                                                                                                                                                | 45       |

| 3.2  | Frequency magnitude response of a non-ideal integrator.                                                                                                                                                                          | 46       |

| 3.3  | Circuit diagram of telescopic cascode amplifier.                                                                                                                                                                                 | 49       |

| 3.4  | Simulated loop gain of the telescopic cascode op amp in unity feedback (a)     |    |

|------|--------------------------------------------------------------------------------|----|

|      | magnitude (dB) (b) phase (deg.), (TT corner at $27^{\circ}$ C)                 | 51 |

| 3.5  | Input-referred noise voltage PSD of the telescopic cascode amplifier           | 55 |

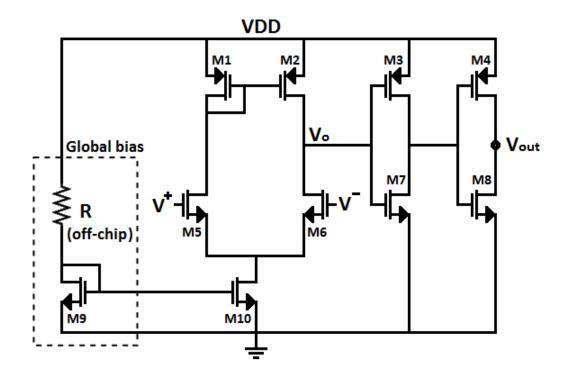

| 3.6  | Circuit diagram of the comparator used in the IDC                              | 58 |

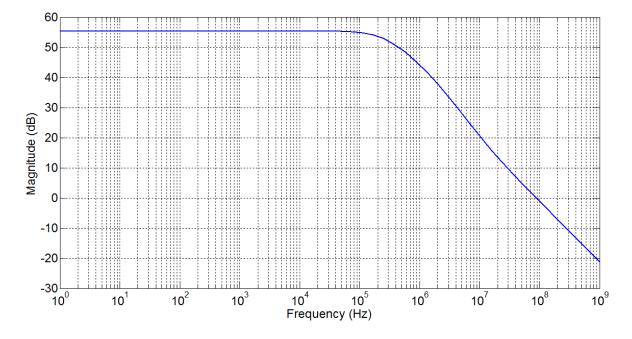

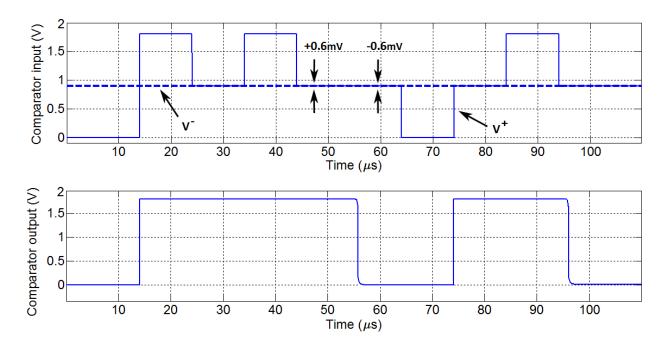

| 3.7  | Magnitude of comparator frequency response from input to $V_o$                 | 59 |

| 3.8  | Transient response of the comparator                                           | 60 |

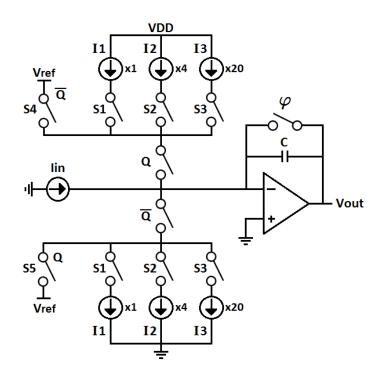

| 3.9  | DC reference current sources I1, I2, and I3                                    | 61 |

| 3.10 | Cascode current mirror circuit design                                          | 62 |

| 3.11 | Transistor channel length (a) NMOS (b) PMOS                                    | 63 |

| 3.12 | NOR gate implementation of non-overlapping clock generator                     | 64 |

| 3.13 | Non-overlapping clock waveforms: (a) Rising edge delay (b) Falling edge delay. | 65 |

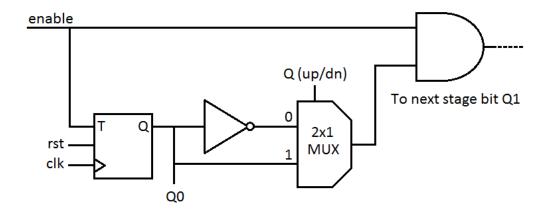

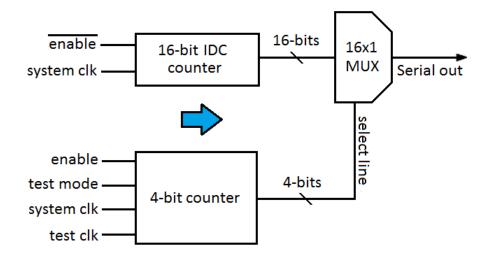

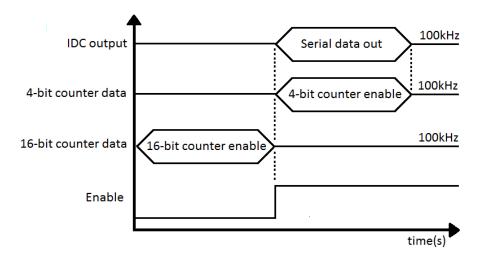

| 3.14 | Single stage of the 16-bit counter.                                            | 66 |

| 3.15 | Circuit for parallel to serial converter                                       | 67 |

| 3.16 | Parallel-to-serial converter waveforms                                         | 68 |

| 3.17 | Scan chain circuit.                                                            | 69 |

| 3.18 | IDC Nyquist plot of the simulated values.                                      | 70 |

| 3.19 | IDC output waveforms with and without offset correction.                       | 70 |

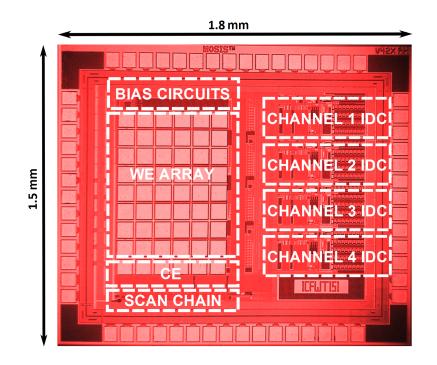

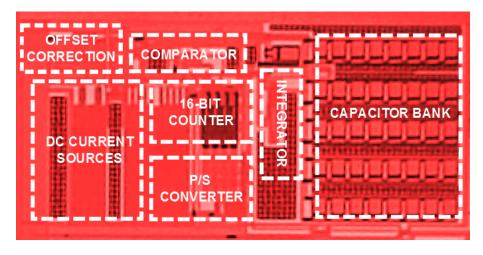

| 4.1  | Photograph of the fabricated chip                                              | 72 |

| 4.2  | IDC channel components                                                         | 72 |

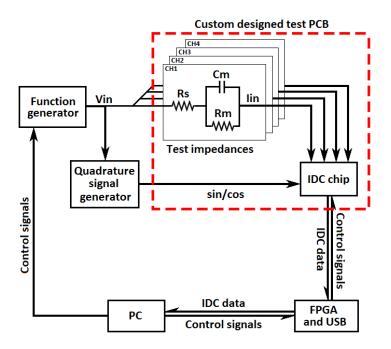

| 4.3  | Block diagram of the IDC chip test setup.                                      | 73 |

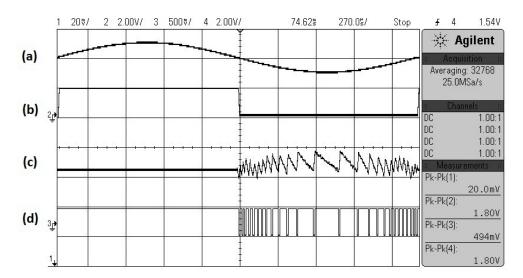

| 4.4  | IDC oscilloscope waveforms.                                                              | 74 |

|------|------------------------------------------------------------------------------------------|----|

| 4.5  | Linear range of IDC channels.                                                            | 76 |

| 4.6  | Differential nonlinearity error of the IDC channels.                                     | 77 |

| 4.7  | Integral nonlinearity error of the IDC channels.                                         | 78 |

| 4.8  | Phase response of IDC channel 4                                                          | 79 |

| 4.9  | Nyquist plot of the IDC for variable input phase.                                        | 80 |

| 4.10 | IDC frequency response of (a) channel 1, (b) channel 2, (c) channel 3, and               |    |

|      | (d) channel 4                                                                            | 81 |

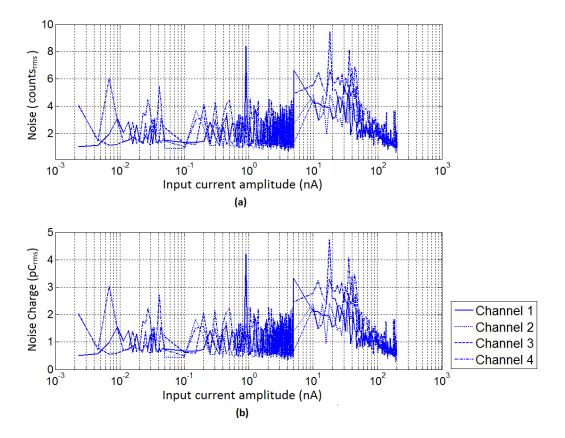

| 4.11 | Measured noise of the IDC channel output                                                 | 82 |

| 4.12 | SNR of the IDC channels.                                                                 | 83 |

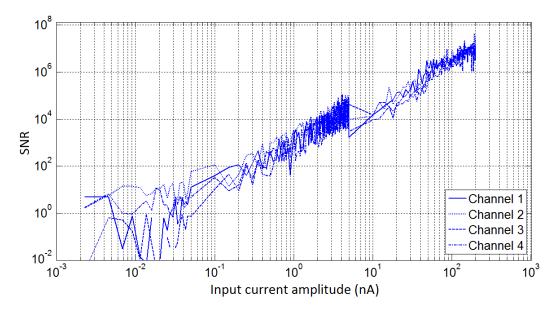

| 4.13 | Nyquist plot of the ideal and extracted test impedance where $R_s=500 \text{ k}\Omega$ , |    |

|      | $R_m = 10 \text{ M}\Omega$ , and $C_m = 2 \text{ nF}$ .                                  | 84 |

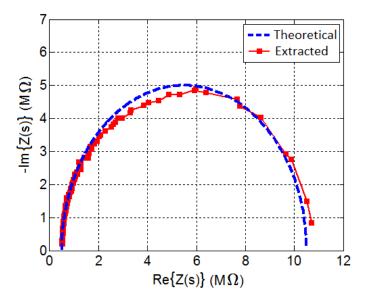

| 4.14 | Extracted impedance: (a) Magnitude (b) Phase                                             | 85 |

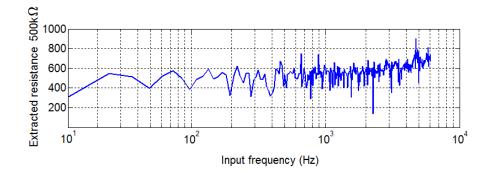

| 4.15 | Extracted impedance value with offset correction circuit enabled                         | 86 |

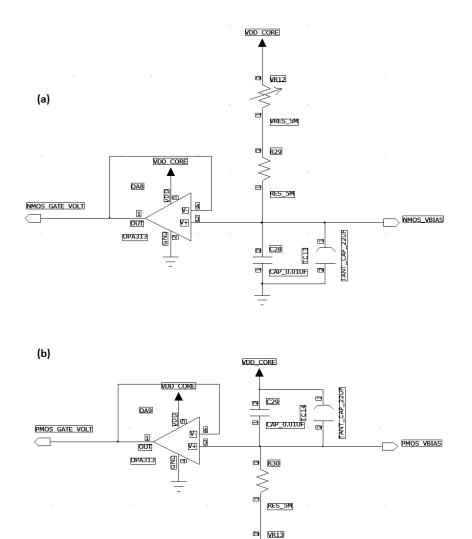

| A.1  | Circuit used to provide the bias voltages to the chip, (a) NMOS bias circuit             |    |

|      | (b) PMOS bias circuit.                                                                   | 91 |

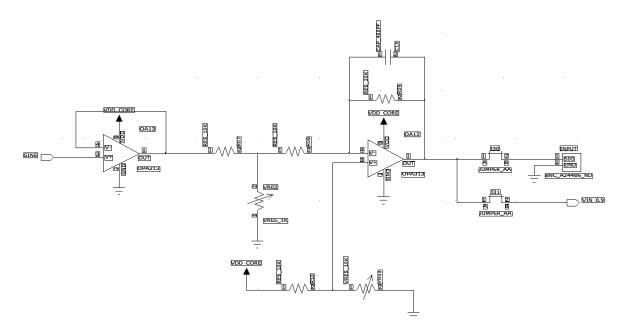

| A.2  | Circuit to control amplitude and dc level of quadrature signals                          | 92 |

| A.3  | Transimpedance amplifier to measure chip currents                                        | 93 |

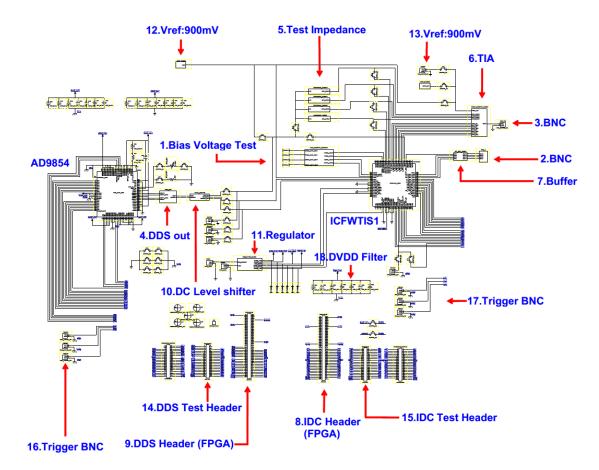

| A.4  | Test board schematic of the impedance sensor                                             | 94 |

| A.5  | FR-4 PCB test board for the impedance sensor.                                            | 95 |

| B.1  | Bonding diagram of the sensor chip                                                       | 99 |

# Chapter 1

# Introduction

Bioimpedance analysis enables the study of the physical and chemical properties of mammalian cells under different conditions and environments. The way live cells react to external stimuli helps to determine the effect of various chemical compounds and agents on the morphology of cells. This process finds applications in the fields of drug screening, DNA testing, security monitoring [1], and water purification [2].

The motility of live cells is an important parameter in the above applications and is normally observed by time lapse microscopy. Cells are cultured and their motion pattern gives information about their activity during wound healing and cell organization processes [3]. Motility analysis has also enabled the study of the growth of cancer cells. Time lapse cameras are used to capture the cellular motion, however, this technique is limited by the need for greater speed and sensitivity at high resolution.

The process of drug testing and its effectiveness on certain chemical and physical properties of the cells is very complex and time consuming. Traditionally, *in vitro* or *in vivo* cell based assays were used for drug testing, but their results were inconsistent due to the effect of environmental variations [6]. Most of these technologies used fluorescence based imaging systems in which the fluorescent labels (chemical compounds which re-emit light at a higher wavelength than that of the incident light source) are used to enhance the observability of the cellular samples under a fluorescence microscope [6][7]. Although this technique gives valuable information about the cell behavior, exposure to such chemical compounds and optical beams for long period of time can damage the live cells, making it harder to accurately investigate the cellular sample [8].

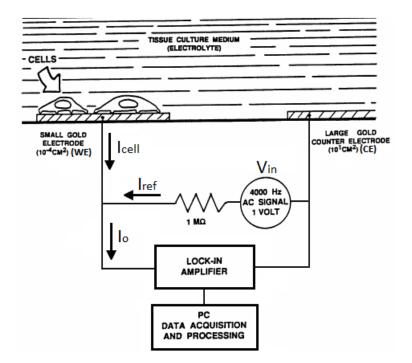

To address these issues, motion detection using a fully electronic approach was developed which is label free and does not require a large amount of image data processing. In this technique, a monolayer of cells is allowed to grow on gold-plated microelectrodes in a controlled environment, as shown in Fig. 1.1 [3]. A large counter electrode (CE) is used to set the reference voltage of the tissue culture medium (electrolyte) while cells are cultured on the surface of a working electrode (WE). An ac voltage  $V_{in}$  is applied to 1 M $\Omega$ resistance generating a known current  $I_{ref}$ .  $V_{in}$  is also applied between CE and WE, which produces an ac current  $I_{cell}$  containing impedance information.

This setup is connected to a lock-in amplifier to extract the cellular data. A lockin amplifier is an electronic circuit which detects and accurately measures very small ac currents by rejecting the noise components of the system [4]. An ac input signal to be detected is multiplied by a known internal reference signal and then passed through a low-pass filter which rejects the high frequency noise. If the frequencies and phase of both signals are equal, then a dc output signal is produced which is proportional to the amplitude of the input signal. This enables us to accurately determine the amplitude of a small sinusoidal signal in a noisy environment. As the cells move and merge, the distance between cells and/or between cells and electrode changes, resulting in changed values of the cell resistance and capacitance [5]. The magnitude and phase of the ac current  $I_o$  (which is the sum of the cell current  $I_{cell}$  and reference current  $I_{ref}$ ) that goes into the lock-in amplifier also changes. This impedance variation is used to study the behavior of the cells.

Fig. 1.1: Impedance measurement system for cell motion detection (adapted from [3]).

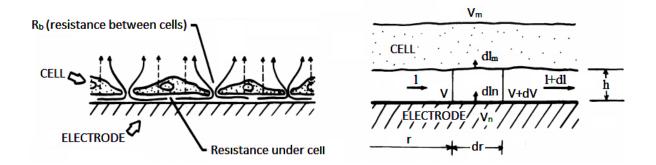

The pioneering work to study the motility of cells [3] using the impedance model was done by Giaever *et al.* They modeled a confluent WI-38 VA13 cell layer on the surface of the WE (shown in Fig. 1.2) and solved the first and second-order modified Bessel function [3]. In this model it is assumed that the potential above the cell surface is constant and the current flows radially through the space between the cells. The simplified impedance of the cell membrane is assumed to be purely capacitive and is given by  $Z_m = 1/(j\omega C_m/2)$ , where  $C_m/2$  is the series equivalent capacitance of the upper and lower cell membrane and  $\omega$  the radial frequency in rad/s of the applied voltage signal.

Fig. 1.2: Diagram of cells in tissue culture emphasizing the dimensions at cell-electrode interface (adapted from [3]).

In order to develop the differential equation, the space between the cells and the electrode surface is divided into infinite number of rings with inner radius r and outer radius r + dr, as illustrated in Fig. 1.2. The horizontal current causes the voltage change  $\Delta V$  as it moves from the inner to the outer ring and the vertical current passes through the cell membrane. The modified Bessel function is given by [3]:

$$\frac{d^2V}{dr^2} + \frac{1}{r}\frac{dV}{dr} - \gamma^2 V + \beta = 0,$$

(1.1)

where

$$\gamma^2 = \frac{\rho}{h} \left[ \frac{1}{Z_n} + \frac{1}{Z_m} \right], \tag{1.2}$$

and

$$\beta = \frac{\rho}{h} \left[ \frac{V_n}{Z_n} + \frac{V_m}{Z_m} \right]. \tag{1.3}$$

In the above equations,  $V_n$  is the potential of the electrode,  $V_m$  is the potential measured at the outer cell layer, h is the height of the space between the cell and the electrode,  $\rho$  is the resistivity of the cell culture medium and  $Z_n$  is the impedance of the cell-free electrode.

The solution of (1.1) is the sum of modified Bessel functions which can be solved for an impedance of a cell covered electrode  $Z_c$ , given by [3]:

$$\frac{1}{Z_c} = \frac{1}{Z_n} \left[ \frac{Z_n}{Z_n + Z_m} + \frac{\frac{Z_m}{Z_n + Z_m}}{\frac{i\gamma r_c}{2} \frac{I_0(\gamma r_c)}{I_1(\gamma r_c)} + 2R_b \left(\frac{1}{Z_n} + \frac{1}{Z_m}\right)} \right],$$

(1.4)

and

$$\gamma r_c = \alpha \sqrt{\frac{1}{Z_n} + \frac{1}{Z_m}},\tag{1.5}$$

where  $I_0$  and  $I_1$  are modified Bessel functions of the first kind of order 0 and 1, *i* is  $\sqrt{-1}$ ,  $R_b$  is the lateral distance between the two cells,  $r_c$  is the radius of the cell and

$$\alpha = r_c \sqrt{\frac{\rho}{h}}.\tag{1.6}$$

It is observed from (1.4) that the total impedance depends on  $R_b$  and  $\alpha$ , and their values can be estimated from the best fit data analysis. The resistance  $R_b$  helps to determine the amount of current flow between the cells. The parameter  $\alpha$  is used to calculate the vertical distance h which enables the study of the surface adhesion of the cellular layer.

The traditional approach described previously [3] uses long cables to connect the electrode array to the lock-in amplifier, which adds parasitic capacitance, increases electromagnetic interference, and requires a large test setup [2]. It reduces the sensitivity and accuracy of the cell measurements leading to performance issues.

### 1.1 Cell Membrane Impedance Model

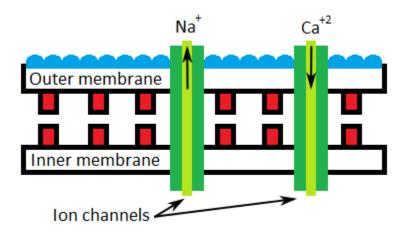

Human tissues are made up of cells arranged in a unique order. The basic structure of the cell consists of a phospholipid bilayer membrane which forms the cell boundary and contains protein ion channels and other molecules. This bilayer membrane does not allow the passage of the charged particles, except through the embedded ion channels. A basic model of the cell membrane is shown in Fig. 1.3.

Fig. 1.3: Basic human cell membrane structure.

Ion channels are closed by default and when they are in this state the cell is said to be inactive. The outer and inner cell membrane is electrically insulating. When a ligand (molecules in living tissues which combine with cells in case of a biological event) is introduced at specific binding sites on the cell membrane, the cell is said to be activated and ion channels are opened. This allows transfer of ions  $Na^+$ ,  $K^+$ ,  $Ca^{+2}$ , and  $Cl^-$  through the ion channels, resulting in modified electrical properties of the cells. This forms the basis of the impedance spectroscopic technique to study the cellular response by activating a membrane receptor, and then analyzing the current variations through the cell. Live cells in the human body communicate through G-protein coupled receptors (GPCRs) [9] and ligand gated ion channels (LGICs) [10]. The basic principle of communication is similar. As soon as the ligand-receptor interaction activates the ion channel, ions start to move in and out of the membrane, resulting in the cell impedance variation.

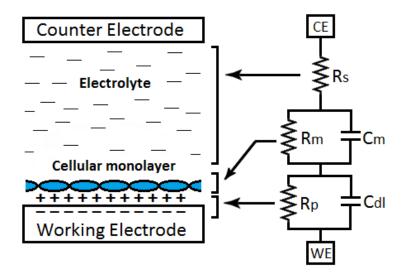

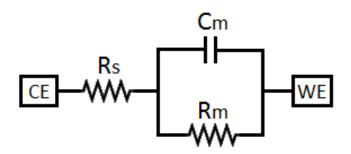

Such reaction of cell membrane to the activation process and generation of small currents make it possible to model the membrane structure as a combination of passive RC circuits [11][12]. Fig. 1.4 shows a circuit model representing a cellular monolayer cultured on the WE surface in the presence of an electrolyte.

Fig. 1.4: Passive circuit model of a cellular sample and electrode-electrolyte interface.

The electrolyte resistance  $R_s$  is in series with the cell impedance, which can be modeled as a membrane capacitance  $C_m$  in parallel with membrane resistance  $R_m$ . An electrical double layer exists at the interface between the working electrode and its surrounding electrolyte due to the adsorption of ions on the surface. Some leakage current also flows through the solution when the potential of the electrode is changed (polarization process). This gives rise to another impedance in series with the membrane which is modeled as a double-layer capacitance  $C_{dl}$  in parallel with a polarization resistance  $R_p$ . Since  $C_{dl}$  is normally much larger than  $C_m$ , the effect of  $C_{dl}$  can be ignored. A simplified passive circuit model of a cell membrane is shown in Fig. 1.5. Reported experimental values of a typical cell membrane resistance and capacitance are 1-2 k $\Omega \cdot \text{cm}^2$  and 1-4  $\mu \text{F} \cdot \text{cm}^{-2}$  [2]. The range of  $C_m$  and  $R_m$  values calculated for different areas (where the area is defined as the total area of the cell membrane in contact with the WE) is given in Table 1.1.

Fig. 1.5: Simplified passive circuit model of a cell membrane.

| Area $(\mu m^2)$ | $R_{m,min}$ (G $\Omega$ ) | $R_{m,max}$ (G $\Omega$ ) | $C_{m,min}$ (pF) | $C_{m,max}$ (pF) |

|------------------|---------------------------|---------------------------|------------------|------------------|

| 1                | 100                       | 200                       | 0.01             | 0.04             |

| 10               | 10                        | 20                        | 0.1              | 0.4              |

| $10^{2}$         | 1                         | 2                         | 1                | 4                |

| $10^{3}$         | 0.1                       | 0.2                       | 10               | 40               |

| $10^{4}$         | 0.01                      | 0.02                      | 100              | 400              |

Table 1.1: Calculated values of membrane resistance and capacitance for different electrode areas covered by a cellular layer.

### **1.2** Electrochemical Impedance Spectroscopy (EIS)

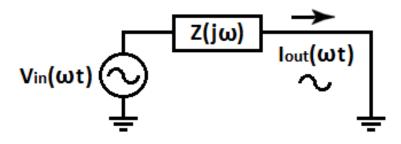

The general technique used to measure the cell impedance is known as electrochemical impedance spectroscopy (EIS). A small ac voltage signal at various frequencies is applied to the cellular monolayer in the presence of an electrolyte and the resulting ac current at each frequency is monitored. The ratio of input ac voltage to output current is the impedance. In cell biology, this technique of bioimpedance measurement is sometimes referred to as cellular dielectric spectroscopy (CDS) [6].

The main advantages of EIS are that it does not require the use of chemical labels and allows for real-time detection [7]. In addition to the cell sensors, EIS also finds applications in channel membrane protein biosensors [13][14], gas sensors [15] and humidity sensors [16]. Even DNA sensors can be analyzed by tracking the capacitive component of the cellular impedance [17].

Fig. 1.6: Block diagram of a general impedance spectroscopy system.

Fig. 1.6 shows the block diagram of a general EIS system for cellular impedance measurements. Impedance  $Z(j\omega)$  represents the cells being measured. If a small signal

voltage  $V_{in}(\omega t) = A_i \sin(\omega t)$ , where t is the time and  $A_i$  is the input amplitude, is applied across  $Z(j\omega)$ , the current  $I_{out}(\omega t)$  through the impedance is given by

$$I_{out}(\omega t) = A_o sin(\omega t + \phi), \qquad (1.7)$$

where  $A_o$  and  $\phi$  are the output amplitude and phase of the sensor current, respectively. The admittance  $\mathbf{Y}(j\omega)$  can be written in phasor form as:

$$\mathbf{Y}(j\omega) = \frac{\mathbf{I}_{out}(j\omega)}{\mathbf{V}_{in}(j\omega)} = \frac{A_o e^{j\phi}}{A_i},\tag{1.8}$$

where  $\mathbf{I}_{out}(j\omega)$  and  $\mathbf{V}_{in}(j\omega)$  are the output current and input voltage phasors, respectively. Equation (1.8) can also be expressed as

$$\mathbf{Y}(j\omega) = \frac{A_o}{A_i} \cos(\phi) + j \frac{A_o}{A_i} \sin(\phi)$$

(1.9)

using Euler's identity, where  $\frac{A_o}{A_i}cos(\phi)$  is the real part and  $\frac{A_o}{A_i}sin(\phi)$  is the imaginary part of the admittance. The magnitude of the admittance is given by

$$|\mathbf{Y}(j\omega)| = \frac{A_o}{A_i},\tag{1.10}$$

and the phase is given by

$$\angle \mathbf{Y}(j\omega) = \tan^{-1} \left[ \frac{\sin(\phi)}{\cos(\phi)} \right]. \tag{1.11}$$

We have a system, where we are able to apply the input voltage and measure the output current. If we expand (1.7), we get

$$I_{out}(\omega t) = A_o \cos(\phi) \sin(\omega t) + A_o \sin(\phi) \cos(\omega t), \qquad (1.12)$$

where

$$A_o cos(\phi) = Re\{A_i \mathbf{Y}(j\omega)\} = Re\{\mathbf{I}_{out}(j\omega)\},\tag{1.13}$$

and

$$A_o sin(\phi) = Im\{A_i \mathbf{Y}(j\omega)\} = Im\{\mathbf{I}_{out}(j\omega)\}.$$

(1.14)

There are two approaches commonly used for impedance spectroscopy, namely fast Fourier transform (FFT) and frequency response analysis (FRA). These techniques are well known in the area of bio-impedance measurement and will be discussed later in the chapter.

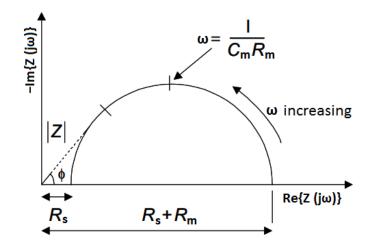

### 1.2.1 Nyquist Plot

The Nyquist plot displays how the real and imaginary parts of the impedance varies over a range of stimulus frequencies. As discussed earlier, the complex cellular impedance is frequency dependent and can be analyzed by considering the passive cell model shown in Fig. 1.5. The equivalent impedance of the simplified circuit model of the cellular membrane is:

$$Z(j\omega) = \frac{(R_m + R_s)[1 + \frac{j\omega C_m R_m R_s}{R_m + R_s}]}{1 + j\omega C_m R_m},$$

(1.15)

The impedance magnitude is given by

$$|Z(j\omega)| = (R_m + R_s) \sqrt{\frac{1 + (\frac{\omega C_m R_m R_s}{R_m + R_s})^2}{1 + (\omega C_m R_m)^2}},$$

(1.16)

and the phase response is given by

$$\angle Z(j\omega) = -tan^{-1} \left[ \frac{\omega C_m R_m^2}{R_m + R_s + \omega^2 R_s R_m^2 C_m^2} \right].$$

(1.17)

A general Nyquist plot of the cellular impedance model is shown in Fig. 1.7.

Fig. 1.7: General Nyquist plot of the cell impedance for model given in Fig. 1.5.

The center frequency of the Nyquist plot is given by  $\omega = 1/(R_m C_m)$ . Analysis of (1.16) shows that at very low frequencies, the capacitor can be modeled as an open circuit. The equivalent impedance is purely real and is equal to  $R_s + R_m$ . At very high frequencies, the capacitor can be modeled as a short circuit and the impedance is equal to the solution resistance  $R_s$ .

# 1.3 CMOS Integrated Circuits for Cellular Impedance Measurements

In order to address the issues related to the cell measurement systems, a more compact and robust sensor system is required. This can be achieved by integrating sensor interface circuits and an electrode array on the same complementary metal-oxide-semiconductor (CMOS) integrated circuit where the electrodes are in direct physical contact with the living cells being measured. The reduced physical distance between the sensor array and the corresponding front-end electronics improves the measurement bandwidth and reduces susceptibility to electromagnetic interference, leading to more accurate measurements. Onchip cell sensing also provides a level of multiplexing not possible using a passive electrode array and off-chip measurement instruments.

### **1.3.1** Impedance Extraction Techniques

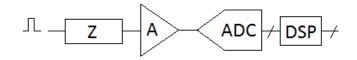

#### 1.3.1.1 Fast Fourier Transform

FFT based methods depend on digital signal processing to extract the impedance information over a wide range of frequencies. A step or sinusoidal signal is applied to the cellular sample and the response is transmitted to a digital signal processor (DSP) after data conversion. The FFT algorithm is then applied to the time domain output to extract the real and imaginary parts of the impedance under test. A typical FFT based sensor is shown in Fig. 1.8. Its hardware requirements include an analog-to-digital converter (ADC) and a DSP kit to process the impedance data.

Fig. 1.8: Block diagram of the FFT approach.

#### 1.3.1.2 Frequency Response Analysis

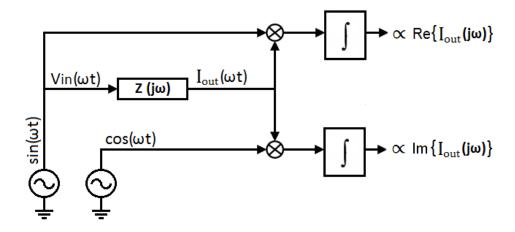

Frequency response analysis (FRA) is another technique that is used for EIS. It requires the sine and cosine signals which are multiplied by the input voltage signal. The result is then integrated over an entire input period to extract the real and imaginary parts of the impedance. A block diagram of this approach is shown in Fig. 1.9. Its hardware requirements include an analog multiplier and an integrator (low-pass filter) [18]. The output current  $I_{out}(\omega t)$  is multiplied by  $sin(\omega t)$  and  $cos(\omega t)$  to separate the real and imaginary parts. From FRA definition and (1.7), the real part of the output current is obtained by computing the following:

Fig. 1.9: System block diagram for a frequency response analysis approach.

$$\int_0^{NT} I_{out}(\omega t) \times \sin(\omega t) \, \mathrm{d}t = \frac{1}{2} NT A_o \cos(\phi) = Re\{A_i Y(j\omega)\} \times \frac{NT}{2},\tag{1.18}$$

where T is the time period of the input sinusoidal signal, N is the number of periods, and  $A_o cos(\phi)$  is the real part of the output current.

Similarly, by multiplying the output current by  $cos(\omega t)$ , we get the imaginary part of the cell impedance current:

$$\int_{0}^{NT} I_{out}(\omega t) \times \cos(\omega t) \, \mathrm{d}t = \frac{1}{2} NT A_o \sin(\phi) = Im\{A_i Y(j\omega)\} \times \frac{NT}{2}, \tag{1.19}$$

where  $A_o sin(\phi)$  is the imaginary part of the output current. There are several architectures used to implement the FRA approach. These include analog impedance coherent detection and a mixed-signal lock-in amplifier architecture.

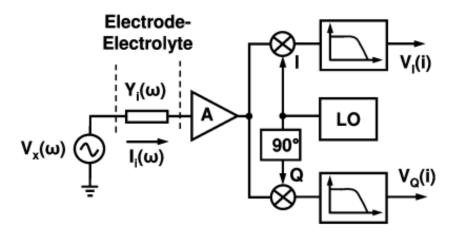

### 1.3.1.2.1 Analog Coherent Detection Architecture

The analog coherent detection architecture uses fully analog components to amplify and then multiply the sensor current with quadrature signals. A block diagram of the coherent detection architecture from Manickam *et al.* is shown in Fig. 1.10 [7]. A small ac voltage  $V_x(\omega)$  is applied using a counter electrode and the resulting current  $I_i(\omega)$  generated through the impedance under investigation is amplified by a low-noise transimpedance amplifier (TIA). The result is then multiplied with sine and cosine signals at the same frequency. The resulting signals are then filtered using a low-pass filter to remove higherorder harmonics generated during the mixing process.

Fig. 1.10: Analog coherent detection architecture for impedance measurement from [7].

The cell admittance is given by

$$Y_i(\omega) = \frac{I_i(\omega)}{V_x(\omega)},\tag{1.20}$$

where  $V_I(i)$  and  $V_Q(i)$  are the in-phase and quadrature signals at the output of the sensor, respectively. The admittance magnitude is given by [7]

$$|Y_i(\omega)| = \frac{\sqrt{V_I^2(i) + V_Q^2(i)}}{A|V_x(\omega)|},$$

(1.21)

and the admittance phase is given by

$$\angle Y_i(\omega) = \tan^{-1} \left[ \frac{V_Q(i)}{V_I(i)} \right].$$

(1.22)

Performance parameters of the coherent detection system are summarized in Table 1.2. Due to the high bandwidth transimpedance amplifier and mixers, this implementation is relatively power hungry [7], which might cause biological issues as the chip heats up.

| Technology          | $0.35 \ \mu m \ CMOS$            |

|---------------------|----------------------------------|

| Die size            | $2 \times 2 \text{ mm}^2$        |

| Array size          | 10×10                            |

| Frequency range     | $10~\mathrm{Hz}-50~\mathrm{MHz}$ |

| Power consumption   | 84.8 mW                          |

| Current sensitivity | 330 pA                           |

| Dynamic range       | 97 dB                            |

Table 1.2: Performance parameters of the analog coherent detection architecture [7].

#### 1.3.1.2.2 Lock-in Impedance-to-Digital Converter

An efficient impedance sensor system needs to measure the data locally, without the need of processing large amounts of cellular data which is a time consuming process. It should be able to convert analog data to digital domain, be compact, and less power hungry. This is because if the chip surface heats up, it might change the electrical properties of the cells leading to incorrect results. It should also be able to accommodate large number of on-chip electrodes to track the impedance in parallel to increase the sensor throughput [1].

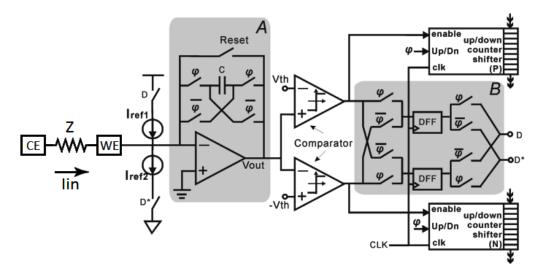

Yang *et al.* proposed a lock-in impedance-to-digital converter (IDC) to implement the FRA algorithm [1]. To carry out the multiplication and integration, it makes use of a flipping capacitor and an integrator, which gives the real and imaginary parts in the analog domain. These components are then digitized by an ADC as shown in Fig. 1.11 [1].

Fig. 1.11: Principle schematic of a lock-in IDC circuit, adapted from [1].

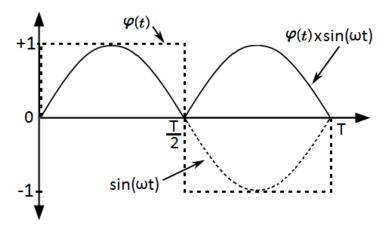

When a small ac signal  $V_{in}$  is applied across the impedance, it produces a current  $I_{in}$ which is integrated over the entire input signal time period. The clock signal  $\varphi$  (in phase with the input ac signal) is '1' and '0' during the first and second half of the input period as shown in Fig. 1.12.

Fig. 1.12: Waveform showing  $\varphi$  and its multiplication with input ac signal.

Two comparators limit the integrator output between  $V_{th}$  and  $-V_{th}$ . During the first phase, the integrator output goes above  $V_{th}$ , flip-flop output D goes high and turns on dc current source  $I_{ref1}$ , which injects charge into the integrator and brings the output within the threshold limit. Similarly, when the integrator output goes below  $-V_{th}$ ,  $D^*$ goes high, turning on  $I_{ref2}$  which pushes the integrator output up towards the threshold voltage. Top and bottom counters count the pulses when the integrator output is higher and lower than  $V_{th}$  and  $-V_{th}$ , respectively. These counts, when multiplied by the clock period and reference dc current  $I_{ref,1,2}$ , give the total charge injected or removed during integration. In the second half period, when  $\varphi=0$ , the integrator capacitor C is flipped, which reverses the charge polarity and represents the input signal multiplication by '-1'. A similar integration process is carried out during the second phase. By periodically flipping the capacitor, the input signal is multiplied by '1' and '-1', which is required by the FRA algorithm to extract the real part of impedance at the end of the integration period, and the imaginary part when  $\varphi$  is shifted by 90°.

#### 1.3.1.2.2.1 Implementation of FRA Algorithm

In Fig. 1.11, the multiplication with sine and cosine signals can be implemented by flipping the integrator capacitor C periodically. When capacitor is flipped, the charged plates are swapped, resulting in current to flow in the opposite direction [1]. This is analogous to multiplying the input signal by '1' and '-1' which represents the current flow in one direction from 0 to T/2 and then in the opposite direction from T/2 to T, respectively [1].

The mathematical representation of the capacitor flipping technique to implement FRA algorithm is now discussed. To get the real part, multiplier signal  $\varphi(t)$  needs to be in phase with  $sin(\omega t)$  and is defined as:

$$\varphi(t) = \begin{cases} 1, \ 0 \le t < T/2 \\ -1, \ T/2 \le t < T \end{cases}$$

(1.23)

The multiplication of  $\varphi(t)$  from (1.23) by the input current and then integration, gives the real part of the output current:

$$\int_{0}^{NT} I_{out}(\omega t) \times \varphi(t) \, \mathrm{d}t = \frac{2}{\pi} NT A_o \cos(\phi), \qquad (1.24)$$

where  $A_o cos(\phi)$  is the real part of the output current, similar to (1.18). To obtain the imaginary part,  $\varphi(t)$  in phase with the  $cos(\omega t)$  is defined as:

$$\varphi(t) = \begin{cases} 1, \ 0 \le t < T/4 \\ -1, \ T/4 \le t < 3T/4 \\ 1, \ 3T/4 \le t < T \end{cases}$$

(1.25)

This time the multiplication of  $\varphi(t)$  from (1.25) by the input current and then integration, gives the imaginary part (1.26):

$$\int_{0}^{NT} I_{out}(\omega t) \times \varphi(t) \, \mathrm{d}t = \frac{2}{\pi} NT A_o sin(\phi), \qquad (1.26)$$

where,  $A_o sin(\phi)$  is the imaginary part of the output current, similar to (1.19).

The analog coherent detection approach provides a measurement bandwidth up to 50 MHz at the expense of relatively high power consumption (84.8 mW). The lock-in amplifier on the other hand consumes only 6  $\mu$ W power but the bandwidth of the sensor is very low. It can measure impedance over a frequency range from 1 mHz to 10 kHz and has linearity up to 78 fA of input current, making it more sensitive to smaller currents as compared to the coherent detection technique which can detect around 330 pA of input current. The performance parameters of the lock-in IDC system are summarized in Table 1.3.

| Technology          | $0.5 \ \mu m \ CMOS$                 |

|---------------------|--------------------------------------|

| Die size            | $3 \times 3 \text{ mm}^2$            |

| Array size          | $10 \times 10$                       |

| Frequency range     | $1 \mathrm{~mHz} - 10 \mathrm{~kHz}$ |

| Power consumption   | $6 \ \mu W$                          |

| Current sensitivity | 400 pA at $f_{in}=1$ Hz              |

| Dynamic range       | $50 \mathrm{~dB}$                    |

Table 1.3: Measured performance parameters of lock-in IDC [1].

#### **1.3.1.3** Comparison of FFT and FRA approaches

FFT based techniques have been used for quite some time to perform EIS. One advantage of the FFT-based approach is the speed of data extraction, which can be higher than the FRA-based technique. This is because a multi-frequency signal can be input and the impedance extracted over a wide band of frequencies at once, which reduces measurement time. On the other hand, the FFT approach is hardware intensive and power hungry due to the dedicated hardware required by the DSP, which implements FFT algorithm [18].

On the other hand, the FRA approach addresses the hardware issues associated with the FFT method. In contrast to FFT, FRA can have a relatively simple hardware implementation [18] comprising a multiplier, integrator, and an ADC with lower design requirements to locally process and extract the impedance information. This approach is hence suitable for a compact and low power sensor design. However, one major drawback of FRA is that it is slower as compared to FFT approach, because it only measures the impedance at one frequency at a time. Therefore it is time consuming process when FRA is used for data extraction at multiple frequencies.

In this thesis, we use an FRA approach to implement impedance extraction of live cells. The reason for pursuing FRA is that we need a compact on-chip circuit that does not require a full DSP engine. Our target is a low-frequency sensor which has low power consumption so that cells do not heat up during impedance extraction. The measurement time is also not a major concern in our application because we want to observe the cell behavior over many hours.

### Chapter 2

## System Architecture and Modeling

The purpose of this chapter is to present the architecture of the proposed CMOS impedance extraction system and develop the sensor specifications and system models which will be used to design the circuit blocks in Chapter 3. A novel approach has been adopted to implement the FRA algorithm using a synchronous voltage to frequency converter (SVFC), which is a type of ADC [19].

### 2.1 System Architecture

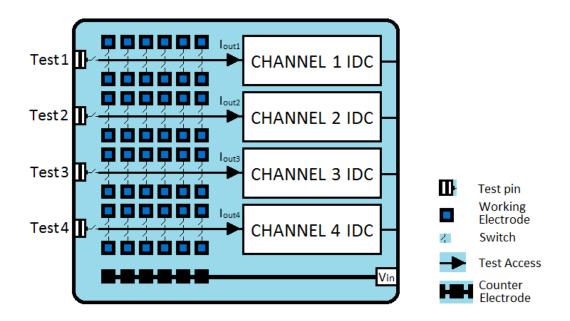

The architecture of the proposed impedance measurement system is shown in Fig. 2.1. For parallel data readout, the system comprises four channels containing an IDC and an  $8\times 6$ working electrode array. The size of each electrode is  $85 \ \mu m \times 85 \ \mu m$  and is formed using the top-metal aluminum layer of the CMOS process. Live cellular samples will eventually be cultured on the surface of the electrode array. There is also a counter electrode built on-chip to set the potential of the electrolyte during the measurement process.

Fig. 2.1: Block diagram of the multi-channel impedance measurement system.

Working electrodes are controlled using on-chip switches which are operated by a flipflop scan chain. External pins have also been provided to test each IDC channel independently using known input currents. Each channel has a dedicated bank of working electrodes, and therefore, the impedance of multiple cellular samples can be extracted simultaneously with distributed measurement workload.

## 2.2 System Specifications

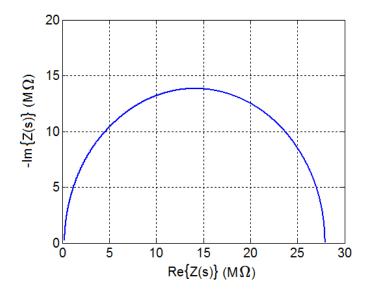

Impedance sensor systems are required to measure the input current levels to extract the real and imaginary parts of the complex cellular impedance. The values of membrane resistance and capacitance determine the sensor input current level over a range of frequencies applied during EIS. Consider the simplified model of the cell membrane impedance in Fig. 1.5. For the electrode size of our chip and assuming the electrode is fully covered by the cellular monolayer, the typical values of membrane resistance, capacitance, and solution resistance from Section 1.1 are:  $R_m$ =27.68 M $\Omega$ ,  $C_m$ =72.25 pF, and  $R_s$ =250 k $\Omega$ , respectively. The Nyquist plot of this cellular impedance is shown in Fig. 2.2.

Fig. 2.2: Nyquist plot of typical cellular impedance for 85  $\mu$ m×85  $\mu$ m working electrode area.

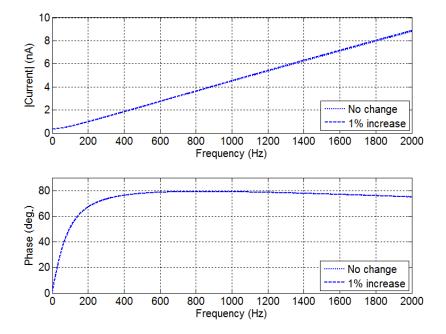

To simplify the analysis, we assume that only the cell membrane capacitance is variable. The smallest input current level the sensor must measure is dictated by the smallest capacitance change that the cell would undergo over the frequency range of interest. In this work, we have targeted a frequency range from 0.1 Hz to 2 kHz. Assuming the membrane capacitance increases by 1%, the magnitude and phase of the current before and after the capacitance change is shown in Fig. 2.3. A nominal input signal amplitude of 10 mV<sub>pk</sub> is used for the analysis to avoid a non-linear response.

Fig. 2.3: Effect of 1% increase in  $C_m$  value on (a) magnitude (b) phase of input current level.

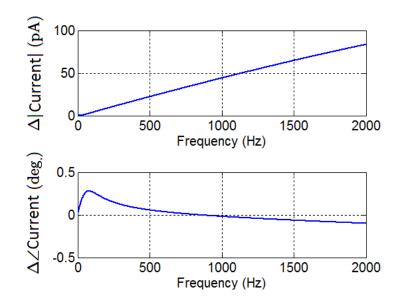

The change in the magnitude and phase of the input current level is shown in Fig. 2.4. It can be observed that 1% variation in the membrane capacitance causes a maximum of 85 pA change in the input current for input frequencies up to 2 kHz. In addition a phase change of  $\pm 0.25^{\circ}$  occurs over this frequency interval.

From the plot given in Fig. 2.3, the maximum input sensor current is 10 nA for the given electrode area and frequency range. However, to provide flexibility, we have assumed

Fig. 2.4: Change in output current magnitude and phase due to 1% membrane capacitance increase.

a maximum (full-scale) current  $I_{FS}$  of 50 nA. The smallest current  $I_{LSB}$  that can be represented by the sensor is given by

$$I_{LSB} = \frac{I_{FS}}{2^N},\tag{2.1}$$

where N is the number of bits of resolution of the IDC. Assuming a 10-bit nominal resolution, the calculated least significant bit (LSB) current is 48.8 pA. Smaller currents can be measured by increasing the resolution of the sensor, which will be discussed later in this chapter.

As explained previously, power consumption is also an important design parameter in sensor systems used for EIS. We have targeted a power consumption of under 150  $\mu$ W per IDC channel.

## 2.3 Novel Implementation of FRA Algorithm

Various schemes have been developed to implement the FRA algorithm for impedance extraction such as in [1]. As explained in section 1.3.1.2.2, the input signal multiplication by '1' and '-1' in the first and second half of the input period, respectively, is implemented by flipping the integrator capacitor periodically. Although it makes use of the entire integration period to extract the information, it is prone to charge injection effects from the switch network around the capacitor. The op amp input offset voltage also leads to an input offset current which gets integrated. This adds an offset error to the final digital value. In this design, a new algorithm and approach has been developed to extract the impedance components.

In our approach, we use half the integration period for impedance extraction, unlike the technique described in [1]. During the other half of the integration period, we automatically store the input offset voltage of the integrator op amp. This offset voltage is then subtracted during the integration phase to reduce the offset. To carry out the traditional EIS, a sinusoidal voltage signal is applied to the cultured cells. Equation (1.7) gives the amplitude and phase information of the output current. This information is then transformed into real and imaginary parts using the FRA algorithm.

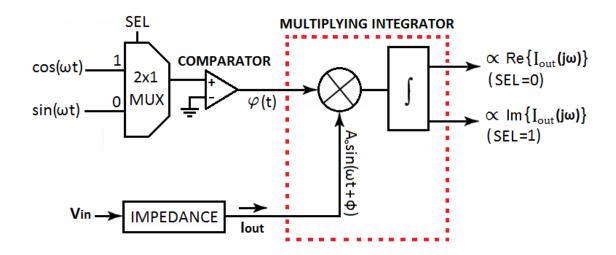

A block diagram of our proposed impedance extraction system is shown in Fig. 2.5. An input voltage  $V_{in}(\omega t)$  is applied to the cell impedance  $Z(j\omega)$ , resulting in current  $I_{out}(\omega t)$ . In order to extract the real part, *select* address line of  $2 \times 1$  MUX is set to '0'. The signal  $sin(\omega t)$  is multiplied by  $A_o sin(\omega t + \phi)$  and then integrated over time period T of the input signal given by  $T = \frac{2\pi}{\omega}$ . The integrator output is converted to the digital domain, providing the real part at a particular frequency. Similarly, to extract the imaginary part, the select line is set to '1', and  $cos(\omega t)$  is multiplied by the input current, giving the imaginary part.

Fig. 2.5: Block diagram showing the proposed impedance extraction approach based on the FRA algorithm.

### 2.3.1 Real Part Extraction

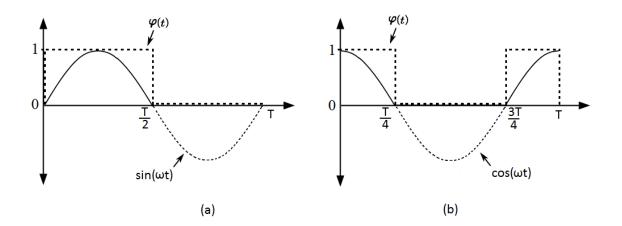

The multiplier signal  $\varphi(t)$  in phase with the input signal  $sin(\omega t)$ , as shown in Fig. 2.6 (a), is defined as:

$$\varphi(t) = \begin{cases} 1, \ 0 \le t < T/2 \\ 0, \ T/2 \le t < T \end{cases}$$

(2.2)

To apply the FRA algorithm, the current  $I_{out}(\omega t)$  is multiplied by signal  $\varphi(t)$  and integrated over period T, given by (2.3).

$$\int_0^T I_{out}(\omega t) \times \varphi(t) \, \mathrm{d}t =$$

(2.3)

$$\int_{0}^{\frac{T}{2}} A_{o}sin(\omega t + \phi) \times (1) \, \mathrm{d}t + \int_{\frac{T}{2}}^{T} A_{o}sin(\omega t + \phi) \times (0) \, \mathrm{d}t$$

(2.4)

$$=\frac{1}{\pi}TA_{o}cos(\phi). \tag{2.5}$$

For N input periods, the total input charge from (2.5) is given by  $\frac{1}{\pi}NTA_o\cos(\phi)$ , where  $A_o\cos(\phi)$  is the real part of the output current.

### 2.3.2 Imaginary Part Extraction

To obtain the imaginary part of  $I_{out}(\omega t)$ , the multiplier signal  $\varphi(t)$  is in phase with  $\cos(\omega t)$ , as shown in Fig. 2.6 (b) and is defined as:

$$\varphi(t) = \begin{cases} 1, \ 0 \le t < T/4 \\ 0, \ T/4 \le t < 3T/4 \\ 1, \ 3T/4 \le t < T \end{cases}$$

(2.6)

The impedance current  $I_{out}(\omega t)$  is multiplied by  $\varphi(t)$  and integrated over period T, given by

$$\int_0^T I_{out}(\omega t) \times \varphi(t) \, \mathrm{d}t =$$

(2.7)

$$\int_{0}^{\frac{T}{4}} A_{o}sin(\omega t+\phi) \times (1) \ \mathrm{d}t + \int_{\frac{T}{4}}^{\frac{3T}{4}} A_{o}sin(\omega t+\phi) \times (0) \ \mathrm{d}t + \int_{\frac{3T}{4}}^{T} A_{o}sin(\omega t+\phi) \times (1) \ \mathrm{d}t \ (2.8)$$

$$=\frac{1}{\pi}TA_{o}sin(\phi).$$

(2.9)

For N input periods, the total input charge from (2.9) is given by  $\frac{1}{\pi}NTA_o sin(\phi)$ , where  $A_o sin(\phi)$  is the imaginary part of the output current.

Fig. 2.6: Multiplier signal  $\varphi(t)$  definition. (a) In phase with  $sin(\omega t)$  (b) in phase with  $cos(\omega t)$ .

### 2.4 Impedance-to-Digital Converter Design

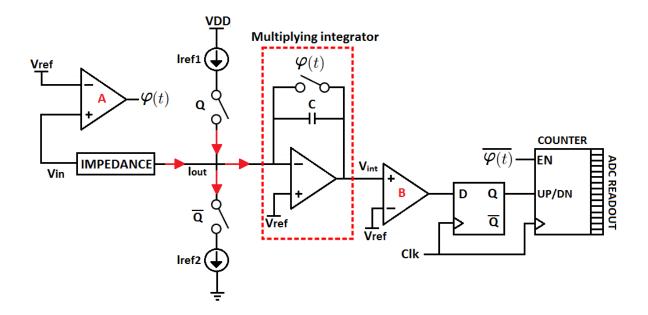

To realize the algorithm explained in the previous section in hardware, an SVFC architecture has been adopted. A voltage-to-frequency converter (VFC) consists of an oscillator whose frequency is linearly proportional to the control voltage; the higher the input voltage the higher the output digital count. A clocked VFC is called an SVFC [19]. Impedance extraction system based on an SVFC is developed, which makes use of a multiplying integrator and digital circuitry for FRA implementation, as shown in Fig. 2.7. Multiplication and integration can be achieved by operating the feedback switch of the integrator using a periodic signal  $\varphi(t)$ . The output of the multiplying integrator gives the analog value that is proportional to the real and imaginary parts of the output current and is digitized by a 16-bit counter. This digital data is transmitted serially off-chip by controlling the  $16 \times 1$ MUX address lines.

Fig. 2.7: Circuit diagram of impedance-to-digital converter built using an SVFC.

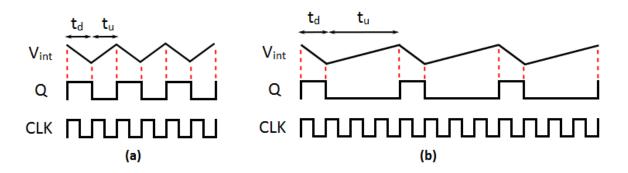

In order to get an insight of how the SVFC works, consider the waveforms shown in Fig. 2.8. When  $I_{out}$  is zero in Fig. 2.8 (a), the flip-flop output Q switches the current sources  $I_{ref1}$  and  $I_{ref2}$  at half the clock frequency, which adds and removes an equal amount of charge (assuming  $I_{ref1}=I_{ref2}$ ) to and from the integrator. The bidirectional counter measures the time duration  $t_u$  and  $t_d$  and records an equal number of high and low pulses in this case, respectively. Therefore, the final count value at the end of the charging and discharging period is zero.

For the second case shown in Fig. 2.8 (b),  $I_{out}$  is greater than zero. The integrator output voltage  $V_{int}$  therefore ramps down for time  $t_d$ . At the next clock edge, the flip-flop output changes state and turns on the negative current source  $I_{ref2}$  which removes charge from the integrator. The integrator output voltage starts to ramp up for a time duration  $t_u$  which is proportional to the output current  $I_{out}$ . In this case, the frequency of Q is less than half the clock frequency so the counter value will not be zero.

Fig. 2.8: SVFC waveforms when the output current is (a) equal to zero and (b) greater than zero.

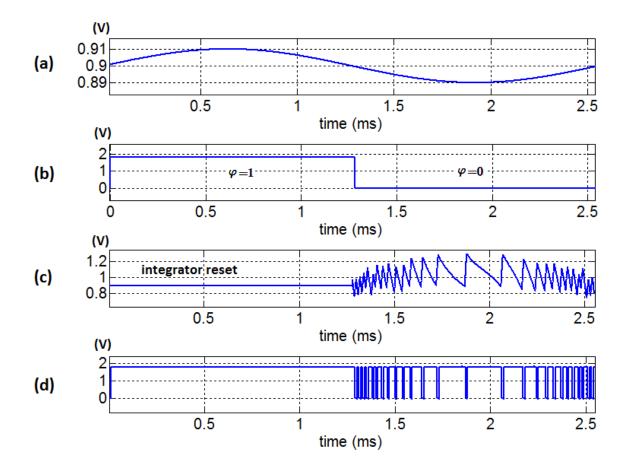

As an example, consider the simulation waveforms of the SVFC in Fig. 2.9. An input ac voltage  $V_{in}$  of 10 mV peak amplitude and 390.6 Hz (Fig. 2.9 (a)) is applied to a 200  $k\Omega$  resistance which produces small ac current  $I_{out}$ . Signal  $V_{in}$  also goes to comparator A which generates an in-phase square wave signal  $\varphi(t)$  (Fig. 2.9 (b)) which controls the feedback switch of the integrator. As mentioned earlier, in the first half period when  $\varphi(t)=1$  and the feedback switch is on, the input offset of the integrator op amp is stored. During the second half period, when  $\varphi(t)=0$ , the feedback switch turns off and the input current starts to integrate. As the integrator output voltage (shown in Fig. 2.9 (c)) rises above the reference voltage  $V_{ref}$  (set to 900 mV in this example), the output of comparator B, and hence the flip-flop output Q, goes high (Fig. 2.9 (d)). This turns on the current source  $I_{ref1}$  which injects charge into the integrator, pushing its output below the reference voltage. Similarly, when the integrator output is lower than  $V_{ref}$ ,  $\overline{Q}$  goes high and turns on  $I_{ref2}$  which removes charge and brings the integrator output above  $V_{ref}$ . At the end of the integration period T (2.56 ms in this example), the measured current is digitized by a 16-bit digital counter, which is disabled as soon as  $\varphi(t)$  goes high for the next input period. This data is serially shifted out to a field programmable gate array (FPGA) and then to a PC via universal bus service (USB) connection to extract the impedance components from the measured current.

Fig. 2.9: Simulation waveforms of the SVFC based impedance sensor for 200 k $\Omega$  resistance at 390.6 Hz input signal frequency. (a) Input ac voltage signal, (b) comparator A output, (c) integrator output, and (d) flip-flop output.

## 2.5 Principle of Impedance Extraction

To describe the concept of impedance extraction using integrated circuit components, again consider the SVFC in Fig. 2.7. The amount of input dc current injected  $(I_{ref1})$  and removed  $(I_{ref2})$  from the integrator (Fig. 2.7), when multiplied by the time for which it is applied, gives the amount of charge  $Q_{out}$  transferred during the integration phase. From Fig. 2.8 (b), the integrator output voltage  $V_{int}$  at the end of the charging and discharging period must be equal to zero:

$$-\frac{I_{out} + I_{ref1}}{C}t_d + \frac{I_{ref2} - I_{out}}{C}t_u = 0.$$

(2.10)

Equation (2.10) can be simplified to

$$I_{out}(t_u + t_d) = I_{ref2}t_u - I_{ref1}t_d,$$

(2.11)

for a single charging and discharging period  $t_u + t_d$ . For a complete input signal period T, (2.11) can be written as

$$\int_{0}^{T} I_{out} \, \mathrm{d}t = \int_{0}^{t_{u}} I_{ref2} \, \mathrm{d}t - \int_{0}^{t_{d}} I_{ref1} \, \mathrm{d}t, \qquad (2.12)$$

where  $\int_0^{t_d} I_{ref1} dt$  and  $\int_0^{t_u} I_{ref2} dt$  is the total amount of charge added and removed from the integrator in one input period.

Suppose  $\sum_{i=1}^{N} D_i$  and  $\sum_{i=1}^{N} D_i^*$  are the positive and negative counts when the current sources  $I_{ref1}$  and  $I_{ref2}$  are on, respectively. The charge added and removed can be calculated by multiplying positive counts by  $I_{ref1}T_{clk}$  and negative counts by  $I_{ref2}T_{clk}$ . For the first half cycle, from t=0 to t=T/2, after adding residue charge  $CV_{res}$  at the integrator output, (2.12) can be written as [1]:

$$\int_{0}^{\frac{T}{2}} I_{out} \, \mathrm{d}t = CV_{res1} + I_{ref1}T_{clk} \sum_{i=1}^{N} D_i - I_{ref2}T_{clk} \sum_{i=1}^{N} D_i^*.$$

(2.13)

Similarly, for the second half cycle from t=T/2 to t=T, (2.11) can be written as:

$$\int_{\frac{T}{2}}^{T} I_{out} \, \mathrm{d}t = CV_{res1+res2} + I_{ref1}T_{clk} \sum_{i=N+1}^{2N} D_i - I_{ref2}T_{clk} \sum_{i=N+1}^{2N} D_i^*.$$

(2.14)

The total input charge from t=0 to t=T can be found by combining (2.13) and (2.14):

$$\int_{0}^{\frac{T}{2}} I_{out} \, \mathrm{d}t + \int_{\frac{T}{2}}^{T} I_{out} \, \mathrm{d}t \approx I_{ref} T_{clk} \left[ \sum_{i=1}^{N} D_i - \sum_{i=1}^{N} D_i^* + \sum_{i=N+1}^{2N} D_i - \sum_{i=N+1}^{2N} D_i^* \right]. \quad (2.15)$$

The residue voltages  $CV_{res}$  have been ignored because their magnitude is negligible compared to the counts and can be regarded as noise over the digital counts [1]. Also, dc current sources  $I_{ref1}$  and  $I_{ref2}$  are set equal to  $I_{ref}$  which factors out  $I_{ref}T_{clk}$ . Now (2.15) can be simplified to

$$\int_0^T I_{out} \, \mathrm{d}t = I_{ref} T_{clk} \left[ P_{counter1} - N_{counter1} + P_{counter2} - N_{counter2} \right], \qquad (2.16)$$

where  $P_{counter1}$  and  $P_{counter2}$  are the positive, and  $N_{counter1}$  and  $N_{counter2}$  are the negative counts during the first and second half of the input period, respectively. Bidirectional counter is disabled during the first half period. Therefore, using  $P_{counter1} - N_{counter1} = 0$ in (2.16) gives the expression for the total input charge:

$$\int_0^T I_{out} \, \mathrm{d}t = I_{ref} T_{clk} [P_{counter2} - N_{counter2}]. \tag{2.17}$$

As discussed earlier, the FRA algorithm gives the real and imaginary part of the impedance current which is found by multiplying the input current by signal  $\varphi(t)$  and

then integrating it over a period T. This is effectively the amount of integrated charge during the input period. After solving (2.5) and (2.17), we get:

$$Re\{I_{out}(j\omega)\} = I_{ref}T_{clk}[P_{counter2} - N_{counter2}] \times \pi/T, \qquad (2.18)$$

where  $P_{counter2} - N_{counter2}$  is the final value of the bi-directional counter at the end of the input period T and  $\varphi(t)$  is in phase with  $sin(\omega t)$ . Same expression can be used to calculate the imaginary part of the output current  $Im\{I_{out}(j\omega)\}$  when  $\varphi(t)$  is in phase with  $cos(\omega t)$ .

The real and imaginary parts are then used to calculate the impedance under test. The impedance output current  $I_{out}(\omega t) = A_o sin(\omega t + \phi)$  carries the impedance information, where  $A_o$  and  $\phi$  are the magnitude and phase of the extracted current, respectively, and given by:

$$A_o = \sqrt{Re\{I_{out}(j\omega)\}^2 + Im\{I_{out}(j\omega)\}^2},$$

(2.19)

$$\phi = \tan^{-1} \left[ \frac{Im\{I_{out}(j\omega)\}}{Re\{I_{out}(j\omega)\}} \right].$$

(2.20)

The impedance can be calculated by dividing the known input signal amplitude  $A_i$  by the extracted value of the output current, as given by

$$Z(j\omega) = \frac{A_i}{A_o \angle \phi},\tag{2.21}$$

where  $\left(\frac{A_i}{A_o}\right)$  and  $\left(-\phi\right)$  are the magnitude and phase of the measured impedance.

## 2.6 Resolution of Impedance Sensor

The system is operated at a clock rate of 100 kHz. This frequency is chosen so that an input current of 100 nA and a feedback capacitor of 2 pF does not saturate the integrator. Considering the impedance measurement at a single frequency cycle, the input signal is integrated over half input period and therefore, the nominal resolution of the sensor is given by  $\frac{T}{2T_{clk}}$ , where T and  $T_{clk}$  are the input stimulus and clock periods, respectively. For example, if the input stimulus frequency is 390.6 Hz, then the resolution of the impedance sensor will be 128 (7-bits). In order to increase the resolution, we have to consider M number of input cycles (i.e., for a desired resolution of 8-bits, the value of M would be 2). Similarly, we can take measurements over multiple input cycles M to achieve the desired resolution by dividing (2.18) by M.

## 2.7 Dynamic Range Programmability

The dynamic range of a current sensor is the ratio of the maximum to the minimum value of the measured current. For this impedance sensor, the maximum value of the current is determined by the integrator saturation limit (900 mV) from the reference voltage and the minimum current can be found from (2.18). To make the dynamic range of the impedance sensor more flexible, the integrator in this design is provided with a bank of four 2 pF capacitors and reference current sources of 50 nA, 200 nA, and 1  $\mu$ A. For a clock frequency of 100 kHz and input signal frequencies of 1 Hz, 10 Hz, 100 Hz and 1000 Hz, the maximum current range and the nominal resolution of the system is given in Table 2.1 for 50 nA, Table 2.2 for 200 nA, and Table 2.3 for 1  $\mu$ A of input dc current.

| $C_F (pF)$ | $f_{in}$ (Hz) | $I_{in,min}$ (pA) | $I_{in,max}$ (nA) | Nominal Resolution (bits) |

|------------|---------------|-------------------|-------------------|---------------------------|

|            |               |                   |                   | (for one input period)    |

|            | 1             | 1.6               | 100               | 17                        |

| 2          | 10            | 16                |                   | 14                        |

| 2          | 100           | 160               | 180               | 11                        |

|            | 1000          | 1600              |                   | 7                         |

|            | 1             | 1.6               |                   | 18                        |

| 4          | 10            | 16                | 360               | 15                        |

| 4          | 100           | 160               |                   | 12                        |

|            | 1000          | 1600              |                   | 8                         |

|            | 1             | 1.6               | 540               | 19                        |

| 6          | 10            | 16                |                   | 16                        |

| 0          | 100           | 160               |                   | 12                        |

|            | 1000          | 1600              |                   | 9                         |

| 0          | 1             | 1.6               | 720               | 19                        |

|            | 10            | 16                |                   | 16                        |

| 8          | 100           | 160               |                   | 13                        |

|            | 1000          | 1600              |                   | 9                         |

Table 2.1: Dynamic range programmability of IDC for 50 nA reference current at 100 kHz clock.

| $C_F (pF)$ | $f_{in}$ (Hz) | $I_{in,min}$ (pA) | $I_{in,max}$ (nA) | Nominal Resolution (bits) |

|------------|---------------|-------------------|-------------------|---------------------------|

|            |               |                   |                   | (for one input period)    |

|            | 1             | 6.3               |                   | 15                        |

| 2          | 10            | 63                | 100               | 12                        |

|            | 100           | 630               | 180               | 9                         |

|            | 1000          | 6300              |                   | 5                         |

|            | 1             | 6.3               |                   | 16                        |

| 4          | 10            | 63                | 360               | 13                        |

| 4          | 100           | 630               |                   | 10                        |

|            | 1000          | 6300              |                   | 6                         |

|            | 1             | 6.3               | 540               | 17                        |

| 6          | 10            | 63                |                   | 14                        |

| 6          | 100           | 630               |                   | 10                        |

|            | 1000          | 6300              |                   | 7                         |

| 8          | 1             | 6.3               | 720               | 17                        |

|            | 10            | 63                |                   | 14                        |

|            | 100           | 630               |                   | 11                        |

|            | 1000          | 6300              |                   | 7                         |

Table 2.2: Dynamic range programmability of IDC for 200 nA reference current at 100 kHz clock.

| $C_F (pF)$ | $f_{in}$ (Hz) | $I_{in,min}$ (nA) | $I_{in,max}$ (nA) | Nominal Resolution (bits) |

|------------|---------------|-------------------|-------------------|---------------------------|

|            |               |                   |                   | (for one input period)    |

|            | 1             | 0.0314            |                   | 13                        |

| 2          | 10            | 0.314             | 180               | 10                        |

|            | 100           | 3.14              |                   | 6                         |

|            | 1000          | 31.4              |                   | 3                         |

|            | 1             | 0.0314            |                   | 14                        |

| 4          | 10            | 0.314             | 360               | 11                        |

| 4          | 100           | 3.14              |                   | 7                         |

|            | 1000          | 31.4              |                   | 4                         |

|            | 1             | 0.0314            | 540               | 15                        |

| C          | 10            | 0.314             |                   | 11                        |

| 6          | 100           | 3.14              |                   | 8                         |

|            | 1000          | 31.4              |                   | 5                         |

| 0          | 1             | 0.0314            | 720               | 15                        |

|            | 10            | 0.314             |                   | 12                        |

| 8          | 100           | 3.14              |                   | 8                         |

|            | 1000          | 31.4              |                   | 5                         |

Table 2.3: Dynamic range programma bility of IDC for 1  $\mu \rm A$  reference current at 100 kHz clock.

## 2.8 Operational Amplifier Offset Correction

Practical operational amplifiers exhibit non-idealities including finite dc gain, limited bandwidth, dc offsets, etc. For this application, large dc voltage offsets can limit the signal swing of the integrator output and reduce the performance of the impedance sensor. In order to remove the effect of dc offsets in our system, we store the op amp input offset voltage during the first half cycle of the input period when the integrator is in a unity feedback configuration, and then subtract this offset during the next period.

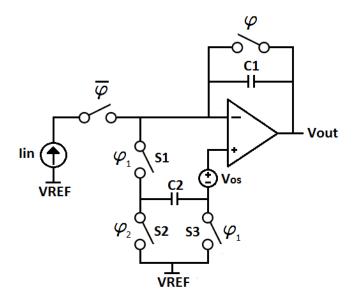

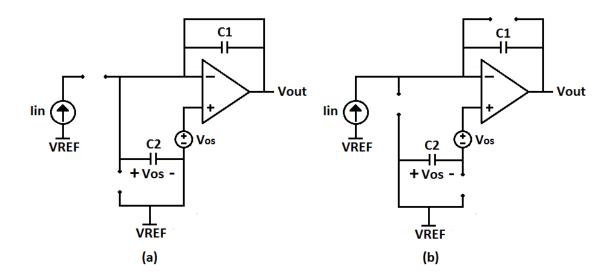

Consider the block diagram of the offset correction circuit in Fig. 2.10. During the first half period, the value of  $\varphi(t)$  is '1', which sets the integrator in a unity feedback mode (Fig. 2.11 (a)). The op amp internal offset voltage  $V_{os}$  will be stored on the capacitor C2. During the next half period, when  $\varphi(t)$  is '0' (Fig. 2.11 (b)),  $V_{ref} - V_{os}$  is applied at the non-inverting terminal of the integrator. In this phase, the offset voltage is canceled out during integration. Similarly, for the next period, offset is stored in the first half cycle and applies the correction during the second half period. The offset correction is carried out continuously during the consecutive measurement cycles to remove any uncertainty from the integrator output. It is important to note that the signals  $\varphi_1(t)$  and  $\varphi_2(t)$  are produced from  $\varphi(t)$  using a non-overlapping clock generator discussed in the next chapter.

Fig. 2.10: Implementation of the offset correction technique.

Fig. 2.11: Offset correction circuit for (a) the first half and (b) the second half of the input period T.

# 2.9 System Specifications

Table 2.4 gives the system specifications of our impedance sensor.

| Parameter                     | Target value |

|-------------------------------|--------------|

| Full scale current $(I_{FS})$ | 50  nA       |

| Minimum current $(I_{LSB})$   | 48.8 pA      |

| IDC nominal resolution        | 10  bit      |

| Measurement bandwidth         | 2 kHz        |

Table 2.4: System specifications.

# Chapter 3

# Circuit Design

This chapter focuses on the circuit level design of the impedance sensor blocks discussed in Chapter 2. This system consists of a multiplying integrator, comparator, flip-flop, digital counter and MUX which process the impedance information and transmit the digital data to an FPGA. Transistor and component level design in a 1.8 V 0.18  $\mu$ m CMOS process is presented in the following sections.

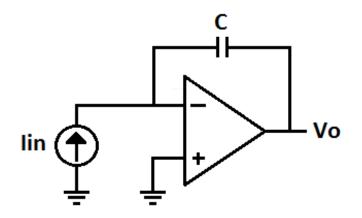

## 3.1 Integrator

In our impedance sensor, a multiplying integrator detects the small input current signals. A circuit diagram of an ideal integrator is shown in Fig. 3.1. The time domain output voltage  $V_o(t)$  of the integrator is given by

$$V_o(t) = -\frac{1}{C} \int_0^t I_{in}(\tau) \ d\tau,$$

(3.1)

where C is the feedback capacitor and  $I_{in}$  is the input signal current.

Fig. 3.1: Ideal integrator.

The transfer function  $V_o(s)/I_{in}(s)$  of the ideal integrator is given by

$$\frac{V_o(s)}{I_{in}(s)} = -\frac{1}{sC}.$$

(3.2)

From (3.2), there is a single pole at dc so the gain of the ideal integrator starts to roll off from  $\omega=0$  rad/s at -20 dB/dec. In practical integrators, the op amp input offset voltage causes dc current to flow into the integrator. If the circuit is allowed to integrate long enough, the integrator output will saturate. Therefore, in any practical implementation, a parallel reset switch must be included to periodically reset the charge on the capacitor.

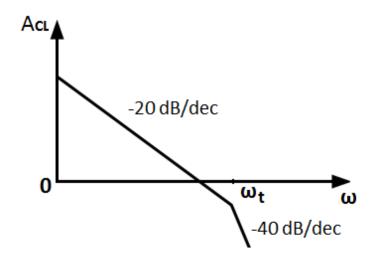

Now we describe the response of a non-ideal integrator. Consider the open-loop transfer function  $A_{OL}(s)$  of a non-ideal op amp with dc gain  $A_o$  and a dominant pole at  $\omega_{3dB}$ :

$$A_{OL}(s) = \frac{A_o}{1 + \frac{s}{\omega_{3dB}}}.$$

(3.3)

The closed-loop transfer function  $A_{CL}(s)$  of the non-ideal integrator is given by

$$A_{CL}(s) = -\frac{1}{(sC)(1+\frac{s}{\omega_t})} , \qquad (3.4)$$

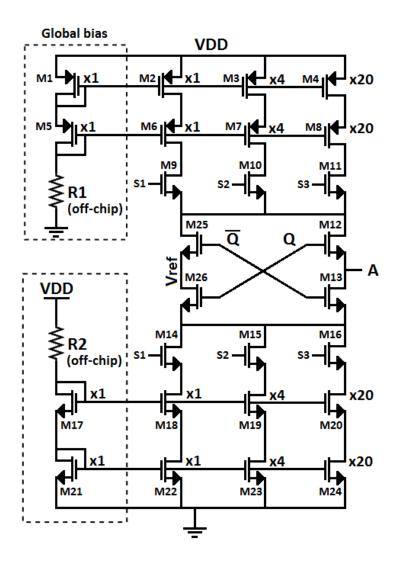

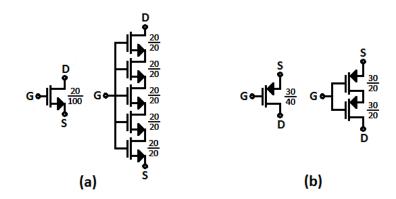

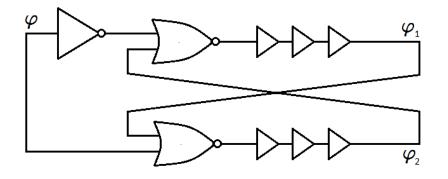

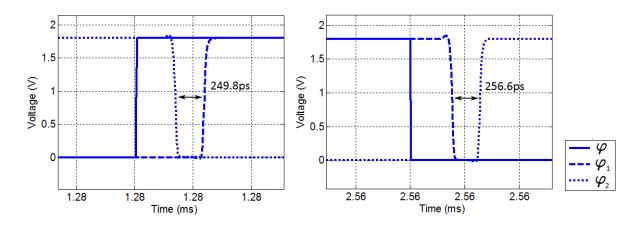

where  $\omega_t$  is the unity-gain frequency of the op amp and is approximately equal to  $A_o\omega_{3dB}$ . The frequency magnitude response of a non-ideal integrator is shown in Fig. 3.2. We observe from (3.4) that there is a low frequency pole at 0 Hz. The integrator gain is very high initially, but as the input frequency increases, capacitor impedance gets smaller and the gain keeps decreasing at -20 dB/dec. At very high frequencies, there is another pole at the unity gain frequency  $\omega_t$  of the open-loop response, resulting in the gain falling by -40 dB/dec.