## High Performance Elliptic Curve Cryptographic Co-processor

by

Jonathan Lutz

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

$\mathrm{in}$

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2003

©Jonathan Lutz, 2003

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Abstract

In FIPS 186-2, NIST recommends several finite fields to be used in the elliptic curve digital signature algorithm (ECDSA). Of the ten recommended finite fields, five are binary extension fields with degrees ranging from 163 to 571. The fundamental building block of the ECDSA, like any ECC based protocol, is elliptic curve scalar multiplication. This operation is also the most computationally intensive. In many situations it may be desirable to accelerate the elliptic curve scalar multiplication with specialized hardware.

In this thesis a high performance elliptic curve processor is developed which is optimized for the NIST binary fields. The architecture is built from the bottom up starting with the field arithmetic units. The architecture uses a field multiplier capable of performing a field multiplication over the extension field with degree 163 in 0.060  $\mu$ sec. Architectures for squaring and inversion are also presented. The co-processor uses López and Dahab's projective coordinate system and is optimized specifically for Koblitz curves. A prototype of the processor has been implemented for the binary extension field with degree 163 on a Xilinx XCV2000E FPGA. The prototype runs at 66 MHz and performs an elliptic curve scalar multiplication in 0.233 msec on a generic curve and 0.075 msec on a Koblitz curve.

#### Acknowledgements

This thesis is sponsored in part by Motorola, Inc. I am particularly grateful to Dan Cronin, Jim Dworkin, and Jeff LaVell of Motorola for their continued support throughout the course of this research effort. Additionally, special thanks is due Professor Anwarul Hasan for his time, guidance, and encouragement. And to my colleagues and friends, Amir and Arash, for the many coffee breaks at Tim Hortons.

To my wife and best friend,

Sarah Joy

## List of Abbreviations

- ASIC Application Specific Integrated Circuit

- CLB Configurable Lobic Block

- DSA Digital Signature Algorithm

- ECC Elliptic Curve Cryptography

- ECDSA Elliptic Curve Digital Signature Algorithm

- FPGA Field Programmable Gate Array

- GF Galois Field

- IOB Input/Output Block

- NAF Non-adjacent Form

- NIST National Institute of Standards in Technology

- $\tau$ -NAF  $\tau$ -adic Non-adjacent Form

- SSL Secure Socket Layer

## Contents

| 1        | Intr | oduction                                 | 1        |

|----------|------|------------------------------------------|----------|

|          | 1.1  | Motivation                               | 1        |

|          | 1.2  | Scope of the Work and Objectives         | 2        |

|          | 1.3  | Thesis Organization                      | 3        |

| <b>2</b> | Bac  | kground                                  | <b>5</b> |

|          | 2.1  | Mathematical Background                  | 5        |

|          |      | 2.1.1 Groups                             | 6        |

|          |      | 2.1.2 Finite Fields                      | 8        |

|          | 2.2  | Arithmetic over Binary Finite Fields     | 12       |

|          |      | 2.2.1 Multiplication                     | 13       |

|          |      | 2.2.2 Inversion                          | 15       |

|          | 2.3  | Arithmetic over the Elliptic Curve Group | 16       |

|          | 2.4  | Implementation Media                     | 18       |

|          |      | 2.4.1 Field Programmable Gate Arrays     | 20       |

|          |      | 2.4.2 The Rapid-Prototyping Platform     | 23       |

| 3        | Hig  | h Performance Finite Field Arithmetic    | 26       |

|   | 3.1 | Multip  | lication                                                 | 27 |

|---|-----|---------|----------------------------------------------------------|----|

|   |     | 3.1.1   | Algorithm                                                | 29 |

|   |     | 3.1.2   | Computation of $R(x)W(x) \mod F(x) \ldots \ldots \ldots$ | 32 |

|   |     | 3.1.3   | The Multiplier Data Path                                 | 37 |

|   |     | 3.1.4   | Choice of Digit Size                                     | 39 |

|   | 3.2 | Squari  | ng                                                       | 39 |

|   | 3.3 | Inversi | on                                                       | 42 |

|   | 3.4 | Compa   | arator/Adder                                             | 45 |

|   | 3.5 | Conclu  | ding Remarks                                             | 46 |

| 4 | A C | Co-proc | essor Architecture for ECC Scalar Multiplication         | 47 |

|   | 4.1 | Projec  | tive Coordinates                                         | 49 |

|   | 4.2 | Scalar  | Multiplication using Recoded Integers                    | 51 |

|   |     | 4.2.1   | Scalar Multiplication using Binary NAF                   | 52 |

|   |     | 4.2.2   | Scalar Multiplication using $\tau$ -NAF                  | 53 |

|   |     | 4.2.3   | Summary and Analysis                                     | 60 |

|   | 4.3 | Co-pro  | cessor Architecture                                      | 61 |

|   |     | 4.3.1   | The Data Path                                            | 62 |

|   |     | 4.3.2   | The Micro-sequencer                                      | 65 |

|   |     | 4.3.3   | Top Level Control                                        | 68 |

|   |     | 4.3.4   | Choice of Field Arithmetic Units                         | 71 |

|   |     | 4.3.5   | Usage Model                                              | 74 |

|   | 4.4 | FPGA    | Prototype                                                | 74 |

|   | 4.5 | Result  | S                                                        | 75 |

| <b>5</b> | Con | ncludin | ng Remarks                                         | 78  |

|----------|-----|---------|----------------------------------------------------|-----|

|          | 5.1 | Summ    | ary and Contributions                              | 78  |

|          | 5.2 | Future  | e Work                                             | 79  |

| A        | Mic | ro-cod  | le supporting Curve Arithmetic and Field Inversion | 80  |

|          | A.1 | Point   | Addition                                           | 80  |

|          |     | A.1.1   | Generic Point Addition                             | 81  |

|          |     | A.1.2   | Koblitz Curve Point Addition                       | 84  |

|          |     | A.1.3   | Efficient Koblitz Curve Point Addition             | 87  |

|          | A.2 | Point   | Doubling                                           | 89  |

|          | A.3 | Field I | Inversion                                          | 90  |

|          |     | A.3.1   | Inversion by Square and Multiply                   | 91  |

|          |     | A.3.2   | Inversion by Itoh and Tsujii                       | 92  |

|          | A.4 | Coord   | inate Conversion                                   | 95  |

|          | A.5 | Copy    | Routines                                           | 95  |

|          |     | A.5.1   | Copy $P$ to $Q$                                    | 96  |

|          |     | A.5.2   | Copy $-P$ to $Q$                                   | 96  |

| В        | Тоо | l Rela  | ted Scripts and Setup Files                        | 97  |

|          | B.1 | Synthe  | esis Scripts                                       | 97  |

|          |     | B.1.1   | Synthesis Compile Scripts                          | 98  |

|          |     | B.1.2   | Synthesis Constraints Script                       | 103 |

|          | B.2 | Place   | and Route Scripts                                  | 104 |

|          |     | B.2.1   | Top Level Place and Route Script                   | 104 |

|          |     | B.2.2   | User Constraints File                              | 107 |

## List of Tables

| 2.1 | NIST Recommended Finite Fields                                             | 12 |

|-----|----------------------------------------------------------------------------|----|

| 3.1 | Performance/Cost Trade-off for Multiplication over $\mathrm{GF}(2^{163})$  | 40 |

| 3.2 | Comparison of Various Inversion Methods for $\mathrm{GF}(2^{163})$         | 45 |

| 3.3 | Performance of Finite Field Operations                                     | 46 |

|     |                                                                            |    |

| 4.1 | Comparison of Projective Point Systems                                     | 51 |

| 4.2 | Cost of Scalar Multiplication in terms of Field Operations $\ldots \ldots$ | 61 |

| 4.3 | Representation of the Scalar $k$                                           | 69 |

| 4.4 | Example Representations of the Scalar                                      | 69 |

| 4.5 | Performance of Field and Curve Operations                                  | 76 |

| 4.6 | Performance and Cost Results for Scalar Multiplication                     | 77 |

| 4.7 | Comparison of Published Results                                            | 77 |

# List of Figures

| 2.1 | Functionality of a CLB                                                    | 21 |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Functionality of an IOB                                                   | 22 |

| 2.3 | CLB Organization                                                          | 23 |

| 3.1 | LFSR Based Multiplier                                                     | 28 |

| 3.2 | The Multiplier Data-Path                                                  | 31 |

| 3.3 | Generating $x^i W(x) \mod F(x) \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

| 3.4 | Computing $R(x)W(x) \mod F(x)$                                            | 35 |

| 3.5 | Computation of a Single Bit in $R(x)W(x) \mod F(x) \ldots \ldots$         | 36 |

| 3.6 | Modified Multiplier Data-Path                                             | 38 |

| 3.7 | Data-Path of the Squaring Unit                                            | 41 |

| 3.8 | Data-Path of the Comparator/Adder                                         | 46 |

| 4.1 | Co-Processor's Hierarchical Control Path                                  | 62 |

| 4.2 | Co-Processor Data-Path                                                    | 63 |

| 4.3 | Field Element Storage                                                     | 64 |

| 4.4 | 32-bit/163-bit Address Map                                                | 64 |

| 4.5 | Efficient Frobenius Mapping                                               | 65 |

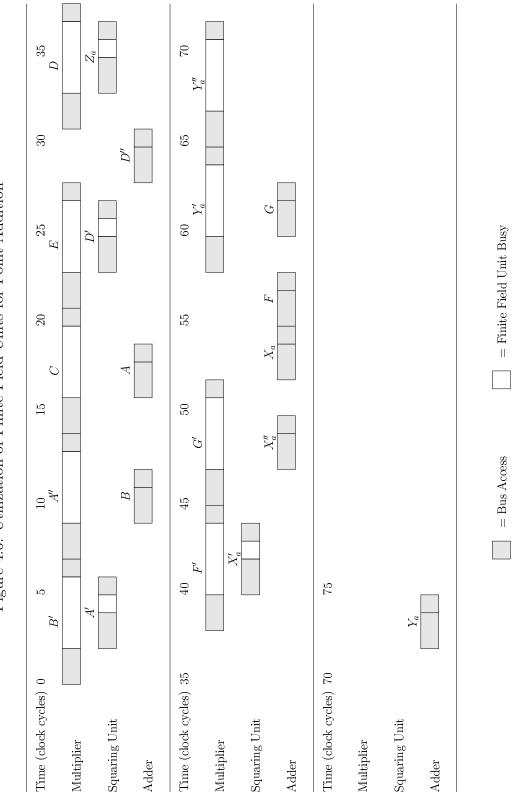

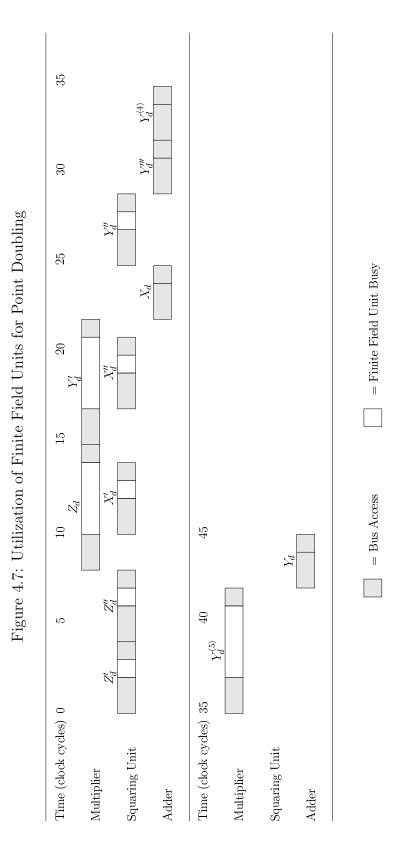

| 4.6 | Utilization of Finite Field Units for Point Addition | 72 |

|-----|------------------------------------------------------|----|

| 4.7 | Utilization of Finite Field Units for Point Doubling | 73 |

## Chapter 1

## Introduction

### 1.1 Motivation

The use of elliptic curves in cryptographic applications was first proposed independently in [17] and [24]. Since then several algorithms have been developed whose strength relies on the difficulty of the discrete logarithm problem over a group of elliptic curve points. Prominent examples include the Elliptic Curve Digital Signature Algorithm (ECDSA) [25], EC El-Gammal and EC Diffie Hellman [14]. In each case the underlying cryptographic primitive is elliptic curve *scalar* multiplication. This operation is by far the most computationally intensive step in each algorithm. In applications where many clients authenticate to a single server (such as a server supporting SSL [8, 27] or WTLS [1]), the computation of the scalar multiplication becomes the bottle neck which limits throughput. In a scenario such as this it may be desirable to accelerate the elliptic curve scalar multiplication with specialized hardware. In doing so, the scalar multiplications are completed more quickly and the computational burden on the server's main processor is reduced.

Elliptic curve-based cryptosystems are most closely related to algorithms like the Digital Signature Algorithm (DSA) which are based on the discrete logarithm problem. In the DSA, the parameters can be chosen to provide efficient implementations of the algorithm. In the same way, the parameters of ECC based cryptosystems can be selected to optimize the efficiency of the implementation. Unfortunately, the selection of the ECC parameters is not a trivial process and, if chosen incorrectly, may lead to an insecure system. In response to this issue NIST recommends ten finite fields, five of which are binary fields, for use in the ECDSA [25]. For each field a specific curve, along with a method for generating a pseudo-random curve, are supplied. These curves have been intentionally selected for both cryptographic strength and efficient implementation.

Such a recommendation has significant implications on design choices made while implementing elliptic curve cryptographic functions. In standardizing specific fields for use in elliptic curve cryptography (ECC), NIST allows ECC implementations to be heavily optimized for curves over a single finite field. As a result, performance of the algorithm can be maximized and resource utilization, whether it be in code size for software or logic gates for hardware, can be minimized.

### **1.2** Scope of the Work and Objectives

Presented in this thesis are hardware architectures for multiplication, squaring and inversion over binary finite fields. Each of these architectures is optimized for a specific finite field with the intent that it might be implemented for any of the five NIST recommended binary curves. These finite field arithmetic units are then integrated together along with control logic to create an elliptic curve cryptographic co-processor capable of computing the scalar multiple of an elliptic curve point. While the coprocessor supports all curves over a single binary field, it is optimized for the special Koblitz curves [18].

To demonstrate the feasibility and efficiency of both the finite field arithmetic units and the elliptic curve cryptographic co-processor, the latter has been implemented in hardware using a field programmable gate array (FPGA). The design was synthesized, timed and then demonstrated on a physical board holding an FPGA.

The objectives of the work presented in this thesis are twofold: First to develop a high performance hardware finite field arithmetic units with low resource requirements. Second to integrate the arithmetic units into an efficient hardware elliptic curve scalar multiplier.

### **1.3** Thesis Organization

This thesis is organized as follows. Chapter 2 gives an overview of the basic mathematical concepts used in elliptic curve cryptography. This chapter also provides an introduction to the hardware/software system used to implement the elliptic curve scalar multiplier. Chapter 3 presents efficient hardware architectures for finite field multiplication and squaring. A method for high speed inversion is also discussed. In Chapter 4 a hardware architecture of an elliptic curve scalar multiplier is presented. This architecture uses the multiplication, squaring and inversion methods discussed in Chapter 3. Finally Chapter 5 provides concluding remarks and a summary of the

#### CHAPTER 1. INTRODUCTION

research contributions documented in this thesis.

## Chapter 2

## Background

The fundamental building block for any elliptic curve-based cryptosystem is elliptic curve scalar multiplication. It is this operation that will be implemented. Provided in this chapter is an overview of the mathematics behind elliptic curve scalar multiplication as well as an introduction to FPGA technology which will be used in the implementation. The chapter is organized as follows: An introduction to concepts in abstract algebra including groups and fields. Next is given an overview of arithmetic over binary finite fields followed by a discussion of arithmetic over elliptic curve groups. The chapter concludes with a brief description of the implementation media used to prototype the elliptic curve scalar multiplier.

### 2.1 Mathematical Background

Elliptic curve cryptography is built on two underlying algebraic structures. They are finite groups and finite fields. This first section provides an introduction to these

concepts. The definitions and theorems have been gathered from [9], [23] and [29] and are given without proof. These texts as well as [4] and [21] provide further discussion of the mathematics behind elliptic curve cryptography.

#### 2.1.1 Groups

**Definition 1.** Let G be a set. A *binary operation* on G is a function that assigns each ordered pair of elements in G an element in G.

**Definition 2.** An algebraic group (G, \*) is defined by a nonempty set G and a binary operation \*. (G, \*) is said to be a group if the following properties hold:

- Closure: For all elements  $a, b \in G$ , element  $(a * b) \in G$ .

- Associativity: For all elements  $a, b, c \in G$ , (a \* b) \* c = a \* (b \* c).

- Identity: There exists an element  $e \in G$  such that for any element  $a \in G$ a \* e = e \* a = a. The element e is referred to as the group identity.

- Inverse: For every element a ∈ G, the inverse b = a<sup>-1</sup> is also an element of G.

Then a \* b = b \* a = e.

**Definition 3.** If for all elements  $a, b \in G$ , a \* b = b \* a, then G is a *commutative* or *Abelian group*.

**Theorem 1.** There is a single identity in every group G.

**Example:** The integers form a group under addition. The group  $(\mathbb{Z}, +)$  possesses the properties listed in Definition 2 and has the identity e = 0.

**Example:** The set of non-zero integers under multiplication does not form a group.  $(\mathbb{Z}^*, \cdot)$  possesses all the properties of a group except one. Elements 1 and -1 are the only elements whose multiplicative inverse is also in  $\mathbb{Z}^*$ . Element 2, for example, has inverse  $1/2 \notin \mathbb{Z}^*$ .

**Definition 4.** The order of G, denoted as |G|, is the number of elements in the set G.

**Definition 5.** The order of element  $g \in G$ , denoted as |g|, is defined to be the smallest positive integer t such that  $g^t = e$ .

**Definition 6.** Element  $g \in G$  is said to be a generator of G if every element in G can be expressed by  $g^i$  for some integer i. Then |g| = |G|.

**Example:** Consider the group defined by the set  $G = \mathbb{Z}_5^* = \{1, 2, 3, 4\}$  under multiplication. Then the order of the group is |G| = 4. Since

```

2^{0} \mod 5 = 1

2^{1} \mod 5 = 2

2^{2} \mod 5 = 4

2^{3} \mod 5 = 3

2^{4} \mod 5 = 1

```

the order of element 2 is 4. And since

$$4^0 \mod 5 = 1$$

$4^1 \mod 5 = 4$

$4^2 \mod 5 = 1$

the order of element 4 is 2. Note that element 2 is a generator of the group but 4 is not.

#### 2.1.2 Finite Fields

A finite field can be considered as a finite set whose elements form a group under two binary operations; usually multiplication and addition. More specifically,

**Definition 7.**  $(F, +, \cdot)$  is a field if the following properties hold:

- The elements of F form a group under addition.

- The non-zero elements of F form a group under multiplication.

- The addition and multiplication operations are commutative, i.e. a + b = b + aand ab = ba for all  $a, b \in F$ .

- The multiplication operation can be distributed through the addition operation,

i.e. a(b + c) = ab + ac for all a, b, c ∈ F.

**Definition 8.** A field F with a finite number of elements is a *finite field*.

**Definition 9.** The *order* of a field F is the number of elements in F.

**Definition 10.** A generator of the non-zero elements of a finite field F is said to be a *primitive element* or *generator* of F.

**Definition 11.** The *characteristic* of a finite field is the smallest positive integer j such that

$$\underbrace{1+1+\dots+1}_{j \text{ times}} \equiv 0.$$

**Example:** Consider the field GF(7) containing the elements 0, 1, 2, 3, 4, 5 and 6. The order of the field is 7 and the characteristic is also 7 since

$$\underbrace{1+1+1+1+1+1}_{7 \text{ times}} \equiv 0 \pmod{7}.$$

Element 3 generates GF(7) as shown below.

$$3^{0} \equiv 1 \pmod{7}$$

$3^{4} \equiv 4 \pmod{7}$

$3^{1} \equiv 3 \pmod{7}$   $3^{5} \equiv 5 \pmod{7}$

$3^{2} \equiv 2 \pmod{7}$   $3^{6} \equiv 1 \pmod{7}$

$3^{3} \equiv 6 \pmod{7}$

**Definition 12.** A unique<sup>1</sup> finite field exists for every prime-power order. These fields are denoted  $GF(p^m)$  where p is prime and m is a positive integer.

In cryptographic applications, two types of fields are commonly used. They are

- Prime Fields: GF(p) where p is large

- Binary Fields:  $GF(2^m)$  where m is large

<sup>&</sup>lt;sup>1</sup>Unique in the sense that all fields of a specific prime-power order are isomorphic.

The architectures described in the following chapters perform arithmetic over binary finite fields. Attention will be focused exclusively on this specific case for the duration of the this thesis.

**Element Representation:** The binary field  $GF(2^m)$  contains  $2^m$  elements. Precisely how each element is represented is defined by the basis being used. The two most common representations are *polynomial* basis and *normal* basis. The work discussed in this thesis uses polynomial basis.

Let GF(2)[x] denote the set of polynomials over GF(2). Then for any irreducible polynomial

$$F(x) = x^m + f_{m-1}x^{m-1} + \dots + f_2x^2 + f_1x + 1$$

with  $f_i \in GF(2)$ , GF(2)[x]/F(x) is a finite field with  $2^m$  elements [23]. Since the field of order  $2^m$  is unique up to isomorphism, the elements of the binary field  $GF(2^m)$  can be uniquely represented by the set of polynomials over GF(2) of degree less than m. Furthermore, field addition is performed by adding two such polynomials over GF(2). Field multiplication is performed by straightforward multiplication of two polynomials and reducing mod F(x). The irreducible polynomial F(x) is often referred to as the *reduction polynomial* or *field polynomial*.

**Example:** Consider the field  $GF(2^3)$  with the irreducible polynomial  $F(x) = x^3 + x + 1$ . The elements of the field are contained in the set

$$\{0, 1, x, x+1, x^2, x^2+1, x^2+x, x^2+x+1\}$$

The element x + 1 generates  $GF(2^3)$  as shown below.

$$(x+1)^{0} \equiv 1 \pmod{F(x)}$$

$$(x+1)^{1} \equiv x+1 \pmod{F(x)}$$

$$(x+1)^{2} \equiv x^{2}+1 \pmod{F(x)}$$

$$(x+1)^{3} \equiv x^{2} \pmod{F(x)}$$

$$(x+1)^{4} \equiv x^{2}+x+1 \pmod{F(x)}$$

$$(x+1)^{5} \equiv x \pmod{F(x)}$$

$$(x+1)^{6} \equiv x^{2}+x \pmod{F(x)}$$

$$(x+1)^{7} \equiv 1 \pmod{F(x)}$$

The characteristic of the field is two since

$$1+1 \equiv 0 \pmod{2}.$$

NIST recommends the fields  $GF(2^{163})$ ,  $GF(2^{233})$ ,  $GF(2^{283})$ ,  $GF(2^{409})$  and  $GF(2^{571})$ for use in the Elliptic Curve Digital Signature Algorithm (ECDSA). These fields and corresponding reduction polynomials are listed in Table 2.1. Note that each of the reduction polynomials listed in the table is either a trinomial or a pentanomial. Also, note that the second leading non-zero coefficient of the polynomial has a relatively small degree when compared to the degree of the whole polynomial. Polynomials were chosen with these properties in order to benefit the resulting implementation of finite field arithmetic.

| Field         | Reduction Polynomial                      |

|---------------|-------------------------------------------|

| $GF(2^{163})$ | $F(x) = x^{163} + x^7 + x^6 + x^3 + 1$    |

| $GF(2^{233})$ | $F(x) = x^{233} + x^{74} + 1$             |

| $GF(2^{283})$ | $F(x) = x^{283} + x^{12} + x^7 + x^5 + 1$ |

| $GF(2^{409})$ | $F(x) = x^{409} + x^{87} + 1$             |

| $GF(2^{571})$ | $F(x) = x^{571} + x^{10} + x^5 + x^2 + 1$ |

Table 2.1: NIST Recommended Finite Fields

### 2.2 Arithmetic over Binary Finite Fields

The elements of the binary field  $GF(2^m)$  are interrelated through the operations of addition and multiplication. Since the additive and multiplicative inverses exist for all fields, the subtraction and division operations are also defined. Discussed in this section are basic methods for computing the sum, difference and product of two elements. Also presented is a method for computing the inverse of an element. The inverse, along with a multiplication, is used to implement division.

Addition and Subtraction: If we define the field elements  $a, b \in GF(2^m)$  to be the polynomials  $A(x) = a_{m-1}x^{m-1} + \cdots + a_1x + a_0$  and  $B(x) = b_{m-1}x^{m-1} + \cdots + b_1x + b_0$  respectively, then their sum is written

$$S(x) = A(x) + B(x) = \sum_{i=0}^{m-1} (a_i + b_i) x^i.$$

(2.1)

Working in a field of characteristic two provides two distinct advantages. First, the bit additions  $a_i + b_i$  in (2.1) are performed modulo 2 and translate to an exclusive-OR (XOR) operation. The entire addition is computed by a component-wise XOR operation and does not require a carry chain. The second advantage is that in GF(2) the element 1 is its own additive inverse (i.e. 1 + 1 = 0 or 1 = -1). It can be concluded then that addition and subtraction are equivalent.

#### 2.2.1 Multiplication

The product of field elements a and b is written as

$$P(x) = A(x) \times B(x) \mod F(x) = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j x^{i+j} \mod F(x)$$

where F(x) is the field reduction polynomial. By expanding B(x) and distributing A(x) through its terms we get

$$P(x) = b_{m-1}x^{m-1}A(x) + \dots + b_1xA(x) + b_0A(x) \mod F(x).$$

By repeatedly grouping multiples of x and factoring out x we get

$$P(x) = (\cdots (((A(x)b_{m-1})x + A(x)b_{m-2})x + \cdots + A(x)b_1)x + A(x)b_0) \mod F(x).$$

(2.2)

Starting with the inner most parenthesis and moving out, Algorithm 1 performs the computation required to compute the right hand side of (2.2). This algorithm can be used to compute the product of a and b.

Algorithm 1 Bit-Level Multiplication Input: A(x), B(x), and F(x)Output:  $P(x) = A(x) \times B(x) \mod F(x)$   $P(x) \leftarrow 0$ ; for i = m - 1 downto 0 do  $P(x) \leftarrow xP(x) \mod F(x)$ ; if  $(b_i == 1)$  then  $P(x) \leftarrow P(x) + A(x)$ ;

Many of the faster multiplication algorithms rely on the concept of group-level multiplication. Let g be an integer less than m and let  $s = \lceil m/g \rceil$  (Note that g is different here from previous usage). If we define the polynomials

$$B_{i}(x) = \begin{cases} \sum_{j=0}^{g-1} b_{ig+j} x^{j} & 0 \le i \le s-2, \\ (m \mod g) - 1 & \\ \sum_{j=0}^{(m \mod g) - 1} b_{ig+j} x^{j} & i = s-1, \end{cases}$$

then the product of a and b is written

$P(x) = A(x) \left( x^{(s-1)g} B_{s-1}(x) + \dots + x^g B_1(x) + B_0(x) \right) \mod F(x).$

In the derivation of equation (2.2) multiples of x were repeatedly grouped then factored out. This same grouping and factoring procedure will now be implemented for multiples of  $x^g$  arriving at

$$P(x) = (\cdots ((A(x)B_{s-1}(x))x^g + A(x)B_{s-2}(x))x^g + \cdots)x^g + A(x)B_0(x) \mod F(x)$$

which can be computed using Algorithm 2.

Algorithm 2 Group-Level MultiplicationInput: A(x), B(x), and F(x)Output:  $P(x) = A(x)B(x) \mod F(x)$  $P(x) \leftarrow B_{s-1}(x)A(x) \mod F(x);$ for k = s - 2 downto 0 do $P(x) \leftarrow x^g P(x);$  $P(x) \leftarrow B_k(x)A(x) + P(x) \mod F(x);$

#### 2.2.2 Inversion

For any element  $a \in GF(2^m)$  the equality  $a^{2^m-1} \equiv 1$  holds. When  $a \neq 0$ , dividing both sides by a results in  $a^{2^m-2} \equiv a^{-1}$ . Using this equality the inverse,  $a^{-1}$ , can be computed through successive field squarings and multiplications. In Algorithm 3 the inverse of an element is computed using this method.

The primary advantage to this inversion method is the fact that it does not require hardware dedicated specifically to inversion. The field multiplier can be used to perform all required field operations.

Algorithm 3 Inversion by Square and Multiply

Input: Field element aOutput:  $b \equiv a^{(-1)}$   $b \leftarrow a;$ for i = 1 to m - 2 do  $b \leftarrow b^2 * a;$  $b \leftarrow b^2;$

## 2.3 Arithmetic over the Elliptic Curve Group

The field operations discussed in the previous section are used to perform arithmetic over an elliptic curve. This thesis is aimed at the elliptic curve defined by the nonsupersingular Weierstrass equation for binary fields. This curve is defined by the equation

$$y^{2} + xy = x^{3} + \alpha x^{2} + \beta \tag{2.3}$$

where the variables x and y are elements of the field  $GF(2^m)$  as are the curve parameters  $\alpha$  and  $\beta$ . The points on the curve, defined by the solutions, (x, y), to (2.3) form an additive group when combined with the "point at infinity". This extra point is the group identity and is denoted by the symbol  $\mathcal{O}$ . By definition, the addition of two elements in a group results in another element of the group. As a result any point on the curve, say P, can be added to itself an arbitrary number of times and the result will also be a point on the curve. So for any integer k and point P adding P to itself k-1 times results in the point

$$kP = \underbrace{P + P + \dots + P}_{P}$$

k times

Given the binary expansion  $k = 2^{l-1}k_{l-1} + 2^{l-2}k_{l-2} + \cdots + 2k_1 + k_0$  the scalar multiple kP can be computed by

$$Q = kP = 2^{l-1}k_{l-1}P + 2^{l-2}k_{l-2}P + \dots + 2k_1P + k_0P.$$

By factoring out 2, the result is

$$Q = (2^{l-2}k_{l-1}P + 2^{l-3}k_{l-2}P + \dots + k_1P)2 + k_0P.$$

By repeating this operation it is seen that

$$Q = (\cdots ((k_{l-1}P)2 + k_{l-2}P)2 + \cdots + k_1P)2 + k_0P$$

which can be computed by the well known (left-to-right) double and add method for scalar multiplication shown in Algorithm 4.

Algorithm 4 Scalar Multiplication by Double and Add Method

Input: Integer  $k = (k_{l-1}, k_{l-2}, \dots, k_1, k_0)_2$ , Point P

Output: Point Q = kP

$Q \leftarrow \mathcal{O}$ ;

if  $(k_{l-1} == 1)$  then

$Q \leftarrow P$ ;

for i = l - 2 downto 0 do

$Q \leftarrow DOUBLE(Q)$ ;

if  $(k_i == 1)$  then

$Q \leftarrow ADD(Q, P)$ ;

Two basic operations required for elliptic curve scalar multiplication are point ADD and point DOUBLE. The mathematical definitions for these operations are derived from the curve equation in (2.3). Consider the points  $P_1$  and  $P_2$  represented by the coordinate pairs  $(x_1, y_1)$  and  $(x_2, y_2)$  respectively. Then the coordinates,  $(x_a, y_a)$ , of point  $P_a = P_1 + P_2$  (or ADD $(P_1, P_2)$ ) are computed using the equations

$$x_a = \left(\frac{y_1 + y_2}{x_1 + x_2}\right)^2 + \frac{y_1 + y_2}{x_1 + x_2} + x_1 + x_2 + \alpha$$

$$y_a = \left(\frac{y_1 + y_2}{x_1 + x_2}\right)(x_1 + x_a) + x_a + y_1.$$

Similarly the coordinates  $(x_d, y_d)$  of point  $P_d = 2P_1$  (or DOUBLE $(P_1)$ ) are computed using the equations

$$x_d = x_1^2 + \left(\frac{\beta}{x_1^2}\right)$$

$$y_d = x_1^2 + \left(x_1 + \frac{y_1}{x_1}\right)x_d + x_d.$$

So the addition of two points can be computed using two field multiplications, one field squaring, eight field additions and one field inversion. The double of a point can be computed using two field multiplications, one field squaring, six field additions and one field inversion.

## 2.4 Implementation Media

In the end, the goal of this work is to implement the field and group arithmetic described above using hardware. This can be done using two different hardware technologies. They are:

- Application Specific Integrated Circuits (ASICs)

- Field Programmable Gate Arrays (FPGAs)

ASICs are typically used when a design is massed produced or when performance is of the utmost importance. FPGAs, on the other hand, lend themselves nicely to research work where a design is being prototyped. The following attributes of the FPGA design flow are particularly advantageous.

- 1. Relatively small initial setup cost. A single FPGA is inexpensive when compared to the manufacturing cost of an ASIC design.

- 2. Simplified implementation flow. In most cases, the FPGA vendor (such as Xilinx or Altera) will provide a fully integrated tool flow. This flow will have been fully tested for compatibility with the FPGA and as a result fewer tool related problems can be expected.

- 3. Fast turn around time. An FPGA can be programmed in less than a minute and can also be reprogrammed many times. An ASIC on the other hand may take months to fabricate.

- 4. Simplified integration. Whether using an ASIC or FPGA design flow, the design must be integrated into a hardware/software system. It is common for FPGAs to be sold within such a system, minimizing the integration task required of the designer.

It makes sense that most other ECC prototypes have been implemented using FPGA technology. By following suit, results can be more easily compared to those of previously reported work. The following section provides an overview of the fundamental principles on which FPGAs are based. Introduced next is the Rapid-Prototyping Platform which includes the FPGA and hardware/software system used to prototype the design discussed in this thesis.

#### 2.4.1 Field Programmable Gate Arrays

An FPGA or field programmable gate array is an integrated circuit consisting of

- Configurable Logic Blocks (CLBs),

- Input/Output Blocks (IOBs) and

- programmable interconnect.

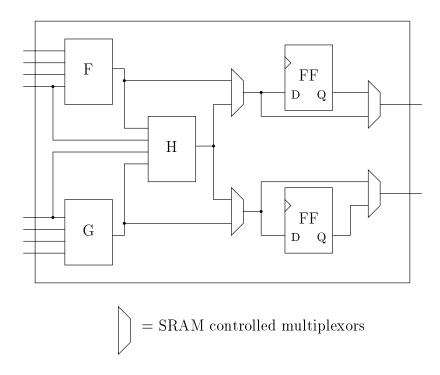

**Configurable Logic Blocks:** A typical Configurable Logic Block (CLB) is composed of both combinational and sequential logic. The combinational logic can be configured to create any of a number of possible boolean functions. Flip-Flops are provided to support sequential logic and can be utilized or bypassed depending on the configuration. Figure 2.1 shows an example CLB with 8 inputs and 2 outputs. The blocks F, G and H are programmable functions which can be configured to perform any one of a number of different boolean functions. The functions are typically implemented with either look-up tables (LUTs) or logic gates. The actual number of possible boolean functions depends on the implementation. The multiplexors are used to configure the interconnect inside the CLB.

Figure 2.1: Functionality of a CLB

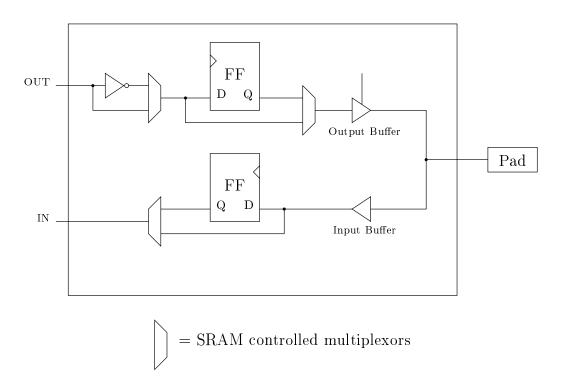

**Input/Output Blocks:** The Input/Output Blocks (IOBs) are blocks used to connect internal *nets* to external pins or pads on the FPGA. These blocks control the direction of the signal and can also register both input and output data. Figure 2.2 shows an example IOB.

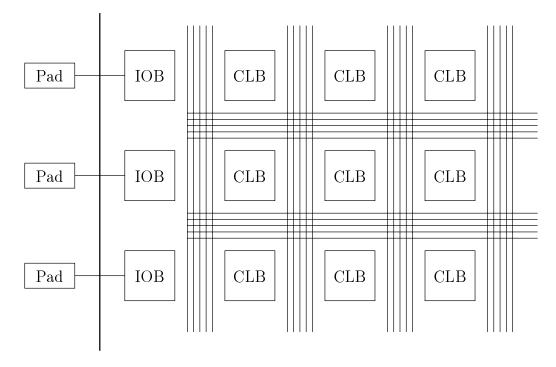

**Programmable Interconnect:** An FPGA is made of many IOBs and CLBs. These blocks can be configured and connected together to achieve complex functionality. The connections between the blocks are performed by the programmable interconnect. There are several ways in which the CLBs, IOBs and programmable interconnect are organized. One such organization is the symmetric array method. As shown in Figure 2.3, the CLBs are organized in a two dimensional array with

Figure 2.2: Functionality of an IOB

IOBs around the perimeter. The programmable interconnect is routed in between the blocks.

**Configuring the FPGA:** The configuration of each CLB and IOB as well as the programmable interconnect is defined when a design is loaded into the FPGA. The configuration is typically stored in static RAM cells. This allows the configuration to be preserved through reset of the FPGA while still providing the option of reconfiguration.

Figure 2.3: CLB Organization

#### 2.4.2 The Rapid-Prototyping Platform

The Rapid-Prototyping Platform (RPP) [6, 7] is a hardware/software system provided to Canadian universities by Canadian Microelectronics Corporation (CMC). The major hardware components included in the system are:

- ARM Integrator/AP,

- ARM Integrator/CM7TDMI and

- ARM Integrator/LM-SCV600E+.

The Integrator/CM7TDMI board contains a fully functional ARM7 core. The Integrator/LM-SCV600E+ board holds a Xilnix XCV2000E FPGA. The chips on these two boards

are allowed to communicate through the Integrator/AP board. The common bus between the ARM7 core and the Virtex FPGA is the Arm High Performance Bus (AHB). In this system the ARM7 is the bus master and the design loaded onto the FPGA is the slave. In other words, the ARM7 core initiates bus transactions and the FPGA design responds to them.

The hardware and software design flows of the RPP are thoroughly documented in [6]. Provided here is a brief overview. Hardware flow, the more complicated of the two flows, is summarized in the following steps.

- 1. HDL (Hardware Description Language) coding. This is done in either VHDL or Verilog HDL.

- 2. Functional simulation and verification (Cadence Verilog XL).

- 3. Synthesis (Synopsys FPGA Compiler II).

- 4. Place/Route (Xilinx Foundation Software).

- 5. Static Timing Analysis (Xilinx Foundation Software).

- 6. Generate the bit file (Xilinx Foundation Software).

- 7. Download the bit file onto the FPGA.

If the design fails to pass static timing analysis, changes may need to be made to the HDL in which case all the steps must be performed again. The software side is less complicated.

- Write the driver code in C using the ARM Firmware Suite provided with the RPP software environment. The firmware suite provides read and write commands used to access address locations on the AHB bus.

- 2. Compile the code for the ARM7 core.

- 3. Download the core into memory on the ARM7 core.

- 4. Execute the code.

# Chapter 3

# High Performance Finite Field Arithmetic

In order to optimize the curve arithmetic discussed in Section 2.3 the underlying field operations must be implemented in a fast and efficient way. The required field arithmetic operations are addition, multiplication, squaring and inversion. Each of these operations have been implemented in hardware for use in the prototype discussed in Chapter 4. Generally speaking, field multiplication has the greatest effect on the performance of the entire elliptic curve scalar multiplication.<sup>1</sup> For this reason, focus will be primarily on the field multiplier when discussing hardware architectures for field arithmetic.

This chapter is organized as follows. Section 3.1 presents a hardware architecture designed to perform finite field multiplication. In Section 3.2 the ideas presented for multiplication are extended to create a hardware architecture optimized for squar-

<sup>&</sup>lt;sup>1</sup>Inversion takes much longer than multiplication, but its effect on performance can be greatly reduced through use of projective coordinates. This is discussed in greater detail in Section 4.1.

ing. Section 3.3 gives a method for inversion due to Itoh and Tsujii. This method does not require any additional hardware but instead uses the multiplication and squaring units described in Sections 3.1 and 3.2. Section 3.4 gives a description of a comparator/adder which both compares and adds finite field elements. Finally, Section 3.5 summarizes results gleaned from a hardware prototype of each arithmetic unit/routine.

#### 3.1 Multiplication

Hardware/software architectures for field multiplication can be roughly categorized into three groups. Bit Serial multipliers are based on Algorithm 1 on page 14 where each coefficient of operand b is considered in a separate iteration of the for loop. Such an implementation is resource efficient in that it can be implemented using an m-bit LFSR defined by the reduction polynomial F(x) along with an m bit accumulator. The LFSR and accumulator are connected as shown in Figure 3.1. The disadvantage of such an architecture is the number of iterations required of the for loop. In hardware, the m iterations translate to a minimum of m clock cycles. In contrast, Bit Parallel multipliers complete a multiplication in a single iteration. All m-bits of both input operands are considered at the same time and the result is immediately generated. Unfortunately, such a multiplier cannot be implemented in software and may result in a costly design when implemented in hardware. The minimum clock period of such an implementation is also likely to be large. A compromise between these architectures is the Digit Serial multiplier. This multiplier is based on Algorithm 2 on page 15 and considers multiple coefficients of operand b in each iteration.

Figure 3.1: LFSR Based Multiplier

A multiplication is completed in  $\lceil m/g \rceil$  iterations and requires fewer resources than the bit parallel method.

In [13] a digit serial multiplier is proposed which is based on look-up tables. This method was implemented in software for the field  $GF(2^{163})$  and reported in [16]. To the best of our knowledge this performance of 0.540  $\mu$ -seconds for a single field multiplication is the fastest reported result for a software implementation. In this section the possibilities of using this look-up table-based algorithm in hardware will be explored.

First to be described in this section is the algorithm used for multiplication. Then presented is a hardware structure designed to compute  $R(x)W(x) \mod F(x)$  where R(x) and W(x) are polynomials with degrees g - 1 and m - 1 respectively and  $g \ll m$ . A description of the multiplier's data path follows. In conclusion there will be a discussion behind the reasons for the choice of digit sizes.

#### 3.1.1 Algorithm

The computations of

$$P(x) \leftarrow x^g P(x) \mod F(x)$$

and

$P(x) \leftarrow B_k(x)A(x) + P(x) \mod F(x)$

from the **for** loop of Algorithm 2 on page 15 can be broken up into the following steps.

$$V_1 = x^g \sum_{i=0}^{m-g-1} p_i x^i,$$

$$V_2 = x^g \sum_{i=m-g}^{m-1} p_i x^i \mod F(x)$$

$$V_3 = B_k(x) A(x) \mod F(x) \text{ and }$$

$$P(x) = V_1 + V_2 + V_3$$

Note that  $V_1$  is a g-bit shift of the lower m - g bits of P(x).  $V_2$  is a g-bit shift of the upper g bits of P(x) followed by a modular reduction.  $V_3$  requires a polynomial multiplication and reduction where the operand polynomials have degree g - 1 and m - 1. Algorithm 2 can be modified to create Algorithm 5.

In [13] polynomials  $V_2$  and  $V_3$  are computed with the assistance of look-up tables mainly for software implementation. The look-up tables used to compute  $V_2$  and  $V_3$ are referred to as the *M*-Table and *T*-Table respectively. The *M*-Table is addressed by the bit string  $(p_{m-1}, p_{m-2}, \ldots, p_{m-g})$  interpreted as the integer  $2^{g-1}p_{m-1} + 2^{g-2}p_{m-2} + \cdots + p_{m-g}$ . Similarly the *T*-Table is addressed by the coefficients of  $B_k(x)$ , or the Input: A(x), B(x), and F(x)Output:  $P(x) = A(x)B(x) \mod F(x)$   $P(x) \leftarrow B_{s-1}(x)A(x) \mod F(x);$ for k = s - 2 downto 0 do  $V_1 \leftarrow x^g \sum_{i=0}^{m-g-1} p_i x^i;$   $V_2 \leftarrow x^g \sum_{i=m-g}^{m-1} p_i x^i \mod F(x);$   $V_3 \leftarrow B_k(x)A(x) \mod F(x);$  $P(x) \leftarrow V_1 + V_2 + V_3;$

integer  $B_k(x = 2)$ . The elements of the *M*-Table are a function of the reduction polynomial F(x) and can be precomputed. The elements of the *T*-Table are a function of A(x) and hence are dynamic. These values must be computed at the beginning of every multiplication.

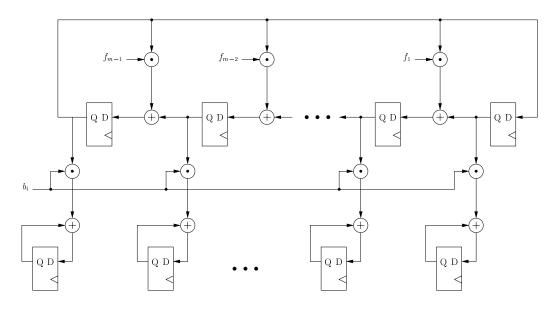

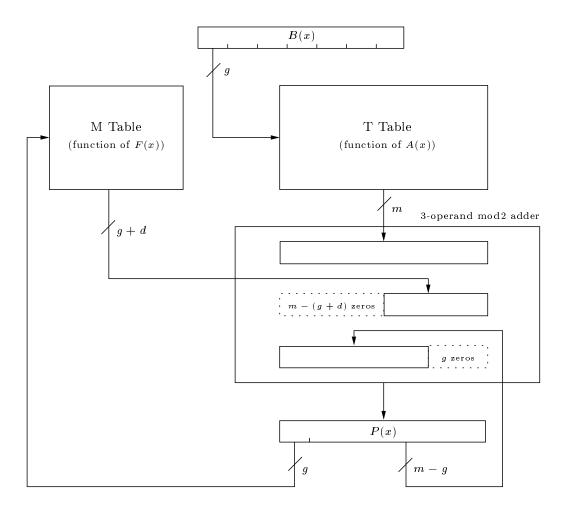

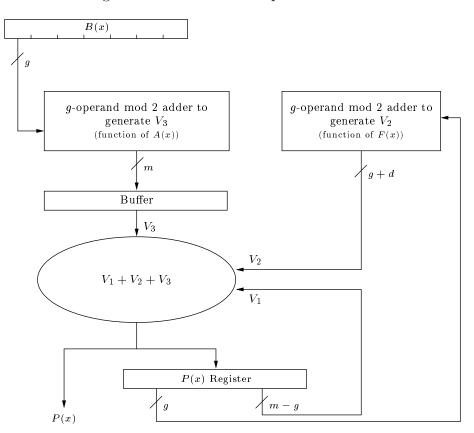

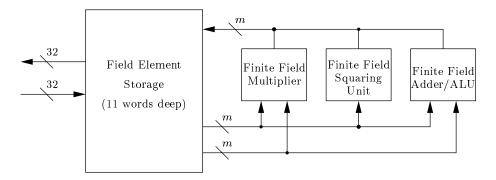

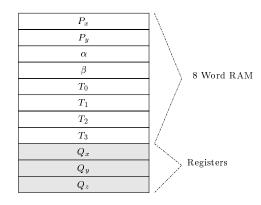

The data path associated with this method is shown in Figure 3.2. The given multiplier is based on this method but is optimized specifically for hardware implementation.

Figure 3.2: The Multiplier Data-Path

#### **3.1.2** Computation of $R(x)W(x) \mod F(x)$

Instead of using tables, the polynomials  $V_2$  and  $V_3$  are computed on the fly. The computation of  $V_2$  and  $V_3$  are similar in that they both require a multiplication of two polynomials followed by a reduction, where the first polynomial has degree g - 1and the other has degree less than m. This is obvious for  $V_3$  and can be shown easily for  $V_2$ . Note that

$$V_2 = p_{m-1}x^{m+g-1} + \dots + p_{m-g+1}x^{m+1} + p_{m-g}x^m \mod F(x)$$

$$= x^m \left( p_{m-1}x^{g-1} + \dots + p_{m-g+1}x + p_{m-g} \right) \mod F(x).$$

The field reduction polynomial  $F(x) = x^m + x^d + \dots + 1$  provides us the equality  $x^m \equiv x^d + \dots + 1$ . Substituting for  $x^m$  we see that

$$V_2 = (x^d + \dots + 1) (p_{m-1}x^{g-1} + \dots + p_{m-g+1}x + p_{m-g}) \mod F(x).$$

Provided d + g < m,  $V_2$  results in a polynomial of degree less than m which does not need to be reduced. Since d is relatively small for all five NIST polynomials, it is reasonable to assume that d+g < m. For the remainder of this work, this assumption will be made.

With this said, the following method can be used to compute both  $V_2$  and  $V_3$ . Consider the polynomial multiplication and reduction  $R(x)W(x) \mod F(x)$  where  $R(x) = \sum_{i=0}^{g-1} r_i x^i$  and W(x) is a polynomial with degree less than m. Then

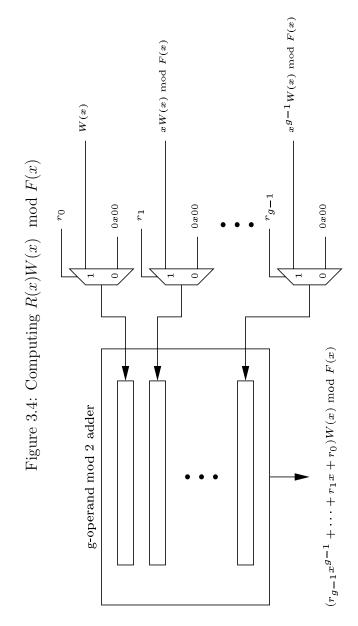

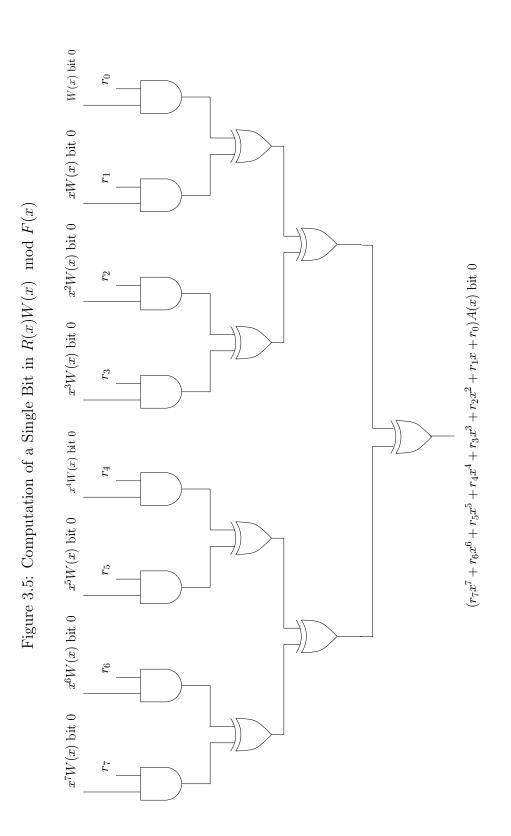

$$\begin{aligned} R(x)W(x) \mod F(x) = & r_{g-1}(x^{g-1}W(x) \mod F(x)) \\ &+ r_{g-2}(x^{g-2}W(x) \mod F(x)) \\ &\vdots \\ &+ & r_1(xW(x) \mod F(x)) \\ &+ & r_0(W(x) \mod F(x)) \end{aligned}$$

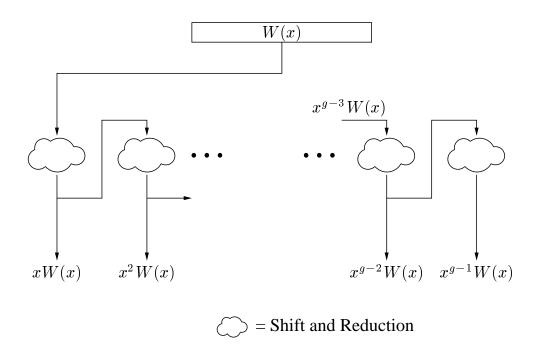

The value  $x^iW(x) \mod F(x)$  is just a shifted and reduced version of  $x^{i-1}W(x)$ mod F(x). So each value  $x^iW(x) \mod F(x)$  can be generated sequentially starting with  $x^0W(x)$  as shown in Figure 3.3. When using a reduction polynomial with a low Hamming weight, such as a trinomial or pentanomial, these terms can be computed quickly at very little cost. Once these values are determined, the final result is computed using a g-input modulo 2 adder. The inputs to the adder are enabled by their corresponding coefficient  $r_i$ . This is shown in Figure 3.4. Note that the polynomial  $x^iW(x)$  affects the output of the adder only if the coefficient bit  $r_i$  is a one. Otherwise the input associated with  $x^iW(x)$  is driven with zeros.

Each individual output bit of the g-operand mod 2 adder is computed using g-1XOR gates and g AND gates. The AND gates are used to enable each input bit and the XOR gates compute the mod 2 addition. Figure 3.5 demonstrates how this is done. The depth of the logic in the figure is linearly related to g.

Figure 3.3: Generating  $x^i W(x) \mod F(x)$

This method for multiplication is implemented for computation of both  $V_2$  and  $V_3$ . In the case of  $V_3$ , the polynomial W(x) has degree m-1 and will change for every field multiplication. For  $V_2$  the polynomial W(x) has degree d and is fixed. The value d is the degree of the second leading non-zero coefficient of F(x). For reasonable digit sizes this computation can be performed in a single clock cycle.

#### 3.1.3 The Multiplier Data Path

The multiplier's data path connecting the  $V_2$  and  $V_3$  generators along with the adder used to compute  $P(x) = V_1 + V_2 + V_3$  is shown in Figure 3.6. A buffer is inserted at the output of the  $V_3$  generator to separate its delay from the delay of the adder for  $V_1 + V_2 + V_3$ . This, in effect, increases the maximum possible value for the digit size g. If added by itself, this buffer would add a cycle of latency to the multiplier's performance time. This extra cycle is compensated for by bypassing the P(x) register and driving the multiplier's output with the output of the 3-operand mod2 adder. It is important to note that the delay of the 3-operand mod2 adder is being merged with the delay of the bus which connects the multiplier to the rest of the design. In this case the relatively relaxed bus timing had room to accommodate the delay.

Figure 3.6: Modified Multiplier Data-Path

#### 3.1.4 Choice of Digit Size

The multiplier will complete a multiplication in  $\lceil m/g \rceil$  clock cycles. Since this is a discrete value, the performance may not change for every value of g. To minimize cost of the multiplier (which increases with g) the smallest digit size g should be chosen for a given performance  $\lceil m/g \rceil$ . For example, the digit sizes g = 21 and g = 22 for field size m = 163 result in the same performance,  $\lceil \frac{163}{21} \rceil = \lceil \frac{163}{22} \rceil = 8$ , but g = 22 requires a larger multiplier.

A prototype of this multiplier for the field  $GF(2^{163})$  and NIST polynomial has been implemented for each of the digit sizes shown in Table 3.1. For each digit size, the table lists the corresponding cycle performance and resource cost. A maximum digit size of g = 41 was chosen for several reasons. First, as the performance cost of the actual field multiplication decreases, the relative cost of loading and unloading the multiplier increases. So as the digit size increases, its affect on the total performance (including time to load and unload the multiplier) decreases. Second, results showed that g > 41 had difficulty meeting timing at the target operating frequency of 66 MHz. Instead of spending time redesigning the field multiplier, a maximum digit size of 41 was selected.

# 3.2 Squaring

While squaring is a specific case of general multiplication and can be performed by the multiplier, performance can be improved significantly by optimizing the architecture specifically for the case of squaring. The square of an element a represented by A(x) involves two mathematical steps. The first is the polynomial multiplication of A(x)

| Digit  | Performance     | # LUTs | # Flip |

|--------|-----------------|--------|--------|

| Size   | in clock cycles |        | Flops  |

| g = 1  | 163             | 677    | 670    |

| g = 4  | 41              | 854    | 670    |

| g = 28 | 6               | 3,548  | 670    |

| g = 33 | 5               | 4,040  | 670    |

| g = 41 | 4               | 4,728  | 670    |

Table 3.1: Performance/Cost Trade-off for Multiplication over  $GF(2^{163})$

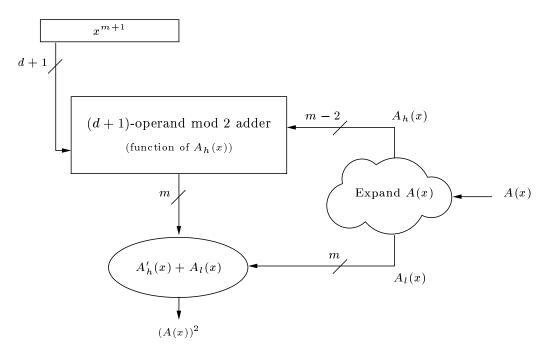

resulting in

$$A^{2}(x) = a_{m-1}x^{2m-2} + \dots + a_{2}x^{4} + a_{1}x^{2} + a_{0}.$$

The second is the reduction of this polynomial modulo F(x). If the terms with degree greater than m - 1 are separated and  $x^{m+1}$  is factored out where possible the result will be  $A^2(x) = A_h(x)x^{m+1} + A_l(x)$  where

$$A_h(x) = a_{m-1}x^{m-3} + \dots + a_{\left(\frac{m+3}{2}\right)}x^2 + a_{\left(\frac{m+1}{2}\right)}$$

$$A_l(x) = a_{\left(\frac{m-1}{2}\right)}x^{m-1} + \dots + a_1x^2 + a_0,$$

The polynomial  $A_l(x)$  has degree less than m and does not need to be reduced. The product  $A_h(x)x^{m+1}$  may have degree as large as 2m - 2. The reduction polynomial gives us the equality  $x^m = x^d + \cdots + 1$ . Multiplying both sides by x, we get  $x^{m+1} = x^{d+1} + \cdots + x$ . So

$$A_h(x)x^{m+1} = A_h(x) (x^{d+1} + \dots + x).$$

This multiplication can be performed using a method similar to the one described in Section 3.1. The same architecture used to compute  $R(x)W(x) \mod F(x)$  in the multiplier is used here to compute  $x^{m+1}A_h(x)$ . The digit size is set to g = d + 2and the elements of g-operand mod 2 adder are generated from  $A_h(x)$ .  $A_h(x)$  is in turn generated by expanding A(x) (i.e. inserting zeros between the coefficient bits of A(x)). Since the digit size is set to d + 2, the multiplication is completed in a single cycle. This method only works if d + 2 < m which is the case for each of the NIST polynomials. Figure 3.7 shows the data flow for the squaring operation. Note that the flow does not include any buffers and so is implemented in pure combinational logic.

Figure 3.7: Data-Path of the Squaring Unit

The prototype of this squaring unit for field  $GF(2^{163})$  using the NIST reduction

polynomial runs at 66 MHz and is capable of performing a squaring operation in a single clock cycle. This implementation requires 330 LUTs and 328 Flip Flops.

# 3.3 Inversion

The inversion method described in Algorithm 3 on page 16 requires m - 1 squarings and m - 2 multiplications. In order to accurately estimate the cycle performance of the inversion, consideration must be given to the performance of the multiplication and squaring units as well as the time required to load and unload these units. The architecture of the elliptic curve scalar multiplier will be discussed in detail in Chapter 4. For now, it is sufficient to know that the arithmetic units are loaded using two independent m bit data buses and unloaded using a single m bit data bus. The operands are stored in a dual port memory which takes two clock cycles to read from and one cycle to write to. These combined makes three cycles that are required to both load and unload any arithmetic unit. Further analysis assumes that these three cycles remain constant for all m. If  $C_s$  and  $C_m$  denote the number of clock cycles required to complete a squaring and multiplication respectively, then an inversion can be completed in

$$(C_s + 3)(m - 1) + (C_m + 3)(m - 2)$$

clock cycles. For the field  $GF(2^{163})$  where  $C_s = 1$  and  $C_m = 4$ , this translates to 1775 clock cycles.

Performance can be improved by using Algorithm 6 due to Itoh and Tsujii [15]. This algorithm is derived from the equation  $a^{(-1)} \equiv a^{2^m-2} \equiv \left(2^{2^{m-1}-1}\right)^2$  which is true for any element  $a \in GF(2^m)$ . From

$$a^{2^{t}-1} \equiv \begin{cases} \left(a^{2^{t/2}-1}\right)^{2^{t/2}} \left(a^{2^{t/2}-1}\right) & \text{for } t \text{ even,} \\ a \left(a^{2^{t-1}-1}\right)^{2} & \text{for } t \text{ odd,} \end{cases}$$

(3.1)

the computation required for the exponentiation  $2^{2^{m-1}-1}$  can be iteratively broken down. Algorithm 6 requires  $\lfloor \log_2(m-1) \rfloor + H(m-1) - 1$  multiplications and m-1squarings. Using the notation defined earlier, this translates to

$$(C_s+3)(m-1) + (C_m+3)(\lfloor \log_2(m-1) \rfloor + H(m-1) - 1)$$

clock cycles. For  $GF(2^{163})$  this translates to 711 clock cycles.

| Algorithm | 6 | Optimized | Inversion | by | Square | and | Multiply [ | 15] |

|-----------|---|-----------|-----------|----|--------|-----|------------|-----|

|           |   |           |           |    |        |     |            |     |

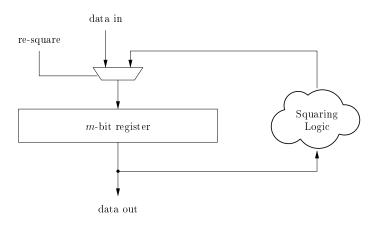

Inputs: Field element a, Binary representation of  $m - 1 = (m_{l-1}, \dots, m_2, m_0)_2$ Output:  $b \equiv a^{(-1)}$   $b \leftarrow a^{m_{l-1}}$ ;  $e \leftarrow 1$ ; for i = l - 2 downto 0 do  $b \leftarrow b^{2^e}b$ ;  $e \leftarrow 2e$ ; if  $(m_i == 1)$  then  $b \leftarrow b^2a$ ; e = e + 1;  $b \leftarrow b^2$ ; Now, the majority of the time spent for each squaring operation is used to load and unload the squaring unit (three out of the four cycles). Algorithm 6 requires several sequences of repetitive squaring (i.e. computations of the form  $x^{2^t}$ ). These repeated squarings do not require intermediate values to be stored outside the squaring unit. By modifying the squaring unit to support the *re-square* of an element, most of the memory accesses otherwise required to load and unload the squaring unit are eliminated. In fact, the squaring unit only needs to be loaded and unloaded once for each multiplication. Hence the number of clock cycles is reduced to

$$(C_s(m-1) + 3(\lfloor \log_2(m-1) \rfloor + H(m-1) - 1)) + (C_m + 3)(\lfloor \log_2(m-1) \rfloor + H(m-1) - 1)$$

clock cycles. For the field  $GF(2^{163})$  with  $C_s = 1$  and  $C_m = 4$ , this results in 252 clock cycles.

This is a competitive value since a typical hardware implementation of the Extended Euclidean Algorithm (EEA) is expected to complete an inversion in approximately 2m clock cycles or 326 cycles for  $GF(2^{163})$ . This corresponds to a 60 clock cycle reduction or 20% performance improvement without requiring hardware dedicated specifically for inversion. Table 3.2 lists the performance numbers of the previously mentioned inversion methods when implemented over the field  $GF(2^{163})$ .

The actual time to complete an inversion using the ECC co-processor architecture discussed in Chapter 4 is 259 clock cycles. The 7 extra cycles are due to control related instructions executed in the micro-sequencer.

| Method                     | # Squarings | # Multiplications                        | # Cycles |

|----------------------------|-------------|------------------------------------------|----------|

| Square & Multiply          | m-1         | m-2                                      | 1127     |

| Itoh & Tsujii              | m-1         | $\lfloor \log_2(m-1) \rfloor + H(m) - 1$ | 711      |

| Itoh & Tsujii w/ re-square | m-1         | $\lfloor \log_2(m-1) \rfloor + H(m) - 1$ | 252      |

| EEA                        | -           | -                                        | 326      |

Table 3.2: Comparison of Various Inversion Methods for  $GF(2^{163})$

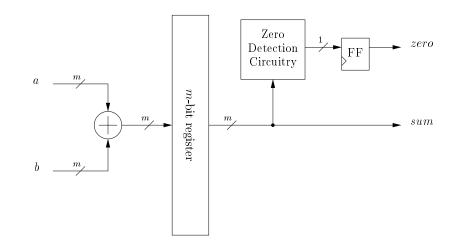

## 3.4 Comparator/Adder

The primary purpose of the Comparator/Adder is to compute the sum of two field elements. This is done with an array of *m* exclusive OR gates. To minimize register usage as well as time to complete the addition, the sum of the two operands is the only value stored in a register. In this way, the sum is available immediately after the operands are loaded into the Comparator/Adder. In other words, it takes zero clock cycles to complete a finite field addition.

In addition to computing the sum of two finite field elements, the Comparator/Adder also acts as a comparator. The comparison is performed by taking the logical NOR of all the bits in the sum register. If the result is a one, then the sum is zero and the two operands are equal. If operand a is set to zero, then operand b can be tested for zero. The logic depth for the zero detect circuitry (the *m*-bit NOR gate) is  $\log_2(m)$  and is registered before being sent out of the module. Figure 3.8 provides a functional diagram of the Comparator/Adder.

Figure 3.8: Data-Path of the Comparator/Adder

## 3.5 Concluding Remarks

In this chapter, we have discussed hardware architectures designed to perform finite field addition, multiplication and squaring. Also discussed was an efficient method for inversion which uses the squaring and multiplication units. The performance results associated with these arithmetic units are summarized in Table 3.3.

| Operation # Cy |     | # Cycles Including Initial an |  |  |

|----------------|-----|-------------------------------|--|--|

| (g = 41)       |     | Final Data Movement           |  |  |

| Multiplication | 4   | 7                             |  |  |

| Squaring       | 1   | 4                             |  |  |

| Addition       | 0   | 3                             |  |  |

| Inversion      | 256 | 259                           |  |  |

Table 3.3: Performance of Finite Field Operations

# Chapter 4

# A Co-processor Architecture for ECC Scalar Multiplication

In the recent past, several articles have proposed various hardware architectures/accelerators for ECC. These elliptic curve cryptographic accelerators can be categorized into three functional groups. They are

- Accelerators which use general purpose processors to implement curve operations but implement the finite field operations using hardware. References

[2] and [32] are examples of this. Both of these implementations support the composite field GF(2<sup>155</sup>).

- 2. Accelerators which perform both the curve and field operations in hardware but use a small field size such as  $GF(2^{53})$ . Architectures of this type include those proposed in [30] and [10]. In [30], a processor for the field  $GF(2^{168})$  is synthesized, but not implemented. Both works discuss methods to extend their implementation to a larger field size but do not actually do so.

Accelerators which perform both curve and field operations in hardware and use fields of cryptographic strength such as GF(2<sup>163</sup>). Processors in this category include [3, 12, 19, 26, 28].

The work discussed in this chapter falls into category three. The architectures proposed in [26] and [28] were the first reported cryptographic strength elliptic curve co-processors. Montgomery scalar multiplication with an LSD multiplier was used in [28]. In [26] a new field multiplier is developed and demonstrated in an elliptic curve scalar multiplier. In both [19] and [3] parameterized module generation is discussed. To the best of our knowledge the architecture proposed in [12] offers the fastest scalar multiplication using FPGA technology at 0.144 milliseconds. This architecture uses Montgomery scalar multiplication with López and Dahab's projective coordinates. They use a shift and add field multiplier but also compare LSD and Karatsuba multipliers.

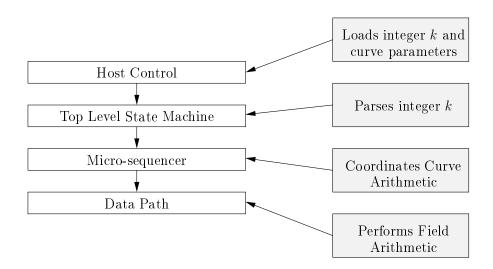

In this chapter a hardware architecture for elliptic curve scalar multiplication is proposed. The architecture uses projective coordinates and is optimized for scalar multiplication over the Koblitz curves. The arithmetic routines discussed in Chapter 3 are used to perform the field arithmetic. This architecture has been implemented and demonstrated on an FPGA.

The chapter is organized as follows. Section 4.1 introduces projective coordinates and discusses some of the reasons for using a projective system. Section 4.2 presents two methods for recoding the scalar. They are non-adjacent form (NAF) and  $\tau$ -adic non-adjacent form ( $\tau$ -NAF). Then in Section 4.3 the ideas described in 4.1 and 4.2 are implemented in a co-processor architecture for scalar multiplication. The data path and different levels of control are outlined there. Section 4.4 discusses the prototype of the scalar multiplier. Finally in Section 4.5 concludes with results gathered from the prototype.

#### 4.1 **Projective Coordinates**

Projective coordinates allow the inversion required by each DOUBLE and ADD to be eliminated at the expense of a few extra field multiplications. The benefit is measured by the ratio

$$\frac{\text{Time to Complete Inversion}}{\text{Time to Complete Multiplication}}.$$

(4.1)

The inversion algorithm proposed by Itoh and Tsujii [15] will be used and therefore, the ratio in (4.1) is guaranteed to be larger than  $\lfloor \log_2(m-1) \rfloor$  and could be larger depending on the efficiency of the squaring operations. Therefore, projective coordinates will provide us the best performance for NIST curves. Several flavors of projective coordinates have been proposed over the last few years. The prominent ones are *Standard* [22], *Jacobian* [5, 14] and López & Dahab [20] projective coordinates.

If the affine representation of P be denoted as (x, y) and the projective representation of P be denoted as (X, Y, Z), then the relation between affine and projective coordinates for the Standard system is

$$x = \frac{X}{Z}$$

and  $y = \frac{Y}{Z}$

For Jacobian projective coordinates the relation is

$$x = \frac{X}{Z^2}$$

and  $y = \frac{Y}{Z^3}$

Finally for López & Dahab's, the relation between affine and projective coordinates is

$$x = \frac{X}{Z}$$

and  $y = \frac{Y}{Z^2}$

For López & Dahab's system the projective equation of the elliptic curve in (2.3) then becomes

$$Y^2 + XYZ = X^3Z + \alpha X^2Z^2 + \beta Z^4.$$

It is important to note that when using the left-to-right double and add method for scalar multiplication all point additions are of the form ADD(P,Q). The base point P is never modified and as a result will maintain its affine representation (i.e. P = (x, y, 1)). The constant Z coordinate significantly reduces the cost of point addition (from 14 field multiplications down to 10). The addition of two distinct points  $(X_1, Y_1, Z_1) + (X_2, Y_2, 1) = (X_a, Y_a, Z_a)$  using *mixed* coordinates (one projective point and one affine point) is then computed by

$$A = Y_2 \cdot Z_1^2 + Y_1 \qquad E = A \cdot C$$

$$B = X_2 \cdot Z_1 + X_1 \qquad X_a = A^2 + D + E$$

$$C = Z_1 \cdot B \qquad F = X_a + X_2 \cdot Z_a \qquad (4.2)$$

$$D = B^2 \cdot (C + \alpha \cdot Z_1^2) \qquad G = X_a + Y_2 \cdot Z_a$$

$$Z_a = C^2 \qquad Y_a = E \cdot F + Z_a \cdot G$$

Similarly, the double of a point  $(X_1, Y_1, Z_1) + (X_1, Y_1, Z_1) = (X_d, Y_d, Z_d)$  is computed

by

$$Z_d = Z_1^2 \cdot X_1^2$$

$$X_d = X_1^4 + \beta \cdot Z_1^4$$

$$Y_d = \beta \cdot Z_1^4 \cdot Z_d + X_d \cdot (\alpha \cdot Z_d + Y_1^2 + \beta \cdot Z_1^4)$$

(4.3)

In Table 4.1, the number of field operations required for the affine, Standard, Jacobean and López & Dahab coordinate systems are provided. In the table the symbols  $\mathcal{M}, \mathcal{S}, \mathcal{A}$  and  $\mathcal{I}$  denote field multiplication, squaring, addition and inversion respectively.

| System        | Point Addition                                              | Point Doubling                                              |

|---------------|-------------------------------------------------------------|-------------------------------------------------------------|

| Affine        | $2\mathcal{M} + 1\mathcal{S} + 8\mathcal{A} + 1\mathcal{I}$ | $3\mathcal{M} + 2\mathcal{S} + 4\mathcal{A} + 1\mathcal{I}$ |

| Standard      | $13\mathcal{M} + 1\mathcal{S} + 7\mathcal{A}$               | $7\mathcal{M} + 5\mathcal{S} + 4\mathcal{A}$                |

| Jacobian      | $11\mathcal{M} + 4\mathcal{S} + 7\mathcal{A}$               | $5\mathcal{M} + 5\mathcal{S} + 4\mathcal{A}$                |

| López & Dahab | $10\mathcal{M} + 4\mathcal{S} + 8\mathcal{A}$               | $5\mathcal{M} + 5\mathcal{S} + 4\mathcal{A}$                |

Table 4.1: Comparison of Projective Point Systems

The projective coordinate system defined by López and Dahab will be used since it offers the best performance for both point addition and point doubling.

## 4.2 Scalar Multiplication using Recoded Integers

The binary expansion of an integer k is written as  $k = \sum_{i=0}^{l-1} k_i 2^i$  where  $k_i \in \{0, 1\}$ . For the case of elliptic curve scalar multiplication the length l is approximately equal to m, the degree of the extension field. Assuming an average Hamming weight, a scalar multiplication will require approximately l/2 point additions and l-1 point doubles. Several recoding methods have been proposed which in effect reduce the number of additions. In this section two methods are discussed; NAF [11, 31] and  $\tau$ -adic NAF [18, 31].

#### 4.2.1 Scalar Multiplication using Binary NAF

The symbols in the binary expansion are selected from the set  $\{0,1\}$ . If this set is increased to  $\{0,1,-1\}$  the expansion is referred to as *signed binary* (SB) representation. When using this representation, the double and add scalar multiplication method must be slightly modified to handle the -1 symbol (often denoted  $\overline{1}$ ). If the expansion  $k'_{l-1}2^{l-1}+\cdots+k'_12+k'_0$  where  $k'_i \in \{0,1,\overline{1}\}$  is denoted by  $(k'_{l-1},\ldots,k'_1,k'_0)_{SB}$ , then Algorithm 7 computes the scalar multiple of point P. The negative of the point

**Algorithm 7** Scalar Multiplication for Signed Binary Representation Input: Integer  $k = (k'_{l-1}, k'_{l-2}, \dots, k'_1, k'_0)_{\text{SB}}$ , Point P

Output: Point Q = kP  $Q \leftarrow \mathcal{O};$  **if**  $(k'_{l-1} \neq 0)$  **then**   $Q \leftarrow k'_{l-1}P;$  **for** i = l - 2 **downto** 0 **do**   $Q \leftarrow \text{DOUBLE}(Q);$  **if**  $(k'_i \neq 0)$  **then**  $Q \leftarrow \text{ADD}(Q, k'_iP);$

(x, y) is (x, x + y) and can be computed with a single field addition. The signed

binary representation is redundant in the sense that any given integer has more than one possible representation. For example, 17 can be represented by  $(1001)_{SB}$  as well as  $(101\overline{1})_{SB}$ .

Interest here is in a particular form of this signed binary representation called NAF or non-adjacent form. A signed binary integer is said to be in NAF if there are no adjacent non-zero symbols. The NAF of an integer is unique and it is guaranteed to be no more than one symbol longer than the corresponding binary expansion. The primary advantage gained from NAF is its reduced number of non-zero symbols. The average Hamming weight of a NAF is approximately l/3 [31] compared to that of the binary expansion which is l/2. As a result, the running time of elliptic curve scalar multiplication when using binary NAF is reduced to (l + 1)/3 point additions and l point doubles. This represents a significant reduction in run time.

In [31], Solinas provides a straightforward method for computing the NAF of an integer. This method is given here in Algorithm 8.

### 4.2.2 Scalar Multiplication using $\tau$ -NAF

Anomalous Binary Curves (ABC's), first proposed for cryptographic use in [18], provide an efficient implementation when the scalar is represented as a complex algebraic number. ABC's, often referred to as the Koblitz curves, are defined by

$$y^2 + xy = x^3 + \alpha x^2 + 1 \tag{4.4}$$

with  $\alpha = 0$  or  $\alpha = 1$ . The advantage provided by the Koblitz curves is that the DOUBLE operation in Algorithm 7 can be replaced with a second operation, namely

Algorithm 8 Generation of Binary NAF [31] Input: Positive integer k Output: k' = NAF(k)  $i \leftarrow 0$ ; while (k > 0) do if  $(k \equiv 1 \pmod{2})$  then  $k'_i \leftarrow 2 - (k \mod{4})$ ;  $k \leftarrow k - k'_i$ ; else  $k'_i \leftarrow 0$ ;  $k \leftarrow k/2$ ;  $i \leftarrow i + 1$ ;

Frobenius mapping, which is easier to perform.

If point (x, y) is on a Koblitz curve then it can be easily checked that  $(x^2, y^2)$ is also on the same curve. Moreover, these two points are related by the following Frobenius mapping

$$\tau(x,y) = (x^2, y^2)$$

where  $\tau$  satisfies the quadratic equation

$$\tau^2 + 2 = \mu\tau. \tag{4.5}$$

In (4.5),  $\mu = (-1)^{1-\alpha}$  and  $\alpha$  is the curve parameter in (4.4) and is 0 or 1 for the Koblitz curves.

The integer k can be represented with radix  $\tau$  using signed representation. In this

case, the expansion is written

$$k = \kappa_{l-1}\tau^{l-1} + \cdots + \kappa_1\tau + \kappa_0,$$

where  $\kappa_i \in \{0, 1, \overline{1}\}$ . Using this representation, Algorithm 7 can be rewritten, replacing the DOUBLE(Q) operation with  $\tau Q$  or a Frobenius mapping of Q. The modified algorithm is shown in Algorithm 9. Since  $\tau Q$  is computed by squaring the coordinates of Q, this suggests a possible speed up over the DOUBLE and ADD method.

Algorithm 9 Scalar Multiplication for  $\tau$ -adic IntegersInput: Integer  $k = (\kappa_{l-1}, \kappa_{l-2}, \ldots, \kappa_1, \kappa_0)_{\tau}$ , Point POutput: Point Q = kP $Q \leftarrow \mathcal{O};$ if  $(\kappa_{l-1} \neq 0)$  then $Q \leftarrow \kappa_{l-1}P;$ for i = l - 2 downto 0 do $Q \leftarrow \tau Q;$ if  $(\kappa_i \neq 0)$  then $Q \leftarrow ADD(Q, \kappa_i P);$

This complex representation of the integer can be improved further by computing its non-adjacent form. Solinas proved the existence of such a representation in [31] by providing an algorithm which computes the  $\tau$ -adic non-adjacent form or  $\tau$ -NAF of an integer. This algorithm is provided here in Algorithm 10. In most cases, the input to Algorithm 10 will be a binary integer, say k (i.e.  $r_0 = k$  and  $r_1 = 0$ ). If k has length l then TNAF(k) will have length 2l, roughly twice the length of NAF(k). Algorithm 10 Generation of  $\tau$ -adic NAF [31] Input:  $r_0 + r_1 \tau$  where  $r_0, r_1 \in \mathbb{Z}$ Output:  $u = \text{TNAF}(r_0 + r_1 \tau)$   $i \leftarrow 0$ ; while  $(r_0 \neq 0 \text{ or } r_1 \neq 0)$  do if  $(r_0 \equiv 1 \pmod{2})$  then  $u_i \leftarrow 2 - (r_0 - 2r_1 \mod{4});$   $r_0 \leftarrow r_0 - u_i;$ else  $u_i \leftarrow 0;$   $t \leftarrow r_0;$   $r_0 \leftarrow r_1 + \mu r_0/2;$   $r_1 \leftarrow -t/2;$  $i \leftarrow i + 1;$  The length of the representation generated by Algorithm 10 can be reduced by either preprocessing the integer k, as is done in [31], or by post processing the result. A method for post processing the output of Algorithm 10 is presented here.

Remember that  $\tau(x,y) = (x^2,y^2)$ . Since  $z^{2^m} = z$  for all  $z \in GF(2^m)$ , it follows that

$$\tau^m(x,y) = (x^{2^m}, y^{2^m}) = (x,y).$$

This relation gives us the general equality

$$(\tau^m - 1)P \equiv 0$$

where P is a point on a Koblitz curve. As a result, any integer k expressed with radix  $\tau$  can be reduced modulo  $\tau^m - 1$  without changing the scalar multiple kP. This reduction is performed easily with a few polynomial additions. Consider the  $\tau$ -adic integer

$$u = u_{2m-1}\tau^{2m-1} + \dots + u_{m+1}\tau^{m+1} + u_m\tau^m + u_{m-1}\tau^{m-1} + \dots + u_1\tau + u_0.$$

Factoring out  $\tau^m$  wherever possible, the result is

$$u = (u_{2m-1}\tau^{m-1} + \dots + u_{m+1}\tau + u_m)\tau^m + (u_{m-1}\tau^{m-1} + \dots + u_1\tau + u_0)$$

Substituting  $\tau^m$  with 1 and combining terms results in

$$u = ((u_{2m-1} + u_{m-1})\tau^{m-1} + \dots + (u_{m+1} + u_1)\tau + (u_m + u_0).$$

The output of Algorithm 10 is approximately twice the length of the input but may be slightly larger. Assuming the length of the input to be approximately m symbols, the reduction method must be capable of reducing  $\tau$ -adic integers with length slightly greater 2m. Algorithm 11 describes this method for reduction.

Algorithm 11 Reduction mod  $\tau^m$ Input:  $u = u_{l-1}\tau^{l-1} + \dots + u_1\tau + u_0$  with  $m \le l < 3m$ Output: v = REDUCE-TM(u)  $v \leftarrow 0;$ if (l > 2m) then  $v \leftarrow (u_{l-1}\tau^{l-2m-1} + \dots + u_{2m+1}\tau + u_{2m});$ if (l > m) then  $v \leftarrow v + (u_{2m-1}\tau^{m-1} + \dots + u_{m+1}\tau + u_m);$  $v \leftarrow v + (u_{m-1}\tau^{m-1} + \dots + u_1\tau + u_0);$

Now the result of Algorithm 11 has length m but is no longer in  $\tau$ -adic NAF form. There may be adjacent non-zero symbols and the symbols are not restricted to the set  $\{0, 1, \overline{1}\}$ .

The input of Algorithm 10 is of the form  $r_0 + r_1 \tau$  where  $r_0, r_1 \in \mathbb{Z}$ . The output is

the  $\tau$ -adic representation of the input. For  $v \in \mathbb{Z}[\tau]$  we can write

$$v = v_{m-1}\tau^{m-1} + \dots + v_2\tau^2 + v_1\tau + v_0$$

=  $v_{m-1}\tau^{m-1} + \dots + v_2\tau^2 + \text{TNAF}(v_1\tau + v_0)$

Now the two least significant symbols of v are in  $\tau$ -adic NAF. Repeating this procedure for every bit in v the entire string can be converted to  $\tau$ -adic NAF. This process is described in Algorithm 12.

Algorithm 12 Regeneration of  $\tau$ -adic NAFInput:  $v = v_{m-1}\tau^{m-1} + \dots + v_1\tau + v_0$ Output:  $w = \text{REGEN_TNAF}(v)$  $w \leftarrow v$ ; $i \leftarrow 0$ ;while  $(w_j \neq 0 \text{ for some } j \ge i)$  doif  $(w_i == 0)$  then $i \leftarrow i + 1$ ;else $t_0 \leftarrow w_i$ ; $t_1 \leftarrow w_{i+1}$ ; $w_i \leftarrow 0$ ; $w_{i+1} \leftarrow 0$ ; $w \leftarrow w + \text{TNAF}(t_1\tau + t_0)$ ; $i \leftarrow i + 1$ ;

The output of Algorithm 12 is in  $\tau$ -adic NAF and has a length of approximately m symbols. If the result is larger than m symbols, it is possible to repeat Algorithms 11

and 12 to further reduce the length. Algorithms 10, 11 and 12 have been implemented in C and were used to generate test vectors for the prototype discussed later in this chapter. During testing, it was found that a single pass of these algorithms generates a  $\tau$ -adic representation with average length of m and a maximum length of  $m + 5^1$ .

Like radix 2 NAF the  $\tau$ -adic NAF uses the symbol set  $\{1, 0, \overline{1}\}$  and has an average Hamming weight of approximately l/3 for an l-bit integer [31]. So Algorithm 9 has a running time of l/3 point additions and l - 1 Frobenius mappings.

#### 4.2.3 Summary and Analysis

A point addition using López & Dahab's projective coordinates requires ten field multiplications, four field squarings and eight field additions. A point double requires five field multiplications, five field squarings and four field additions. Using this information, the run time for scalar multiplication can be written in terms of field operations. Typically scalar multiplication is measured in terms of field multiplications, inversions and squarings, ignoring the cost of addition. In the case of this architecture, field multiplication and squaring are completed quickly enough that the cost of field addition becomes significant. The run times using binary, binary NAF and  $\tau$ -adic NAF representations are shown in Table 4.2. These values are based on the curve addition and doubling equations defined in (4.2) and (4.3) assuming arbitrary curve parameters  $\alpha$  and  $\beta$  and the average Hamming weights discussed in the previous sections. For the case of  $\tau$ -NAF, a Frobenius mapping is assumed to require three squaring operations. The symbols  $\mathcal{M}$ ,  $\mathcal{S}$ ,  $\mathcal{A}$  and  $\mathcal{I}$  correspond to field multiplication, squaring, addition and inversion respectively. In each case it is assumed that the length of the

<sup>&</sup>lt;sup>1</sup>These are empirical rather than analytical results.

integer is approximately equal to m.

|             | Generic $m$                                                                                         | m = 163                                                             |

|-------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|