# Image Sensor Pixel Integration for Large Area Imaging

by

## Byung-kyu Park

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2001

© Byung-kyu Park 2001

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre rélérence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-65254-8

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### **Abstract**

This thesis examines the various issues underlying integration of Mo/a-Si:H image sensor with inverted-staggered thin film transistor (TFT) for large area digital x-ray imaging applications.

The thin film transistor process has been modified to include a highly doped ( $n^+$ ) microcrystalline silicon ( $\mu$ c-Si:H) film as the contact layer in the source and drain regions. The deposition temperature of the  $n^+$   $\mu$ c-Si:H film is varied from 200°C to 400°C to observe the crystalline and amorphous phase formations in these films. The results show that the films deposited at low temperatures are more crystalline in nature than their high temperature counterparts.

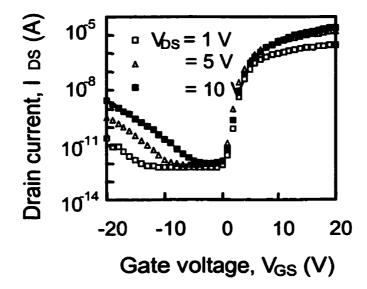

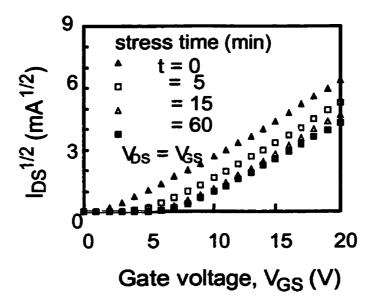

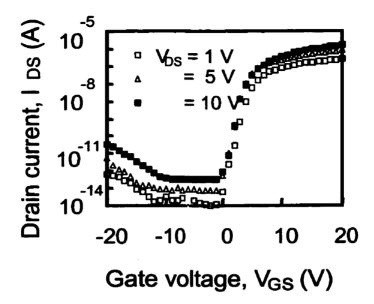

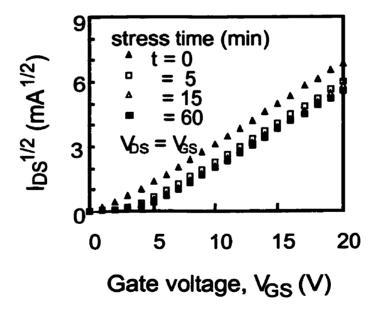

A comparison of the performance of aluminium (Al)-gated thin film transistors is presented in which the process parameters are varied in terms of the sputter deposition temperature, process pressure, and power. Gate films deposited at  $30^{\circ}\text{C/5mTorr/300W}$  yield TFT characteristics with low leakage current (~ 10 fA at low  $V_{DS}$ ), an ON/OFF ratio better than  $10^{8}$ , and a mobility of  $1.1 \text{ cm}^{2}/\text{Vs}$ . In contrast, films deposited at  $150^{\circ}\text{C/10mTorr/400W}$ , yield a significant degradation in leakage current (~ 1 pA) and mobility (0.77 cm<sup>2</sup>/Vs). The degradation stems from the high surface roughness of the a-SiN:H gate insulator, and hence the TFT channel.

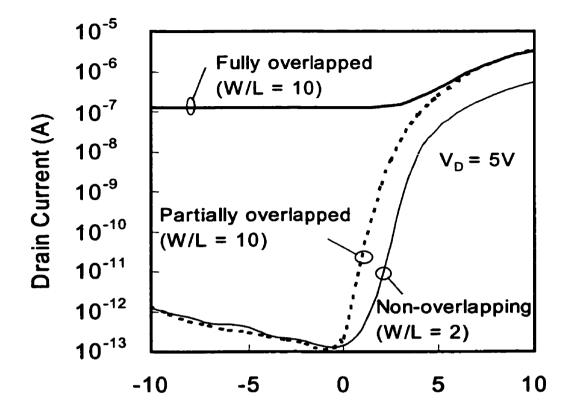

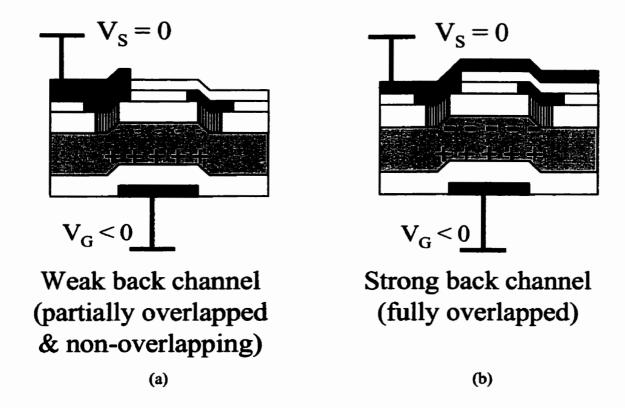

Two different pixel integration processes for direct x-ray detection are studied. In one process, the Schottky diode is stacked on top of the TFT. In the other process, the two devices did not overlap. The two processes are compared in terms of mask count and pixel performance. Fully-overlapped and partially-overlapped pixel structures provide high fill factor, but suffer from the stresses due to multi-layers. In addition, the TFT leakage current of a fully-overlapped pixel is very high (~10<sup>-7</sup> A), due to parasitic capacitance. The partially-overlapped structure also suffers from high stress, however.

the leakage current is considerably lower and comparable to that of a discrete TFT. The stress is not as severe in the non-overlapping structures. Also, the leakage current is of the order of 100fA.

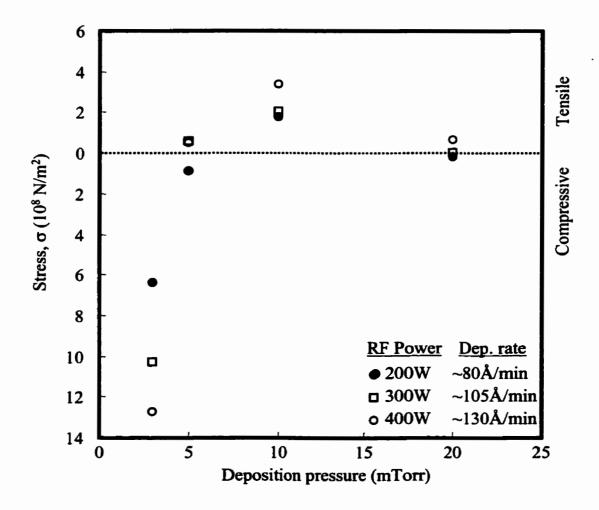

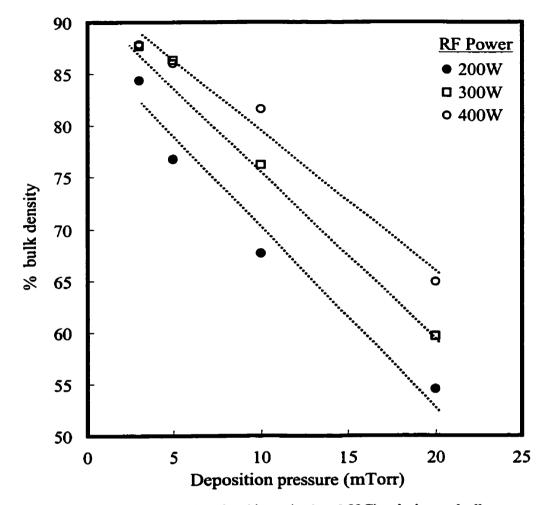

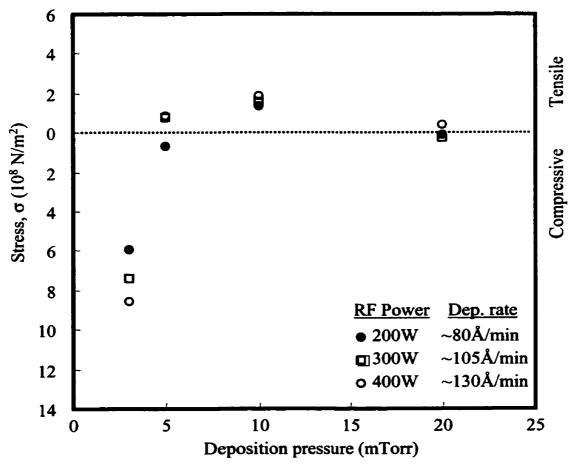

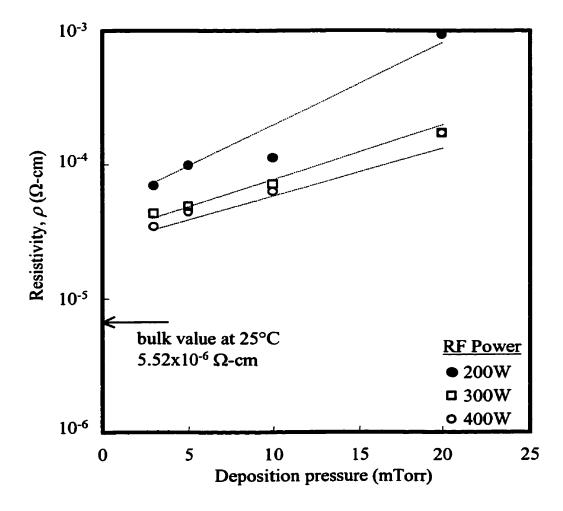

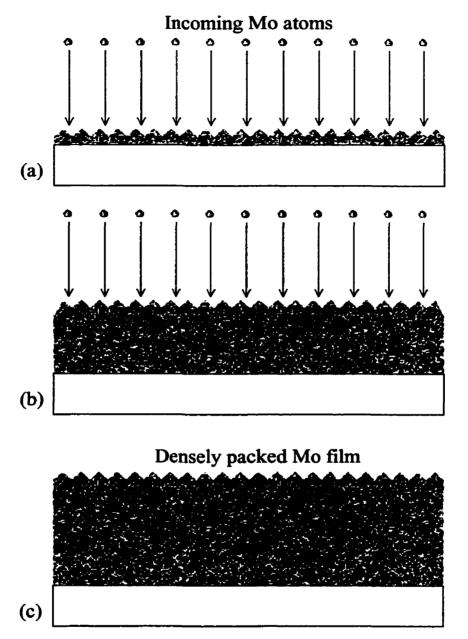

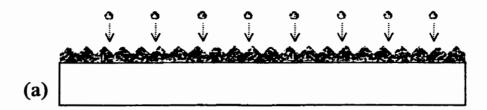

The high intrinsic film stress associated with the stacked pixel structures has been further investigated. It is shown that the high compressive stress of Mo film ( $\sim 10^9$  Pa) can be reduced to  $\sim 10^7$  Pa by varying the deposition process parameters without seriously undermining the physical and electrical properties of the films.

A small-scale (4 rows x 5 columns) teat array has been designed and characterized. The results show that several technical challenges need to first be solved before extending the design to a larger array for x-ray image generation. The most outstanding challenge is to improve the uniformity of the Schottky diode interface.

## Acknowledgements

I thank God for giving me strength to finish this work.

I would like to express my deep gratitude to my parents for their continuous support and encouragement. For four long years, they have been my greatest sponsors and motivators. I am very grateful to my wife, Soo-jung, who put up with all the late nights, working holidays and weekends, and the weeks I was away for research conferences. My greatest source of inspiration has been Rebecca, my daughter, who accepted her father to be unavailable at times.

Most of my hands-on knowledge of the fabrication processes was inherited from Dr. Murthy Rambhatla. Without him, I couldn't have finished my work in four years. I thank all my friends for being there for me. My special thanks to Isaac Chan, who kept me awake in my office with loud audio sound effects late at night. I am sorry that I couldn't spend more time with new members in our group, Czang-ho Lee. Joe Street, Tracy Zhou and Dr. Go-young Moon. I thank Prof. Andrei Sazonov, Dr. Denis Striakhilev, Sheng Tao, and Roger Grant for numerous inspiring discussions.

Finally, I would like to express my special thanks to my supervisor. Professor Arokia Nathan, for his technical support, guidance, and encouragement. I am honoured to have Professor William I. Milne, head of the electronic devices and materials group. Department of Engineering, University of Cambridge, as my external examiner.

# **Contents**

| l | Intr | roduction |                                            |    |

|---|------|-----------|--------------------------------------------|----|

|   | 1.1  | Backgro   | ound History of Amorphous Silicon          | 1  |

|   | 1.2  | Motivat   | ions                                       | 2  |

|   | 1.3  | Advanta   | ges of a-Si:H Technology                   | 3  |

|   | 1.4  | X-Ray [   | Detection Schemes                          | 4  |

|   |      | 1.4.1     | Indirect Detection Scheme                  | 4  |

|   |      | 1.4.2     | Direct Detection Scheme                    | 6  |

|   |      | 1.4.3     | Detection Scheme of This Study             | 8  |

|   |      | 1.4.4     | Comparisons of Different Detection Schemes | 11 |

|   | 1.5  | Thin Fil  | m Deposition                               | 11 |

|   |      | 1.5.1     | Plasma Enhanced Chemical Vapor Deposition  | 15 |

|   |      | 1.5.2     | Sputter Deposition                         | 19 |

|   |      | 1.5.3     | Film Deposition in Vacuum                  | 20 |

|   | 1.6  | Overvie              | w of the Thesis                                                 | 22 |

|---|------|----------------------|-----------------------------------------------------------------|----|

| 2 | Thir | ı Film Tı            | ransistors (TFTs)                                               | 23 |

|   | 2.1  | TFT Op               | eration                                                         | 23 |

|   | 2.2  | TFT Fat              | prication                                                       | 27 |

|   | 2.3  | Low-Te               | mperature. Low-Resistivity Highly Doped Microcystalline Silicon |    |

|   |      | (n <sup>+</sup> μc-S | i:H)                                                            | 29 |

|   |      | 2.3.1                | Motivation for Studying n <sup>+</sup> μc-Si:H                  | 30 |

|   |      | 2.3.2                | Crystallinity Shown by GIXD                                     | 31 |

|   |      | 2.3.3                | Crystallinity Shown by Raman Spectroscopy                       | 33 |

|   |      | 2.3.4                | Hydrogent Content (FTIR)                                        | 34 |

|   |      | 2.3.5                | Resistivity                                                     | 36 |

|   |      | 2.3.6                | Optical Band Gap                                                | 37 |

|   |      | 2.3.7                | Crystallization at Low Temperature                              | 38 |

|   |      | 2.3.8                | TFT Performance Improvement                                     | 47 |

|   | 2.4  | Aluminu              | ım Gate Metallization                                           | 50 |

|   |      | 2.4.1                | TFT Gate Metals (Mo, Cr, Cu or Al)                              | 50 |

|   |      | 2.4.2                | Motivation for Studying Aluminum Gate TFT                       | 51 |

|   |      | 2.4.3                | Surface SEM                                                     | 52 |

|   |      | 2.4.4                | Intrinsic Film Stress                                           | 56 |

|   |      | 245                  | Surface Roughness                                               | 57 |

|   |      | 2.4.6    | Gate/Gate Dielectric Interface (Cross-Section SEM) | 59  |

|---|------|----------|----------------------------------------------------|-----|

|   |      | 2.4.7    | TFT Performance Comparisons                        | 64  |

| 3 | Leal | kage Cur | rent of Mo/a-Si:H Schottky Diodes                  | 69  |

|   | 3.1  | Large V  | ariation in Schottky Interface I-V Characteristics | 69  |

|   | 3.2  | Modifie  | d Schottky Diode Fabrication Process               | 73  |

|   | 3.3  | Scaling  | the Device Size                                    | 77  |

|   | 3.4  | Transpo  | rt Mechanisms across Mo/a-Si:H Schottky Barrier    | 81  |

| 4 | X-R  | ay Pixel | Integration                                        | 88  |

|   | 4.1  | Pixel De | esign Considerations                               | 88  |

|   |      | 4.1.1    | Pixel Size: Dimensions                             | 88  |

|   |      | 4.1.2    | Fill Factor                                        | 89  |

|   | 4.2  | Pixel Fa | brication Processes                                | 90  |

|   |      | 4.2.1    | Process I: Stacked Pixels                          | 90  |

|   |      | 4.2.2    | Process II: Non-Overlapping Pixels                 | 94  |

|   | 4.3  | Process  | Considerations                                     | 97  |

|   |      | 4.3.1    | Mask Count and Process Steps                       | 97  |

|   |      | 4.3.2    | Other Fabrication Issues                           | 98  |

|   |      | 4.3.3    | Intrinsic Film Stress                              | 101 |

|   | 4.4  | Performa | ance Considerations                                | 101 |

|   |      | 441      | Leakage Current                                    | 101 |

|   |      | 4.4.2      | X-Ray Response                                     | 103 |

|---|------|------------|----------------------------------------------------|-----|

| 5 | Intr | insic Filn | n Stress                                           | 110 |

|   | 5.1  | Motivati   | on for Studying Mechanical Film Stress             | 110 |

|   | 5.2  | Breakdo    | wn of Film Stress                                  | 112 |

|   |      | 5.2.1      | Total Stress, σ <sub>totall</sub>                  | 112 |

|   |      | 5.2.2      | External Stress. $\sigma_{external}$               | 113 |

|   |      | 5.2.3      | Thermal Stress, $\sigma_{thermal}$                 | 120 |

|   |      | 5.2.4      | Intrinsic Stress, $\sigma_{intrinsic}$             | 121 |

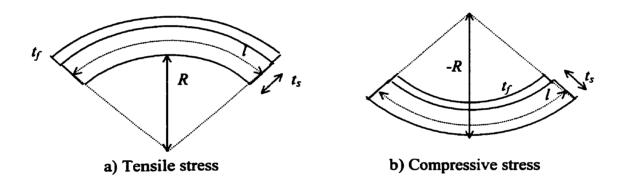

|   | 5.3  | Stress M   | easurement Setup                                   | 122 |

|   |      | 5.3.1      | Wafer Bow Measurements                             | 122 |

|   |      | 5.3.2      | Shadow Masks                                       | 125 |

|   | 5.4  | Stress M   | easurement Results                                 | 127 |

|   |      | 5.4.1      | Intrinsic Film Stress on Glass Substrate           | 127 |

|   |      | 5.4.2      | Intrinsic Film Stress in Thin Film Transistors     | 128 |

|   |      | 5.4.3      | Intrinsic Film Stress in Mo/a-Si:H Schottky diodes | 128 |

|   | 5.5  | Compres    | ssive or Tensile Intrinsic Stress of Mo Films      | 133 |

|   |      | 5.5.1      | At Low Deposition Pressure                         | 133 |

|   |      | 5.5.2      | At High Deposition Pressure                        | 136 |

|   |      | 5.5.3      | At Medium Deposition Pressure                      | 136 |

|   | 5.6  | Chaosina   | the Process Pressure                               | 142 |

| 6 | Arra       | y Fabrication | 143 |  |  |

|---|------------|---------------|-----|--|--|

|   | 6.1        | Array Designs | 143 |  |  |

|   | 6.2        | Fabrication   | 146 |  |  |

|   | 6.3        | Testing       | 146 |  |  |

|   | 6.4        | Evaluation    | 151 |  |  |

| 7 | Con        | clusions      | 156 |  |  |

| A | ppeno      | dix A         | 159 |  |  |

| A | ppen       | dix B         | 166 |  |  |

| A | Appendix C |               |     |  |  |

| A | Appendix D |               |     |  |  |

| A | ppen       | dix E         | 169 |  |  |

| A | ppen       | dix F         | 172 |  |  |

| R | References |               |     |  |  |

# **List of Figures**

| 1.1 | Indirect x-ray detection method. based on combination of a phosphor layer and an a-Si:H image sensor                                                                                                                                                                        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | Pixel circuit schematic diagram of indirect x-ray detection array. Each pixel contains a p-i-n photodiode to capture the visible light emitted from the phosphor layer and a TFT to make the array gate-addressable.                                                        |

| 1.3 | Direct x-ray detection method using a thick vapor-deposited amorphous selenium layer.                                                                                                                                                                                       |

| 1.4 | Pixel circuit schematic diagram of direct x-ray detection array. Each pixel contains a storage capacitor to keep the charge generated by x-rays. The selenium layer is continuous over the entire detection area. The bias line is not shown in the simplified array layout |

| 1.5 | X-ray detection scheme based on Mo/a-Si:H Schottky diode9                                                                                                                                                                                                                   |

| 1.6 | Direct detection x-ray imaging pixel based on a-Si:H/Mo Schottky diode as a detector. (a) Circuit schematic diagram. (b) Equivalent circuit diagram.                                                                                                                        |

| 1.7 | Surface coverage of tin film processes (a) CVD process. (b) PVD process15                                                                                                                                                                                                   |

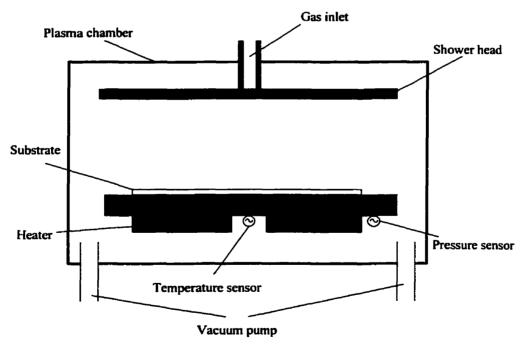

| 1.8  | PlasmaTherm VII parallel plates PECVD system for thin film depositions                                                                                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.9  | A simplified cross section view of the PECVD chamber. Only the most vital components are shown                                                                                                     |

| 1.10 | Edwards magnetron DC/RF sputtering system for thin metal depositions                                                                                                                               |

| 1.11 | A simplified cross sectional view of the Edward sputtering system. Only the most vital components are shown                                                                                        |

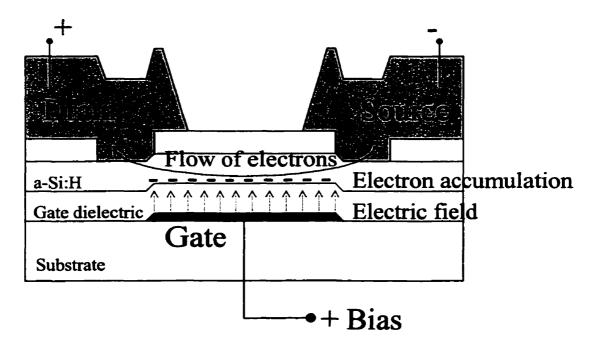

| 2.1  | Inverted-staggered a-Si:H TFT. When the gate positively biased, an electron channel is induced at the gate dielectric/intrinsic silicon interface providing a conduction path from drain to source |

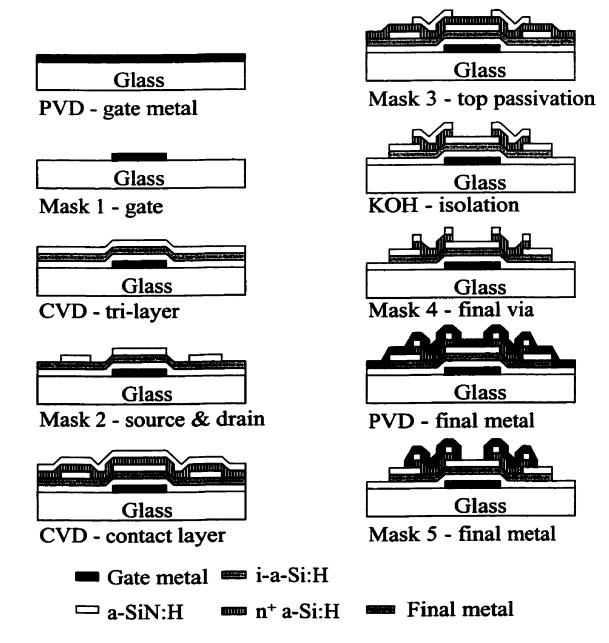

| 2.2  | Fabrication sequence of thin film transistor in inverted staggered structure deposited on Corning 7050 glass substrate                                                                             |

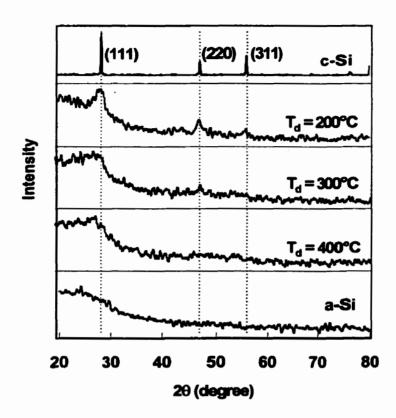

| 2.3  | X-ray diffraction patterns for $n^+$ $\mu$ C-Si:H films deposited at 200°C, 300°C and 400°C32                                                                                                      |

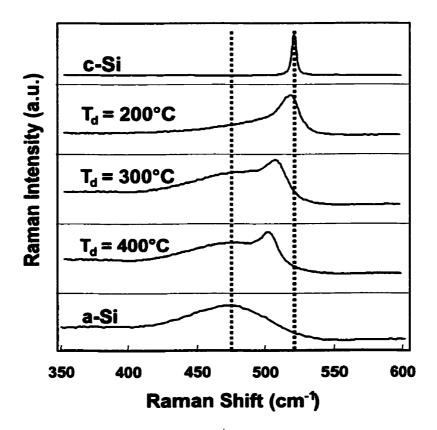

| 2.4  | Raman spectra for n <sup>+</sup> μc-Si:H films deposited at 200°C, 300°C and 400°C34                                                                                                               |

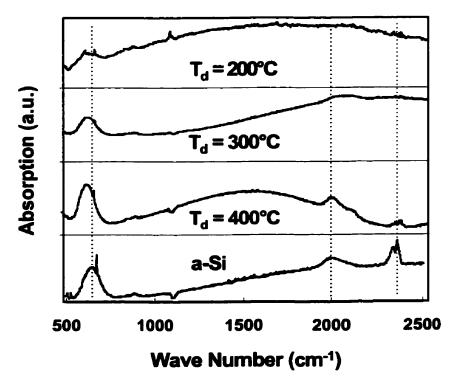

| 2.5  | Infrared spectra for $n^+$ $\mu c\text{-Si:H}$ films deposited at 200°C, 300°C and 400°C35                                                                                                         |

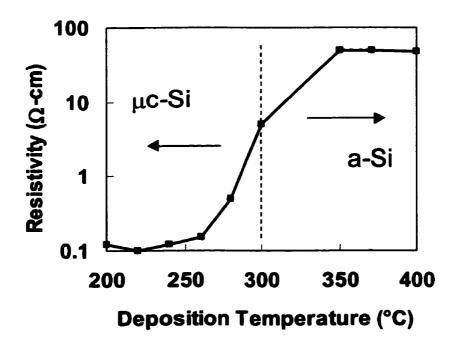

| 2.6  | Resistivity of $n^+$ $\mu$ c-Si:H films as a function of the deposition temperature36                                                                                                              |

| 2.7  | Optical band gap of $n^+$ $\mu c\text{-Si:H}$ films as a function of the deposition temperature37                                                                                                  |

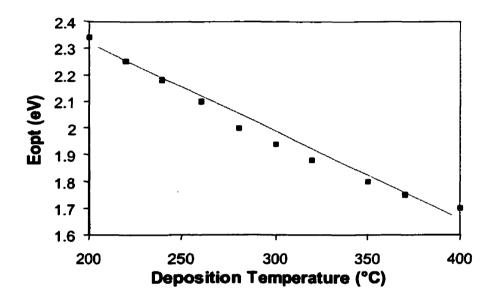

| 2 B  | The three layer model of microcrystalline film growth                                                                                                                                              |

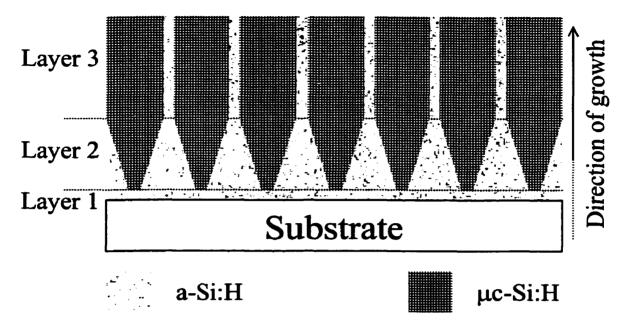

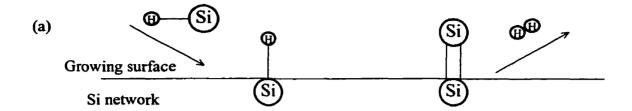

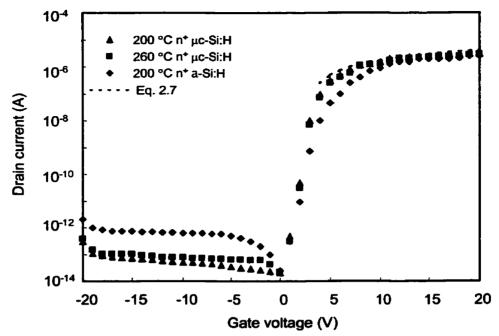

| 2.9  | The etching mechanisms of hydrogen atoms in the microcrystalline growth                                                                  |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | process. (a) Etching of unstable and strained Si-Si bond. (b) Etching of a                                                               |    |

|      | stable and strong Si-Si bond                                                                                                             | 44 |

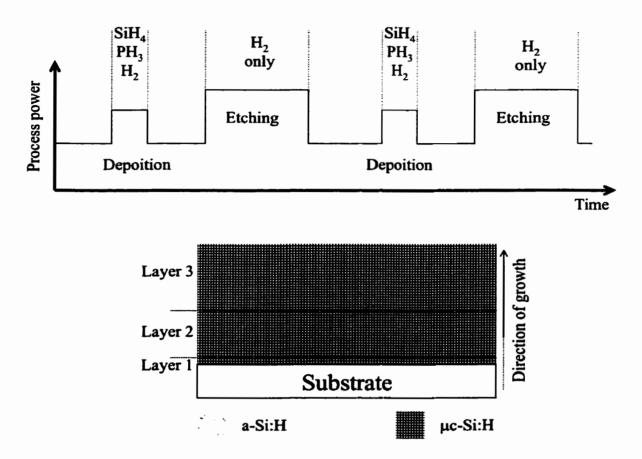

| 2.10 | Layer-by-layer deposition of microcrystalline films. The process is repeated between deposition cycle and etching cycle. The result is a |    |

|      | microcrystalline film from the very initial layer                                                                                        | 45 |

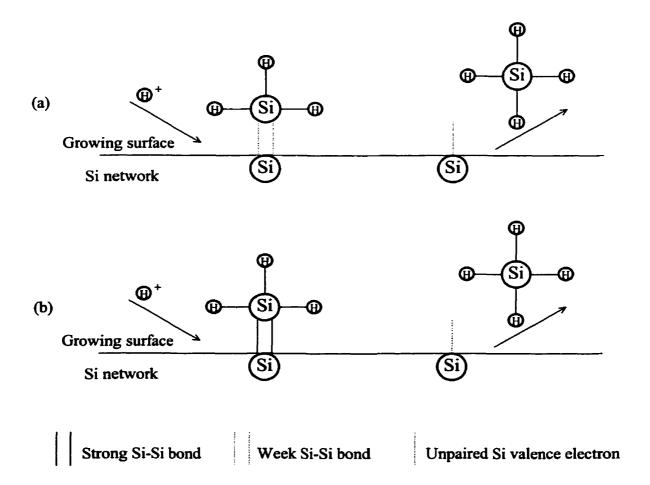

| 2.11 | The deposition mechanisms in the growth of microcrystalline silicon films.                                                               |    |

|      | (a) An inception of a silane radical which leads to a strong and stable Si-Si                                                            |    |

|      | bond. (b) An inception of a silane radical which leads to an unstable and                                                                |    |

|      | strained Si-Si bond.                                                                                                                     | 46 |

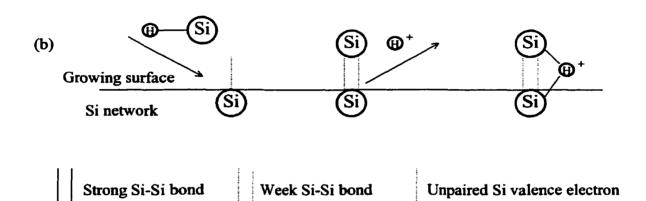

| 2.12 | Transfer characteristics of TFTs fabricated with 200°C n <sup>+</sup> μc-Si:H, 260°C                                                     |    |

|      | n <sup>+</sup> μc-Si:H and 260°C n <sup>+</sup> a-Si:H films as contact layers                                                           | 49 |

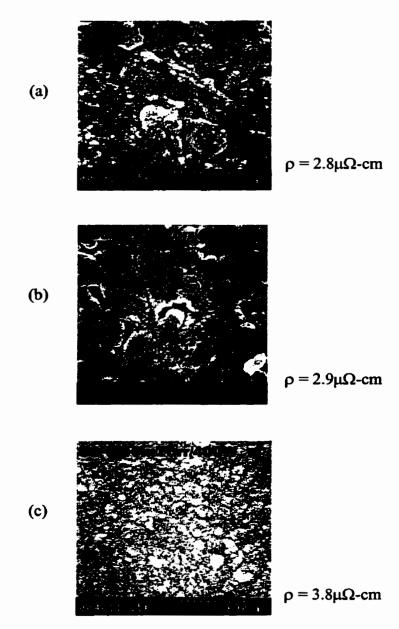

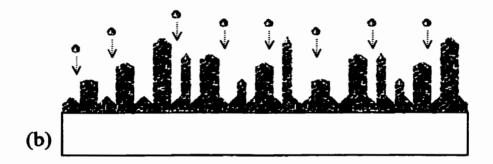

| 2.13 | SEM micrographs of the Al films deposited at (a) 150°C. (b) 100°C. and                                                                   |    |

|      | (c) 30°C, and subject to thermal annealing at 260°C for 12 hours. The                                                                    |    |

|      | process pressure and power were fixed at 10mTorr and 400W,                                                                               |    |

|      | respectively                                                                                                                             | 53 |

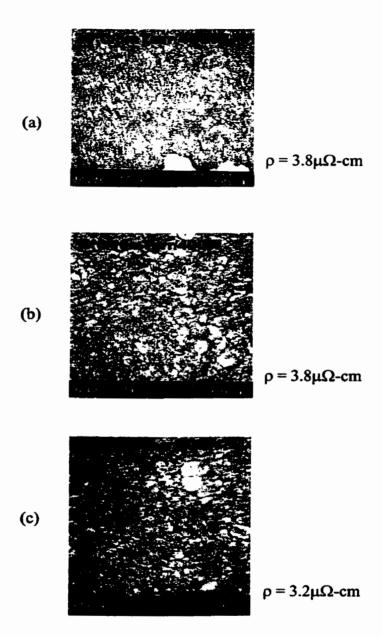

| 2.14 | SEM micrographs of the Al films deposited at (a) 5mTorr. (b) 10mTorr.                                                                    |    |

|      | and (c) 20mTorr, and subject to thermal annealing at 260°C for 12 hours.                                                                 |    |

|      | The deposition temperature and power were fixed at 30°C and 400W.                                                                        |    |

|      | respectively                                                                                                                             | 54 |

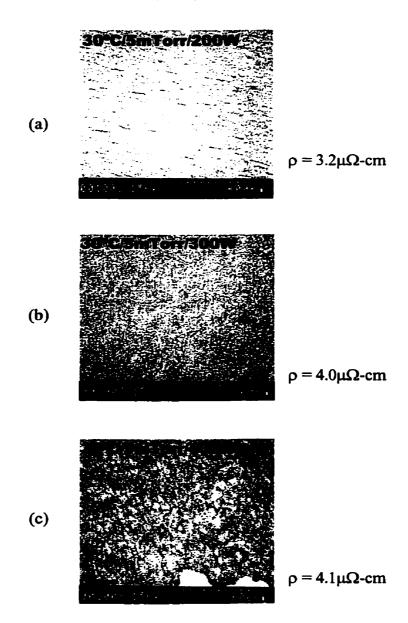

| 2.15 | SEM micrographs of the Al films deposited at (a) 200 W, (b) 300 W, and                                                                   |    |

|      | (c) 400 W, and subject to thermal annealing at 260°C for 12 hours. The                                                                   |    |

|      | process pressure and temperature were fixed at 5mTorr and 30°C.                                                                          |    |

|      | respectively                                                                                                                             | 55 |

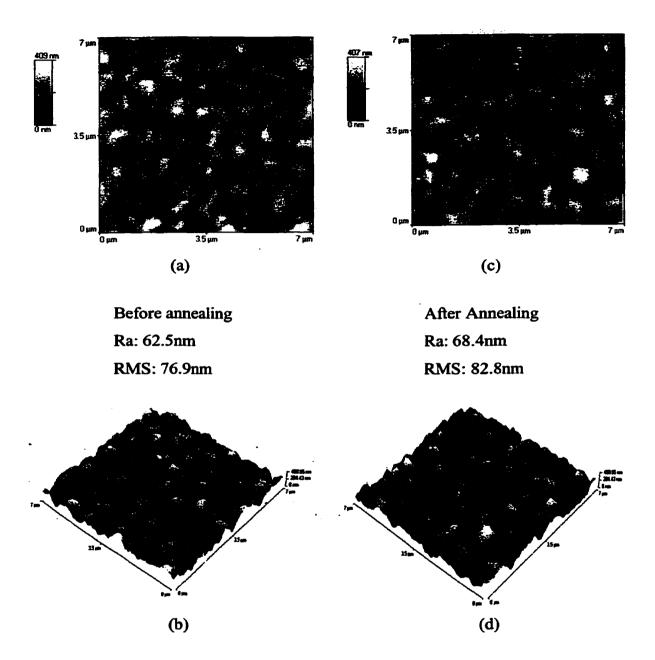

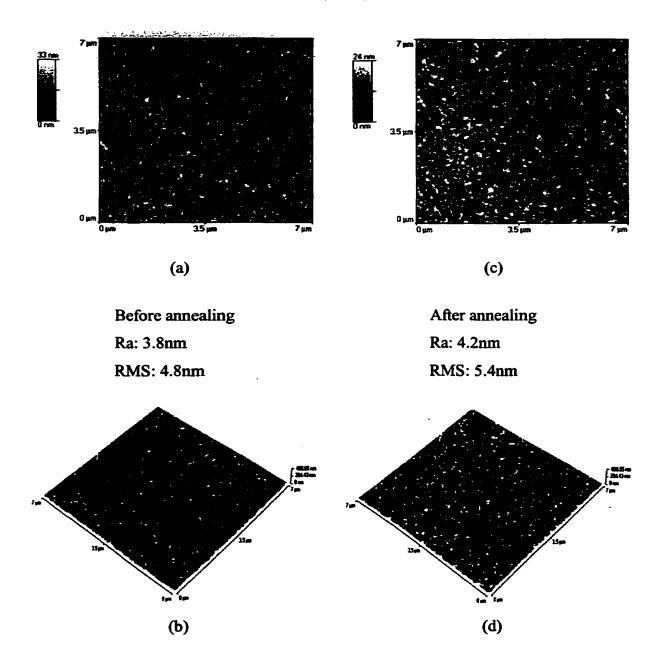

| 2.16 | AFM images of Al gate film deposited at 150°C, 10mTorr, and 400W - before annealing a) top view, b) 3-D view and after annealing at 260°C c)                      |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | top view, d) 3-D view                                                                                                                                             | 60 |

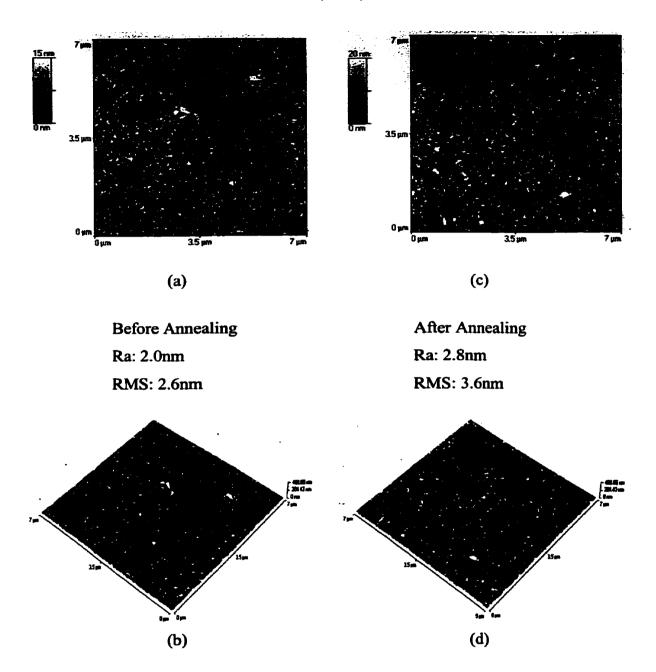

| 2.17 | AFM images of Al gate film deposited at 30°C, 5mTorr, and 400W - before annealing a) top view, b) 3-D view and after annealing at 260°C c) top view, d) 3-D view  | 61 |

| 2.18 | AFM images of Al gate film deposited at 30°C, 5mTorr, and 300W - before annealing a) top view, b) 3-D view and after annealing at 260°C c) top view, d) 3-D view. | 62 |

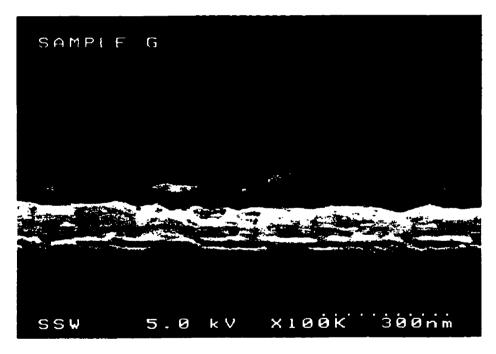

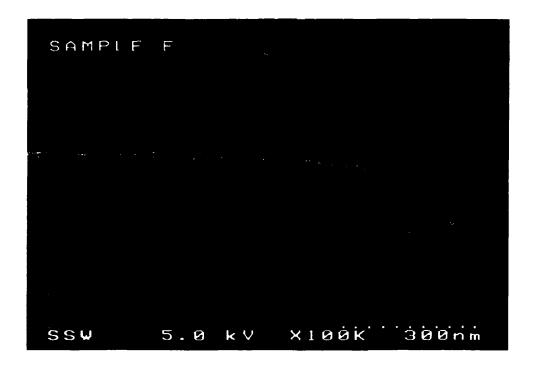

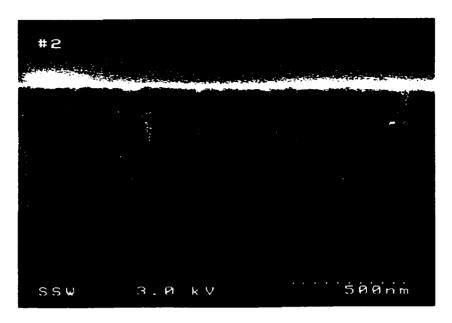

| 2.19 | Cross-section SEM image of Al gate and gate dielectric interface. Al gate metal was deposited at 150°C, 10mTorr and 400W                                          | 63 |

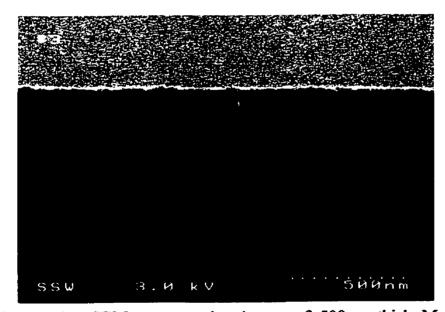

| 2.20 | Cross-section SEM image of Al gate and gate dielectric interface. Al gate metal was deposited at 30°C, 5mTorr and 300W                                            | 64 |

| 2.21 | Transfer characteristics of a TFT fabricated with Al gate metal in Fig. 2.19                                                                                      | 66 |

| 2.22 | Shift in threshold voltage of a TFT fabricated with Al gate metal in Fig. 2.19.                                                                                   | 66 |

| 2.23 | Transfer characteristics of a TFT fabricated with Al gate metal in Fig. 2.20                                                                                      | 67 |

| 2.24 | Shift in threshold voltage of a TFT fabricated with Al gate metal in Fig. 2.20.                                                                                   | 67 |

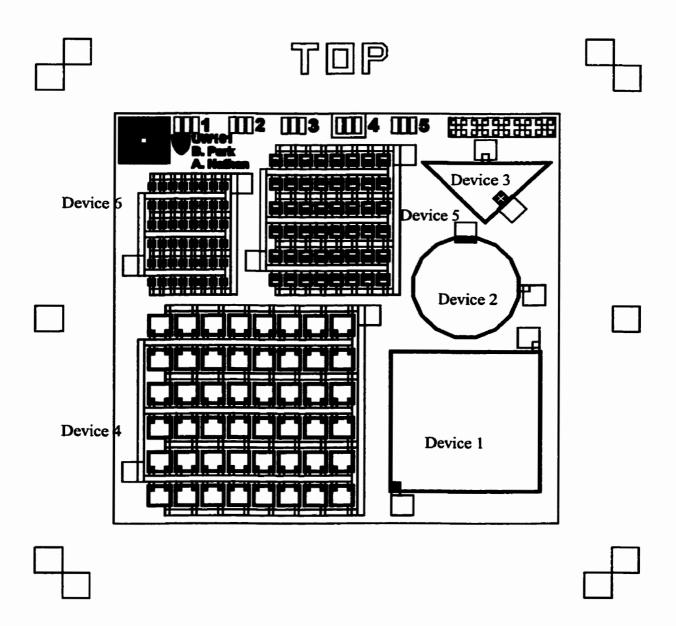

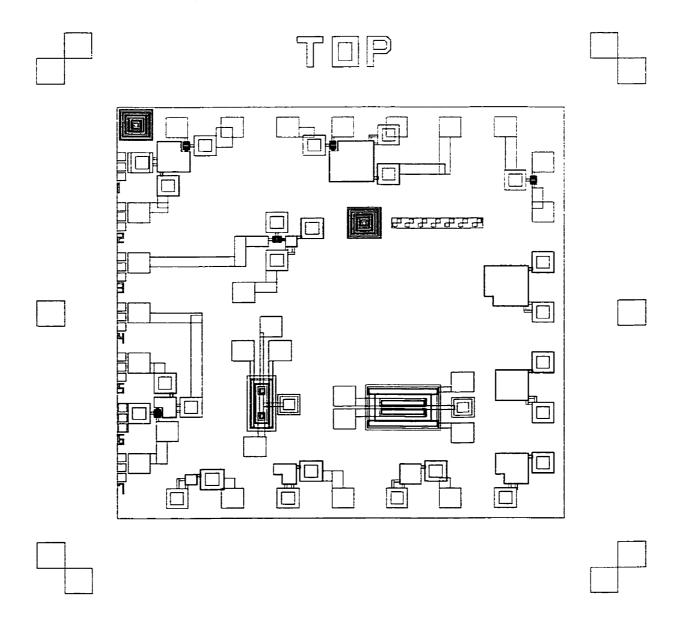

| 3.1  | A mask layout for Schottky diode leakage current studies.                                                                                                         | 70 |

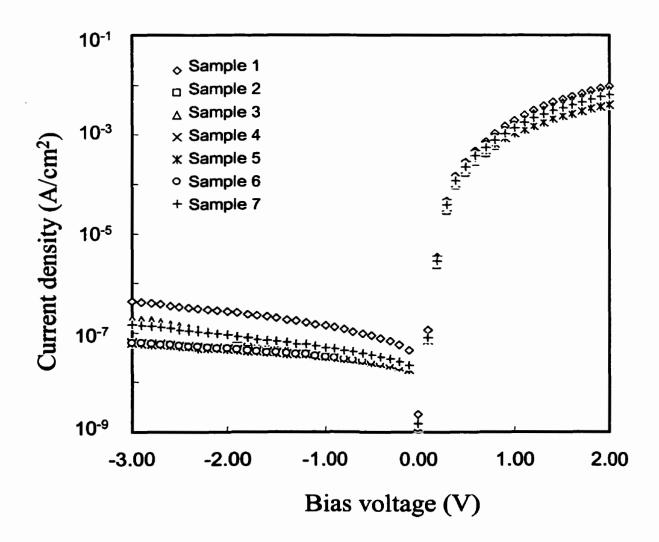

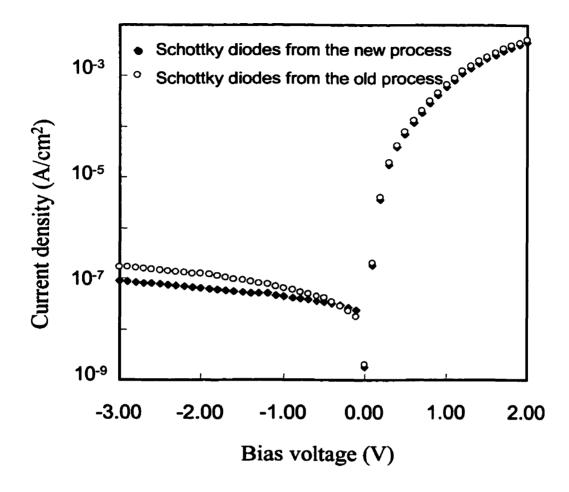

| 3.2  | Current density of device 1 (Schottky diode) in Fig. 3.1.                                                                                                         | 72 |

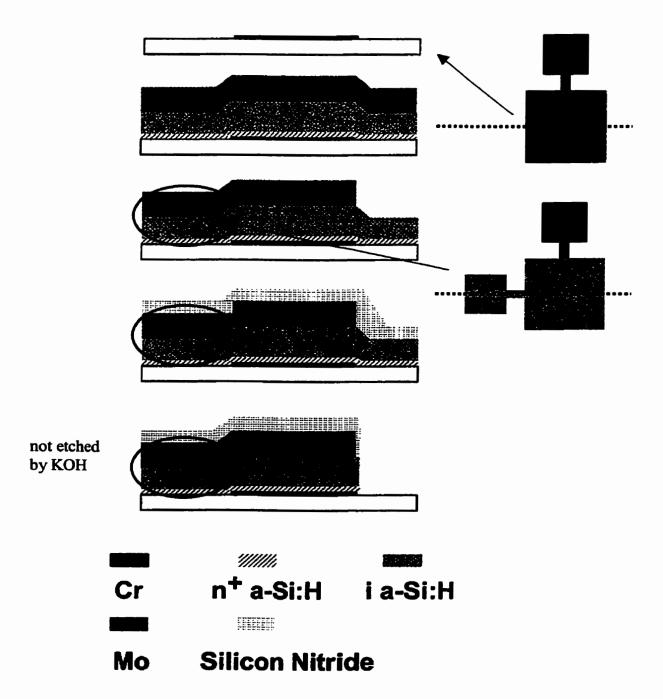

| 3.3  | Old fabrication sequence of mo/a-Si:H Schottky diodes, adapted from [33]                                                                                          | 74 |

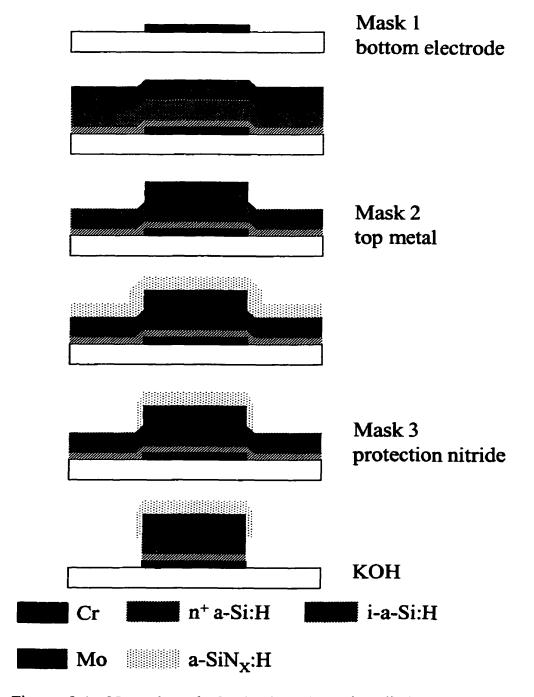

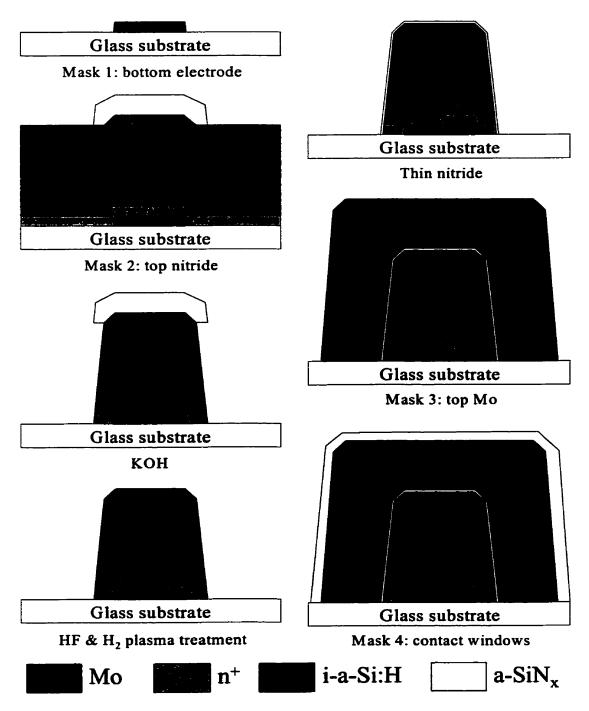

| 3.4  | New 5-mask Mo/a-Si:H Schottky diode fabrication sequence                                                                                                          | 75 |

| 3.5  | Comparison of the current density of Schottky diodes, fabricated with the                                                                                                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | old 4-mask process and the modified 5-mask process.                                                                                                                                                     | 76  |

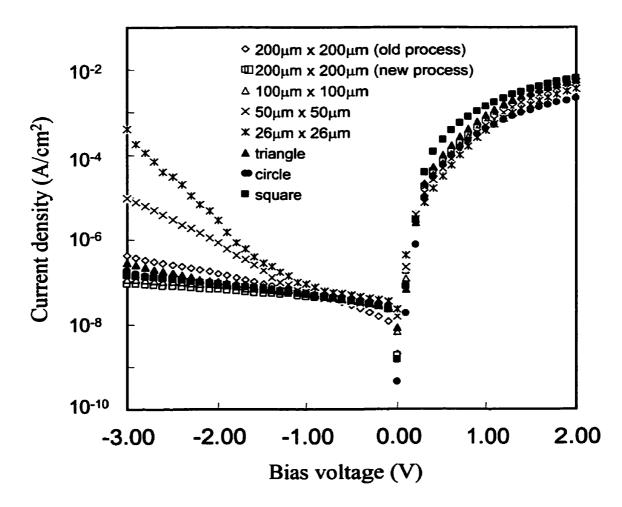

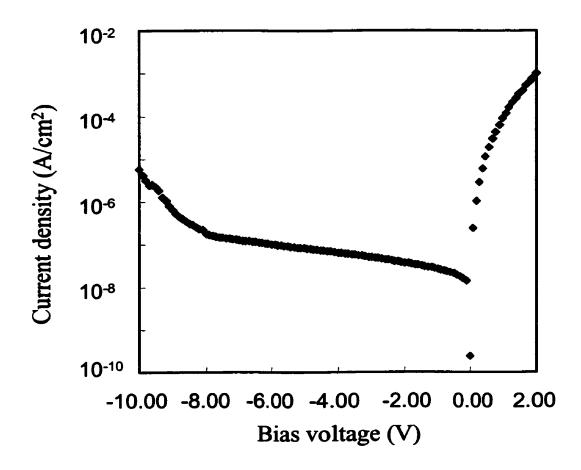

| 3.6  | Leakage current density of the Schottky diodes with different dimensions                                                                                                                                | 78  |

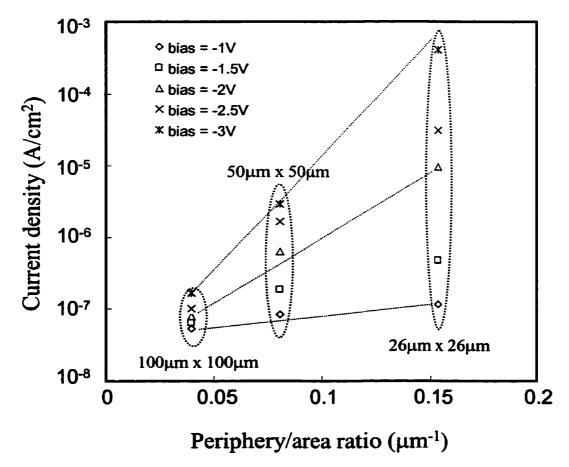

| 3.7  | Leakage current density as a function of periphery/area ratio (μm <sup>-1</sup> )                                                                                                                       | 79  |

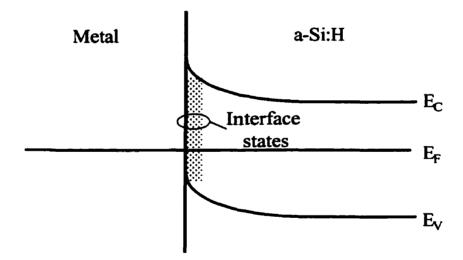

| 3.8  | Energy band diagram of Schottky interface. The interface states at the Schottky barrier are caused by abrupt termination of the silicon bonds. This is an intrinsic property of the Schottky interface. | 81  |

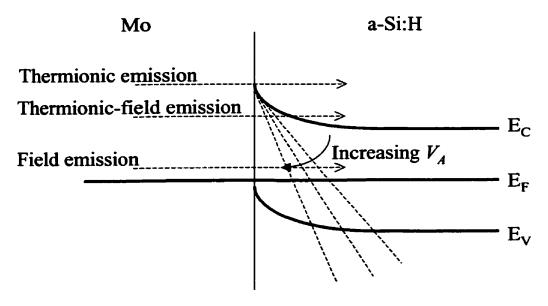

| 3.9  | Transport mechanisms across Mo/a-Si:H Schottky barrier                                                                                                                                                  |     |

| 3.10 | Leakage current density of 700µm x 700µm Schottky diode under high reverse bias.                                                                                                                        | 85  |

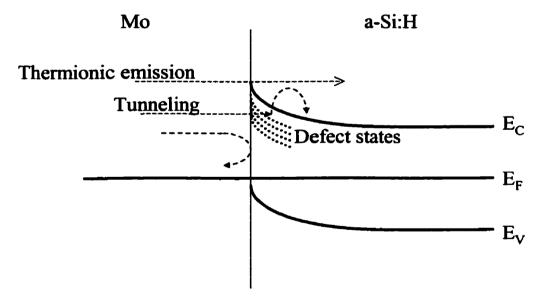

| 3.11 | Effect of defect states in the band gap on the leakage current conduction in Schottky diodes.                                                                                                           | 86  |

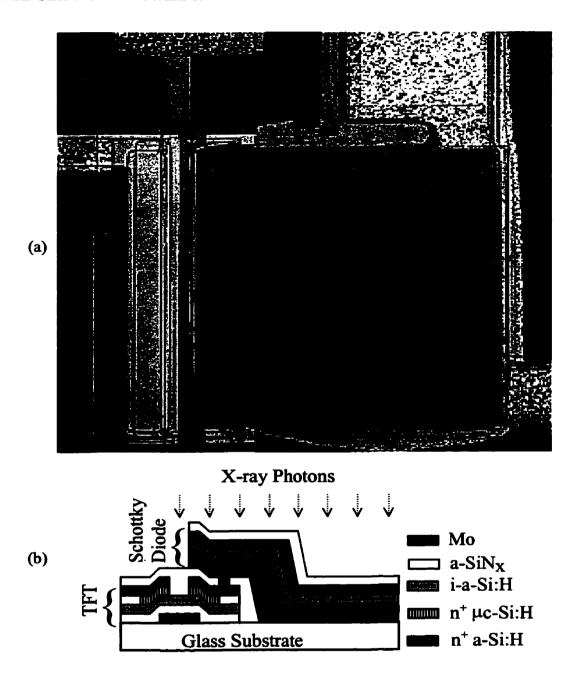

| 4.1  | Fully overlapped x-ray pixel; a) top view, b) cross-sectional view                                                                                                                                      | 91  |

| 4.2  | Partially overlapped x-ray pixel; a) top view, b) cross-sectional view                                                                                                                                  | 92  |

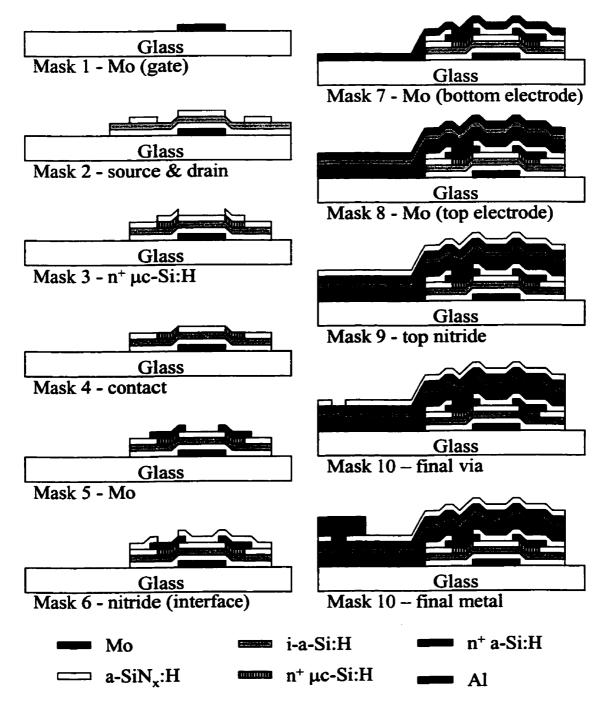

| 4.3  | Process sequence of stacked x-ray pixel                                                                                                                                                                 | 93  |

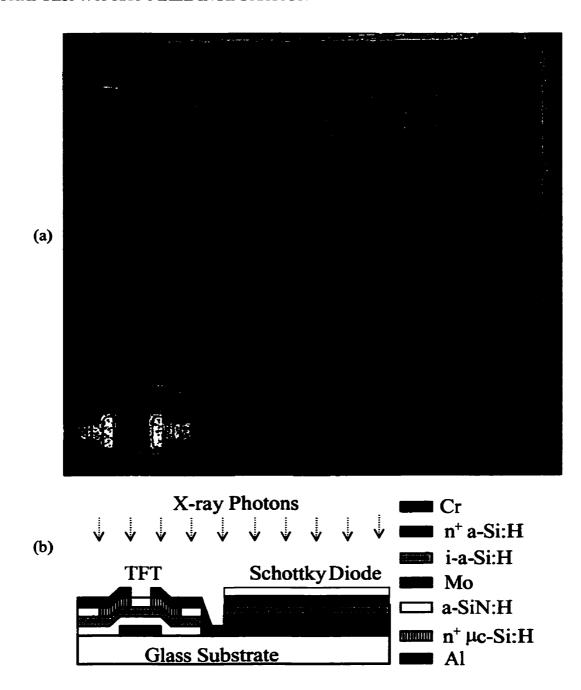

| 4.4  | Non-overlapping x-ray pixel; a) top view. b) cross-sectional view                                                                                                                                       | 95  |

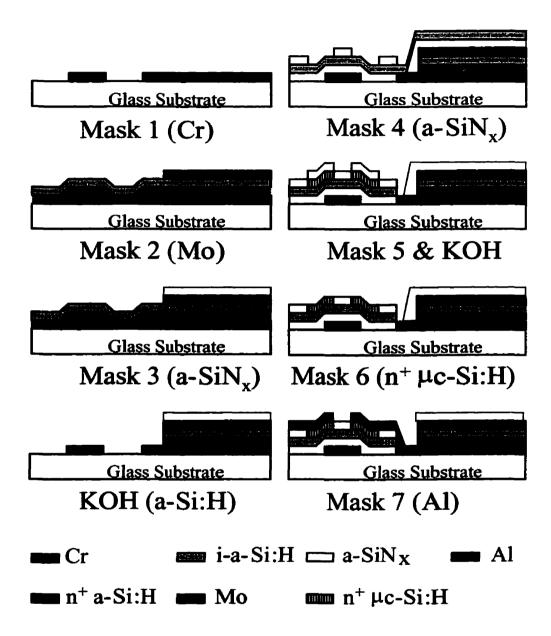

| 4.5  | Process steps of non-overlapping x-ray pixel.                                                                                                                                                           | 96  |

| 4.6  | Top view of damaged thin layers, i-a-Si:H, n <sup>+</sup> μc-Si:H and a-SiN:H, due to Cr etching.                                                                                                       | 99  |

| 4.7  | Top view of damaged thin film layers due to stresses associated with Mo. a-SiN:H and i-a-Si:H layers.                                                                                                   | 100 |

| 4.8  | Leakage currents of TFTs in the different pixel structures.                                                                                                 | .102 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.9  | Formation of parasitic back channel a) in the partially overlapped pixel and non-overlapping pixel, and b) in fully overlapped pixel with a metal ( $V_S$ = |      |

|      | 0V) covering the gate area.                                                                                                                                 | .103 |

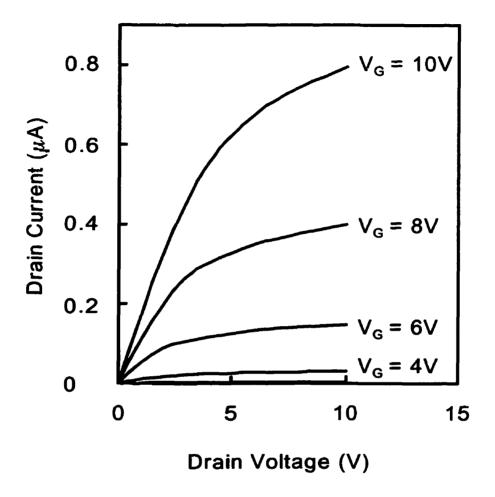

| 4.10 | Switching behavior of the non-overlapping TFT (W=20µm/L=10µm)                                                                                               | .104 |

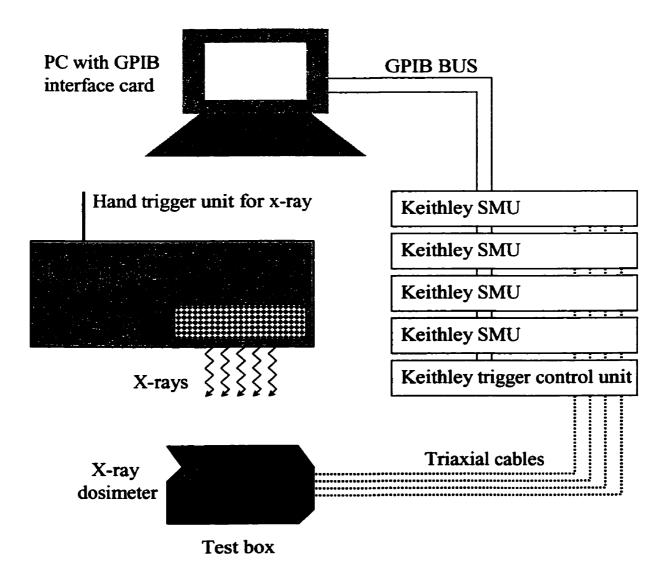

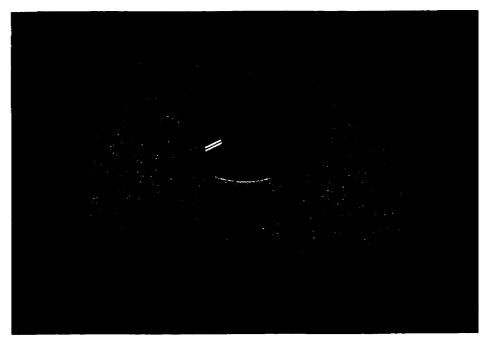

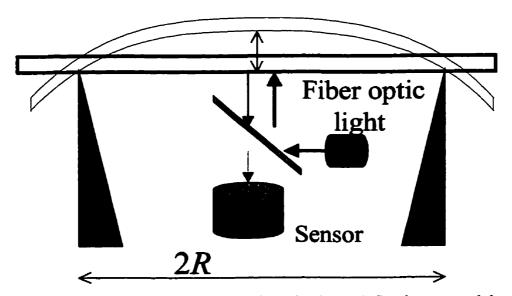

| 4.11 | X-ray sensitivity measurement setup                                                                                                                         | .105 |

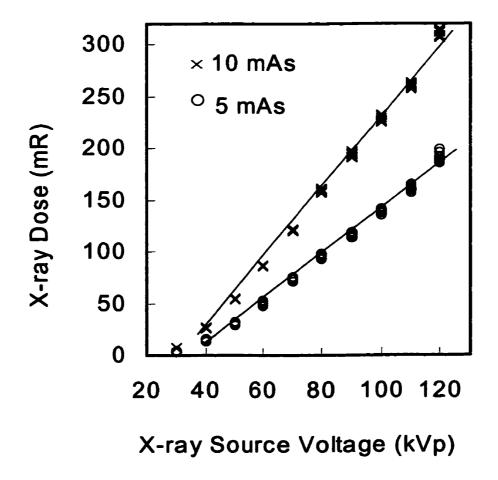

| 4.12 | X-ray dose vs. source voltage.                                                                                                                              | .106 |

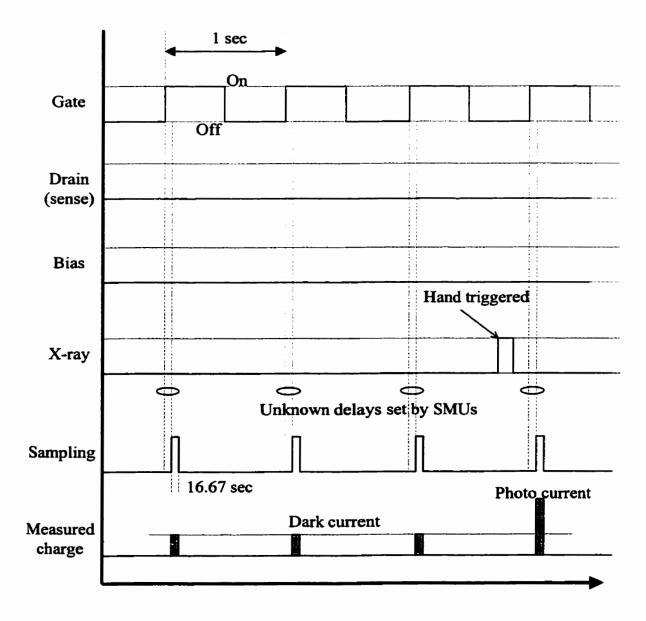

| 4.13 | Timing diagram of x-ray sensitivity measurement                                                                                                             | .107 |

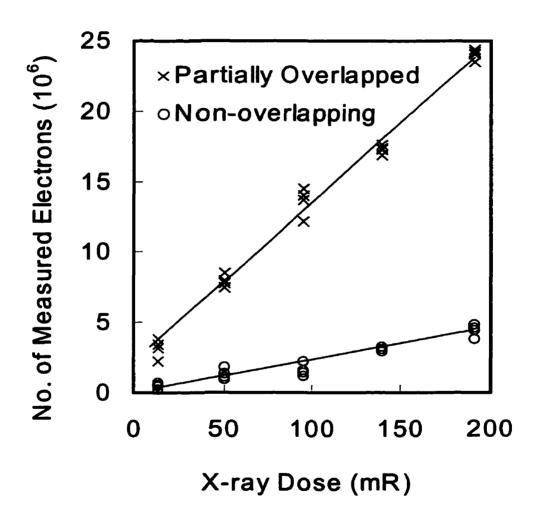

| 4.14 | Number of measured electrons vs. x-ray dose.                                                                                                                | .108 |

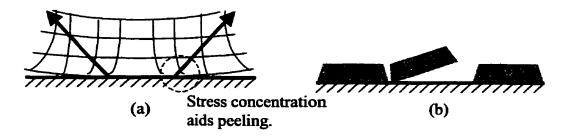

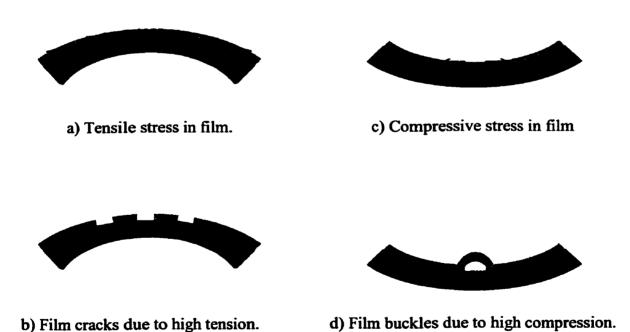

| 5.1  | a) Qualitative cross-sectional portrait of a thin film with tensile stress. b)                                                                              |      |

|      | Catastrophic peeling-off failure from tensile film stress                                                                                                   | .111 |

| 5.2  | a) Qualitative cross-sectional portrait of a thin film with tensile stress. b)                                                                              |      |

|      | Catastrophic buckling failure from tensile film stress.                                                                                                     | .111 |

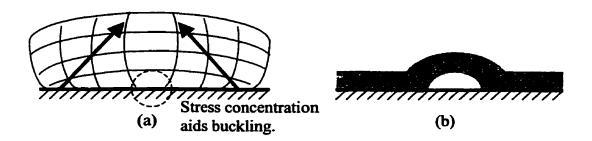

| 5.3  | Characteristics of the stress-strain relationship.                                                                                                          | 114  |

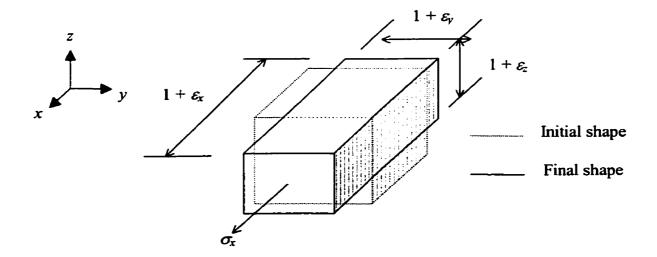

| 5.4  | Strain resulting from uniaxial stress applied to a cube                                                                                                     | 115  |

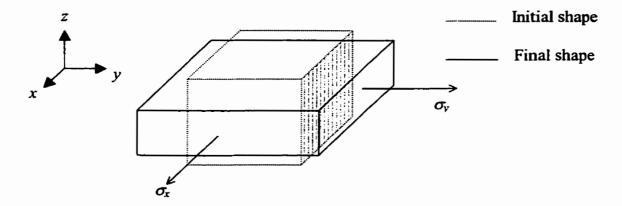

| 5.5  | Strain resulting from biaxial stress applied to a cube                                                                                                      | 116  |

| 5.6  | Stresses in thin film when an external force is applied.                                                                                                    | 117  |

| 5.7  | Simplified portraits of substrate bending effects                                                                                                           | 118  |

| 5.8  | Ionic Systems Stressgauge.                                                                                                                                  | 123  |

| 5.9  | Apparatus for observing the bow deflection caused by stress.                                                                                                | 123  |

| 5.10 | Shadow masks for depositing Mo film only at the center of the glass                                                                                         |      |

|      | wafers.                                                                                                                                                     | 125  |

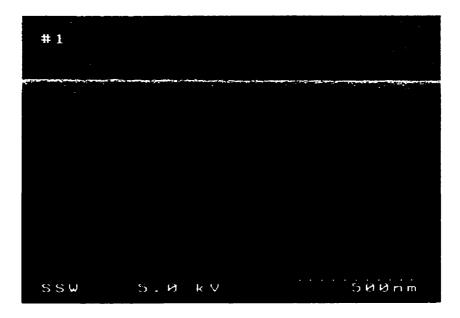

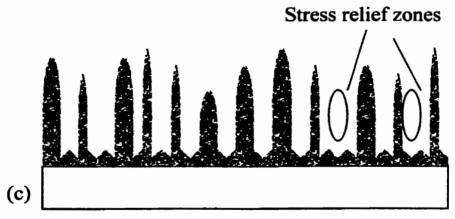

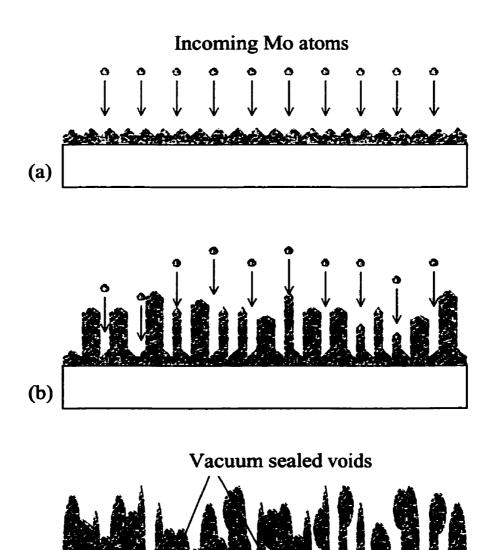

| 5.23 | SEM cross section image of 500nm thick Mo film deposited at 5mTorr and 400Watts                                                                                                                                            | 40 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.24 | SEM cross section image of 500nm thick Mo film deposited at 10mTorr and 400Watts                                                                                                                                           | 40 |

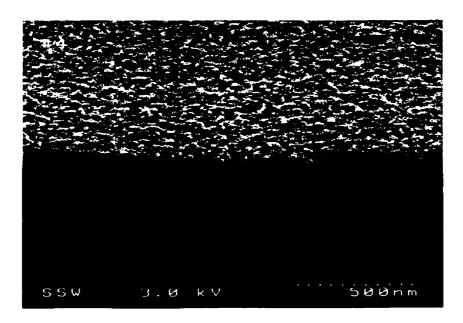

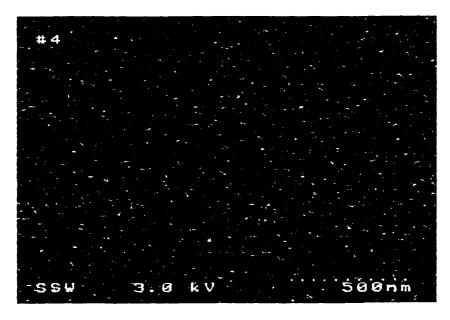

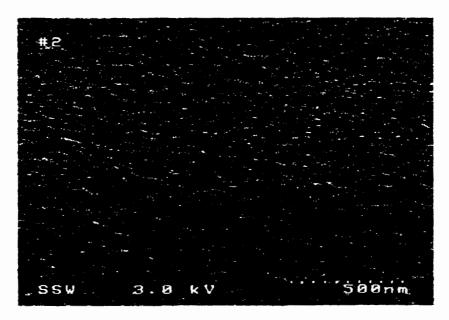

| 5.25 | SEM surface morphology image of 500nm thick Mo film deposited at 5mTort and 400Watts                                                                                                                                       | 41 |

| 5.26 | SEM surface morphology image of 500nm thick Mo film deposited at 10mTorr and 400Watts1                                                                                                                                     | 41 |

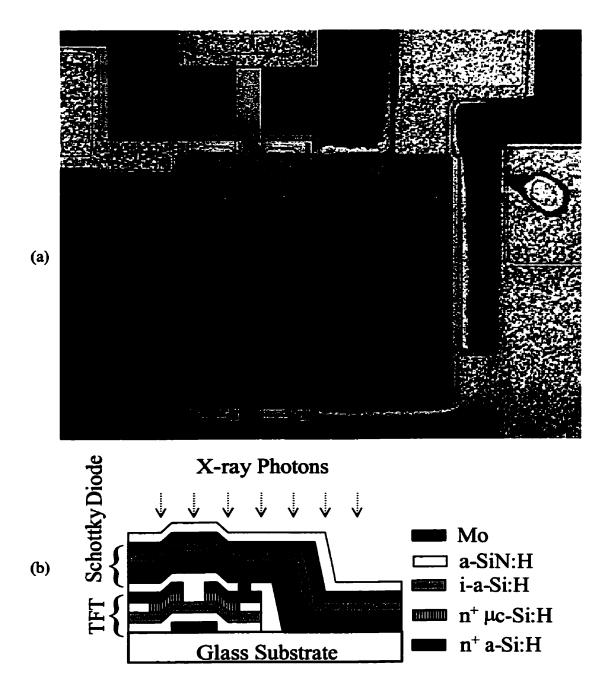

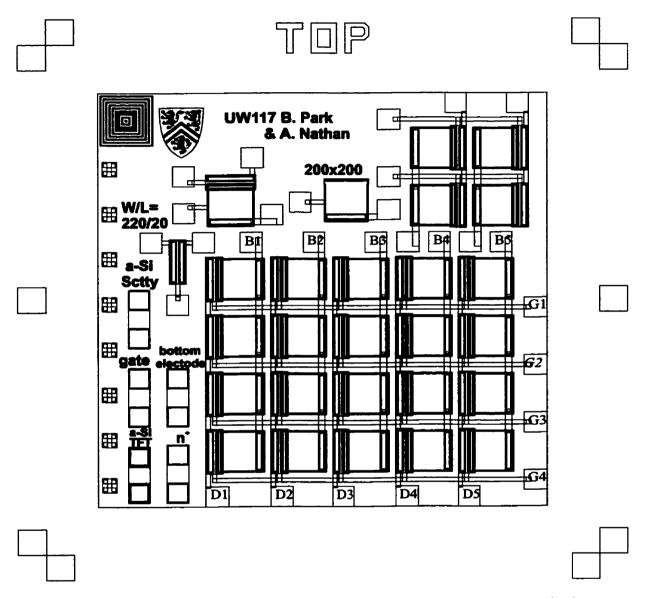

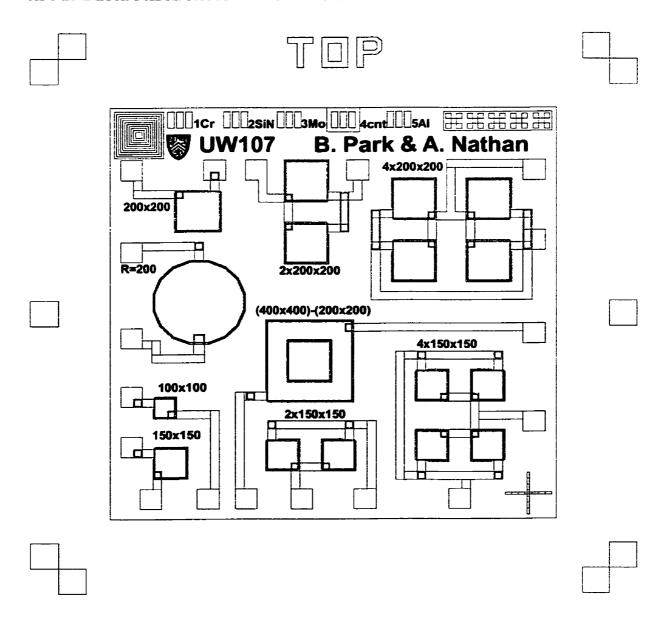

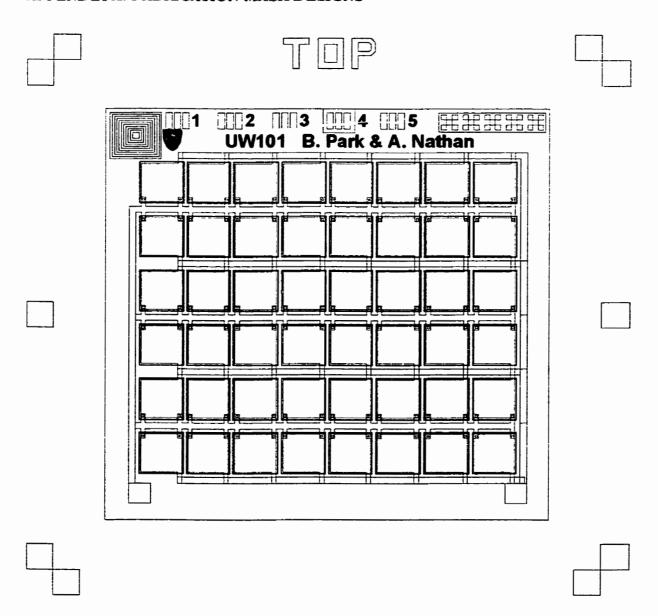

| 6.1  | X-ray imaging array design based on the pixel configuration presented in section 4.2.1. Schottky diode: 200μm x 200μm. TFT: L 20μm. W 200μm. The top Mo layer can be replaced with ITO for optical imaging                 | 44 |

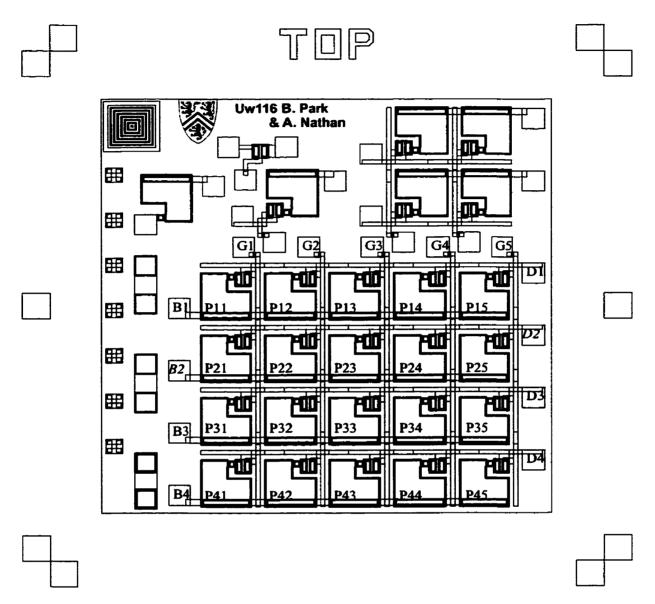

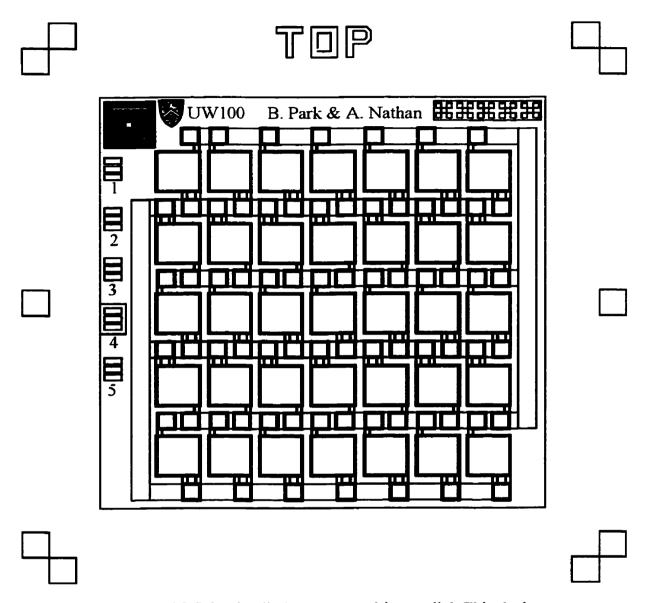

| 6.2  | X-ray imaging array design based on the pixel configuration presented in section 4.2.2. Schottky diode: $43000\mu m^2$ . TFT: L $20\mu m$ , W $50\mu m$ . The TFT in each pixel occupies an area of $110\mu m$ x $90\mu m$ | 45 |

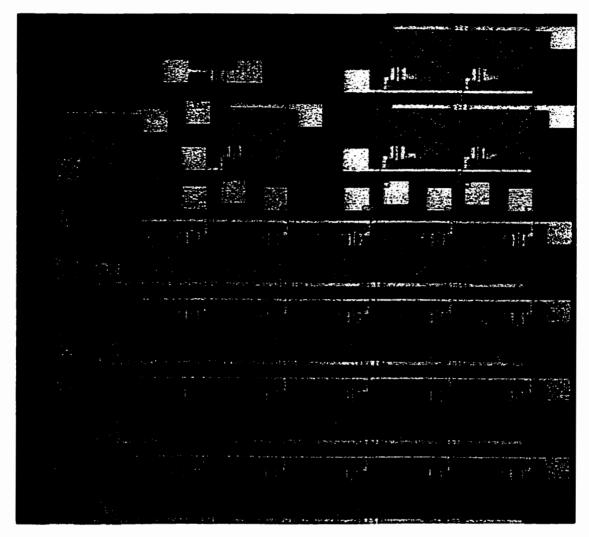

| 6.3  | X-ray imaging array. The picture was taken after all fabrication steps were completed                                                                                                                                      | 47 |

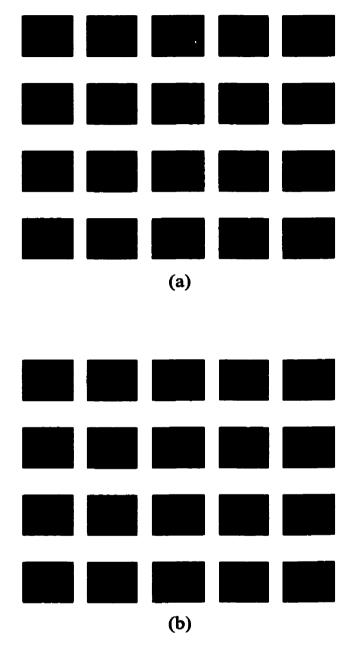

| 6.4  | Image taken by the array shown in Fig. 6.3 without the x-ray illumination.  (a) shows an ideal case image. (b) is created by a filter in Eq. 6.1                                                                           | 52 |

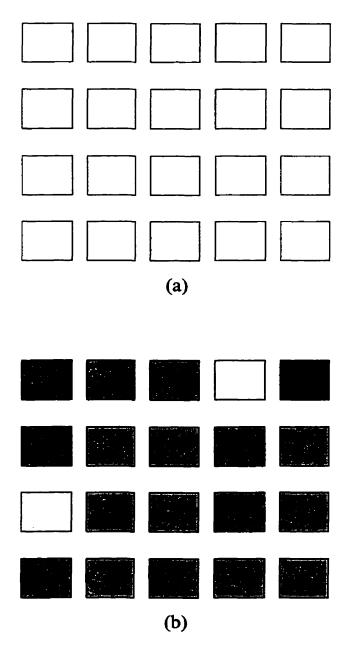

| 6.5  | Image taken by the array shown in Fig. 6.3 with the presence of x-rays. (a) shows an ideal case image. (b) is created by a filter in Eq. 6.2                                                                               | 53 |

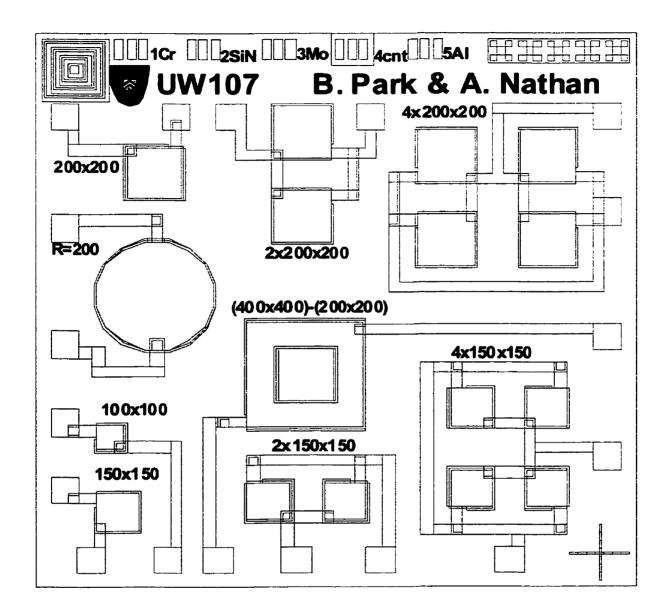

| A.l  | Mask layout design for m-i-s structure. The fabrication sequence is illustrated in Fig. A.2. This process requires a hydrogen plasma treatment at the insulator/silicon interface.                                         | 60 |

| A.2 | X-ray sensor fabrication sequence based on m-i-s structure                    | .161 |

|-----|-------------------------------------------------------------------------------|------|

| A.3 | 48 Schottky diodes connected in parallel. This design was used to measure     |      |

|     | the leakage current of the diode in section 3.2 and 3.3. All diodes are       |      |

|     | 200μm x 200μm. The fabrication sequence of this diode process is              |      |

|     | illustrated in Fig. 3.4.                                                      | .162 |

| A.4 | 35 Schottky diodes connected in parallel. This design was used to measure     |      |

|     | the leakage current of the diode fabricated with the old process sequence.    |      |

|     | All diodes are 200μm x 200μm. The fabrication sequence of this diode          |      |

|     | process is illustrated in Fig. 3.3. The old process is only 4 mask process.   |      |

|     | An extra step was added here for the final metallization (Al) for easier wire |      |

|     | bonding                                                                       | .163 |

| A.5 | Non-overlapping pixel designs studied in Chapter 4. The dimensions of the     |      |

|     | diode are varied from 200μm x 200μm to 50μm x 50μm while the TFT is           |      |

|     | kept at W: 20μm, L: 10μm                                                      | .164 |

| A.6 | Stacked pixel designs studied in Chapter 4. The dimensions of the diode is    |      |

|     | kept at 200μm x 200μm. while the TFT is varied - W: 200μm/L: 20μm,            |      |

|     | W: 90µm/L: 90µm, and W: 10µm/L: 100µm                                         | .165 |

# **List of Tables**

| 1.1 | Comparisons of the difference x-ray detection scheme14                                 |

|-----|----------------------------------------------------------------------------------------|

| 1.2 | Various thin film deposition techniques [32]14                                         |

| 2.1 | Deposition conditions of n <sup>+</sup> μc-Si:H films used in this study (FR indicates |

|     | the flow rate of each gas)31                                                           |

| 2.2 | Deposition parameters of Al films deposited as the gate metallization52                |

| 2.3 | Intrinsic stress of Al films deposited at various deposition conditions,               |

|     | before and after annealing. (-: compressive, +: tensile)58                             |

| 3.1 | Dimensions of the devices in the mask layout shown in Figure 3.171                     |

| 3.2 | The periphery to area ratio of the Schottky diodes in Figs. 3.6 and 3.780              |

| 4.1 | Design requirements for large area x-ray imaging arrays for different                  |

|     | imaging modalities, adopted from [11]89                                                |

| 5.1 | Measured intrinsic stress of thin films deposited on Corning 7059 glass                |

|     | substrate127                                                                           |

| 6.1  | Off currents, photo currents and number of measured electrons of pixels of x-ray imaging array shown in Fig. 6.3. | 149 |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

| B.1  | Calculated value of thermal stress of thin films on glass substrate. "-" sign denotes compressive stress.         | 166 |

| C.1  | Deposition parameters of PECVD films.                                                                             | 167 |

| C.2  | Deposition parameters of PVD films.                                                                               | 168 |

| D.1  | Etchant, etching temperature and etch rate of all films                                                           | 169 |

| F. i | RCA wafer cleaning process [113].                                                                                 | 172 |

## Chapter 1

## Introduction

#### 1.1 Background History of Amorphous Silicon

Hydrogenated amorphous silicon has become the material of choice in semiconductor technology, particularly in solar cells construction and active matrix display industries [1, 2, 3, 4, 5, 6, 7, 8]. The most outstanding attribute of amorphous silicon technology is its large area capability [7, 8]. Although the material contains defects that are associated with "no long-range order" crystalline structure [1, 2, 3], it still possesses all the requisite properties for semiconductors, such as doping, photoconductivity, and junction formation [4, 5, 6].

In the 1960s, when the physicists first turned their attention to the differences between the electronic states of amorphous and crystalline semiconductors, they found that evaporated or sputtered pure silicon had a very large defect density [1]. At the time, it seemed impossible to use amorphous silicon as a semiconducting material. It was not until the late 1960s when amorphous silicon was deposited from silane plasma for the first time by Dr. Chittick's group [2], and later on by Dr. Spear's group in the early 1970s, that the plasma deposited material had greatly improved semiconducting

properties [3]. It was then discovered in the mid 1970s that the improved properties were the result of hydrogen incorporation, which removed the electronic states in the band gap by binding hydrogen atoms to the dangle bond defects, thus eliminating the trapping and recombination centers [4]. Also in the mid 1970s, physicists discovered that amorphous silicon could be doped. The addition of phosphine or diborane to the silane plasma lead to n-doped or p-doped amorphous silicon films, respectively [5, 6]. The ability to control the location of the Fermi level in the band gap, along with the good photoconductivity of amorphous silicon, led to solar cell application in the late 1970s [7]. After the first thin film transistor was deposited in 1978 with a silicon nitride film from silane and ammonia gas mixture in the plasma chamber, display and imaging industries started to develop active TFT matrix arrays [8]. Since then, the rapid development of the active matrix liquid crystal display for laptop computer screens has allowed for advanced two-dimensional imaging arrays. One of the recent advanced imaging applications is the imaging of x-rays which will ultimately replace current conventional x-ray film.

#### 1.2 Motivations

The main objective of this work is to investigate the production feasibility of a largearea flat panel x-ray imaging array with hydrogenated amorphous silicon technology. The x-ray imaging array can replace the conventional screen films used for radiography (ex. chest x-ray and mammography).

The main advantages of digital radiology include the following:

(i) Fast turn around time. In a simple case of biopsy, doctors will no longer have to wait for several iterations of the 20-minute long film development cycle just to see if the end of the needle has reached the desired area in the body [9].

- (ii) Improved image visualization. For example, the contrast between images is enhanced, which allows for more accurate diagnoses [10].

- (iii) Assistance in finding subtle abnormalities [11, 12].

- (iv) Easy electronic storage and retrieval.

- (v) Remote viewing. With the advances in internet and wireless communications, doctors can view the image from remote places. It also facilitates tele-conferencing.

#### 1.3 Advantages of a-Si:H technology

Hydrogenated amorphous silicon offers a suitable platform for medical x-ray imaging over other process technologies, such as CCD or CMOS technologies. The most outstanding advantages of a-Si:H are:

- (i) the capacity to inexpensively deposit films of uniform thickness over a large area [13, 14];

- (ii) resistance to radiation damage [15];

- (iii) optical band gap of 1.7eV;

- (iv) low temperature deposition capability with plasma-enhanced chemical vapor deposition (PECVD) technique;

- (v) little constraint on substrate material; and

- (vi) low leakage current of a-Si:H devices due to low conductivity.

The low device leakage current will be discussed in greater detail in the main body of this thesis. The main driving force of the a-Si:H flat panel array is the active matrix liquid crystal display (AMLCD) industry. In each pixel of the array in this application, there is a thin film transistor (TFT) whose function is to locally switch the pixel on and off, hence the term "active." The light-emitting device in the flat display panel can be replaced with any type of photo sensors – in this project, x-ray sensors – to convert the active matrix display array to an x-ray imaging array.

#### 1.4 X-ray Detection Schemes

#### 1.4.1 Indirect Detection Scheme

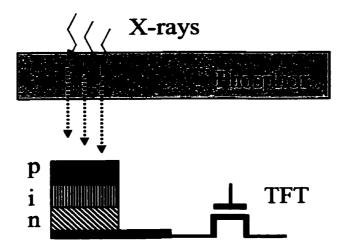

One method to detect x-rays using a-Si:H technology is to convert the radiation into visible light in an intermediate (phosphor) layer, then detect the visible light with a-Si:H photosensors (Fig. 1.1). Since 1985, there have been a number of reports on the fabrication and testing of x-ray imaging arrays, most of which rely on the indirect detection mechanism [15, 16, 17, 18, 19, 20, 21, 22, 23, 24, 25]. One of the research groups working on this scheme is *dpiX*, *LLC* in Palo Alto, CA. *dpiX* manufactures a-Si:H image sensor arrays with pixel sizes from 127µm to 392µm and image formats from 20cm x 25cm to 30cm x 40cm in area. These arrays are supplied with a coating of cesium iodide, used as an x-ray scintillating layer. The commercially available array is then assembled into a complete imaging system. Following this, gate driver and readout amplifier circuit boards are connected to the array. Moreover, the electronics on the array is designed for radiographic imaging in which the frame time is greater than 3 seconds [25]. This array is reported to have a noise level of approximately 0.3fC and the maximum signal of 3 pC [26], which allows a potential dynamic rage of ~10000. High

Figure 1.1: Indirect x-ray detection method, based on combination of a phosphor layer and an a-Si:H image sensor.

Figure 1.2: Pixel circuit schematic diagram of indirect x-ray detection array. Each pixel contains a p-i-n photodiode to capture the visible light emitted from the phosphor layer and a TFT to make the array gate-addressable.

dynamic range and low noise are essential figures of merits for large area imaging electronics [26]. Figure 1.2 illustrates the pixel schematics of this indirect detection method along with a simplified drawing of the array layout.

The medical imaging is performed either in radiographic mode or fluoroscopic mode. In the radiographic mode, the imager captures a single image in response to a brief x-ray exposure. The requirements for radiographic imagers are a large-area, a high resolution and a high dynamic range [26]. In the fluoroscopic mode, the imager has to capture a continuous real-time sequence of x-ray images at a rate of at least 15 frames per second [26]. The most outstanding requirement for fluoroscopic arrays is speed, which is largely dependent on the performance of the TFTs in the array [13]. The requirement for high speed switching, meaning fast data transfer, will be discussed in details in section 2.1.

The efficiency of indirect x-ray detection is determined by a number of factors, e.g., the efficiency of conversion of x-ray photons to visible light, the efficiency of the photodetectors in converting the visible light to a useful electrical signal, and fill factor [14, 18, 19, 25]. This scheme has been reported to yield good results at relatively high x-ray energies. However, at low energies, the detection efficiency is not as high [25]. This technological difficulty does not appear to be an issue in the direct detection scheme. This idea will be further explained in the following section.

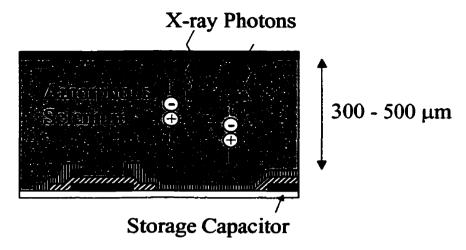

#### 1.4.2 Direct Detection Scheme

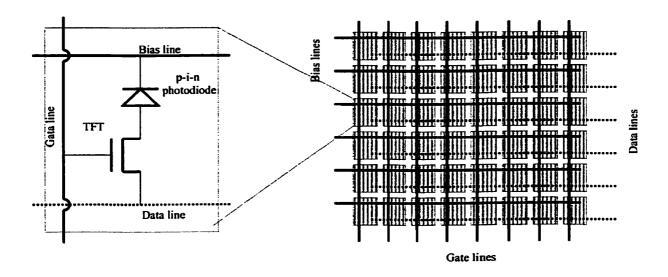

Alternatively, a direct detection scheme can also be employed (Fig.1.3). This scheme requires thick ( $300 \sim 500 \mu m$ ) vapor-deposited amorphous selenium (a-Se) layers [27, 28, 29]. In this method, x-ray photons are absorbed in the a-Se layer, where their radiation energies are transferred to the generation of electron-hole (e-h) pairs.

Figure 1.3: Direct x-ray detection method using a thick vapor-deposited amorphous selenium layer.

Figure 1.4: Pixel circuit schematic diagram of direct x-ray detection array. Each pixel contains a storage capacitor to keep the charge generated by x-rays. The selenium layer is continuous over the entire detection area. The bias line is not shown in the simplified array layout.

Subsequently, the e-h pairs are separated by an applied electric field and collected to form the signal. Our collaborator, Dr. J Rowlands' group at Sunnybrook Hospital of the University of Toronto, has successfully produced x-ray images using a-Se as the x-ray photoconductor [11, 27, 28]. The design of a direct detection array is very similar to that of the indirect array. It consists of a two-dimensional array of TFTs (Fig. 1.4). The major difference here is that, in this design, an additional storage capacitor is required. A storage capacitor is made by overlapping the pixel electrode with either adjacent gate line or a separate ground line. Radiation detection is accomplished with a uniform layer of x-ray sensitive photoconductor deposited on the active matrix (see Fig. 1.3). The top surface is a continuous high voltage bias electrode which is used to apply an electric field across the photoconductor. When electron-hole pairs are created by the x-ray photons, they are then separated by this applied electric field. The storage capacitor collects the charge generated and holds it until the gate of the TFT is turned on.

The direct detection method offers advantages in resolution and efficiency [27, 28]. Moreover, they do not depend on scintillation layers. However, despite the potentially high resolution of these image sensors, the thick selenium layer introduces difficulties in the collection of the generated charges [28]. A strong electric field is required to separate the e-h pairs, which is achieved by applying a high bias voltage (4 ~ 10kV). Furthermore, charge trapping in the a-Se layer can lead to an image lag, which reduces the frame rate of the imaging array [27].

#### 1.4.3 Detection Scheme of This Study

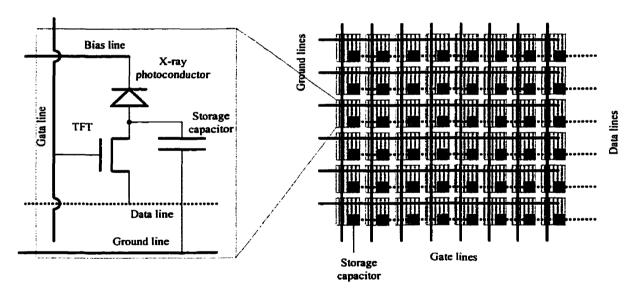

In 1997, α-sidic group has developed the design, fabrication, and characterization of a direct-conversion x-ray detector based on Molybdenum (Mo)/a-Si:H Schottky diode for low-energy x-rays [30, 31]. In this diode, the interaction of x-ray photons with Mo leads

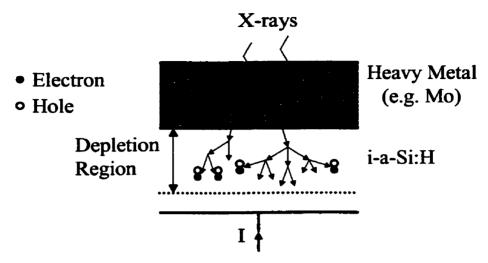

Figure 1.5: X-ray detection scheme based on Mo/a-Si:H Schottky diode.

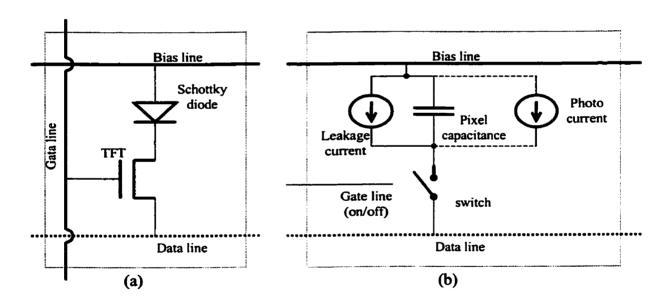

Figure 1.6: Direct detection x-ray imaging pixel based on a-Si:H/Mo Schottky diode as a detector. (a) Circuit schematic diagram. (b) Equivalent circuit diagram

to injection of high energy electrons, by virtue of the photoelectric effect, into a reverse-biased a-Si:H depletion layer, where electron (avalanche) multiplication yields a gain (Fig 1.5). The e-h pairs are then separated by the electric field inside the depletion region of the reverse-biased Schottky diode, thereby producing the output signal. The array layout is essentially identical to that of indirect detection array shown in Fig. 1.2.

The pixel operation can be described with the equivalent circuit diagram shown in Fig. 1.6b). The TFT is represented by a switch that is controlled by the gate signal. The Schottky diode can be represented by a capacitor to model the internal pixel capacitance and a current source to model the leakage current of the diode. With the gate signal at "off" and the bias line at a negative voltage, for example -4V, the internal pixel capacitance is not fully charged and the other side of the capacitor is at a voltage level higher than -4V, for example -1.5V. Without x-rays only a small charge is transferred to data line when the gate is turned on. If incidence x-ray photons are present while the gate is turned off, the x-ray can be modeled by an additional current source parallel to the pixel capacitor and the leakage current source. For simplicity, assume that there is a high dose of x-ray, which fully charges the internal pixel capacitance. There is now a strong conductance between the two sides of the capacitor. The opposite side to the bias line of the capacitor is close to -4V. When the gate is turned on, assuming that this charge is retained despite the leakage current of the TFT, a large charge is transferred to the data line. The difference, according to data line, is the dynamic range of the pixel.

At low bias operation (< 4V), the detector yields a sensitivity of approximately  $10^8$  electrons over x-ray energies in the range of  $40 \sim 100$  kVp [30, 31]. The fabrication process of this diode is fully compatible with that of an a-Si:H TFT, which is intended to be used as a switch for charge readout.

The performance of this detection method depends on the quality of the Schottky interface. The silicon/metal interfaces in p-i-n photodiode form ohmic

contacts, since the silicon is heavily doped near the interfaces. A Schottky barrier junction includes an abrupt termination of the semiconductor crystal. The silicon surface contains interface states due to incomplete covalent bonds, which can lead to trapped charges at the metal-semiconductor interfaces. This property of the Schottky diode will be further discussed in Chapter 3 as a discrete device and in Chapter 6 as in a fixed pattern noise within an array.

#### 1.4.4 Comparisons of Different Detection Schemes

The three different x-ray detection schemes that were discussed in the previous sections have their own advantages and disadvantages [9-31]. The ultimate objective for the design of an detection scheme is to optimize the performance of the detector in terms of its ability to capture and digitize the information content of the incident x-rays. Thus, it is important that the different detection schemes be compared for their performance, cost and complexity in fabrication processes. It is not feasible to compare these detection schemes in terms of quantitative figures since no x-ray images have yet been successfully captured with a-Si:H/Mo Schottky diodes. But based on the information from the published literatures, and the results produced from our laboratory, the different detection schemes can be compared qualitatively (Table 1.1).

### 1.5 Thin Film Deposition

The devices made in this work are composed of thin films. There are a number of ways that thin films can be deposited. Major deposition techniques are categorized in Table 1.2. Of all these available deposition techniques, an engineer should be able to determine which methods to use based on the following considerations.

|             | Indirect detection       | Direct detection        | Direct detection          |

|-------------|--------------------------|-------------------------|---------------------------|

|             | scheme using a           | scheme employing a      | scheme with a-            |

| Detection   | scintillating layer to   | thick (~500nm) a-Se     | Si:H/Mo Schottky          |

| scheme      | convert the x-ray        | layer as detector. The  | diode as the x-ray        |

|             | photons to visible       | a-Se layer is           | detector. The diode is    |

|             | light then process the   | deposited by            | reverse biased by a       |

|             | visible light with p-i-n | evaporation over the    | small voltage.            |

|             | photodiode.              | entire array.           |                           |

|             | Since the x-ray          | Although energetic      | According to [30, 31]     |

|             | photons are converted    | electron created by x-  | the gain is ~1000 over    |

|             | to visible light, p-i-n  | ray photons generate    | the x-ray source          |

|             | diodes do not exhibit    | a gain $(g(E) = E/W, E$ | voltage range of          |

| Signal gain | a large gain. The        | is the x-ray energy     | 40kVp - 100kVp. The       |

| and charge  | efficiency of the p-i-n  | and W is the energy     | charge collection         |

| collection  | photodiode is ~75%       | required to generate a  | efficiency should be      |

|             | [16]. At a reverse bias  | electron in a-Se.)      | close to that of the p-i- |

|             | of -8V, the charge       | [28], due to the poor   | n diode. The effect of    |

|             | collection efficiency    | charge collection, not  | the leakage current       |

|             | is nearly 1 [14].        | all electrons get       | will be discussed in      |

|             |                          | stored [27].            | Chapter 3.                |

|             | The p-i-n diodes array   | Even with the           | Image spreading is not    |

|             | does not spread the      | continuous a-Se         | a concern in this         |

|             | image. However, the      | layer, due to the large | design.                   |

| Image       | conversion of x-rays     | bias applied across it, |                           |

| spreading   | emits visible light in   | the generated           |                           |

| • '         | •                        | •                       | •                         |

| <b>1</b>    | <b>1</b>                 |                                    |                          |

|-------------|--------------------------|------------------------------------|--------------------------|

|             | all directions [13].     | electron-hole pairs                |                          |

|             | Anisotropic              | travel vertically [11,             |                          |

|             | phosphors are            | 27, 28].                           |                          |

|             | becoming available.      |                                    |                          |

|             | The smallest pixel       | Since the a-Se layer               | The smallest pixel size  |

|             | size is largely limited  | is continuous, pixel               | is determined by the     |

| G 11 4      | by the anisotropy of     | size is determined by              | leakage current of the   |

| Smallest    | the phosphor layer as    | the size of the TFTs.              | diodes. In Chapter 3, a  |

| pixel size  | well as its conversion   | For mammography,                   | diode as small as        |

|             | efficiency [13]. The     | the pixel can be as                | 26μm² will be            |

|             | smallest pixel size is ~ | small as ~50μm <sup>2</sup> . [27, | observed.                |

|             | 100μm².                  | 28]                                |                          |

|             | With isotropic light     | Because the a-Se                   | In this design, fill     |

|             | emission, a fill factor  | layer is covering the              | factor is determined by  |

|             | >50% does not            | entire array, fill factor          | the size of the TFT and  |

|             | improve the image        | is 100% [9, 10].                   | line width. In Chapter   |

| Fill Factor | quality [14].            |                                    | 6, the arrays have       |

|             |                          |                                    | ~45% fill factor. It can |

|             |                          |                                    | be as high as ~80%       |

|             |                          |                                    | with vertical channel    |

|             |                          |                                    | TFTs.                    |

|             | Along with any           | The electronics to                 | Once the full imaging    |

|             | reduction in signal-to-  | process an image are               | system is developed,     |

|             | noise performance        | the same as in the                 | the electronics          |

|             | generated by blurring    | indirect detection.                | associated with the      |

| Additive    | and sampling stages,     | The electronic noise               | detector will be the     |

| noise       | additional noise arises  | per pixel is                       | same as the other two.   |

|             | II                       | <sup>-</sup>                       | l i                      |

| from the electronics  | approximately 1000    |   |  |

|-----------------------|-----------------------|---|--|

| such as amplifier     | electrons [27]. There |   |  |

| noise. The electronic | is an additional shot |   |  |

| noise per pixel is    | noise caused by       |   |  |

| approximately 1000    | thermal excitation of |   |  |

| electrons [13].       | charge carriers in a- | } |  |

|                       | Se layer.             |   |  |

Table 1.1: Comparisons of the difference x-ray detection scheme.

| Γ      |        | Mechanism           |                        |                                           |  |

|--------|--------|---------------------|------------------------|-------------------------------------------|--|

|        |        | Physical            | Chemical               |                                           |  |

| ,      | Plasma | Sputtering          | Reactive<br>Sputtering | Plasma-assisted chemical vapor deposition |  |

| Medium | Vapor  | Evaporation         | Reactive evaporation   | Chemical vapor deposition                 |  |

|        | Liquid | Spinning or preying | Particle plating       | Plating anodization                       |  |

|        | Solid  | Diffusion           | Ion implantation       | Case-hardening                            |  |

Table 1.2: Various thin film deposition techniques [32].

- (i) The appropriate deposition rate for the required thickness, purity and production rate.

- (ii) The effects on substrate in terms of heat, ion bombardment, etc.

- (iii) Reliability and lifetime requirements.

- (iv) Affordability.

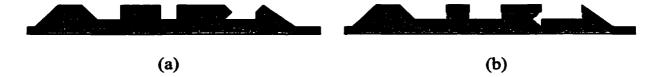

The family of silicon films can be easily deposited by the CVD process whereas the metals films can be deposited by the PVD process. Both processes allow for the films to be deposited at a low temperature, <400°C, which is the temperature that the substrate glass, Corning 1737, starts to soften. The CVD process is well-known [32] for its conformal coverage of the substrate profile (Fig. 1.7a). This is a very useful property of CVD process when wet etch processes are used and the protection layer is a thin insulating layer, such as silicon nitride. However, the PVD process covers only the top surfaces. Vertical profiles do not get covered by films deposited by the PVD process, which can lead to uncovered and exposed surface (Fig. 1.7b). The effect of this step coverage will be shown in Chapter 3 as a part of the Schottky diode device performance.

Figure 1.7: Surface coverage of tin film processes (a) CVD process. (b) PVD process.

# 1.5.1 Plasma Enhanced Chemical Vapor Deposition

For the thin film device fabrication, two plasma enhanced chemical vapor deposition (PECDV) chambers are available, namely PlasmaTherm VII (Fig. 1.8) and Oxford

Figure 1.8: PlasmaTherm VII parallel plates PECVD system for thin film depositions.

PECVD systems. Both systems have a parallel plate reactor chamber. The advantage of PECVD system over low pressure CVD (LPCVD) system is that the deposition temperature can be lowered due to the RF power being applied to the parallel plates, which help dissociate the source gas molecules (Fig 1.9). The PlasmaTherm VII system is used for depositions of intrinsic amorphous silicon layer, n<sup>+</sup> doped amorphous silicon layer, and silicon nitride layer. This chamber is used for the tri-layer deposition of TFT (Chapter 2) and active layer in the Schottky diode (Chapter 3). The Oxford PECVD system is mainly used for n<sup>+</sup> doped microcrystalline silicon layer (Chapyer 2), which serves as the contact layer in TFTs. Chemical vapor deposition is the reaction or decomposition of gases flowing over a heated substrate, leaving behind a solid film as a reaction product. When the source gas, for example, silane, enters the PECVD chamber and the RF power is applied on the parallel plates, the source gas molecules dissociate

Figure 1.9: A simplified cross section view of the PECVD chamber. Only the most vital components are shown.

into silane radicals such as SiH<sub>3</sub>, SiH<sub>2</sub> and SiH. Unfortunately, the exact plasma chemical balance equations are still not discovered. But the products of such plasma reactions are thin films which compose thin film devices that are being used everyday. Chapter 2 will examine the CVD plasma deposition process for microcrystalline silicon films in an attempt to explain why crystallization happens at low deposition temperature with hydrogen dilution in the plasma chamber.

Figure 1.10: Edwards magnetron DC/RF sputtering system thin metal film depositions.

#### 1.5.2 Sputter Deposition

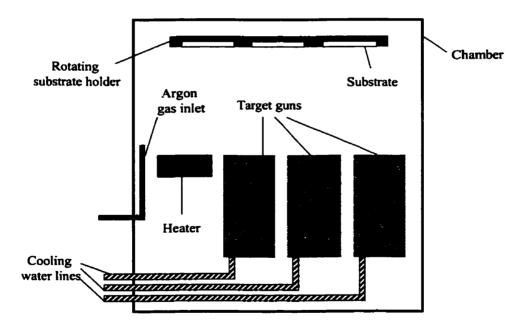

Edwards magnetron sputtering system (Fig. 1.10) used for this work has three target guns so that a combination of metal layers can be deposited in one vacuum pump-down This system has both DC and RF power supplies. For highly conductive metal such as aluminum, the DC power supply is used. For metals not as conductive as aluminum, such as molybdenum, the RF power supply is used. Unlike the PECVD process, the process gas atoms do not get deposited in the film. However, the sputtering gas molecules do have a chance to get trapped in the film. They do not bind to the metal Atoms, simply fill in the voids created during the deposition. Edwards system uses argon as the sputter gas [32]. Figure 1.11 shows a rotating substrate holder in the PVD chamber. The purpose of the rotating substrate is to improve the uniformity of film

Figure 1.11: A simplified cross sectional view of the Edward sputtering system. Only the most vital components are shown.

thickness. Unlike the PECVD system, whose uniformity difference is within 5%, the PVD system has a uniformity of 10%, or even 15% when the DC power supply is used.

Sputtering is the process of removing surface atoms by ion bombardment. Sputtering processes can be used to deposit films or even to clean or etch surfaces [32]. When positive ions are generated by an ion source such as a glow discharge, they bombard a negative cathode, the target material. The momentum of the ion is transferred to the surface atoms of the target, some of which acquire sufficient energy to leave the surface. Then, these atoms from the target material travel by diffusion to reach the surface of the substrate. Chapter 5 of this thesis will discuss that the quality of films deposited by the PVD sputtering process depends on how much energy the sputtering atoms carry by the time they reach the substrate surface.

#### 1.5.3 Film Deposition in Vacuum

Understanding the film deposition mechanisms in vacuum is very difficult. This thesis does not focus on the film deposition. However, the devices fabricated for this work are made of thin films, deposited by the CVD and PVD systems. Therefore, this thesis does contain discussions of vacuum environment, such as the analysis of microcrystalline growth in chapter 2 and the sputtering kinetics in Chapter 5. In this section, some of the terms that are discussed in the main body of this thesis are introduced.

The international standard unit of pressure is the pascal, Pa, which is defined as a Newton per meter<sup>2</sup>, N/m<sup>2</sup>. This unit is used to describe the film stresses in Chapter 5. But this unit is seldom used when describing the vacuum chamber pressure. For thin film deposition processes, the vacuum pressure is the torr, Torr, or millitorr, mTorr. One torr is the pressure exerted by the weight of a one millimeter high column of mercury. One pascal is 7.5 mTorr.

In a vacuum, the density of molecules (or atoms) is very low compared to that of the ambient environment at atmospheric pressure. Thus, the molecules travel long distances before they collide with another molecule. The mean free path,  $\lambda$ , of a particle in a vacuum is the average distance that it travels before it collides with another molecule. The mean free path depends on how close together the molecules are and how big a collision target they make. How far the particles are from another depends on the degree of vacuum. The mean free path is expressed as [32]

$$\lambda = kT/\sigma P \tag{1.1}$$

where P is the pressure,  $\sigma$  is the collision cross section, k is the Boltzmann's constant and T is the temperature. The effect of a change in mean free path of the atoms in the sputtering system on the properties of the film being deposited will be presented in Chapter 5.

Both CVD and PVD chambers have to be brought to ambient atmospheric environment for the loading and unloading of wafers. Then, the chambers are pumped down to the base vacuum level of  $\sim 10^{-6}$  Torr. Very often, this vacuum level is considered to be "clean" and free of foreign gas molecules. For a given temperature, the density, n, of atoms or molecules in a vacuum is directly proportional to pressure. The relationship is [32]

$$n = 9.67 \times 10^{18} P/T \text{ molecules/cm}^3$$

. {1.2}

When a vacuum chamber is open and pumped down to  $10^{-6}$  Torr, there are still 10 billion gas molecules in the chamber. It is, therefore, wise not to completely ignore the chance of contamination in the film growth. Furthermore, the rate at which these molecules bombard the surfaces in a vacuum, called bombardment flux,  $\Gamma$ , is given by [32]

$$\Gamma = n\sqrt{(kT/2\Pi M)} = 3.15 \times 10^{22} P/\sqrt{(MT)} \text{ particles/cm}^2/\text{second}$$

{1.3}

where M is the atomic or molecular weight of the particle. At  $10^{-6}$  Torr,  $\Gamma$  is  $\sim 10^{15}$  particles/cm<sup>2</sup>/second. From Eqs. 1.14 and 1.15, the time it takes to form a mono-layer of the surface of the wafer at  $10^{-6}$  Torr is only  $\sim 1$  sec. As it will be mentioned later in this thesis, HF dip process is used in device fabrications in order to remove the native oxide at the surface before the wafers are loaded into the plasma chambers. But at atmospheric pressure, it takes only 1  $\mu$ sec to form a mono-layer on the surface after the HF dip process. The purpose of this HF dip is really to clean the surface rather than to remove the native oxide, unless the native oxide is really thick. The effect of this mono-layer formation on the surface will be discussed in Chapter 2 and Chapter 3 for TFT and Schottky diode device performances, respectively.

#### 1.6 Overview of the Thesis

This thesis describes the technological difficulties that were encountered in integrating this direct detection x-ray sensor with a TFT (as a switch) to make an imaging pixel. Chapter 2 discusses the advancements made in the TFT process and device performance. Chapter 3 presents the leakage current behavior of the Schottky diode. Chapter 4 explores the fabrication process integration of the two devices. Here, two very different processes are compared in terms of the process complexity and the pixel performance. Chapter 5 focuses on the intrinsic film stress that can cause catastrophic damage to deposited films. Chapter 6 discusses the designs of x-ray imaging arrays, followed by conclusions. Although the arrays fabricated in this work are on a very small scale (2mm die), they can be used as templates for larger scale arrays (2" to 6" arrays). Other mask designs are presented in the Appendices along with fabrication specifics.

# Chapter 2

# Thin Film Transistors (TFTs)

Thin film transistors are most widely used as the switching element in large-area electronics applications. In imaging applications, achieving low leakage current of the transistor is crucial [26]. Each pixel should retain the charge collected by the sensor for as long as possible. This can be achieved only when the leakage current of the transistor is small. For faster switching speed, the transistors should have fast rising current in the sub-threshold region [13, 26]. And as the area of the display/imaging arrays becomes larger (>~17"), the gate delay due to RC constant can become a limiting factor [8, 22, 26]. Thus, the transistor should employ low resistivity gate metal in order to reduce the RC constant. This chapter deals with the advancements achieved in TFT performance with respect to the above mentioned.

# 2.1 TFT Operation

In flat panel display applications, polycrystalline silicon TFTs are often used as the switching devices due to their high device mobility, which leads to higher maximum drive current to the light emitting device and higher frame rates. In imaging

applications, due to the low device leakage current requirement, amorphous silicon TFTs are used. The TFTs used for this study are based on the inverted-staggeredstructure which is widely used in a-Si:H large area displays and imaging systems [9 -29]. A simplified cross-sectional view of the TFT is shown in Fig. 2.1. This TFT operates in the n-channel accumulation mode when a positive bias is applied, i.e., when the TFT is on. The electric field from the gate metal attracts electrons in the intrinsic amorphous silicon layer to form a thin n-channel at the gate dielectric interface. When a positive bias is applied to the drain with the respect to the source, the electrons can flow from source to drain. This TFT operation follows the usual semiconductor relations for MOSFET transistors. The challenge for a-Si:H TFT is achieving low on-resistance,  $R_{ON}$ . For large area imaging applications, the frame rate can be  $15 \sim 70$  frames/s [13, 14, 21]. A simple calculation can be done assuming that the frame rate is 30 frames/s and there are 2000 gate lines in the large area imaging array. In this case, each line must be read in 15 µs. Allowing 5 µs for gate switching, the actual time left for the TFT to transfer the charge from the sensor to the data line is only 10us. Again, assuming that the transfer of charge takes 5 time constants (RC) and the pixel capacitance is  $\sim 1pF$  [33], the on-resistance of the TFT is

$$R_{ON} \le 2 M\Omega$$

{2.1}

In the imaging applications, the TFT operates in the linear regime for which the onresistance, the ratio of source drain voltage and current, is [34]

$$R_{ON} = V_{DS}/I_{DS} = [C_G \cdot \mu_{FE}(V_G - V_T)W/L]^{-1}, \qquad \{2.2\}$$

where  $C_G$  is the gate capacitance,  $\mu_{FE}$  is the field effect mobility,  $V_G$  is the gate bias,  $V_T$  is the threshold voltage, W is the width of the TFT, and L is the TFT channel length. For a thin film transistor with the gate dielectric thickness of 250nm and a field effect

Figure 2.1: Inverted-staggered a-Si:H TFT. When the gate positively biased, an electron channel is induced at the gate dielectric/intrinsic silicon interface providing a conduction path from drain to source.

mobility of  $\sim 1 \text{ cm}^2/\text{Vs}$ , the gate capacitance is  $\sim 5 \times 10^{-8} \text{F/cm}^2$  [35]. Then, the equation for on-resistance can be simplified to

$$R_{ON} = 25[(V_G - V_T)W/L]^{-1} M\Omega.$$

{2.3}

For a TFT with  $V_G - V_T = 5V$ , the requirement suggested in Eq. 2.1 can be achieved if the aspect ratio of the transistor W/L is greater than 2.5. In Chapter 6 (see Fig. 6.2), the channel of the TFTs in the array is  $50\mu$ m wide and  $20\mu$ m long, which results in W/L ratio of 2.5. The upper limit of this ratio is strongly governed by another array design requirement, namely, fill factor. The trade-off of these two design criteria will be revisited in Chapter 4 where the pixel designs will be discussed. In this chapter,

however, since the TFT is presented as a single discrete device, the aspect ratio is kept at  $10 \text{ (W} = 200 \mu\text{m} / L = 20 \mu\text{m})$ .

The requirement for low on-resistance of the channel is really for the fluoroscopy application. For radiographic application, the TFT is required to hold the charge on the pixel for the radiographic frame time which can be as long as one second or even longer. If only 1% of the data loss is allowed on a pixel whose pixel capacitance is 1pF, and the frame time is 1 second, the required *RC* constant of the TFT when turned off is

$$R_{OFF}C > 100 \text{ second},$$

{2.4}

which means that

$$R_{OFF} > 10^{14} \,\Omega.$$

{2.5}

This is why low TFT leakage current is important for radiographic application. In the following section of this chapter, the TFT device performance will be compared in terms of the leakage current. A TFT leakage current of 100 fA or higher is not suitable for x-ray imaging applications.

The current-voltage characteristics of a-Si:H TFTs are effectively the same as those of a crystalline silicon MOS transistors except for a fact that the magnitude of the current level of a-Si:H TFTs are much lower. The accumulated charge at the gate dielectric interface can be expressed using the MOS transistor equation [36]

$$Q(x) = C_G[V_G - VT - V(x)], \{2.6\}$$

where V(x) is the additional voltage along the channel at distance x that is formed by the applied bias  $V_{DS}$ . The drain current  $I_D$  can be expressed as

$$I_D(x) = W \cdot Q(x) \cdot \mu_{FE} \cdot E(x), \qquad \{2.7\}$$

where E(x) is the electric field between drain and source. Substituting Eq. 2.6 into Eq. 2.7 leads to

$$I_D(x) = W \bullet \mu_{FE} \bullet C_G[V_G - V_T - V(x)] dV(x)/dx.$$

{2.8}

Integrating Eq. 2.8 along the channel results in

$$I_D(x) = \mu_{FE} \cdot C_G[(V_G - V_T)V_D - V_D^2] \cdot W/L.$$

(2.9)

Just as in the MOS transistors case, the drain current of a-Si:H TFTs saturates after a certain bias point at  $V_{DS}$ . When  $\Delta I_D/\Delta V_{DS}=0$ , the drain saturation current can be expressed as

$$I_{D\_Saturation} = 1/2 \bullet \mu_{FE} \bullet C_G (V_G - V_T)^2 \bullet W/L.$$

{2.10}

Equations  $2.6 \sim 2.10$  are essentially the same as the MOSFET model equations. These equations will be revisited in the following sections of this chapter where measured a-Si:H TFT device characteristics are presented.

#### 2.2 TFT Fabrication