# Power Characterization of a Gbit/s FPGA Convolutional LDPC Decoder

by

## Si-Yun Li

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2012

$\bigodot$ Si-Yun Li2012

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

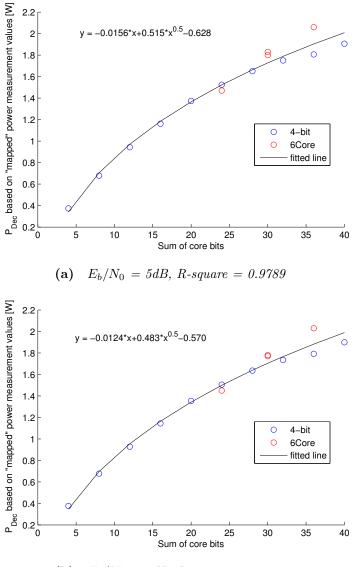

In this thesis, we present an FPGA implementation of parallel-node low-density-paritycheck convolutional-code (PN-LDPC-CC) encoder and decoder. A 2.4 Gbit/s rate-1/2 (3, 6) PN-LDPC-CC encoder and decoder were implemented on an Altera development and education board (DE4). Detailed power measurements of the FPGA board for various configurations of the design have been conducted to characterize the power consumption of the decoder module. For a  $E_b/N_0$  of 5 dB, the decoder with 9 processor cores (pipelined decoder iteration stages) has a bit-error-rate performance of  $10^{-10}$  and achieves an energyper-coded-bit of 1.683 nJ based on raw power measurement results. The increase in  $E_b/N_0$ can effectively reduce the decoder power and energy-per-coded-bit for configurations with 5 or more processor cores for  $E_b/N_0 < 5$  dB. The incremental decoder power cost and incremental energy-per-coded-bit also hold a linearly decreasing trend for each additional processor core. Additional experiments are performed to account for the effect of the efficiency of the DC/DC converter circuitry on the raw power measurement data. Further experiments have also been conducted to quantify the effect of clipping thresholds, bit width for each processor core on bit-error-rate (BER) performance, power consumption, logic utilization of the decoder. A "6Core" decoder with growing bit-width log-likelihood ratios (LLRs) has been found to have a BER performance near that of a "6Core" 6-bit decoder while consuming similar power, and logic utilization to that of a 5-bit "6Core" decoder.

#### Acknowledgements

I would like to thank my supervisors Dr. Vincent Gaudet and Dr. Duncan Elliott for their guidance, support, funding, and their confidence in me and my work.

Many thanks to Dr. Manoj Sachdev and Dr. Siddharth Garg for taking the time to read my thesis as well as allowing me to borrow the DE4 board from Dr. Sachdev's group.

Thanks to Dr. Chris Backhouse for lending me the extra equipments for power measurements.

I would also like to thank Dr. Zhengang Chen for developing the PN-LDPC-CC codes and Dr. Tyler Brandon for providing HDL code for the encoder and decoder modules, and for making my project possible.

A big thank you to Philip Marshall, Russell Dodd, Brendan Crowley and Stephen Holmes for their support and guidance for LDPC-related problems and discussions.

Special thanks to Logan Gunthrope and Gary Block for their extensive support in HDL, LDPC-CC, Tcl and FPGA-related matters.

To Danny Tsuei, thank you for showing me how to make use of the JTAG-MM interface with the DE4 board, which greatly sped up the data-gathering portion of my work.

Thank you to Karl Jensen for his extensive support with LaTeX-related problems.

Special thanks to Altera for the donation of the DE4 board.

Lastly, I would like to thank University of Waterloo for the QEIIGSST scholarship, and NSERC and PetroCanada for funding.

#### Dedication

This is dedicated to my parents and friends.

# **Table of Contents**

| Li | List of Tables x |                                |          |  |  |

|----|------------------|--------------------------------|----------|--|--|

| Li | st of            | Figures xi                     | ii       |  |  |

| N  | omer             | xvi                            | ii       |  |  |

| 1  | Intr             | oduction                       | 1        |  |  |

|    | 1.1              | Motivation                     | 1        |  |  |

|    | 1.2              | Thesis Organization            | 4        |  |  |

| 2  | Bac              | kground                        | <b>5</b> |  |  |

|    | 2.1              | LDPC Definitions               | 5        |  |  |

|    | 2.2              | LDPC Decoding                  | 7        |  |  |

|    | 2.3              | LDPC-CC Definitions            | 0        |  |  |

|    | 2.4              | State-of-the-art LDPC Decoders | 2        |  |  |

|    |                  | 2.4.1 ASIC-based LDPC Decoders | 12       |  |  |

|    |                  | 2.4.2 FPGA-based LDPC Decoders | 3        |  |  |

| <ul> <li>3.2 PN-LDPC-CC Encoder</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3                | FPO | GA Implementation 1                            |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------------------------------------------------|----|--|

| <ul> <li>3.2.1 Gate-Swapping</li> <li>3.2.2 Clock-gating</li> <li>3.3 PN-LDPC-CC Decoder</li> <li>3.3.1 Truncated Min-Sum Check Sum Operation</li> <li>3.3.2 Removal of Reset Circuitry in Check-Node</li> <li>3.3.3 Removal of Saturation Bit</li> <li>3.3.4 Clock-gated Registers</li> <li>3.4 System Design</li> <li>3.4 System Design</li> <li>4 Power Measurement</li> <li>4.1 Available Power Measurement Methods</li> <li>4.2 Board Power Measurement Method</li> <li>4.3 DC/DC Converter Efficiency</li> <li>4.3.1 Estimation Based on Data Sheet</li> <li>4.3.2 Estimation Based on Experimental Results</li> </ul> |                  | 3.1 | PN-LPDC-CC                                     | .8 |  |

| 3.2.2       Clock-gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  | 3.2 | PN-LDPC-CC Encoder                             | 20 |  |

| 3.3       PN-LDPC-CC Decoder         3.3.1       Truncated Min-Sum Check Sum Operation         3.3.2       Removal of Reset Circuitry in Check-Node         3.3.3       Removal of Saturation Bit         3.3.4       Clock-gated Registers         3.4       System Design         3.4       System Design         4       Power Measurement         4.1       Available Power Measurement Methods         4.2       Board Power Measurement Method         4.3       DC/DC Converter Efficiency         4.3.1       Estimation Based on Data Sheet         4.3.2       Estimation Based on Experimental Results            |                  |     | 3.2.1 Gate-Swapping                            | 22 |  |

| <ul> <li>3.3.1 Truncated Min-Sum Check Sum Operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |     | 3.2.2 Clock-gating                             | 24 |  |

| 3.3.2       Removal of Reset Circuitry in Check-Node         3.3.3       Removal of Saturation Bit         3.3.3       Removal of Saturation Bit         3.3.4       Clock-gated Registers         3.4       System Design         3.4       System Design         4       Power Measurement         4.1       Available Power Measurement Methods         4.2       Board Power Measurement Method         4.3       DC/DC Converter Efficiency         4.3.1       Estimation Based on Data Sheet         4.3.2       Estimation Based on Experimental Results                                                             |                  | 3.3 | PN-LDPC-CC Decoder                             | 24 |  |

| 3.3.3 Removal of Saturation Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |     | 3.3.1 Truncated Min-Sum Check Sum Operation    | 27 |  |

| 3.3.4       Clock-gated Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |     | 3.3.2 Removal of Reset Circuitry in Check-Node | 27 |  |

| 3.4       System Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |     | 3.3.3 Removal of Saturation Bit                | 27 |  |

| <ul> <li>4 Power Measurement</li> <li>4.1 Available Power Measurement Methods</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |     | 3.3.4 Clock-gated Registers                    | 28 |  |

| <ul> <li>4.1 Available Power Measurement Methods</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | 3.4 | System Design                                  | 28 |  |

| <ul> <li>4.1 Available Power Measurement Methods</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 Down Mongument |     | er Measurement 3                               | ર  |  |

| <ul> <li>4.2 Board Power Measurement Method</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |     |                                                |    |  |

| <ul> <li>4.3 DC/DC Converter Efficiency</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  | 4.1 | Available Power Measurement Methods            | 33 |  |

| <ul> <li>4.3.1 Estimation Based on Data Sheet</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  | 4.2 | Board Power Measurement Method    3            | 87 |  |

| 4.3.2 Estimation Based on Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  | 4.3 | DC/DC Converter Efficiency                     | 0  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |     | 4.3.1 Estimation Based on Data Sheet 4         | 0  |  |

| 4.4 Chapter Summery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |     | 4.3.2 Estimation Based on Experimental Results | 2  |  |

| 4.4 Onapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  | 4.4 | Chapter Summary                                |    |  |

| 5 | Me            | asurement Results and Discussion          | 48 |

|---|---------------|-------------------------------------------|----|

|   | 5.1           | BER Performance                           | 48 |

|   | 5.2           | Power Measurement Results                 | 49 |

|   | 5.3           | Logic Utilization                         | 56 |

|   | 5.4           | Chapter Summary                           | 59 |

| 6 | Pov           | ver-Driven Architectural Exploration      | 61 |

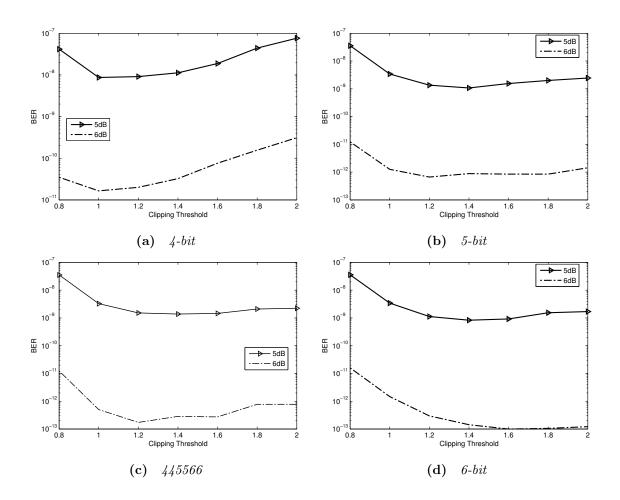

|   | 6.1           | Clipping Threshold versus BER Performance | 62 |

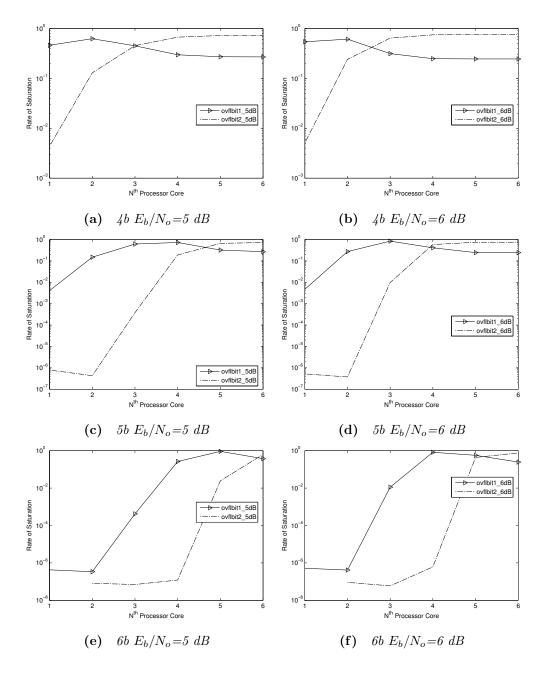

|   | 6.2           | Rate of LLR Saturation                    | 65 |

|   | 6.3           | Results and Analysis                      | 67 |

| 7 | Cor           | nclusions                                 | 74 |

|   | 7.1           | Summary and Contribution                  | 74 |

|   | 7.2           | Future Research                           | 76 |

|   | 7.3           | Publication Arising out of Thesis         | 77 |

| R | References 73 |                                           |    |

| A | PPE           | NDICES                                    | 86 |

| Α | ΑL            | ean Host-FPGA Interface Using JTAG-MM     | 87 |

|   | A.1           | Checklist                                 | 88 |

|   | A.2           | Detailed steps for JTAG-MM                | 88 |

|                       | A.2.1      | Define an SOPC system     | 88  |

|-----------------------|------------|---------------------------|-----|

| A.2.2 Simulation Mode |            | Simulation Mode           | 93  |

|                       | A.2.3      | Hardware Mode             | 94  |

| в                     | Verilog Co | ode for device-under-test | 96  |

| С                     | Tcl Script | s                         | 99  |

|                       | C.1 Tcl Sc | cript for Simulation Mode | 99  |

|                       | C.2 Tcl Sc | ript for Hardware Mode    | 101 |

## List of Tables

| 2.1 | Summary of ASIC-based Implementation Results | <br>14 |

|-----|----------------------------------------------|--------|

| 2.2 | Summary of FPGA Implementation Results       | <br>17 |

| 4.3 | Summary of measured board power result, deduced output current and effi-              |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | ciency for each LTM4601 under various conditions. The FPGA core power is              |    |

|     | calculated by subtracting the measured power for the base case with having            |    |

|     | only PLL control logic on the FPGA core from the measured board power                 |    |

|     | for the cases with the full design on the FPGA core. $\ldots$ . $\ldots$ . $\ldots$ . | 43 |

| 4.4 | Calculated equivalent resistance for the FPGA core power listed in Table 4.3          |    |

|     | with the assumption that $V_{VCC0P9}$ remains constant at 0.9 V                       | 43 |

| 4.5 | Comparison of mapped power measurement values with estimated values                   |    |

|     | from PowerPlay of decoder power of different number of processor cores for            |    |

|     | the $T_s = 192$ , $\rho = 16$ rate-1/2 (3, 6) PN-LDPC-CC code with 4-bit LLRs at      |    |

|     | $E_b/N_0 = 2$ dB running at a clock frequency of 75 MHz on Altera DE4 $\therefore$    | 46 |

| 4.6 | Measured input voltage for FPGA chip at various parallel resistances                  | 47 |

# List of Figures

| 2.1 | Example of H matrix for a rate-1/2 LDPC code with $n = 16, k = 8 \dots$                                                                                                                                                                                   | 6  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Tanner graph representation of the $H$ matrix in Figure 2.1. Variable nodes are shown on top, and check nodes at the bottom $\ldots \ldots \ldots \ldots \ldots$                                                                                          | 7  |

| 2.3 | Basic Communication System. Channel modulator and demodulator are not shown in the picture                                                                                                                                                                | 7  |

| 2.4 | <i>H</i> matrix for LDPC-CC. Note the diagonal band structure of non-zero elements.                                                                                                                                                                       | 11 |

| 3.1 | Sub-matrice $H_{i'}^T(t')$ for PN-LDPC-CC                                                                                                                                                                                                                 | 19 |

| 3.2 | A high-level block diagram of the implemented PN-LDPC-CC encoder. An<br>example of a single encoder node is shown in Figure 3.5. The one-hot en-<br>coding of the phase signal is shown in Figure 3.3. Figure 3.4 depicts the<br>parity output circuitry. | 21 |

| 3.3 | One-hot encoding of the phase signal for the $T_s = 192$ , $\rho = 16$ , rate-1/2<br>(3,6) PN-LDPC-CC, group period $T'_s = 12$ . [1]                                                                                                                     | 21 |

| 3.4 | Parity output circuitry for the $T_s = 192$ , $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-<br>CC, group period $T'_s = 12$ . [1]                                                                                                                                 | 22 |

| 3.5 | A single encoder node from the implemented architecture in this thesis for                                                                                                                                                                                            |              |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|     | the $T_s = 192$ , $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-CC. [1]                                                                                                                                                                                                        | 23           |

| 3.6 | A single decoder processor. $[1]$                                                                                                                                                                                                                                     | 26           |

| 3.7 | An example of a clock-gated register [1]                                                                                                                                                                                                                              | 26           |

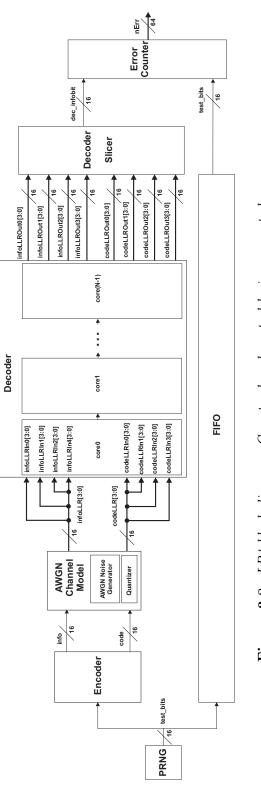

| 3.8 | LP4 block diagram. Counter-based control logics are not shown                                                                                                                                                                                                         | 30           |

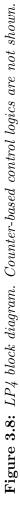

| 3.9 | Interaction between LP4 core on the FPGA and computer Tcl terminal                                                                                                                                                                                                    | 31           |

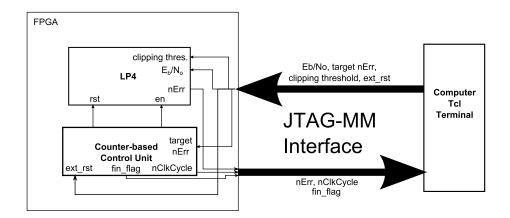

| 4.1 | Decoder power obtained on configurations of 1 to 5 cores with Nios II unit<br>incorporated using board power measurement method with mapping step<br>and Nios II measurement unit                                                                                     | 38           |

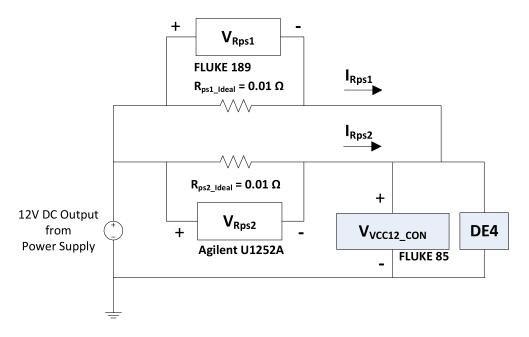

| 4.2 | Power Measurement Set-up                                                                                                                                                                                                                                              | 38           |

| 4.3 | Efficiency versus Load Current with 12-V Input for LTM4601 Regulator.<br>(Taken from the LTM4601 data sheet [2])                                                                                                                                                      | 42           |

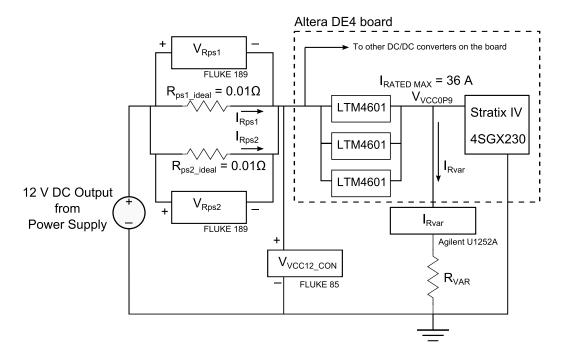

| 4.4 | Schematic for DC/DC efficiency experiment                                                                                                                                                                                                                             | 44           |

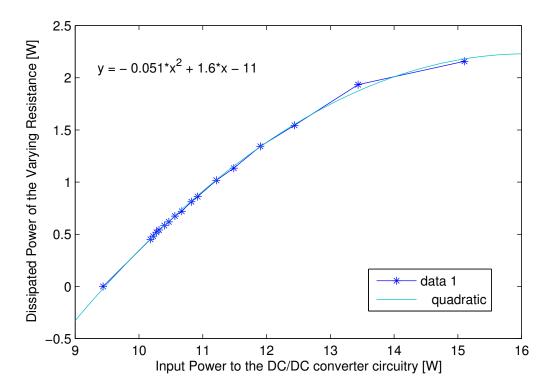

| 4.5 | Input and output power measured for the DC/DC converter circuitry on the Altera DE4 using the setup denoted in Figure 4.4                                                                                                                                             | 45           |

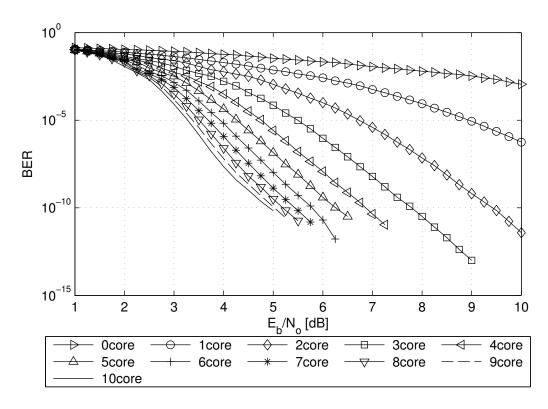

| 5.1 | BER for various numbers of decoder cores for the $T_s = 192$ , $\rho = 16$ rate-1/2<br>(3, 6) PN-LDPC-CC code with 4-bit LLRs at various $E_b/N_0$ obtained from<br>measurements on DE4 based a target number of errors of 1000 based on a<br>PDSK based AWCN shapped | 50           |

|     | BPSK-based AWGN channel.                                                                                                                                                                                                                                              | $\mathbf{S}$ |

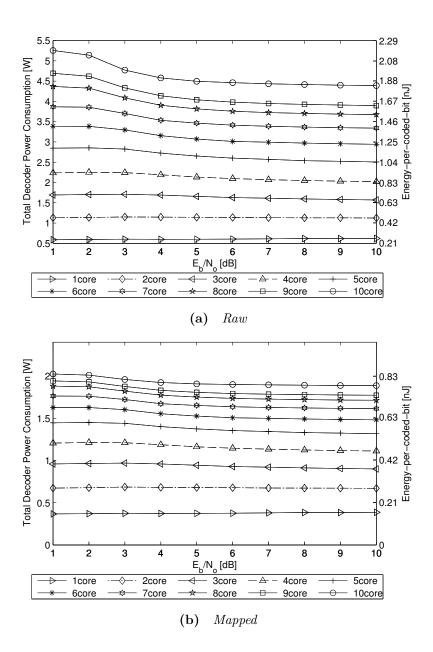

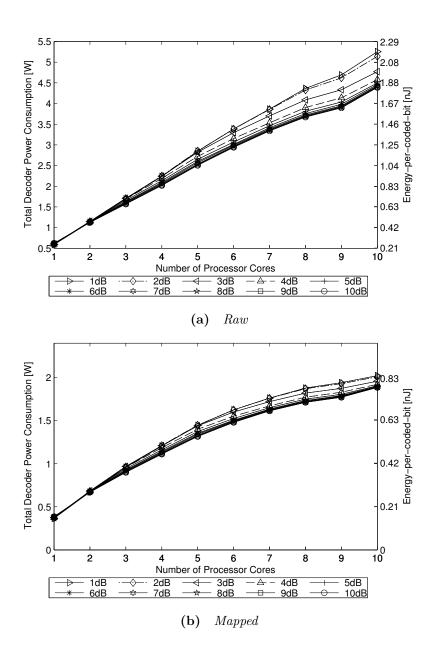

| 5.2 | Average measured decoder power and energy-per-coded-bit at various $E_b/N_0$<br>for various numbers of decoder cores on DE4 with 4-bit LLRs at a 75MHz                                                                                                                                                                                |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | clock with coded throughput of 2.4 Gbit/s for the $T_s = 192$ , $\rho = 16$ , rate-1/2<br>(3,6) PN-LDPC-CC code based on three sets of measurements for each data<br>point.                                                                                                                                                           | 53 |

| 5.3 | Average measured decoder power and energy-per-coded-bit at various $E_b/N_0$<br>for various numbers of decoder cores on DE4 with 4-bit LLRs at a 75MHz<br>clock with coded throughput of 2.4 Gbit/s for the $T_s = 192$ , $\rho = 16$ , rate-1/2<br>(3,6) PN-LDPC-CC code based on three sets of measurements for each data<br>point. | 54 |

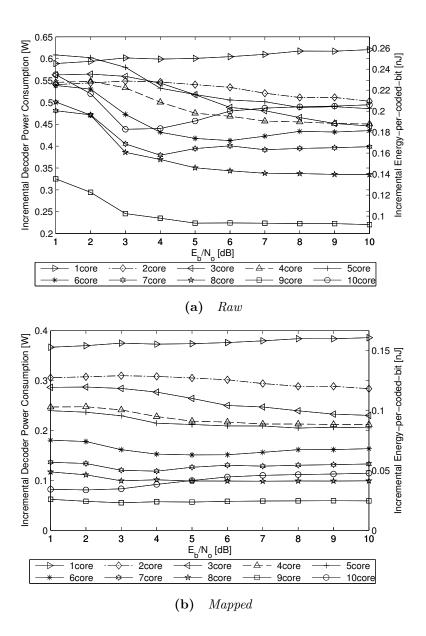

| 5.4 | Incremental measured decoder power and energy-per-coded-bit for every dB of increase in $E_b/N_0$ for various numbers of decoder cores on DE4 with 4-bit LLRs at a 75MHz clock with coded throughput of 2.4 Gbit/s for the $T_s = 192$ , $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-CC code.                                                | 55 |

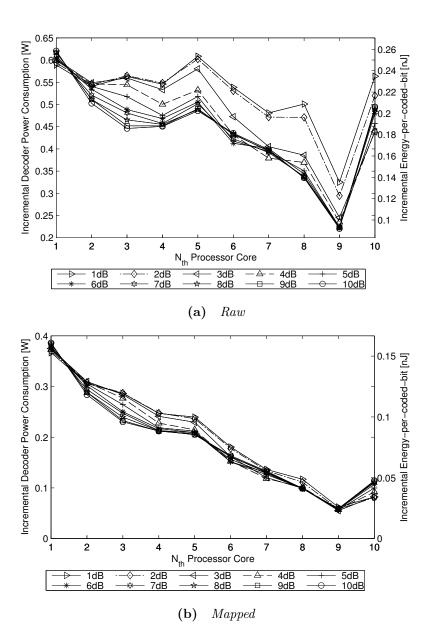

| 5.5 | Incremental measured decoder power and energy-per-coded-bit for each ad-<br>ditional core at various $E_b/N_0$ on DE4 with 4-bit LLRs at a 75MHz clock<br>with coded throughput of 2.4 Gbit/s for the $T_s = 192$ , $\rho = 16$ , rate-1/2 (3,6)<br>PN-LDPC-CC code.                                                                  | 57 |

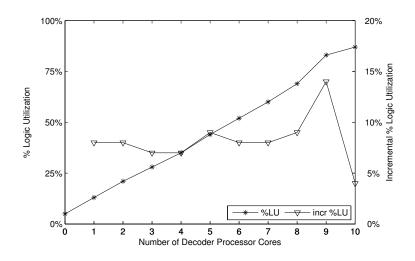

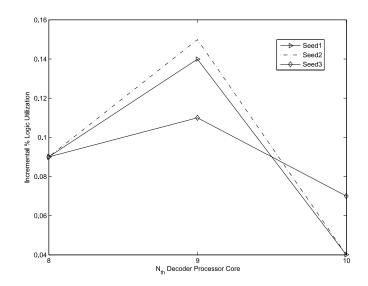

| 5.6 | Logic utilization and incremental logic utilization for various configurations with different numbers of decoder processor cores                                                                                                                                                                                                      | 58 |

| 5.7 | Incremental logic utilization for various configurations with 8, 9, 10 decoder processor cores                                                                                                                                                                                                                                        | 59 |

|     |                                                                                                                                                                                                                                                                                                                                       |    |

| 6.1 | Information BER at $E_b/N_0$ of 2 dB to 8 dB for configurations with 5 to       |    |

|-----|---------------------------------------------------------------------------------|----|

|     | $8$ decoder cores on DE4 with 3-bit LLRs at a $75\mathrm{MHz}$ clock with coded |    |

|     | throughput of 2.4 Gbit/s for the $T_s$ = 192, $\rho$ = 16, rate-1/2 (3,6) PN-   |    |

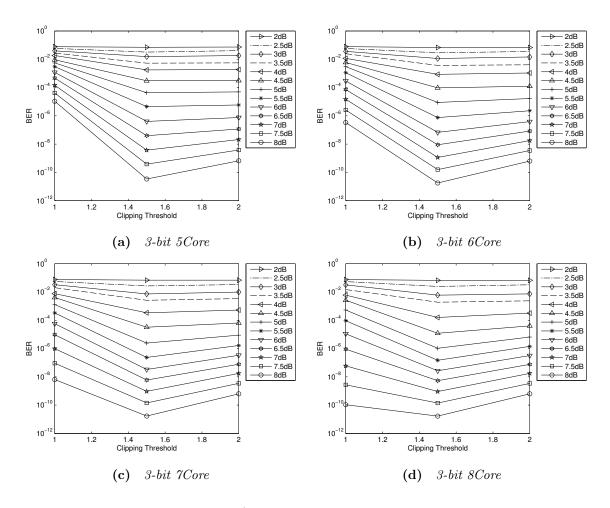

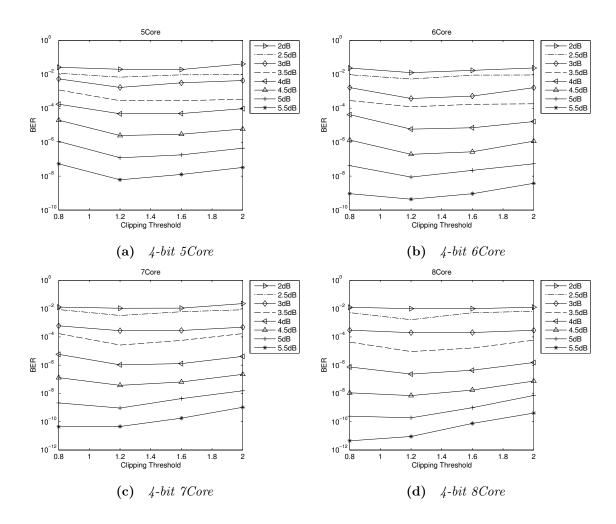

|     | LDPC-CC code using clipping thresholds from 1 to 2 during quantization.         | 63 |

- 6.2 Information BER at  $E_b/N_0$  of 2 dB to 5.5 dB for configurations with 5 to 8 decoder cores on DE4 with 4-bit LLRs at a 75MHz clock with coded throughput of 2.4 Gbit/s for the  $T_s = 192$ ,  $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-CC code using clipping thresholds from 0.8 to 2 during quantization. . . . 64

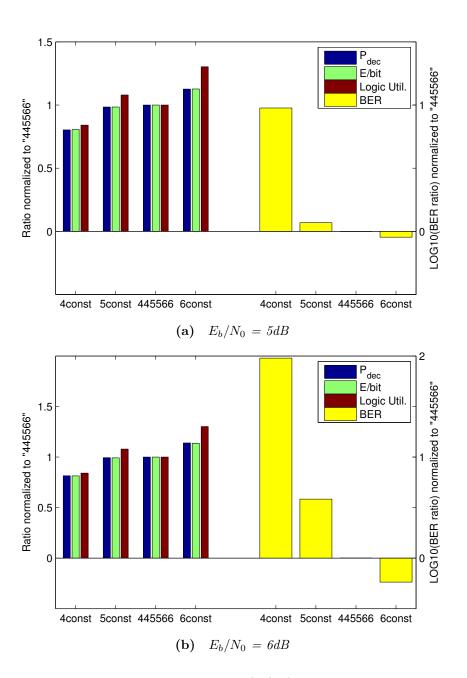

- 6.5 Decoder power, energy-per-coded-bit (E/bit), Logic Utilization, BER normalized to that of the "445566" case. The decoder power and energy-per-coded-bit values are based on the "mapped" values from the DC/DC converter efficiency experiment.

70

| A.1 | Create a new SOPC system                                             | 89 |

|-----|----------------------------------------------------------------------|----|

| A.2 | Clock settings for SOPC                                              | 89 |

| A.3 | Configure JTAG to Avalon Master Bridge                               | 91 |

| A.4 | Connect components for SOPC system                                   | 91 |

| A.5 | HDL code for connecting SOPC system                                  | 92 |

| A.6 | Modelsim message after loading the design                            | 93 |

| A.7 | Returned value on <b>System Console</b> after a <i>read</i> command  | 94 |

| A.8 | Returned value on <b>System Console</b> after a <i>write</i> command | 94 |

# Nomenclature

| ASIC    | Application-Specific Integrated Circuit |

|---------|-----------------------------------------|

| AWGN    | Additive White Gaussian Noise           |

| BER     | Bit-Error-Rate                          |

| BPSK    | Binary Phase-Shift Keying               |

| FIFO    | First-In First-Out                      |

| FPGA    | Field-Programmable Gate Array           |

| LDPC    | Low-Density Parity-Check                |

| LDPC-BC | LDPC Block Codes                        |

| LDPC-CC | LDPC Convolutional Codes                |

| LFSR    | Linear Feedback Shift Register          |

| LLR     | Log-Likelihood Ratio                    |

|         |                                         |

PN-LDPC-CC Parallel-Node Low-Density Parity-Check Convolutional-Code

Tcl Tool Command Language

| Н         | Parity-check matrix (PCM)                        |

|-----------|--------------------------------------------------|

| $E_b/N_0$ | Energy-per-bit divided by spectral noise density |

| ρ         | node-parallelization factor                      |

| $T_s$     | code period                                      |

| $T'_s$    | group period, $T_s/\rho$                         |

## Chapter 1

# Introduction

### 1.1 Motivation

The goal of forward error control is to minimize the net error rate of a communications channel and to improve the overall efficiency of data transmission over noisy channels by adding redundancy to data to avoid complete data retransmission. Low-density paritycheck (LDPC) codes, in particular, are a class of linear error correcting codes which were first proposed by Gallager in 1962 [3]. LDPC block codes (LDPC-BC) are characterized by a seemingly random parity-check matrix, known as the H matrix, with mostly 0's and a small fixed number of 1's. However, despite its high performance, the decoding of LDPC codes was impractical to implement due to limitations imposed by the processing capabilities available at the time.

After being forgotten, LDPC codes were rediscovered by MacKay and Neal [4]. Through the use of a probabilistic decoding algorithm, LDPC codes were proven to perform substantially better than standard convolutional codes could, and their performance approaches Shannon's theoretical channel capacity limit [5]. Since then, LDPC codes have become one of the most intensive research areas in coding theory. There has been a lot of research done to analyze the behaviour and performance of LDPC codes over different channels (e.g. binary erasure channel, binary symmetric channel, additive white Gaussian noise channel) and under various constraints. Various approaches have been taken to design and construct good LDPC codes to achieve channel capacity-approaching performance [6]. LDPC codes have since been widely adopted in numerous digital communications standards, such as the 10GBase-T Ethernet (IEEE 802.3an), wireless-N network standard (IEEE 802.11n), IEEE 802.16e, DVB-S2, an enhanced specification for digital video broadcasting, and wireless personal area network (802.15.3c). Numerous designs of LDPC block code decoders have been shown in recent literature to achieve a decoding throughput in the range of multi-Gb/s through optimizations in decoding algorithms, architecture, and code construction [7, 8, 9, 10, 11, 12, 13, 14].

Turbo codes are another family of popular error-correction codes with capacity-approaching performance, which were first introduced in 1993 [15]. In parallel with the development of LDPC codes, there has also been a lot of active research done in the area of turbo codes. They have been incorporated in 3G and 4G mobile telephony standards such as HSPA, EV-DO and LTE, as well as in other standards, such as WIMAX standard (IEEE 802.16), and DVB-RCS, a specification for interactive satellite communication system. Numerous turbo decoders with Gbit/s performance have been reported in literature [16, 17, 18, 19].

LDPC convolutional codes (LDPC-CC), on the other hand, were first proposed in [20] as a convolutional variant of the original LDPC codes, and past studies have shown that welldesigned LDPC-CCs have the same capacity-approaching BER performance as LDPC-BCs [20, 21]. The flexibility to handle frames of arbitrary lengths, a characteristic shared with convolutional codes, makes LDPC-CC a suitable candidate for practical implementations of communication scenarios, such as video streaming and packet-switching networking. LDPC-CCs have been incorporated in the next-generation High Definition Power Line Communication (HD-PLC) specification [22], and it has also been proposed for use in Global Navigation Satellite System (GNSS) along with its block-code variant [23]. The implementation of LDPC-CC encoding has also been shown to be simpler than its block-oriented counterpart [24, 25]. Recent literature on LDCC-CC-based decoders has also demonstrated the ability to achieve Gbit/s decoding throughput [26, 27, 28].

Past implementations of LDPC decoders have mostly used Field Programmable Gate Arrays (FPGA) as an intermediate tool to prototype their designs instead of targeting it as the final platform [29, 30, 31], because of its relatively slower clock speed, larger area and higher power consumption compared to full-custom application-specific integrated-circuit (ASIC) implementation. However, FPGA does provide much faster turnaround time than ASIC. Therefore, it would be interesting to consider the feasibility of using state-of-the-art FPGAs as final design platform. Recent literature on LDPC decoders implemented on FPGAs has shown improvements in decoding throughput and some of them have even been shown to achieve throughput in the range of several Gigabits per second (Gbit/s) [32, 33, 31, 34]. However, the lack of reported power measurement figures from existing FPGA implementations of LDPC decoder designs has made it difficult to analyze the gap in power consumption between FPGA implementations and ASIC implementations of LDPC decoders, and to explore FPGA-specific architectural tradeoffs.

This thesis presents an FPGA implementation of a parallel-node low-density-paritycheck-convolutional-code (PN-LDPC-CC) decoder and a set of detailed power measurement data conducted using a simple power measurement set-up. This work verifies the ability of an FPGA-based PN-LDPC-CC decoder to achieve decoding throughput in the Gbit/s range while consuming a reasonable amount of power, which demonstrates the feasibility of using FPGA as a final design platform. Architectural tradeoffs of the PN-LDPC-CCs are further investigated, and further experiments have also been conducted to quantify the effect of clipping thresholds, bit width for each processor core on BER performance, power consumption, logic utilization of the decoder. A "6Core" decoder with growing bit-width LLRs has been found to have a BER performance near that of a "6Core" 6-bit decoder. while consuming similar power, and logic utilization to that of a 5-bit "6Core" decoder.

### 1.2 Thesis Organization

This thesis is organized as follows. Chapter 2 includes the background on LDPC-BC as well as LDPC-CC, and the gap between FPGA and ASIC implementation, and a summary of performance results from the existing ASIC and FPGA LDPC decoders. Chapter 3 presents a background on the PN-LDPC-CC encoder and decoder architectures as well as the other system modules implemented in our experiment. Chapter 4 provides a description of the power measurement method employed for further power characterization of our system. Chapter 5 presents the measurement results of our FPGA implementation and the resulting discussion. Chapter 6 presents the results from a performance optimization of the decoder by varying the clipping threshold, precision of each decoder processor core. Conclusions, contributions, and further research directions are presented in Chapter 7.

## Chapter 2

## Background

This chapter first presents a description on LDPC, decoding of LDPC and LDPC-CC codes respectively in Section 2.1 to 2.3. Then a general background on the gap between FPGA and ASIC implementation is outlined in Section 2.4 along with a summary of the performance results from existing ASIC and FPGA implementations of LDPC decoders.

#### 2.1 LDPC Definitions

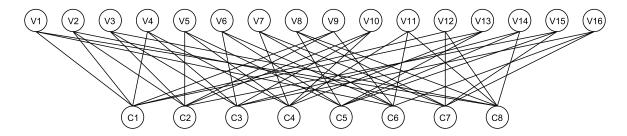

Low-density parity-check (LDPC) codes are a class of linear error-control codes, which were first introduced in 1962 [3]. An LDPC code is a linear block code of rate R = k / n, characterized by a sparse (n - k) by n parity-check matrix, H. The length of the code is denoted by n, the number of message bits is denoted by k, and (n - k) is the number of the parity (redundant) bits in the codeword. An example for a rate-1/2 LDPC code with n = 16 and k = 8 is shown in Figure 2.1. All the valid codewords x of an LDPC code must satisfy the constraint  $Hx^T = 0$ . An LDPC code can also be represented by a bipartite graph, known as the Tanner Graph [35]. The corresponding Tanner Graph for the H matrix in Figure 2.1 is depicted in Figure 2.2. Each codeword bit corresponds to a variable node, labeled  $v_i$ , and each parity bit corresponds to a check node, labeled  $c_i$ . Each entry  $h_{ij}$  of 1 in the H matrix corresponds directly to an edge (or connection) between variable node i and check node j in its graphical representation.

The *H* matrix of a *regular* LDPC code contains a fixed number of of 1's in each column, denoted by  $d_v$ , and a fixed number of 1's in each row, denoted by  $d_c$ . In other words, for a regular LDPC code, the number of edges connected to a check node and the number of edges connected to a variable node are constant. An *irregular* LDPC, on the other hand, has nodes of varying degrees defined by a degree distribution. Although LDPC codes are block codes, there also exist LDPC convolutional codes (LDPC-CC), which are further described in Section 2.3.

Figure 2.1: Example of H matrix for a rate-1/2 LDPC code with n = 16, k = 8

**Figure 2.2:** Tanner graph representation of the H matrix in Figure 2.1. Variable nodes are shown on top, and check nodes at the bottom

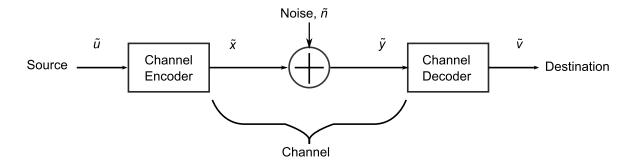

Figure 2.3: Basic Communication System. Channel modulator and demodulator are not shown in the picture.

### 2.2 LDPC Decoding

In a basic communication system, as depicted in Figure 2.3, an information message  $\tilde{u}$  is encoded by the channel encoder to a coded sequence  $\tilde{x}$  with added redundancy to provide error protection. The coded sequence  $\tilde{x}$  is then modulated by the modulator to allow transmission through the channel, where it gets distorted by noise. At the receiving side, the received signal is demodulated by the demodulator. The demodulated sequence  $\tilde{y}$  then goes through the channel decoder, where it gets decoded into received encoded message,  $\tilde{v}$ , and sent to destination.

For an LDPC decoder, the received channel messages are expressed in the form of

log-likelihood-ratios (LLRs), which represent the scaled and quantized channel samples of original encoded data with added noise scaled according to a  $E_b/N_0$ , the ratio of the energyper-transmitted bit versus the spectral noise density. An LLR is defined by Equation 2.1, where  $P(x_i = 0/1|y_i)$  is the probability that  $x_i$  is zero or one respectively knowing the value of  $y_i$ , for an additive white Gaussian noise (AWGN) channel based on binary phase-shift keying (BPSK) modulation scheme. Equation (2.4) describes the operation at the variable node that computes the final decoder outputs.

$$LLR_{i}(y) = \ln \frac{P(x_{i} = 0|y_{i})}{P(x_{i} = 1|y_{i})}$$

(2.1)

LDPC codes can be iteratively decoded using the Sum-Product Algorithm (SPA), which is a general-purpose algorithm for probabilistic inference based on factor graphs [36]. The variable-node and check-node operations of SPA can be generalized in Equation (2.2) and (2.3), where  $L_i^0$  represents the initial received LLR at variable node i,  $\lambda_{i\to j}$ represents an LLR from variable node i to check node j,  $L_{j\to i}$  represents an LLR from check node j to variable node i,  $d_c$  denotes degree of the current check node, and  $d_v$  denotes the degree of the current variable node.

$$\lambda_{i \to j} = L_i^0 + \sum_{\substack{k=1\\k \neq j}}^{d_v} L_{k \to i}$$

$$(2.2)$$

$$L_{j \to i} = 2 \tanh^{-1} \left( \prod_{\substack{k=1\\k \neq i}}^{d_c} \tanh\left(\frac{\lambda_{k \to j}}{2}\right) \right)$$

(2.3)

$$\lambda_{i \to j}^{n} = L_{i}^{0} + \sum_{k=1}^{d_{v}} L_{k \to i}$$

(2.4)

Let  $y_i$  denote the received message at variable node  $i, i \in \{1, d_v\}$ , from an AWGN channel. The SPA decoding procedure can be described as the following steps, where the extrinsic principle of excluding self-message is applied at both the check-node and variable-node operations:

- 1. Set n = 0. Initialize LLR  $L_i^n$  as  $\frac{2}{\sigma_N^2}y_i$  for each variable node *i*, where  $\sigma_N$  is the noise variance and  $\sigma_N^2 = \frac{N_0}{2}$ , where  $N_0$  is the noise power spectral density.

- 2. Variable node LLRs are passed along all edges to the connected check nodes as inputs: $\lambda_{i\to j} = L_i^n$ , where  $j \in \{1, d_c\}$ .

- 3. At the check node, the outgoing LLR sent from the current check node j along the edge to each connected variable node i is computed using Equation (2.3).

- 4. At the variable node, the outgoing LLR sent from the current variable node i to each connected check node j is computed using Equation (2.2).

- 5. The result for the current decoding iteration n is  $\lambda_{i \to j}^n$ , the sum of the result of the variable node computations, computed using the Equation (2.4).

- 6. If  $\lambda_{i \to j}^n$  satisfies the constraint  $\lambda_{i \to j}^n \cdot H^T = 0$  or a fixed number of iterations are reached, terminate decoding and output the current result. If neither condition is met, set n = n + 1, return to Step 2 to start the next iteration.

However, while being capable of achieving excellent bit-error-rate (BER) performance, the implementation of the SPA has been shown to be rather demanding of hardware resources, because it is an iterative numerically intensive algorithm that performs arithmetic operations on real-valued information of large blocks of data. However, the SPA is an inherently parallel algorithm. A good alternative to SPA is the Min-Sum algorithm [37, 38, 39], which is an approximation of the SPA that offers reduced complexity. The simplification of the SPA is achieved by approximating the check-node operation depicted in Equation 2.3 with the operation described in Equation 2.5 instead, where the magnitude of the outgoing message on edge i is the minimum of the incoming message magnitudes excluding the one from edge i, and its sign is the XOR of the signs of the incoming messages except the one from edge i.

its inherent parallelism,

$$L_{j \to i} = \left(\prod_{\substack{k=1\\k \neq i}}^{d_c} sign\left(\lambda_{k \to j}\right)\right) \times \min_{\substack{k=1,\dots,d_c\\k \neq i}} |\lambda_{k \to j}|$$

(2.5)

This approximation eliminates the use of LUTs to implementation *tanh* calculations, which in turn reduces the complexity in hardware implementation. However, a loss of up to 1.03 dB is observed in decoding performance after the application of the min-sum approximation [40]. There also exists a number of modifications proposed for the original min-sum approximation, such as the offset min-sum algorithm and the normalized min-sum algorithm, which both perform very close to the ideal sum-product algorithm or even outperform that in some cases, but have hardware complexity closer to that of min-sum algorithm [39].

### 2.3 LDPC-CC Definitions

LDPC convolutional codes (LDPC-CC) were first proposed in [20]. An LDPC-CC bears the same characteristics as conventional convolutional codes, where a current code bit depends on present and previous information bits only. An LDPC-CC can be characterized by

$$H^{T} = \begin{bmatrix} \ddots & \ddots & & & & & \\ & H_{m_{s}}^{T}(t) & \cdots & H_{0}^{T}(t) & & & \\ & & \ddots & \vdots & \ddots & \\ & & & H_{m_{s}}^{T}(t+m_{s}) & \cdots & H_{0}^{T}(t+m_{s}) \\ & & & \ddots & \vdots & \ddots \end{bmatrix}$$

Figure 2.4: H matrix for LDPC-CC. Note the diagonal band structure of non-zero elements.

a parity-check matrix, H. However, unlike LDPC block codes (LDPC-BC), which have finite-length parity-check matrices, the parity-check matrix for LDPC-CC in infinite in length. Like LDPC-BC, all of the valid codewords w of an LDPC-CC must satisfy the condition, where  $wH^T = 0$ . The transposed form of the H matrix for an LDPC-CC with the rate R = b / c (b < c) is shown in Figure 2.4, where the  $H_i^T(t)$   $(i = 0, 1, ..., m_s)$ represents the periodic time-varying sub-matrices of size  $c \times (c-b)$  and the parameter  $m_s$  is called the code memory. For a finite code period  $T_s$ ,  $H_i^T = H_i^T (t + T_s)$  for all i and t. If  $T_s = 1$ , the LDPC-CC is considered time-invariant, else time-varying. The overall constraint length of the rate -b / c LDPC-CC is defined as  $\nu = c \times (m_s + 1)$ . For regular LDPC-CCs, both the column weight (K) and the row weight (J) of  $H^T$  are constant, and such a code can be referred to as an  $(m_s, J, K)$  LDPC- CC code. For a  $(m_s, J, K)$  code, the column weight (K) defines the number of LLRs entering check-node from the variable-node, while the row weight (J) defines the number of LLRs entering each variable-node from the check-nodes. While the LDPC decoding algorithms described in Section 2.2 still apply for LDPC-CC, the iterations are realized as pipelined "processor cores". Additional parallelism can be achieved through design of the LDPC-CC code to allow the encoding and decoding of  $\rho$  information bits per cycle, as demonstrated in [26], where  $\rho$  is defined as the parallelization ratio.

### 2.4 State-of-the-art LDPC Decoders

An LDPC decoder can be implemented in a digital Application-Specific Integrated Circuit (ASIC) or Field-Programmable Gate Array (FPGA). There have also been analog implementations of LDPC decoders [41, 42]. Digital ASIC implementation is usually preferred as it provides higher clock frequency, smaller area and lower power consumption than FPGA implementation. In a recent paper, Kuon and Rose presented experimental measurements of area, speed, and power consumption to analyze the gap between ASICs and FPGAs [43]. They suggest that by making use of the available hard heterogeneous blocks (such as memory, DSP blocks) on FPGAs, the resulting gap in area can be narrowed, as can the gap in power consumption. However, they also suggest that the possibility of narrowing the gap in clock speed performance would depend largely on how well the designs are tailored to the functionality of the DSP block.

The performance of several state-of-the-art ASIC-based LDPC decoders that is reviewed in Section 2.4.1. Preference is given to designs with reported power measurements to demonstrate the trend of power consumptions of ASIC-based LDPC decoders. A summary of several Gbit/s FPGA decoders is also provided in Section 2.4.2.

#### 2.4.1 ASIC-based LDPC Decoders

An LDPC decoder that supports four code rates of IEEE 802.15.3c applications is presented in [13]. The proposed decoder utilizes row-based layered scheduling, and achieves a maximum throughput of 5.79 Gbit/s at a clock frequency of 197 MHz. Darabiha *et al.* introduced a highly-parallel decoder architecture with low routing overhead and proposed a method to detect early convergence of iterative decoder to allow reduction in dynamic power [9]. A bit-serial fully-parallel LDPC decoder employing the proposed architecture and optimization is reported to achieve a total throughput of 3.3 Gbit/s. A Reed-Solomonbased LDPC (RS-LDPC) decoder suitable for 10GBASE-T Ethernet is presented in [14]. The resulting decoder delivers a throughput of 47.7 Gbit/s at a clock frequency of 700 MHz, and is capable of achieving a BER of  $10^{-14}$  at SNR of 5.5 dB with the use of a post-processing algorithm. to Lastly, an LDPC-CC decoder fabricated in a 90-nm process is reported to achieve 2.37 Gbit/s at a clock frequency of 198 MHz [28]. The proposed decoder employs the on-demand variable node activation scheduling to improve convergence speed, and a node-level optimization to increase decoding throughput. A summary of the results from the aforementioned ASIC-based LDPC decoders is included in Table 2.1.

#### 2.4.2 FPGA-based LDPC Decoders

Darabiha *et al.* introduced a bit-serial decoding scheme that addresses the issue in interconnect complexity in fully parallel implementations of LDPC decoders, along with a simplified check node architecture [29]. The reduction in interconnect complexity is achieved by allowing the multi-bit messages to be communicated between variable node and check node over single wires. The viability of both ideas is demonstrated on a fully parallel FPGA implementation of a (480, 355) Reed-Solomon-based LDPC decoder, which has been shown to achieve a decoding throughput of 650 Mbps at a clock frequency of 61 MHz. A fully parallel LDPC decoder based on revised stochastic decoding was presented by Tehrani *et al.* [30]. The method of noise-depending-scaling (NDS) and the use of edge memories (EM) have been applied to the original stochastic decoding scheme [44]. The resulting decoder has been shown to achieve a decoding throughput of 706 Mbps at a signal-to-noise ratio of 3 dB. In addition to the methods of NDS and of EM, internal memories (IMs) are used for each subnode in the high-degree variable nodes to reduce the

|                              | [13]                  | [6]                       | [14]                   | [28]                |

|------------------------------|-----------------------|---------------------------|------------------------|---------------------|

| CMOS Technology              | 65-nm                 | 130-nm                    | 65-cm                  | 90-cm               |

| Type of LDPC Code            | LDPC-BC               | LDPC-BC                   | LDPC-BC                | LDPC-CC             |

| LDPC Code                    | (672, k) k=336,       | (660, 480)                | (2048, 1723)           | (491, 3, 6)         |

|                              | 420,504,588           |                           |                        |                     |

| Code Rate                    | 1/2, 5/8, 3/4, 7/8    | 0.74                      | 0.84                   | 1/2, 	2/3,          |

|                              |                       |                           |                        | 3/4, 4/5, 5/6       |

| Core Area $[mm^2]$           | 1.56                  | 7.3                       | 5.35                   | 2.24                |

| Iteration or Processor Count | 5                     | 15                        | 8                      | IJ                  |

| Input Quantization           | 4-bit                 | 4-bit                     | 4-bit                  | 6-bit               |

| BER                          | $10^{-6}$ at 9 dB for | $< 10^{-8}$ at 5.5 dB     | $< 10^{-12}$ at 5.5 dB | $10^{-5}$ at 2.5 dB |

|                              | k = 588, 16-QAM       |                           |                        |                     |

|                              | modulation            |                           |                        |                     |

| Supply Voltage [V]           | 1                     | 1.2                       | 1.2                    | 1  V                |

| Clock Fequency [MHz]         | 197                   | 300                       | 002                    | 198                 |

| Throughput [Gbit/s]          | 39.9                  | 3.30                      | 47.7                   | 2.37                |

| Power [mW]                   | 450                   | 398                       | 2800                   | 284                 |

| Energy Efficiency [pJ/bit]   | 11.3                  | $120 \pmod{\text{coded}}$ | 58.7                   | 0.12                |

Table 2.1: Summary of ASIC-based Implementation Results

occurrence of the hold state in a high-degree variable node [32]. A 1.66 Gbit/s fully parallel stochastic decoder based on the irregular WiMAX (1056, 528) LDPC code using the aforementioned techniques has been shown to achieve a BER of  $10^{-8}$  at an  $E_b/N_o$  of 4.25 dB. In [33], an FPGA-based decoder based on the 1200-bit rate-1/2 LDPC code using a modified min-sum algorithm has been shown to achieve a decoding throughput of 6 Gbit/s. Chandrasetty *et al.* proposed a modified 2-bit Min-Sum Algorithm (MMS2), which is implemented on an FPGA-based LDPC decoder that achieves an average throughput of 10.2 Gbit/s at an  $E_b/N_o$  of 4dB [31]. The difference between the proposed MMS2 algorithm and the traditional Min-Sum algorithm lies in the variable node operation. In MMS2, the variable node operation involves an additional mapping step that maps the computed sum in higher precision to a 2-bit message to be passed to the check node. The mapping is based on a threshold value obtained from Monte-Carlo simulations.

FPGA-specific architectural techniques named vectorization and folding are proposed by Chen et al. in [34] for quasi-cyclic LDPC decoders. Vectorization takes advantage of the configurable data width of embedded memory on FPGAs by packing multiple messages into the same physical word, which is loaded and stored simultaneously. However, to concurrently process the messages delivered in each memory access and to take care of the data alignment and addressing, additional logic resources are needed. The extra required hardware resources may result in degraded performance, or it may not even fit on the FPGA due to the alignment logic and interconnect complexity. An additional tool, named QCSyn, which synthesizes a vector architecture for a given quasi-cyclic code, is also developed to ensure high resource utilization. Folding, on the other hand, is a memory virtualization technique that allows large LDPC codes to be implemented on commercially-available FPGAs with a small number of available block RAMs by mapping messages corresponding to multiple sub-matrices in the same physical block RAMs. Results of all the aforementioned implementations based on FPGAs are presented in Table 2.2. None of the included implementations have reported any power values with the exception of the *vectorization*-based implementation [34], which has not identified how power values were obtained. Therefore, this thesis focuses on the power characterization of an FPGA-based LDPC-CC decoder. The next chapter describes the architecture of our FPGA implementation of the PN-LDPC-CC, and detailed power measurement set-up is provided in Chapter 4.

| Ref.                           | [29]              | [30]                 | [32]                 | [34]                 | [34]                | [31]                 | [33]                 | This work               |

|--------------------------------|-------------------|----------------------|----------------------|----------------------|---------------------|----------------------|----------------------|-------------------------|

| FPGA                           | Stratix           | Virtex4 <sup>2</sup> | Virtex4 <sup>2</sup> | Virtex4 <sup>2</sup> | Virtex4             | Virtex4 <sup>2</sup> | Virtex4 <sup>2</sup> | Stratix IV              |

|                                | EF 1380           |                      |                      |                      | AC4VLA10U           |                      |                      | EF45GA230               |

| LDPC                           | RS-based          | (1024,               | Irregular            | Irregular            | (8176,              | Regular $(3,$        | PEG-based            | PN-LDPC-                |

| Code                           | (480,             | 512)                 | (1056,               | (3969,               | 7156) QC            | (9)                  | (6,3)                | $CC (3,6) T_s$          |

|                                | 355)              |                      | 528)                 | 3213) QC             |                     |                      |                      | = 192                   |

| $f_{CLK}$                      | $61 \mathrm{MHz}$ | $212 \mathrm{MHz}$   | $222 \mathrm{~MHz}$  | 195.7 MHz            | 212.2  MHz          | $123 \mathrm{~MHz}$  | $100 \mathrm{MHz}$   | $75 \mathrm{MHz}$       |

| Throughput                     |                   | 706                  | 1.66                 | 1.474                | 713.8               | 10.2  Gbit/s         | 12  Gbit/s           | 2.4  Gbit/s             |

|                                | Mbit/s            | Mbit/s               | Gbit/s               | Gbit/s               | Mbit/s              |                      |                      |                         |

| BER                            | 1                 | $10^{-6}$ at 3       | $10^{-8}$ at         | 1                    | $10^{-12}$ at       | $10^{-5}$ at 3.9     | 1                    | $10^{-8}$ at            |

|                                |                   | $^{\mathrm{dB}}$     | 4.25  dB             |                      | $4.25~\mathrm{dB}$  | $^{\mathrm{dB}}$     |                      | $4.25~\mathrm{dB}$      |

| # of Iter.                     | 15                | 15                   | ı                    | 15                   | 15                  | 1                    | 10                   | 9 (proc.)               |

| Logic Uti-                     | 66588             | 1                    | 1                    | 1                    | 1                   | 1                    | 1                    | 83%                     |

| lization                       | (84%)             |                      |                      | _                    |                     |                      |                      |                         |

| Slices                         | 1                 | 32875                | 46097                | 62362                | 17856               | 33345                | 40613                | 1                       |

|                                |                   |                      |                      | (20%)                | (26%)               |                      | (45%)                |                         |

| Slice FF                       | I                 | I                    | I                    | 68003                | 27210               | 15691                | 18945                | 1                       |

|                                |                   |                      |                      | (55%)                | (20%)               |                      | (10%)                |                         |

| 4-1/P LUTs                     | ı                 | ı                    | I                    | 111035               | 27046               | 58,053               | 69038                | ı                       |

|                                |                   |                      |                      | (62%)                | (20%)               |                      | (38%)                |                         |

| Block RAM                      | I                 | I                    | I                    | $330 \ (98\%)$       | 80(28%)             | I                    | 1                    | I                       |

| Power                          | I                 | I                    | I                    | 7632  mW             | $3033 \mathrm{~mW}$ | I                    | 1                    | $4105~\mathrm{mW}^{-1}$ |

| Energy/bit                     | I                 | I                    | I                    | 5.18  nJ             | 4.25  nJ            | I                    | I                    | $1.71 \text{ nJ}^{-1}$  |

| <sup>1</sup> Measured raw data | ram data          |                      |                      |                      |                     |                      |                      |                         |

Table 2.2: Summary of FPGA Implementation Results

<sup>1</sup> Measured, *raw data* <sup>2</sup> XC4VLX200

17

## Chapter 3

## **FPGA** Implementation

This chapter first provides a brief summary on Parallel-Node Low-Density Parity-Check Convolutional Codes (PN-LDPC-CCs) in Section 3.1. Then a detailed description on the architecture of the PN-LDPC-CC-based encoder and decoder implemented is provided in Section 3.2 and 3.3. Lastly, an overview of the remaining modules of the system implemented on FPGA is presented in Section 3.4.

### 3.1 PN-LPDC-CC

Architecture-aware PN-LDPC-CCs were initially developed by Chen *et al.* [26]. Both implementation-oriented constraints and performance-oriented constraints are applied in the construction of PN-LDPC-CCs to allow parallelism in the encoder and decoder architecture and to also ensure BER performance of the code. For PN-LDPC-CC, the parity-check matrix  $H^T$  is organized into groups of sub-matrices  $H_{i'}^T(t')$  of size  $\rho \times \rho$ , where  $\rho$  is defined as the node-parallelization factor, for parallel processing. The code period  $T_s$  and code

$$H_{i'}^{T}(t') = \begin{bmatrix} H_{i\cdot\rho+\rho-1}^{T}(\rho\cdot t) & H_{i\cdot\rho+\rho-1}^{T}(\rho\cdot t+1) & \cdots & H_{i\cdot\rho+\rho-1}^{T}(\rho\cdot t+\rho-1) \\ H_{i\cdot\rho+\rho-2}^{T}(\rho\cdot t) & H_{i\cdot\rho+\rho-2}^{T}(\rho\cdot t+1) & \cdots & H_{i\cdot\rho+\rho-2}^{T}(\rho\cdot t+\rho-1) \\ \vdots & \vdots & \ddots & \vdots \\ H_{i\cdot\rho}^{T}(\rho\cdot t) & H_{i\cdot\rho}^{T}(\rho\cdot t+1) & \cdots & H_{i\cdot\rho}^{T}(\rho\cdot t+\rho-1) \end{bmatrix}$$

Figure 3.1: Sub-matrice  $H_{i'}^T(t')$  for PN-LDPC-CC

memory  $m_s$  are also measured in terms of such groups, where the group period,  $T'_s$ , is defined as the ratio of  $T_s/\rho$ , and group memory,  $m'_s$ , is defined as  $m_s/\rho$ , hence,  $T_s$  and  $m_s$ must be multiples of  $\rho$  by design. The phase parameter,  $\phi, \phi \in [0, T_s)$ , refers to the specific row in the parity-check matrix, is also used to specify check constraints at each instant in time. Additionally, for PN-LDPC-CC, a new parameter group phase,  $\phi', \phi \in [0, T'_s)$  is introduced. The mapping from  $H^T_i(t)$  to  $H^T_{i'}(t')$  is shown in Figure 3.1.

In [1], it is shown that  $\rho$  can be increased significantly with little impact on the BER performance, and the main factors affecting BER performance are code period  $(T_s)$  of the code and the decoding algorithm.

A series of circuit optimizations to the PN-LDPC-CC encoder/decoder architecture presented in [26] and the corresponding synthesis results in terms of energy-per-encodedbit versus throughput and area versus throughput for each improvement are reported by Brandon in [1]. The throughput for both the encoder and the decoder is be defined as the product of clock frequency and node parallelization factor,  $\rho$ , divided by the rate of LDPC-CC code, R, as shown in Equation (3.1).

$$N_{enc/dec\,Throughput} = \frac{f_{clk} \times \rho}{R} \tag{3.1}$$

Our implementation of the PN-LDPC-CC encoder and decoder is based on a preexisting PN-LDPC-CC architectures by Brandon [1], which are described in details in Section 3.2 and 3.3.

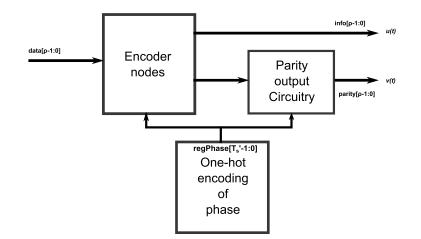

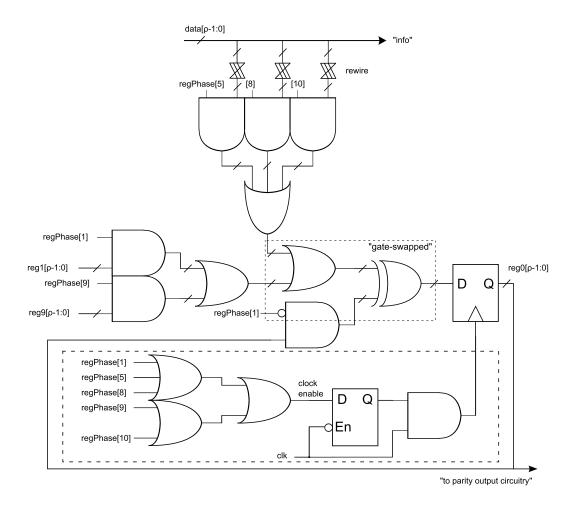

### 3.2 PN-LDPC-CC Encoder

A high-level architecture of the PN-LDPC-CC-based encoder implemented in our studies is depicted in Figure 3.2. The input data[ $\rho$ -1:0] is connected to each register bank regX[ $\rho$ -1:0],  $X \in \{0, T'_s\}$  of the  $T'_s$  encoder nodes, where  $T'_s$  is the group period of the PN-LDPC-CC, and  $\rho$  is the parallelization ratio of the code. An example of a single encoder node based on a  $T_s = 192$ ,  $\rho = 16$ , rate-1/2 (3, 6) PN-LDPC-CC is shown in Figure 3.5. The data in the encoder node is updated according to the regPhase[ $T'_s$ -1:0] signals, but remains in the flip-flop until it gets replaced in the next period. The parity output, v(t), is then actively chosen from one set of the  $T'_s$  encoder node registers based on the regPhase signals, as shown in the parity output circuitry in Figure 3.4. For a given rate-1/2 PN-LDPC-CC code with  $\rho = 16$ , the encoder outputs 16 information bits, u(t), and 16 parity bits, v(t), per clock cycle.

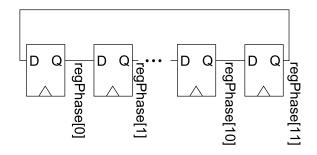

The group of phase signals, regPhase, is shown in Figure 3.2 and 3.5, which control the "info" and "parity" updates, are created with one-hot encoding logic, where only one register is being set upon the reset of the encoder, as depicted in Figure 3.3.

As shown in Figure 3.5, the register bank inside each encoder node is implemented as a circular buffer, where it is constrained so that it becomes the next register bank in the next phase, and the input data accepted by the constrained register bank is unique to each phase.

The output parity vector, v(t), is multiplexed out from one of the  $T'_s$  register banks with width of  $\rho$  based based on the phase specified by the regPhase signals, as shown in

Figure 3.2: A high-level block diagram of the implemented PN-LDPC-CC encoder. An example of a single encoder node is shown in Figure 3.5. The one-hot encoding of the phase signal is shown in Figure 3.3. Figure 3.4 depicts the parity output circuitry.

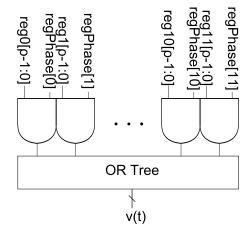

Figure 3.3: One-hot encoding of the phase signal for the  $T_s = 192$ ,  $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-CC, group period  $T'_s = 12$ . [1]

Figure 3.4: Parity output circuitry for the  $T_s = 192$ ,  $\rho = 16$ , rate-1/2 (3,6) PN-LDPC-CC, group period  $T'_s = 12$ . [1]

The presented encoder node shown in Figure 3.5 includes two optimizations by Brandon [1], which are outlined in Section 3.2.1 and 3.2.2.

### 3.2.1 Gate-Swapping

The technique named "gate-swapping" is applied to the design of the encoder node. It conditionally swaps the 3-input XOR with a simpler 2-input XOR and a 2-input OR gate when the phase-gated data ("info") and register ("parity") updates inside an encoder node do not occur in the same phase [1]. In Figure 3.5, an encoder node that meets the requirement for "gate-swapping" is depicted. The "gate-swapped" area shown in Figure 3.5 is where the swapping takes place. It can be seen that the regPhase signals, which control the "info" updates in this depicted encoder node are regPhase[5], regPhase[8], and regPhase[10]. The signals that control the "parity" update are regPhase[1] and regPhase[9].

Figure 3.5: A single encoder node from the implemented architecture in this thesis for the  $T_s = 192, \ \rho = 16, \ rate-1/2 \ (3,6) \ PN-LDPC-CC. \ [1]$

In this case, the phase signals controlling the "info" and the "parity" updates in this encoder node are different; so this allows these phase-gated data and register updates to be combined with a 2-input OR gate, and the result of that is then fed into a 2-input XOR gate. However, in the cases, where the "info" and "parity" updates are controlled by the same phase signals, the 3-input XOR cannot be replaced by a 2-input OR gate and a 2input XOR. The number of occurrence of simultaneous "info" and "parity" updates varies among all PN-LDPC-CCs. A consistent small reduction in power and area is observed by Brandon among the implemented encoders based on various PN-LDPC-CCs with the application of this technique in [1].

#### 3.2.2 Clock-gating

Latch-based clock-gating [45] is applied to the encoder node design. As depicted at the bottom portion of Figure 3.5, the regPhase phase signals associated with for that particular encoder node are ORed together and the result is latched. The clock is ANDed with the output of the latch to form a new clock signal that controls the encoder-node registers. Brandon noted in [1] that the phase signals have switching rates of  $1/2 \cdot T'_s$  per clock cycle and the clock switches once per cycle, so gating the clock with the phase signals can lead to a reduction in dynamic power. A significant reduction in power consumption for all PN-LDPC-CCs using the resulting architecture is observed [1].

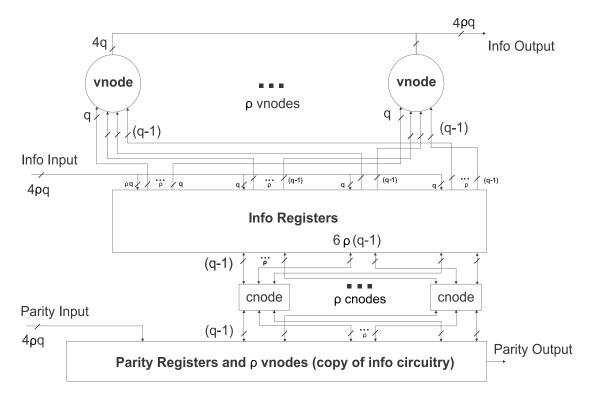

## 3.3 PN-LDPC-CC Decoder

The decoder implemented in our design is formed by cascading identical decoder processors in series. A single decoder processor consists of  $2\rho$  variable-node (vnode) units,  $\rho$  checknode (cnode) units and multiple memories for storage purpose. Figure 3.6 depicts a highlevel architecture of a single decoder processor for a rate-1/2 (3, 6) PN-LDPC-CC.

The operation of a decoder processor can be described as follows: as shown in Figure 3.6, the processor takes in channel LLRs or the information and parity LLRs from a previous decoder processor and stores them in the respective info and parity registers. The information/parity input databus has a initial bit-width of  $4\rho q$ , where 4 represents the degree of the variable node,  $\rho$  is the node parallelization factor and q is the bit-width of the LLRs. With the application of TMS, the LLR bit-width of storage elements is reduced by 1 bit by dropping the LSB, with the exception of the channel samples, as denoted in Figure 3.6. LLRs from the info and parity registers are read and routed to the appropriate check-node units in each phase. The processed LLRs from the check-node operations are then written back to the same registers that they were read from, with the exception of one of the parity LLRs, which is routed directly to a variable-node unit. Simultaneously, the variable-node units obtain the processed LLRs from the info and parity registers. The output LLRs from the variable-node units become the outputs of the decoder processor, which are fed into the subsequent decoder processor for another decoding iteration, or they become the input of the hard-decision slicer to form a stream of decoded info bits. The info and parity registers used for storage all have a common clock-gated structure, which is shown in Figure 3.7.

The depicted architecture includes a series of optimizations suggested in [1], which are summarized in the following subsections with their effects on the performance of the PN-LDPC0CC design.

Figure 3.6: A single decoder processor. [1]

Figure 3.7: An example of a clock-gated register [1]

#### 3.3.1 Truncated Min-Sum Check Sum Operation

Brandon [1] has employed a technique named truncated min-sum check sum operation (TMS) for the design of the check node unit. The TMS technique conditionally subtracts a constant value from the check-node LLR magnitudes when the least-significant-bit (LSB) of the LLR is set. This subtracted constant is equal to the maximum value that the LSB can represent. The application of TMS has demonstrated an decrease in energy-per-decoded-bit and area [1].

#### 3.3.2 Removal of Reset Circuitry in Check-Node

Due to the nature of LDPC-CC decoder being deterministic in that the order of operations only depends on the code and not the data, the values in uninitialized registers are unimportant. With this knowledge, the maximum LLR magnitude can be multiplexed into the check-node instead of allowing the LLR values from uninitialized memory locations into the check-node. This is achieved by keeping each input into the check-node at the maximum magnitude until a predetermined phase is reached. The LLR values from the memory are used as inputs to the check-nodes once this predetermined phase is reached. Using this method allows the reset circuitry/memory initialization to be eliminated from the design. Although the effect of the removal of the reset circuitry is minimal on the energy-per-decoded-bit based on simulation results, it does further reduce area [1].

#### 3.3.3 Removal of Saturation Bit

The removal of the saturation bit in the sign-magnitude representation of LLRs is achieved by approximating the function of the saturation bit using the maximum LLR magnitude. This modification has been shown to have an advantage of reducing power consumption and area [1]. However, the removal of saturation bits also results in a small loss in BER performance [1].

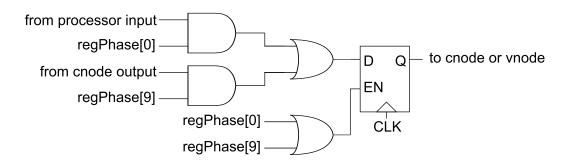

#### 3.3.4 Clock-gated Registers

The technique of clock-gating is applied on the info and parity registers. An example of how a register is clock-gated with the phase signal is depicted in Figure 3.7. This technique does not only further reduce area, but it also reduces the energy-per-decoded-bit [1].

### 3.4 System Design