## Role of Cryptographic Welch-Gong (WG-5) Stream Cipher in RFID Security

by

#### Rajesh Kumar Mota

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2012

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

The purpose of this thesis is to design a secure and optimized cryptographic stream cipher for passive type Radio Frequency Identification (RFID) tags.

RFID technology is a wireless automatic tracking and identification device. It has become an integral part of our daily life and it is used in many applications such as electronic passports, contactless payment systems, supply chain management and so on. But the information carried on RFID tags are vulnerable to unauthorized access (or various threats) which raises the security and privacy concern over RFID devices. One of the possible solutions to protect the confidentiality, integrity and to provide authentication is, to use a cryptographic stream cipher which encrypts the original information with a pseudo-random bit sequence. Besides that RFID tags require a resource constrained environment such as efficient area, power and high performance cryptographic systems with large security margins. Therefore, the architecture of stream cipher provides the best trade-off between the cryptographic security and the hardware efficiency.

In this thesis, we first described the RFID technology and explain the design requirements for passive type RFID tags. The hardware design for passive tags is more challenging due to its stringent requirements like power consumption and the silicon area. We presented different design measures and some of the optimization techniques required to achieve low-resource cryptographic hardware implementation for passive tags.

Secondly, we propose and implement a lightweight WG-5 stream cipher, which has good proven cryptographic mathematical properties. Based on these properties we measured the security analysis of WG-5 and showed that the WG-5 is immune to different types of attacks such as algebraic attack, correlation attack, cube attack, differential attack, Discrete Fourier Transform attack (DFT), Time-Memory-Data trade-off attack. The implementation of WG-5 was carried out using 65 nm and 130 nm CMOS technologies. We achieved promising results of WG-5 implementation in terms of area, power, speed and optimality. Our results outperforms most of the other stream ciphers which are selected in eSTREAM project.

Finally, we proposed RFID mutual authentication protocol based on WG-5. The security and privacy analysis of the proposed protocol showed that it is resistant to various RFID attacks such as replay attacks, Denial-of-service (DoS) attack, ensures forward privacy and impersonation attack.

#### Acknowledgements

I would like to thank my MASc supervisor, Dr. Mark Aagaard for his support during this work. I would also like to thank my thesis readers Dr. Guang Gong and Dr. Anwar Hasan for their insightful comments that helped in improving the quality of this thesis. I would like to thank my fellow researchers Kalikinkar Mandal and Hazem Shehata for their valuable discussions during this work. Finally, I would like to thank Ontario Graduate Scholarship (OGS) program for their generous support in this research work.

My family has played a significant role and very supportive during my entire work. No words to express my gratitude to my wonderful wife, Swayam. She has been understanding and supported me unconditionally.

Dedicated to my mom, dad, sister, brother and my wife.

## **Table of Contents**

| Li | st of   | Tables                                         | ix |

|----|---------|------------------------------------------------|----|

| Li | st of ] | Figures                                        | xi |

| 1  | Intr    | roduction                                      | 1  |

|    | 1.1     | Motivation                                     | 2  |

|    | 1.2     | Organization                                   | 3  |

| 2  | Ove     | erview of Cryptography                         | 5  |

|    | 2.1     | Keywords                                       | 5  |

|    | 2.2     | Objectives of cryptography                     | 6  |

|    | 2.3     | Overview of Cryptosystem                       | 6  |

|    |         | 2.3.1 Symmetric key cryptosystems              | 7  |

|    |         | 2.3.2 Asymmetric key cryptosystems             | 9  |

|    |         | 2.3.3 Symmetric vs asymmetric key cryptography | 9  |

|    | 2.4     | Other cryptographic primitives                 | 10 |

|    |         | 2.4.1 Hash functions                           | 10 |

|    |         | 2.4.2 Digital signatures                       | 10 |

|    | 2.5     | Cryptographic protocols                        | 11 |

|    |         | 2.5.1 Key-exchange and entity authentication   | 12 |

|    |         | 2.5.2 Identification                           | 12 |

|    | 2.6     | Pseudo-randomness                              | 13 |

|    | 2.7     | Attacks                                        | 13 |

| 3 | Mat | ematical Background 10                                         |

|---|-----|----------------------------------------------------------------|

|   | 3.1 | Introduction                                                   |

|   |     | 3.1.1 Modular Arithmetic                                       |

|   | 3.2 | Groups and Fields                                              |

|   | 3.3 | Finite Fields:                                                 |

|   |     | 3.3.1 Finite Field of the form $GF(p)$ :                       |

|   |     | 3.3.2 Polynomial Arithmetic:                                   |

|   |     | 3.3.3 Finite Field of the form $GF(p^n)$ :                     |

|   | 3.4 | Basis                                                          |

|   |     | 3.4.1 Selection of basis for hardware implementation:          |

|   | 3.5 | LFSR and mathematical description:                             |

|   |     | 3.5.1 Different types of sequences:                            |

|   |     | 3.5.2 Advantages of LFSR Properties:                           |

|   |     | 3.5.3 Hardware implementation of LFSR over Galios fields:      |

|   |     | 3.5.4 Polynomial multiplication and division in LFSR:          |

| 4 | Wel | n-Gong stream cipher 3.                                        |

|   | 4.1 | Stream Ciphers                                                 |

|   | 4.2 | Classification of stream ciphers                               |

|   | 4.3 | Stream Ciphers based on LFSRs                                  |

|   | 4.4 | Classification of stream cipher attacks                        |

|   | 4.5 | Welch-Gong (WG) Stream Cipher:                                 |

|   |     | 4.5.1 Introduction:                                            |

|   |     | 4.5.2 Mathematical description of WG: 38                       |

|   |     | 4.5.3 WG transformation                                        |

|   |     | 4.5.4 Properties of WG:                                        |

|   |     | 4.5.5. Selection of parameters for WG hardware implementation. |

| 5 | Rad | io Frequency Identification (RFID)               | 43 |

|---|-----|--------------------------------------------------|----|

|   | 5.1 | RFID technology                                  | 43 |

|   | 5.2 | Components of RFID system                        | 45 |

|   |     | 5.2.1 Types of tags                              | 46 |

|   | 5.3 | Inductive coupling communication                 | 47 |

|   | 5.4 | RFID Standards and frequency bands               | 48 |

|   |     | 5.4.1 Standards                                  | 48 |

|   |     | 5.4.2 EPC structure and classes                  | 48 |

|   |     | 5.4.3 Frequency bands and characteristics        | 50 |

|   | 5.5 | RFID security by hardware design                 | 50 |

|   |     | 5.5.1 Role of cryptography                       | 51 |

|   |     | 5.5.2 Lightweight cryptography                   | 52 |

|   |     | 5.5.3 Factors for good constraint implementation | 53 |

|   |     | 5.5.4 RFID optimality metrics                    | 54 |

|   |     | 5.5.5 RFID design considerations and process     | 55 |

|   |     | 5.5.6 Low Power Design techniques                | 58 |

|   | 5.6 | RFID privacy goals and definitions               | 58 |

|   | 5.7 | Types of attacks on RFID tags                    | 59 |

|   | 5.8 | summary                                          | 60 |

| 6 | WG  | -5 Stream Cipher                                 | 61 |

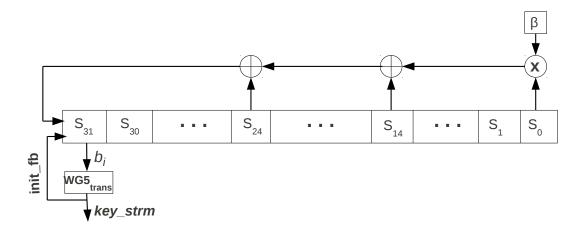

|   | 6.1 | WG-5 keystream generator                         | 61 |

|   | 6.2 | Cryptographic properties of WG-5                 | 63 |

|   | 6.3 | Security analysis of WG-5                        | 63 |

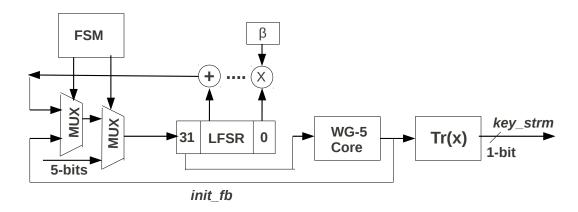

|   | 6.4 | WG-5 in hardware                                 | 65 |

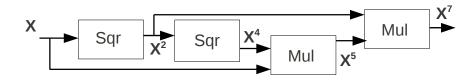

|   |     | 6.4.1 WG-5 Core and trace function               | 66 |

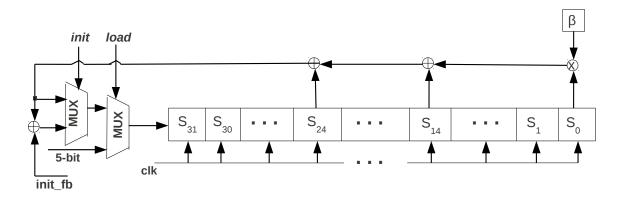

|   |     | 6.4.2 Linear feedback shift register             | 67 |

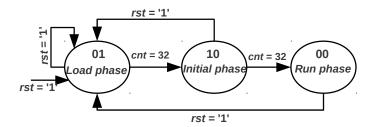

|   |     | 6.4.3 Finite state machine (FSM)                 | 68 |

|   | 6.5 | Area and performances results                    | 69 |

| Bi | bliog | raphy                                                       | 81        |

|----|-------|-------------------------------------------------------------|-----------|

|    | 7.1   | Future work                                                 | 80        |

| 7  | Con   | clusion                                                     | <b>79</b> |

|    | 6.7   | Comparison of results                                       | 75        |

|    |       | 6.6.1 Security and privacy analysis of the current protocol | 71        |

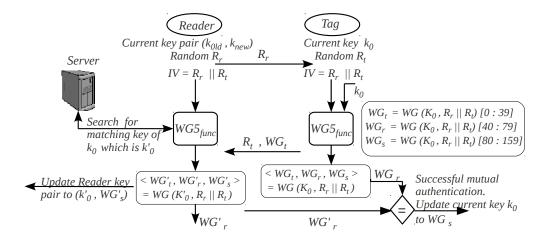

|    | 6.6   | WG-5 in RFID mutual authentication protocol                 | 70        |

## **List of Tables**

| 5.1 | characteristics of passive and active tags                         | 47 |

|-----|--------------------------------------------------------------------|----|

| 5.2 | RFID tag frequency bands and characteristics (Based on [1])        | 51 |

| 6.1 | Configuration of WG-5 based on <i>init</i> and <i>load</i> signals | 67 |

| 6.2 | Area and performance of WG-5                                       | 69 |

| 6.3 | WG-5 Protocol comparison                                           | 75 |

| 6.4 | Comparison of WG-5 with other Hardware ciphers in 130 nm           | 77 |

| 6.5 | Results of other block and stream ciphers                          | 78 |

## **List of Figures**

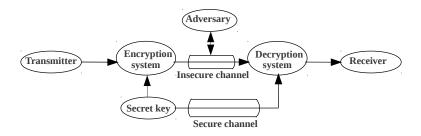

| 2.1 | Cryptosystem                                   | 7  |

|-----|------------------------------------------------|----|

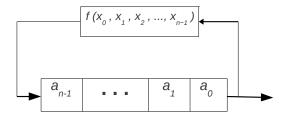

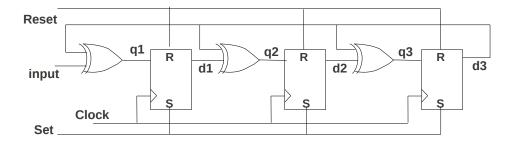

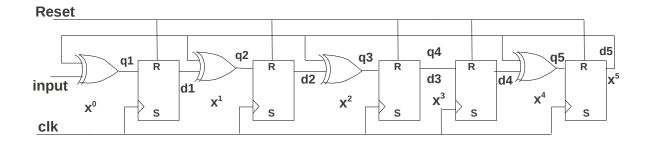

| 3.1 | Block diagram of LFSR                          | 27 |

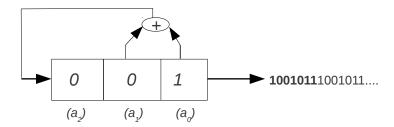

| 3.2 | 3-stage LFSR                                   | 28 |

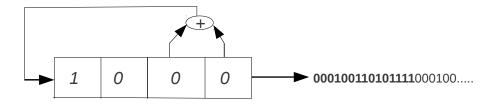

| 3.3 | 4-stage LFSR                                   | 29 |

| 3.4 | 3-bit LFSR circuit                             | 30 |

| 3.5 | LFSR implementing characteristic polynomial    | 30 |

| 3.6 | LFSR implementing multiplication               | 31 |

| 3.7 | LFSR implementing division                     | 31 |

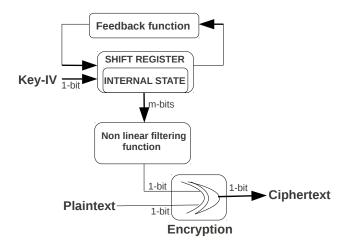

| 4.1 | Architecture of stream cipher                  | 34 |

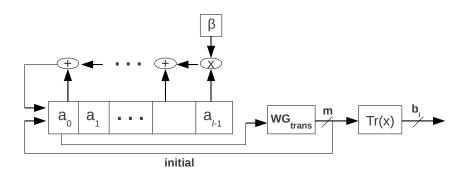

| 4.2 | WG Keystream generator                         | 38 |

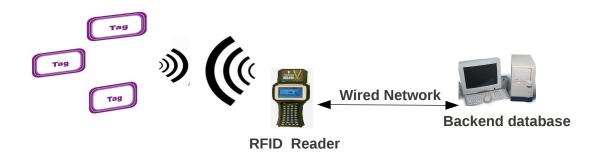

| 5.1 | RFID System                                    | 45 |

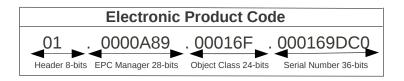

| 5.2 | EPC structure                                  | 49 |

| 6.1 | WG-5 Keystream generator                       | 62 |

| 6.2 | Architecture of WG-5                           | 66 |

| 6.3 | WG-5 Normal basis circuit                      | 66 |

| 6.4 | WG-5 LFSR                                      | 67 |

| 6.5 | WG-5 Finite State Machine Implementation       | 68 |

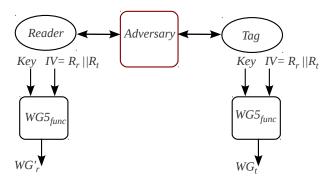

| 6.6 | RFID Mutual authentication protocol using WG-5 | 70 |

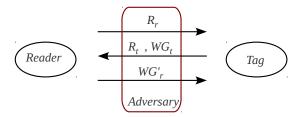

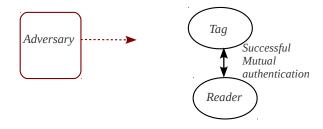

| 6.7 | Man-in-the-middle attack                       | 71 |

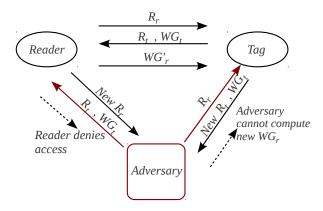

| 6.8 | Replay attack                                  | 72 |

| 6.9  | Impersonation attack      | 72 |

|------|---------------------------|----|

| 6.10 | De-synchronization attack | 74 |

| 6.11 | Tag recovery from attack  | 74 |

## Chapter 1

## Introduction

Cutting edge technologies have made recent advances in microelectronics. One of the most advanced and widely used technologies is wireless, non-contact automatic system or Radio Frequency Identification (RFID) [2]. It was first introduced during World War II, since then, it has become an integral part of our daily lives. Nowadays, RFID tags are used in various applications such as, item tracking, contactless smart cards, access control, e-passports, supply chain management and so on [3]. The use of this technology by some of the major companies like Wal-Mart Stores Inc. and the US military forces agency have greatly increased the popularity and demand of RFID systems.

RFID systems consist of mainly three components; *tags*, which can store information or data; *readers*, which is used for reading the data from the tags; *back-end database* system which is connected to readers via network for the processing of tag's data. Generally, the information stored in RFID tags are in the form of unique code called as Electronic product code (EPC) and is available in various lengths (96, 108 bits) [4] [5] depending upon the application.

Based on their power sources RFID tags are differentiated into *Passive*, *active* and *semi passive*. In the current work we focus on the passive type RFID tags. Passive tags do not contain batteries unlike semi passive and active tags. Passive tags extract power from the reader via electromagnetic waves which makes it small and less expensive. The size of the tag varies depending on applications. Due to the technological advancements in semiconductor manufacturing, researchers are shrinking the size of RFID tag which further reduces its cost. With the increasing applications and high demands, RFID systems must full fill some of the design goals such as low cost, small size and higher data rates.

The aim of the present work is to propose a lightweight stream cipher called WG-5 for the low cost passive RFID tags. WG-5 is a variant of WG stream ciphers [6], which was submitted to eSTREAM project in 2007. Further, it was focused as a multi-output WG ciphers (MOWG) [7]

wherein, its trade offs between the security and hardware matrices were discussed. In [8], WG-7 has been proposed as a lightweight stream cipher and its software implementation was carried out on different micro controller units. In the present work, the design goal of WG-5 stream cipher is to ensure cryptographically secure and to achieve hardware implementation efficiently in terms of less gate count, low power and better performance using the current CMOS technologies. The next goal is to propose a mutual authentication protocol based on the proposed lightweight stream cipher. Further, the proposed protocol must be secure against some of the attacks such as man-in-the-middle, denial of service, tampering of tags and also to ensure RFID privacy.

#### 1.1 Motivation

The major concern in RFID systems is security and privacy. Usually, RFID tags communicate data in the form of unique code, to the readers, over an unsecured communication channel. The unique code can be related to manufacturer details of any product or it can be personal information. The security and privacy issues arise in RFID systems when the unique code are accessed by an unauthorized readers by eavesdropping or rogue monitoring. This leads to manipulation of tags data, tracking the objects or persons. To overcome the aforementioned concerns, cryptographic solutions or alternatively symmetric cipher cryptosystems are introduced in low cost passive RFID tags.

The silicon area utilization of the passive tags is directly proportional to the cost of the tag and according to one of the previous studies, the cost of the passive tags should not exceed five cents [9]. Based on current advanced CMOS technologies, the design of cryptographic circuitry for RFID tags should not be more than 5000 GE (gate equivalence) [10] [11]. The symmetric stream ciphers can be implemented in RFID tags with less than 5000 GE [12].

Since passive RFID tags receive their power from the reader, the power consumption is an important factor to be considered. The power consumption usually vary depending on the tag operations performed such as; transmission rate, response time and writing the data into tags memory [10]. Generally, the power available for cryptographic design in passive tag should be in the range of 5 to 15  $\mu$ A [10] [13]. Therefore, passive tags have very limited power availability to perform the aforementioned operations. Thus, one can envisaged that, the implementation of symmetric cryptosystem in low cost passive tags would be a challenging task due to its constrained environment. The cryptographic designs which achieve these RFID passive design goals such as less area, low power and low cost are called *lightweight cryptography*.

In addition, *single authentication protocols* are one of the solutions to ensure security and privacy in RFID systems which ensures that, the data is communicated between the two authorized persons. If the tag authenticates a reader it means that the data is sent only to the authorized

reader. Similarly, if the reader authenticates a tag, it suggests that the tag is not forged by any unauthorized entities. Moreover, compared to *single authentication protocols*, the *mutual authentication protocol* is more secure way of communication in which both the reader and the tag authenticates each other before exchanging the data. Most of the authentication protocols published are based on block ciphers or other cryptographic systems such as hash functions [14] [15] [16] [17] [18] and very few protocols are based on stream ciphers [19] [20].

#### 1.2 Organization

In chapter 2, we discuss the background information on various cryptographic systems and their properties. In addition, we explain different types of attacks that an adversary can perform over a cryptographic system. In chapter 3, we describe the overview of mathematical concepts like finite fields, polynomials, normal, polynomial and optimal normal basis which play an important role in designing a symmetric stream ciphers. Since, the design of stream cipher depends on the selection of basis we explain various options that can be selected depending on the hardware requirements in section 3.4. Later in section 3.5, we discuss the LFSR properties and its hardware representation for any given polynomials over a finite field.

In chapter 4, we discuss the overview of stream ciphers and different types of attacks on them. In section 4.5, we describe the WG stream cipher [6] and its proven cryptographic properties. WG stream cipher is based on the mathematical definitions and the keystream is generated based on its WG transformation function which are explained in section 4.5.2 and 4.5.3 respectively. Since, WG transformation function can be implemented in different architectures, the procedure for selecting the parameters for its implementation were explained in section 4.5.5. The important parameters that are involved in design of WG stream cipher are number of bits over the finite field, primitive feedback polynomial, generating polynomial, length of the LFSR, representation of field elements either in normal or polynomial basis or ONB, multiplier architectures like serial or parallel based depending on the selection of basis. These parameters can affect the security level of WG cipher and utilization of hardware resources of the cipher.

In chapter 5, we gave an overview of RFID systems, its applications, different frequency bands, EPC structure and standards. The main focus of this chapter is to explain the security hardware design requirements for passive type RFID tags. Section 5.5, explains the role of cryptographic solutions, RFID optimality metrics, RFID hardware design considerations and different optimization techniques for passive type RFID tags. Finally, section 5.6 and 5.7 describes some of the RFID privacy goals and definitions and explain different types of attacks on RFID systems respectively.

In chapter 6, we propose lightweight stream cipher WG-5 for low cost passive RFID tags.

After selecting the design parameters for WG-5, we describe the architecture of WG-5 keystream generator and calculated the related properties of WG-5 in section 6.1 and 6.2 respectively. Based on the measured properties we carried out the security and privacy analysis of WG-5 stream cipher in section 6.3. Later, we carried out the implementation details of WG-5 cipher starting with the datapath i.e. WG-5 core and then the control units; LFSR and FSM in section 6.4. Furthermore, we measured the implementation details of WG-5 cipher using 65 and 130 nm CMOS technology in section 6.5. In section 6.6, we proposed RFID mutual authentication protocol based on WG-5 stream cipher and its security and privacy analysis has been carried out in section 6.6.1. Atlast, we compared the WG-5 results with other existing stream and block ciphers in section 6.7.

Finally, in chapter 7 the conclusion of present work is described along with the future work.

## Chapter 2

## **Overview of Cryptography**

The communication over an insecure channel can be accessed by unauthorized persons. In order to prevent from unauthorized accesses, cryptography is widely used in different applications. Cryptography provides few of the security objectives which is discussed in section 2.2. In section 2.3, the types of cryptosystems such as symmetric and asymmetric key systems are discussed. In cryptography, hash functions and digital signatures play an important role in achieving some of the security objectives, which is explained in section 2.4. In order to achieve high level of security few of the cryptographic protocols has been described in section 2.5. While, in section 2.6 the concept of pseudo-randomness is discussed. Atlast in section 2.7 different types of possible attacks on the cryptographic systems are discussed.

#### 2.1 Keywords

**Keywords:** These are the following keywords listed below which are used throughout this material.

- *Information*: It can be a data or a message which is communicated between two-parties. The parties can be either a person or a computer terminal.

- *Sender*: Sender is one of the two-parties, who transmits the information.

- *Receiver*: Reciever is also one of the two-parties, who receives the information.

- Attacker/adversary/eavesdropper: An unauthorized party who tries to get access to the secure communication channel used by the sender and receiver.

- *Channel*: It is a means of communication between the sender and receiver. Channels can be secure and unsecured. Secure channel does not allow the attacker to modify, delete, insert or read the information, compared to unsecured channel.

- *Confidentiality or Secrecy*: Assurance for the data or information that is communicated and cannot be accessed by any unauthorized parties.

- *Cryptography*: Study of mathematical techniques which deal with the information security. It enables the confidentiality, when information is communicated via unsecured channel. Cryptographic algorithms are designed by mathematical techniques to introduce security.

- *Cipher*: Any encryption technique referred as a cipher. Formally, its a technique of concealing the readability and meaning of the original information.

- *Cryptographic system*: Its a collections of various cryptographic algorithms which includes ciphers and cryptographic protocols.

- *Cryptanalysis*: A technique used for deciphering the information, without any knowledge of enciphering details. Persons who work on cryptanalysis are called as attackers or cryptanalysts.

- *Entity*: An entity can be referred to as person or computer terminal.

#### 2.2 Objectives of cryptography

The main goal of cryptography is to prevent and detect the fraud from the malicious activities. Cryptography not only provide better security over the communication channels but also provides following services.

- 1. *Confidentiality:* It ensures that when the information is transmitted over a channel and not accessed by any unauthorized person.

- 2. *Data Integrity:* It ensures the ability to address the manipulation of original data. Manipulation can be either insertion, modification or deletion.

- 3. Authentication: It ensures the ability to identify or to verify the communicating parties so that, no one should be able to pretend as Alice and send an information to Bob (*data origin authentication*). Alice and Bob should be able to identify each other (here Alice is a sender and Bob is a receiver) (*entity authentication*) [21]

- 4. *Non-repudiation:* It prevents from denying the previous commitments or actions done by the communicating parties.

## 2.3 Overview of Cryptosystem

It is a collection of various cryptographic algorithms which includes ciphers and various cryptographic protocols. The model of the cryptosystem is shown in Figure 2.1. There are three

parties involved in the cryptosystem called as transmitter, receiver and adversary. Initially the transmitter chooses a *plaintext* message before it transmits over a channel. Generally communication takes place over an insecure channel before transmitting to the legitimate receiver. In order to avoid malicious activities by the adversary about the plaintext; the transmitter transforms the plaintext into unknown format known as *ciphertext* with the help of a *secret key* (sequence of bits). The process of transformation is known as *encryption*. Before transmitting the information, the sender must share the secret key with the receiver by means of some secure channel. Once receiver knows the secret key and recovers the plaintext message by applying the transformation called as *decryption* over the ciphertext.

Figure 2.1: Cryptosystem

Encryption algorithm is a transformation or substitution of steps while, decryption algorithm is just a reverse run of it. Usually, the secret key and the plaintext are inputs for the encryption algorithm. Secret key values are independent of the plaintext and the encryption algorithm produces various outputs for different secret key values. For secure cryptosystem one should design a strong encryption algorithm and choose the secret key wisely. For example, the secret key must be long and possess randomness properties so that, the adversary should not decrypt the ciphertext and discover the secret key.

There are two types of cryptosystem which are as follows. If the sender and receiver uses the same secret key for encryption and decryption operation, then the system is called as the *symmetric key* or single-key or conventional cryptosystem [22]. If both the sender and receiver uses two different keys thats is *public-key* (non-secret) and *private-key*(secret) for encryption and decryption then the system is called as *asymmetric key*, two-key or *public-key cryptosystem*.

#### 2.3.1 Symmetric key cryptosystems

Symmetric-key cryptosystems provide secure communication between a pair of communication parties and the adversary who tries to intercepts the message (m) cannot get any significant

information about the message contents. In this system both the sender and receiver share the same secret key (k) for both encryption (E) and decryption (D) operations.

**Example:** If Alice wants to send a message m to Bob through a secure communication channel. Using encryption algorithm, Alice first generates ciphertext (C) as E(k,m)=C and sends it to Bob. Bob on the other side, using decryption algorithm he restores the original message as D(k,C)=m.

Typically, symmetric key cryptosystems are used for ensuring the *confidentiality* and *integrity* of the data. One way to achieve data integrity is by using *message authentication code* (MAC) algorithm [23]. In this algorithm, first the sender generates the MAC code which is a simple block of data that is generated depending on the message length using secret key by running the MAC algorithm. The message along with the MAC code are sent to the receiver and the receiver would check the *integrity* of the incoming message by running the same MAC algorithm and comparing the transmitted MAC code. If the code is identical then the receiver can assure that there is no modifications done to the message.

**Example:** If Alice wants to send a message m to Bob, then Alice generates MAC code as X = MAC(k, m) using MAC algorithm. Usually the MAC code is protected by a secret key k. Now Alice sends X along with m to Bob. At the receiver side Bob verifies the data integrity of the message by checking the MAC code.

Symmetric key cryptosystems are of two types; *Stream ciphers* and *Block ciphers* and explained below.

#### **Stream ciphers:**

In stream cipher the plaintext is converted to ciphertext by one bit at a time. It generates arbitrarily long stream of key material (bits) known as *keystream*. The generation of *keystream* output is based up on the *internal state* which is usually hidden inside the cipher and changes frequently as cipher operates. During encryption the *keystream* is XORed (exclusive-or operation) with each plaintext one bit at a time. Some of the examples of stream ciphers are Welch-Gong (WG) cipher, RC4, grain, trivium, A5/1 and so on.

#### **Block ciphers:**

Block cipher operates on the fixed length blocks (i.e. group of bits) of plaintext or ciphertext. The encryption operation is an unvarying transformation, which is controlled by using the secret key. For example, a block cipher might take 128-bit block of plaintext as an input and generate 128-bit block of ciphertext. Examples of block ciphers are Data Encryption Standard (*DES*), Advanced Encryption Standard (*AES*) and so on.

#### 2.3.2 Asymmetric key cryptosystems

Public key cryptosystem is a well known example of asymmetric key cryptosystem. The concept of public key cryptosystem was mainly introduced to distribute the secret keys securely, which is also known as key agreement scheme [21]. The basic idea behind the public key cryptosystem is that, each person contains two different keys one is called the public key (pk) and the other is called the private key or secret key (sk). The public key is available to everybody where as, the secret key is kept secret and it is known only to the owner. The public key is used for encrypting the message while the private key is used for decryption.

**Example:** In public key cryptography Alice uses Bob's public key for encryption operation as E(pk, m) = C and sends ciphertext to Bob. Bob on the other hand recovers the message from ciphertext, using his secret key by decryption operation as D(sk, C) = m.

From the above example we need to know that only Bob knows the secret key and nobody can decrypt the message, even Alice cannot decrypt the message back even if she has lost the message. This system provides better *confidentiality* of the data.

The well known examples of public key algorithms are *RSA* (named after its inventors: Rivest, Shamir, Adleman) and *Diffie–Hellman* algorithms.

#### 2.3.3 Symmetric vs asymmetric key cryptography

- 1 . Symmetric key systems provide secure communication channel whereas asymmetric-key systems are good at secure key exchange management.

- 2 . Design of symmetric key systems are easy to analyze and implement in hardware implementation compared to asymmetric. Because, symmetric key systems consists of simple mathematical operations involving addition, subtraction and multiplication operations. and these operations can be implemented by using simple XOR and AND gates in hardware. Where as, public key systems consists of hard complex mathematical operations which involves addition, multiplication and division or inversion, which utilizes more number of gates for implementation, for example elliptic curve crypto systems.

- 3 . Length of key for symmetric-key ciphers are relatively short compared to asymmetric-key systems.

- 4 . To ensure better security various cryptographic mechanisms like pseudo-random number generators, digital signatures use the concepts of both symmetric-key and asymmetric-key system.

#### 2.4 Other cryptographic primitives

In this section we discuss about two algorithms; hash functions and digital signatures. In cryptography these are used to ensure data integrity and authentication. Hash functions are considered as one of the encryption algorithms like secret key and public key algorithms and known as one-way encryption systems where no secret keys are used. Whereas, digital signatures use concepts of public key cryptosystems and ensure non-repudiation by using hash functions.

#### 2.4.1 Hash functions

*Cryptographic hash functions* takes a block of message as an input and returns random bit string of fixed length known as *hash value*. The hash value will change if the input message is altered intentionally or accidentally.

#### Cryptographic hash function properties

- 1. For any given message, it is easy to compute hash value.

- 2. For any given hash value, it is infeasible to find its corresponding message.

- 3. For any two messages, their hash values need not be the same.

In cryptography, hash functions are used to provide the *integrity* of a message (m). if the hash value of m is stored in a secure place then the modification of m can be detected by calculating the hash value and comparing it with the stored value. Hence, the hash functions are also known as *modification detection codes* (MDCs) [23].

In addition, hash functions provide message *authentication* and it authenticate the origin of the message. If hash functions are used in message authentication it is called as message authentication code (MAC).

#### 2.4.2 Digital signatures

The process of *signing* to impose the transformation of message and the secret key into a tag is called as *digital signature*. The purpose of *Digital signatures* is to provide a reason to the receiver to trust or identify the message which is sent by the known sender only.

Digital signatures uses the concept of *public-key cryptosystem*. Usually, digital signatures depend on the secret key of the signer and can be generated only by the signer. In general, digital signature consists of two algorithms they are [23]:

- 1. Sign algorithm: It takes a message and a secret key as an input and generates the signature.

- 2. *Verify algorithm*: For the given message, public-key and signature, it verifies whether the message is authentic or not.

Digital signatures are intended to provide both *data integrity*, *authentication* and *non-repudiation* of the message.

**Example:** If Alice wants to sign a message (m), by using the Sign algorithm with secret key (sk) and generates the signature as s = Sign(sk, m). When Bob receives the signature (s) for the message m, he checks the signature is valid or not by applying the verify algorithm by using Alice's public key (pk) as Verify(pk, s, m) = valid.

From the above example, we can say that Bob can verify the Alice signature and the message. It is possible only when Bob uses the correct Alice's public key and the message.

On the other hand, there are possibilities that adversary can inject the message into the communication channel and pretend as Alice or Bob. It is called as a *forgery* or possible type of *attacks* (see section 2.7) on the transit information. In that case nobody can identify the forgery of the message, even Bob too. To overcome these type of forgeries or attacks, digital signatures uses cryptographic *hash functions*. Here, Alice first applies the hash function to the message to get the hash value and than she encrypts the hash value using her private key. This encrypted hash value is used as Alice signature and sends the digital signed message to the Bob. Now, Bob knows the message and the digital signature. Now, Bob applies the hash function on the message to get the hash value and decrypts the hash value using Alice public-key. Finally, Bob verifies whether the two hash values are *valid* or *not*; if they are valid then Bob confirms that the digital signature message is sent by Alice.

Thus, by using the hash functions in digital signatures the *non-repudiation* can be ensured. It suggests that now Alice cannot state that the message is not signed by her.

#### 2.5 Cryptographic protocols

A *Cryptographic protocol* can be defined as an algorithm with well defined sequence of steps which must be followed by two or more communicating parties, to solve the issues involving confidentiality, authenticity and data-integrity.

In modern cryptography, the development of well defined protocols lead us to provide high level of security. Cryptographic protocols are developed based on *cryptographic primitives* such

as hash functions, symmetric and asymmetric algorithms. Cryptographic protocols are called as *multi-party algorithms*. Meaning, it must be communicated between at least two parties.

#### 2.5.1 Key-exchange and entity authentication

The major draw back of symmetric-key cryptosystem is the key exchange or key agreement. This issue becomes more evident especially when, used in a cluster of network systems where more than two entities communicate. It is know that, in symmetric-key systems both Alice and bob agrees on a secret key. To share the secret key securely symmetric-key system uses the concept of public-key cryptosystems. The first solution available for the key exchange problem is the *Diffie-Hellman key agreement* protocol [21] which is based on public-key cryptosystems.

The draw back of continuous key exchange using Diffie-Hellman key agreement is that, there is no authentication between the communicating parties. Whereas, entity authentication ensures the identity of the communicating parties there by avoiding impersonation. In entity authentication, Alice can prove her identity by signing her signature on the messages. There are possibilities that adversary can intercepts Alice signed message and later on adversary can authenticate as Alice. This type of attack is called as *replay attack*. One solution to prevent from replay attack is to vary the Alice signature in [23].

One of the methods used to prevent replay attack is the *challenge-response protocol*. This protocol is based on public-key digital signature scheme. In challenge-response protocol, first Bob sends any random number to Alice and she uses the same random number in the message and signs it with her signature before sending back to Bob. Now Bob verifies the random number which he has sent earlier to Alice and later on Bob validates her signature. Here, the random number is viewed as a challenge. Other than this protocol, there are other protocols like *two-way* and *three-way* authentication protocols [23]. These authentication protocols play a major role in some of the technologies for instance in RFID technology, where the RFID reader and tag must authenticate each other for communications. How cryptographic authentication protocols are used in RFID will be discussed in chapter 6.

#### 2.5.2 Identification

*Identification* is defined as a technique which provides the identities of both the entities to verify each other which are involved in a communication.

One of the techniques used earlier is personal identification number (PIN) and password method. If Alice wants to do electronic transactions with the bank, first she has to enter her PIN and a password into the system to view her account details. But the passwords and PIN are not

secure. Since there are chances that if anyone come to know her password or PIN during her transaction, it might impersonate as Alice and extract all her banking details.

There are protocols designed to eradicate these type of issues. For example, fiat-shamir identification protocol, zero-knowledge [23]. Thus, cryptographic protocols play a major role in ensuring the confidentiality, data integrity, authentication and non-repudiation. The key-agreement generally should take place between two parties (sender and receiver) in the field of communication. The establishment of keying methods between the parties ensures the confidentiality of secret keys so that, once the secret keys are agreed, any messages can be encrypted securely. Once the keys are agreed, it also ensures the authenticity by using public or private key agreement, this can be achieved using the concepts of digital signatures or hash functions. Now the receiver can verify the senders identity and ensures the non-repudiation. By using public keying methods one can provide the data-integrity, that is if the senders key is signed by any trusted third party then the receiver can consider that key with confidence.

#### 2.6 Pseudo-randomness

The concept of randomness is used for the better encryption purpose. Most of the encryption algorithms prefer the random key selection so that, keys cannot be predicted by an adversary. In general, pseudo-random sequence bits are generated by an algorithm known as *pseudo-random bit generators*. The output of these generators is a long sequence of pseudo-random sequence of bits for any given small random input which is known as the initial state. The basic building blocks of pseudo-random generators are the Linear feedback shift register (LFSR) [24].

#### 2.7 Attacks

The main objective of cryptography is to provide security for the transmitted message from the adversary, who tries to extract the information from the transmitted message. Before designing any cryptographic system one should assume that, the adversary knows everything about cryptographic system implementation and the algorithms used. This principle is commonly stated as the *kerkhoff's principle*.

Adversaries try to extract information about the secret key so that, ciphertext can be broken to recover the original message. Attacks by the adversaries can be classified into two types, *passive* and *active*.

In *passive* type of attacks, the adversary observes only the communication channel and it is a threat to the confidentiality of the data.

In *active* type of attacks, the adversary can modify, delete or inject the data into the communication channel and it is threat to the data integrity, authenticity and confidentiality.

Attacks can be divided into following types based on the resources used by the adversary. The objective of these types of attacks is to recover the plaintext from the ciphertext or to extract the information about the secret key.

- 1. *Ciphertext-only attack:* In this type of attack the adversary has the knowledge of ciphertext and tries to extract the plaintext or the decryption key from the known ciphertext. Any encryption scheme is considered insecure if it cannot resist this type of attack.

- 2. *Known-plaintext attack:* Here the adversary uses knowledge of plaintext and its corresponding ciphertext and tries to extract the secret key and recover the encrypted message.

- 3. *Chosen-ciphertext attack:* The adversary selects the ciphertext and tries to decrypt its corresponding plaintext. Assuming that the attacker has access to the decryption system.

- 4. *Chosen-plaintext attack:* In this type of attack the adversary first chooses the plaintext and obtain its ciphertext. After few analysis on how to obtain the plaintext from the unknown ciphertext, the adversary tries to analyze the cryptographic pattern outputs that are being used and try to recover the secret key.

- 5. *Man-in-the-middle attack:* Here the adversary gets access to the communication channel used by the sender and receiver and tries to send some non-specific key exchange informations from the middle of communication.

- 6. *Replay attack:* The adversary retains the capability to store or record the communication of the sender and receiver. Later on the adversary replays the same communication after some point of time.

- 7. *Relay attacks:* It is similar to man-in-the-attack and replay attack. In this the adversary relays the message from the sender and sends it to the receiver. Relay attacks are commonly occur in wireless devices such as RFID devices.

- 8. *Side-channel attacks:* In side channel attacks, the attacker tries to get secret information of the cryptographic systems which are implemented (physically) hardware.

- (a) *Timing analysis attacks:* In timing attacks, the attacker tries to analyze the execution time taken by the cipher for encryption or decryption operations. Basically, it is based on measuring the time taken by a unit to perform its operation and the measuring information can reveal the secret key.

| (b) | <i>Power analysis attacks:</i> In this type of attacks, the attacker tries to get information from the power consumptions of the devices. |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

|     |                                                                                                                                           |

## Chapter 3

## **Mathematical Background**

#### 3.1 Introduction

Finite Fields play a major role in some of the most interesting applications of modern algebra to the real world. In particular, the applications related to the data communication is a vital concern in our information friendly society. In today's technological advancements in the areas of space and satellite communications, protecting the privacy of information involve the use of finite fields in one way or the another.

This chapter begins with a brief overview of concepts of field and group. Next, we will explain the concepts and types of finite fields of the form GF(p), where p is a prime number. Before going to the details of finite field extension of the form GF(p), where p is a positive integer, it needs to be discussed some of the elementary background in polynomial arithmetic operations. Finally, we briefly discuss about the normal basis and types of optimal normal basis.

#### 3.1.1 Modular Arithmetic

Modular arithmetic has gained importance in the area of cryptography. In Public Key Cryptosystem algorithms such as RSA and Diffie-Hellman algorithm uses the theory of modular arithmetic including, symmetric key algorithms such as AES, IDEA and RC4. The major advantage of using modular arithmetic is that it allows us to do faster multiplication operations. For example, in any complex operations such as polynomial greatest common divisor calculation where we come across large number of integers to perform number of multiplication operations. The use of modular arithmetic reduces the computing times of these large operations. In one of the applications like error correcting codes each digit of the code is related to the elements of the finite field by using the modular arithmetic theory.

Note that, the modular operator (mod n) maps all the integers within the confined set of integers  $\{0, 1, 2, ... (n-1)\}$  and all the arithmetic operations are performed within this set. This techniques is called as **modular arithmetic**.

The set of integers and nonzero integers of mod n are denoted by  $\mathbb{Z}_n$  and  $\mathbb{Z}_n^*$  respectively.

**Example 1:** Modular addition and multiplication over modulo 23.

Suppose,

$$12 + 20 = (12 + 20) \mod 23 = 32 \mod 23 = 9$$

since the remainder is 9 when 32 is divided by 23.

Similarly, in multiplication operation;  $8 \times 9 = 72 \mod 23 = 3$ , since the remainder is 3 when 72 is divided by 23.

#### 3.2 Groups and Fields

Fields and groups are the well known algebraic structures of the abstract or modern algebra. In abstract algebra, we work with sets on which elements can be operated algebraically. For instance, we can say that by combining two elements of a set in several different ways the third element of the set can be obtained. All these operations will follow certain specific rules which will define the nature of the set. The notation followed for operations on set of elements is usually same as the notation for ordinary addition and multiplication.

#### Groups:

**Definition 1** A group (G) is defined as a pair  $(S, \bullet)$ , where S is set of elements with binary operation  $\bullet$ , such that, it obeys axioms from A1 - A4.

The binary operator • is generic and can be referred to addition, multiplication and other mathematical operation.

**Note:** Here the set S is the representation of group G. From now on we represent group as G.

# Axioms Meaning A1. Closure For all a, b in $G, a \bullet b$ will be in GA2. Associative For all a, b, c in $G, a \bullet (b \bullet c) = (a \bullet b) \bullet c$ . A3. Identity There exists an element e in G, for all a in G, such that $a \bullet e = e \bullet a = a$ . More formally, $\exists e \in G$ , $\forall a \in G, a \bullet e = e \bullet a = a$

**Note:** We denote identity element in G as **i**

A4. Inverse For every

$$a$$

in  $G$ , there exists an element  $x$  in  $G$ , such that  $a \bullet x = x \bullet a = \mathbf{i}$ . More formally,  $\forall a \in G, \exists x \in G, a \bullet x = x \bullet a = \mathbf{i}$

In order to satisfy the A4 axiom the operation must have an identity element.

**Example 2:** For any positive integer  $n(\mathbb{Z}_n, +)$  is a group.

The set  $\mathbb{Z}_5 = \{0, 1, 2, 3, 4\}$ , where n = 5, with addition module 5 forms a group, for example  $2 + 4 = 1 \pmod{5}$ .

**Example 3:** If p is prime then  $(\mathbb{Z}_p^*, \times)$  is a group.

The set  $\mathbb{Z}_5^* = \{1, 2, 3, 4\}$ , where p = 5, with multiplication module 5 forms a group, for example  $2 \times 4 = 3 \pmod{5}$ .

**Note:** If a group has finite number of elements then it is called as *finite group*, otherwise, it is an *infinite group*. The *order* of the group is the number of elements in the group.

**Definition 2** A group is called an **abelian group** if it satisfies the following axiom.

Axioms Meaning

A5. Commutativity For all a, b, in G,  $a \bullet b = b \bullet a$

**Definition 3** A group is called **cyclic** if there are one or more members that can be used to generate all members by raising the **generator** to a power. More formally:  $\exists g \in G, \forall a \in G, \exists k, a = g^k$

A cyclic group is always abelian.

**Example 4:** If p is prime then  $(\mathbb{Z}_p^*, \times)$  is a cyclic group.

The Cyclic group  $(\mathbb{Z}_7^*, \times)$ , where p = 7, the order of the finite group is 6. And the elements 3 and 5 are the generators of this cyclic group  $\mathbb{Z}_7^* = \{1, 2, 3, 4, 5, 6\}$ , then the powers of 3 module 7 are

$$1 = 3^6, 2 = 3^2, 3 = 3^1, 4 = 3^4, 5 = 3^5, 6 = 3^3$$

Fields:

**Definition 4** A *field F*, is defined as a set of elements with two binary operations +,  $\times$ , which is represented as  $(F, +, \times)$ . Such that it obeys the following axioms.

| Axioms           | Meaning                                                |

|------------------|--------------------------------------------------------|

| (A1 - A5)        | F forms a abilian group with respect to addition       |

| (A1 - A3) and A5 | F with respect to multiplication satisfies the axioms. |

**Note:** The additive and multiplicative identity elements in F is denoted by 0 and 1 respectively.

A6. Multiplicative inverse For every

$$a$$

in  $F$ , except  $a=0$ , there exists an element  $x$  in  $F$  such that  $a\times x=x\times a=1$ . More formally,  $\forall~a\neq 0\in F, \exists~x\in F,$   $a\times x=x\times a=1$

**Example 3:** For any field  $(F, +, \times)$ . (F, +) forms an abilian group.

**Example 4:** For any field  $(F, +, \times)$ .  $(F^*, \times)$  forms an abilian group, where  $F^*$  is the elements of F excluding additive identity element 0.

#### 3.3 Finite Fields:

Finite fields play a major role in the area of cryptography. Most of the cryptographic algorithms such as the Digital Signature Standard (DSS), the El Gamal public key encryption, elliptic curve public key cryptography are heavily depend on the properties of finite fields and it is also used in Advanced Encryption Standard (AES) cryptography.

The order of the finite field must be a power of prime  $p^n$ , where n is a positive integer. Here two cases exits; for n = 1, the finite field is of the form GF(p) where GF stands for Galois Field and for n > 1, the finite field is of the form  $GF(p^n)$ . The finite field GF(p) has different structure compared to the finite field  $GF(p^n)$ .

#### **Types of Finite Fields:**

- (i) **Prime field:** It is defined as a field of the form GF(p) of order p, where p is prime. All the elements in this field and arithmetic operations  $(+, \times)$  perform with respect to the modulo p.

- (ii) **Binary field:** It is defined as a field of the form  $GF(p^n)$  of order  $p^n$ , where n is a positive integer. Usually binary field is constructed using the prime field.

#### **3.3.1** Finite Field of the form GF(p):

For any prime p, finite field of order p, the elements of GF(p) is defined as the set  $\{0, 1, 2, ...(p-1)\}$ , along with the arithmetic operations modulo p. GF(p) can also be denoted by the set of integers  $\mathbb{Z}_p$ .

**Example 4:** The arithmetic operations in the simplest finite field of the form GF(p).

The simplest finite field is GF(2), where p=2, and its elements are  $\{0,1\}$ , this is a special case where the arithmetic operations + and  $\times$  is just equivalent to the XOR and AND operations respectively.

The additive inverse elements for 0 and 1 is 0 and 1 respectively.

The multiplicative inverse elements for 0 and 1 is -(do not exist) and 1 respectively.

**Example 5:** The arithmetic operations in the finite field of the form GF(3).

The finite field of GF(3), where p = 3, and its elements are  $\{0, 1, 2\}$ , the arithmetic operations + and  $\times$  is just as simple operations on integers followed by a reduction modulo p. For instance, in GF(3), 2 + 2 = 4 which is reduced to 1 modulo 3. Similarly,  $2 \times 2 = 4$  reduced to 1 module 3.

The additive inverse elements for 0, 1 and 2 is 0, 2 and 1 respectively.

The multiplicative inverse elements for 0, 1 and 2 is -(do not exist), 1 and 2 respectively.

**Note**: Before going to the finite field of the form  $GF(p^n)$ , we need to discuss about the concepts of polynomials. Since they are extensively used in finite fields  $GF(p^n)$ .

#### 3.3.2 Polynomial Arithmetic:

The elements of  $GF(p^n)$ , when n > 1, can be represented as polynomials, whose cofficients belong to GF(p) and degree should be less than n. When p is 2, the elements of  $GF(p^n)$  is represented as binary numbers  $\{0,1\}$ . This means that each term in a polynomial expression is represented by one bit in the corresponding binary expression.

We are interested in polynomials over fields. From now on the field will be denote as  $(F, +, \times)$  as F.

**Definition 5** A polynomial is defined as a mathematical expression involving sum of powers in one or more variables multiplied by their cofficients (constants). A polynomial with one variable and their constant cofficients is represented by

$$f(x) = a_n x^n + a_{n-1} x^{n-1} + \dots + a_2 x^2 + a_1 x + a_0 = \sum_{i=0}^n a_i x^i$$

where, n (integer  $n \geq 0$ ) is called the degree of the polynomial, where the cofficients  $a_i$ ,  $0 \leq i \leq n$ , are elements of F and x is the symbol which is not belonging to F referred to as indeterminate (symbol which does not stand for anything). F is also called cofficient set, when  $a_n \neq 0$  and such polynomials are known to be defined over F. It is possible to have same powers of x when we compare two polynomials f(x) and g(x) over F.

Let

$$f(x) = \sum_{i=0}^{n} a_i x^i$$

and  $g(x) = \sum_{i=0}^{m} b_i x^i$

A. Addition of f(x) and g(x) is defined by:

$$f(x) + g(x) = \sum_{i=0}^{n} (a_i + b_i) x^i$$

, for  $n = m$

#### **B.** Multiplication of f(x) and g(x) is defined by:

$$f(x) \times g(x) = \left(\sum_{i=0}^{n} a_i x^i\right) \times \left(\sum_{i=0}^{m} b_i x^i\right) = \sum_{k=0}^{n+m} c_k x^k$$

where

$$c_k = \sum_{0 \le i < k} a_i b_{k-i} = a_0 b_k + a_1 b_{k-1} + \dots + a_{k-1} b_1 + a_k b_0.$$

Note that the degree of the product is the sum of the degrees of the two polynomials.

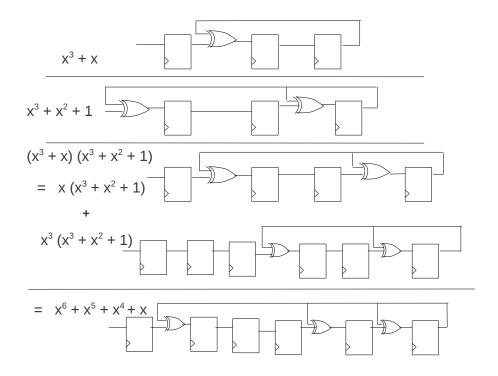

**Example 6:** Let

$$f(x) = x^3 + x^2 + 1$$

and  $g(x) = x^3 + x$ , calculate  $f(x) \times g(x)$

$$x^{3} \times (x^{3} + x^{2} + 1) = x^{6} + x^{5} + x^{3}$$

$$x \times (x^{3} + x^{2} + 1) = x^{4} + x^{3} + x$$

$$= x^{6} + x^{5} + x^{4} + x$$

#### C. Division of m(x) and p(x) is defined by:

Polynomial division over Galois field can be computed using the rules of multiplication and addition. The division of two polynomials  $m(x) \div p(x)$  is defined as  $m(x) = q(x) \times p(x) + r(x)$ , where quotient q(x) and reminder r(x) are results of the division operation.

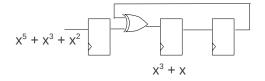

**Example 7:** Let

$$m(x) = x^5 + x^3 + x^2$$

and  $p(x) = x^3 + x$ , calculate  $m(x) \div p(x)$ .

Therefore q(x) is  $x^2$  and r(x) is  $x^2$ .

Verify the above results using the definition:

$$m(x) = q(x) \times p(x) + r(x)$$

=  $(x^{2}) \times (x^{3} + x) + x^{2}$

=  $x^{5} + x^{3} + x^{2}$

**Note:** Polynomials over F are important in constructing the structure of linear feedback shift register sequences (See Section 3.7).

#### **3.3.3** Finite Field of the form $GF(p^n)$ :

In this section we are interested in constructing the finite field of the form  $GF(p^n)$ . In the previous section we saw finite field of the form GF(p) of order p, where p is prime. The elements of  $GF(p) = \mathbb{Z}_p = \{0, 1, 2, ... (p-1)\}$ , under arithmetic operations  $(+, \times)$  are performed with respect to modulo p operation. We use the similar concept to construct the finite field of the form  $GF(p^n)$ , containing q-1 elements, where  $(q=p^n)$  under the reduced module  $p^n-1$  operation.

**Fact:** The set  $GF(p^n)$  along with two arithmetic operations  $(+, \times)$  forms a finite field and the order of the field is  $p^n$ .

**Note:** We denote non zero elements of  $GF(p^n)$  as  $GF(p^n)^*$ .

#### Irreducible Polynomial over Field:

**Definition 6** A polynomial i(x) is known as an **irreducible polynomial** over a field F, if and only if i(x) cannot be derived as a product of two or more polynomials over field F. With analogy to integers, an irreducible polynomial is also called a **prime polynomial**.

Fact: For every prime p and for every degree n > 1, there exists at least one irreducible polynomial of degree n over GF(p).

**Example 8:** Consider the irreducible polynomial  $i(x) = x^3 + x + 1$  over the field GF(2).

The possible factors of i(x) with degree less than i(x) are x and x+1. The product of these two possibilities will not be equal to  $x^3+x+1$ . Therefore, the given i(x) is irreducible polynomial over GF(2).

#### **Primitive Element and Primitive Polynomial:**

**Definition 7** A primitive element of  $GF(p^n)$  is an element which is a generator of a cyclic group  $GF(p^n)^*$ . An irreducible polynomial over GF(p) having zero as a primitive element in  $GF(p^n)$  is called a primitive polynomial over GF(p).

**Note:** Not all irreducible polynomials are primitive.

#### **Root of Polynomial:**

**Definition 8** If p(x) is a polynomial over F, then the element  $\alpha \in F$  such that  $p(\alpha) = 0$  is called a root (or zero) of the polynomial p(x).

#### Subfield:

**Definition 9** If a subset S whose elements are from field F which satisfies the field axioms along with the arithmetic operations of F, then S is called a **subfield** of F.

$GF(p^m)$  is a subfield of  $GF(p^n)$ , if and only if m is a positive divisor of n, i.e.,  $GF(p^m) \subset GF(p^n)$ .

**Example 9:**  $GF(2^2) \subset GF(2^4)$  and  $GF(2^4) \subset GF(2^{12})$

#### **Extension Field:**

**Definition 10** A field F is known as an **extension field**, if S is a subset lying under the set F with respect to the field operations then by definition S is a subfield of F and F is an extension field of S. Which is denoted by F/S and read as "F over S".

If F is an extension field of field L, which in turn an extension of K, then L is an **intermediate field** of the field extension F/S.

To construct (extension field) a finite field of the form  $(GF(p^n), +, \times)$ , of order  $p^n$ , where n is a positive integer, by selecting an irreducible polynomial as f(x) of degree n over GF(p). Let  $\alpha$  be a root of the f(x), which satisfies f(x) as  $f(\alpha) = 0$ . Then  $GF(p^n)$  is defined as [25]

$$GF(p^n) = \{ a_0 + a_1 \alpha + \dots + a_{n-1} \alpha^{n-1} \mid a_i \in GF(p) \}$$

**Note:** Here one should know that the addition operation is done by module GF(p) whereas, the multiplication is done by modulo of irreducible polynomial.

**Example 11:** To construct a finite field of the form  $GF(2^3)$  with irreducible polynomial  $f(x) = x^3 + x + 1$  over the field GF(2).

Let  $\alpha$  be a root of f(x), i.e.  $f(\alpha) = 0$ . The finite field  $GF(2^3)$  is defined as  $\{a_0 + a_1 \alpha + a_2 \alpha^2 \mid a_i \in GF(2)\}$

All the elements of  $GF(2^3)$  can be derived from the given equation  $f(x) = f(\alpha) = \alpha^3 + \alpha + 1 = 0$ , with respect to the modular 7 operation.

The elements of  $GF(2^3)$  are  $0, 1, \alpha, \alpha^2$  and from  $\alpha^3$  they can be derived as  $\alpha^3 = \alpha + 1$ , and  $\alpha^4$  can be written as  $= (\alpha^3)(\alpha) = (\alpha + 1)(\alpha) = \alpha^2 + \alpha$ . Similarly, we can derive rest of the elements.

For the given irreducible polynomial of degree 3, table given below shows 3-tuple binary, polynomial and exponential notations.

| Binary<br>Notation | Polynomial<br>Notation  | Exponential notation  |

|--------------------|-------------------------|-----------------------|

| 000                | 0                       | $0 = \alpha^{\infty}$ |

| 100                | 1                       | $1 = \alpha^0$        |

| 010                | α                       | α                     |

| 001                | $\alpha^2$              | $\alpha^2$            |

| 110                | $1 + \alpha$            | $\alpha^3$            |

| 011                | $\alpha + \alpha^2$     | $\alpha^4$            |

| 111                | $1 + \alpha + \alpha^2$ | $\alpha^5$            |

| 101                | $1+\alpha^2$            | $\alpha^6$            |

|                    | $\alpha^7 = 1$          |                       |

Here the elements of  $GF(2^3)$  are represented in polynomial notation (basis and is explained in section 3.4) and exponential notation which represents the elements in  $GF(2^3)$ . Also note that,

GF(2<sup>3</sup>)\* i.e. the non zero elements of GF(2<sup>3</sup>) form a cyclic group of order 7 with generator  $\alpha$ , where  $\alpha^7 = 1$ .

The polynomial f(x) and  $\alpha$  is called the defining polynomial and defining element respectively. We can say that  $GF(2^3)$  is the *extension field* of GF(2).

For instance, addition of two elements  $(1 + \alpha + \alpha^2)$  and  $(1 + \alpha)$  is  $(1 + \alpha + \alpha^2) + (1 + \alpha^2) = \alpha$ .

For multiplication, it can be written in a simpler way as  $(1 + \alpha + \alpha^2) = \alpha^5$  and  $(1 + \alpha^2) = \alpha^6$ . Therefore  $(1 + \alpha + \alpha^2)(1 + \alpha^2) = \alpha^5\alpha^6 = \alpha^{11} = \alpha^4 = \alpha + \alpha^2$

#### **Trace Function:**

**Definition 11** Suppose,  $F = GF(p^n)$  and K = GF(p), then the trace function  $Tr_{F/K}(x)$  is defined by

$$Tr(x) = Tr_{F/K}(x) = x + x^p + \dots + x^{p^{n-1}} = \sum_{i=0}^{n-1} x^{p^{i+1}}, x \in F$$

The trace function Tr(x) converts  $GF(p^n) \to GF(p)$

**Example 11:** For the finite field  $GF(2^3)$  which is defined by  $\alpha^3 + \alpha + 1$ . Compute  $Tr(\alpha)$  and  $Tr(\alpha^3)$ .

From the trace function Tr(x), when p=2 and n=3, we can extract  $Tr(\alpha)=\alpha+\alpha^2+\alpha^4=\alpha+\alpha^2+\alpha+\alpha^2=0$ , Similarly for  $Tr(\alpha^3)=\alpha^3+\alpha^6+\alpha^5=(1+\alpha)+(1+\alpha^2)+(1+\alpha+\alpha^2)=1$

### 3.4 Basis

Basis can be defined based on the circumstances being used. For instance, an element in a finite field can be represented in the form of a basis. Since, we are interested in finite fields where two types of basis exists; *polynomial basis* and *normal basis*. Thus an element in a finite field can be represented either in polynomial [26] [27] or normal basis [28] [29] [30].

#### **Polynomial Basis:**

**Definition 12** Consider the finite field as  $GF(p^n)$  and let  $\alpha \in GF(p^n)$  be the root of an irreducible polynomial of degree n over GF(p). Then the **Polynomial basis** is represented as  $\{1, \alpha, \alpha^2 \dots \alpha^{n-1}\}$  of  $GF(p^n)$  over GF(p).

Where  $\alpha$  is called a primitive element of  $GF(p^n)$ .

**Example 12:** If p = 3 and n=2. then  $GF(3^2)$  is a simple extension field of GF(3) of degree 2. Let  $\alpha \in GF(3^2)$ , be a root of the irreducible polynomial  $x^2 + 1$  over GF(3), then the polynomial basis is  $\{1, \alpha\}$  of  $GF(3^2)$  over GF(3).

#### **Normal Basis:**

**Definition 13** For any positive integer n in  $GF(p^n)$ , there will be always a normal basis for the finite field  $GF(p^n)$  over GF(p). If  $\gamma \in GF(p^n)$  be a normal element, then the **normal basis** is represented as  $\{\gamma, \gamma^{2^1}, \alpha^{2^2} \dots \gamma^{2^{n-1}}\}$ .[31].

where  $\gamma$  is called a generator or normal element of  $GF(p^n)$  over GF(p). Which is is represented in the form of  $n \times m$  matrix and denoted by M.

**Example 13:** If p = 2 and n=3. then  $GF(2^3)$  is a simple extension field of GF(2) of degree 3. Let  $\alpha \in GF(2^3)$ , be a root of the irreducible polynomial  $x^3 + x^2 + 1$  over GF(2), then the normal basis is  $\{\alpha, \alpha^2, 1 + \alpha + \alpha^2\}$  of  $GF(2^3)$  over GF(2).

### 3.4.1 Selection of basis for hardware implementation:

In this section we briefly discuss about the selection of basis for the finite field arithmetic operations especially for hardware implementation. We know that finite fields play a vital role in cryptography and especially in symmetric and asymmetric key cryptosystems which involve finite field arithmetic operations.

Usually arithmetic operations over  $GF(2^n)$  are performed under reduced modulo of the irreducible polynomial f(x) over GF(2). Arithmetic addition and subtraction operations are performed under modulo 2. Addition of two polynomials is nothing but the bit-wise exclusive-or (XOR) operation of their binary representation whereas multiplication operation is the complex and time consuming over the field  $GF(2^n)$ . Complexity is based on the selection of irreducible polynomial and the basis used to represent the finite field elements. Besides that there are past publications [32] [33], where they talk about the efficient implementation of finite field arithmetic.

Polynomial basis is considered for hardware optimizations, because in polynomial basis the the multiplication operation can be implemented using simple shift and XOR operations [34]. In normal basis hardware implementation for squaring an element is simply a right cyclic shift of its coordinates [31]. Therefore, squaring in normal basis is simple and cost effective. But, multiplication in normal basis is more complex. Complex in terms of utilization of hardware

resources such as number of logic gates, area and so on. To overcome this in normal basis, in [35] they introduced the optimal normal basis.

Optimal normal basis holds an upper hand in efficient hardware resources utilization [28] [29], such as number of logic gates, XOR and AND gates compared to normal basis. In section 5, we have seen two types of optimal normal basis, type I and type II. Type I basis are efficient in hardware implementation over  $GF(2^n)$ , but the drawback is that they are not suitable to some of the cryptographic areas since n is even [31] whereas type II is suitable since n can be odd. Since then number of researchers started to introduce efficient implementation of multipliers using type II [31] [33] [28] [29].

# 3.5 LFSR and mathematical description:

Linear feedback shift register (LFSR) have been widely used in keystream generators in stream ciphers, random number generators in most of the cryptographic algorithms. In this section we discuss about LFSR definitions and their sequence representation. Each of the square blocks in figure 3.1, is a 2 state (0 or 1) storage units. The n binary storage units are called as the stages of the shift register and their contents are in the form of n bits in length, which is called as the internal state of the shift register.

Figure 3.1: Block diagram of LFSR

Let  $(a_0, a_1, a_2, ..., a_{n-1}) \in GF(2^n)$  be the initial state of the LFSR and  $f(x_0, x_1, x_2, ..., x_{n-1})$  be the feedback function or feedback polynomial, as shown in figure 3.1. If the feedback function is a linear function then it can be expressed as

$$f(x_0, x_1, x_2, ..., x_{n-1}) = c_0 x_0 + c_1 x_1 + c_2 x_2 + ..... + c_{n-1} x_{n-1}, \ c_i \in GF(2)$$

(3.1)

After each consecutive clock pluses the LFSR will generate a output binary sequence  $\underline{b}$  of the form  $\underline{b} = a_0, a_1, ...$

The output sequence of the LFSR satisfies the following recursive relation [24]

$$a_{k+n} = \sum_{i=0}^{n-1} c_i a_{k+i}, \quad k = 0, 1, \dots$$

(3.2)

The output of the LFSR is considered as a linear recursive sequence. If the feedback function is linear then the output sequence is called LFSR sequence. Otherwise it is called as the *nonlinear feedback shift register* (NLFSR) sequence.

**Notes:** Let  $\underline{b}$  is the binary sequence. In general the linear feedback function equation (3.2) is represented in polynomial of the form  $f(x) = x_n + c_{n-1}x_{n-1} + ... + c_1x + c_0$ , which is known as the *characteristic polynomial* of the LFSR.

**Example 1:** Consider a 3-stage LFSR as shown in figure 3.2 with the linear feedback function  $f(x_0, x_1, x_2) = x_0 + x_1$  with initial state as (1, 0, 0) equivalent to  $(a_0, a_1, a_2)$ . The output sequence would be 10010111001011... which is repeated periodically with a period of 7.

Figure 3.2: 3-stage LFSR

### 3.5.1 Different types of sequences:

- 1. **Binary Sequence:**  $\underline{b} = b_i$ ,  $b_i \in GF(2)$ , is a binary sequence over GF(2).

- 2. **M-Sequence:** The output sequence generated by an n-stage LFSR with non zero initial values and has maximal period  $2^n 1$  is know as the maximal length sequence or in short called as m sequence [25].

- 3. **De-Bruijn sequence:** De-Bruijn sequence is the output of an n-stage NLFSR having period  $2^n$  and satisfies the n-tuple occurrence exactly once in each period. From any m sequence with period as  $2^n 1$  we can obtain the de-Bruijin sequence by inserting a 0 into the run of n-1 consecutive zeros of the m sequence [25].

**Example 2:** Consider a 4-stage LFSR as shown in figure 3.3 with the characteristic polynomial  $f(x) = x^4 + x + 1$  and with the initial state as (0,0,0,1) equivalent to  $(a_0,a_1,a_2,a_3,a_4)$ . The output is a m - sequence is 0001001101011111000100... which is repeated periodically with a period of 15.

Figure 3.3: 4-stage LFSR

### 3.5.2 Advantages of LFSR Properties:

Since LFSR's are widely used in keystream generators. To consider LFSR based keystream generators as cryptographically secure, the design of LFSR should have the following desirable properties [21].

- 1. Large Period.

- 2. Large Linear complexity.

- 3. Good statistical properties.

**Notes:** If  $\underline{b}$  is a binary sequence then the linear complexity of  $\underline{b}$  is the shortest length of the LFSR that generates  $\underline{b}$ . It is denoted by LS( $\underline{b}$ ). For any given  $\underline{b}$  of length N, one can compute the linear span of the sequence using the *Berlekamp-Massey algorithm*.

# 3.5.3 Hardware implementation of LFSR over Galios fields:

In hardware implementation the LFSR contains N registers connected together to form a shift register. Generally, shift register is a sequence of flip flops in which the output of the last flip flop is connected (feedback) to the earlier flip flops by an XOR gate as shown in figure 4. Suppose the length of the LFSR is N than it consists of N – stages of flip-flops and the stored bits are controlled by a single clock. At each clock pulse, the bits in the storage elements is shifted by one position (right position) to the next stage, that is, there is a transition from one state to next.

Figure 3.4: 3-bit LFSR circuit

Some of the design parameters when designing LFSR are the number of flip flops, external or internal XOR gates, feedback taps (inputs fed to the XOR) and reset signal. On reset the register is set to all 1's and for analysis purpose here we use LFSRs with internal XOR gates since their circuitry are matched with the polynomials over the Galois fields.

The LFSR generates a maximum bit sequence of length  $2^n-1$  combinations, where n is the size of the finite field. The feedback taps on the LSFR is selected based on the chosen polynomial over the finite field. Polynomial arithmetic operations are carried out with respect to the  $mod\ 2$  operations i.e. the coefficients of the polynomial must be either 1's or 0's. These polynomials are called feedback or characteristic polynomials. The LFSR bit sequence can be represented by the characteristic polynomial. If the bit sequence is 110011 then the characteristic polynomial is denoted as  $x^5 + x^4 + x^1 + 1$ .

**Example 3:** Represent the LFSR for the characteristic polynomial  $p(x) = x^5 + x^4 + x^2 + x + 1$ .

Figure 3.5: LFSR implementing characteristic polynomial

From the above example exponents of polynomial are represented as:  $x^0$  is the input to the LFSR,  $x^1$  is the output of the first flip flop and  $x^2$  is the output of the second and so on. Moreover the maximum exponent of the polynomial represents the number of flip flops used in the LFSR.

other exponents denote the flip flops with or without tap connections to the feedback line from the last flip flop.

## 3.5.4 Polynomial multiplication and division in LFSR:

Using the example 6 from section 3.3.2, the multiplication  $f(x) \times g(x) = (x^3 + x^2 + 1) \times (x^3 + x)$  circuit using LFSR is shown in figure below.

Figure 3.6: LFSR implementing multiplication

Similarly, by reusing the example 7, the division of  $m(x) = x^5 + x^3 + x^2$  and  $p(x) = x^3 + x$  can be implemented using LFSR is shown in the figure below.

Figure 3.7: LFSR implementing division