# Impact of Mechanical Stress on the Electrical Stability of Flexible a-Si TFTs

by

Melissa J. Chow

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2011 © Melissa J. Chow 2011 I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The development of functional flexible electronics is essential to enable applications such as conformal medical imagers, wearable health monitoring systems, and flexible lightweight displays. Intensive research on thin-film transistors (TFTs) is being conducted with the goal of producing high-performance devices for improved backplane electronics. However, there are many challenges regarding the performance of devices fabricated at low temperatures that are compatible with flexible plastic substrates. Prior work has reported on the change in TFT characteristics due to mechanical strain, with especially extensive data on the effect of strain on field-effect mobility. This thesis investigates the effect of gate-bias stress and elastic strain on the long-term stability of flexible lowtemperature hydrogenated amorphous silicon (a-Si:H) TFTs, as the topic has yet to be explored systematically.

An emphasis was placed on bias-stress measurements over time in order to obtain information on the physical mechanisms of instability. Drain current was measured over various intervals of time to track the degradation of devices due to metastability, and results were then compared across devices of various sizes under tensile, compressive, and zero strain. Transfer characteristics of the TFTs were also measured under the different conditions, to allow for extraction of parameters that would provide insight into the instability mechanisms. In addition to parameter extraction, the degradation and recovery of TFT output current was quantitatively compared for various bias-stress times across the different levels of strain. Finally, the instability mechanisms are modelled with a Markov system to further examine the effect of strain on long-term TFT operation.

From the analysis of results, it was found that shallow charge trapping in the dielectric is the main mechanism of instability for short bias stress times, and did not seem to be greatly affected by strain. For longer bias stress times of over 10000 seconds, defect creation in the a-Si:H becomes a more significant contributor to instability. Both tension and compression increased defect creation compared to TFTs with zero applied strain. Compression appeared to cause the greatest increase in the rate of defect formation, likely by weakening Si-Si bonds in the a-Si:H. Tension appeared to cause a less significant increase, possibly due to a strengthening of some proportion of the Si-Si bonds caused by the slight elongation of bond length or because the applied tension relieves intrinsic compressive stress in a-Si:H film. A longer conduction path and greater dielectric area appears to increase the bias-stress and strain-related effects. Therefore reducing device size should increase the reliability of flexible TFTs.

#### Acknowledgements

I would like to acknowledge Reza Chaji for sparking the initiation of the study, and for his helpful recommendations. I would like to thank Arash Fomani and Maryam Moradi for their help with device fabrication and data analysis. Thank you for taking the time for our numerous insightful discussions.

I am especially grateful towards William Wong for his invaluable guidance and faithful encouragement. This work would truly not have been possible without your support. A bucket of thanks to René Lujan and the Palo Alto Research Center for fabricating and flying in some TFTs to save the day.

I would also like to express my earnest thanks for the contributions of the following people:

To Mohammad Esmaeili Rad, Nikolas Papadopoulos, and Salman Kabir for always being available and open for discussion; your advice is greatly appreciated. To Sanjiv Sambandan for providing enlightening information regarding modelling. To Minoli Pathirane for her help with the initial fabrication processes. To Siva Sivoththaman and Hany Aziz for reading my thesis, and to Arokia Nathan and Andrei Sazonov for their input. To Richard Barber, Rossi Ivanova and Roger Grant for their assistance with laboratory and test equipment; without your help the measurements would surely not have gone as smoothly. To Karl Janzen and the UW Engineering Machine Shop for their efforts with the testbench. Finally, I would like to thank Zhao Li for providing tips and resources on IAT<sub>F</sub>X formatting.

Lastly, I wish to acknowledge the support of Ignis Innovation Inc. and the University of Waterloo.

### Dedication

For the pursuit of knowledge.

# Table of Contents

| List of Tables |       |                                 |    |  |  |  |

|----------------|-------|---------------------------------|----|--|--|--|

| $\mathbf{Li}$  | st of | Figures                         | x  |  |  |  |

| 1              | Intr  | oduction                        | 1  |  |  |  |

|                | 1.1   | Applications of flexible TFTs   | 1  |  |  |  |

|                | 1.2   | Advantages of amorphous silicon | 3  |  |  |  |

|                | 1.3   | Motivation                      | 5  |  |  |  |

| <b>2</b>       | Bac   | kground on a-Si:H TFTs          | 7  |  |  |  |

|                | 2.1   | Properties of amorphous silicon | 7  |  |  |  |

|                | 2.2   | Device structure                | 11 |  |  |  |

|                | 2.3   | TFT operation                   | 13 |  |  |  |

|                |       | 2.3.1 Above threshold           | 14 |  |  |  |

|                |       | 2.3.2 Subthreshold              | 15 |  |  |  |

|                | 2.4   | Metastability                   | 17 |  |  |  |

|    |                      | 2.4.1  | Charge trapping                 |    |

|----|----------------------|--------|---------------------------------|----|

|    |                      | 2.4.2  | Defect creation                 |    |

|    |                      | 2.4.3  | Relaxation                      | 25 |

| 3  | Exp                  | erime  | nt                              | 26 |

|    | 3.1                  | Prior  | work                            |    |

|    | 3.2                  | Appro  | pach                            | 28 |

|    | 3.3                  | Measu  | rement procedure                | 29 |

|    | 3.4                  | Testbe | $\operatorname{ench}$           | 30 |

| 4  | $\operatorname{Res}$ | ults   |                                 | 34 |

|    | 4.1                  | TFT I  | parameters and bias stress      | 34 |

|    | 4.2                  | Bias s | stress degradation and recovery | 43 |

|    | 4.3                  | Model  | lling of trapping               | 50 |

| 5  | Cor                  | clusio | ns                              | 57 |

| Re | efere                | nces   |                                 | 59 |

# List of Tables

| 3.1 | Calculated values of strain                  | 32 |

|-----|----------------------------------------------|----|

| 4.1 | Percent threshold voltage shift              | 47 |

| 4.2 | Percent of threshold voltage shift recovered | 48 |

# List of Figures

| 1.1  | Exploded cross-section of an AMOLED display panel | 2  |

|------|---------------------------------------------------|----|

| 1.2  | 2-T pixel circuit                                 | 3  |

| 1.3  | Comparison of mobility for various TFT materials  | 5  |

| 2.1  | Structure of amorphous vs. crystalline silicon    | 8  |

| 2.2  | Density of states in amorphous silicon            | 8  |

| 2.3  | Conductance of doped TFTs vs. strain $[1]$        | 10 |

| 2.4  | Various TFT structures                            | 11 |

| 2.5  | TFT cross-section                                 | 12 |

| 2.6  | TFT in operation                                  | 13 |

| 2.7  | Energy band diagram for the gate of a TFT         | 13 |

| 2.8  | Example of subthreshold slope $(S_f)$ extraction  | 16 |

| 2.9  | Charge trapping mechanisms [2]                    | 18 |

| 2.10 | Energy band diagram of charge trapping mechanism  | 19 |

| 2.11 | Localized defect creation process [3]             | 21 |

| 2.12 | Energy diagram of defect creation [3]                                                                                                                            | 22 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.13 | Density distribution of defect states $[4]$                                                                                                                      | 23 |

| 3.1  | Model for surface strain calculation                                                                                                                             | 31 |

| 3.2  | TFT sample mounted on strain testbench                                                                                                                           | 33 |

| 4.1  | An example of measured vs. simulated $I_{DS}$ vs. $V_{GS}$                                                                                                       | 36 |

| 4.2  | Normalized $R_{DS}$ , $\alpha$ , $V_T$ and $\mu_{eff}$ vs. strain                                                                                                | 37 |

| 4.3  | $R_{DS}$ and normalized $R_{DS}$ vs. total bias stress time $\ldots \ldots \ldots \ldots \ldots$                                                                 | 38 |

| 4.4  | $\alpha$ vs. total bias stress time (initial values are plotted with dashed lines)                                                                               | 39 |

| 4.5  | $V_T$ and normalized $V_T$ vs. total bias stress time $\ldots \ldots \ldots \ldots \ldots$                                                                       | 40 |

| 4.6  | $\mu_{eff}$ and normalized $\mu_{eff}$ vs. total bias stress time                                                                                                | 41 |

| 4.7  | Data for $S_f$ extraction $\ldots \ldots \ldots$ | 42 |

| 4.8  | $S_f$ and normalized $S_f$ vs. total bias stress time $\ldots \ldots \ldots \ldots \ldots \ldots$                                                                | 42 |

| 4.9  | Example of bias stress degradation and recovery data                                                                                                             | 43 |

| 4.10 | Log-log plot of normalized $V_T$ shift over 1000 s bias stress                                                                                                   | 45 |

| 4.11 | Normalized $I_{DS}$ and normalized $V_T$ shift for 100 s bias stress and recovery .                                                                              | 46 |

| 4.12 | Normalized $I_{DS}$ and normalized $V_T$ shift for 1000 s bias stress and recovery                                                                               | 47 |

| 4.13 | Normalized $I_{DS}$ and $V_T$ shift for 10000 s bias stress and recovery; dotted line                                                                            |    |

|      | is for a device with W/L = 200/8 instead of 200/16 $\hdots$                                                                                                      | 48 |

| 4.14 | Markov model of trapping                                                                                                                                         | 51 |

| 4.15 | Sample calculation of $\lambda_1$ , $\lambda_2$ and $\varphi$ from measured $V_T$ shift $\ldots \ldots \ldots$                                                   | 53 |

| 4.16 | Values and normalized values for $r_{01}$ |    |    | • | <br> | <br>• | <br>• | <br> | • | <br>53 |

|------|-------------------------------------------|----|----|---|------|-------|-------|------|---|--------|

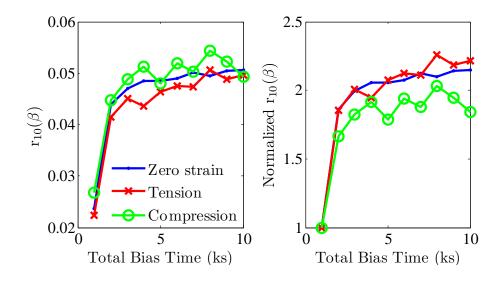

| 4.17 | Values and normalized values for $r_{10}$ |    |    |   | <br> |       | <br>• | <br> |   | <br>54 |

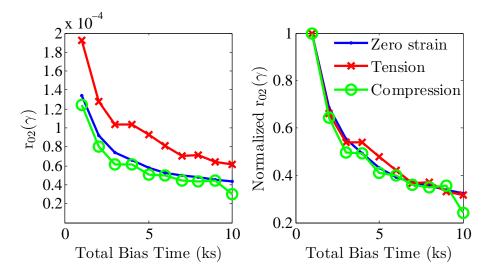

| 4.18 | Values and normalized values for $r_{02}$ | •  |    |   | <br> | <br>• | <br>• | <br> |   | <br>54 |

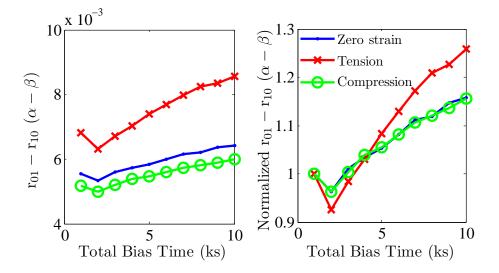

| 4.19 | Values and normalized values for $r_{01}$ | -r | 10 |   | <br> |       |       | <br> | • | <br>55 |

# Chapter 1

# Introduction

### **1.1** Applications of flexible TFTs

Flexible large-area electronics are an area of increasing research interest, and offer a wealth of potential applications. Flexible films have the inherent advantage of being lightweight and immune to shattering, making them well-suited for implementation in portable devices. Flexibility also provides new freedoms in terms of design by enabling the development of conformal or flexible displays and sensors. Examples of applications under development include contact-lens displays [5]; hemispherical imaging arrays that allow for wide-angle viewing [6]; wearable health monitors; as well as flexible electronic readers [7].

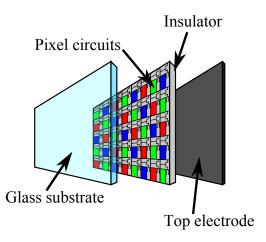

A common component to both display and imaging applications is the thin-film transistor (TFT). TFTs are used in active-matrix backplanes, which allow for highly responsive and precise control of the arrays of lighting or sensor elements that form display or imaging screens. A cross-section of a typical active-matrix organic light-emitting diode (AMOLED) display panel is shown in Figure 1.1. Each lighting unit in the array, or pixel, is typically

Figure 1.1: Exploded cross-section of an AMOLED display panel

comprised of a red, a green and a blue subpixel. Each subpixel contains an OLED and a pixel circuit with TFTs to control the OLED. By varying the intensity of each subpixels' output, their combined output is capable of rendering a range of colours at various brightness.

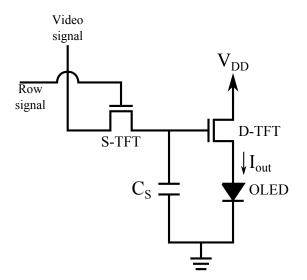

A simple 2-transistor circuit that can be used to control a subpixel of a display is illustrated in Figure 1.2. First, a signal is applied across a horizontal row of subpixels, turning on the switch TFT (S-TFT). The row is then ready to receive video signals from the vertical lines. The vertical lines program each OLED in the activated row by applying a voltage to the gate of the drive TFT (D-TFT), which delivers the necessary current for the OLED to emit light at the required intensity. The S-TFTs are then switched off for the row, isolating the OLEDs from the vertical lines. Voltage at the gate of the D-TFT is maintained by charge stored on capacitor  $C_S$ , holding the OLED output at the required level. The S-TFTs in the next row are then switched on, and the above procedure repeats until the rest of the screen is programmed.

The components and functionality of a sensor panel are similar to those of the display

Figure 1.2: 2-T pixel circuit

panel described above. If the OLEDs are replaced with photodiodes, each pixel becomes a sensor that converts incident light into electrical signals that can be recorded, capturing the image.

## 1.2 Advantages of amorphous silicon

Researchers have demonstrated functional flexible TFTs fabricated from a variety of materials. The research documented in this thesis focusses on hydrogenated amorphous silicon (a-Si:H) TFTs, as they offer several key advantages. Firstly, a-Si:H TFTs are currently in widespread commercial production, most notably for application in flat-screen display panels. Flexible a-Si:H TFTs can be produced by the same processes, which facilitates adoption of the technology by industry as there is no need for investment in novel fabrication equipment. Existing knowledge can be applied towards the development of flexible a-Si:H TFTs as they are based on a relatively mature technology. There are several other advantages with a-Si:H with respect to fabrication. It can be deposited uniformly over large substrates, making it ideally suited for large-area electronics. Large substrates are desirable as not only can larger panel sizes be produced, an increasing number of panels can be cut from a single substrate for efficient large-volume production. The fabrication of a-Si:H TFTs is also possible at relatively low temperatures such as 120C, enabling the use of inexpensive, flexible plastic substrates which typically have glass-transition temperatures in the range of 80 °C to 150 °C [8].

Another advantage is that a-Si:H can be finely patterned by photolithography. Although TFTs in most commercial display applications have minimum feature sizes on the order of tens of micrometers, the limit of the technology is below the submicron level. Being an amorphous material, a-Si:H forms good interfaces with a variety of materials. This is significant as interface properties, especially between the semiconductor channel and gate dielectric of a TFT, are important determinators of device performance. This also allows for flexibility in terms of processing and selection of materials for TFT substrates and device layers.

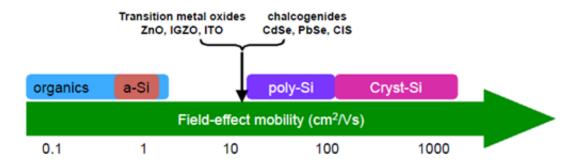

Although organic TFTs may be simple and cheap to fabricate as well [9], amorphous silicon has a relatively high mobility compared to organic materials. Figure 1.3 shows a comparison of the mobility of a-Si:H with other TFT materials. Crystalline and polycrystalline silicon can offer higher mobility but also require high temperature processes which would damage flexible plastic substrates or additional unconventional process steps. At about  $1 \text{ cm}^2/\text{V} \cdot \text{s}$ , the electron mobility of amorphous silicon is more than sufficient for display applications [10]. High mobility is necessary for good current driving ability, which allows a large amount of current to be controlled by a device with small area. This is important for applications such as the drive TFT shown previously in Figure 1.2, as a smaller device size minimizes the area of the pixel circuit. More space is then available for

Figure 1.3: Comparison of mobility for various TFT materials

a larger OLED which results in a higher resolution display.

## 1.3 Motivation

A major challenge of developing flexible displays and sensors with amorphous silicon is electrical metastability. The electrical characteristics of a-Si:H TFTs, such as threshold voltage, gradually shift over time when a gate bias is applied. The metastability leads to a degradation in the operation of TFT circuits and limits the device lifetime. Taking the pixel circuit in Figure 1.2 as an example, metastability is present in the TFTs controlling the output current of the OLEDs and causes the current to decrease over time. This phenomenon leads to a decrease in the brightness of the pixels, and eventually causes the display to become perceptibly dimmer.

In order to advance flexible a-Si:H TFT technology, it is necessary to gain a better understanding of the shift mechanisms under the influence of applied mechanical strain. Such knowledge could then be applied at the device level to design more robust flexible TFTs. Alternately, systems can be designed to compensate for instability using knowledge of the long-term device behaviour. The effects of applied strain, occurring when a flexible device is bent, on the physical mechanisms of instability are not well characterized. Hence, it is the goal of the research presented in this thesis to investigate the impact of simultaneous electrical and mechanical stress on the behaviour of flexible a-Si:H TFTs.

# Chapter 2

# Background on a-Si:H TFTs

## 2.1 Properties of amorphous silicon

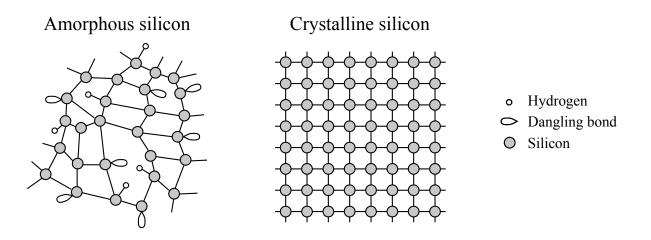

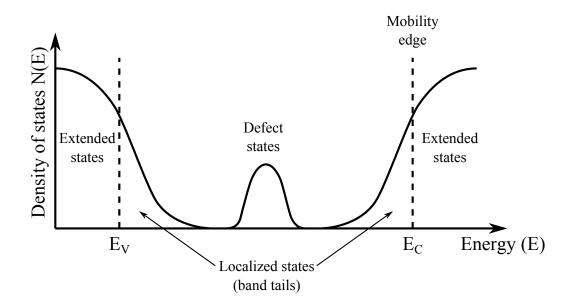

Over a short range of a few interatomic distances, the structure of amorphous silicon closely resembles that of crystalline silicon, with valence and conduction bands formed from the splitting of the sp3 hybrid orbitals in tetrahedrally bonded silicon. Therefore both the amorphous and crystalline phases have similar overall electronic structure, with band gaps of about 1.7 eV and 1.1 eV respectively [10]. The disordered structure of amorphous silicon becomes apparent over longer ranges, and influences its electronic properties in various ways. The variation in bond lengths and angles in amorphous silicon form broad band tails at the conduction and valence bands instead of the clearly defined band edges in crystalline silicon. Amorphous silicon also contains coordination defects as shown in Figure 2.1, which can lead to electronic states deep within the mobility gap. Such defects can occur in the a-Si:H bulk, but are also common at the semiconductor-dielectric interface. The conduction and valence bands, band tails and deep defect states in amorphous silicon

Figure 2.1: Structure of amorphous vs. crystalline silicon

are described by the distribution of the density of states N(E) as illustrated in Figure 2.2.

Figure 2.2: Density of states in amorphous silicon

The band tails in amorphous silicon consist of localized states and are separated from

the extended states in the conduction band by the mobility edge. The localized states are defined as such as carriers in the states are confined to a small volume of the material and do not contribute to conduction at T = 0 K [11]. The localized states in the upper half of the mobility gap act as acceptor-like states which are neutral when empty and negatively charged when filled with an electron. The localized states closer to the valence band act as donor-like states that a positively charged when empty and neutral when filled with an electron. The density of states (DOS) in the band tails are given by exponential equations as a function of energy [10]:

$$g_A(E) = g_{nt} \exp\left(\frac{E - E_C}{E_{nt}}\right)$$

$$g_D(E) = g_{pt} \exp\left(\frac{E_V - E}{E_{pt}}\right)$$

(2.1)

$g_A(E)$  and  $g_D(E)$  are the density of acceptor-like and donor-like states respectively.  $g_{nt}$ and  $g_{pt}$  are the DOS at  $E_C$  and  $E_V$  for the tail states as shown in Figure 2.2.  $E_{nt} = kT_{nt}$ and  $E_{pt} = kT_{pt}$  are defined as the characteristic slopes of the conduction and valence band tails, with k being the Boltzmann constant, and characteristic temperatures of  $T_{nt}$  and  $T_{pt}$ .

Conduction in a-Si:H mainly occurs through a combination of movement of carriers through the extended states and hopping in the localized states [12]. The conductivity in the extended states is given by

$$\sigma = \sigma_0 \exp^{\frac{E_F - E_C}{kT}} \tag{2.2}$$

$$= q\mu_{band}n_{band} \tag{2.3}$$

where  $n_{band}$  is the extended states and  $\mu_{band}$  is the mobility in the extended states. Therefore  $n_{band} = N_b \exp((E_F - E_C)/kT)$  with  $N_b = \sigma_0/q\mu_{band}$ . In the conduction band,  $\sigma_0 \approx 350 \ \Omega^{-1} \cdot \text{cm}^{-1}$  and the band mobility  $\mu_{band} \approx 13 \ \text{cm}^2/\text{V} \cdot \text{s}$  [11]. The Fermi energy is dependent on the DOS distribution and is ~ 0.6 meV below  $E_C$  at room temperature [10].  $E_F$  is slightly closer to the conduction band as the valence band tail is wider than the conduction band tail. In state-of-the-art a-Si:H, hopping in the deep states around  $E_F$  is an insignificant mechanism of conduction as there is a low density of defects  $(10^{15} - 10^{16} \text{ cm}^{-3})$ due to hydrogen passivation [13]. However, the deep defect states influence the behaviour of a-Si TFTs by acting as traps for carriers.

The band mobility is much higher for electrons than holes in a-Si:H, and consequently TFTs for most practical applications are n-type.  $\mu_{band}$  is significantly limited by scattering in disordered material, as evident in comparing  $\mu_{band} \approx 13 \text{ cm}^2/\text{V} \cdot \text{s}$  for electrons in a-Si:H whereas the room temperature mobility of c-Si is ~1000 cm<sup>2</sup>/V · s. Scattering increases with the amount of disorder in the material which causes  $\mu_{band}$  to vary with mechanical strain [10].

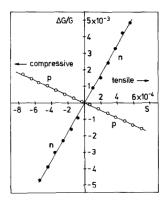

Consequently, the conductivity is also affected by strain. Strain can change the level of disorder in the material (i.e. by slightly altering bond lengths and angles), which affects the width of the distribution of tail states. The change in the charge distribution in the localized states leads to a slight shift in the Fermi level. For n-type material, compression lowers conductivity while the opposite is true for tension as shown in Figure 2.3. Similar

Figure 2.3: Conductance of doped TFTs vs. strain [1]

behaviour can be expected for n-type TFTs, and has been observed in previous experiments [14, 15].

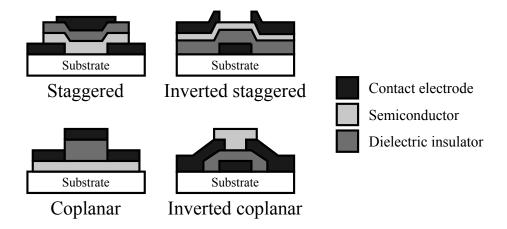

### 2.2 Device structure

The TFTs used in this study featured an inverted, staggered structure. This structure is commonly used in the production of TFTs for research and commercial purposes due to several benefits [9]. Various TFT structures are shown in Figure 2.4. With the inverted

Figure 2.4: Various TFT structures

structure, also known as a bottom-gate TFT, the gate dielectric is deposited before the semiconductor channel of the device. The dielectric and semiconductor layers are conventionally deposited by plasma-enhanced chemical vapour deposition (PECVD). With a non-inverted top-gate structure, where the semiconductor layer is deposited first, the plasma used for depositing the dielectric can damage the semiconductor near the interface of the two materials. This process may lead to poor device performance as TFT operation relies on the formation of an accumulated electron channel close to the interface. Therefore,

the inverted structure is more likely to produce TFTs with good characteristics.

The coplanar structure arranges the gate, source and drain on the same side of the semiconductor, which creates a conduction channel that is closer to the ideal structure assumed by most TFT models [16]. However, offsets between the edge of the gate and the source/drain will lead to a high series resistance which degrades the performance of the device. This is not a problem with the staggered structure as it includes some overlap between the source/drain and gate, which creates a relatively large contact area.

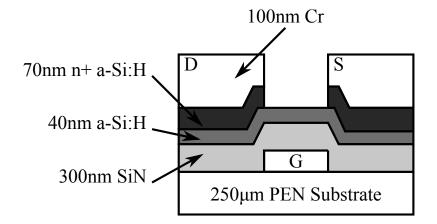

A cross-section diagram of a typical device used in this study is shown in Figure 2.5. A 250 µm-thick polyethylene naphthalate (PEN) film was used as a substrate to allow for

Figure 2.5: TFT cross-section

flexibility. The TFTs were fabricated with a 4-mask back-channel-etch (BCE) process with a maximum temperature of 150 °C. First, the gate metal layer is patterned from 100 nm of Cr sputtered onto the substrate. Next, the gate dielectric layer is deposited by PECVD of a 300 nm-thick layer of a-SiNx:H, followed by 40 nm of a-Si:H forming the semiconductor channel, and 70 nm of n+ doped nc-Si:H for low-resistance source/drain contacts. The top metal layer is deposited by sputtering 100 nm of Cr. The drain and source contacts are then patterned by etching down to the a-Si:H layer. Lastly, an encapsulation layer of 300 nm a-SiNx:H was deposited on top of the samples.

## 2.3 TFT operation

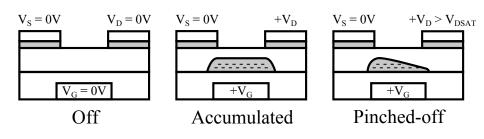

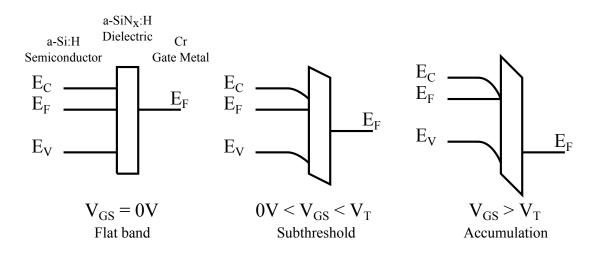

The operation of a typical n-type, accumulation-mode TFT is illustrated by Figure 2.6 and the energy band diagrams in Figure 2.7. The device is off without applied bias to the gate.

Figure 2.6: TFT in operation

Figure 2.7: Energy band diagram for the gate of a TFT

When  $V_{GS}$  is increased, the Fermi level moves towards the conduction band and electrons

accumulate near the gate to form a channel for conduction. The n+ doped material at the source and drain also contribute mobile carriers to help form the channel. When  $V_{DS}$  is subsequently increased, a drain-source current is generated. The TFT essentially acts as a resistor, with  $I_{DS}$  increasing linearly with  $V_{DS}$ . Further increasing  $V_{DS}$  will eventually cause the accumulation at the drain to decrease due to the lower potential difference from the gate, leading to a pinched-off channel as shown in Figure 2.6. This causes the device current to saturate at a maximum value.

#### 2.3.1 Above threshold

The above-threshold characteristics of the TFTs can be described by a model developed by P. Servati [17]. This model was chosen as it accounts for parasitic elements such as contact resistance and provides information on the physical properties of the devices. According to this model, the above-threshold drain-source current is described as

$$I_{DS} = \frac{\mu_{eff}}{\alpha} \zeta C_i^{\alpha - 1} \frac{W}{L_{eff}} \left[ (V'_{GS} - V_T)^{\alpha} - (V'_{GD} - V_T)^{\alpha} \right]$$

(2.4)

where  $\mu_{eff}$  is the effective mobility,  $C_i$  the gate capacitance which was measured to be approximately 20 nF/cm<sup>2</sup>, W is the device width,  $L_{eff}$  is the effective length, and  $V_T$  is the threshold voltage.  $V'_{GS}$  and  $V'_{DS}$  are the terminal voltages with contact resistance taken into account:

$$V'_{GS} = V_{GS} - I_{DS}R_S$$

and  $V'_{DS} = V_{DS} - I_{DS}(R_S + R_D)$  (2.5)

$\zeta$  is related to the properties of the a-Si:H material and is given by:

$$\zeta = \frac{(q\epsilon\alpha v_{th}n_o)^{1-\alpha/2}}{\alpha - 1} \tag{2.6}$$

where  $n_o$  is an arbitrary normalizing number for the density of carriers in the a-Si:H. Setting it as 10<sup>16</sup> makes it close to the value of  $1/(q\epsilon v_{th})^{1/2}$  and allows  $\zeta$  to be simplified into an expression that is only dependent on  $\alpha$ :

$$\zeta \approx \frac{(10^{16}\alpha)^{1-\alpha/2}}{\alpha-1} \tag{2.7}$$

The power parameter  $\alpha$  is given by  $2V_{nt}/v_{th}$  where  $E_{nt} = qV_{nt}$  gives the characteristic slope of the conduction band tail as in Equation 2.1.  $v_{th}$  is the thermal voltage (25.8 mV at 300 K).

In the linear region of operation,  $V'_{DS} \ll V'_{GS}$  and the following can be derived from Equations 2.4 and 2.5:

$$I_{DS,lin} = \frac{\mu_{eff}}{\alpha} \zeta C_i^{\alpha - 1} \frac{W}{L_{eff}} \left( V_{GS} - V_T - 0.5 V_{DS} \right)^{\alpha - 1} \left( V_{DS} - R_{DS} I_{DS} \right)$$

(2.8)

where it is assumed that  $R_S = R_D = R_{DS}/2$ .

In the saturation region of operation (neglecting non-idealities such as the channel length modulation effect for simplicity)

$$I_{DS,sat} = \frac{\mu_{eff}}{\alpha} \zeta C_i^{\alpha - 1} \frac{W}{L_{eff}} \gamma_{sat} \left( V_{GS}' - V_T \right)^{\alpha}$$

(2.9)

where  $\gamma_{sat} = 1 - (1 - \alpha_{sat})^{\alpha}$ ) with  $\alpha_{sat}$  being a saturation parameter related to the drainsource voltage at which pinch-off occurs. Most practical applications employ TFTs biased in the saturation region due to the higher output current, and also because  $I_{DS}$  becomes a sole function of the overdrive voltage  $(V_{GS} - V_T)$  and independent of  $V_{DS}$ , giving the device a high output impedance.

#### 2.3.2 Subthreshold

In the subthreshold region of operation, the TFT current increases exponentially with increasing  $V_{GS}$ , allowing the device to turn on rapidly. The drain current is defined as [18]

$$I_{DS,sub} = I_{sub0} \frac{W}{L} \exp\left(\frac{V_{GS} - V_{TS}}{S_f}\right)$$

(2.10)

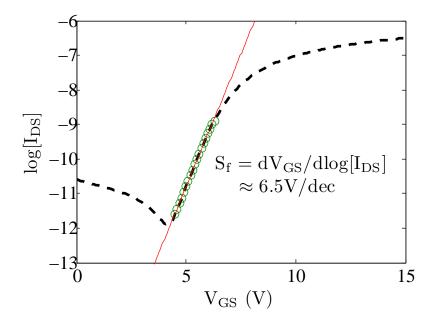

where  $V_{TS}$  denotes the onset of the subthreshold region from the off state, such that the equation holds for  $V_{TS} < V_{GS} < V_T$ .  $S_f$  is the subthreshold slope that is obtained graphically from the plot of  $log(I_{DS})$  versus  $V_{GS}$  as shown in Figure 2.8. At low  $V_{GS}$ ,

Figure 2.8: Example of subthreshold slope  $(S_f)$  extraction

electrons begin to accumulate in a thin layer at the top interface of the channel, leading to the small subthreshold current. As the Fermi level is near mid-gap in this mode of operation, most of the induced carriers go to the deep states caused by defects in the bulk and interface of a-Si:H. Therefore, the subthreshold slope is correlated to the density of deep states.

### 2.4 Metastability

As mentioned in Section 1.3, a-Si:H TFTs exhibit metastable behaviour under prolonged bias stress. Although there is some uncertainty about the exact physical mechanisms of instability, various studies agree that a simultaneous combination of charge trapping in the a-SiNx:H dielectric and defect state creation in a-Si:H is responsible for threshold voltage shift in TFTs [19]. In previous studies regarding TFTs with a-SiNx:H dielectric, charge trapping has been shown to be the main contributor to  $V_T$  shift at high gate voltage bias while defect creation is more significant with lower bias stress [20]. However, the dominant mechanism at a given bias voltage can vary depending on device processing conditions; charge trapping has been reported to be dominant in devices with  $V_{GS}$  of ~100 V [2] or as low as 10 V [21]. In order to determine which mechanism is dominant, it is necessary to measure the  $V_T$  shift behaviour of devices and see whether they match the kinetics of charge trapping versus defect state creation processes.

#### 2.4.1 Charge trapping

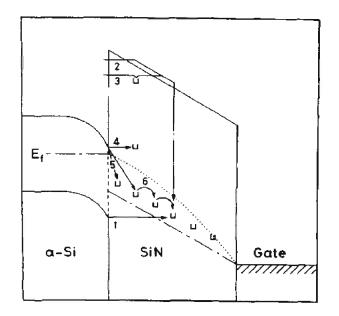

When a TFT is biased in accumulation, electrons can become trapped in the dielectric. Figure 2.9 illustrates the various possible trapping processes. Direct tunnelling from the valence band, Fowler-Nordheim injection, and trap-assisted injection (1-3) occur only at high electric fields and are negligible for normal TFT operation. For the TFTs used in this study, the most likely mechanism is the tunnelling of electrons from the conduction band and from filled conduction band tail states to trap states in the a-SiNx:H (5). After a certain amount of time under bias stress, trap states in the dielectric can become filled to a depth where it may become favourable for electrons to hop from occupied shallow states to deeper traps in the dielectric (6) instead. Conduction in the gate-dielectric (6)

Figure 2.9: Charge trapping mechanisms [2]

is a temperature-dependent process and appears to become significant only above room temperature, so it may not be applicable to the devices in this study. However, it is necessary to look at the temperature dependence of bias-stress measurements in order to rule out this mechanism.

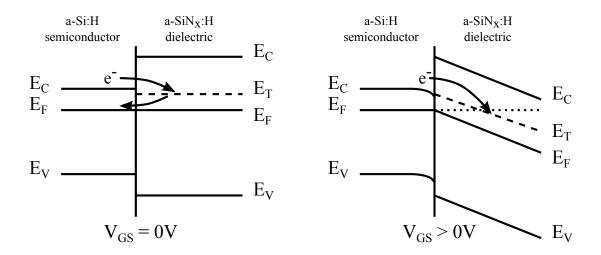

Figure 2.10 shows an energy band diagram of the trapping mechanism under positive bias. Electrons can randomly tunnel into trap states at an energy  $E_T$  in the a-SiNx:H. When the TFT is at zero bias, electrons that have tunnelled into the dielectric can easily return to the a-Si:H as  $E_T$  is above  $E_F$  of the a-Si:H. This is because there is a high density of states available above the Fermi energy of the semiconductor, due to the conduction band tail. Under positive bias,  $E_T$  past a certain depth in the dielectric dips below  $E_F$  of the a-Si:H. Electrons in these trap states are then unable to return to the a-Si:H until the bias is removed, as there are virtually no unfilled states below  $E_F$  in the semiconductor.

Figure 2.10: Energy band diagram of charge trapping mechanism

The charge trapping process described above results in a parallel shift of transfer characteristics, with no changes in the subthreshold slope.  $V_T$  shift through this mechanism has a low temperature dependence and a logarithmic time dependence given by [22]:

$$\Delta V_T = r_d \log[1 + \frac{t}{t_0}] \tag{2.11}$$

$r_d$  depends on the density of traps  $N_t$  in the dielectric and  $t_0$  is a time constant which can include a temperature-dependent supply function.

An alternative model exists for this charge trapping process [21]. It is assumed that the trap energy level remains constant throughout the dielectric, and therefore the tunnelling of electrons is unaffected by trap depth. In reality, it is more likely for electrons to tunnel into traps nearer to the interface. Hence this model introduces a capture cross-section term, S(x), that decreases exponentially with distance x into the dielectric and is given by

$$S(x) = S_0 \exp[-ax] \tag{2.12}$$

where a is a decay parameter dependent on the electron tunnelling effective mass, barrier height, and electric field. The concentration of filled trap states in the a-SiNx:H at depth x and bias stress time t changes according to the following equation:

$$\frac{dn_{tr}(x,t)}{dt} = S(x)\vec{v}[n_t[N_{tr} - n_{tr}(x,t)] - n_{empty}(x)n_{tr}(x,t)]$$

(2.13)

where  $n_t$  is the density of trapped electrons in conduction band tail near the interface,  $\vec{v}$  is the thermal velocity of electrons, and  $n_{empty}$  is the concentration of empty trap states at distance x.

Integrating  $n_{tr}$  through the thickness d of the dielectric gives the total trapped charge and hence the  $V_T$  shift is expressed as

$$\Delta V_T(t) = \frac{q}{C_i} \int_{x=0}^d n_{tr}(x,t) dx \qquad (2.14)$$

$$\Delta V_T(t) \approx \frac{qN_{tr}}{aC_i} \ln(\frac{t}{t_0}) \tag{2.15}$$

where

$$t_0 = \frac{1}{S_0 \vec{v} n_t} \exp(ax_0)$$

(2.16)

The equation can also be further developed to consider a Gaussian distribution of trap states instead of a single trap energy.

Another model for charge trapping proposes a multiple-trapping mechanism. Electrons from the a-Si:H conduction band become localized in a broad distribution of conduction band tail states that exist at the semiconductor-dielectric interface. The electrons initially hop or inject directly into lower energy interfacial states or to shallow traps in the a-SiNx:H. Over longer bias stress times, larger electric fields and/or higher temperatures, these states become filled and the electrons are emitted back to the a-Si:H conduction band tail states and/or move to deeper traps in the dielectric. The mix of trapping events and movement between traps results in a power-law time dependence instead of a logarithmic time dependence [23, 24]. The  $V_T$  shift is modelled by a stretched exponential equation [25]:

$$\Delta V_T = \Delta V_0 \left[ 1 - \exp\left[ -\left(\frac{t_{ST}}{\tau}\right)^\beta \right] \right]$$

(2.17)

where  $\Delta V_0$  is the approximate effective voltage drop across the insulator,  $t_{ST}$  is the bias stress time, and  $\tau = \tau_0 \exp(E_{\tau}/kT)$  is the characteristic trapping time of carriers where the thermal activation energy is  $E_a = E_{\tau}\beta$  with  $\beta$  being the stretched-exponential exponent.  $E_{\tau}$  is the average effective energy barrier that electrons have to overcome when tunnelling from the a-Si:H to the dielectric, and  $\tau_0$  is thermal prefactor for emission over the barrier.  $\beta$  and  $\tau$  are independent of bias voltage unlike  $\Delta V_0$ .

#### 2.4.2 Defect creation

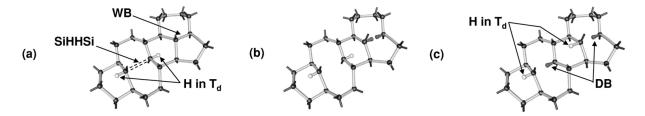

Although defect creation in a-Si:H is not fully understood, two possible mechanisms have been proposed. It is inferred that the defect creation process begins with the breaking of Si-H bonds, releasing H atoms which then collide and form a bound, paired hydrogen complex (SiHHSi) as well as dangling bonds. This reaction is illustrated in Figure 2.11a. A second

Figure 2.11: Localized defect creation process [3]

mechanism involves the breaking of weak Si-Si bonds that are in close proximity to SiHHSi complexes. The hydrogen atoms subsequently rearrange to leave dangling bonds close to the hydrogen atoms (SiHdb), as shown in Figure 2.11b-c, which stabilizes the dangling

bonds. The second process, and therefore Si-Si bond breaking, is the rate limiting step for defect creation [26].

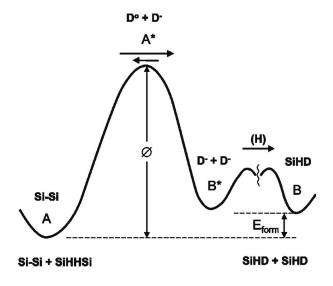

Figure 2.12 shows an energy band diagram of the defect creation process under electron

Figure 2.12: Energy diagram of defect creation [3]

accumulation. The initial Si-Si bond is at energy A. The breaking of the bond forms a D0 and a D- state as the bond becomes occupied by only a single electron. This is described as the intermediate state A<sup>\*</sup>. The dangling bonds then stabilize to state B. B<sup>\*</sup> is an additional intermediate state for a backward reaction where both dangling bonds become negatively charged. This state is possible due to disorder in a-Si:H causing an exponential distribution of energy barrier heights  $\emptyset$ , so a backwards reaction can occur for the lower range of barrier heights. The barrier height  $\emptyset$  primarily determines the rate of defect creation, while the total amount of defect creation is mainly dependent on the energy difference  $E_{form}$  between the initial and final states [3].

From studies of a-Si:H TFTs deposited under a range of deposition conditions to vary

the intrinsic stress, compressive stress in the a-Si:H results in a shortening of Si-Si bonds, which reduces the energy required to break the bonds [27]. Conversely, the Si-Si bond strengthens with increasing bond length distortion up to 1 Å [28]. However, some groups have speculated that sufficiently high tension can weaken Si-Si bonds and increase the rate of defect creation as well [29, 30].

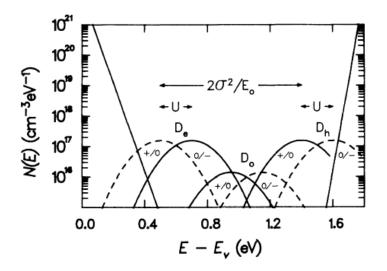

The energy of the created defects can vary depending on the conditions of dangling bond formation. The dangling bonds can also be charged (e.g. by capturing an electron). The density distribution of defect states is shown in Figure 2.13. Defect states formed

Figure 2.13: Density distribution of defect states [4]

under positive bias with electron accumulation (De) have energy levels in the lower half of the a-Si:H bandgap. Defects formed under negative bias with hole accumulation (Dh) have energy levels in the upper half of the bandgap. De states are initially formed as dangling bonds which have captured an electron (D-) as described previously, while Dh states start out as positively charged dangling bonds (D+). However, the defects can subsequently transition to different charge states. Some D0 states are formed as well, but are relatively low in density. The various energies of the defect states are exponential distributions due to the disorder in a-Si:H.

It has been experimentally shown that moving the Fermi energy affects the distribution and density of states. Raising the Fermi energy towards the conduction band by applying a positive bias stress increases the density of De states. A higher density of De states results in a positive shift of electron threshold voltage. The electron subthreshold slope is unaffected while the hole subthreshold slope is degraded. Conversely, negative bias stress which moves the Fermi energy closer to the valence band causes an increase in Dh states. This causes positive electron  $V_T$  shift as well, but also degrades the electron subthreshold slope [4].

The  $V_T$  shift due to defect creation can be simply modelled by a stretched-exponential equation [31]

$$\Delta V_T(t) = (V_{GS} - V_{T0}) \left[ 1 - \exp\left[ -\left(\frac{t}{\tau}\right)^{\beta} \right] \right]$$

(2.18)

where  $V_{T0}$  is the initial threshold voltage, and  $\tau$  and  $\beta$  are characteristic parameters for defect creation during bias stress. According to this equation, the  $V_T$  shift has a power-law time dependence.

An improved and more complex model has also been presented which gives a stretchedhyperbola equation for the  $V_T$  shift [27]:

$$\Delta V_T(E_{th}) = V_0 \left( 1 - \frac{1}{1 + \exp\left[\frac{E_{th} - E_A}{kT_0}\right]^{1/\epsilon}} \right)$$

(2.19)

where  $E_{th} = kT ln(vt)$  is the thermalisation energy, such that after a time t at temperature kT, all defect creation sites with energy barriers less than  $E_{th}$  will have converted to defects.

$V_0$  is the initial overdrive voltage,  $E_A$  is the typical energy barrier for defect creation under a given level of electron accumulation and  $kT_0$  is the characteristic slope of the exponential distribution of barriers.  $\epsilon = \alpha - 1$  where  $\alpha$  is obtained from the slope of  $V_T$  shift over  $(V_{GS} - V_{T0})$ .

#### 2.4.3 Relaxation

Relaxation is primarily due to charge detrapping, from electrons simply back-tunnelling to a-Si:H. Shallow trap states in the nitride close to the dielectric interface are more likely to detrap reversibly, unlike deeper states.

Defect removal occurs through a different process than simply the reverse of defect creation. Instead of the annealing of broken Si-Si bonds, defect removal is dependent on the breaking of Si-H bonds. The released hydrogen atoms then passivate dangling bond defects, and could occur locally like with defect creation process and also after long-range diffusion [3, 26]. Time scales for defect annealing are much longer than is relevant for our experiment at room temperature. Therefore the primary mechanism of relaxation is charge detrapping.

# Chapter 3

# Experiment

### 3.1 Prior work

The effect of mechanical strain on flexible a-Si:H TFTs has long been a subject of research interest. Initial studies focussed on determining failure mechanisms and the maximum level of strain devices could tolerate. It was found that TFTs tended to fail due to cracking under tension and by delamination and buckling of the device layers under compression [32]. The maximum amount of strain that can be applied without device failure is dependent on the mechanical properties of the substrate, device geometry, deposition conditions and thicknesses of the TFT layers, but was found to be ~0.5% tensile and ~2% compressive strain for a-Si:H TFTs on polyimide film [33].

There has also been much investigation on the electrical behaviour of TFTs with applied strain below the failure limit. Many groups have measured the transfer characteristics of TFTs strained to various levels of tension and compression. It has been found that the electron field effect mobility increases with tension [34] and decreases with compression [35], with a linear dependence on the applied strain. The sensitivity of the mobility to the change in strain has been described as

$$M_{\epsilon}(\mu) = \frac{\Delta\mu}{\mu \cdot \epsilon} \tag{3.1}$$

where  $\epsilon$  is the applied strain. Sensitivity values ranging from ~ 22 to ~ 26 have been reported for a-Si:H TFTs on polyimide film [29]. The mobility changed instantly with the application of strain, then remained stable while being held under strain for 40 hours [36]. However, the sensitivity gradually decreased from 23.6 to 11.1 with multiple strain load cycles which suggests that prolonged strain may have caused long-term changes in device characteristics. Threshold voltage, subthreshold swing and Ioff showed monotonic trends with respect to time when a sequence of random levels of strain was applied, which indicated that the results were also affected by bias-stress-induced instability [29]. The influence of uniaxial applied strain on device characteristics was found to be strongest when the strain was oriented in parallel to the drain-source current [14]. The effect of strain on bias-stress instability of flexible TFTs has been studied to some extent as well. Threshold voltage shift over 2h with constant gate voltage bias stress was found to be greater under tension than without strain [30].

The cause of the aforementioned shifts in device characteristics has mainly been attributed to strain-induced changes in the a-Si:H material. Strain changes the characteristic slope of the conduction band tail as discussed in Section 2.1, which may have led to the observed changes in mobility [15, 37]. The increased instability with tension was speculated to be due to the weakening of Si-Si bonds under strain, leading to increased creation of dangling bonds [30]. This hypothesis was confirmed with atomic force microscopy (AFM) and micro-Raman spectra of the top side of back-channel-etched a-Si:H TFTs after bending. The long-range structure of the a-Si:H was deformed by applied tension, but the short-range structure remained about the same. An interpretation of this phenomenon is that the applied strain causes a redistribution of traps from localized states to deep states, leading to changes in  $V_T$ , field-effect mobility and subthreshold swing [37].

## 3.2 Approach

The goal of this study is to further investigate electrical bias-stress instability in mechanically strained a-Si:H TFTs, as the topic has yet to be explored systematically. The study also aims to determine whether strain affects the magnitude and rate of the physical mechanisms which cause threshold voltage shift. Hence, an emphasis was placed on bias-stress measurements over time. Drain current was measured over various intervals of time to track the degradation of devices due to metastability, and results were then compared across different levels of strain.

In previous studies of TFT behaviour under mechanical strain, parameters such as threshold voltage and field-effect mobility were often extracted from linear extrapolation of transfer characteristics, based on an ideal square-law model for TFT operation [16]. However, this method of extraction results in a threshold voltage that is sensitive to series resistance and dependent on mobility. The field-effect mobility also increases gradually with increasing  $V_{GS}$ , which introduces uncertainty when selecting data points for linear extrapolation and introduces error into the extracted parameters [38]. The drain current in a-Si:H TFTs may also have a power parameter that is different from the ideal square-law model which assumes a value of 2 [16].

A general method for threshold voltage extraction in non-crystalline MOSFETs which circumvents the above difficulties has been presented [39]. However, the extraction is based on devices biased in the saturation region of operation. Although TFTs are usually biased in saturation for most practical applications, a pinched-off channel complicates the collection of data for the purpose of studying bias-stress instability. As there is a large variation of the overdrive voltage along the channel, TFTs biased in saturation show a non-uniform  $V_T$  shift along the length of the device [40].

In this study, the above-threshold characteristics of the TFTs were extracted using a procedure based on the compact model developed by P. Servati [41], which was presented in Section 2.3.1. This model was chosen as it accounts for parasitic elements such as contact resistance, allows for extraction of a non-ideal power parameter, and defines parameters such as an effective mobility which provides information on the physical properties of the a-Si:H channel.

### 3.3 Measurement procedure

First, the transfer characteristics for various TFTs were measured by applying a drain voltage of 0.1 V and sweeping the gate voltage from 0 V to 20 V. Initial device characteristics extracted from the linear region of operation showed an Ion/Ioff ratio of greater than  $10^5$ , threshold voltage of around 4 V, transconductance of about 50 pA/mV, and subthreshold swing of 0.7 V/dec. The devices showed a high degree of uniformity across the wafer; variation of the above parameters was within about 5% across the TFTs measured.

Uniaxial tensile strain was then applied to several devices, with the strain oriented parallel to the drain-to-source current path. Transfer characteristics were measured for comparison with data obtained when the device was unstrained. Individual devices were then subjected to bias stress for various durations of time by applying a constant gate voltage of 20 V and monitoring the drain current with a 0.1 V drain voltage applied. Separate TFTs were monitored for bias stress times of 100 s, 1000 s and 10000 s. After the 100 s and 1000 s bias stress tests, the gate voltage was set to 0 V and the device was allowed to recover. The drain current was monitored with a very low duty cycle pulsed measurement. At various intervals, the drain current was measured by applying a 20 V pulse to the gate while the drain voltage remained held at 0.1 V. The pulse width was set to 1 s, with off intervals of up to 300 s. The pulse width was chosen to be long enough to eliminate transient fluctuations in the measured current due to charging of parasitic capacitances, but also short enough to minimize further aging of the device, which could hinder recovery.

For the 10000 s bias stress measurement, transfer characteristics with  $V_{DS} = 0.1$  V and 1 V over  $V_{GS} = 0$  V to 20 V were also measured at 1000 s intervals during the bias stress time. To track TFT recovery, transfer characteristics were measured approximately 30 hours after the bias stress was removed from the devices.

The above measurements were then repeated with a separate group of TFTs that were put under uniaxial compressive strain. All measurements were also repeated with a group of TFTs that were not subjected to any mechanical stress, as a reference for comparison with the strained cases.

### 3.4 Testbench

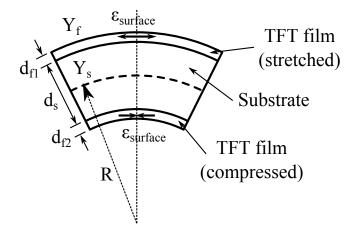

Tensile and compressive strain was applied to the TFTs by bending samples to convex and concave curves of known radii. The exact amount of strain in the channel of each TFT is difficult to determine as the samples consist of many layers of different materials patterned to various geometries. However, the strain can be calculated by modelling the bent device as the simplified structure shown in Figure 3.1. This model treats the various device layers as a single uniform film with Young's modulus  $Y_f$ , sitting on one surface of the

Figure 3.1: Model for surface strain calculation

substrate with thickness  $d_s$  and Young's modulus  $Y_s$ . For applied tension and compression respectively, the TFTs are represented as either a layer of thickness  $d_{f1}$  on the outside of the bend or as a layer of thickness  $d_{f2}$  on the inside. The strain on the TFT film surface can then be estimated by the following equation [33]:

$$\epsilon_{\text{surface}} = \left(\frac{1}{R} \pm \frac{1}{R_0}\right) \frac{d_s + d_{f1} + d_{f2}}{2} \cdot \frac{\chi(\eta_1^2 + \eta_2^2) + 2(\chi\eta_1 + \chi\eta_1\eta_2 + \eta_2) + 1}{\chi(\eta_1 + \eta_2)^2 + (\eta_1 + \eta_2)(1 + \chi) + 1}$$

(3.2)

where  $\chi = Y_f/Y_s$ ,  $\eta_1 = d_{f1}/d_s$  and  $\eta_2 = d_{f2}/d_s$ .  $R_0$  is the initial radius of the sample, with the plus and minus signs representing applied bending opposite to or with the builtin curvature. In the samples used in this experiment, the deposition conditions of the device layers were carefully chosen to minimize the internal film stresses. Accordingly, the samples were fairly flat. Therefore it is assumed that the internal film stresses are negligible compared to externally applied forces, allowing the  $R_0$  term in the equation to be ignored.

The estimated values of strain for the various radii are listed in Table 3.1. Values were calculated using  $Y_f = 200$  GPa [33],  $Y_f = 6.1$  GPa [6] and film thicknesses as described in Section 2.2.

| Bending radius (mm) | Tensile strain (%) |     |  |

|---------------------|--------------------|-----|--|

| 38                  | 0.3                | 0.3 |  |

| 32                  | 0.4                | 0.4 |  |

| 22                  | 0.6                | 0.5 |  |

| 16                  | 0.9                | 0.7 |  |

| 11                  | 1.2                | 1.0 |  |

| 6                   | 2.2                | 1.8 |  |

| 4                   | 3.5                | 2.8 |  |

Table 3.1: Calculated values of strain

Metal support structures for each bending radius were created to hold the TFTs under constant strain during measurement. Samples with dimensions of approximately 1.5 cm by 1.5 cm containing multiple devices were positioned and attached to the curved surfaces of the structures such that the applied strain was aligned along the drain-to-source current path of the TFTs. The structures were then placed into a probe station and the devices were measured directly as shown in Figure 3.2.

Figure 3.2: TFT sample mounted on strain testbench

## Chapter 4

# Results

## 4.1 TFT parameters and bias stress

The above-threshold characteristics of the TFTs were extracted using a procedure based on the model presented in Section 2. TFTs were biased in the linear region of operation, with a gate voltage of 20 V. The threshold voltage, power parameter, contact resistance, and effective mobility were extracted from transfer characteristics measured every 1000 s for a total time of 10000 s.

From Equation 2.8 and assuming negligible contact resistance effects, the linear transconductance can be derived as

$$g_{m,lin} = \frac{\mathrm{d}I_{DS,lin}}{\mathrm{d}V_{GS}} = \frac{\mu_{eff}}{\alpha} \zeta C_i^{\alpha - 1} \frac{W}{L_{eff}} (\alpha - 1) \left( V_{GS} - V_T - 0.5 V_{DS} \right)^{\alpha - 2} V_{DS}$$

(4.1)

Dividing the drain-source current by this yields

$$\frac{I_{DS,lin}}{g_{m,lin}} = \frac{(V_{GS} - V_T - 0.5V_{DS})}{\alpha - 1}$$

(4.2)

Therefore, by plotting  $I_{DS,lin}/g_{m,lin}$  versus  $V_{GS}$  and fitting a line to the linear region, initial values for  $\alpha$  and  $V_T$  can be extracted from the slope and x-intercept. The values of  $\alpha$ and  $V_T$  were then further refined through curve-fitting to the measured  $I_{DS}$  versus  $V_{GS}$ data. This is necessary to improve the accuracy of  $\alpha$  as the initial values assume  $R_{DS}$  is negligible. The error in  $\alpha$  compared to the initial value can be estimated as [17]

$$\Delta \alpha_{\rm lin} \approx -k_o(\alpha - 1) \tag{4.3}$$

where

$$k_{o} = \frac{R_{DS} W \mu_{\text{eff}} \zeta C_{i}^{\alpha - 1}}{L_{\text{eff}} (V_{GS0} - V_{T})^{\alpha - 1}}$$

(4.4)

with  $V_{GS0}$  being the highest value of  $V_{GS}$  where the plot of  $I_{DS,lin}/g_{mlin}$  remains linear (i.e. unaffected by  $R_{DS}$ ). Thus the value of  $\alpha$  should be slightly higher than the initial value when RDS is considered.

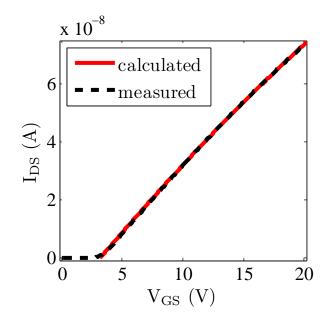

Using the fitted values for  $\alpha$ ,  $V_T$  was further refined by determining the intercept of  $I_{DS}^{1/(\alpha-1)}$  versus  $V_{GS}$ . The new values of  $\alpha$  and  $V_T$  were then used in Equation 2.8, and further fitting was conducted to refine  $R_{DS}$ . Depending on whether  $R_{DS}$  was raised or lowered, the value of alpha was adjusted accordingly. This process was then iterated to improve the accuracy of the extracted parameters. Figure 4.1 compares the measured drain-source current with values calculated from parameters obtained through fitting. Note that the fitting only applies to the linear region of operation and therefore deviates from the measured values at lower values of  $V_{GS}$ .

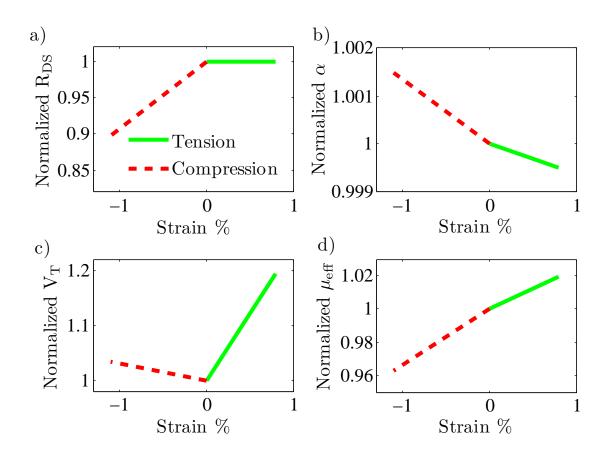

The values for  $R_{DS}$ ,  $\alpha$ ,  $V_T$ , and  $\mu_{eff}$  are plotted with respect to the applied strain in Figures 4.2a to 4.2d. The data was extracted from devices with zero applied strain and at the maximum levels of tension and compression without visible damage to the TFTs (roughly 1% strain). However, further study is required to rule out the presence of any micro-cracking which could affect the measured characteristics.

Figure 4.1: An example of measured vs. simulated  $I_{DS}$  vs.  $V_{GS}$

The extracted parameters are plotted as a function of total bias stress time in Figures 4.3 to 4.8. In addition to the above-threshold parameters, the subthreshold swing was also extracted from the transfer characteristics.

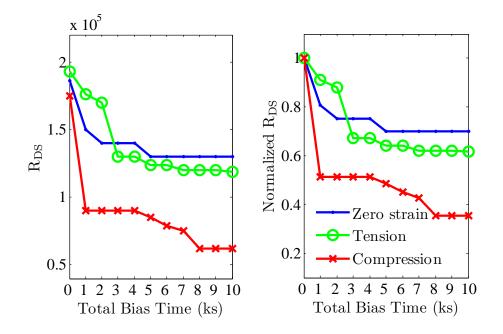

$R_{DS}$  seems to be unaffected by the level of applied tension used in the experiment. However,  $R_{DS}$  decreases with compression in Figure 4.2a. This could be due to the closing of pre-existing micro-cracks and/or a decrease in contact resistance as the TFT layers at the drain and source are compressed [42]. From Figure 4.3,  $R_{DS}$  drops steeply with bias stress over the first 1000 s for the unstrained and compression cases, then remains fairly stable for the rest of the 10000 s. Under tension,  $R_{DS}$  continues to decrease until 3000 s, then remains roughly constant. The overall change for tension is similar to the unstrained case. The greatest decrease occurs for compression. However, the decrease in extracted  $R_{DS}$  over bias stress time may be due to the lowering of the drain-source current

Figure 4.2: Normalized  $R_{DS}$ ,  $\alpha$ ,  $V_T$  and  $\mu_{eff}$  vs. strain

with increasing  $V_T$  shift as  $V_{GS}$  is held constant for the measurement. The degradation in the transfer characteristic due to series resistance becomes less apparent with lower  $I_{DS}$ , leading to a lower value of  $R_{DS}$  when extracted by curve-fitting. It is necessary to do a more accurate  $R_{DS}$  extraction by measuring and comparing devices with a greater variation in channel length. Also, a higher value of  $V_{GS}$  or constant-current measurements could be used to obtain data with a smaller ratio of change in overdrive voltage.

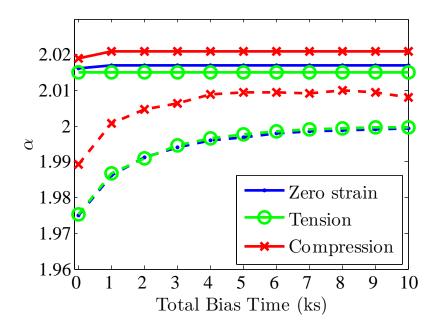

Figure 4.2b shows that  $\alpha$  increases with compression and decreases with tension. As defined in Section 2.3.1,  $\alpha$  is directly proportional to the characteristic slope  $E_{nt}$  of the

Figure 4.3:  $R_{DS}$  and normalized  $R_{DS}$  vs. total bias stress time

conduction band tail. The data indicates that the conduction band tail widens with compression and narrows for tension, which agrees with findings by previous groups [34]. Figure 4.4 shows that  $\alpha$  remains roughly constant with increasing bias stress time, but with a slight increase over the first 1000 s for the unstrained and compression cases. The fairly constant values for  $\alpha$  show that the distribution of localized states near the conduction band do not change significantly during the bias stress experiment. This result is expected as positive bias stress should mainly create defect states at energies below mid-gap according to the defect pool model discussed in Section 2.4.2.

The values of  $\alpha$  obtained from curve-fitting vary much less with respect to bias time than the roughly extracted values obtained initially from Equation 4.2. This is because the fitting process considers the  $R_{DS}$  parameter, which decreases under bias stress over time as shown in Figure 4.3. The decreasing value of  $R_{DS}$  essentially absorbs the change seen in

Figure 4.4:  $\alpha$  vs. total bias stress time (initial values are plotted with dashed lines)

the initial  $\alpha$ . The slight increase in  $\alpha$  over the first 1000 s of bias stress for the unstrained and compression cases is most likely an artefact of extraction caused by this correlation.

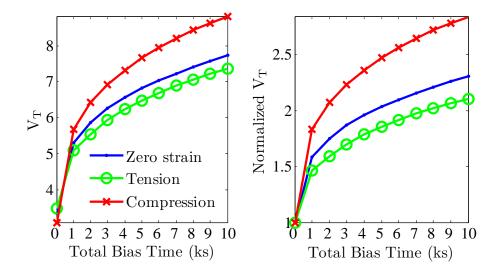

Figure 4.2c shows that  $V_T$  increases slightly with both applied tension and compression, and with a somewhat more pronounced effect for tension. Figure 4.5 shows the  $V_T$  shift over 10000 s bias stress time for the various cases of applied strain. The  $V_T$  shift over long-term bias stress is highest for compression, which is in accordance with the hypothesis of increased defect creation under compression due to bond breaking as discussed in Section 2.4.2. Although the  $V_T$  increased slightly with the initial application of tension, the magnitude of shift under bias stress is slightly lower for TFTs under tension than for unstrained TFTs. This could be a sign of decreased defect creation due to the slight elongation and strengthening of Si-Si bonds. Alternately, the tension could be relieving some of the intrinsic compressive stress in the a-Si:H film, leading to the same effect.

Figure 4.5:  $V_T$  and normalized  $V_T$  vs. total bias stress time

Figure 4.2d indicates that  $\mu_{eff}$  decreases with compression, and increases with tension. This corresponds to the trends in field-effect mobility previously reported by multiple groups [15, 30]. The plot of  $\mu_{eff}$  versus bias stress time in Figure 4.6 shows a faster rate of decrease under tension and compression, while  $\mu_{eff}$  for the unstrained case remains relatively constant. Both types of strain result in lower final values of  $\mu_{eff}$  than for zero applied strain, with the lowest value for compression. This may again indicate increased defect state creation over bias stress time for both strained cases, with a greater impact with compression than tension. Greater disorder is induced by increased bond-breaking in the a-Si:H and increases the scattering of electrons, thus lowering the effective mobility. From the derivation of the model equations,  $\mu_{eff}$  is defined as

$$\mu_{eff} = \mu_{band} \frac{N_{fi}}{N_{ti}^{\frac{\alpha}{2}}} N_o^{\left[\frac{\alpha}{2} - 1\right]}$$

(4.5)

where  $N_{fi}$  and  $N_{ti}$  are respectively the concentrations of free and trapped electrons in the a-Si:H with no band bending.  $N_o$  and  $\alpha$  are as previously defined.  $\alpha$  was determined to be

Figure 4.6:  $\mu_{eff}$  and normalized  $\mu_{eff}$  vs. total bias stress time

roughly constant.  $u_{band}$  decreases with the level of disorder in the material which agrees with the data and above explanation. The decrease in  $\mu_{eff}$  can be further accelerated by an increase in the ratio of trapped versus free carriers, due to increased trapping in either the a-Si:H or a-SiNx:H.

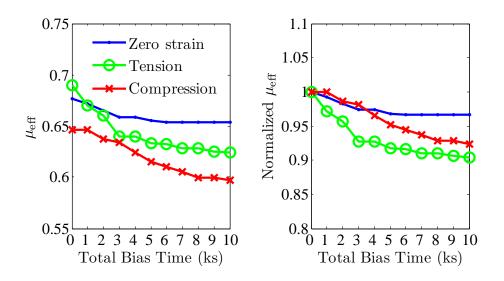

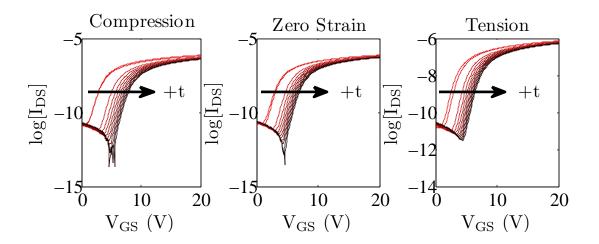

Figure 4.7 shows semi-log plots of transfer characteristics under various strain conditions. The direction of the arrows indicate data taken at increasing lengths of bias stress time, up to a total of 10000 s. From Figure 4.8, the subthreshold swing  $S_f$  seems to improve slightly over the bias stress time. There is only a slight difference between all the strain cases, and the variation may not be statistically significant. The general decrease in  $S_f$  reinforces that no upper bandgap defect states (Dh) are being created with positive bias stress. The change in  $S_f$  could also be an artefact of the extraction. A gradual decrease in  $I_{off}$  with bias stress was apparent for TFTs under compression or zero strain as seen in Figure 4.7, which could lead to lower extracted values of  $S_f$ . A lower  $I_{off}$  could suggest an increased density of trapped charge in the dielectric which would hinder electron accu-

Figure 4.7: Data for  $S_f$  extraction

Figure 4.8:  $S_f$  and normalized  $S_f$  vs. total bias stress time

mulation at low bias. Therefore strain may increase charge injection to the a-SiNx:H with prolonged bias stress.

### 4.2 Bias stress degradation and recovery

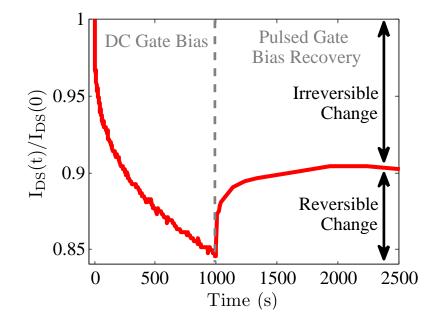

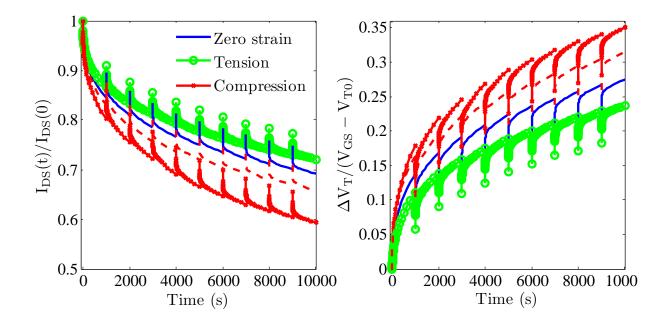

Figure 4.9 shows a sample of experimental data obtained from a bias stress and recovery

Figure 4.9: Example of bias stress degradation and recovery data

measurement as described in Section 3.3. The drain current shows the percentage of degradation over time while a constant gate bias is applied. For all measurements, devices were kept in the linear region of operation, such that the TFT drain-source current would remain approximately linearly proportional to  $V_{GS} - V_T$ . The devices exhibited excellent uniformity and a constant gate bias of 20 V was used in all measurements, with a low drain voltage of 0.1 V.

From curve fitting to the model equations in Section 4.1,  $R_{DS}$  was determined to be on the order of  $10^5 \Omega$  at maximum, while measured values of  $I_{DS}$  were on the order of  $10^{-8}$  A. Therefore  $V_{DS} >> R_{DS}I_{DS}$  and it can be assumed that the influence from contact resistance is insignificant. The parameter alpha was found to be roughly equal to 2, and remained fairly constant over bias stress time. Therefore, the TFT current for linear operation from Equation 2.8 can be simplified as:

$$I_{DS,lin} = \mu_{eff} C_i \frac{W}{L_{eff}} (V_{GS} - V_T) V_{DS}$$

$$\tag{4.6}$$

The change in the normalized drain current can then be used to determine the  $V_T$  shift of a given device by the following relation:

$$\Delta V_T = \left[1 - \frac{I_{DS,lin}(t)g_{m0}}{I_{DS,lin}(0)g_m}\right] (V_{GS} - V_{T0})$$

(4.7)

The gate bias is removed after 1000 s in the example shown in Figure 4.9, and the drain current is shown to partially recover. The current rises rapidly once the bias is removed, then quickly settles to a maximum value that stays fairly constant for several hours. The proportion of the current that is recovered can be considered an indicator of a 'reversible' shift in  $V_T$ , while the amount of current not recovered essentially marks a permanent change in terms of practical device operation [43].

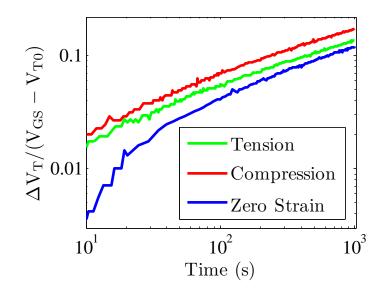

The exact physical origins of the instability in  $V_T$  are not revealed by the measurement data. Figure 4.10 shows a log-log plot of  $V_T$  shift over 1000 s of bias stress time for TFTs under different strain conditions. The data after ~200 s of bias stress follows a power-law time dependence, as it appears roughly linear on the plot. As explained in Section 2.4, this could be due to defect creation and/or charge trapping into multiple states with subsequent redistribution. The non-linearity near the beginning of the bias stress time suggests that a different mechanism of charge trapping is dominant at small time scales. The data also shows a slight decrease near the end of the bias stress period. This is likely due to the change in overdrive voltage  $(V_{GS} - V_T)$  caused by the increase in  $V_T$  over time. Therefore it is recommended that further measurements be taken using a higher value of  $V_{GS}$  or with constant-current bias stress.

Figure 4.10: Log-log plot of normalized  $V_T$  shift over 1000 s bias stress

However, it is possible to characterize the proportion of  $V_T$  shift as reversible or irreversible by examining the recovery of the stressed TFTs. It has been established that  $V_T$ shift is due to charge trapping either into the gate dielectric or into defects created within the semiconductor channel while the device is under bias stress. The trapped charges can be classified as being in reversible or 'fast' states that readily trap and detrap carriers to the extended conduction states, or in irreversible 'slow' states that do not easily release the trapped charges. Fast states include shallow traps in the gate dielectric close to the top interface and defect states in the semiconductor channel with low energy barrier height. Slow states include traps deep in the dielectric which have a lower probability of carrier tunnelling, and defect states in the a-Si:H with a high energy barrier to formation.

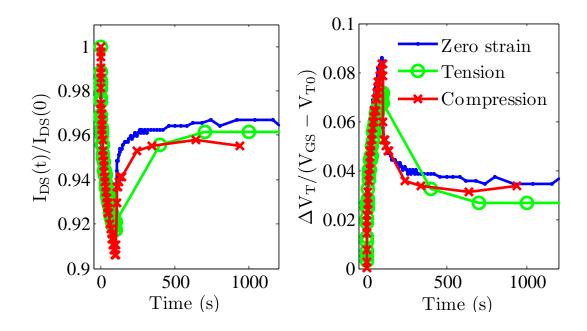

Figure 4.11 shows measurement results for devices subjected to 100 s of applied electrical bias stress. The devices appeared to degrade about the same amount for the unstrained TFTs and the TFTs under tension or compression. The amount of current and magnitude

Figure 4.11: Normalized  $I_{DS}$  and normalized  $V_T$  shift for 100 s bias stress and recovery

of  $V_T$  shift recovered after removing the bias stress was almost identical for all three cases as well.

After 1000 s of bias stress time, Figure 4.12 shows that the devices under tension degraded a similar amount as unstrained devices, while TFTs under compressive strain showed greater degradation in comparison. The proportion of  $V_T$  shift recovered after the bias stress period was again similar for all three cases, but was slightly lower for the strained cases than for unstrained by a difference or roughly 10%. The percentage of reversible  $V_T$  shift for each test case is summarized in Table 4.2.

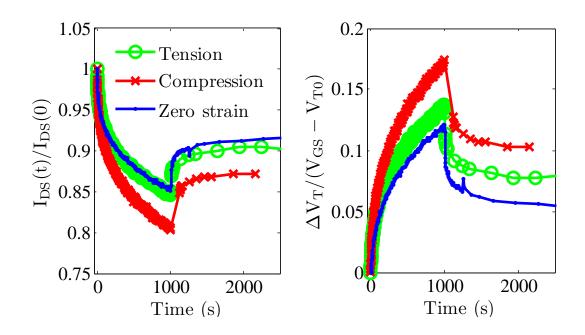

Figure 4.13 shows the current degradation and  $V_T$  shift for devices measured in 1000 s intervals for a total bias time of 10000 s. The brief interruptions allowed transfer characteristics to be measured between the intervals. Again, the current degradation and  $V_T$ shift were notably more significant for devices under compressive strain than for tension

Figure 4.12: Normalized  $I_{DS}$  and normalized  $V_T$  shift for 1000 s bias stress and recovery or zero strain. This trend corresponds with the plot of  $V_T$  shift derived earlier through curve-fitting of the transfer characteristics.

Table 4.1 and 4.2 summarize the magnitude of  $V_T$  shift and recovery observed for the

| Bias time (s) | Unstrained | Tension | Compression |  |

|---------------|------------|---------|-------------|--|

| 100           | 8.6        | 7.1     | 8.3         |  |

| 1000          | 12         | 14      | 17          |  |

| 10000         | 27         | 24      | 35          |  |

Table 4.1: Percent threshold voltage shift

various bias stress times and strain conditions. At shorter bias times, the percentages of degradation were roughly the same for the various strain cases. However, the amount of  $V_T$  shift for devices under compression becomes much greater with longer bias stress time

Figure 4.13: Normalized  $I_{DS}$  and  $V_T$  shift for 10000 s bias stress and recovery; dotted line is for a device with W/L = 200/8 instead of 200/16

| Bias time (s) | Unstrained | Tension | Compression |

|---------------|------------|---------|-------------|

| 100           | 60         | 63      | 63          |

| 1000          | 54         | 44      | 41          |

Table 4.2: Percent of threshold voltage shift recovered

when compared to devices under tension or zero strain. Overall, devices under tension seemed to have the same or slightly lower instability than the unstrained TFTs. The data suggests that strain does not affect TFT instability for low bias stress times of ~100 s, but becomes more significant with longer times. Compressive strain seems to cause increased  $V_T$  shift while tension slightly decreases  $V_T$  shift over long bias stress times.

The recovery data indicates that for low bias times, the TFT instability is mostly

reversible. The large magnitude of recovery points towards shallow charge trapping rather than defect creation as the main mechanism of instability at 100 s and 1000 s [43]. The percentage of recovery is significantly higher for the 100 s stress case than compared to the 1000 s case, which suggests that irreversible changes such as deep a-SiNx:H trapping and a-Si:H defect creation gradually become the dominant instability mechanisms over longer bias stress times.

The 100 s data shows a slightly greater amount of recovery for TFTs in tension and compression than for zero strain. It is unclear if this signifies that strain increases shallow charge trapping in the nitride, which is the main mechanism of instability at lower stress times. Since only a small amount of instability was observed during conditions in which charge trapping was dominant, the experiment should be repeated with higher bias stress such that trapping becomes the main mechanism of instability. Subsequently, TFTs should be observed for longer bias stress times to see if strain has an effect on charge trapping.

The trend in  $V_T$  recovery is reversed at 1000 s, with the strained devices showing lower recovery than for the unstrained devices. As discussed previously, both compression and tension can increase the rate of defect creation by weakening Si-Si bonds. This corresponds to the lower recovery for the strained cases at longer bias stress times when irreversible changes become more apparent. The recovery is slightly higher for tension than for compression, possibly because of intrinsic compressive stress in a-Si:H film cancelling out some of the applied tension and causing a slightly lower rate of defect creation. Tension can also strengthen some proportion of Si-Si bonds in the a-Si:H, as discussed in Section 2.4.2.

In addition, Figure 4.13 shows that the normalized  $V_T$  shift was lower for devices with a shorter channel length. As the devices were similar in all other regards, the trends discussed above are likely due to the material properties of the a-Si channel and gate dielectric as anticipated. The longer conduction path and greater dielectric area increases the degradation and strain-related effects for the longer devices. The differences observed in TFT behaviour under various strain and bias stress time are unlikely to originate from the drain/source contacts or metal traces as these are constant across the TFTs tested since the devices share a common width. However, it is recommended that a greater number of devices with larger variation in channel length be measured to confirm this trend and to verify that the results are statistically significant.

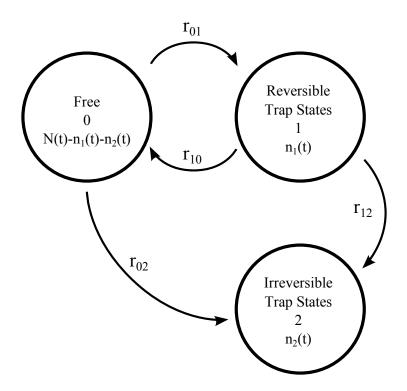

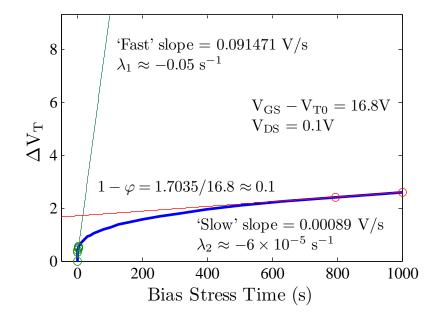

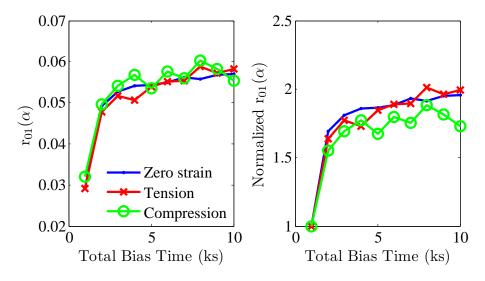

## 4.3 Modelling of trapping

The charge trapping into fast reversible and slow irreversible states as described in the previous section can be modelled as a Markov system as shown in Figure 4.14 [44]. It is assumed that holes do not have significant influence due to their low mobility in a-Si [10], and only electrons are considered as carriers. State 1 represents fast trap states and State 2 represents slow trap states, with  $n_1(t)$  and  $n_2(t)$  being the number of trapped electrons in each state at time t. The total number of electrons in the system is N(t). The number of free electrons in the conduction band is given by  $N(t) - n_1(t) - n_2(t)$ .  $r_{ij}$  are constants that represent the rate at which carriers pass from State i to State j. It is assumed that there is a negligible rate of detrapping from the slow states.

The system can be expressed as the following set of rate equations:

$$\frac{dn_1(t)}{dt} = (r_{01})[N(t) - n_1(t) - n_2(t)] + (-r_{10} - r_{12})n_1(t)$$

$$\frac{dn_2(t)}{dt} = (r_{02})[N(t) - n_1(t) - n_2(t)] + (r_{12})n_1(t)$$

(4.8)

It can be assumed the rate of free carriers becoming trapped in fast traps is much greater than the rate of carriers moving from fast traps to slow traps, as hopping from shallow to deep traps in the dielectric is unlikely at the relatively low bias stress times,  $V_{GS}$  and

Figure 4.14: Markov model of trapping

temperature used in this experiment [25]. Therefore it is assumed that  $r_{12}$  is very small, and the equations can be simplified. Letting  $\alpha = r_{01}$ ,  $\beta = r_{10}$  and  $\gamma = r_{02}$ , the equations can be expressed as:

$$\frac{d\vec{n}(t)}{dt} = \begin{bmatrix} -\alpha - \beta & -\alpha \\ -\gamma & -\gamma \end{bmatrix} \vec{n}(t) + \begin{bmatrix} \alpha \\ \gamma \end{bmatrix} N(t)$$

(4.9)

where

$$\vec{n}(t) = \begin{bmatrix} n_1(t) \\ n_2(t) \end{bmatrix}$$

It is assumed there are no trapped charges initially and  $n_1(0) = n_2(0) = 0$ . Since a constant gate voltage bias stress is used,  $N(t) = [(V_{GS} - V_{T0})C_i/q]u(t)$  where u(t) is the