# Fault Tolerant Cryptographic Primitives for Space Applications

by

Marcio Juliato

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2011

© Marcio Juliato 2011

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Spacecrafts are extensively used by public and private sectors to support a variety of services. Considering the cost and the strategic importance of these spacecrafts, there has been an increasing demand to utilize strong cryptographic primitives to assure their security. Moreover, it is of utmost importance to consider fault tolerance in their designs due to the harsh environment found in space, while keeping low area and power consumption. The problem of recovering spacecrafts from failures or attacks, and bringing them back to an operational and safe state is crucial for reliability. Despite the recent interest in incorporating on-board security, there is limited research in this area. This research proposes a trusted hardware module approach for recovering the spacecrafts subsystems and their cryptographic capabilities after an attack or a major failure has happened. The proposed fault tolerant trusted modules are capable of performing platform restoration as well as recovering the cryptographic capabilities of the spacecraft. This research also proposes efficient fault tolerant architectures for the secure hash (SHA-2) and message authentication code (HMAC) algorithms. The proposed architectures are the first in the literature to detect and correct errors by using Hamming codes to protect the main registers. Furthermore, a quantitative analysis of the probability of failure of the proposed fault tolerance mechanisms is introduced. Based upon an extensive set of experimental results along with probability of failure analysis, it was possible to show that the proposed fault tolerant scheme based on information redundancy leads to a better implementation and provides better SEU resistance than the traditional Triple Modular Redundancy (TMR). The fault tolerant cryptographic primitives introduced in this research are of crucial importance for the implementation of on-board security in spacecrafts.

#### Acknowledgements

My most sincere thanks for my wife Rita, for all her love, confidence and respect. My honest admiration for your strength while dealing with all the difficulties that have crossed our ways. Thanks for being such a generous and courageous person, as well as for facing head-on the next challenges that are approaching. Your collaboration and support were crucial in allowing me to pursue my PhD. I consider myself a lucky person to share my life with you. For you, my dear, my immense gratitude and love.

Special thanks to my parents Salete and Roberto for their infinite love, tireless dedication, insightful guidance, and immense comprehension. My profound admiration for the respectful and inspiring environment that I have been immersed since I know myself as a person. Thanks for instigating my curiosity and supporting me in all my endeavors (even in my craziest experiments). Thanks for teaching me how to have solid references and how to follow good principles. Without your support I would never have the chance to pursue my dreams and achieve my objectives. Thanks for my family, specially to my grandma Izabel and my sisters Vanessa and Denise, for their constant support even thousands of kilometers away.

Sincere thanks to my supervisor, Prof. Cathy Gebotys, for kindly showing me the horizon when I was looking at my own feet. Thanks for all confidence deposited in my person and in my capabilities. Also, thanks for your constant kindness and for receiving me with a smile in every single time that we met. Without your generous support, my PhD would never had become a reality. Kind thanks to my committee members, namely Professors Alfred Menezes, Andrew Kennings, Anwar Hasan, and Kris Gaj, for peer-reviewing and providing valuable comments on my thesis.

Thanks to the University of Waterloo and the Department of Electrical and Computer Engineering for the fabulous infrastructure and the many research and teaching opportunities that I have been offered while pursuing my PhD. Besides, my kind thanks to University of Campinas, Brazil, and to my previous supervisors, Professors Guido Araujo, Julio Lopez, and Paulo Centoducatte. I am really thankful to all institutions and educators that conducted me in the process of learning how to learn, specially for introducing me to critical thinking, skepticism, and scientific methodology.

Last but not least, thanks for my colleagues at the Embedded Security Lab, namely, Reouven Elbaz, Edgar Mateos, Dave Kenney, Solmaz Ghaznavi, Patrick Longa, Farhad Haghihgizadeh, Amir Khatibzadeh, and Brian White. I really appreciate your friendship, company, and discussions in the lab. Also, thanks to all my friends, some nearby, others far away, for all their support and for all journeys we have taken throughout all these years.

#### Dedication

This PhD thesis is dedicated for meritorious people that could not pursue their dreams and achieve their objectives. Not because of their intellectual capacity or motivation, but due to deficient health, disabilities, inadequate alimentation, peace deprivation, indecent quality of life, inappropriate conditions of study and work, socio-economic problems, natural catastrophes, wars and conflicts, despotism, prosecution, and discrimination in its various forms. This thesis is also dedicated to those people who, even against all odds and adversities, continue to work hard in the name of science, knowledge and free thinking.

# **Table of Contents**

| Li       | st of | Table         | 5                       | x  |

|----------|-------|---------------|-------------------------|----|

| Li       | st of | Figure        | es xi                   | ii |

| Li       | st of | Abbre         | eviations x             | v  |

| ΕĮ       | oigra | $\mathbf{ph}$ | xvi                     | ii |

| 1        | Intr  | oducti        | ion                     | 1  |

|          | 1.1   | Motiva        | $\operatorname{ation}$  | 1  |

|          | 1.2   | Contri        | ibutions                | 4  |

|          | 1.3   | Thesis        | Overview                | 5  |

| <b>2</b> | Bac   | kgrou         | nd                      | 7  |

|          | 2.1   | Fault         | Tolerance               | 7  |

|          |       | 2.1.1         | Fundamental Concepts    | 7  |

|          |       | 2.1.2         | Radiation Effects       | 9  |

|          |       | 2.1.3         | SEUs in ASICs and FPGAs | 3  |

|          |       | 2.1.4         | Mitigation Techniques   | 8  |

|          | 2.2   | Space         | Systems                 | 4  |

|          |       | 2.2.1         | Spacecraft Subsystems   | 5  |

|          |       | 2.2.2         | Space Missions          | 0  |

|   |                   | 2.2.3                                                                            | Threats Against Space Missions                  | 32                                                                                                                     |

|---|-------------------|----------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   |                   | 2.2.4                                                                            | Security Requirements                           | 37                                                                                                                     |

|   |                   | 2.2.5                                                                            | Platforms for Space                             | 41                                                                                                                     |

|   | 2.3               | Crypt                                                                            | ographic Algorithms                             | 46                                                                                                                     |

|   |                   | 2.3.1                                                                            | SHA-2 Algorithm Description                     | 46                                                                                                                     |

|   |                   | 2.3.2                                                                            | HMAC Algorithm Description                      | 49                                                                                                                     |

|   | 2.4               | Summ                                                                             | ary                                             | 51                                                                                                                     |

| 3 | Pre               | vious 1                                                                          | Research                                        | 53                                                                                                                     |

|   | 3.1               | Hardw                                                                            | vare Implementation of Cryptographic Primitives | 53                                                                                                                     |

|   | 3.2               | Fault                                                                            | Tolerant Cryptographic Primitives               | 60                                                                                                                     |

|   | 3.3               | Fault                                                                            | Injection Attacks                               | 64                                                                                                                     |

|   | 3.4               | Summ                                                                             | ary                                             | 66                                                                                                                     |

|   |                   |                                                                                  |                                                 |                                                                                                                        |

| 4 | Sec               | ure Sy                                                                           | stem Recovery                                   | 67                                                                                                                     |

| 4 | <b>Sec</b><br>4.1 | v                                                                                | v                                               | 6 <b>7</b><br>67                                                                                                       |

| 4 |                   | Refere                                                                           | nce Platform                                    |                                                                                                                        |

| 4 | 4.1               | Refere                                                                           | nce Platform                                    | 67                                                                                                                     |

| 4 | 4.1               | Refere<br>Hash                                                                   | nce Platform                                    | 67<br>69                                                                                                               |

| 4 | 4.1               | Refere<br>Hash 2<br>4.2.1<br>4.2.2                                               | nce Platform                                    | 67<br>69<br>69                                                                                                         |

| 4 | 4.1<br>4.2        | Refere<br>Hash 2<br>4.2.1<br>4.2.2                                               | nce Platform                                    | 67<br>69<br>69<br>71                                                                                                   |

| 4 | 4.1<br>4.2        | Refere<br>Hash 1<br>4.2.1<br>4.2.2<br>Truste                                     | nce Platform                                    | 67<br>69<br>69<br>71<br>72                                                                                             |

| 4 | 4.1<br>4.2        | Refere<br>Hash 2<br>4.2.1<br>4.2.2<br>Truste<br>4.3.1                            | nce Platform                                    | <ol> <li>67</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>73</li> </ol>                                     |

| 4 | 4.1<br>4.2        | Refere<br>Hash 1<br>4.2.1<br>4.2.2<br>Truste<br>4.3.1<br>4.3.2                   | nce Platform                                    | <ol> <li>67</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> </ol>                         |

| 4 | 4.1<br>4.2        | Refere<br>Hash 1<br>4.2.1<br>4.2.2<br>Truste<br>4.3.1<br>4.3.2<br>4.3.3          | nce Platform                                    | <ul> <li>67</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>77</li> </ul>             |

| 4 | 4.1<br>4.2        | Refere<br>Hash 1<br>4.2.1<br>4.2.2<br>Truste<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4 | nce Platform                                    | <ul> <li>67</li> <li>69</li> <li>69</li> <li>71</li> <li>72</li> <li>73</li> <li>74</li> <li>77</li> <li>79</li> </ul> |

| <b>5</b> | Har | dware   | Software Approaches for SHA-2 and HMAC                                    | 88  |

|----------|-----|---------|---------------------------------------------------------------------------|-----|

|          | 5.1 | Hardw   | vare/Software Partitioning                                                | 88  |

|          | 5.2 | Custo   | m Instructions                                                            | 90  |

|          |     | 5.2.1   | Level 1: Instruction ROTR                                                 | 90  |

|          |     | 5.2.2   | Level 2: Instructions Sum_Sig and Ch_Maj                                  | 90  |

|          |     | 5.2.3   | Level 3: Instructions Sig and Sum_Ch_Maj                                  | 91  |

|          | 5.3 | Periph  | nerals                                                                    | 92  |

|          |     | 5.3.1   | Level 4: Peripheral $SHA_256$                                             | 92  |

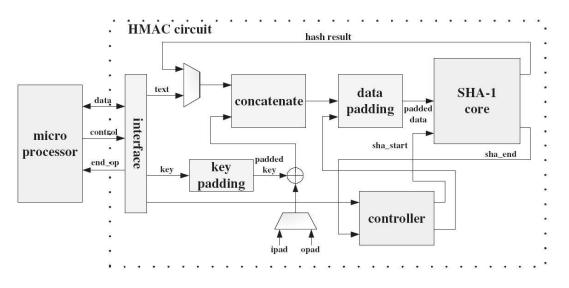

|          |     | 5.3.2   | Level 5: Peripheral HMAC_SHA_256                                          | 94  |

|          | 5.4 | Exper   | imental Results                                                           | 99  |

|          |     | 5.4.1   | Custom Instructions and Peripherals Implementation $\ldots \ldots \ldots$ | 99  |

|          |     | 5.4.2   | SHA-256 Results                                                           | 100 |

|          |     | 5.4.3   | HMAC/SHA-256 Results                                                      | 101 |

|          | 5.5 | Summ    | ary                                                                       | 102 |

| 6        | Fau | lt Tole | erant SHA-2                                                               | 104 |

|          | 6.1 | Fault   | Tolerance Schemes                                                         | 104 |

|          |     | 6.1.1   | Full Triple Modular Redundancy                                            | 105 |

|          |     | 6.1.2   | TMR for Registers and Encoded Memory                                      | 106 |

|          |     | 6.1.3   | Encoded Registers and Memory                                              | 107 |

|          | 6.2 | Exper   | imental Results                                                           | 110 |

|          |     | 6.2.1   | Implementation Area                                                       | 110 |

|          |     | 6.2.2   | Frequency of Operation                                                    | 111 |

|          |     | 6.2.3   | Throughput                                                                | 112 |

|          |     | 6.2.4   | Power Consumption                                                         | 113 |

|          | 6.3 | Summ    | ary                                                                       | 114 |

| <b>7</b>     | Fau   | lt Tole       | erant HMAC                                                                                       | 115   |

|--------------|-------|---------------|--------------------------------------------------------------------------------------------------|-------|

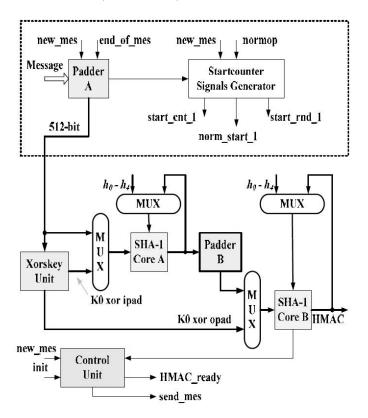

|              | 7.1   | Fault         | Tolerance Schemes                                                                                | 115   |

|              |       | 7.1.1         | Triple Modular Redundancy                                                                        | . 116 |

|              |       | 7.1.2         | TMR for Registers and Encoded Memory                                                             | . 117 |

|              |       | 7.1.3         | Encoded Registers and Memory                                                                     | . 119 |

|              | 7.2   | Exper         | imental Results                                                                                  | 122   |

|              |       | 7.2.1         | Implementation Area                                                                              | . 122 |

|              |       | 7.2.2         | Frequency of Operation                                                                           | . 123 |

|              |       | 7.2.3         | Throughput                                                                                       | . 123 |

|              |       | 7.2.4         | Power Consumption                                                                                | . 126 |

|              | 7.3   | Summ          | nary                                                                                             | . 127 |

| 8            | SEU   | U <b>Resi</b> | stance Analysis                                                                                  | 129   |

|              | 8.1   | Proba         | bility of Failure                                                                                | . 129 |

|              |       | 8.1.1         | Triple Modular Redundancy                                                                        | 131   |

|              |       | 8.1.2         | TMR for Registers and Encoded Memory                                                             | 132   |

|              |       | 8.1.3         | Encoded Registers and Memory                                                                     | 134   |

|              | 8.2   | Quant         | titative Analysis                                                                                | 135   |

|              |       | 8.2.1         | Memory Resistance Results                                                                        | 135   |

|              |       | 8.2.2         | Register Resistance Results                                                                      | . 137 |

|              | 8.3   | Summ          | nary                                                                                             | . 139 |

| 9            | Dis   | cussior       | ns, Conclusions and Future Work                                                                  | 141   |

|              | 9.1   | Truste        | ed Platform                                                                                      | . 141 |

|              | 9.2   | Fault         | Tolerant SHA-2 and HMAC                                                                          | . 144 |

|              | 9.3   | Conclu        | usions $\ldots$ | . 148 |

|              | 9.4   | Future        | e Work                                                                                           | 150   |

| $\mathbf{R}$ | efere | nces          |                                                                                                  | 152   |

# List of Tables

| 2.1 | Parity Bits Affected by Bit-Flips in a Hamming Code                               | 23  |

|-----|-----------------------------------------------------------------------------------|-----|

| 2.2 | SHA-2 Algorithm Parameters                                                        | 46  |

| 4.1 | TRM Implementation Results                                                        | 80  |

| 4.2 | TKM Implementation Results (128-bit Keys)                                         | 81  |

| 4.3 | TRM and TKM Processing Times                                                      | 81  |

| 4.4 | Recovery Protocol Delay                                                           | 85  |

| 4.5 | Exhaustive Search Attack against Trusted Modules                                  | 86  |

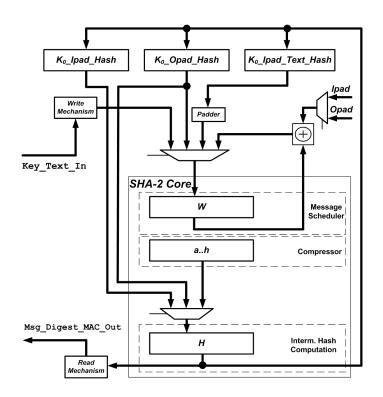

| 5.1 | HMAC Register Names and Sizes                                                     | 96  |

| 5.2 | HW/SW System Implementation Area                                                  | 100 |

| 5.3 | HW/SW SHA-256 Results (1024-Bit Text) $\ldots \ldots \ldots \ldots \ldots \ldots$ | 101 |

| 5.4 | HW/SW HMAC/SHA-256 Results (512-Bit Key, 512-Bit Text)                            | 102 |

| 6.1 | SHA-2 Memory Requirements                                                         | 105 |

| 6.2 | SHA-2 Register Requirements                                                       | 105 |

| 6.3 | SHA-2 Implementation Area                                                         | 110 |

| 6.4 | SHA-2 Frequency of Operation                                                      | 111 |

| 6.5 | SHA-2 Throughput                                                                  | 112 |

| 6.6 | SHA-2 Dynamic Power Consumption                                                   | 113 |

| 7.1 | HMAC Memory Requirements                                                          | 116 |

| 7.2 | HMAC Register Requirements                            | 116 |

|-----|-------------------------------------------------------|-----|

| 7.3 | HMAC Implementation Area                              | 122 |

| 7.4 | HMAC Frequency of Operation                           | 123 |

| 7.5 | HMAC/SHA-2 Clock Cycles for Hash and MAC Computations | 125 |

| 7.6 | HMAC Throughput                                       | 125 |

| 7.7 | HMAC Dynamic Power Consumption                        | 126 |

|     |                                                       |     |

| 8.1 | Resistance Analysis Parameters                        | 136 |

| 8.2 | Probability of Memory Failure                         | 136 |

| 8.3 | Normalized Memory Resistance Comparison               | 137 |

| 8.4 | Probability of Register Failure                       | 138 |

| 8.5 | Normalized Register Resistance Comparison             | 139 |

# List of Figures

| 2.1  | Ionization of a Silicon Surface                                                      | 10 |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | SET in Sequential and Combinational Logic                                            | 12 |

| 2.3  | SET in an SRAM Memory Cell                                                           | 12 |

| 2.4  | Traditional FPGA Architecture                                                        | 14 |

| 2.5  | Traditional Logic Block Architecture                                                 | 15 |

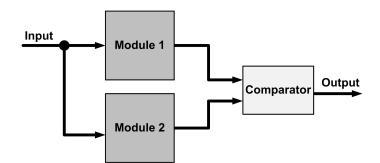

| 2.6  | Dual Modular Redundancy                                                              | 19 |

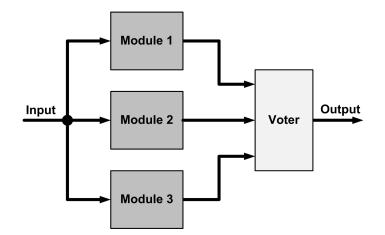

| 2.7  | Triple Modular Redundancy                                                            | 20 |

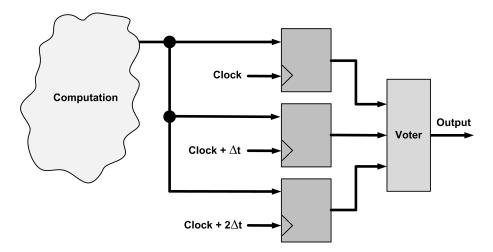

| 2.8  | Time Redundancy                                                                      | 21 |

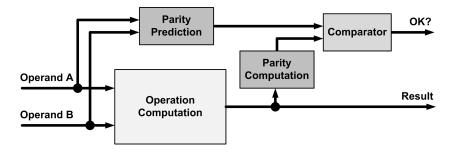

| 2.9  | Parity Prediction                                                                    | 22 |

| 2.10 | Hamming Code-Word Structure                                                          | 23 |

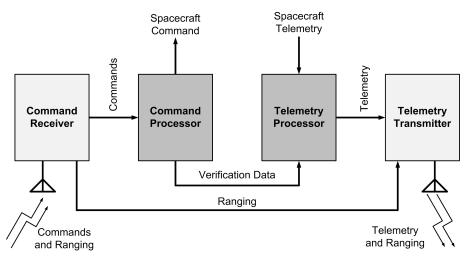

| 2.11 | TT&C Subsystem                                                                       | 26 |

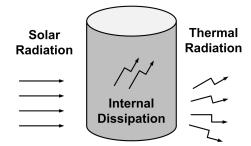

| 2.12 | Thermal Balance                                                                      | 27 |

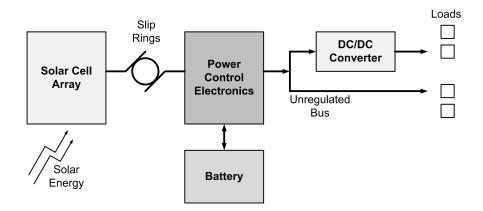

| 2.13 | Power Subsystem                                                                      | 28 |

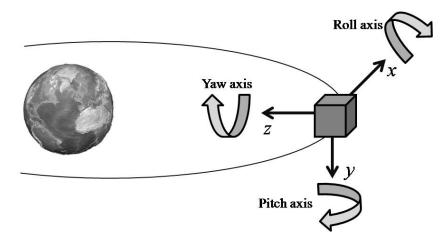

| 2.14 | Attitude Control: Pitch, Roll and Yaw                                                | 30 |

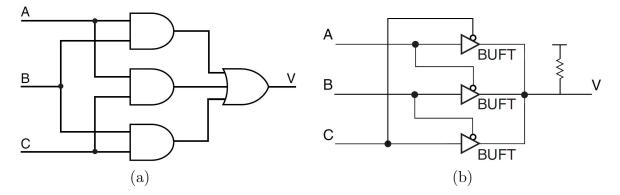

| 2.15 | Majority Voting Implemented with (a) LUTs and (b) Tri-State Buffers from [22]        | 42 |

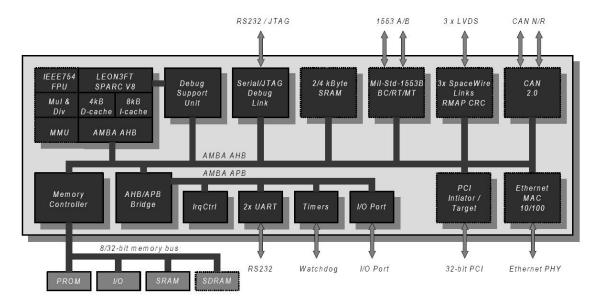

| 2.16 | Leon3-FT Architecture from [67]                                                      | 44 |

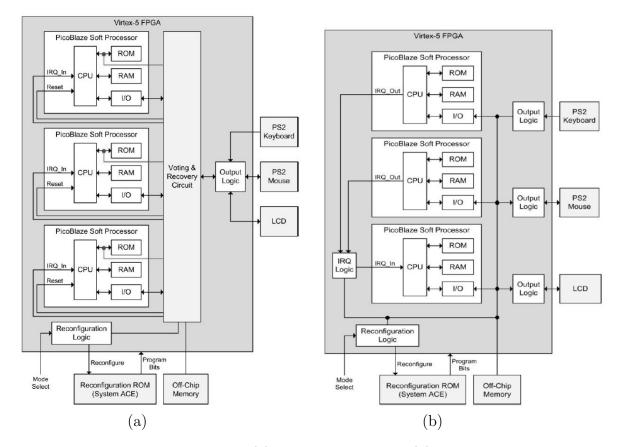

| 2.17 | PicoBlaze Platform in (a) Fault Tolerant and (b) Parallel Processing Modes from [99] | 45 |

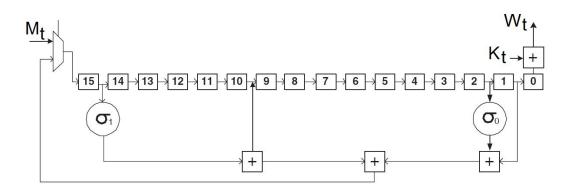

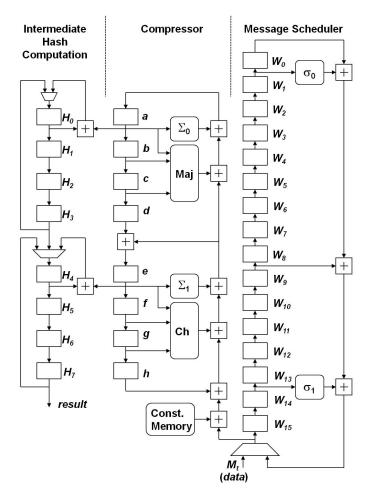

| 3.1  | SHA-256 Message Scheduler Module from [169]                                          | 54 |

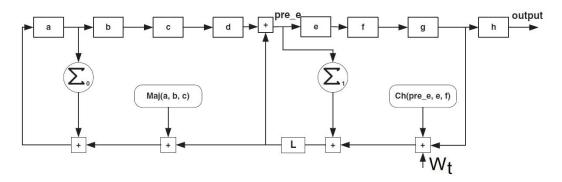

| 3.2  | SHA-256 Compression Function Module from [169]                                           | 54 |

|------|------------------------------------------------------------------------------------------|----|

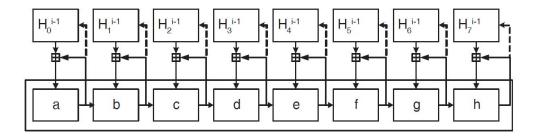

| 3.3  | SHA-256 Intermediate Hash Module from [169]                                              | 55 |

| 3.4  | SHA-512 Message Scheduler using CSAs from [8]                                            | 56 |

| 3.5  | SHA-512 Compression Function using CSAs from [8]                                         | 56 |

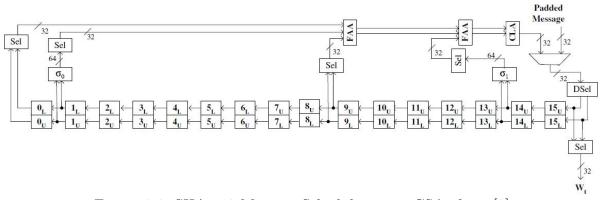

| 3.6  | HMAC Processor Architecture from [96]                                                    | 57 |

| 3.7  | HMAC Processor Architecture from [108]                                                   | 58 |

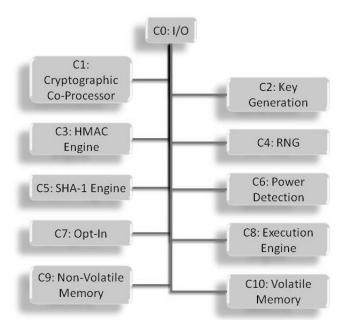

| 3.8  | TPM Architecture from $[57]$                                                             | 59 |

| 3.9  | SHA-512 Datapath with Error Detection from [9]                                           | 61 |

| 3.10 | AES Round with (a) Error Detection and (b) Error Detection and Correction from [15]      | 62 |

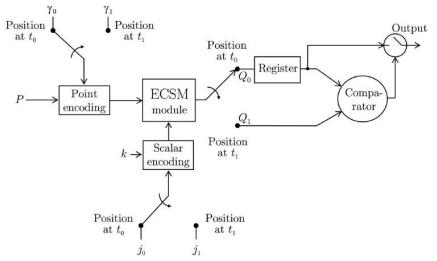

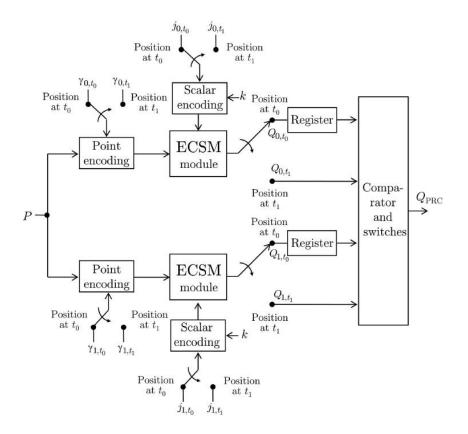

| 3.11 | ECSM using Full Recomputation with Point and Scalar Randomization from [50]              | 63 |

| 3.12 | ECSM using Point and Scalar Randomization with (a) DMR and (b) TMR from [50]             | 63 |

| 3.13 | ECSM using Parallel and Recomputation with Point and Scalar Random-<br>ization from [50] | 64 |

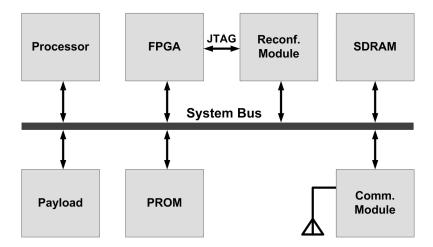

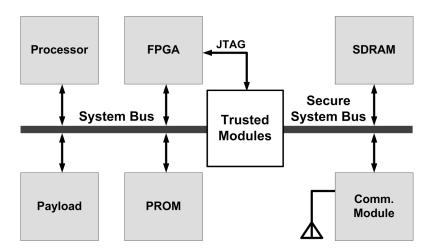

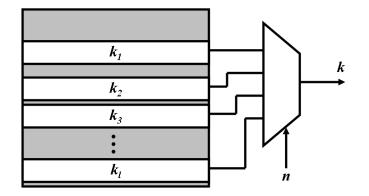

| 4.1  | Untrusted Computational Platform                                                         | 68 |

| 4.2  | Protocol for Hash-Based Key Generation                                                   | 71 |

| 4.3  | Trusted Computational Platform                                                           | 75 |

| 4.4  | Trusted Key Recovery Module                                                              | 77 |

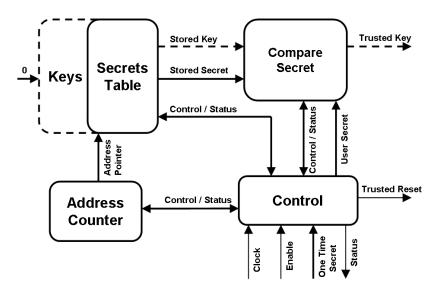

| 4.5  | Trusted Reset and Key Recovery Modules Architecture                                      | 78 |

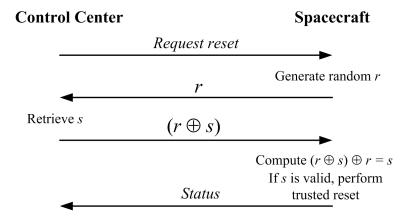

| 4.6  | Protocol for Trusted Reset                                                               | 82 |

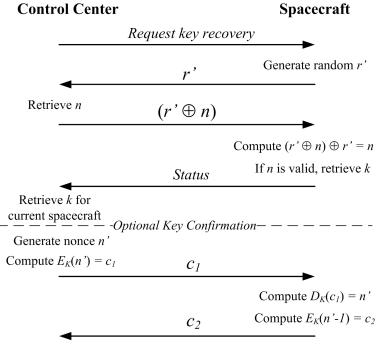

| 4.7  | Protocol for Trusted Key Recovery                                                        | 83 |

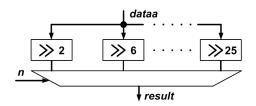

| 5.1  | Block Diagram of Instruction ROTR                                                        | 90 |

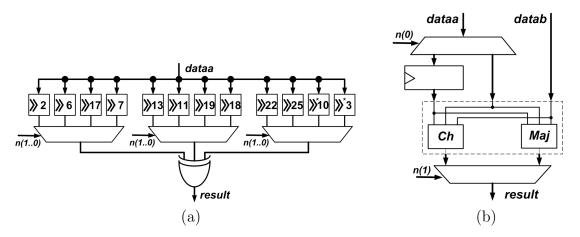

| 5.2  | Block Diagrams of Instructions (a) $\texttt{Sum\_Sig}$ and (b) <code>Ch_Maj</code>       | 91 |

| 5.3  | Block Diagrams of Instructions (a) Sig and (b) Sum_Ch_Maj                                | 92 |

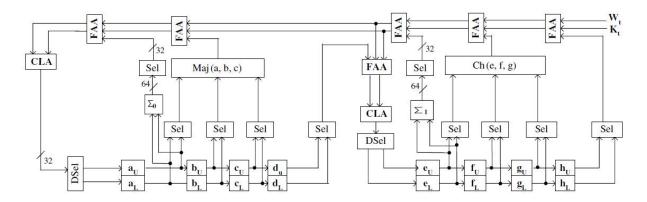

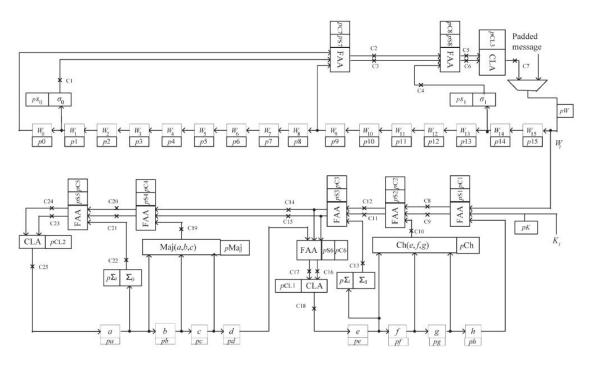

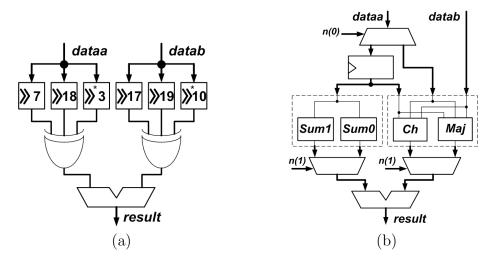

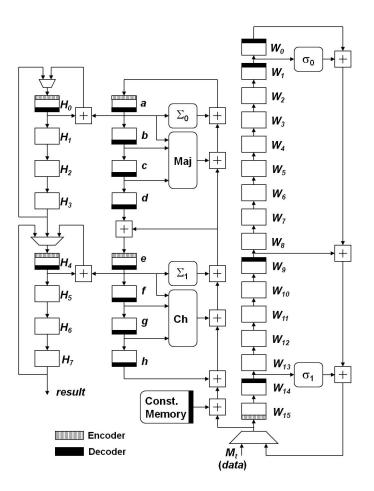

| 5.4  | SHA-2 NoFT Architecture                                                                  | 93 |

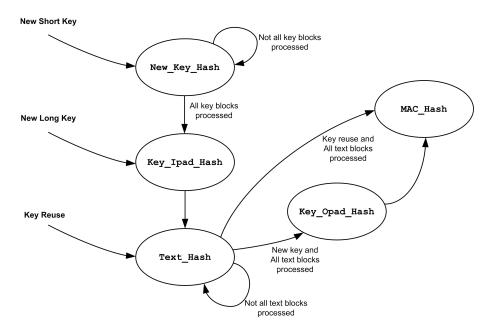

| 5.5 | HMAC NoFT Architecture                                                                         | 95  |

|-----|------------------------------------------------------------------------------------------------|-----|

| 5.6 | HMAC Finite State Machine Diagram                                                              | 97  |

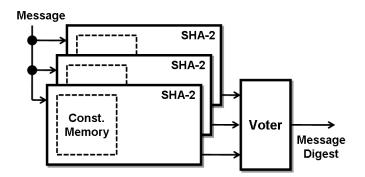

| 6.1 | SHA-2 FullTMR Architeture                                                                      | 106 |

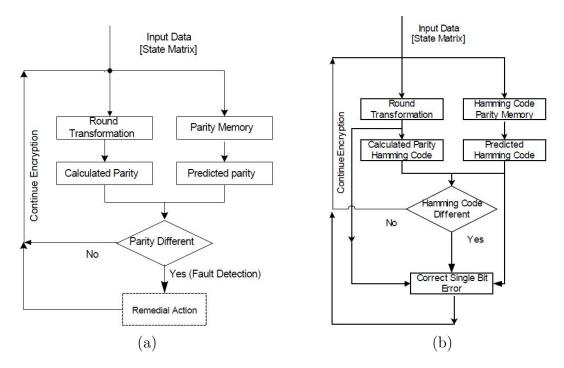

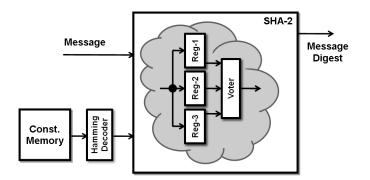

| 6.2 | SHA-2 TMRReg&HCMem Architecture                                                                | 107 |

| 6.3 | SHA-2 HCRegs&HCMem Architecture                                                                | 109 |

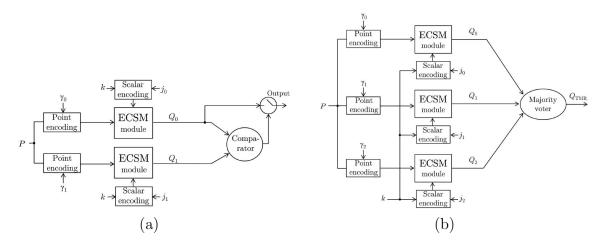

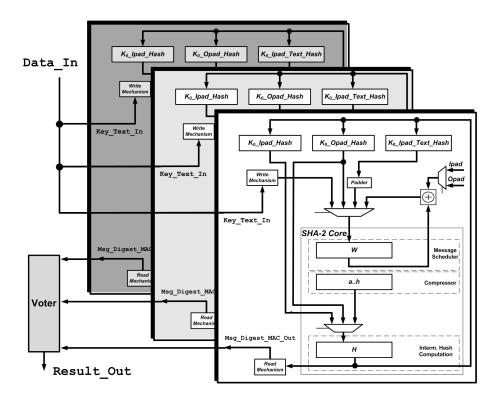

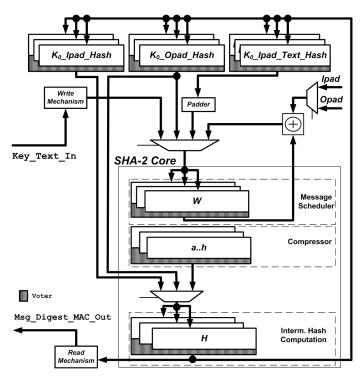

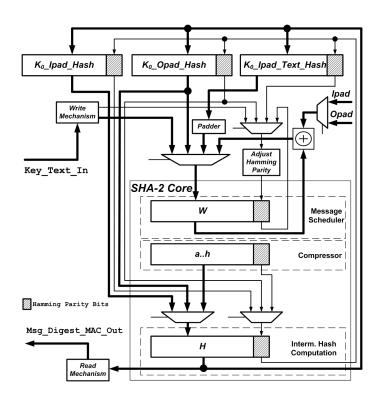

| 7.1 | HMAC FullTMR Architecture                                                                      | 117 |

| 7.2 | HMAC TMRRegs&HCMem Architecture                                                                | 118 |

| 7.3 | HMAC HCRegs&HCMem Architecture                                                                 | 121 |

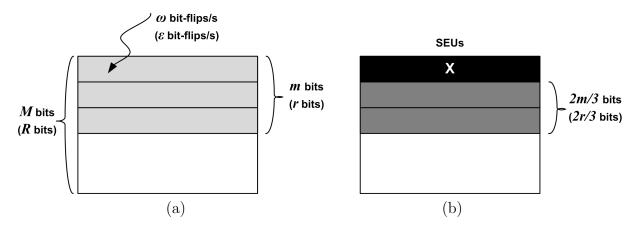

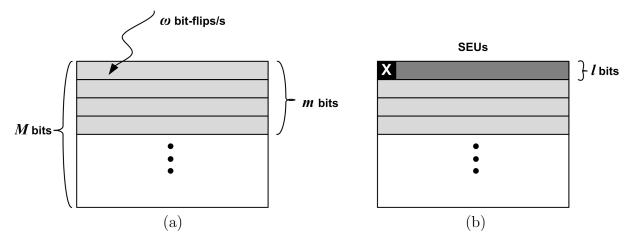

| 8.1 | SEU Resistance Analysis for $\mathtt{FullTMR}\text{'s}$ Memory (and Registers) $\ . \ . \ .$ . | 131 |

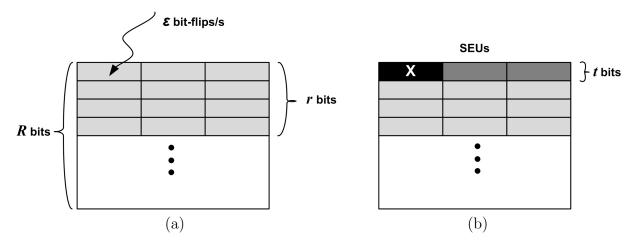

| 8.2 | SEU Resistance Analysis for TMRRegs&HCMem's Memory                                             | 133 |

| 8.3 | SEU Resistance Analysis for TMRRegs&HCMem's Registers                                          | 134 |

| 8.4 | SEU Resistance Analysis for HCRegs&HCMem's Registers                                           | 135 |

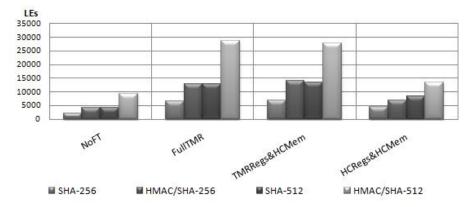

| 9.1 | SHA-2 and HMAC Graphical Comparison of Implementation Area                                     | 145 |

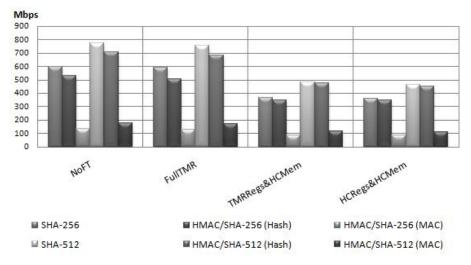

| 9.2 | SHA-2 and HMAC Graphical Comparison of Throughput                                              | 146 |

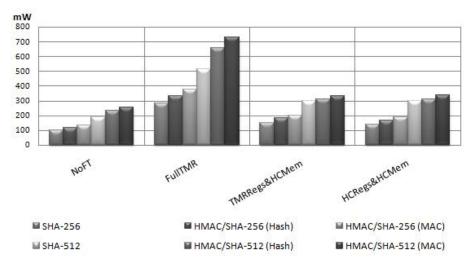

| 9.3 | SHA-2 and HMAC Graphical Comparison of Dynamic Power Consumption                               | 146 |

# List of Abbreviations

| AES                  | Advanced Encryption Standard                        |

|----------------------|-----------------------------------------------------|

| ALU                  | Arithmetic Logic Unit                               |

| AsiaSat              | Asia Satellite Telecommunications Co. Ltd           |

| ASIC                 | Application Specific Integrated Circuit             |

| BRAM                 | Block RAM                                           |

| CCSDS                | Consultative Committee for Space Data Systems       |

| CCTV                 | China Central Television Station                    |

| CLA                  | Carry Look-Ahead Adder                              |

| CLB                  | Configurable Logic Block                            |

| CRC                  | Cyclic Redundancy Check                             |

| CSA                  | Carry Save Adder                                    |

| DOD                  | United States Department of Defense                 |

| DMR                  | Dual Modular Redundancy                             |

| DSS                  | Digital Signature Standard                          |

| ECSS                 | European Cooperation for Space Standardization      |

| EEPROM               | Electrically Erasable Programmable Read-Only Memory |

| EPROM                | Erasable Programmable Read-Only Memory              |

| ESA                  | European Space Agency                               |

| FAA                  | Full Adder Array                                    |

| FPGA                 | Field Programmable Gate Array                       |

| GAO                  | United States General Accounting Office             |

| GEO                  | Geostationary Orbit                                 |

| GLONASS              | Global Navigation Satellite System                  |

| $\operatorname{GPL}$ | GNU General Public License                          |

| GPS                  | Global Positioning System                           |

| GSO                  | Geosynchronous Orbit                                |

| HEO                  | High Earth Orbit                                    |

| HMAC                 | Keyed-Hash Message Authentication Code              |

| IKE                  | Internet Key Exchange                               |

| I/O                  | Input/Output                                        |

| ISO                  | International Organization for Standardization      |

| $\operatorname{JPL}$ | Jet Propulsion Laboratory                           |

| JTAG                 | Joint Test Action Group                             |

| KEK                  | Key Encryption Key                                  |

| LE                   | Logical Element                                     |

| LEO           | Low Earth Orbit                                |

|---------------|------------------------------------------------|

| LTTE          | Liberation Tigers of Tamil Eelam               |

| LUT           | Look-Up Tables                                 |

| MAC           | Message Authentication Code                    |

| MBU           | Multiple Bit Upset                             |

| MEO           | Medium Earth Orbit                             |

| MoD           | British Ministry of Defense                    |

| NASA          | National Aeronautics and Space Administration  |

| NIST          | National Institute of Standards and Technology |

| NRE           | Non-Recurring Engineering                      |

| PROM          | Programmable Read-Only Memory                  |

| RAM           | Random Access Memory                           |

| RNG           | Random Number Generator                        |

| $\mathbf{RF}$ | Radio Frequency                                |

| SHA           | Secure Hash Algorithm                          |

| SHS           | Secure Hash Standard                           |

| SEB           | Single Event Burnout                           |

| SEE           | Single Event Effect                            |

| SEFI          | Single Event Functional Interrupt              |

| SEGR          | Single Event Gate Rupture                      |

| SEL           | Single Event Latchup                           |

| SET           | Single Transient Effect                        |

| SEU           | Single Event Upset                             |

| SKI           | Secret Key Infrastructure                      |

| SRAM          | Static RAM                                     |

| SDRAM         | Synchronous Dynamic RAM                        |

| TCG           | Trusted Computing Group                        |

| THCM          | Trusted Hash and Configuration Module          |

| TID           | Total Ionizing Dose                            |

| TKM           | Trusted Key Recovery Module                    |

| TM            | Trusted Module                                 |

| TMR           | Triple Modular Redundancy                      |

| TPM           | Trusted Platform Module                        |

| TRM           | Trusted Reset Module                           |

| TT&C          | Telemetry, Tracking and Command                |

| UK            | United Kingdom                                 |

| U.S.          | United States                                  |

| USA           | United States of America                       |

### Epigraph

I do not know what I may appear to the world, but to myself I seem to have been only like a boy playing on the sea-shore, and diverting myself in now and then finding a smoother pebble or a prettier shell than ordinary, whilst the great ocean of truth lay all undiscovered before me.

Isaac Newton (1643-1727)

## Chapter 1

## Introduction

This chapter presents the motivation that led to the development of this research, and lists the main contributions resulting from this thesis. It also provides the reader with a summary of each chapter that comprises the remainder of this document.

### 1.1 Motivation

Spacecrafts are extensively used by public and private sectors to support a wide variety of services. For instance, they provide communication services, support navigation and meteorological services, allow for scientific experiments to be conducted, and are even utilized to increase homeland security. Some countries also employ non-military satellites to increase their military communication capabilities. For instance, during the Desert Shield and Desert Storm operations the United States (U.S.) Department of Defense (DOD) used commercial satellites to perform 45% of all communications between the U.S. and the Persian Gulf [140]. With regard to the costs involved, the space sector is a multi-billion business. According to a report from the U.S. General Accounting Office (GAO) [140], the commercial satellite industry generated \$85 billion in revenue in 2000. The Galileo program [54] from the European Space Agency (ESA) [53] had an initial cost of 3.4 billion Euros [52], with a recent request of additional 1.9 billion Euros [125] to complete the program. Galileo is estimated to have an annual market for services and equipment of 200 billion Euros by 2013 [52].

Considering the numbers presented above, the disruption of satellite services, whether intentional or not, can have a major economic impact. For example, in 1998 a failure of the Galaxy IV satellite disrupted about 80 to 90 percent of 45 million pagers across the U.S. for 2 to 4 days [140]. This failure also blocked the authorization of credit card transactions at points of sale such as gasoline pumps. With the growing worldwide demand for satellite-based services, the dependence on these spacecrafts tends to increase and so do the financial losses in case of failure. As a result, spacecrafts must perform with high reliability and availability.

The construction, launch and operation of spacecrafts are usually carried out by space agencies and contractors. Details of such activities are traditionally not made available to the general public, leading to the false impression that third parties cannot tamper with or compromise spacecrafts after launch. However, as mentioned in [24], advances in technology allow for more complex attacks to be easily launched against space systems. As a result, it is definitely not a good strategy to rely on obscurity and uniqueness to assure the security of spacecrafts. Anti-jamming techniques are used to avoid interference with communications. However, strong security becomes mandatory if the spacecraft is to be protected against attackers. For example, if security is not addressed properly, an attacker could possibly perform replay attacks, intercept proprietary data, send invalid commands, or masquerade as a legitimate user.

Due to the current lack of appropriate countermeasures to protect spacecrafts, the probability of success may be high if some individual, group, or organization put effort in compromising space systems. Not only satellites orbiting Earth are at risk, but also deep space spacecrafts and probes. For instance, several TV transmissions based on satellites have already been attacked and hijacked [103]. Some of them were used to transmit adult content to inappropriate audiences, while others transmitted propaganda and protest material [138, 124, 49, 142, 153, 113, 141]. Although these incidents were related to the tampering of the satellites' data link, the incident can become even more serious if the Tracking, Telemetry and Control (TT&C) link is targeted. If the TT&C link is attacked, the spacecraft may be put out of its orbital path, dropped down to Earth, or compromised in such a way that it can become nothing else than space junk. For instance, reports indicate that attackers took control of a British satellite and demanded money to give the control back to the operators [56, 72, 126].

Since countries rely heavily on commercial satellites for communication, threats to those spacecrafts have the potential of putting a nation's critical infrastructures at risk [140, 145, 14]. For instance, at the time the United Kingdom (UK) Ministry of Defense (MoD) satellite was attacked, Margaret Beckett, leader of UK House of Commons, warned about the big impact that electronic attacks can have in Britain's communications infrastructures. She complemented: "Hijacking a satellite is one of the first activities in an infowar attack". Therefore, as pointed out by the U.S. GAO [140], it is evident that security of spacecrafts

should be more fully addressed.

The implementation of strong security mechanisms in spacecrafts is not straightforward [23]. One of the difficulties encountered is the protection of security mechanisms from the harsh environment found in space. Radiation originating from both the Sun and deep space is the best documented cause of a class of errors known as Single Event Upsets (SEUs) [107]. SEUs are forms of soft errors, i.e., they are errors that occur in the circuitry of a system causing bit-flips, but are not damaging to the hardware. According to a study of on-orbit spacecraft failures [168], 45% of failures happen due to electrical reasons. Of all subsystems failures, 27% happen in the telemetry, tracking and control (TT&C) as well as in the command and data handling subsystems (CDH), mainly due failures in control processor 26%, in electric circuitry 17%, and computer resets 7%. Considering these two subsystems, the TT&C alone is responsible for more than 70% of the failures.

Although SEUs are of great concern in aerospace applications, some applications can comfortably tolerate bit-flips. On the one hand, a photo taken by an Earth observation satellite may not get corrupted if a bit-flip happens in a storage element holding one of its pixels. On the other hand, cryptographic computations are very sensitive with respect to SEUs, so that a bit-flip in cryptographic data is enough to cause the cryptographic computation to fail. For example, a bit-flip in early rounds of AES can cause 50% of the bits of the result to be erroneous [17]. As reported in [168], about 35% of the failures that happen on TT&C and CDH leads to the loss of the mission whereas 60% of them leads to the mission degradation. Therefore, the fault tolerant implementation of cryptographic primitives in the aforementioned spacecraft subsystems is crucial to ensure that mission reliability is not decreased by the utilization of security mechanisms.

Once launched, spacecrafts follow their orbital or deep space paths. The duration of their operational lifetimes, in turn, may vary from a couple of months to decades. Therefore, they must be capable of operating for long periods of time without physical maintenance. An exception to this case is the Hubble Space Telescope [120], which was serviced four times since it began its operation in 1990. In all those occasions, the Space Shuttle [123] was used. Since the average cost to launch the Space Shuttle is \$450 million [123], post-launch maintenance is performed only in rare exceptions (not to mention the retirement of the Space Shuttle program in 2011). Post launch maintenance is not the case for the whole majority of spacecrafts. As a consequence, it is crucial to design fault tolerant systems, so that the effects of radiation on circuits do not cause critical failures. Such failures could disrupt the normal operation of the spacecraft or even cause its loss.

Furthermore, the fact of employing rockets to launch spacecrafts into space imposes very stringent restrictions on the hardware size and weight. Also, given that spacecrafts are usually powered by solar panels and re-chargeable batteries, there are heavy restrictions on power consumption of their electrical subsystems. Additionally, heat transfer in space is solely carried out by conduction and radiation. The lack of convection imposes severe constraints on power dissipation of on-board circuitry. Finally, given the tight budget which is very often imposed on space agencies, the cost of embedded components must also be considered when building spacecrafts. As part of the computational subsystem of spacecrafts, cryptographic primitives used in space applications must take all these constraints into account while being designed and implemented.

### **1.2** Contributions

Given the range of threats against spacecrafts and the multiple constraints imposed by space systems, this research has the main goal of proposing fault tolerant security mechanisms for space applications. Specifically, main problems being addressed in this research include:

- 1. How to recover a spacecraft from an attacker who has gained control over its computational platform?

- 2. How to perform a secure restoration of the spacecraft's cryptographic capabilities in face of failures and attacks?

- 3. How to maximize security in the recovery mechanism and how to quantify it?

- 4. How to achieve efficiency in fault tolerance mechanisms for cryptographic primitives tailored to space applications so that they can cope with radiation-induced faults and demand minimum implementation requirements?

- 5. How to determine the resistance against of SEUs of fault tolerance mechanisms and how to compare different schemes?

In face of the aforementioned questions, the first goal is to propose schemes to recover the spacecraft and its cryptographic capabilities after major failures or attacks have occurred. A major failure can result from SEUs, a power outage, and/or a temperature variation. Since cryptographic data is quite sensitive to bit-flips, an SEU in cryptographic computation will certainly lead to failures. Furthermore, even when space systems implement security mechanisms, attackers can potentially exploit security holes to break into the system. In that case, there should still exist some means to bring the spacecraft control back to the ground operators. More precisely, it is necessary to detect when attacks or failures have happened, bring the spacecraft to a safe state, and re-establish a secured communication channel with the control center.

The second goal relates to proposal and evaluation of fault tolerant schemes for integrity and authentication schemes. More specifically, the main focus is on the Secure Hash Algorithm (SHA-2) [133] and on the keyed-hash message authentication code (HMAC) [132] based on SHA-2. Hash functions can be applied to space systems in many different ways. It could be employed in invasion detection and recovery schemes [88] to determine, for example, whether an attacker, who may have broken into the spacecraft, has tampered with the system's program memories or the configuration of Field Programmable Gate Arrays (FPGAs). Integrity and authentication are also of utmost importance in secure communications. For instance, they are used to certify that the data received from a control center was not modified and came from a valid control center (not from an attacker). As a result, it becomes possible to assure, for example, that maneuvering commands are from a legitimate operator and that they were not accidentally or maliciously compromised. Authentication mechanisms are fundamental when updating the spacecraft hardware and software in case of attacks and failures. Moreover, the resistance against SEUS of each fault tolerant technique proposed for SHA-2 and HMAC was evaluated through a probability of failure analysis. Such an analysis allowed for the comparison of the proposed schemes against well established for space systems such as Triple Modular Redundancy (TMR).

### **1.3** Thesis Overview

The remainder of this thesis is organized as follows:

Chapter 2 provides a short introduction to fault tolerance and space systems. It includes fundamental concepts, commonly used definitions, and an introduction to radiation effects on electronic circuits. Also, technological, architectural and recovery techniques for mitigating SEUs are presented. In addition, several aspects of space systems are described, such as spacecraft subsystems, space missions types and security levels. Several threats against space systems are reviewed followed by a number of known attacks that have been reported during the last couple of decades. Moreover, a set of security requirements for space systems is presented, most of them based on standards and recommendations of the Consultative Committee for Space Data Systems (CCSDS).

Chapter 3 comprises the state-of-the-art in security for space systems. It includes some traditional SEU mitigation techniques that have been used in space applications. Next,

previous research on hardware implementation of cryptographic primitives is presented. Although most of them do not consider fault tolerance, they provide ideas and optimization techniques that can be adopted in conjunction with mitigation schemes. Some proposals of fault tolerant security mechanisms that could be utilized in space systems are also presented in this chapter.

Chapter 4 presents proposals for fault tolerant system recovery. Specifically, the proposed approach rely on a trusted platform along with a challenge-response protocol to recover spacecrafts in case of major failures and attacks followed by the re-establishment of their cryptographic capabilities. The system recovery process relies on the computation of integrity checks, which in turn employ fault tolerant hash functions.

Chapter 5 introduces hardware/software approaches tailored for SHA-2 and HMAC algorithms. Several levels of partitioning are explored, which includes simple operations implemented as custom instructions as well as entire SHA-2 and HMAC algorithms implemented as peripherals. Through experimental results based upon a NIOS2 processor it was possible to precisely determine the gains of performance in face of the increase in the system implementation area.

Chapter 6 proposes efficient fault tolerance mechanisms targeting SHA-2 hash functions. Several hardware design architectures are evaluated in hardware implementations based on FPGAs. Furthermore, implementation aspects of each approach are discussed, such as implementation area, memory requirements, power consumption, frequency of operation, and throughput. As a result, it was possible to show that the proposed scheme based on information redundancy provides fault tolerance with considerable savings in terms of implementation area, memory requirements and power consumption.

Chapter 7 explores the fault tolerant technique based on information redundancy to HMAC. Again, several hardware designs were proposed and analyzed using FPGAs. Experimental results have shown that the proposed technique provides even better implementation results for HMAC, which has a more complex architecture compared to SHA-2.

Chapter 8 introduces a probabilistic analysis in order to determine the robustness of each fault tolerance mechanisms in the presence of SEUs. A systematic analysis of the resistance against of SEUs is a crucial complementary step towards a more comprehensive evaluation the fault tolerant cryptographic modules. Through the determination of the probability of failure of each module, it was possible to directly compare the different fault tolerance approaches considered in this research, including the widely used TMR.

Chapter 9 discusses the contributions of this research and compares them with related work. Additionally, this chapter presents the conclusions of this thesis and future work.

# Chapter 2

# Background

This chapter comprises three main sections. The first one aims at providing background information on fault tolerance, which includes fundamental concepts and definitions, radiation effects on electronic circuits, as well as SEU mitigation techniques. The second section provides an overview on space systems, which comprises spacecraft subsystems, types of space missions and associated threats, security requirements, and hardware platforms in space. The last section introduces the SHA-2 and HMAC algorithms which are further utilized in the following chapters.

## 2.1 Fault Tolerance

Nowadays, computer systems are employed in a wide variety of tasks, varying from text editors and web browsers to embedded control of devices, machines and spacecrafts. On the one hand, when a text editor crashes, it may not cause much more than frustration and limited loss of data. On the other hand, a failure in a medical, military or aerospace system can pose threats to human life and national security, as well as cause environmental disasters and severe losses. Consequently, these critical tasks demand the employment of fault tolerant computer systems.

### 2.1.1 Fundamental Concepts

There are three fundamental concepts in the fault tolerant field: fault, error and failure. A fault refers to the occurrence of events in hardware and software, such as the alteration of

a physical property, a manufacturing imperfection, or a programming bug. Errors can be defined as consequences of faults, which cause the deviation of a given information from its correct value. A failure is a consequence of an error and is manifested as a corrupted execution of a given task [87].

Alternatively, faults, errors and failures can be explained by considering three universes, namely physical, informational and external [87]. The physical universe is constituted of physical entities, such as semiconductor devices. A fault is then defined as the physical alteration or defect of a component in the physical universe. On top of that comes the informational universe, which comprise pieces of information, such as a byte (or any other data unit). When a piece of information gets corrupted, it is said that an error has occurred. Finally, there is the external universe, where the consequences of errors show up. The incorrect result or processing, caused by errors, is called a failure.

To illustrate the differences between those three concepts, consider a high energy particle hitting a silicon chip. This collision could upset the charge balance on silicon causing a transistor to switch off. This alteration of physical properties can be denoted as a fault. If the affected transistor is used to implement a register, some stored information can be altered. The consequence is going to be an error in the data stored in the register. Next, by using this corrupted register, a cryptographic algorithm will certainly perform, for example, an erroneous signature check therefore causing a failure.

#### 2.1.1.1 Design Goals

Systems are designed with multiple goals in mind, where functionality and performance are the more common ones. However, some other requirements are very often found in space applications, such as reliability, availability, and safety. The inclusion of fault tolerance into the system can help designers to meet the aforementioned requirements.

**Reliability** is defined as the probability that a system will perform its designed tasks for a certain period of time, say  $[t_0, t]$ , assuming that it was perfectly functional at  $t_0$ . During  $[t_0, t]$  no incorrect performance or maintenance is acceptable. In space applications, t can be in the order of decades. Fault tolerance can improve system reliability by keeping it functional when hardware and software failures occur. This can be achieved, for example, through the use of redundant units, so that the system can operate even when one or more units are not functional. Availability is the probability that a system is operational at the instant of time t. That is to say that the system has a very narrow time frame to recover from failures. Hence, it is possible to have frequent, but short, periods of inoperability and still achieve high availability. The use of spare units, for example, favors high availability, if tasks can be transfered from one unit to the other in a short time frame.

**Safety** refers to the capability of the system to fail in a safe manner. It is defined as the probability that the subsystem will function correctly or will stop working in such a way that it does not disturb the rest of the system. Detecting subsystem failures and disrupting its abnormal functioning is fundamental for achieving safety.

#### 2.1.2 Radiation Effects

Radiation effects on electronic chips can vary from temporary malfunction to permanent damage [121]. They can suffer from Total Ionizing Dose (TID) Effects as a result of a long exposure to radiation. Also, they can be caused by a single energetic particle and then are denoted as SEEs. TID effects are consequences of accumulating ionizing damage, which causes devices to suffer with, for example, threshold shifts, increased current leakage and altered functional timing. They are mainly caused by protons and neutrons, usually found in Solar Wind, in the Van Allen Belt, and in Cosmic Rays [121]. TID effects can be reduced through device shielding, but since that involves the device manufacturing, it is out of the scope of this research. SEEs are caused by high-energy subatomic particles and electromagnetic waves, which can come from many different sources. High-energy subatomic particles, such as electrons, protons, neutrons, alpha particles (Helium nuclei), heavy ions (heavier than Helium), commonly found in Solar Wind, in the Van Allen Belt, and in Cosmic Rays. Electromagnetic waves, such as X-rays and gamma rays can be found in cosmic rays and in radioactive decay. The interaction of cosmic rays with Oxygen and Nitrogen present in the Earth's atmosphere also generate neutrons as well as other secondary particles such as pions and muons.

SEEs can happen at the ground level, aircraft altitudes, and in space [102]. At the ground level, they are mainly caused primarily by neutrons and secondarily by protons. At the sea level, for example, an average flux of 20 neutrons/ $cm^2$ /hour can be found. However, not only radiation coming from space interferes with applications at the ground level. The packaging material of chips may contain radioactive impurities, whose radioactive decay emits particles with the potential of causing SEEs. Airborne applications face higher levels of neutrons flux, more specifically, 7,200 neutrons/ $cm^2$ /hour. Therefore, they are

more prone to suffer SEEs than applications on the ground. Nevertheless, ground level and airborne applications are naturally protected by the Earth's atmosphere. Radiation coming from space, such as gama rays, X-rays, protons, alpha particles and heavy ions, are mainly absorbed by the Earth's atmosphere. That implies that spaceborne applications suffer more severely from its direct exposure to radiation coming from space. Although the Earth's magnetosphere deflects most of the Solar Wind, some radiation are still able to reach Earth's atmosphere and surface in polar regions. Besides, the magnetosphere traps protons, electrons, and other nuclei such as alpha particles. This region of trapped particles is called Van Allen Belt. As a consequence, spacecrafts operating past the Earth's magnetosphere must deal with higher levels of radiation, either trapped in the Van Allen belt or coming from space.

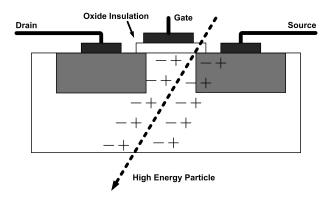

When subatomic particles and electromagnetic waves carry enough energy, they can displace electrons, atoms and molecules. This process is referred to as ionization. As pictured in Figure 2.1, an ionizing radiation transversing a silicon chip creates a track of electron hole pairs. The consequence is a charge accumulation, which might become a transient current pulse (often called a glitch). This phenomenon is denoted as Single Transient Effect (SET).

Figure 2.1: Ionization of a Silicon Surface

Advances in technology have made it possible to build transistors with reduced dimensions, thinner gate oxides, and lower operation voltages. As a consequence, information can be represented or stored using electric signals with reduced intensity. As a result, particles that once used to be innocuous, can now have higher potentials to cause upsets. In other words, as transistor sizes scales down, they become more sensitive to SEEs.

Several types of SEEs can happen within digital circuits [5]. If a transistor has a parasitic PNPN structure, radiation effects can cause the parasitic transistor to turn on

the primary one indefinitely. More specifically, this transistor pair acts like a thyristor. This phenomenon is called Single Event Latchup (SEL). The only way to turn off the induced thyristor is to power cycle the device. Another phenomenon happens when a transistor is turned on by radiation and its drain-source voltage is higher than the device's breakdown limit. The consequences are excessive drain-voltage currents and overheating, therefore causing the transistor burn out. This event is denoted as Single Event Burnout (SEB). Yet another effect caused by radiation is called Single Event Gate Rupture (SEGR). It happens when ionizing radiation hits the transistor at the same time a high voltage is applied its gate. The result is the rupture of the gate's dioxide insulation, followed by overheating and destruction of the gate region. Likewise SEBs, SEGRs causes permanent damage to the transistor. Nevertheless, the more common consequences of SETs are SEUs.

#### 2.1.2.1 Single Event Upsets

An SEU can be defined as a change of state in storage elements as a consequence of ionizing radiation. Since digital computers manipulate information in its binary representation, a change of state is basically a bit-flip in registers or memory elements. SEUs are considered soft errors in the sense that they do not cause permanent damage to the circuit. Actually, the effects of SEUs over registers and memory can be reversed by rewriting the correct information to the storage element. Given that an SEU is a more common consequence of an SET, the former is of main interest in this research. In order to adopt countermeasures to mitigate SEUs in digital circuits, it is necessary to understand how SEUs are generated. SETs can happen in combinational and sequential logic of digital circuits.

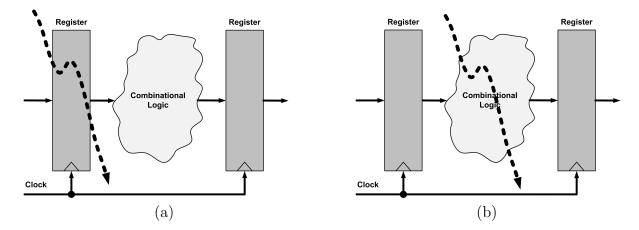

A typical digital circuit configuration very often found in sequential circuits is illustrated in Figure 2.2. It consists of a register feeding a combinational logic, which in turn writes its results back to a register. If an SET happens in a register, as depicted in Figure 2.2 (a), it can cause its transistors to change state therefore flipping the stored bit. In this case, it is said that an SEU happened directly in the register. As a consequence, the combinational logic will receive an incorrect input value coming from the registers. SETs can also occur in a transistor of the combinational part of the circuit, as shown in Figure 2.2 (b). The inversion of a transistor state will cause a flipped signal to propagate through the combinational logic. Eventually, this corrupted output reaches the input of a register. Next, if setup and hold times of the register are met, the input will be sampled at the rising (or falling) edge of the clock. The result is an incorrect computation being stored within a register, i.e. an indirect register SEU occurring through the combinational logic.

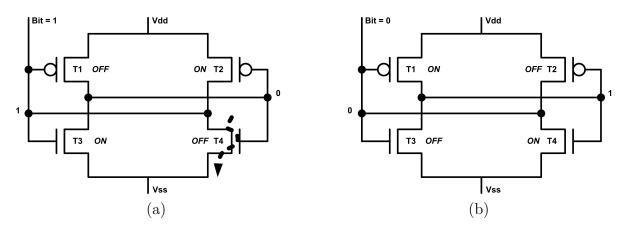

Similarly, SETs can cause SEUs in SRAM memory cells. Figure 2.3 (a) shows a simplified SRAM memory cell, consisting of four transistors, T1, T2, T3, and T4, as preseted

Figure 2.2: SET in Sequential and Combinational Logic

in [102]. Depending on the states of the transistors, the cell can store a '0' or a '1'. Assuming that the transistors are in such a configuration that the cell holds the value '1' as the information bit. Also, let a SET happen in the gate of transistor T4, as illustrated in Figure 2.3 (a), causing it to turn on. Consequently, the upper-left and bottom-left transistors will be, respectively, turned on and off. Also, the up-right transistor will be turned off. The result is an inversion on the value of the stored bit, which became '0', as shown in Figure 2.3 (b). In sum, an SEU happened in the SRAM cell.

Figure 2.3: SET in an SRAM Memory Cell

Although SEUs in a single bit has been discussed so far, multiple bits can also be affected by a single high-energy particle. Depending on the angle of incidence of the particle, it may travel through several transistors therefore causing the so called Multiple Bit Upset (MBU). Due to the two-dimension disposition of transistors on a chip die, MBUs are less likely to happen than SEUs. However, due to transistor scaling, a single particle can affect neighboring transistors, thus causing MBUs to occur more often. Moreover, depending on a combinational logic fan-out, a single SET can provoke multiple transient pulses at the outputs. Again, if these SETs meet setup and hold times, they can upset multiple registers therefore causing MBUs.

SEUs can also interfere with controlling portions of a digital circuit, for example, its state machine. As a consequence, the circuit can enter invalid states and even come to a complete halt therefore requiring a power cycle to come back to normal operation. This functional disruption due to SEUs are denoted Single Event Functional Interrupt (SEFI).

#### 2.1.3 SEUs in ASICs and FPGAs

ASICs are customized integrated circuits designed to perform a dedicated function. They can be designed using three main techniques: Standard Cells, Gate Arrays, and Full Custom. Standard Cell employs third party tools and utilizes a library of pre-fabricated building blocks (the so called standard cells) to design the integrated circuit. Once the physical placement of all standard cells is done, the designer must perform the circuit routing therefore electrically connecting all the standard cells. At the end, lithographic layers are produced, which are then used to fabricate the chip die. In contrast, Gate Array design does not employ individual cells. Instead of that, several pre-designed lithographic layers are employed, each of them consisting of transistors, gates and other devices. In this technique, all the appropriate elements must be connected together to obtain the desired circuit functionality. Alternatively, the Full Custom approach requires all elements of the entire lithographic layers to be designed. In other words, all the transistors of the chip are individually conceived and electrically connected.

Regardless of the technique used, chip dies are produced following the specifications of lithographic layers. After that, the chip's functionality is fixed and no further modification is possible without a chip re-spin. Although ASICs' combinational logic can suffer from SEUs, the implemented circuitry cannot be altered by such upsets. Consequently, ASICs provide high immunity against SEUs regarding its circuit functionality. However, radiation effects on the transistors of an ASIC can still cause SEUs in registers and memory elements, as previously described.

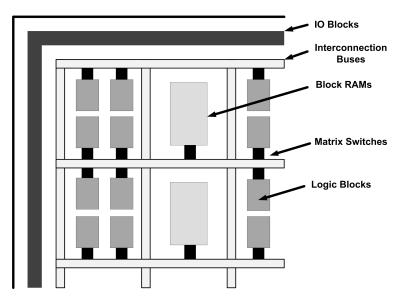

FPGAs are devices based on an architecture that can be configured in many different ways, following the designer's specifications. A traditional (simplified) FPGA internal architecture, as illustrated in Figure 2.4, is constituted by Logic Blocks, Input/Output (I/O) Blocks and Block Random Access Memories (Block RAMs) which are electrically connected by Routing Matrices and Interconnection Buses. More precisely, the term *programming* refers to the process of configuring and interconnecting the FPGA's internal elements. This is achieved by 1) configuring the Logic Blocks and Block RAMs with the appropriate binary values; 2) configuring the Routing Matrices to turn on and off the appropriate connections; and 3) configuring I/O Blocks to function as input, output, or tri-state pins.

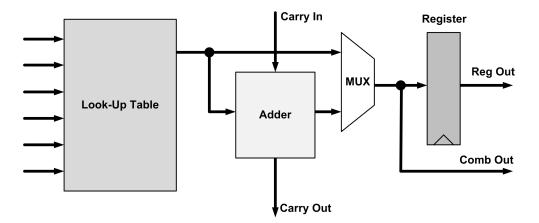

Figure 2.4: Traditional FPGA Architecture

Logic Blocks are configurable elements which implement combinational logic by using Look-Up Tables (LUTs). Specifically, a traditional Logic Block is composed of a LUT, an adder (or carry logic), a multiplexer and a register, as shown in Figure 2.5. I/O Blocks perform the signal interfacing between the FPGA's internal elements and its external circuitry. Block RAMs are on-chip memory based on Static RAM (SRAM) cells. Interconnection buses are sets of wires responsible for electrically connecting the Logic Blocks, Block RAMs and I/O Blocks. Actually, the fine-grained connection between those elements and the Interconnection Bus is performed by a set of multiplexers, namely Matrix Switches. By using this architecture, for instance, it is possible for the FPGA to receive input signals, route it to the Logic Block, perform a computation, and output the results. Obviously this is a trivial example in face of the very complex designs currently supported by FPGAs.

FPGAs are produced by several manufacturers, such as Altera [41], Xilinx [84], Actel [36], QuickLogic [48], Atmel [44], and Lattice [47]. Most of them implement an archi-

Figure 2.5: Traditional Logic Block Architecture

tecture similar to the one aforementioned.

FPGAs are available in different technologies: SRAM, Flash and Anti-fuse. One-time configurable devices named structured ASICs are also currently available. The type of FPGA is defined by the technology used to implement its configuration memory, which also determines whether the device can be reconfigured. Independently of implementation technology, most devices include Block RAMs traditionally constructed from SRAM cells. Moreover, all devices implement registers within their Logic Blocks.

Advantages and disadvantages exist for each of those devices. Some may provide high resistance against radiation and no reconfigurability. Others may provide high density and reconfigurability, but no protection against radiation. For the whole majority of devices, both SRAMs cells and registers are sensitive to SEUs and must be protected through the use of mitigation techniques. According to the FPGA features, a given type of device becomes more suitable to specific subsystems of the spacecraft.

**SRAM-based FPGAs** can provide reconfigurability, high density and high performance. These features make these FPGAs attractive for space applications. Current devices support the implementation of very complex systems while keeping satisfactory performance. However, SRAM FPGAs consumes a considerable amount of power when compared to ASICs. Besides, their configuration elements are based on SRAM memory and can be affected by SEUs [71]. If an SEU occurs in a bit of a LUT, it can modify the implemented combinational logic. Also, an SEU in a memory cell of a Matrix Switch can connect (or disconnect) a wire, therefore compromising the correct signal routing. In addition, an SEU in an I/O Block can turn an output pin into an input pin and vice-versa.

In sum, an SEU in a configuration element can easily disrupt the functioning of an entire design implemented in the device. Due to the vulnerability of their configuration elements to SEUs, fault tolerant techniques must be carefully chosen to guarantee the functionality of the design implemented within the device. Also, SRAM-based FPGAs tend to be used in applications where some failures might be tolerated. Good examples are payload systems which are usually complex in terms of functionality, but not crucial to the normal operation of the spacecraft. Applications requiring high reliability such as control of the spacecraft may be implemented using ASICs, flash and anti-fuse FPGAs.

**Flash-based FPGAs** employs non-volatile memory cells based on flash memory technology to store the device configuration. Since flash memory can be electrically erased and reconfigured, the device can be reprogrammed. Additionally, radiation cannot easily modify the state of flash cells, which makes the device configuration resistant to SEUs. These FPGAs can provide both low power consumption than SRAM-based FPGAs, although still higher than anti-fuse devices. However, the frequency of operation of the latter is usually lower than the former. Flash-based FPGAs do not currently provide such high density as their SRAM counterparts do [62]. However, an advantage is that the configuration elements of flash-based FPGAs offer very high immunity to SEUs [32, 64]. As a result these devices can be used to implement important subsystems, which require both reliably and reconfigurability, as is the case of TT&C and attitude control.

Anti-fuse FPGAs use metal-to-metal connections to define their configuration. Given that these connections are permanent, an anti-fuse FPGA is programmed only once and cannot be reconfigured. Furthermore, metal-to-metal connections cannot be altered by radiation. Thus, the configuration of anti-fuse FPGAs are immune to SEUs and more reliable than reconfigurable FPGAs. Further, anti-fuse FPGAs consume very low power compared to SRAM FPGAs. If no reconfigurability is needed, anti-fuse FPGAs is a very good option to achieve high reliability and low NRE costs. This is normally the case of TT&C and attitude control subsystems of spacecrafts.

**Structured ASICs** represent another promising technology for space application. Examples include HardCopy [37] and EasyPath [80] from Altera and Xilinx, respectively. Structured ASICs combine both the high flexibility and low NRE costs of FPGA design with ASICs features such as low power and high speed. The methodology consists of first designing and verifying the project using FPGAs. Once all the design requirements are

achieved, the project is migrated to structured ASIC device which becomes the final version of the chip to be used by the target application. After that, its functionality cannot be altered. Although the configuration of structured ASICs is immune to SEUs, registers and memories must employ fault tolerance techniques to cope with bit-flips. Considering the stringent requirements of space applications, structured ASICs have become an attractive alternative to the traditional ASICs adopted in crucial spacecraft subsystems.

ASICs provide both higher performance and lower power consumption. A major drawback of ASICs is their high NRE costs. Furthermore, once the chip is manufactured, its functionality cannot be modified. Any further modification or addition of features imply in a costly chip re-spin, followed by testing and validation. The whole process may take weeks to finish which can potentially impact the mission schedule. Since ASICs do not utilize reconfigured elements such as SRAM-based FPGAs, the former provides a higher immunity against SEUs than the latter in terms of circuit functionality. However, ASICs memories and registers are still vulnerable to bit-blips caused by SEUs. ASICs have traditionally been used for crucial spacecraft subsystems requiring high levels of reliability such as TT&C and attitude control.

In order to increase reliability, space systems computational platform employ hardware devices that utilizes technological techniques such as radiation hardening. Examples of radiation hardened FPGAs commonly found in space are the flash-based Actel RT ProASIC3 [33] and its anti-fuse counterparts RTAX [34] and RTSX [35]. Besides, Xilinx provides SRAM-based radiation-hardened FPGAs such as the Virtex-4QV [83] and the recently released Virtex-5QV [82].

It is important to notice that, although the Jet Propulsion Laboratory (JPL) Electronic Parts Engineering Office [139] has performed radiation testing and qualification of some devices produced by some manufacturers, it does not mean that devices produced by other manufacturers cannot operate in space. For instance, Altera CycloneII [38] FPGAs utilized in this research have not been broadly utilized in space applications. However, according to Altera [42], they meet the requirements of military and aerospace customers. This FPGA relies upon an automated mechanism to perform CRC checks over its own configuration and demand the chip re-configuration if some error is found.

In summary, depending on the device used its functionality may or may not be immune to SEUs. In spite of that, whatever the device used, fault tolerant techniques must always be present to ensure protection of registers and memory elements against SEUs. Thus, if fault tolerant design is to be met in space applications, SEUs must be properly addressed by mitigation techniques.

#### 2.1.4 Mitigation Techniques

Fault tolerance is an attribute of a system capable of performing its functions correctly in the presence of faults within its constituting components [87]. In order to achieve fault tolerance, fault mitigation techniques must be considered. They can be classified into Technological techniques, Architectural techniques, and Recovery techniques.