## Automatic Datapath Abstraction of Pipelined Circuits

by

Vlad Ciubotariu

A thesis presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of Doctor of Philosophy in Computer Science

Waterloo, Ontario, Canada, 2011

©Vlad Ciubotariu 2011

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners. I understand that my thesis may be made electronically available to the public.

### Abstract

Pipelined circuits operate as an assembly line that starts processing new instructions while older ones continue execution. Control properties specify the correct behaviour of the pipeline with respect to how it handles the concurrency between instructions. Control properties stand out as one of the most challenging aspects of pipelined circuit verification. Their verification depends on the datapath and memories, which in practice account for the largest part of the state space of the circuit. To alleviate the state explosion problem, abstraction of memories and datapath becomes mandatory. This thesis provides a methodology for an efficient abstraction of the datapath under all possible control-visible behaviours. For verification of control properties, the abstracted datapath is then substituted in place of the original one and the control circuitry is left unchanged. With respect to control properties, the abstraction is shown conservative by both language containment and simulation.

For verification of control properties, the pipeline datapath is represented by a network of registers, unrestricted combinational datapath blocks and muxes. The values flowing through the datapath are called parcels. The control is the state machine that steers the parcels through the network. As parcels travel through the pipeline, they undergo transformations through the datapath blocks. The control-visible results of these transformations fan-out into control variables which in turn influence the next stage the parcels are transferred to by the control. The semantics of the datapath is formalized as a labelled transition system called a parcel automaton. Parcel automata capture the set of all control visible paths through the pipeline and are derived without the need of reachability analysis of the original pipeline. Datapath abstraction is defined using familiar concepts such as language containment or simulation. We have proved results that show that datapath abstraction leads to pipeline abstraction.

Our approach has been incorporated into a practical algorithm that yields directly the abstract parcel automaton, bypassing the construction of the concrete parcel automaton. The algorithm uses a SAT solver to generate incrementally all possible control visible behaviours of the pipeline datapath. Our largest case study is a 32-bit two-wide superscalar OpenRISC microprocessor written in VHDL, where it reduced the size of the implementation from 35k gates to 2k gates in less than 10 minutes while using less than 52MB of memory.

## Acknowledgments

I am very grateful to my supervisor Mark Aaagaard without whose support and encouragements this thesis would not have reached completion. Also, I am grateful for all the good friends I have been blessed with, and I would like to thank my friend Marjan for her comforting help during the hardest moments.

# **Table of Contents**

| Li | st of I | figures         |                                      | viii |

|----|---------|-----------------|--------------------------------------|------|

| Li | st of T | <b>[ables</b> ] |                                      | xii  |

| 1  | Intr    | oductio         | n                                    | 1    |

|    | 1.1     | Overvi          | ew Of Background And Related Work    | 4    |

|    | 1.2     | Approa          | ach And Contributions                | 5    |

|    | 1.3     | Outline         | e Of Thesis                          | 6    |

| 2  | Bacl    | kground         | l And Related Work                   | 7    |

|    | 2.1     | Labele          | d Transition Systems                 | 7    |

|    | 2.2     | Model           | Checking                             | 11   |

|    | 2.3     | Circuit         | S                                    | 13   |

|    | 2.4     | Related         | d Work                               | 27   |

|    |         | 2.4.1           | Microprocessor Verification          | 27   |

|    |         | 2.4.2           | Hazard-Based Verification Techniques | 29   |

|    |         | 2.4.3           | Datapath Abstraction                 | 30   |

| 3  | Pipe    | line Mo         | odels                                | 33   |

|    | 3.1     | Pipelin         | e Models                             | 33   |

|    | 3.2     | Abstra          | ction For Control Properties         | 46   |

|    |         | 3.2.1           | Simulation                           | 47   |

|   |                                                                             | 3.2.2 Language Containment                              | 50                                                          |

|---|-----------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|

|   | 3.3                                                                         | Abstract Interpretation Of Pipeline Datapath            | 52                                                          |

|   | 3.4                                                                         | Summary                                                 | 55                                                          |

| 4 | Paro                                                                        | cel Automata                                            | 56                                                          |

|   | 4.1                                                                         | Overview Of Abstraction Using Parcel Automata           | 57                                                          |

|   | 4.2                                                                         | Fan-Out Graphs                                          | 66                                                          |

|   | 4.3                                                                         | Parcel Steps In <i>DiffAddMult</i>                      | 69                                                          |

|   | 4.4                                                                         | Parcel Steps                                            | 80                                                          |

|   | 4.5                                                                         | Parcel Automata                                         | 84                                                          |

|   | 4.6                                                                         | Abstractions Of Parcel Automata                         | 88                                                          |

|   | 4.7                                                                         | Abstract Interpretation Using Parcel Automata           | 97                                                          |

|   | 4.8                                                                         | Summary                                                 | 99                                                          |

| - |                                                                             |                                                         |                                                             |

| 5 | Data                                                                        | apath Abstraction Framework                             | 100                                                         |

| 5 | <b>Data</b><br>5.1                                                          | apath Abstraction Framework         Parcel Independence |                                                             |

| 5 |                                                                             | -                                                       | 100                                                         |

| 5 | 5.1                                                                         | Parcel Independence                                     | 100                                                         |

| 5 | 5.1<br>5.2                                                                  | Parcel Independence                                     | 100<br>103<br>106                                           |

| 5 | 5.1<br>5.2                                                                  | Parcel Independence                                     | 100<br>103<br>106<br>106                                    |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108                             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108<br>114                      |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108                             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul>                               | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108<br>114<br>114               |

| 6 | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108<br>114<br>114<br>114        |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> </ul> | Parcel Independence                                     | 100<br>103<br>106<br>106<br>108<br>114<br>114<br>119<br>132 |

| Bi | bliogr | raphy    |                                              | 192 |

|----|--------|----------|----------------------------------------------|-----|

| 7  | Con    | clusions | 3                                            | 188 |

|    | 6.7    | Summ     | ary                                          | 187 |

|    |        | 6.6.3    | Abstraction Of The OpenRisc Processor        | 183 |

|    |        | 6.6.2    | Implementation                               | 180 |

|    |        | 6.6.1    | Design For Verification Using <i>PipeNet</i> | 178 |

|    | 6.6    | Case S   | tudies                                       | 178 |

|    | 6.5    | Abstra   | ction Algorithms                             | 160 |

|    | 6.4    | Path F   | ormulas                                      | 159 |

|    | 6.3    | Parcel   | Steps In Propositional Logic                 | 154 |

# **List of Figures**

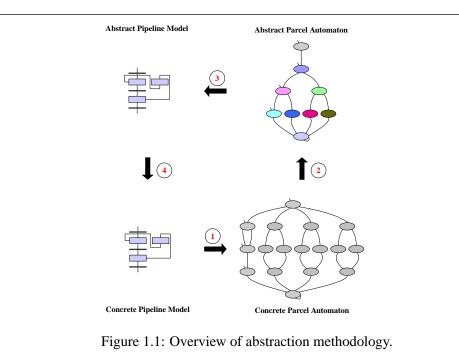

| 1.1  | Overview of abstraction methodology.                      | 4  |

|------|-----------------------------------------------------------|----|

| 2.1  | Commuting diagram for the simulation relation $S$         | 8  |

| 2.2  | Example showing language containment without simulation   | 10 |

| 2.3  | Structure of $\mathbf{CTL}^*$ formulas                    | 11 |

| 2.4  | Adder circuit.                                            | 21 |

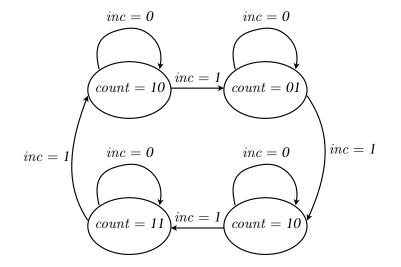

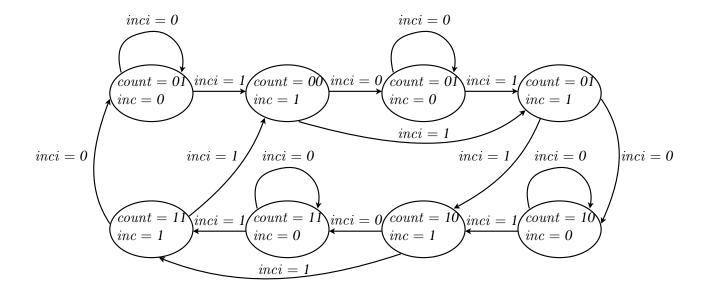

| 2.5  | Counter With Combinational Increment                      | 25 |

| 2.6  | Counter With Registered Increment                         | 26 |

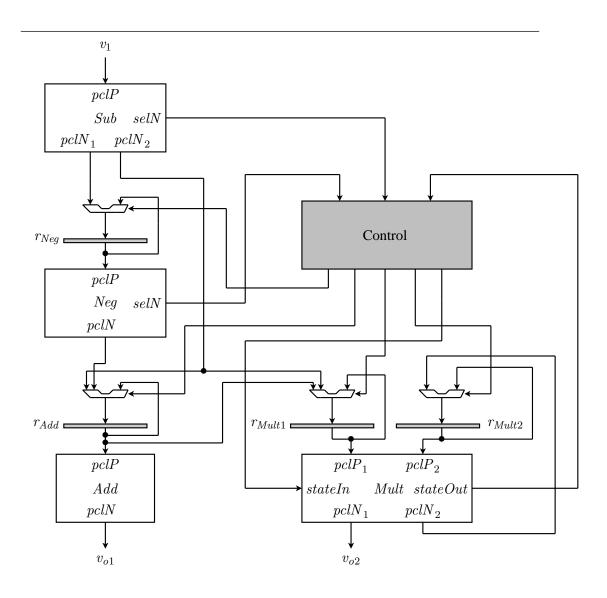

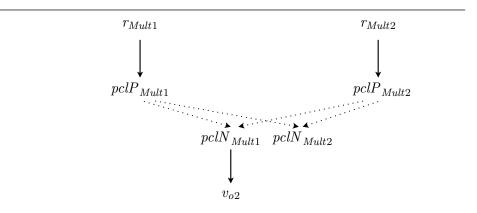

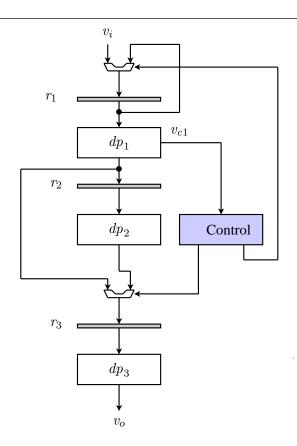

| 3.1  | Block Diagram of <i>DiffAddMult</i>                       | 34 |

| 3.2  | <i>DiffAddMult</i> data types                             | 35 |

| 3.3  | Sub Instance                                              | 35 |

| 3.4  | Datapath Module                                           | 36 |

| 3.5  | Neg Datapath Module                                       | 37 |

| 3.6  | Add Datapath Module                                       | 37 |

| 3.7  | Mult Datapath Module                                      | 38 |

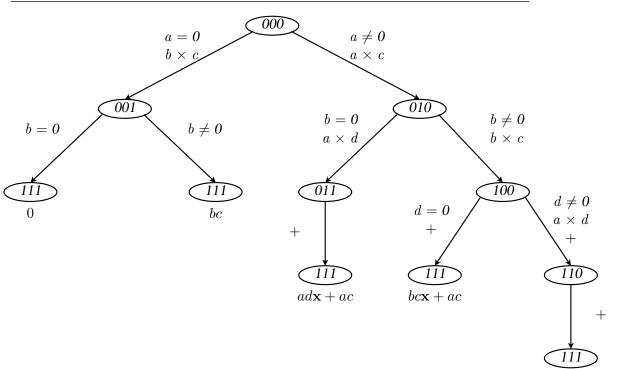

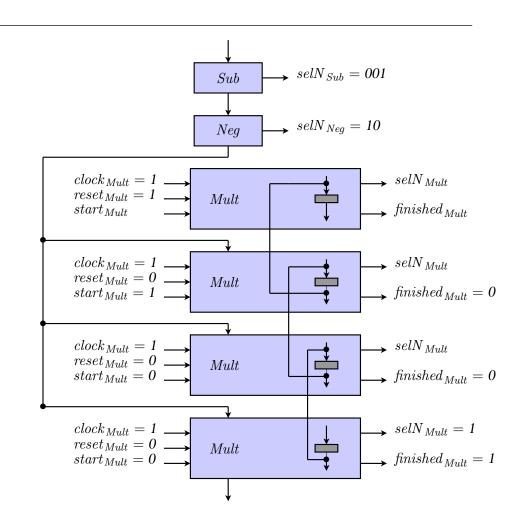

| 3.8  | Sequential Multiplication                                 | 39 |

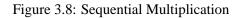

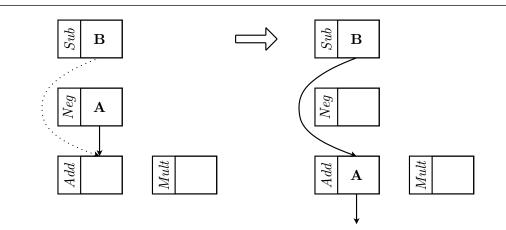

| 3.9  | B waits until A finishes processing.                      | 41 |

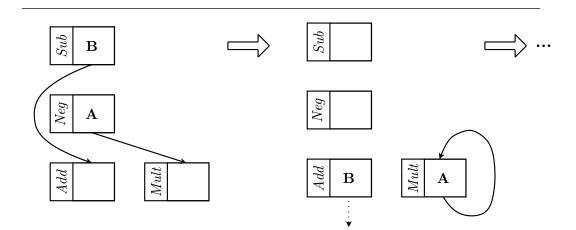

| 3.10 | B stalls because A has higher priority.                   | 42 |

| 3.11 | Mux tree corresponding to the expression in Equation 3.1. | 44 |

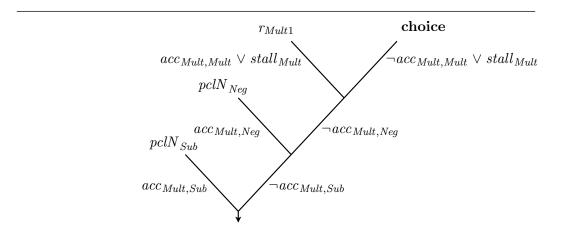

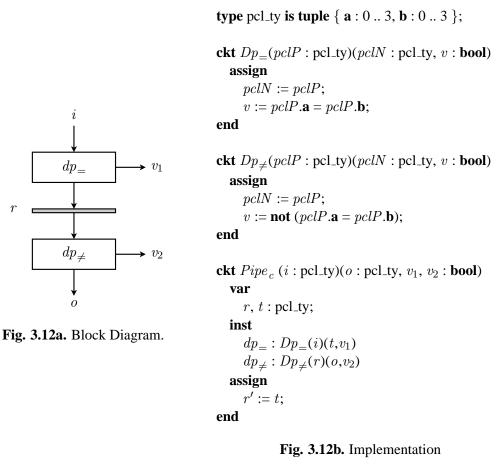

| 3.12 | Concrete Pipeline Model.                                  | 48 |

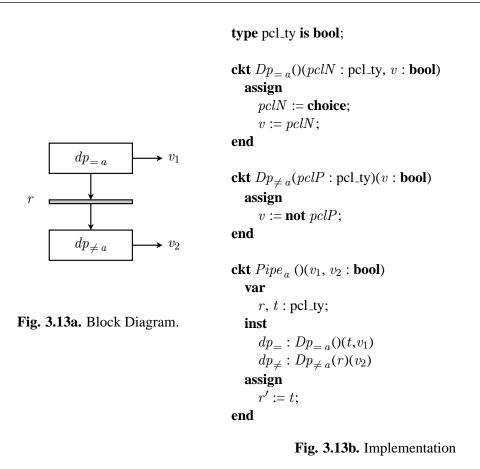

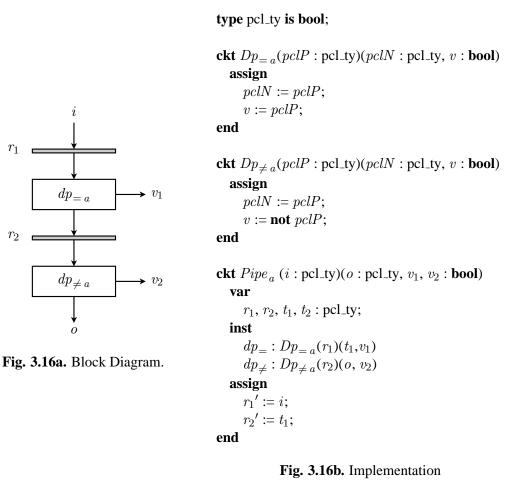

| 3.13                                                                                                                                                                | Abstract Pipeline Model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

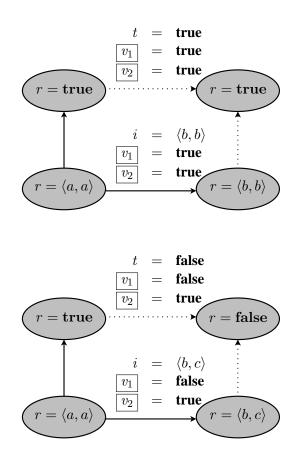

| 3.14                                                                                                                                                                | Commuting diagrams for the case $q_{Pc}(r) = \langle a, a \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                                                                                                                     |

| 3.15                                                                                                                                                                | Commuting diagrams for the case $q_{Pc}(r) = \langle a, b \rangle$ with $a \neq b$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                                                                                     |

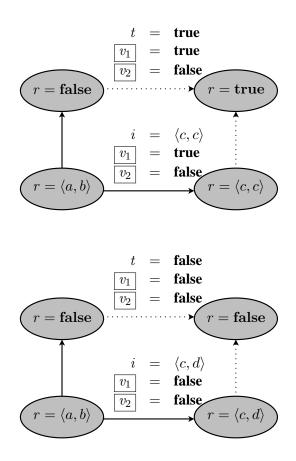

| 3.16                                                                                                                                                                | Abstract Pipeline Model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52                                                                                                                                     |

| 3.17                                                                                                                                                                | Proof Of Language Containment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53                                                                                                                                     |

| 4.1                                                                                                                                                                 | AndOr Block Diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57                                                                                                                                     |

| 4.2                                                                                                                                                                 | AndOr Implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58                                                                                                                                     |

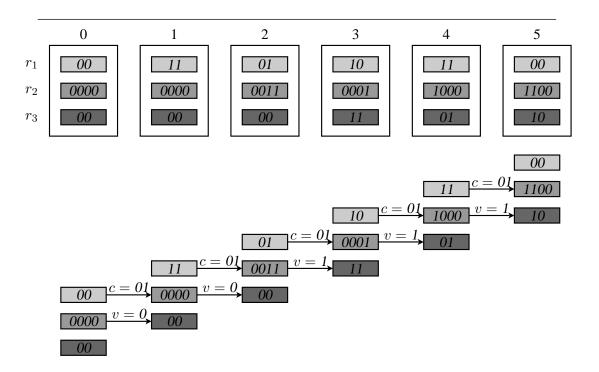

| 4.3                                                                                                                                                                 | AndOr Computation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                                                                                     |

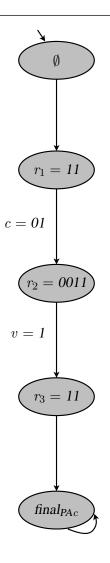

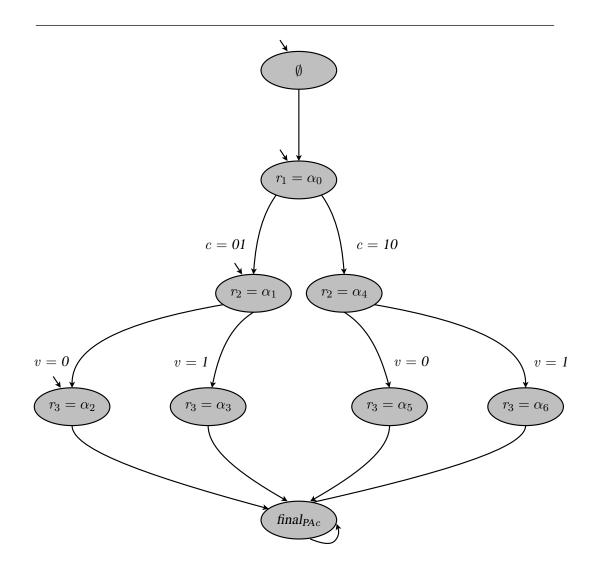

| 4.4                                                                                                                                                                 | AndOr Parcel Automaton.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60                                                                                                                                     |

| 4.5                                                                                                                                                                 | AndOr parcel automaton after one reduction step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                                                                                     |

| 4.6                                                                                                                                                                 | AndOr Abstract Parcel Automaton.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                                                                                     |

| 4.7                                                                                                                                                                 | AndOr Abstract Implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                                                                                                     |

| 10                                                                                                                                                                  | Abstract AndOr Computation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                                     |

| 4.8                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                        |

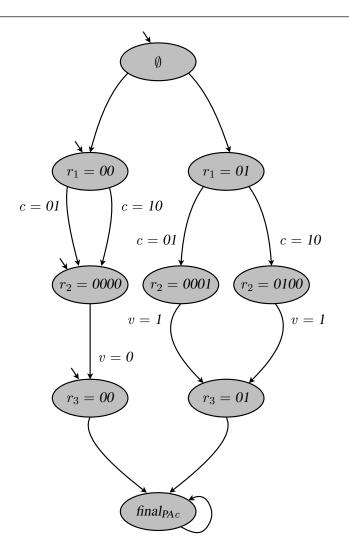

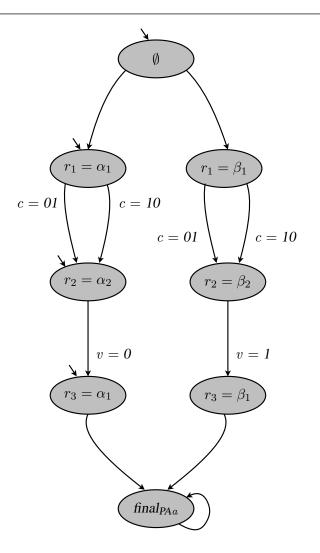

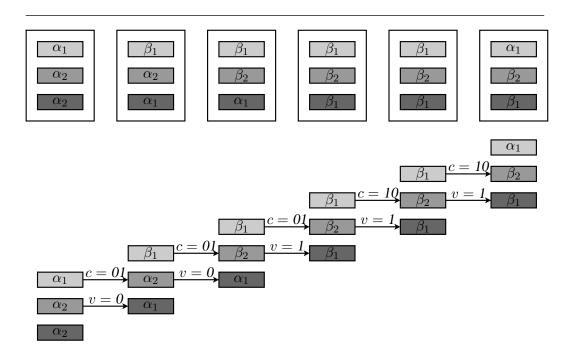

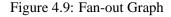

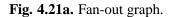

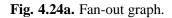

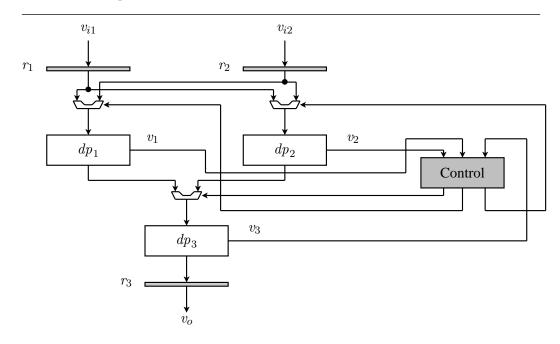

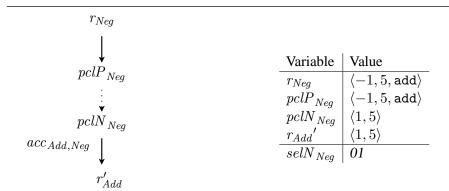

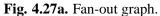

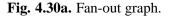

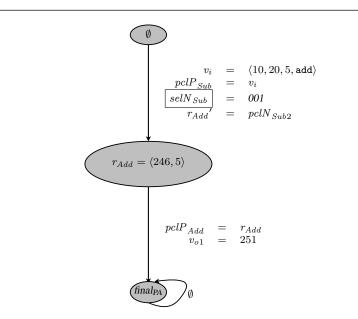

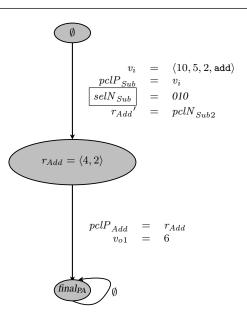

| 4.8<br>4.9                                                                                                                                                          | Fan-out Graph   Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                                     |

| 4.9                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                                                                                                                                     |

| 4.9<br>4.10                                                                                                                                                         | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                                                                                                                                     |

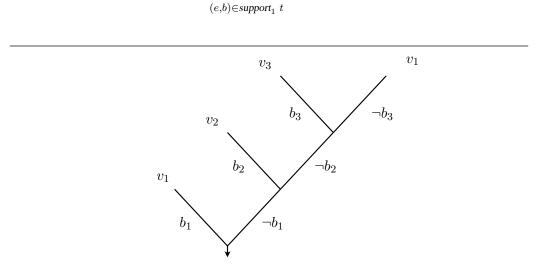

| <ul><li>4.9</li><li>4.10</li><li>4.11</li></ul>                                                                                                                     | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68                                                                                                              |

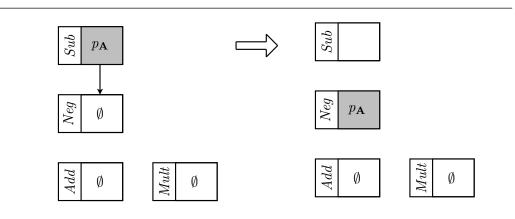

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> </ol>                                                                                                   | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68<br>69                                                                                                        |

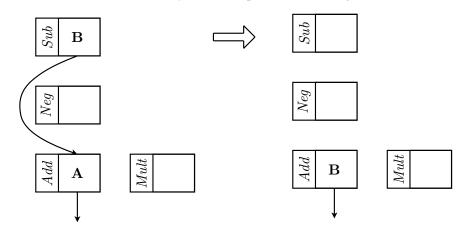

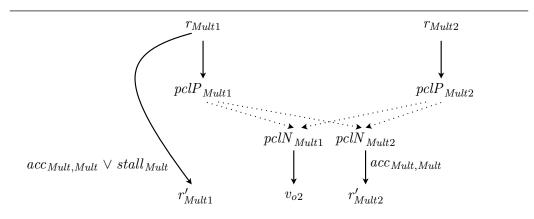

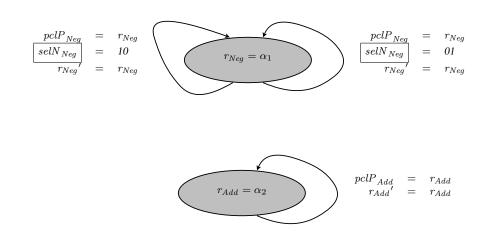

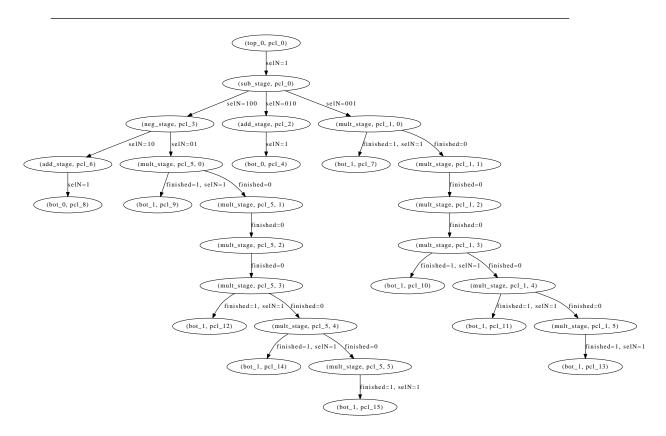

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> </ol>                                                                                     | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68<br>69<br>70                                                                                                  |

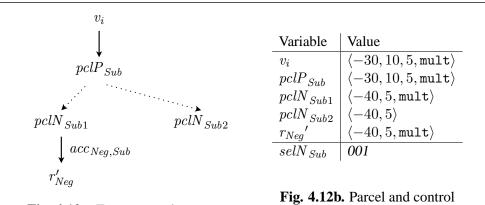

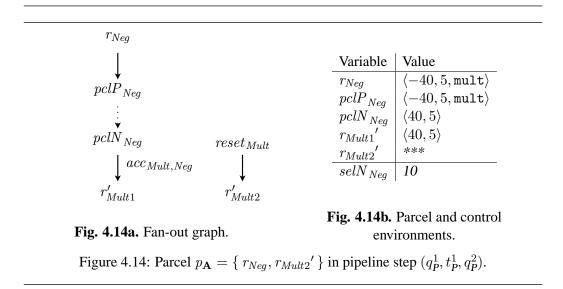

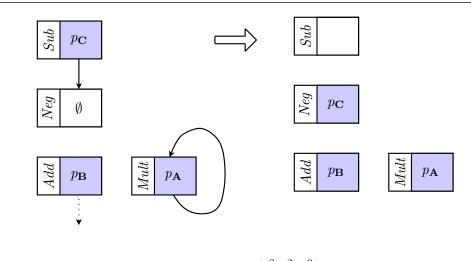

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> </ol>                                                                       | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68<br>69<br>70<br>71                                                                                            |

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> <li>4.15</li> </ol>                                                         | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68<br>69<br>70<br>71<br>71                                                                                      |

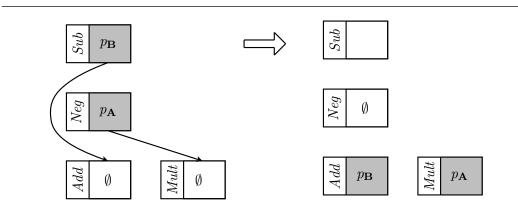

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> <li>4.15</li> <li>4.16</li> </ol>                                           | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v <sub>1</sub> . 68<br>69<br>70<br>71<br>71<br>71<br>72                                                                          |

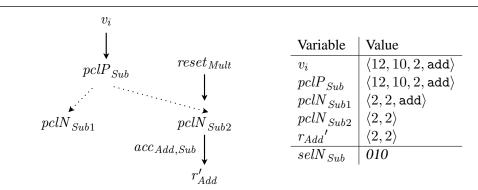

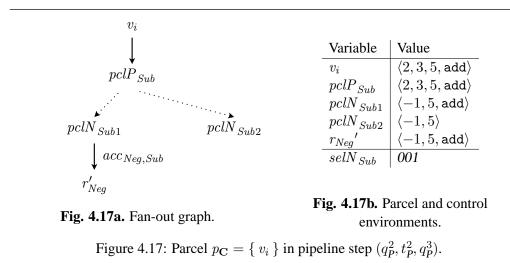

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> <li>4.15</li> <li>4.16</li> <li>4.17</li> </ol>                             | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66<br>v1. 68<br>69<br>70<br>71<br>71<br>72<br>72                                                                                       |

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> <li>4.15</li> <li>4.16</li> <li>4.17</li> <li>4.18</li> </ol>               | Fan-out Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <ul> <li>66</li> <li>v1. 68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> </ul>             |

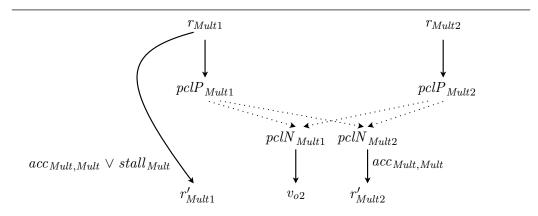

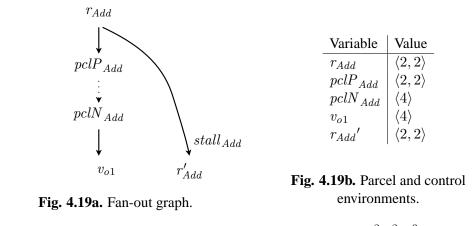

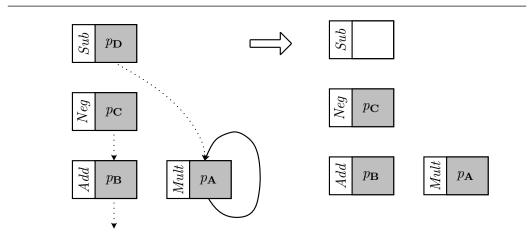

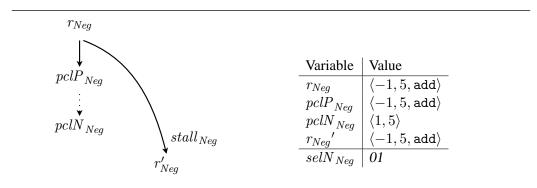

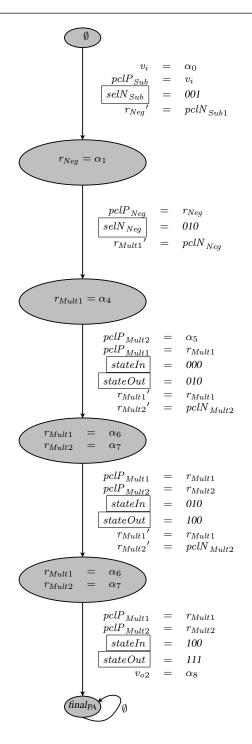

| <ol> <li>4.9</li> <li>4.10</li> <li>4.11</li> <li>4.12</li> <li>4.13</li> <li>4.14</li> <li>4.15</li> <li>4.16</li> <li>4.17</li> <li>4.18</li> <li>4.19</li> </ol> | Fan-out GraphMux tree for the expression if $b_1$ then $v_1$ else if $b_2$ then $v_2$ else if $b_3$ then $v_3$ elsePipeline step $(q_P^0, t_P^0, q_P^1) \in R_P$ .Parcel $p_{\mathbf{A}} = \{ v_i \}$ in pipeline step $(q_P^0, t_P^0, q_P^1)$ .Pipeline step $(q_P^1, t_P^1, q_P^2) \in R_P$ .Pipeline step $(q_P^1, t_P^1, q_P^2) \in R_P$ .Parcel $p_{\mathbf{A}} = \{ r_{Neg}, r_{Mult2}' \}$ in pipeline step $(q_P^1, t_P^1, q_P^2)$ .Parcel $p_{\mathbf{B}} = \{ v_i \}$ in pipeline step $(q_P^1, t_P^1, q_P^2)$ .Parcel $p_{\mathbf{B}} = \{ v_i \}$ in pipeline step $(q_P^2, t_P^2, q_P^3)$ .Parcel $p_{\mathbf{C}} = \{ v_i \}$ in pipeline step $(q_P^2, t_P^2, q_P^3)$ .Parcel $p_{\mathbf{A}} = \{ r_{Mult1}, r_{Mult2} \}$ in pipeline step $(q_P^2, t_P^2, q_P^3)$ . | <ol> <li>66</li> <li>w1. 68</li> <li>69</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>72</li> <li>73</li> <li>74</li> </ol> |

| 4.22 | Parcel $p_{\mathbf{A}} = \{ r_{Mult1}, r_{Mult2} \}$ in pipeline step $(q_P^3, t_P^3, q_P^4)$ |

|------|-----------------------------------------------------------------------------------------------|

| 4.23 | Pipeline step $(q_P^4, t_P^4, q_P^5) \in R_P$                                                 |

| 4.24 | Parcel $p_{\mathbf{C}} = \{ r_{Neg} \}$ in pipeline step $(q_P^4, t_P^4, q_P^5)$              |

| 4.25 | Parcel $p_{\mathbf{A}} = \{ r_{Mult1}, r_{Mult2} \}$ in pipeline step $(q_P^4, t_P^4, q_P^5)$ |

| 4.26 | Parcel $p = \{ r_1, r_2 \}$ can have up to 8 distinct fan-out graphs                          |

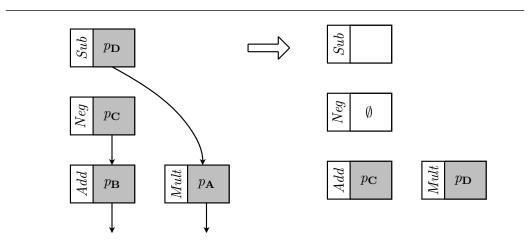

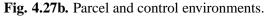

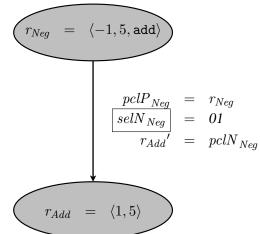

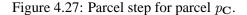

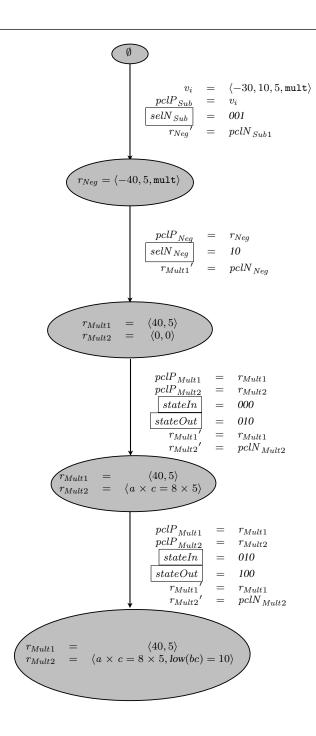

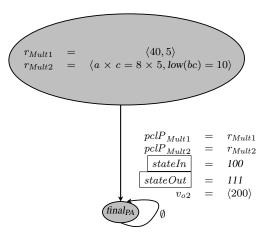

| 4.27 | Parcel step for parcel $p_{\mathbf{C}}$                                                       |

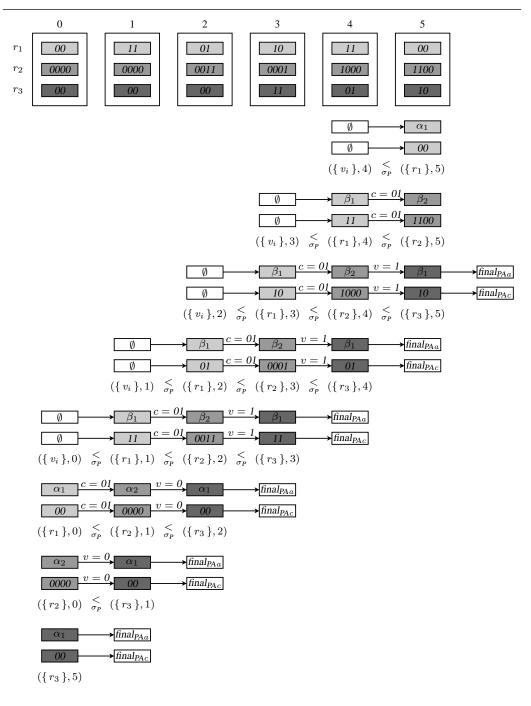

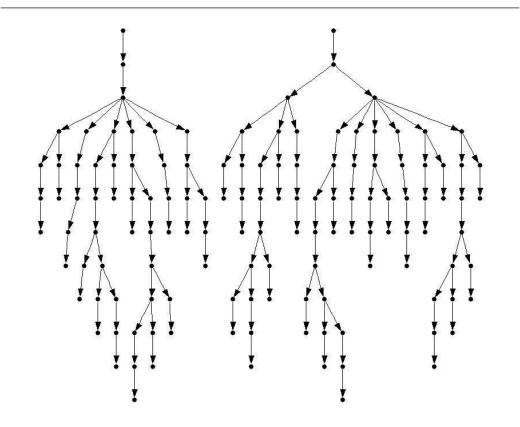

| 4.28 | Parcel automaton for parcel $p_{\mathbf{A}}$                                                  |

| 4.29 | Parcel automaton for parcel $p_{\mathbf{A}}$ (continuation)                                   |

| 4.30 | Parcel $p_{\mathbf{C}} = \{ r_{Neg} \}$ in pipeline step $(q_P^3, t_P^3, q_P^4)$              |

| 4.31 | Parcel automaton illustrating an unreachable parcel computation                               |

| 4.32 | Parcel automaton showing inconsistent datapath behaviour                                      |

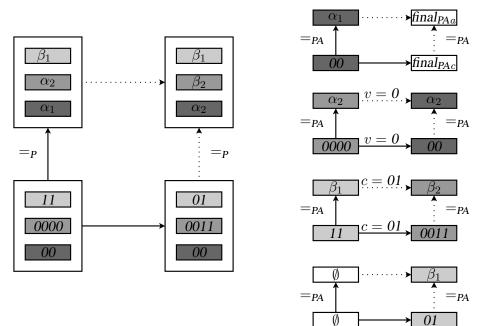

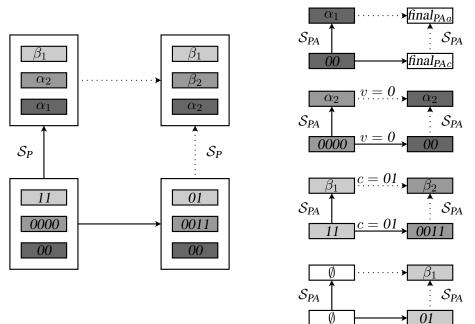

| 4.33 | Abstract parcel automaton                                                                     |

| 4.34 | Abstract parcel automaton (continuation)                                                      |

| 4.35 | Abstract equivalent run corresponding to $p_{\mathbf{A}}$                                     |

| 4.36 | Circuit equivalent to $R_{Sub}$                                                               |

| 5.1  | Parcel map for <i>DiffAddMult</i>                                                             |

| 5.2  | AndOr example                                                                                 |

| 5.3  | AndOr example (simulation)                                                                    |

| 5.4  | AndOr Computation                                                                             |

| 5.5  | Associated parcel automaton run                                                               |

| 5.6  | Construction in Theorem 5.4.8                                                                 |

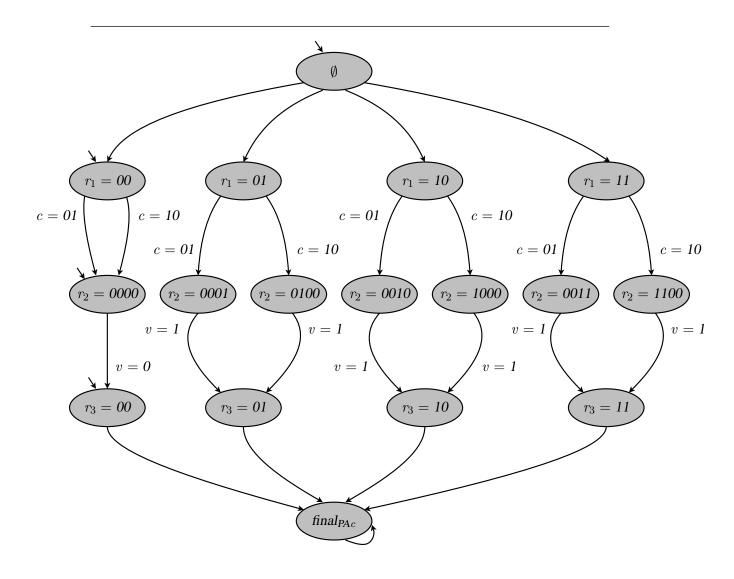

| 6.1  | AndOr Parcel Automaton                                                                        |

| 6.2  | An abstract AndOr parcel automaton                                                            |

| 6.3  | Pipeline models with unreachable datapath computations                                        |

| 6.4  | Pipeline model with stall and exclusive paths                                                 |

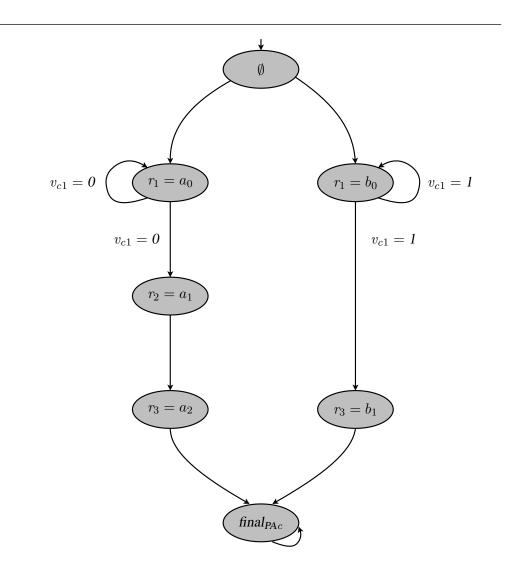

| 6.5  | Partial representation of $pa_{c1}$ using symbolic values                                     |

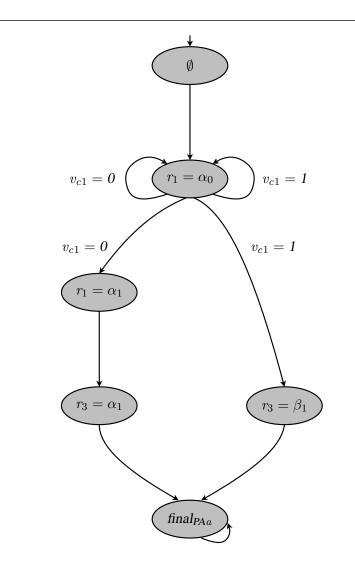

| 6.6  | Partial representation of $pa_a$ constructed by Algorithm 6.3 | 173 |

|------|---------------------------------------------------------------|-----|

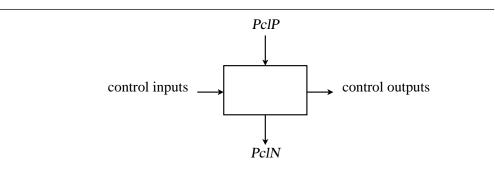

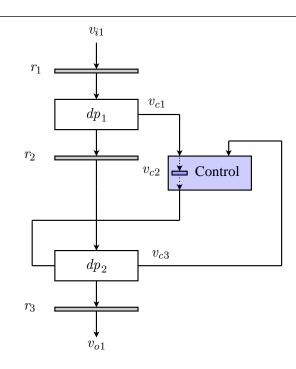

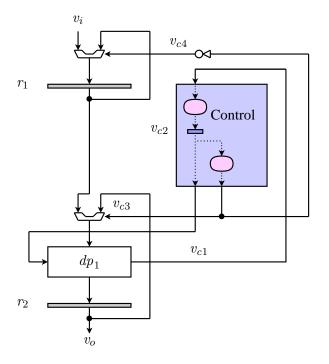

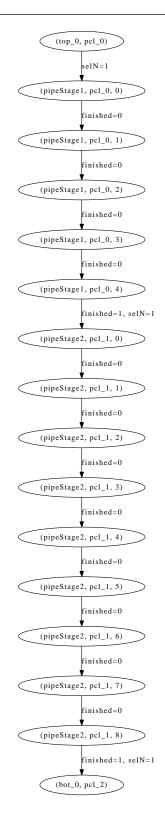

| 6.7  | Pipeline stage template.                                      | 178 |

| 6.8  | Combinational stage.                                          | 180 |

| 6.9  | Sequential Stage                                              | 181 |

| 6.10 | Example of path formula for <i>DiffAddMult</i>                | 182 |

| 6.11 | <i>DiffAddMult</i> abstract parcel automaton                  | 183 |

| 6.12 | Abstract parcel automaton of edge-detector                    | 184 |

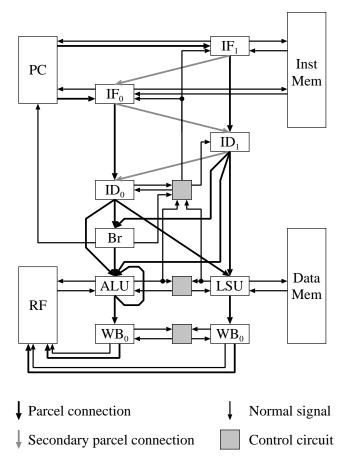

| 6.13 | OpenRisc pipeline                                             | 185 |

| 6.14 | OpenRisc abstract parcel automaton                            | 186 |

# **List of Tables**

| 3.1 | Request variables       |

|-----|-------------------------|

| 3.2 | Accept variables        |

| 6.1 | The path map $\psi$     |

| 6.2 | ORBIS32 Instruction Set |

## **Chapter 1**

# Introduction

Hardware and software systems have a pervasive presence in our day to day lives. From mass produced computer chips and embedded software in our computing devices and cars to systems that control high speed trains, aeroplanes and nuclear plants, our well being and safety is increasingly dependent on whether such systems behave as intended. The consequences of malfunctioning hardware and software range from the nuisance of continuous operating system updates and firmware for our computers and gadgets to mass recalls with high economic cost in the order of millions and billions of dollars and catastrophic accidents that put human life at risk.

The traditional approach to validate hardware and software systems is testing. The testing paradigm uses input vectors to check the input-output behaviour of the system or to drive the system through execution scenarios which are checked against the expected behaviour. Black box testing or functional testing checks the input-output behaviour of the system and is oblivious to its internal structure. White box testing uses the structural information about the system, such as the control flow graph of the program code, to craft input vectors that drive it through execution paths that visit the structural elements such as lines of code or control-flow conditions. The success of testing is measured using coverage metrics.

For medium to large systems the sheer multitude of possible input values makes an exhaustive approach intractable. Thus complete validation through testing is not achievable except for small scale systems. Even when complete coverage is achieved it is not a certainty that all system behaviours have been exercised, since coverage metrics are defined in terms of the structure of the system while there can be exponentially more behaviours. Achieving reasonable coverage through testing in modern day microprocessors takes enormous amounts of time. For instance, simulating a few minutes of a 1GHZ microprocessor takes almost 6 months of simulation time on a large cluster of workstations [Bentley, 2001].

Formal methods [Clarke and Wing, 1996, Clarke and Kurshan, 1996, Dill and Rushby, 1996, Hall,

1990] stand for the collection of methods that apply mathematical reasoning to the proof of correctness of hardware and software systems. The application of formal methods to a system is called formal verification. Formal verification checks a given property holds of all behaviours of the system and is therefore exhaustive, providing a definitive answer to correctness. Formal verification has been applied successful to a wide range of hardware and software systems [Bentley, 2001, Clarke et al., 1995, McMillan, 2001, Dill et al., 1992]. In the real world, formal verification and testing coexist and techniques from formal verification have been used achieve better testing, creating hybrid methodologies.

Due to the theoretical complexity of program verification, ranging from NP-hard to undecidable, with formal verification comes the tradeoff between automation and capacity. In the wide spectrum of formal methods we distinguish two categories of techniques. At one end we have deductive methods that provide virtually unbounded capacity, being able to verify infinite systems, but are also more likely to rely on the intervention of a knowledgeable user to guide the proof. At the other end we have algorithmic methods that are highly automated but are not directly applicable to large systems. The gap between the two types of formal methods is bridged using abstraction and decomposition techniques.

In this thesis we are concerned with using abstraction to improve the capacity of one such automated technique, called model checking, for the verification of pipelined circuits. In model checking, the verified system is called a reactive system and the language in which the properties are described is called temporal logic. To verify properties, model checking performs an exhaustive search of the state space of the reactive system. The size of the state space is the major challenge that impedes the direct use of model checking. The capacity problem incurred due to the state space factor is called the state explosion problem. The state space explosion problem is mitigated using abstraction and decomposition. Our research is concerned with abstraction in the application domain of pipelined circuits.

Pipelining uses the same principle as an assembly line that shifts products simultaneously from one assembly stage to the next. A pipelined circuit divides the execution of instructions, also called parcels, into stages. Upon entering the pipeline, the execution of an instruction happens incrementally as it moves from one stage to the next, until it exits the pipeline. To achieve a similar productivity increase to the assembly line, the pipeline overlaps the execution of instructions whereby each execution stage holds a different instruction. Compared to a non-pipelined circuit that performs the same operation, in an ideal linear pipeline that does not have instruction dependencies, the execution time of individual instructions does not change. However the number of instructions processed per unit of time increases proportionally to the length of the pipeline. The theoretical speedup of a pipeline is not achieved in practice due to dependencies between instructions [Hartstein and Puzak, 2002].

A pipelined circuit consists of a network of stages through which the parcels flow, memories and register files that store instructions and the data operated on, datapath elements that perform the operation corresponding to each pipeline stage and control circuitry that orchestrates the execution of the instructions. The network of stages is linear but only in the simplest circuits. It may contain branches and loops and the paths taken by instructions may be selected dynamically by the control based on the current execution context. The concurrent execution of instructions leads to possible race conditions which in pipeline circuits are called hazards.

There are three types of hazards. Data hazards arise due to data dependencies when the operand of one instruction, the consumer, is created by another, the producer. In such cases, the consumer waits — it stalls — until the operand is ready. Structural hazards arise from resource contention when multiple instructions need to transfer to the same next stage. Finally, control hazards happen due to speculative execution. Instructions that were fetched after a control instruction that is mispredicted, must be removed from the pipeline.

Because of the synchronization problems it solves, the control circuitry is the main source of complexity in the pipeline circuit and therefore, the most likely part of the design to contain design errors. The size of the controller is often within the verification capacity of model checking techniques. What prevents its direct verification is the size of the memories and datapaths which contribute the largest proportion to the state space of the circuit. Memories are easier to abstract, their size reduces to what is needed to accommodate the read and write locations of the maximum number of in-flight instructions. Datapaths are more challenging to abstract because they use the parcel's value to generate feedback signals to the control circuitry and thus affect the overall execution in the pipeline.

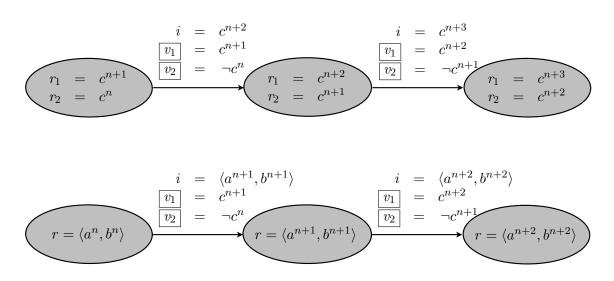

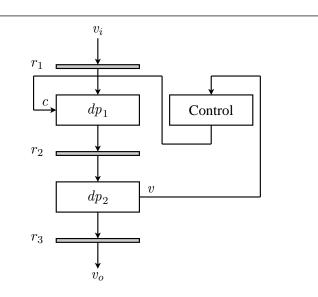

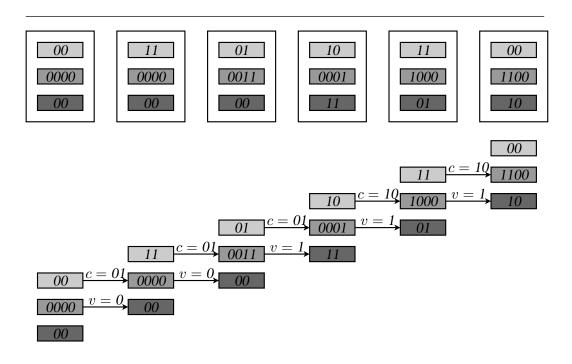

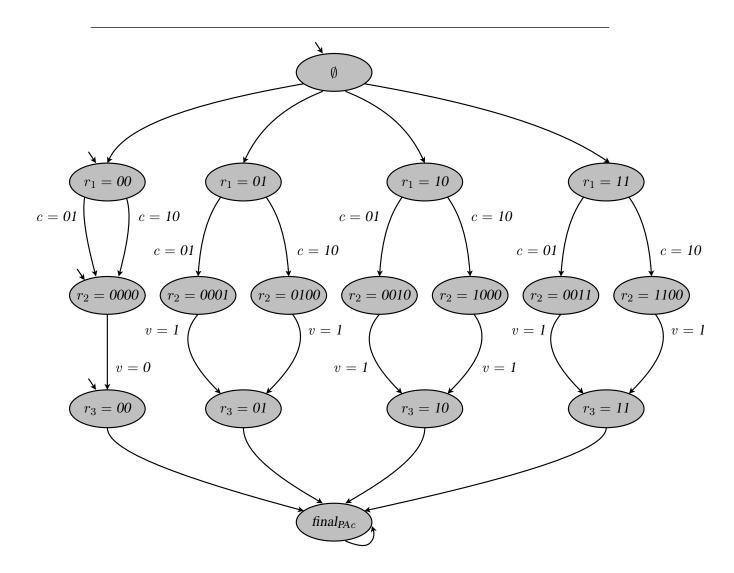

In this thesis we present a novel datapath abstraction technique. The methodology is described pictorially in Figure 1.1. At the core of our approach is the use of a mathematical representation, called parcel automata, to describe the control-visible behaviour of the parcels as they travel through the pipeline. A parcel's behaviour is defined by both the control signals it generates at each stage in the pipeline and the path it takes through the pipeline. In our methodology datapath abstraction is performed by abstracting the concrete parcel automata and then using the abstract parcel automata to define abstract datapaths that are then substituted in place of the concrete ones. The process of replacing the concrete datapath by an abstract one is a form of abstract interpretation. We show that the conventional forms to define abstraction of automata, such as simulation and language containment, carry over to abstract interpretation of the pipeline datapath using parcel automata.

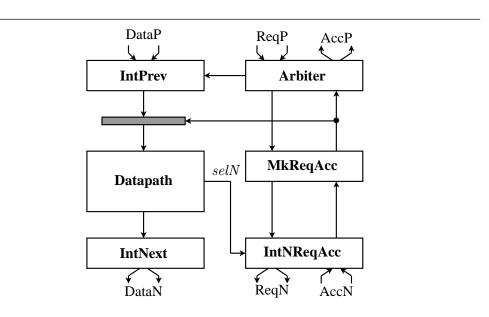

Our contribution is threefold. First, we contribute a formal framework for datapath abstraction using parcel automata. Within this framework we define pipeline models and parcel automata, abstraction of parcel automata and prove correctness of pipeline abstraction using abstract parcel automata. Second, we provide an abstraction algorithm for parcel automata. Our algorithm tackles the state

explosion problem by the symbolic traversal of the concrete parcel automaton using a satisfiability solver. And third, our approach is implemented in a prototype. The tool allows its users to create pipeline models by specifying the top level structure of interconnected pipeline stages. The datapath and control are defined directly in VHDL and then referenced from the high-level model. Datapath abstraction is then performed with the click of a button. As cases studies we used several designs, spanning from simple 32-bit arithmetic pipelines to an edge detector circuit and a 32-bit superscalar OpenRISC microprocessor.

## 1.1 Overview Of Background And Related Work

The most complex pipelined circuits appear in today's microprocessors. Approaches to formal verification of microprocessors include deductive methods using theorem proving and automated techniques using model checking or specialized decision procedures. With any such verification technique one must specify the correctness criteria and then provide a sound verification strategy.

Often, the correctness statement specifies a relationship described using concepts from automata theory. Simulation states that a relationship between the value of specification variables in the implementation states and the specification states is preserved after an execution step of the implementation and specification. Another way to define correctness is through language containment. In this definition, the sets of implementation traces are compared against the set of traces of the

specification. Formulating correctness statements for pipelined circuits is made challenging by the fact that the implementation variables that correspond to the specification reflect changes by partially executed instructions. The pipelined circuit executes multiple instructions in one step while the specification is sequential and executes one instruction at a time.

A correctness framework that overcomes the challenges of aligning the implementation and specification states is called flushing [Burch and Dill, 1994]. In this approach, the implementation state is run, without fetching new instructions into the pipeline, until all the instructions being currently executed complete. Verification techniques using flushing have been performed using both deductive and automatic methods. In deductive approaches, the challenge of applying flushing is identifying proof strategies to deal with the various optimizations of a microprocessor design such as scoreboarding, execution units with variable latency and branch prediction [Sawada and Hunt, 1997, Hosabettu et al., 1998, Skakkebak et al., 1998]. Automatic techniques use efficient decision procedures to prove a simulation relation based on flushing [Lahiri et al., 2002, Velev and Bryant, 2000, Manolios and Srinivasan, 2004].

In a hazard based approach [Aagaard, 2003] the top-level correctness is defined with respect to the three types of pipeline hazards: data, structural and control. Hazard correctness is formulated in terms of pipeline specific properties and thus are more straightforward to define. Most of these properties target the control circuitry. The main impediment in the automatic verification of control properties of pipelined circuits is the large contribution of datapath and memories to their overall size.

Approaches to datapath abstraction vary in the degree of automation and precision and often perform a tradeoff. When a decision procedure is used, datapath abstraction is performed using uninterpreted functions. In model checking, datapath abstraction is done by reducing the bitwidth of the operands. The equivalent of uninterpreted functions in this context is to sever the feedback signals from datapath to control and replace the datapath implementation by wires [Ho et al., 1998]. However, imprecise abstractions pose the threat of false counterexamples: traces of the abstract circuit that violate the property and do not have an equivalent trace in the concrete implementation. The solution is to refine the abstraction in a refinement loop [Andraus et al., 2006] until the property passes or a true counterexample is found.

### **1.2 Approach And Contributions**

Our approach to datapath abstraction targets the verification of control properties. We exploit structural rules in the design of pipelined circuits to derive efficient and accurate abstractions. Our approach is particularly useful for properties that specify the parcel flow through the pipeline and are sensitive to the latency of the paths through the pipeline. Our contribution is an abstraction technique that leverages a novel mathematical representation for the pipeline datapath using a type of automata, called parcel automata. A parcel automaton is a mathematical model for the execution of an instruction. Each state of the automaton represents a parcel in a pipeline state. A transition denotes the transformation of the parcel by the datapath as it moves to the next stage. The label of the transition indicates the control visible effects. A run of the parcel automaton corresponds to a run of a single parcel through the pipeline.

Formalizing the datapath as an automaton presents the advantage of clean mathematical reasoning about datapath abstraction. Simulation and language containment formalize the notion of equivalent parcels, parcels that have the same control visible behaviour as they move through the pipeline. We prove in our framework that both simulation and language containment on parcel automata transfer to pipeline abstraction using parcel automata. Our abstraction algorithm uses a symbolic method based on SAT to simultaneously traverse all equivalent runs of the parcel automaton. The abstraction of the pipeline datapath reduces to collapsing the equivalent runs of the concrete parcel automaton into a run of the abstract parcel automaton. Datapath abstraction is represented as abstraction of parcel automata and pipeline abstraction for control properties is performed as a form of abstract interpretation using abstract datapaths derived from abstract parcel automata.

We have implemented our methodology as part of a verification flow using a prototype tool called Bluenose II. The tool reads the annotated model that describes the structure of the pipeline as a network of interconnected stages. The descriptions of the stages reference the VHDL files that implement the datapaths. Datapath abstraction using a SAT solver is performed by generating CNF formulas from the netlists obtained by synthesis of the datapath files. From the abstract parcel automaton the tool generates VHDL for the abstract datapaths which in turn define the abstract pipeline circuit through abstract interpretation. The abstract circuit is then verified with a model checker.

## **1.3 Outline Of Thesis**

Chapter 2 introduces known concepts that we use throughout the thesis: labeled state machines, circuits and model checking. It also discusses related work. Chapter 3 defines the model of pipelined circuits. In Chapter 4 we present the definition of parcel automata, their abstraction and use in abstract interpretation of pipelined circuits. Chapter 5 describes parcel maps and the correctness of datapath abstraction using parcel automata. Chapter 6 defines path abstraction for parcel automata and presents abstraction algorithms and case studies. Chapter 7 is a summary of the thesis and of our contributions.

## **Chapter 2**

# **Background And Related Work**

In this chapter we describe several concepts that are used throughout the thesis: labeled transition system, model checking and circuits. In Section 2.4 we present related work.

## 2.1 Labeled Transition Systems

**2.1.1 Definition** (Labeled Transition System). A labeled transition system is a tuple  $M = \langle Q, R, T, I \rangle$ :

- Q denotes the set of states

- T is the set of transition labels

- $R \subseteq Q \times T \times Q$  is the transition relation

- $I \subseteq Q$  is the set of initial states

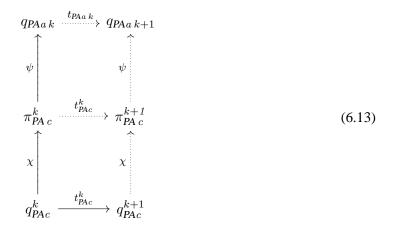

The language  $\mathcal{L}(M)$  of a labeled transition M is the set of infinite runs represented by functions of form  $run : \mathbf{N} \to Q \times T$  such that  $run \ k = (q^k, t^k)$  and  $q^0 \in I \land \forall k. \ (q^k, t^k, q^{k+1}) \in R$ .

Consider two labeled transition systems  $M_1 = \langle Q_1, R_1, T_1, I_1 \rangle$  and  $M_2 = \langle Q_2, R_2, T_2, I_2 \rangle$ . In order to formulate criteria of abstraction, we need to compare states and transition labels of the two transition systems. In general they may belong to disjoint sets and therefore may not be directly comparable. Instead of direct equality, for states we use the labeling functions  $lab_{Q1} : Q_1 \rightarrow L_Q$ and  $lab_{Q2} : Q_2 \rightarrow L_Q$  with the same codomain  $L_Q$ , and, respectively, for transitions use  $lab_{T1} :$  $T_1 \rightarrow L_T$  and  $lab_{T2} : T_2 \rightarrow L_T$ , sharing the codomain  $L_T$ .

Abstraction of labeled transition systems is formulated using simulation [Milner, 1971] or language containment.

Figure 2.1: Commuting diagram for the simulation relation S.

**2.1.2 Definition** (Simulation). A simulation relation between  $M_1$  and  $M_2$  is a relation  $S \subseteq Q_1 \times Q_2$  that satisfies the following conditions:

1. S is compatible with the state labeling.

$$\forall q_1 \in Q_1. \ \forall q_2 \in Q_2. \ (q_1, q_2) \in \mathcal{S} \Longrightarrow lab_{Q_1} q_1 = lab_{Q_2} q_2$$

2. S is total over the initial states of  $M_1$ .

$$\forall q_1 \in I_1. \exists q_2 \in I_2. (q_1, q_2) \in \mathcal{S}$$

3. S is invariant under the transition relations.

$$\forall q_{1} \in Q_{1}. \forall t_{1} \in T_{1}. \forall q'_{1} \in Q_{1}.$$

$$\forall q_{2} \in Q_{2}.$$

$$(q_{1}, q_{2}) \in \mathcal{S} \land (q_{1}, t_{1}, q'_{1}) \in R_{1} \Longrightarrow$$

$$\exists t_{2} \in T_{2}. \exists q'_{2} \in Q_{2}. \ lab_{T1} \ t_{1} = lab_{T2} \ t_{2} \land (q_{2}, t_{2}, q'_{2}) \in R_{2} \land (q'_{1}, q'_{2}) \in \mathcal{S}$$

$$(2.1)$$

Pictorially, Equation 2.1 is described in Figure 2.1. We say that  $M_2$  simulates  $M_1$  if there exists a simulation relation  $S \subseteq Q_1 \times Q_2$ .

The other way to state abstraction is through language containment. Language containment between  $M_1$  and  $M_2$  holds if for every  $run_1 \in \mathcal{L}(M_1)$  there exists an equivalent run  $run_2 \in \mathcal{L}(M_2)$ :

$$\forall run_1 \in \mathcal{L}(M_1). \exists run_2 \in \mathcal{L}(M_2).$$

$$\forall k \in \mathbf{N}. \ lab_{Q1} \ q_1^k = lab_{Q2} \ q_2^k \wedge lab_{T1} \ t_1^k = lab_{T2} \ t_2^k$$

(2.2)

**2.1.3 Proposition.** Simulation implies language containment.

*Proof.* Let S be a simulation relation between  $M_1$  and  $M_2$ . Consider  $run_1 \in \mathcal{L}(M_1)$ . We construct

by induction the sequence  $q_2^0, t_2^0, q_2^1, \ldots, q_2^n$  such that  $(q_1^n, q_2^n) \in \mathcal{S}$  and for all  $k \le n-1$

$$lab_{Q1} q_1^k = lab_{Q2} q_2^k (2.3)$$

$$lab_{T1} t_1^k = lab_{T2} t_2^k (2.4)$$

$$(q_2^k, t_2^k, q_2^{k+1}) \in R_2$$

(2.5)

If  $q_2^0 \in I_2$  and Equation 2.5 holds for  $k \in \mathbb{N}$  then the function  $run_2 : \mathbb{N} \to Q_2 \times T_2$  defined by  $run_2 k = (q_2^k, t_2^k)$  is a run of  $M_2$  equivalent to  $run_1$ .

Base Case n = 0. We choose  $q_2^0$  such that  $(q_1^0, q_2^0) \in S$ .

**Inductive Case** n > 0 By induction we have that  $(q_1^{n-1}, q_2^{n-1}) \in S$ . Therefore, there exist  $t_2^{n-1} \in T_2$  and  $q_2^n \in Q_2$  that make the diagram below commute:

$$\begin{array}{ccc} q_2^{n-1} & \stackrel{t_2^{n-1}}{\longrightarrow} & q_2^n \\ s & & s \\ q_1^{n-1} & \stackrel{t_1^{n-1}}{\longrightarrow} & q_1^n \end{array}$$

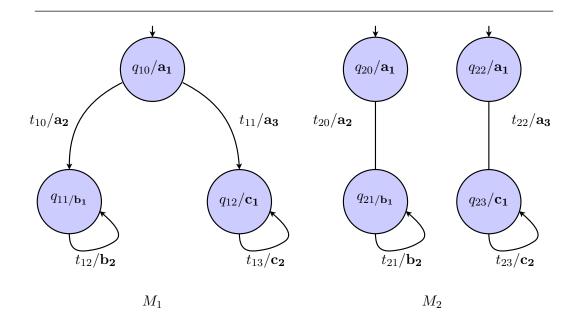

The converse of Proposition 2.1.3 is not necessarily true as shown by the example in Figure 2.2. For each of the two possible runs of  $M_1$  there exists an equivalent run of  $M_2$ . However, there is no state of  $M_2$  that simulates the initial state  $q_{10}$ .

Fig. 2.2a.  $M_1$  and  $M_2$ .

| state    | label                            | transition | label          | state    | label                            | transition | label          |

|----------|----------------------------------|------------|----------------|----------|----------------------------------|------------|----------------|

| $q_{10}$ | $a_1$                            | $t_{10}$   | $a_2$          | $q_{20}$ | $a_1$                            | $t_{20}$   | $a_2$          |

| $q_{11}$ | a <sub>1</sub><br>b <sub>1</sub> | $t_{11}$   | $a_3$          | $q_{21}$ | a <sub>1</sub><br>b <sub>1</sub> | $t_{21}$   | $\mathbf{b_2}$ |

| $q_{12}$ |                                  |            | $\mathbf{b_2}$ | $q_{22}$ | a <sub>1</sub><br>c <sub>1</sub> | $t_{22}$   | $a_3$          |

|          |                                  | $t_{13}$   | $c_2$          | $q_{23}$ | $\mathbf{c_1}$                   | $t_{23}$   | c <sub>2</sub> |

|          |                                  | 1          | 1              |          |                                  |            | I              |

**Fig. 2.2b.** Labeling of  $M_1$ .

Fig. 2.2c. Labeling of  $M_2$ .

Figure 2.2: Example showing language containment without simulation.

### 2.2 Model Checking

Traditional approaches to verification use deductive methods and focus mainly on the proof of correctness of sequential systems [Hoare, 1969, Lamport, 1980]. Such techniques rely on precondition and postcondition properties of smaller programs to derive correctness properties of larger programs. Model checking uses temporal logic [Pnueli, 1977, Clarke et al., 1986] to specify properties about systems that run on an ongoing basis and automated techniques to verify such properties.

There are two main approaches in model checking. In the automata theoretic approach [Vardi, 1996], the temporal specification is converted to an automaton, negated and then intersected with the automaton for the implementation. The property holds if the language of the intersection is empty. In the algorithmic approach, the specification is verified directly by graph traversal on the automaton that represents the implementation. The implementation automaton can be represented either explicitly by storing its states in memory or symbolically using Boolean functions that represent their corresponding characteristic function. The latter form is called symbolic model checking [Burch et al., 1992] and the Boolean functions are represented compactly using binary decision diagrams [Bryant, 1986].

We present a temporal logic called  $\mathbf{CTL}^*$  [Clarke et al., 1986]. The semantics of the logic is described in terms of a state machine that represents the implementation, called a Kripke structure. A Kripke structure is a tuple  $M = \langle Q, R, I, AP, L \rangle$  where  $\langle Q, R, I \rangle$  represents the state machine and  $L : Q \to 2^{AP}$  is a labeling function that describes the set of atomic propositions that hold in a given state.

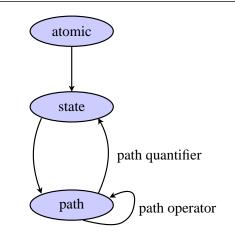

Figure 2.3: Structure of CTL\* formulas.

The structure of  $\mathbf{CTL}^*$  formulas is described in Figure 2.3.  $\mathbf{CTL}^*$  has two types of temporal formulas. Atomic formulas are those in the set AP. Any atomic formula is also a state formula,

and any state formula is also a path formula, verified on the first state of the path. Complex path formulas are constructed using path operators. The application of a path quantifier to a path formula yields a state formula. The syntax of formulas is defined inductively as follows:

Atomic Formulas If  $p \in AP$  is a proposition then p is an atomic formula.

#### **State Formulas**

- Any atomic formula is also a state formula.

- If f is a path formula then  $\mathbf{E} f$  and  $\mathbf{A} f$  are state formulas.

#### **Path Formulas**

- Any state formula is also a path formula.

- If f is a path formula then X f, G f, F f are paths formulas.

- If f and g are path formulas then  $f \mathbf{U} g$  is a path formula.

**E** and **A** are called path quantifiers. **E** f holds in a state if there exists a path from the state that satisfies f. Similarly, **A** f holds in a state, if for all paths from the state f holds. The formula **X** f is true of a path if f holds on the path starting in the next state. **G** f holds when f holds on all suffixes of the path, i.e. holds globally. Similarly, **F** f holds if there exists a suffix that satisfies f, i.e. f holds in the future. The formula f **U** g states that f must hold continously on all suffixes of the path up to, but not necessarily including, the suffix where g holds.

The transition relation of a Kripke structure is required to be total, i.e. for any state q there exists a state q' such that  $(q, q') \in R$ . If  $\pi$  is an infinite path  $(q^0, q^1, \ldots)$  we denote the suffix that starts at position k by  $\pi^k = (q^k, q^{k+1}, \ldots)$ . Satisfiability of **CTL**<sup>\*</sup> formulas is defined as follows:

#### Atomic Formulas

$$q \models p \equiv p \in L(q)$$

**State Formulas**

$$\begin{array}{ll} q \models \mathbf{E} \ f &\equiv \ \exists \ \pi = (q^0, q^1, \ldots). \ q = q^0 \land \pi \models f \\ q \models \mathbf{A} \ f &\equiv \ \forall \ \pi = (q^0, q^1, \ldots). \ q = q^0 \Longrightarrow \pi \models f \end{array}$$

**Path Formulas**

$$\begin{aligned} \pi &\models \mathbf{X} f \equiv \pi^{1} \models f \\ \pi &\models \mathbf{G} f \equiv \forall k. \pi^{k} \models f \\ \pi &\models \mathbf{F} f \equiv \exists k \in \mathbf{N}. \pi^{k} \models f \\ \pi &\models f \mathbf{U} g \equiv \exists k. \pi^{k} \models g \land \forall l < k. \pi^{l} \models f \end{aligned}$$

There are two subsets of  $\mathbf{CTL}^*$  that are used in practice.  $\mathbf{LTL}$  is the subset that consists of formulas of form  $\mathbf{A}$  *f* where *f* is a path formula that does not contain path quantifiers. The other subset is  $\mathbf{CTL}$  which allows only for formulas in which the occurrence of a path operator is preceded by a path quantifier. The  $\mathbf{CTL}$  temporal operators become  $\mathbf{EX}$ ,  $\mathbf{EG}$ ,  $\mathbf{EF}$ ,  $\mathbf{EU}$  and respectively  $\mathbf{AX}$ ,  $\mathbf{AG}$ ,  $\mathbf{AF}$ ,  $\mathbf{AU}$ .

**ACTL**<sup>\*</sup> is a subset of **CTL**<sup>\*</sup> that does not include existential quantifiers. The temporal properties of **ACTL**<sup>\*</sup> are preserved by simulation. Since **LTL** is a subset of **ACTL**<sup>\*</sup>, simulation also preserves **LTL** properties. In addition, **LTL** is also preserved by language containment.

## 2.3 Circuits

In this section we formalize a language for describing circuits. The syntax and semantics of the language are similar to the ones provided by model checkers such as NuSMV [Cimatti et al., 2002]. Circuits are defined using a language for bitvector expressions and their semantics is given using labeled transition systems.

A name is a string of characters that begins with a letter or underscore and then continues with zero or more letters, underscore or digits. An identifier is a sequence of one or more names separated by a '.'. Primed identifiers, identifiers followed by the prime symbol ''', are used to denote next-state variables.

2.3.1 Definition (Identifier). The set Id of identifiers is defined inductively as follows:

- Any name is an identifier.

- If  $id_1$  and  $id_2$  are identifiers then  $id_1 \cdot id_2$  is also an identifier.

Priming an identifier adds the prime symbol to the identifier. The set of primed identifiers is denoted by Id'. If  $id \in Id$  then  $id' \in Id'$  denotes its primed version. If V is a set of identifiers, V' denotes the set  $\{id' \mid id \in V\}$ .

Let **B** denote the set  $\{0, 1\}$ . Bitvector constants are finite words over the alphabet **B**.

**2.3.2 Definition** (Bitvector Constant). For  $n \ge 1$ , let  $\mathbf{B}^n$  denote the set of bitvector constants of size n. The set of all bitvectors  $\bigcup_{n\ge 1} \mathbf{B}^n$  is denoted by  $\mathbf{B}^+$ . Given a bitvector constant  $w \in \mathbf{B}^n$  and  $i \le n, w(i)$  denotes the *i*-th bit of w.

Variables are identifiers with a type. The type of a variable is the set  $\mathbf{B}^n$ , for some  $n \ge 1$ .

**2.3.3 Definition** (Variables).  $V \subseteq$  Id is called a set of variables if it is associated with a type function *Ty*

$$Ty: V \to \{\mathbf{B}^n\}_{n\geq 1}$$

Tyis extended over  $V' \subseteq Id'$ : Ty(v') = Ty(v). Primed variables refer to next-state variables. If v is a current state variable, v' denotes its next-state version. Similarly, if  $v' \in V'$  is a next-state variable, v denotes its current-state version.

**2.3.4 Definition** (Environment). An environment over the set of variables V is a function

$$e: V \to \mathbf{B}^+$$

that assigns each variable a value of its type:

$$\forall v \in V. e(v) \in Ty(v)$$

If  $V_1$  and  $V_2$  are disjoint sets of variables and  $e_1$  and  $e_2$  are environments defined over  $V_1$  and respectively,  $V_2$ , their union  $e_1 \cup e_2$  is the environment over  $V_1 \cup V_2$  defined by

$$(e_1 \cup e_2)(v) = \begin{cases} e_1(v) & : v \in V_1 \\ e_2(v) & : v \in V_2 \end{cases}$$

Let  $V \subseteq Id$  and let e be an environment over V. The environment e' over V' is defined by e'(v') = e(v).

Consider a set of variables  $V_1$ . We say  $V_2$  is a copy of  $V_1$  if there exists a bijective function  $\phi$ :  $V_1 \rightarrow V_2$  such that

$$\forall v \in V_1. Ty(v) = Ty(\phi(v))$$

If  $V_2$  is a copy of  $V_1$  and  $e_1 \in Env(V_1)$  we denote by  $e_1 [V_2/V_1]$  the environment  $e_2 \in Env(V_2)$  such that:

$$\forall v \in V_2. e_2(v) = e_1(\phi^{-1}(v))$$

**2.3.5 Definition** (Bitvector Expression). Let  $V \subseteq Id$  be a set of variables and Ty be the associated type function. Bitvectors are typed expressions over constants in  $B^+$  and variables in V. We say that the bitvector t has type  $B^n$  using the typing expression  $t : B^n$ . If t : B we say t is single-bit.

#### **Base Case**

- If  $v \in V$  is a variable such that  $Ty(v) = \mathbf{B}^n$ , then v is a bitvector expression of type  $\mathbf{B}^n$ .

- If  $w \in \mathbf{B}^n$  is a constant, then w is a bitvector of type  $\mathbf{B}^n$ .

**Inductive Case** Bitvector expressions are constructed using a set of operators. For such an operator **op**, a type rule is used to denote the type requirements on its operands and the type of its application:

$$rac{t_1:\mathbf{B}^{n_1},\ldots,\,t_k:\mathbf{B}^{n_k}}{\mathbf{op}(t_1,\ldots,t_k):\mathbf{B}^n}$$

If t is a bitvector expression then vars(t) stands for the set of variables that appear syntactically in t. Similarly, consts(t) denotes the set of constants  $w \in \mathbf{B}^+$  that appear syntactically in t.

Variables are assigned values by an environment e over V. The semantics of a constant  $w : \mathbf{B}^n$  is  $\llbracket w \rrbracket_e = w$ . The semantics of a variable  $v : \mathbf{B}^n$  is  $\llbracket v \rrbracket_e = e(v)$ . The semantics of a bitvector expression t such that  $t : \mathbf{B}^n$  is denoted by  $\llbracket t \rrbracket_e \in \mathbf{B}^n$ .

Subexpression

Type Rule

$$\frac{t : \mathbf{B}^{n}}{(t) : \mathbf{B}^{n}}$$

Semantics  $\llbracket (t) \rrbracket_{e} = \llbracket t \rrbracket_{e}$

Constant

Type Rule

$$\frac{w \in \mathbf{B}^n}{w : \mathbf{B}^n}$$

Semantics  $\llbracket w \rrbracket_e = w$

Variable

Type Rule

$$\frac{v \in V, \quad Ty(v) = \mathbf{B}^n}{v : \mathbf{B}^n}$$

Semantics

$$[v]_e = e(v)$$

Bitwise Operators The bitvector operator  $\mathbf{op} \in \{\mathbf{not}, \mathbf{and}, \mathbf{or}, \mathbf{xor}, \ldots\}$  is defined using the corresponding Boolean operator  $\mathbf{op}_2 \in \{\mathbf{not}_2, \mathbf{and}_2, \mathbf{or}_2, \mathbf{xor}_2, \ldots\}$ .

Type Rule

$$\frac{t_1 : \mathbf{B}^n, t_2 : \mathbf{B}^n}{t_1 \text{ op } t_2 : \mathbf{B}^n}$$

Semantics  $\llbracket t_1 \text{ op } t_2 \rrbracket_e(i) = \llbracket t_1 \rrbracket_e(i) \text{ op}_2 \llbracket t_2 \rrbracket_e(i), i = \overline{0, n-1}$

Bitwise negation requires only one argument and we present it separately.

Type Rule