# CAD Techniques for Robust FPGA Design Under Variability

by

Akhilesh Kumar

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

© Akhilesh Kumar 2010

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The imperfections in the semiconductor fabrication process and uncertainty in operating environment of VLSI circuits have emerged as critical challenges for the semiconductor industry. These are generally termed as process and environment variations, which lead to uncertainty in performance and unreliable operation of the circuits. These problems have been further aggravated in scaled nanometer technologies due to increased process variations and reduced operating voltage.

Several techniques have been proposed recently for designing digital VLSI circuits under variability. However, most of them have targeted ASICs and custom designs. The flexibility of reconfiguration and unknown end application in FPGAs make design under variability different for FPGAs compared to ASICs and custom designs, and the techniques proposed for ASICs and custom designs cannot be directly applied to FPGAs. Very few techniques have been proposed for FPGA design under variability, with varying degrees of improvement in timing/power variability. However, these have not dealt with leveraging CAD, architecture and circuits co-design methodologies for FPGA design under variability, and further, have not accounted for the impact of the variability in  $V_{dd}$  arising due to IR drops which is important because the performance of a circuit becomes more sensitive to process parameters as  $V_{dd}$  is reduced.

An important design consideration is to minimize the modifications in architecture and circuit to reduce the cost of changing the existing FPGA architecture and circuit. The work in this thesis develops CAD and architecture/circuit design techniques for FPGAs to improve the timing and power yield of FPGA designs under process variations. In the case of environment variations this work focuses on developing design techniques for reducing IR-drops. The focus of this work can be divided into three principal categories, which are, improving timing yield under process variations, improving power yield under process variations and improving the voltage profile in the FPGA power grid.

The work on timing yield improvement implements a Statistical Static Timing Analysis (SSTA) framework to analyze the circuit delay under process variations, such that the statistical distribution of the critical delay can be computed. In this work, the structure of the interconnect is analyzed and it is shown that an optimum number of buffers can be inserted in the interconnect to reduce the variation in circuit delay. Several interconnect architectures are analyzed, under the constraints of the FPGA structure, to find the best architecture which leads to smallest ( $\mu + 3\sigma$ ) of the critical delay. The placement and routing tools are then enhanced such that the delay variability is accounted for when optimizing the critical delay of the circuit. Results indicate that up to 28% improvement in ( $\mu + 3\sigma$ ) of the critical delay can be obtained from the proposed methodology.

The work on power yield improvement for FPGAs selects a low power dual- $V_{dd}$  FPGA design as the baseline FPGA architecture for developing power yield enhancement tech-

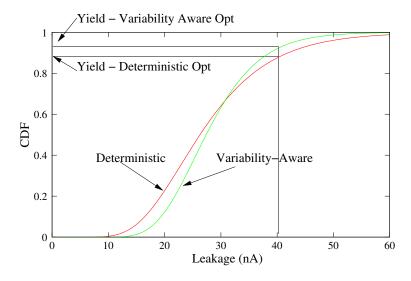

niques. A low power FPGA architecture is selected because, before applying power yield enhancement techniques to a design, it is necessary that a low power design technique is implemented. The power yield enhancement technique proposed in this work is essentially a CAD technique for placement and dual- $V_{dd}$  assignment. The proposed CAD techniques reduce the correlation between leaking FPGA elements such that the total variability of leakage is reduced and power yield is improved. Results indicate that an average reduction of 15% in leakage variability can be obtained from the proposed methodology, with an average of 7.8% power yield improvement. A mathematical programming technique is also proposed to determine the parameters of the buffers in the interconnect such as the sizes of the transistors and threshold voltage of the transistors, all within constraints, such that the leakage variability is minimized under delay constraints. Results show a reduction of 26% in leakage variability without any delay penalty.

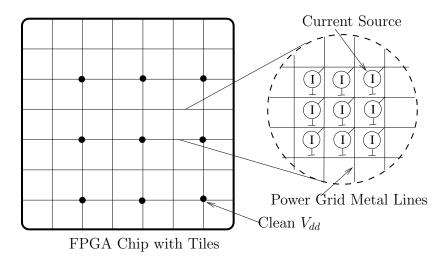

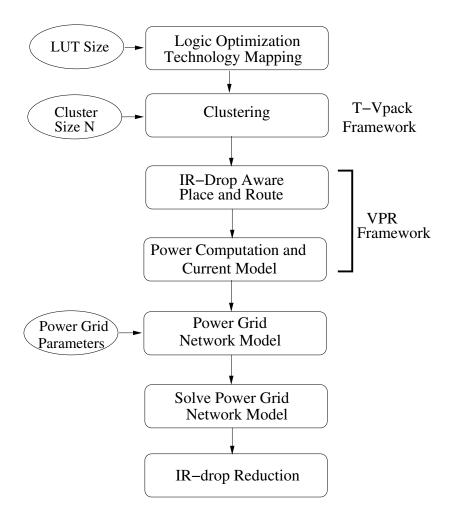

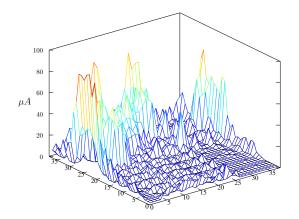

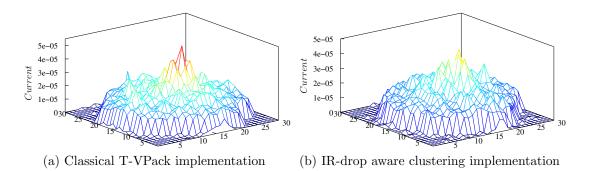

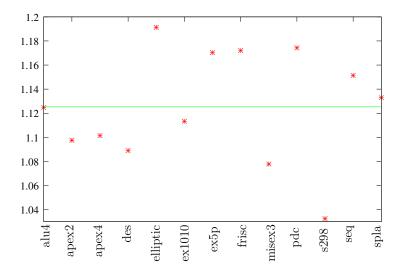

The variability in supply voltage in the power grid occurs due to currents being drawn by the underlying devices. The IR-drops in the power grid leads to reduced speed of the circuit and may also affect the functionality of the design. To reduce IR-drops in the power grid of FPGAs two CAD techniques are proposed in this work. The first technique is an IR-drop aware place and route technique which reduces the high currents drawn in local regions of the chip to reduce the IR-drops. The placement and routing routines are enhanced to incorporate the information about the current distribution profile in the power grid. This is done by redistributing the blocks and nets in such a way so that the spatial distribution of the switching activity profile is more smooth. The CAD techniques result in maximum IR-drop reduction of up to 53% and a reduction in standard deviation of spatial supply voltage distribution by up to 66%.

The second technique is also a CAD technique applied at the clustering stage, where the LUTs are clustered into fixed size logic blocks. The idea here again is to reduce the currents being drawn in a local region. This is achieved by carefully selecting the LUTs to be added to form a cluster. This is because if a cluster has many LUTs with high switching activity nets, then that cluster will experience a large IR-drop. The clustering technique is enhanced such that the new IR-drop aware clustering technique takes into account the switching activities of the nets in the current cluster and the switching activities of the nets connected to potential LUTs that can be added to the current cluster. Results indicate that up to 36% reduction in maximum IR-drop and 27% reduction in standard deviation of the spatial distribution of  $V_{dd}$  can be achieved from the proposed techniques.

#### Acknowledgements

This thesis is dedicated to my parents. My mother, who is my first teacher, and ever full of her untiring support and encouragement, gave me the strength of character for all my pursuits. My father taught me the importance of discipline and hard work with single minded devotion. Amidst all the different pursuits, they taught me how to lead a life of principles and righteousness. And many more things that I have imbibed and learned from them have shaped me as I am today.

Without the invaluable guidance, encouragement and support from my supervisor Prof. Mohab Anis, this thesis would not have been possible. It was his constant guidance that has seen me through this work. Mohab has not only been my supervisor but also a mentor and a friend as well and I have sought his opinion and guidance on many things, which have always been honest, helpful and trustful. He gave me the freedom and flexibility in my research and provided continuous guidance and support in my research pursuits. I am truly grateful and thankful to him for all his help and support and I am glad to say that I have really learned a lot from him during the last six and half years, first as a Master's student and then as a PhD student.

The committee members have also helped a lot in bringing my thesis in the current shape and I am thankful to all of them. Prof. Mark Aagaard, who was also my MASc thesis reader, gave very valuable comments on this thesis which have helped in improving this thesis tremendously. I also had an opportunity to work as a teaching assistant for Prof. Mark Aagaard and learned a lot while working with him. Prof. Manoj Sachdev's comments helped me gain a better insight and improve this thesis. Prof. Yehia Massoud, who was my external examiner, provided me with good comments on my thesis and gave some constructive suggestions for this work. I am also thankful to Prof. Eihab Abdel-Rahman and my co-supervisor Prof Karim Karim for reviewing my thesis.

I am thankful to Prof. Andrew Kennings who has always been very helpful and with whom I have had many discussions on research and teaching. I am thankful to my colleagues at the VLSI research lab with whom I have had not only technical discussions but also shared lighter moments. Javid, Vasudha, Hassan, Ahmed and Mohamed Abu-Rahma have all been a part of my stay at Waterloo. The administrative and technical staff at the Department of Electrical and Computer Engineering have always been very helpful and prompt with their support. Wendy Boles has helped me by going out of the way so many times that I cannot thank her enough. Phil Regier has always promptly helped me with all the technical issues relating to either hardware or software. I would also like thank Nizar Abdallah and Georges Nabaa at Actel Corp., Mountain View, California, for their support during my visit to the company in Fall 2008.

My stay at Waterloo as a graduate student, of almost six and half years, first as a Master's student and then as a PhD student has been made memorable due to so many people that it is impossible to name all of them. My roommates were always there with all their support and I have shared so much with them. Aashish, Sachin and Sarvagya, with whom I have spent such a wonderful time that I cannot imagine my stay at Waterloo without them. Sachin, always ready with his comments on anything, Sarvagya, ever eager to carry out his pranks and Aashish, quietly observant, are some of the cherished memories. We have together celebrated many occasions and talked about so many things that they have become great friends and some of the closest friends for life. Niraj has been such a close and helpful friend with whom I have shared many ups and downs and had long discussions on many things. Srinath has always been very helpful and a close friend with whom I have spent a lot of wonderful time. Addi has been a great friend with whom I have been part of so many activities. Nikita has been very nice and has cooked wonderful dishes on many occasions. I will also remember the fun times with Shaweta during my earlier part of stay at Waterloo. Guru, Neeraj, Jyotsna, Navneet, Prashant, Abir, Aniket, Bala and many others have also been a part of my experiences at Waterloo. My friends from undergraduate days, Gunjan, Roopesh, Santosh, Amitesh and Nagendra have always supported me throughout my graduate studies.

During the later part of my PhD I met Jalaj, and then Darya, Prachi and Shubham. Jalaj has been my roommate and is someone very close to me and he has always been full of support. Darya is not only a wonderful friend but also became so close to me that she is like a sister to me and has always encouraged me and wished the best for all my efforts. Shubham has been such a nice and close friend through all my joys and sorrows. Prachi became a very good friend during the short time that I knew her at Waterloo. I have had a great time with them during the last year of my PhD. Thanks are due to Anupam and Surbhi and their son Anav who have treated me very warmly and friendly during all my visits to California.

Finally, I cannot appreciate enough the great emotional support that I received from my sisters and cousins. My sisters, Kanchan and Shashi, have always been a source of solace for me. My cousin, Sharad, has always supported, encouraged and helped me in my endeavors. We have discussed so many things in such wonderful terms that talking to him always made me happy. I also remember how my cousins Shailly, Rashmi, Pallavi, Himanshu and Sameer were full of good wishes for my work and eagerly waited for my visits to India. Special word of appreciation is also due to my uncles Indra Mohan and Shekhar from whom I have learned so many things in life, right from my childhood days, and who have always been a source of constant support. I would also like to thank all my family members for their constant support and encouragement in all my endeavors.

# Contents

| List of Tables x   |      |                                                                                                           |    |  |

|--------------------|------|-----------------------------------------------------------------------------------------------------------|----|--|

| List of Figures xi |      |                                                                                                           | V  |  |

| 1                  | Intr | roduction                                                                                                 |    |  |

|                    | 1.1  | Motivation                                                                                                | 1  |  |

|                    | 1.2  | Thesis Organization                                                                                       | 2  |  |

| <b>2</b>           | FPO  | A Architecture and CAD Overview                                                                           | 4  |  |

|                    | 2.1  | $\operatorname{ntroduction}$                                                                              | 4  |  |

|                    | 2.2  | FPGA Architecture                                                                                         | 4  |  |

|                    |      | 2.2.1 Logic Block                                                                                         | 4  |  |

|                    |      | 2.2.2 Routing Resources                                                                                   | 6  |  |

|                    |      | 2.2.3 I/O Blocks                                                                                          | 8  |  |

|                    | 2.3  | CAD Tools                                                                                                 | 8  |  |

|                    |      | 2.3.1 Synthesis $\ldots$ | 9  |  |

|                    |      | $2.3.2  \text{Placement}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                | 10 |  |

|                    |      | $2.3.3  \text{Routing}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                  | 12 |  |

|                    | 2.4  | VPR and T-VPack                                                                                           | 13 |  |

| 3                  | Bac  | ground and Related Work 1                                                                                 | .6 |  |

|                    | 3.1  | ntroduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$                   | 16 |  |

|                    | 3.2  | Classification of parameter variations                                                                    | 16 |  |

|   |                | 3.2.1 Process variations                                                                                                                      |

|---|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|   |                | 3.2.2 Voltage Variations $\ldots \ldots 19$ |

|   |                | 3.2.3 Temperature Variations                                                                                                                  |

|   | 3.3            | Modeling of process variations                                                                                                                |

|   |                | 3.3.1 Principal Components Analysis (PCA) Model                                                                                               |

|   |                | 3.3.2 Quad-Tree Model                                                                                                                         |

|   | 3.4            | Yield of a design                                                                                                                             |

|   | 3.5            | Managing Variability in ASICs                                                                                                                 |

|   |                | 3.5.1 Process Variations                                                                                                                      |

|   |                | 3.5.2 Supply Voltage Variations                                                                                                               |

|   | 3.6            | FPGA Design under Variations                                                                                                                  |

|   | 3.7            | Proposed Techniques                                                                                                                           |

| 4 | $\mathbf{Des}$ | sign for Timing Yield 32                                                                                                                      |

|   | 4.1            | Introduction $\ldots \ldots 32$                           |

|   | 4.2            | Statistical Static Timing Analysis                                                                                                            |

|   | 4.3            | Proposed Technique                                                                                                                            |

|   |                | 4.3.1 Impact of Segment Length on Variability                                                                                                 |

|   |                | 4.3.2 Routing Architecture Evaluation                                                                                                         |

|   |                | 4.3.3 Variability-Aware Placement and Routing 43                                                                                              |

|   | 4.4            | Evaluation, Results and Discussions                                                                                                           |

|   |                | 4.4.1 Experimental Details                                                                                                                    |

|   |                | 4.4.2 Results and Discussions                                                                                                                 |

|   | 4.5            | Conclusions                                                                                                                                   |

| 5 | Des            | sign for Power Yield 53                                                                                                                       |

|   | 5.1            | Introduction                                                                                                                                  |

|   | 5.2            | Targeted FPGA Architecture                                                                                                                    |

|   |                | 5.2.1 Statistical Power Model                                                                                                                 |

|   | 5.3            | Proposed Methodology                                                                                                                          |

|   |                |                                                                                                                                               |

|   |      | 5.3.1  | Preliminaries                                                                                                               |

|---|------|--------|-----------------------------------------------------------------------------------------------------------------------------|

|   |      | 5.3.2  | Placement Methodology 60                                                                                                    |

|   |      | 5.3.3  | Dual-Vdd Assignment                                                                                                         |

|   | 5.4  | Evalua | ation, Results and Discussions                                                                                              |

|   |      | 5.4.1  | Experimental Details                                                                                                        |

|   |      | 5.4.2  | Estimating leakage distribution and yield                                                                                   |

|   |      | 5.4.3  | Results and Discussions                                                                                                     |

|   | 5.5  | Conclu | usions                                                                                                                      |

| 6 | Inte | erconn | ect Design under Process Variations 74                                                                                      |

|   | 6.1  | Introd | uction $\ldots \ldots 74$ |

|   | 6.2  | Impac  | t of Process Variations on Leakage and Delay                                                                                |

|   |      | 6.2.1  | Process Parameters and Variations                                                                                           |

|   |      | 6.2.2  | Leakage Modeling                                                                                                            |

|   |      | 6.2.3  | Delay Modeling                                                                                                              |

|   |      | 6.2.4  | Variation Modeling                                                                                                          |

|   | 6.3  | Propo  | sed Methodology                                                                                                             |

|   |      | 6.3.1  | Deterministic Optimization                                                                                                  |

|   |      | 6.3.2  | FOSM Based Model: Accounting for Variability                                                                                |

|   | 6.4  | Evalua | ation, Results and Discussions                                                                                              |

|   | 6.5  | Conclu | asion                                                                                                                       |

| 7 | IR-  | Drop 4 | Aware Place and Route   84                                                                                                  |

|   | 7.1  | Introd | uction                                                                                                                      |

|   | 7.2  | Power  | Grid Model                                                                                                                  |

|   | 7.3  | Propo  | sed Methodology                                                                                                             |

|   |      | 7.3.1  | IR-Drop Aware Placement                                                                                                     |

|   |      | 7.3.2  | IR-Drop Aware Routing                                                                                                       |

|   | 7.4  | Exper  | imental Details, Results and Discussions                                                                                    |

|   |      | 7.4.1  | Experimental Details                                                                                                        |

|   |      | 7.4.2  | Results and Discussions                                                                                                     |

|   | 7.5  | Conch  | usions                                                                                                                      |

| 8 IR-Drop Aware Clustering |       |                                 | 100 |

|----------------------------|-------|---------------------------------|-----|

|                            | 8.1   | Introduction                    | 100 |

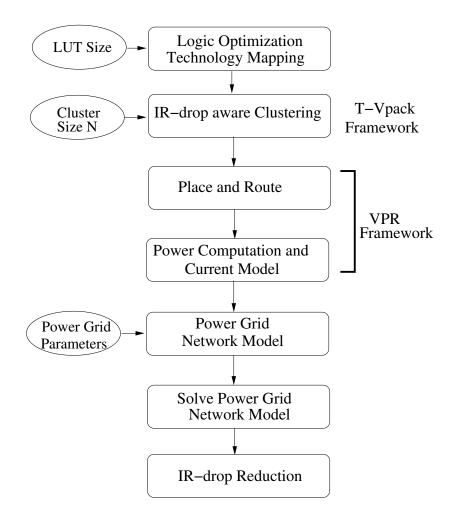

|                            | 8.2   | Proposed CAD Flow               | 100 |

|                            | 8.3   | Proposed Clustering Technique   | 102 |

|                            | 8.4   | Results and Discussions         | 110 |

|                            |       | 8.4.1 Trade-offs and Advantages | 112 |

|                            | 8.5   | Conclusions                     | 116 |

| 9                          | Con   | clusions and Future Work        | 117 |

|                            | 9.1   | Conclusions                     | 117 |

|                            | 9.2   | Future Work                     | 118 |

| Re                         | efere | nces                            | 127 |

# List of Tables

| 4.1 | Routing architecture evaluation                                                            | 41  |

|-----|--------------------------------------------------------------------------------------------|-----|

| 4.2 | Routing architecture evaluation: % Improvement $\ldots \ldots \ldots \ldots \ldots \ldots$ | 42  |

| 4.3 | Benchmark sizes                                                                            | 46  |

| 4.4 | Results of Variability-Aware Design for Timing Yield                                       | 47  |

| 5.1 | Results of variability aware placement                                                     | 70  |

| 6.1 | Results of variability aware and deterministic optimizations                               | 82  |

| 7.1 | Results of IR-Drop Aware Design                                                            | 93  |

| 8.1 | Results of IR-Drop Aware Clustering                                                        | 111 |

| 8.2 | Power savings and runtime for IR-drop aware clustering                                     | 115 |

| 9.1 | Summary of Proposed Techniques                                                             | 118 |

# List of Figures

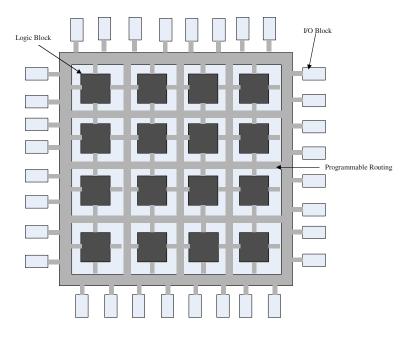

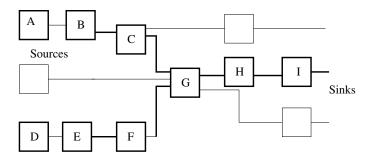

| 2.1 | A basic FPGA                                                                                        | 5  |

|-----|-----------------------------------------------------------------------------------------------------|----|

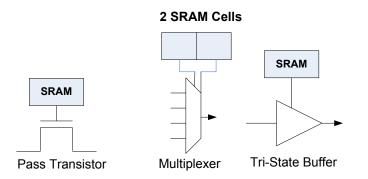

| 2.2 | Programmable switches used in SRAM-based FPGAs                                                      | 5  |

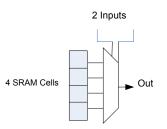

| 2.3 | A 2-input LUT                                                                                       | 5  |

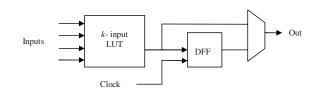

| 2.4 | Basic Logic Element $[1]$                                                                           | 6  |

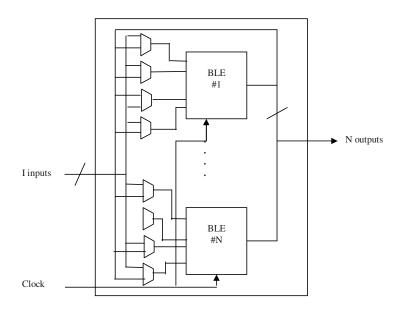

| 2.5 | Cluster based logic block [1]                                                                       | 7  |

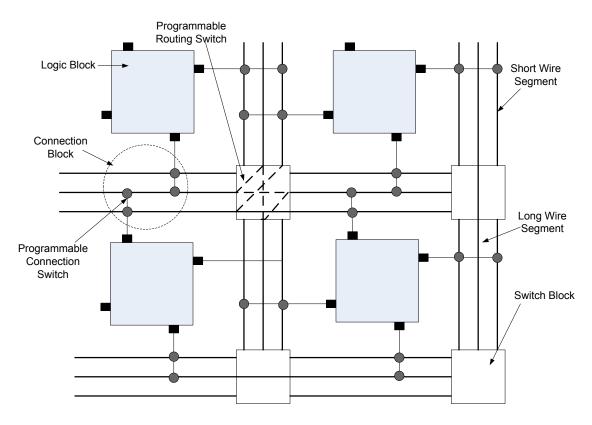

| 2.6 | Island style routing architecture [1]                                                               | 7  |

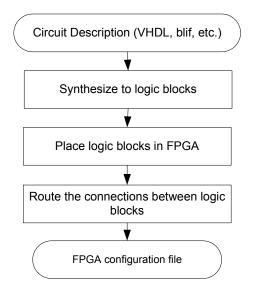

| 2.7 | Basic CAD flow for FPGAs                                                                            | 8  |

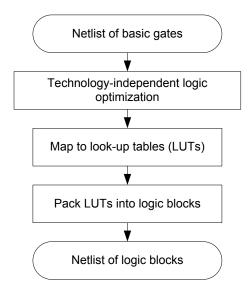

| 2.8 | Synthesis procedure for FPGAs                                                                       | 9  |

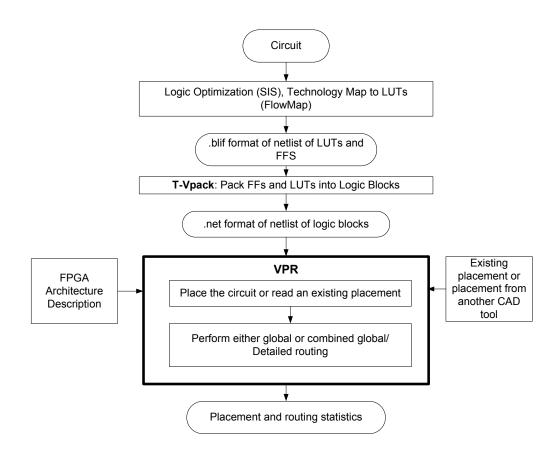

| 2.9 | VPR CAD flow                                                                                        | 14 |

| 3.1 | Variation in Timing and Leakage [2]                                                                 | 17 |

| 3.2 | A general classification of the parameter variations                                                | 18 |

| 3.3 | Grid Model for PCA                                                                                  | 21 |

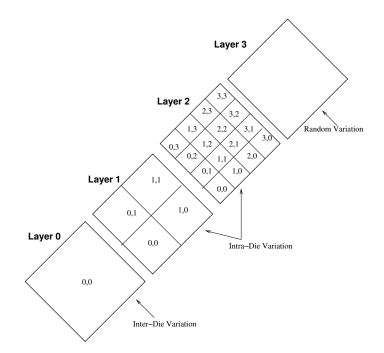

| 3.4 | Layer model for representing the spatially correlated process parameters                            | 22 |

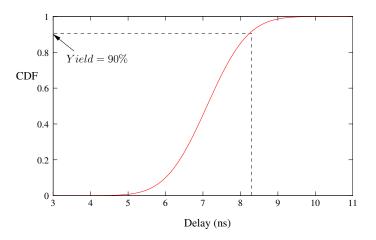

| 3.5 | CDF of a circuit delay to determine the yield $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$    | 24 |

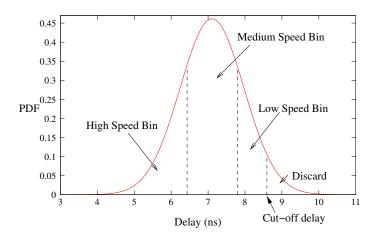

| 3.6 | PDF of a circuit delay and speed binning applied to improve the yield                               | 24 |

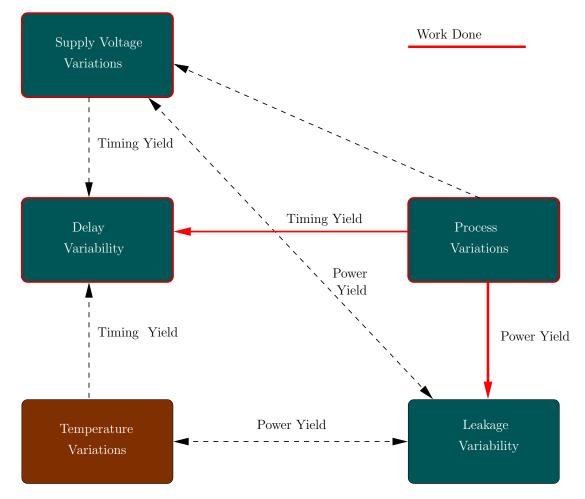

| 3.7 | Interaction between process variations, environments variations and their impact on power and delay | 31 |

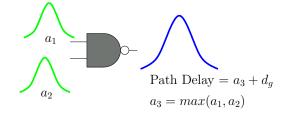

| 4.1 | Merging arrival times                                                                               | 34 |

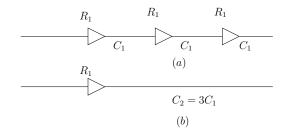

| 4.2 | Impact of buffers on the delay variability                                                          | 38 |

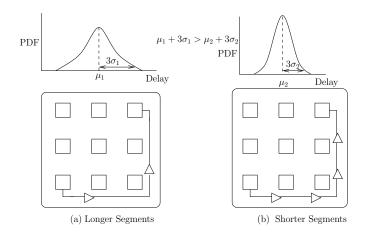

| 4.3 | Delay variability reduction using shorter segments                                                  | 39 |

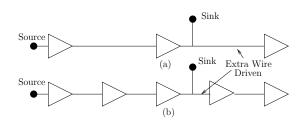

| 4.4 | Extra wire segments in routing                                                                      | 39 |

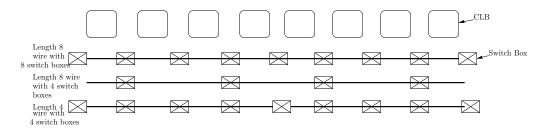

| 4.5 | A section of routing fabric showing different segment lengths $\ldots$ $\ldots$ $\ldots$                                                         | 41  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

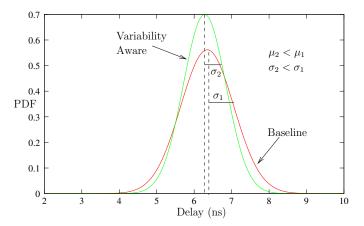

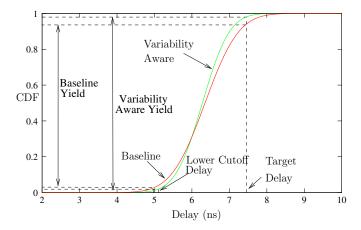

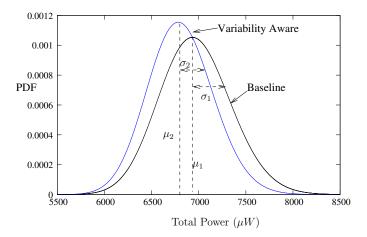

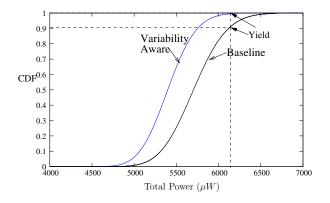

| 4.6 | The PDFs for the baseline and variability aware implementations for the benchmark apex4                                                          | 51  |

| 4.7 | The CDFs for the baseline and variability aware implementations for the benchmark apex4                                                          | 52  |

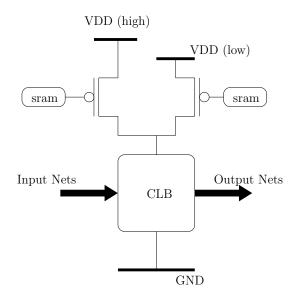

| 5.1 | Dual-Vdd logic block implementation for power reduction                                                                                          | 56  |

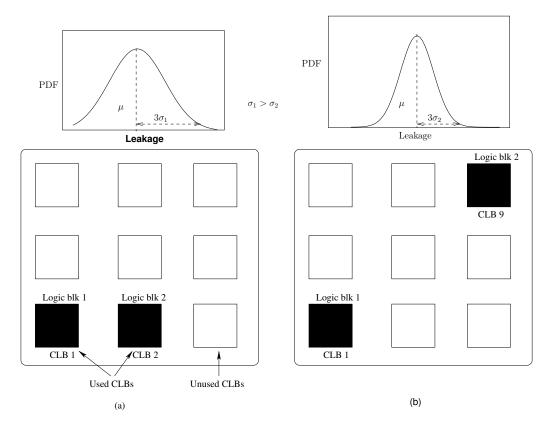

| 5.2 | Example illustrating the impact of placement on leakage pdf. Spatial corre-<br>lation causes the variance of leakage to increase.                | 61  |

| 5.3 | (a) Placement is fairly spread out throughout the FPGA, which leads to reduced leakage variance. (b) Placement more concentrated, higher leakage | 60  |

|     | variance.                                                                                                                                        | 63  |

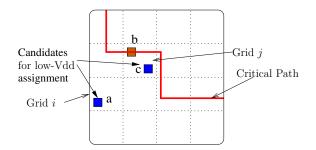

| 5.4 | Variability-Aware Dual-Vdd assignment technique                                                                                                  | 65  |

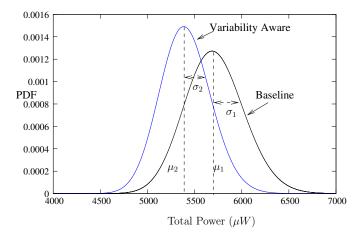

| 5.5 | Power distribution without and with variability aware placement for alu4 .                                                                       | 71  |

| 5.6 | Power distribution without and with variability aware placement for seq                                                                          | 72  |

| 5.7 | CDF of power distributions for alu4 for the baseline implementation and variability aware placement                                              | 72  |

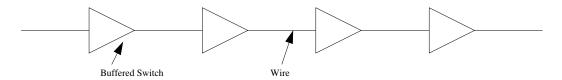

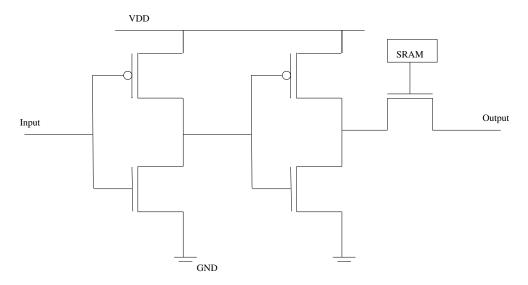

| 6.1 | Interconnect in FPGAs having buffered switches evenly spaced                                                                                     | 74  |

| 6.2 | Schematic of a buffered switch. The SRAM cell controls the pass transistor.                                                                      | 75  |

| 6.3 | CDFs for the deterministic and the variability-aware optimizations                                                                               | 83  |

| 7.1 | Mesh style power grid model                                                                                                                      | 85  |

| 7.2 | Proposed IR-drop aware Place and Route CAD flow                                                                                                  | 87  |

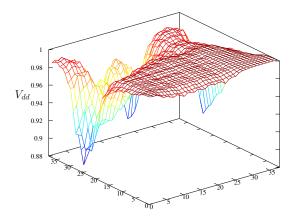

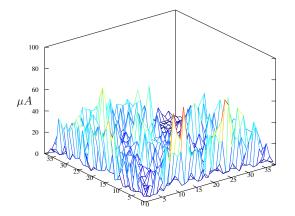

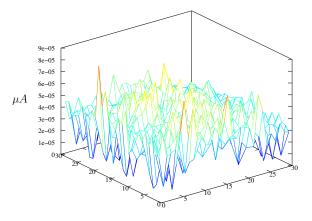

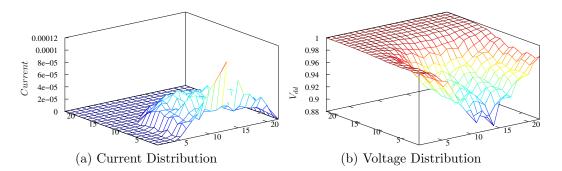

| 7.3 | Current distribution for baseline implementation: $des$                                                                                          | 94  |

| 7.4 | Voltage distribution for baseline implementation: des                                                                                            | 94  |

| 7.5 | Current distribution for IR-drop aware implementation: $des$                                                                                     | 95  |

| 7.6 | Voltage distribution for IR-drop aware implementation: $des$                                                                                     | 95  |

| 7.7 | Current distribution for baseline implementation: $s38417$                                                                                       | 96  |

| 7.8 | Current distribution for IR-drop aware implementation: $s38417$                                                                                  | 96  |

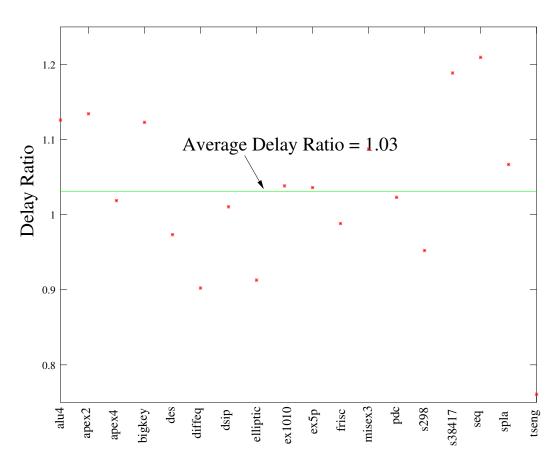

| 7.9 | Ratio of the circuit delay for the IR-drop aware and baseline implementation                                                                     | 98  |

| 8.1 | Proposed IR-drop aware CAD flow                                                                                                                  | 101 |

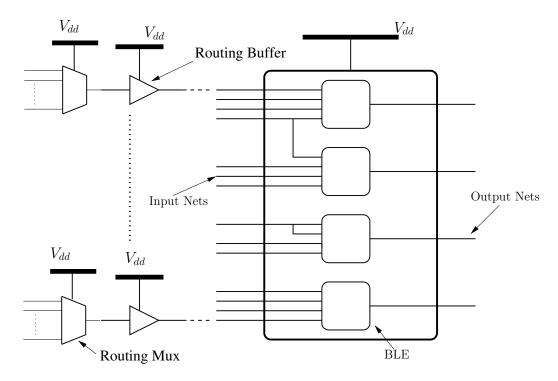

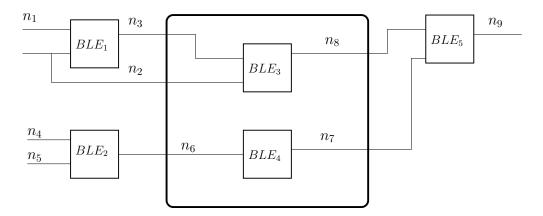

| 8.2 | Logic cluster with input and output nets                                          |

|-----|-----------------------------------------------------------------------------------|

| 8.3 | Criticality tie breaking technique [3]                                            |

| 8.4 | Computing the transition density cost during clustering                           |

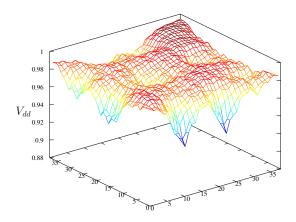

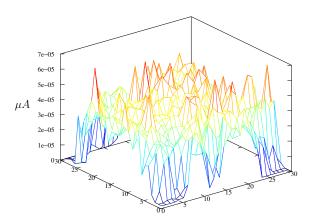

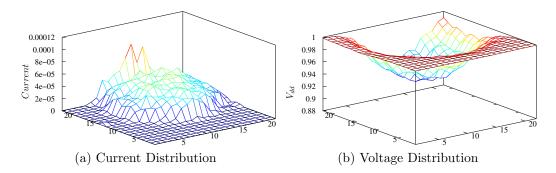

| 8.5 | Current and voltage distribution for the baseline implementation: $alu4$ 112      |

| 8.6 | Current and voltage distribution for the IR-drop aware implementation: $alu4112$  |

| 8.7 | Current distributions for the baseline and IR-drop aware implementations:         |

|     | ex1010                                                                            |

| 8.8 | Ratio of the circuit delay for the IR-drop aware and baseline implementations.114 |

## Chapter 1

## Introduction

## 1.1 Motivation

Integrated circuits are now virtually present in all high-performance computing, communications, and consumer electronics applications. With the increasing complexity of these applications, there has been a growing need to integrate the functions of these applications in smaller packages. To enable this integration, the semiconductor technology is continuously being scaled in the nanometer regime. The high level and complexity of integration along with scaled nanometer technologies present many enormous and critical challenges which must be effectively managed by the designers. In the nanometer technologies, the two most important design challenges cited by the semiconductor industry are the increasing leakage power and the process variations in device characteristics. These two serious issues threaten the life time of silicon technology, and will hinder the development of the microelectronics industry if not addressed. Standby leakage power has been growing at an alarming rate, and constitutes a larger fraction of the total chip power in current and future technology generations. Moreover, the manufacturing process of nanometer transistors and structures has introduced several new sources of variation that have made the control of process (device dimensions) variations more difficult. Additionally, environmental variations are caused by uncertainty in the environmental conditions during the operation of a chip, namely, power supply and temperature fluctuations. Both the process and the environmental variations significantly impact the chips' performance, power dissipation and reliability, and thereby reduce the yield of a design. In recent years several techniques have been proposed for addressing the standby leakage power. The leakage power problem is further aggravated by its strong dependence on process and environmental variations, leading to variation in leakage power which can be as high as 20X [2]. This makes it more difficult for designs to meet a power budget resulting in yield loss. Technology scaling has resulted in circuits which can operate at higher speeds, but this has also made the timing optimization more complex. Traditionally, timing optimization has been done at all levels, where maximum savings in the clock cycles are obtained at the architecture level design optimization. However, circuit level techniques try to further push this limit to increase the operating clock frequency. The delays of the logic gates and interconnects are strongly dependent on the process and environmental parameters, which makes the clock frequency to have significant variation due to variation in these parameters. Meeting the target clock frequency with these variations is a challenge and results in timing yield loss.

Field Programmable Gate Arrays have emerged as a competitive alternative to Application Specific Integrated Circuits (ASICs) to implement designs and their popularity have grown in recent years. FPGAs are preferred means to implement a design for low to medium volume productions because of significant cost reduction and time-to-market advantages. Hence, FPGAs are now utilized extensively in various communication systems/devices. The number of design starts based on FPGAs is continuously increasing because of advances in FPGA technology and newer architectures with improvement in speed and area. Over the past decade, the management of leakage power in FPGA designs has always been overshadowed by performance improvement and dynamic power minimization techniques. However, with contemporary and future FPGAs being built in nanometer technologies, leakage power cannot be ignored. This is aggravated by the very nature of FPGAs, where typical block utilization is around 60% [4], such that 40% of the FPGA is dissipating standby leakage power! Only recently have FPGA designers started to tackle leakage power [5, 6, 7, 8]. The leakage power problem in FPGAs is further compounded by the fact that FPGAs need more number of transistors per logic gate as compared to custom VLSI designs and ASICs. In addition, process and environmental variations impact FPGAs in these principal areas: timing analysis, leakage power prediction, leakage tolerant design, and reliability. The focus of this research is to develop innovative architectures/circuit/CAD co-design for optimization of timing and leakage yield of FPGAs under process variations and improve the robustness of FPGAs under supply voltage variations due to IR-drops. This would enable FPGA designers to answer the following question: "How to utilize novel FPGA architecture, circuit and design automation techniques cooperatively to maximize the FPGA design yield and improve robustness under power, timing and area constraints?"

## **1.2** Thesis Organization

This thesis is organized as follows:

Chapter 2 gives an overview of a typical *SRAM-based* FPGA architecture which is targeted in this work and is widely used in industry.

Chapter 3 describes the process and environment variations and its impact on VLSI

circuits. This section also explains the various modeling techniques for analyzing the impacts of the variations and the modeling approach adopted in this work. This is then followed by a discussion of the related work done for FPGAs.

**Chapter 4** proposes a CAD and architecture co-design technique for improving the timing yield of FPGA designs under process variations. Results are presented to show the improvement in the timing yield.

**Chapter 5** proposes a CAD methodology for improving the power yield of FPGA designs under process variations. The CAD methodology is explained and the results are presented to show the power yield improvement.

**Chapter 6** proposes a mathematical programming technique for determining the parameters of the transistors of the buffers, such as the sizes and the threshold voltages, in the FPGA interconnects for reducing leakage variability under delay constraints.

**Chapter 7** proposes placement and routing techniques for improving the supply voltage profile in the power grid of FPGAs. The proposed placement and routing techniques are explained along with power grid modeling and the results for the improvement of voltage profile in the power grid are discussed.

**Chapter 8** proposes logic clustering technique to improve the supply voltage profile in the power grid of FPGAs. The novel clustering technique is discussed along with the trade-offs and supply voltage profile improvement.

Chapter 9 concludes the work in the thesis and outlines future work.

## Chapter 2

# FPGA Architecture and CAD Overview

## 2.1 Introduction

This chapter describes the FPGA architecture that has been adopted for this research. The various elements of the FPGA is described and the CAD tools associated for implementing an application on the FPGA has been discussed. The CAD flow and each of the stages in the CAD flow is explained along with their algorithms.

## 2.2 FPGA Architecture

A basic FPGA is shown in Fig. 2.1. The FPGA architecture is very regular in structure. It is made up of two main components - logic blocks (CLBs) and routing resources. The logic blocks implement the functionality of the given circuit while the routing resources provide the connectivity for implementing the logic. The logic blocks have the flexibility to connect to the routing resources surrounding them. The logic blocks and the routing resources are configurable, so that they can be programmed to implement any logic. Though many types of architectures have been experimented with, the most popular one is the SRAM based architecture which is described below and has been used in this work [1].

### 2.2.1 Logic Block

The logic block of the SRAM based FPGA is LUT (look-up-table) based and are composed of basic logic elements (BLE). LUT is an array of SRAM cells to implement a truth table.

Figure 2.1: A basic FPGA

Figure 2.2: Programmable switches used in SRAM-based FPGAs

Figure 2.3: A 2-input LUT

Figure 2.4: Basic Logic Element [1]

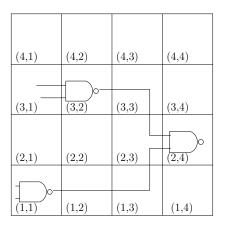

Fig. 2.3 shows a two input LUT. It has 4 SRAM cells and a multiplexer to select one of the SRAM cells. The selection is done by the two select signals to the multiplexer, which serve as inputs to the truth-table. Each BLE consists of a k-input LUT, flip-flop and a multiplexer for selecting the output either directly from the output of LUT or the registered output value of the LUT stored in the flip-flop. Fig. 2.4 shows the basic logic element. Previous works have shown that the 4-input LUT is the most optimum size as far as logic density, and utilization of resources are concerned, and this has been widely used. Cluster based logic blocks were investigated in [1] and it was shown that the cluster based logic block is shown in Fig. 2.5. In the cluster based logic block, the logic block is made up of N BLEs. There are I inputs to the logic block such that each input can connect to all the BLEs. Also the output of each BLE can drive one of the inputs of each of the BLEs. The clock feeds all the BLEs. The work in [1] showed that the logic clusters containing 4 to 10 BLEs achieve good performance. Each subblock is made up of a BLE and the corresponding LUT input multiplexers.

### 2.2.2 Routing Resources

The routing resources are of various types, but the one used in this work is the islandbased architecture. In the island based architecture, the routing resources form a mesh like structure with the horizontal and vertical routing channels. The horizontal and vertical routing channels are connected by switch boxes which are programmable and thus provide the flexibility in making the connections. The logic blocks are connected to the routing channels through the connection boxes which are also programmable. Fig. 2.6 shows the island style routing architecture [1]. The programmable switches used for implementing the interconnections are shown in Fig. 2.2. These programmable switches have SRAM cells which can be programmed to either turn on or turn off the switch. Apart from the logic blocks and the routing resources, the clock distribution is assumed to have a dedicated network. Most of the commercial FPGAs have a structure similar to the one described above or some variant of the above architecture.

Figure 2.5: Cluster based logic block [1]

Figure 2.6: Island style routing architecture [1]

Figure 2.7: Basic CAD flow for FPGAs

### 2.2.3 I/O Blocks

The I/O blocks are also programmable so that they can be configured either as input or as output, or can be tri-stated.

## 2.3 CAD Tools

To implement a circuit on the current generation FPGAs, CAD tools are needed which can generate the configuration bits for the SRAM cells of the FPGAs. Usually the circuit description is provided using Verilog, VHDL, SystemC, or other higher level descriptions. The CAD tools for the FPGAs read this input and output a configuration file for programming the FPGA. Fig. 2.7 shows the basic CAD flow for implementing a digital circuit/system on FPGAs [1]. The CAD flow has three main tasks: Synthesis, placement and routing. In the following sections synthesis, placement and routing for FPGAs are explained. Since VPR and T-Vpack have been used in this work, the discussion will be kept in context of these CAD tools. Almost all of the commercial FPGA CAD flows perform the same basic functions of synthesis, placement and routing.

Figure 2.8: Synthesis procedure for FPGAs

#### 2.3.1 Synthesis

The synthesis of a netlist involves conversion of a circuit description, usually in hardware description language (HDL), into a netlist of basic gates. This netlist of basic gates is then converted into a netlist of FPGA logic blocks. Fig. 2.8 shows the steps involved in the synthesis of a circuit description into a netlist of logic blocks.

Technology independent logic optimization involves the removal of redundant logic and simplification of the logic [9, 10]. The optimized netlist is then mapped to look-up tables, which is a process of identifying the logic gates that would go into a LUT [11]. The final step of the synthesis procedure is the clustering of the LUTs and flip-flops (for sequential logic) into logic blocks. The goal here is usually to minimize the number of logic blocks and/or minimize the delay. The work in [12] used a measure of closeness of LUTs to pack them into a cluster to form a logic block.

The work in [1] uses a timing driven logic block packing tool, called T-VPack. The tool targets packing the BLEs into a cluster shown in Fig. 2.5. It needs the parameters such as number of BLEs per cluster, number of inputs per cluster, size of the LUTs, and number of clocks per cluster. The first stage of the packing procedure simply forms the BLEs by packing a register and a LUT together. Initially the packing procedure packs the BLEs greedily into a cluster, followed by a hill climbing phase if the greedy phase is not able to fill the cluster completely.

To enable a timing driven packing, it is necessary to get an estimate of delays through various paths of the netlist. To enable this computation three types of delays are modeled: delay through a BLE, LogicDelay, delay between blocks in the same cluster, IntraClusterConnectionDelay, and the delay between blocks in different clusters, InterClusterConnectionDelay. The values for these are set as 0.1, 0.1 and 1.0 for LogicDelay, IntraClusterConnectionDelay and InterClusterConnectionDelay, respectively. The InterClusterConnectionDelay cannot be determined until the circuit has been implemented on the FPGA. However, these values represent the correct trend of values, and the performance of T-Vpack is not very sensitive to the exact values. The criticality of a connection is defined as

$$ConnectionCriticality(i) = 1 - \frac{slack(i)}{MaxSlack}$$

(2.1)

where MaxSlack is the largest slack amongst all the connections in the circuit. A new cluster is created by selecting a seed BLE having the highest criticality amongst the un-clustered BLEs. After the seed BLE has been selected, an attraction function is used to determine the next un-clustered BLE, B, to be added to the current cluster C. The attraction function is given by:

$$Attraction(B) = \alpha.Criticality(B) + (1 - \alpha) \left[ \frac{Nets(B) \cap Nets(C)}{MaxNets} \right]$$

(2.2)

where the first term represents the timing part, and the second term represents the cost of nets shared between the current cluster and the BLE under consideration. Any value of  $\alpha$  between 0.4 and 0.8 gives good results. The computation of *Criticality* of a BLE is explained in [1] and also the tie-breaker mechanism used for the case when two or more BLEs have the same criticality. Essentially, the tie-breaker mechanism selects that BLE which reduces the length of the largest number of critical paths.

The hill-climbing phase tries to add more BLEs to the cluster in case it is not full. In this phase adding a BLE to a cluster is allowed even if it leads to more inputs required for the cluster than the maximum allowable. This is done because in some cases the BLE being added might have all its inputs from the BLEs in the current cluster and also might drive the inputs of some of the BLEs in the current cluster. In this case the number of inputs required for the cluster decreases by one. However, this hill climbing phase increases the logic utilization only by 1 - 2% in some of the circuits.

#### 2.3.2 Placement

The work in [1] developed the tool VPR for placement and routing. For placement the FPGA is considered as a set of legal discrete positions at which the logic blocks of the

synthesized netlist can be placed. For placement, the architecture descriptions needed by VPR are:

- 1. The number of logic block input and output pins.

- 2. The number of I/O pads that fit into one row or column of the FPGA.

- 3. The routing channel width (number of tracks in a routing channel).

The placement technique used in VPR is based on simulated annealing [13], which imitates the annealing process used to gradually cool a molten metal to produce high quality metal objects. The simulated annealing works by first starting with an initial random placement by placing the logic blocks randomly on the available locations in the FPGA. The placement then proceeds by making a large number of moves to improve the placement. This is done by selecting a logic block randomly and its new location also randomly. This would produce a change in the cost function, and if the cost function improves, the move is always accepted. However, if the cost function worsens, there is still some probability of acceptance of the move. The probability of acceptance is given by  $e^{-\Delta C/T}$ , where  $\Delta C$  is the change in the cost function and the goal is to decrease the cost function. The T is the temperature parameter and controls the probability of acceptance of the moves which worsen the placement. The temperature is initially set to a high value so that at the beginning of the annealing, virtually all the moves are accepted. The temperature is gradually decreased as the placement improves, such that finally the probability of accepting a bad move is almost negligible. The flexibility of accepting bad moves allows the simulated annealing schedule to overcome the local minima in the cost function.

The VPR sets the initial temperature in the same way as in [14]. The number of moves attempted at each temperature is done as in [15]. It is set to

$$MovesPerTemperature = InnerNum.(N_{blocks})^{4/3}$$

(2.3)

where the default value of *InnerNum* is 10, and  $N_{blocks}$  is the number of logic blocks in the netlist. The fraction of moves accepted is kept close to 0.44 for as long as possible, as it yields better results [15]. However, VPR uses a new method of updating the temperature. The VPR computes the new temperature as  $T_{new} = \gamma T_{old}$ , where the value of  $\gamma$  depends on the fraction of moves accepted at  $T_{old}$ . The idea is to spend maximum time near the temperatures at which large improvements in placement occur. The annealing procedure is not very sensitive to the exact value of  $\gamma$ , if it has the right form,  $\gamma$  is close to 1 if the fraction of moves accepted is close to 0.44, whereas  $\gamma$  is small if the fraction of moves accepted is close to 0.44, whereas  $\gamma$  is small if the fraction of moves accepted is close to 0.44.

is explained in detail in [16]. The cost function for the timing driven placement developed in [16] is given by

$$\Delta C = \lambda \cdot \frac{\Delta TimingCost}{PreviousTimingCost} + (1 - \lambda) \cdot \frac{\Delta WiringCost}{PreviousWiringCost}$$

(2.4)

where  $\triangle TimingCost$  and  $\triangle WiringCost$  represent the change in the timing cost and the change in the wiring cost, respectively, due to a move. The simulated annealing procedure is terminated when

$$T < \epsilon. \frac{Cost}{N_{nets}} \tag{2.5}$$

where  $N_{nets}$  is the total number of nets in the circuit and the value of  $\epsilon$  is set as 0.005.

#### 2.3.3 Routing

The routing of the placed netlist, essentially, determines the switches that need to be turned on in the routing resources of the FPGA. The routing algorithm in VPR is based on the Pathfinder algorithm proposed in [17]. The Pathfinder repeatedly rips-up and re-routes every net in the circuit until all congestion is resolved. One routing iteration involves ripping-up and re-routing every net in the circuit. The first routing iteration routes for minimum delay, even if it leads to congestion, or overuse of routing resources. To remove this overuse another routing iteration is performed. The cost of overusing a routing resource is increased after every iteration. This improves the chance of resolving the congestion. At the end of each routing iteration all the nets are completely routed, although with some congestion. Based on this routing, timing analysis can be done to compute the critical path and also the slack of each source sink connection. The timing driven router uses an Elmore delay model to compute the delays of all the connections. The criticality of a connection beteen source of net i and one of its sink j is computed as follows:

$$Crit(i,j) = max\left(\left[MaxCrit - \frac{slack(i,j)}{D_{max}}\right]^{\eta}, 0\right)$$

(2.6)

where slack(i, j) is the slack available to the connection and  $D_{max}$  is the delay of the critical path. MaxCrit and  $\eta$  are the parameters which determine how the slack impacts the congestion delay trade-off in the cost function. In VPR  $\eta$  is set to 1 and MaxCrit is set to 0.99.

The VPR creates a routing resource graph to describe the FPGA architecture and connectivity information. The wire and the logic block pins of the FPGA are represented as nodes in the routing resource graph, and the switches are represented as directed edges in the graph. This routing resource graph is used to perform the routing.

The routing of a net is done by starting with a single node in the routing resource graph, corresponding to the source of the net. A wave expansion algorithm is invoked (k-1) times to connect the source to each of the net's (k-1) sinks, in order of the criticality of the sinks, the most critical sink being the first. The cost for using a node n during this expansion is given by:

$$Cost(n) = Crit(i, j).delay(n, topology) + [1 - Crit(i, j)].b(n).h(n).p(n)$$

(2.7)

where b(n), h(n) and p(n) are the base cost, historical congestion, and present congestion as explained in [1]. This procedure is repeated for each of the nets to get the complete routing.

## 2.4 VPR and T-VPack

The CAD tools used in this work are VPR, for placement and routing, and T-VPack for clustering of the BLEs [1]. VPR is invoked on the command line as follows [18]

$$vpr netlist.net architecture.arch placement.p routing.r [-options]$$

(2.8)

where *netlist.net* is the circuit description providing the information about the connectivity of the logic blocks, *architecture.arch* is the architecture file which describes the architectural parameters of the FPGA. The output of the final placement is written in *placement.p*, or, if the circuit is only being routed, the placement information is read from the file *placement.p*. The final routing information is written in *routing.p*. VPR has two basic modes of operation. In the first mode, VPR places a circuit on the FPGA and routes it for minimum routing channel width. In the other mode, when the user specifies the routing channel width, VPR attempts to route the circuit only once and if it is un-routable it simply aborts, reporting that the circuit is un-routable. The VPR also provides graphics which shows the actual placement and routing of the logic blocks, along with the routing switches.

T-VPack reads a netlist in the *blif* (Berkeley Logic Interchange Format) format having look-up tables (LUTs) and flip-flops (FFs) and packs these into logic blocks. The output of the T-Vpack is in the *.net* format, which is a netlist of logic blocks. T-VPack is invoked on the command line by

$$t - vpack input.blif output.net [-options]$$

(2.9)

Figure 2.9: VPR CAD flow

where options are used to specify the size of the LUTs, cluster size, inputs per cluster and various optimization options.

The complete VPR CAD flow is shown in Fig. 2.9. SIS [19] is used for logic optimization of the circuit. FlowMap [11] is used for technology-mapping to 4-LUTs and flip-flops. FlowMap produces an output in the *.blif* format. T-VPack packs the netlist into logic blocks and produces an output in the *.net* format. VPR is then used for the placement and routing of the netlist. Other logic optimizers and technology mappers, instead of SIS and FlowMap can also be used in this CAD flow.

## Chapter 3

## **Background and Related Work**

## 3.1 Introduction

The parameter variations affect the performance and the reliability of a circuit, and traditionally guard-banding has been used by providing an excess of safety margin for circuit delay and power. This is done to ensure that the worst case condition in the variations of process, voltage and temperature (PVT) are satisfied. However, with too many process corners it becomes extremely difficult to determine the actual worst case corner, resulting in either too pessimistic or too optimistic designs. Further, designing at worst case corner severely limits the achievable performance-cost trade-off for the circuit.

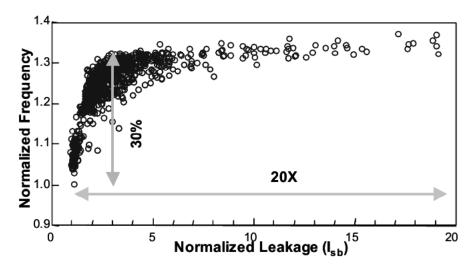

The variability also results in an increased cost of manufacturing because the chips with lower performance are discarded. The 2006 International Technology Roadmap for Semiconductor (ITRS) identifies the variability as one of the key difficult challenges in the scaled technologies. Fig. 3.1 shows the variation in leakage and frequency of microprocessors in a wafer. It shows that for a 30% variation in frequency a 20X variation in leakage is observed.

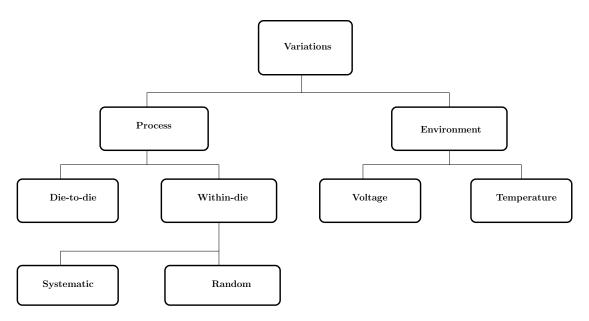

## **3.2** Classification of parameter variations

The parameter variations can be broadly classified into process and environment variations. The process variations relate to all the physical variations caused during the manufacturing process and/or through aging, whereas the environment variations relate to the variations in the operating environment of the chip. Fig. 3.2 shows a general classification of the parameter variations. Although the process parameter variations would in general affect the voltage and temperature variations, the figure does not show that in order to simplify the

Figure 3.1: Variation in Timing and Leakage [2]

depiction. A detailed figure showing the interaction between process parameters variations and environment variations and their impact on power and timing is shown later in this chapter.

#### 3.2.1 Process variations

The process variations can be classified as die-to-die variations and within-die variations. The die-to-die variations have their origin in lot-to-lot variations, wafer-to-wafer variations and within wafer variations. The die-to-die variations impact the parameters in such a way that the values of the parameters remain the same for all the devices on a single die, but vary across different instances of the chip. Within-die variations cause the parameters to vary across a single die. The systematic variations arise from such phenomena that has a predictable behavior. These variations arise from phenomena such as *Optical Proximity* Effect (OPC) and Chemical Mechanical Polishing (CMP). Therefore, theoretically these variations can be modeled and accounted for, by using deterministic analysis. However, since the layout is known at a later design stage and also the modeling is too complicated for the deterministic analysis, it is advantageous to model these variations statistically. The random variations arise from the truly random processes and for these parameters only statistical behavior can be modeled. These variations thus need to be modeled through random variables during the design phase. These random variations can be either independent for each device or can exhibit a spatial correlation. A further classification of the process variations based on their characteristics is as follows [20].

• Source: This relates to the variations arising from the sources such as polishing,

Figure 3.2: A general classification of the parameter variations

lithography, resist, etching, and doping. The non-uniform layout density results in a non-uniform dielectric thickness across the die, after the CMP process. The denser parts of the chip slows down the polishing resulting in the part getting more polished than the other parts. Smaller feature sizes have made lithography variations become more prominent. Also, the stepper lens heating, uneven lens focusing, and aberration lead to variations. The resist coating is non-uniform at the edges due to surface tension and leads to thickness variations. After resist, the etching causes variations due to uneven etching power and density. Since the number of dopant atoms have decreased with scaling, depositing these small number of dopant atoms uniformly for all the transistors is not possible and leads to variations in the dopant concentration.

- **Granularity:** This classifies the variations according to the die-to-die or the withindie variations.

- Manifestation: This refers to the systematic and the random variations.

- **Design impact:** The variations in the manufacturing process results in the variations in one or more design parameters such as the channel length, the threshold voltage and the device and the interconnect widths. Further, the channel length variations impact the threshold voltage of the transistors, the channel length variations caused due to factors such as wafer non-uniformity and lens focus and aberration. The width of the devices vary because of polishing or lithography issues.

• Aging: Most of the variations are static in nature, i.e., they do not change with the age of the die. However, some parameters might vary with age, such as the negative bias temperature instability (NBTI) effect in PMOS devices which cause the threshold voltage of the PMOS devices to increase with aging.

The process variations classified above typically manifest themselves as variations in the channel length, gate oxide thickness, and threshold voltage fluctuations. These process variations have been modeled in this work.

#### 3.2.2 Voltage Variations

The supply voltage,  $V_{DD}$  has been scaling with technology, but a lower limit is set due to reliability concerns. The switching activities and leakage currents in the different parts of the circuit lead to a current distribution in the power supply network which is not uniform. The non-uniformity of the current distributions and its variation with time leads to voltage drops in the supply network across the chip which is both spatial and temporal and in nature. The voltage drops occur due to resistance and inductance of the power supply network. These voltage variations affect the performance of a circuit, and for example, a  $10\% V_{DD}$  variation can cause a 20% variation in the delay [20].

### 3.2.3 Temperature Variations

Elevated temperatures occur in chips during the operation of a chip. The temperature increase is due to the heat generation as a result of power dissipation through switching and leakage. The temperature also gets affected by the ambient temperature of the chip. A higher ambient temperature would decrease the rate of heat flow from the chip to the outside atmosphere, resulting in temperature rise of the chip. The temperature variations are spatial and temporal in nature. The spatial temperature variations are caused due to higher power dissipation in certain parts of the chip as compared to the other parts, resulting in hot spots in the areas with higher power dissipation. The temporal temperature variations are caused due to different periods of activity. During the idle period the temperature of the chip would be lower than during the period in which it is active. The temperature variations not only affect the performance of the chip but can also lead to thermal runaways.

## **3.3** Modeling of process variations

The modeling of the process variations for computing the delay and the power has been investigated extensively. The process variations are random in nature, so they can be mathematically modeled as random variables. However, the main complexity in their behavior is that they exhibit spatial correlation across a chip. Ignoring these spatial correlations can lead to significant errors in analysis and design. Devices which are closer exhibit stronger correlation than the devices which are far apart. Early on, the analog designers used the Pelgrom model for computing the variation between different devices [21]. The Pelgrom model states that for a group of equally designed MOSFET devices, the variance (or mismatch) can be expressed as a function of their size and the distance between them. For example, the threshold voltage variance can be written as,

$$\sigma^2(V_{T0}) = \frac{A_{VT0}^2}{W.L} + S_{VT0}^2.D^2, \qquad (3.1)$$

where  $A_{VT0}$  and  $S_{VT0}$  are technology-dependent coefficients, W and L are the device dimensions, and D is the distance between the devices. Although the Pelgrom model can give a good insight into the nature of variations, it is difficult to scale it in for a design with large number of gates. In such a scenario it is important to account for the impact of multiple sources on a single location to analyze the overall effect of variations.

Two most popular methods for modeling spatially correlated process parameter variations are the *principal components based model*, and the *quad-tree model*. In the former, after obtaining the correlation information, Principal Component Analysis (PCA) is applied. The PCA is used to develop a set of uncorrelated random variables from a set of correlated random variables [22]. The quad-tree model proposed in [23], models the process variations by diving the chip into hierarchical levels and is adopted in this work. The two models are discussed in the following subsections.

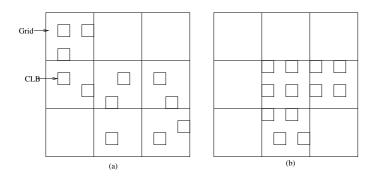

### 3.3.1 Principal Components Analysis (PCA) Model

In the PCA model the spatial correlation is modeled by dividing the chip into n grids, such that each grid is associated with a principal component. Each of the n principal components are independent normal random variables with zero mean and unit variance. The grid model for the spatial correlation is shown in Fig. 3.3. The spatial correlation matrix is based on distance, location, orientation and other factors, and would give a correlation value for each grid with all the grids on the chip.

The value of a process parameter, for example the channel length, of the gate i, is expressed as,

$$L_{g,i} = L_{nom,i} + \sum_{j} \alpha_{i,j} \Delta L_j, \qquad (3.2)$$

Figure 3.3: Grid Model for PCA

where  $\Delta L_j$  is the  $j^{th}$  component and  $\alpha_{i,j} = \sigma_i v_{i,j} \cdot \sqrt{\lambda_j}$ . The  $\sigma_i$  is the standard deviation for grid i,  $v_{ij}$  is the  $i^{th}$  element in the  $j^{th}$  eigenvector of the correlation matrix and  $\lambda_j$  is the  $j^{th}$  eigenvalue of the correlation matrix [22]. The sensitivity matrix, P, for the PCA model can be written as,

$$P = \begin{pmatrix} \alpha_{1,1} & \alpha_{1,2} & \alpha_{1,3} & \dots & \alpha_{1,m} \\ \alpha_{2,1} & \alpha_{2,2} & \alpha_{2,3} & \dots & \alpha_{2,m} \\ \alpha_{3,1} & \alpha_{3,2} & \alpha_{3,3} & \dots & \alpha_{3,m} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \alpha_{n,1} & \alpha_{n,2} & \alpha_{n,3} & \dots & \alpha_{n,m} \end{pmatrix}$$

(3.3)

where each grid of the Fig. 3.3 is associated with one column and one row. Once the spatially correlated parameters have been decomposed into a set of independent principal components, any analysis can be easily performed.

#### 3.3.2 Quad-Tree Model

In this work, the quad-tree model is selected for modeling the process parameter variations. The process parameters, such as the gate lengths of two closely placed transistors have almost identical variation, which means that one random variable can be used for modeling the gate lengths of both transistors. However, the gate lengths of the transistors which are far apart need to be modeled with different random variables with spatial correlation. The quad-tree model accounts for spatial correlation through modeling the variations at several hierarchical levels.

A process parameter, such as channel length is represented as sum of its nominal value  $L_{nom}$ , inter-die variation  $\Delta L_{inter}$ , intra-die variation  $\Delta L_{intra}$ , and random variation

Figure 3.4: Layer model for representing the spatially correlated process parameters

$\triangle L_{random}$ .

$$L_{eff} = L_{nom} + \triangle L_{inter} + \triangle L_{intra} + \triangle L_{random}.$$

(3.4)

In the quad-tree model a process parameter for the complete chip is modeled at several hierarchical levels. The entire chip is divided into several levels with each level modeling a component of the total variation. Starting from the  $0^{th}$  level, each level ( $i^{th}$  level) has  $4^{i}$  equal sized partitions as denoted in Fig. 3.4. Finally, a random level with only one grid becomes the last level in the model. For each process parameter, there is a random variable associated with each of the partitions of each level. All such random variables are independent and identically distributed. To model the process variations for a logic gate, the partition in which the logic gate lies in each of the levels is determined. These variations are then added to obtain the total variation in a process parameter for a logic gate. The spatial correlation of a process parameter between two logic gates is accounted for, by the number of common partitions they share across the different levels. Fig. 3.4 illustrates the modeling of the variations for a chip with three levels. The level 0 represents the inter-die variations because it is common for all the logic gates of the chip. Levels 1 and 2 represent the intra-die variations. Consider a logic gate lying at the top right side of the die, i.e., at the grid location (3,0) in the level 2, and another logic gate lying adjacent to it at the grid location (2,0) in the level 2. The total channel lengths for these logic gates are expressed:

$$L_{eff_{gate1}} = L_{nom} + L_{eff_{0,(0,0)}} + L_{eff_{1,(2,0)}}$$

(3.5)

$$+ L_{eff_{2,(3,0)}} + L_{random}$$

$$L_{eff_{aate2}} = L_{nom} + L_{eff_{0,(0,0)}} + L_{eff_{1,(2,0)}}$$

(3.6)

$$F_{gate2} = L_{nom} + L_{eff_{1,(2,0)}} + L_{eff_{1,(2,0)}} + L_{eff_{2,(2,0)}} + L_{random},$$

(0.0)

where  $L_{eff_{i,(j,k)}}$  represents the random variable for the channel length associated with the level *i* and the partition (j, k).  $L_{random}$  represents the independent random variation. It can be seen that the two logic gates share the [0,(0,0)] and the [1,(2,0)] partitions. This sharing incorporates the spatial correlation in the model, implying that more the number of grids shared, higher is the corresponding spatial correlation. Increasing the number of levels for modeling can improve the accuracy of the model at the expense of the run time. Since the random variables associated with the different partitions are independent within and across the levels, the computation of the means and the variances of the leakage or delay are easier. The total variation of a process parameter is distributed across the different levels in accordance with their spatial correlation. Specifically, the total variance for a process parameter is written as  $\sigma^2 = \sum_{i=0}^{n} \sigma_i^2$ , where *n* is the total number of levels and  $\sigma_i$  is the standard deviation of the corresponding random variable for the level *i*. The quad-tree model is verified by the actual measurements in [24].

## 3.4 Yield of a design

The yield of a design is defined as the number of chips that meet the target performance criterion. The performance parameter is typically the circuit delay or the power dissipation (assuming that the functionality of the circuit is correct). Under parameter variations, the performance characteristics no longer remain deterministic, but are modeled as random variables. The yield of a design for a performance criterion is defined as the CDF of the random variable representing the performance characteristic. For example, given a PDF,  $f(T_d)$ , of the circuit delay,  $T_d$ , the yield at the target delay is calculated by computing the CDF,  $F(T_d)$ , and is given by the equation 3.7.

$$Yield = F(T_d < TargetDelay) = \int_0^{TargetDelay} f(T_d)dT_d$$

(3.7)

The yield point represents the probability of a chip meeting the target delay. Fig. 3.5 shows the yield point for a target delay of 8.3ns for a circuit implemented on an FPGA. In a manufacturing process fabricating a large volume of chips, 90% of the chips will meet the target delay.

Figure 3.5: CDF of a circuit delay to determine the yield

Figure 3.6: PDF of a circuit delay and speed binning applied to improve the yield

Another technique commonly used for improving the yield of a design is *binning*, which is worthwhile to point out in this discussion. An example of speed binning is shown in Fig. 3.6. The figure shows the PDF of the delay of a circuit implemented on an FPGA. The PDF is divided into three bins, the high speed bin for chips with lower circuit delays, the medium speed bin for chips with higher circuit delays, and the low speed bin for chips with highest circuit delay. Any chip having a delay larger than the cut-off delay is discarded, leading to yield loss. The speed binning is done to improve the profitability from selling the chips. This is done by selling the chips in different bins at different prices, with the chips from the lowest speed bin being sold at the least price, and the chips from the higher speed bins being sold at a higher price.

## 3.5 Managing Variability in ASICs

#### 3.5.1 Process Variations

Traditionally, process corners have been used for analyzing designs to meet the targeted performance, power and other design considerations at the best, nominal and worst case process corners. However, this may lead to pessimistic or optimistic designs. Moreover, it is very difficult to determine whether a particular process corner is indeed a best, nominal or worst case corner, because of the significant increase in the number of varying process parameters and operating conditions with technology scaling. Therefore, to design VLSI circuits under process variations, statistical techniques need to be adopted.