# Tunable Superconducting Microwave Filters

by

Paul Laforge

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2010

©Paul Laforge 2010

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

Paul Laforge

#### Abstract

Adaptive microwave systems can benefit from the use of low loss tunable microwave filters. Realizing these tunable filters that show low loss characteristics can be very challenging. The proper materials, tuning elements, and filter designs need to be considered when creating a low loss tunable filter. The integration of low loss microelectromechanical systems (MEMS) and superconducting circuits is one method of achieving these types of tunable filters. The thesis introduces new multi-layer low temperature superconducting (LTS) filters and diplexers and novel topologies for tunable filters and switched multiplexers. An efficient method of designing such filters is proposed. A fabrication process to monolithically integrate MEMS devices with high temperature superconducting (HTS) circuits is also investigated in this thesis.

The reflected group delay method, usually used for filter tuning, is further developed for use in designing microwave filters. It is advantageous in the design of filters to have electromagnetic simulation results that will correlate well to the fabricated microwave filters. A correction factor is presented for use with the reflected group delay method so the group delay needs to be matched to the appropriate value at the center frequency of the filter and be symmetric about the center frequency of the filter. As demonstrated with an ideal lumped element filter, the group delay method can be implemented when a closed form expression for the circuit is not known. An 8-pole HTS filter design and an 8-pole multi-layer LTS filter design demonstrate the use of the reflected group delay method.

Low temperature superconducting filters, couplers and diplexers are designed and fabricated using a multilayer niobium fabrication process traditionally used for superconducting digital microelectronics. The feasibility of realizing highly miniaturized microwave niobium devices allows for the integration of superconducting digital microelectronics circuits and analog microwave devices on a single chip. Microwave devices such as bandpass filters, lowpass filters, bandstop filters, quadrature hybrids, and resistive loads are all demonstrated experimentally. New tunable filter designs are presented that can make use of MEMS switches. A manifold-coupled switched multiplexer that allows for 2<sup>N</sup> possible states is presented. The tunable multiplexer has N filters connected to two manifolds and has embedded switches, which detune certain resonators within the filters to switch between ON and OFF states for each channel. The new concept is demonstrated with a diplexer design and two 3-pole coplanar filters. The concept is further developed through test results of a fabricated HTS triplexer and electromagnetic simulations to demonstrate a superconducting manifold-coupled switched triplexer. Another filter design is presented that makes use of switches placed only on the resonators of the filters. This filter design has N possible states and the absolute bandwidth can be kept constant for all N states.

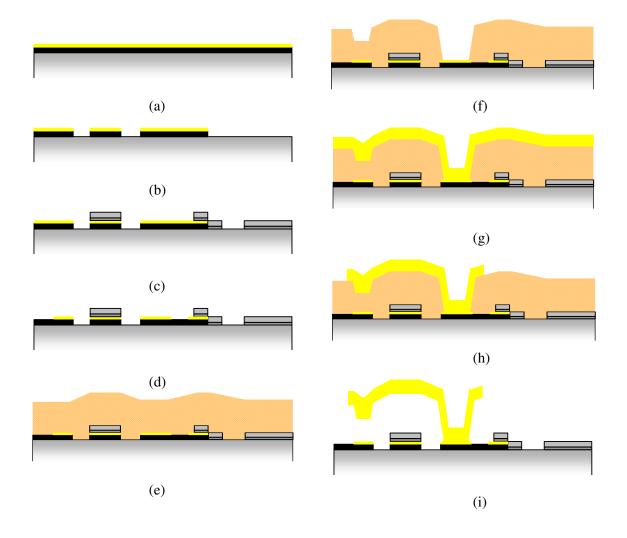

Finally, the integration of HTS circuits and MEMS devices is investigated to realize low loss tunable microwave filters. The hybrid integration is first performed through the integration of an HTS microstrip filter and commercially available RF MEMS switches. A fabrication process to monolithically integrate MEMS devices and high temperature superconducting circuits is then investigated. The fabrication process includes a titanium tungsten layer, which acts as both a resistive layer and an adhesion for the dielectric layer, an amorphous silicon dielectric layer, a photoresist sacrificial layer, and the top gold layer. The fabrication process is built up on a wafer with a thin film of a high temperature superconducting material covered with a thin film of gold. Several processes are tested to ensure that the superconducting properties of the thin film are not affected during the MEMS fabrication process.

#### Acknowledgements

I would like to thank my supervisors Dr. Raafat Mansour and Dr. Ming Yu for their guidance during my PhD studies. I would especially like to thank Dr. Raafat Mansour for his support, knowledge, guidance and never ending enthusiasm and motivation throughout my graduate studies at the University of Waterloo.

The following people provided assistance during my studies, and their support is much appreciated. First, I would like to thank Bill Jolley for assembling and tuning filters and for sharing his knowledge of filter fabrication and cryogenic testing. I would like to thank Roger Grant for the dicing of many substrates. I would like to thank Reena Al-Dahleh for sharing her expertise in clean room fabrication and for the many interesting discussions we shared about all aspects of life. I would like to thank Siamak Fouladi for assistance in taking SEM images, testing devices and performing fabrication processes. I would like to thank Winter Yan for sharing his expertise in MEMS designs and MEMS fabrication, and Tania Oogarah for help with fabrication processes, especially those involving HTS materials. Finally, I would like to thank Maher Bakri-Kassem, Eric Chan, Arash Fomani, Sara Attar, Sormeh Setoodeh, and Haig Atikian for their assistance and knowledge in the fabrication and/or testing of devices.

| List of Figures                                                        | ix  |

|------------------------------------------------------------------------|-----|

| List of Tables                                                         | xvi |

| Chapter 1 Introduction                                                 | 1   |

| 1.1 Motivation                                                         | 1   |

| 1.2 Objectives                                                         | 3   |

| 1.3 Thesis Outline                                                     | 4   |

| 1.4 Glossary of Terms                                                  | 4   |

| Chapter 2 Literature Survey                                            | 7   |

| 2.1 Tunable Filter Technologies                                        | 7   |

| 2.1.1 Active Components                                                | 7   |

| 2.1.2 Mechanical Methods of Tuning                                     | 10  |

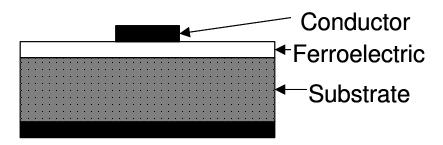

| 2.1.3 Ferroelectric Materials                                          | 18  |

| 2.1.4 Ferrite Materials                                                | 23  |

| 2.1.5 A Comparison of Technologies                                     | 24  |

| 2.2 Tunable Filters with Constant Bandwidth                            | 24  |

| 2.3 Fabrication of MEMS for Operation at Cryogenic Temperatures        | 27  |

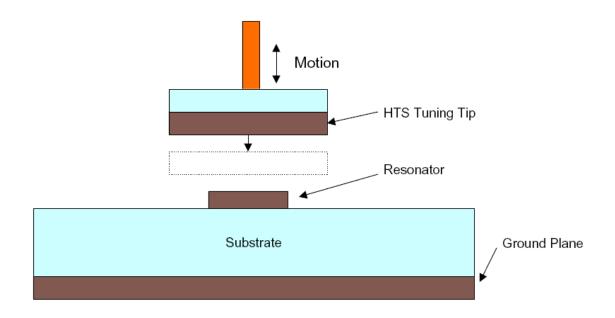

| 2.3.1 Integration of HTS Circuits and MEMS Devices                     | 27  |

| 2.3.2 Modeling of MEMS Devices at Cryogenic Temperatures               |     |

| 2.3.3 Niobium Based MEMS Devices                                       | 31  |

| Chapter 3 Superconducting Filter Design and Implementation             |     |

| 3.1 Reflected Group Delay Method of Designing Filters                  | 35  |

| 3.2 Design of a Lumped Element 8-Pole Filter Using a Circuit Simulator |     |

| 3.3 Design of an 8-Pole Lumped Element Superconducting Filter          | 42  |

| 3.4 Design of an 8-pole Microstrip HTS Filter                          | 46  |

| Chapter 4 Highly Miniaturized Low Temperature Superconducting Circuits | 51  |

| 4.1 Fabrication Process for Superconducting Filters                    | 53  |

| 4.2 Bandpass Filter Design and Measurements                            |     |

# **Table of Contents**

| 4.2.1 Coplanar Waveguide Lumped Element Filter Design and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 4.2.2 Microstrip Filter Design and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59                                                                          |

| 4.3 Quadrature Hybrid Design and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66                                                                          |

| 4.4 Diplexer Design and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69                                                                          |

| 4.5 Bandstop Filter with Low-Pass Filters as Impedance Inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71                                                                          |

| 4.5.1 Bandstop Filter Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                                          |

| 4.5.2 Low-Pass Filter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75                                                                          |

| 4.5.3 Bandstop Filter Design and Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 79                                                                          |

| Chapter 5 Tunable Filter Designs and the Integration of MEMS Devices and HTS Circ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | cuits.82                                                                    |

| 5.1 Manifold-Coupled Switched Multiplexers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |

| 5.1.1 Reconfigurable Diplexer and Filter Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 84                                                                          |

| 5.1.2 Diplexer and Filter EM Simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 5.1.3 Filter Bank Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |

| E O True able Crue anone deratione Trielouser                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                             |

| 5.2 Tunable Superconducting Triplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                             |

| 5.2.1 Triplexer Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 92                                                                          |

| 5.2.1 Triplexer Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92<br>93                                                                    |

| <ul><li>5.2.1 Triplexer Channels</li><li>5.2.2 Manifold-Coupled Switched Triplexer</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92<br>93<br>100                                                             |

| <ul><li>5.2.1 Triplexer Channels</li><li>5.2.2 Manifold-Coupled Switched Triplexer</li><li>5.2.3 Superconducting Reconfigurable Multiplexer</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 92<br>93<br>100                                                             |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                               | 92<br>93<br>100<br>104                                                      |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded</li> </ul>                                                                                                                                                                                                                                                                                                                                                             | 92<br>93<br>100<br>104                                                      |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded Switches</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | 92<br>93<br>100<br>104<br>105<br>109                                        |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded Switches</li> <li>5.3.2 Two State Filter Design and EM Simulations</li> </ul>                                                                                                                                                                                                                                                                                          | 92<br>93<br>100<br>104<br>105<br>109<br>luctors                             |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded</li> <li>Switches</li> <li>5.3.2 Two State Filter Design and EM Simulations</li> <li>5.4 Hybrid Integration and Monolithic Integration of High Temperature Supercond</li> </ul>                                                                                                                                                                                        | 92<br>93<br>100<br>104<br>105<br>109<br>ductors<br>114                      |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded</li> <li>Switches</li> <li>5.3.2 Two State Filter Design and EM Simulations</li> <li>5.4 Hybrid Integration and Monolithic Integration of High Temperature Supercond</li> <li>and Micro-Electro-Mechanical Systems</li> </ul>                                                                                                                                          | 92<br>93<br>100<br>104<br>105<br>109<br>luctors<br>114<br>114               |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded</li> <li>Switches</li> <li>5.3.2 Two State Filter Design and EM Simulations</li> <li>5.4 Hybrid Integration and Monolithic Integration of High Temperature Supercond</li> <li>and Micro-Electro-Mechanical Systems</li> <li>5.4.1 Hybrid Integration of HTS Filters and MEMS Switches</li> </ul>                                                                       | 92<br>93<br>100<br>104<br>105<br>109<br>luctors<br>114<br>114<br>117        |

| <ul> <li>5.2.1 Triplexer Channels</li> <li>5.2.2 Manifold-Coupled Switched Triplexer.</li> <li>5.2.3 Superconducting Reconfigurable Multiplexer</li> <li>5.3 Tunable Filters with Constant Absolute Bandwidth using Embedded Switches .</li> <li>5.3.1 Tuning the Input Coupling and Inter-Resonator Coupling with Embedded Switches</li> <li>5.3.2 Two State Filter Design and EM Simulations</li> <li>5.4 Hybrid Integration and Monolithic Integration of High Temperature Supercond and Micro-Electro-Mechanical Systems</li> <li>5.4.1 Hybrid Integration of HTS Filters and MEMS Switches.</li> <li>5.4.2 Fabrication Process for the Monolithic Integration of HTS and MEMS .</li> </ul> | 92<br>93<br>100<br>104<br>105<br>109<br>luctors<br>114<br>114<br>117<br>122 |

| 6.2 Future Work                                                                   | . 127 |

|-----------------------------------------------------------------------------------|-------|

| Appendix A Fabrication Process for the Monolithic Integration of High Temperature |       |

| Superconductors and MEMS Devices                                                  | . 129 |

| Bibliography                                                                      | . 136 |

# List of Figures

| Etc. 0.15. The lowest of the tought two sets are being a such filles with constant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

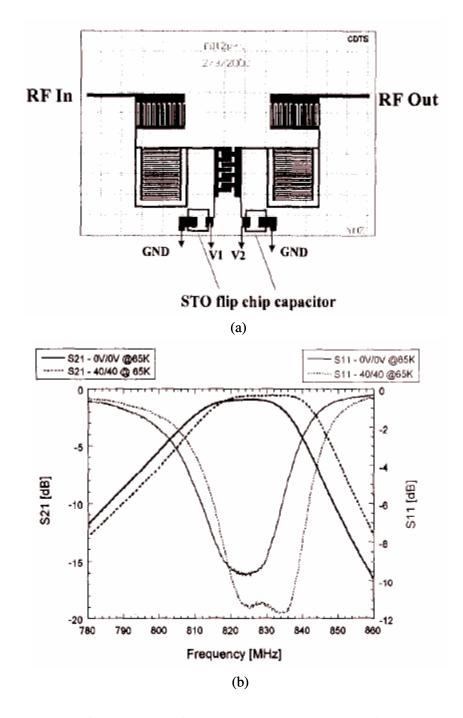

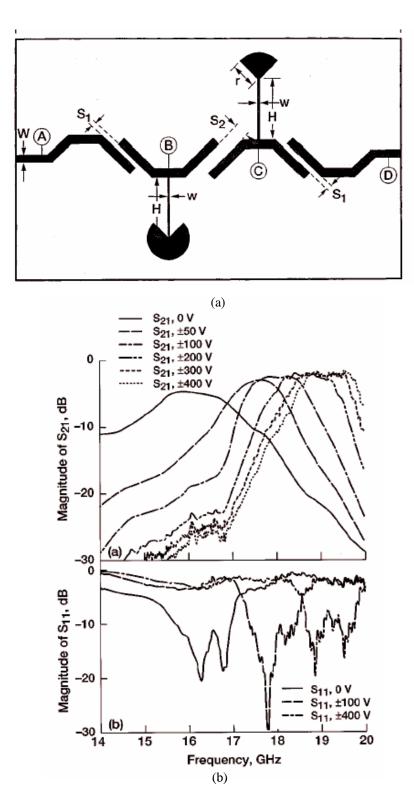

| Fig. 2-15: The layout of the tunable two pole zig-zag hairpin-comb filter with constant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| bandwidth [38]26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Fig. 2-16: Superposition of the measured results of the two pole zig-zag hairpin-comb filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| for center frequencies of 0.498, 0.555, 0.634 0.754, and 0.948 GHz [38]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

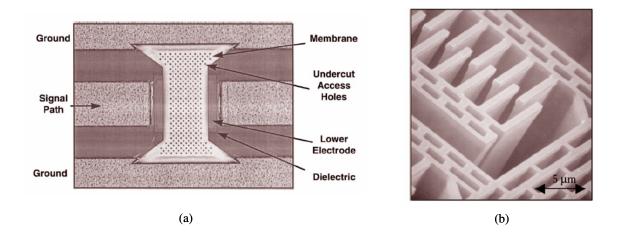

| Fig. 2-17: MEMS shunt switch on an HTS transmission line [40]27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Fig. 2-18: Fabricated shunt switch on a coplanar waveguide transmission line [41]29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

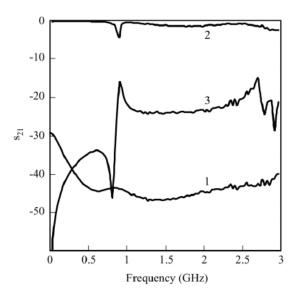

| Fig. 2-19: Measured $S_{21}$ results of the shunt switch 1) T = 300K 2) T=14K with the switch in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| the "up" position 3) T = 14K with the switch in the down position [41]29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

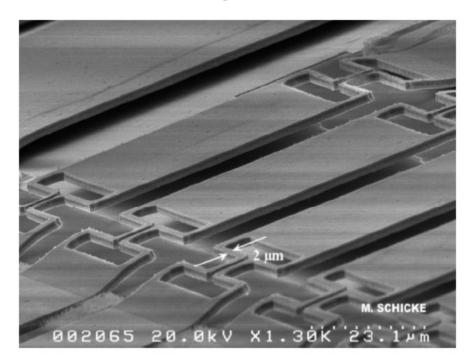

| Fig. 2-20: An image of the fabricated niobium based MEMS capacitors [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 3-1: a) An image of the 8-pole lumped element superconducting filter to be described in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| section 3.3 and b) an image of the fabricated 8-pole superconducting microstrip filter to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| be described in section 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

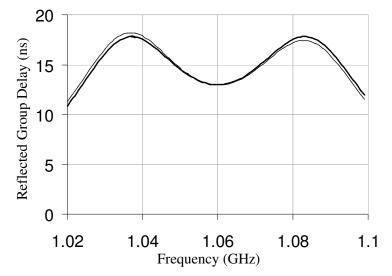

| Fig. 3-2: The reflected group delay response, $\Gamma_d(f)$ , (thin line) and symmetric reflected group                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| delay response, $\Gamma_{d \text{ symmetric}}(f)$ , (bold line) of the first two resonators of an 8-pole filter38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

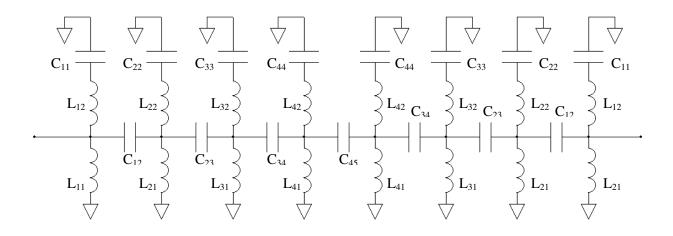

| Fig. 3-3: Image of the lumped element 8-pole filter used to demonstrate the design process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Fig. 3-3: Image of the lumped element 8-pole filter used to demonstrate the design process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

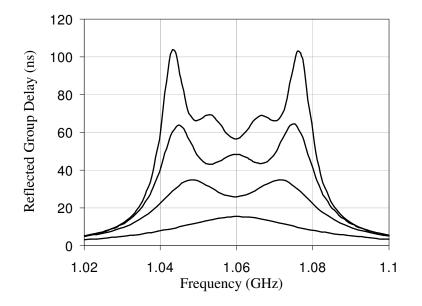

| 39<br>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 39<br>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped<br>element filter design. The response with the lowest value of group delay and one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 39<br>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped<br>element filter design. The response with the lowest value of group delay and one<br>maximum at 1.06 GHz is for the design of the first resonator. The response for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 39<br>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at <i>f</i> <sub>0</sub> 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

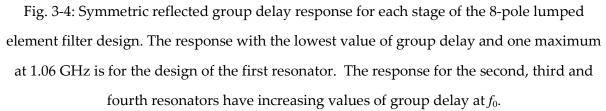

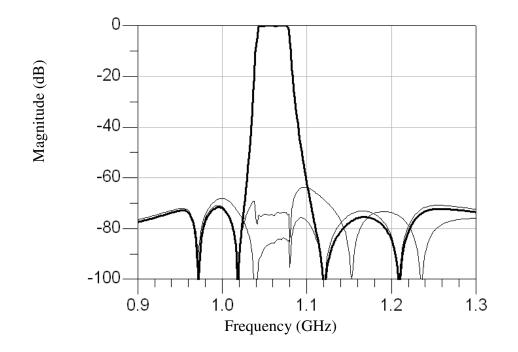

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at <i>f</i><sub>0</sub>40</li> <li>Fig. 3-5: Circuit simulation results of the 8-pole lumped element filter designed with the</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at <i>f</i><sub>0</sub>40</li> <li>Fig. 3-5: Circuit simulation results of the 8-pole lumped element filter designed with the reflected group delay method41</li> </ul>                                                                                                                                                                                                                                                                                                                            |

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at fo</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at <i>f</i><sub>0</sub>40</li> <li>Fig. 3-5: Circuit simulation results of the 8-pole lumped element filter designed with the reflected group delay method</li></ul>                                                                                                                                                                                                                                                                                                                               |

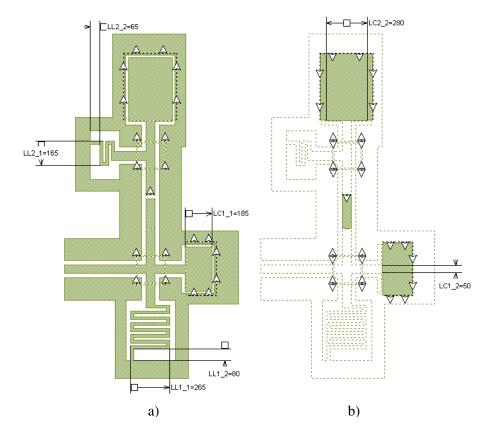

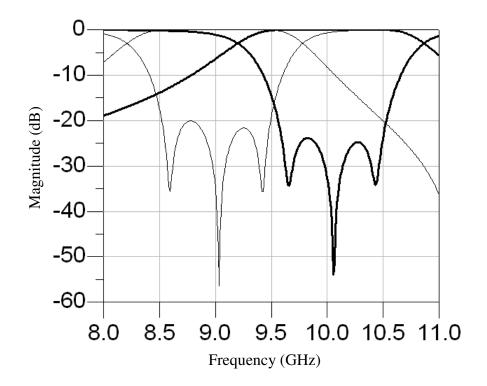

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at <i>f</i>040</li> <li>Fig. 3-5: Circuit simulation results of the 8-pole lumped element filter designed with the reflected group delay method.</li> <li>41</li> <li>Fig. 3-6: Image of a) the bottom metal layer and b) the top metal layer of the capacitors of the first two resonators during the design process.</li> <li>44</li> <li>Fig. 3-7: EM simulation results (bold line) and test results (thin line) of an initial design of</li> </ul>                                            |

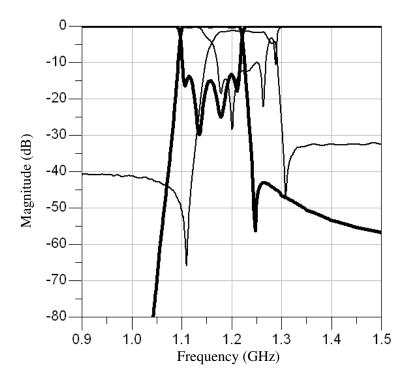

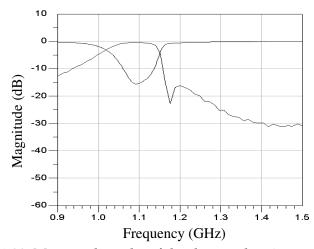

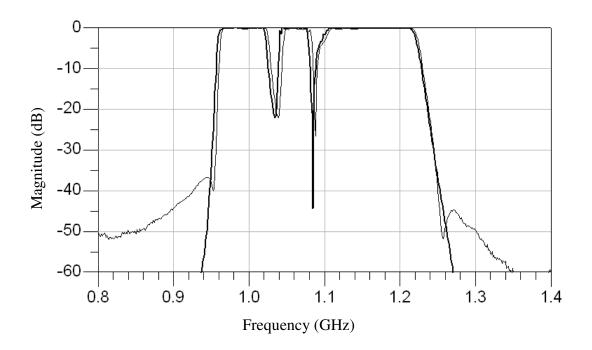

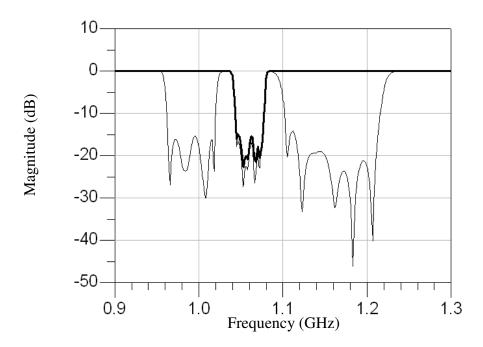

| <ul> <li>39</li> <li>Fig. 3-4: Symmetric reflected group delay response for each stage of the 8-pole lumped element filter design. The response with the lowest value of group delay and one maximum at 1.06 GHz is for the design of the first resonator. The response for the second, third and fourth resonators have increasing values of group delay at f040</li> <li>Fig. 3-5: Circuit simulation results of the 8-pole lumped element filter designed with the reflected group delay method.</li> <li>41</li> <li>Fig. 3-6: Image of a) the bottom metal layer and b) the top metal layer of the capacitors of the first two resonators during the design process.</li> <li>44</li> <li>Fig. 3-7: EM simulation results (bold line) and test results (thin line) of an initial design of the 8-pole lumped element superconducting filter.</li> </ul> |

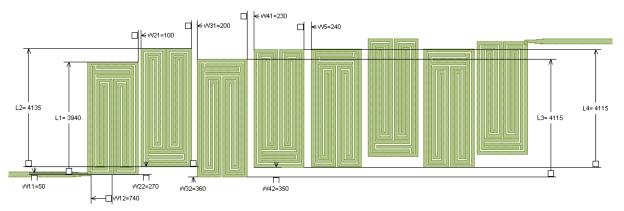

| Fig. 3-9: Layout with the final dimensions in $\mu m$ for the 8-pole HTS filter                   |

|---------------------------------------------------------------------------------------------------|

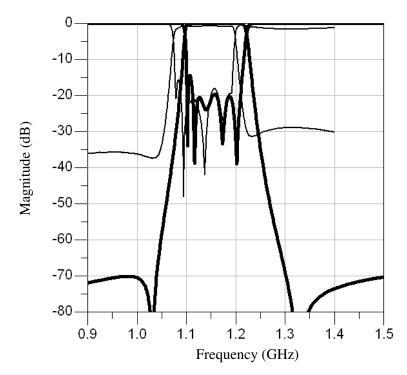

| Fig. 3-10: Lossless EM simulations (bold line) and measured results (thin line) of an initial     |

| design for the 8-pole high temperature superconducting filter                                     |

| Fig. 3-11: Final lossless EM simulation results for the 8-pole high temperature                   |

| superconducting filter                                                                            |

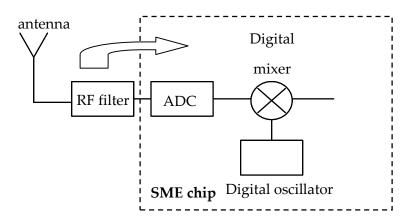

| Fig. 4-1: Architecture of the receiver of an SME radio                                            |

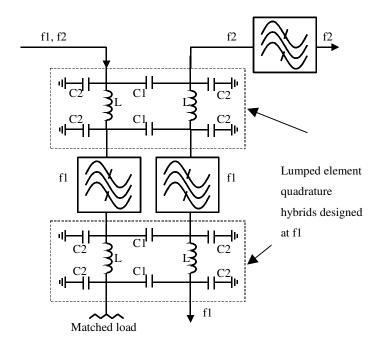

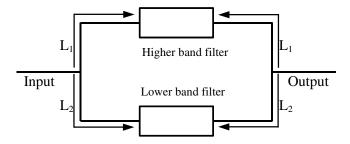

| Fig. 4-2: Lumped element hybrid-coupled diplexer architecture52                                   |

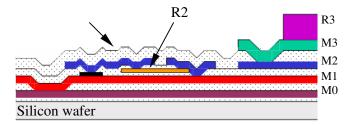

| Fig. 4-3: Cross-section of the HYPRES process54                                                   |

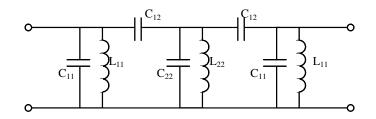

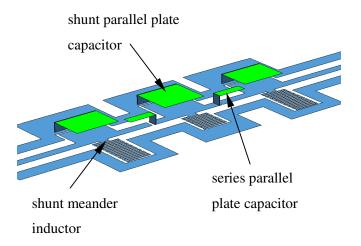

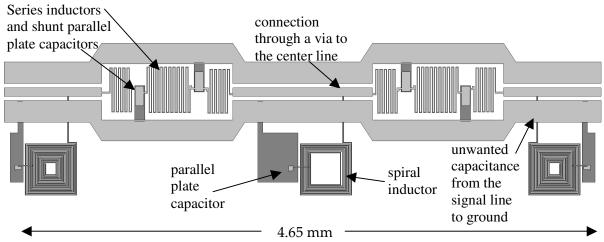

| Fig. 4-4: Circuit layout of the lumped element filter design55                                    |

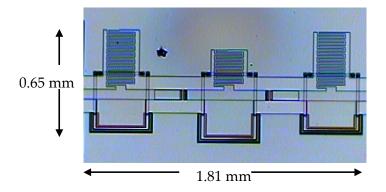

| Fig. 4-5: Image of the fabricated 3-pole lumped element coplanar waveguide filter56               |

| Fig. 4-6: An image of the fabricated multilayer superconducting lumped element filter56           |

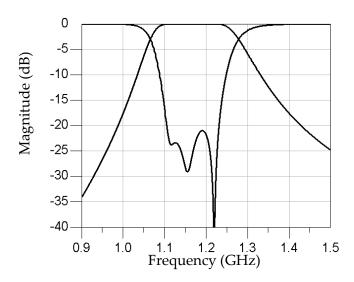

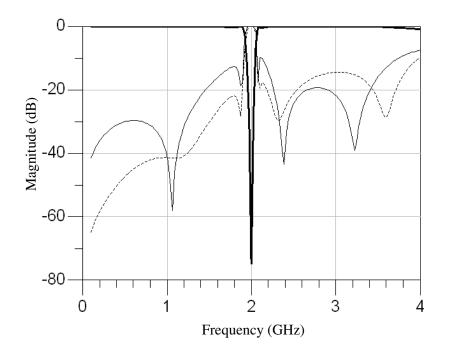

| Fig. 4-7: Lossless EM simulation response of the 3-pole lumped element filter                     |

| Fig. 4-8: Lossless EM simulation response of the lumped element filter with the estimated         |

| fabrication tolerance of ±20%58                                                                   |

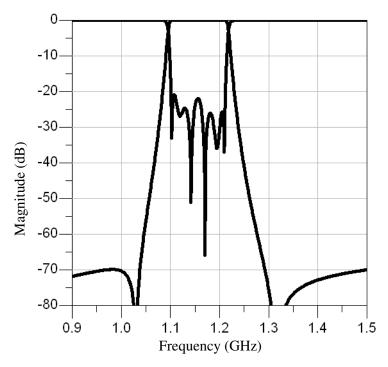

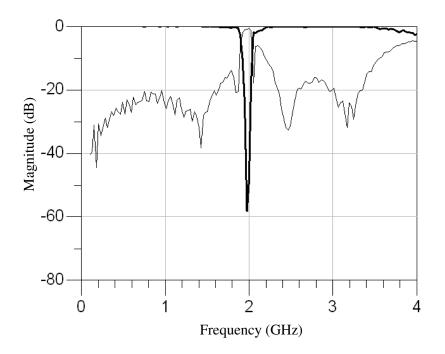

| Fig. 4-9: Measured response of the 3-pole lumped element filter                                   |

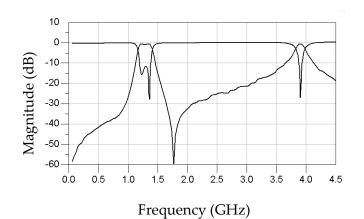

| Fig. 4-10: Wideband measured response of the 3-pole lumped element superconducting                |

| filter                                                                                            |

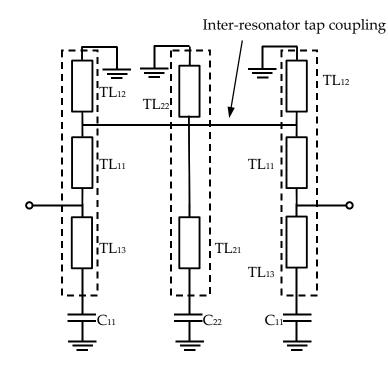

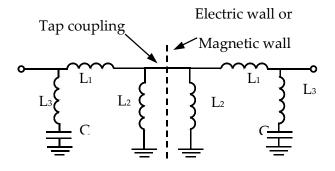

| Fig. 4-11: Circuit layout of a three pole microstrip filter with inter-resonator tap connections. |

|                                                                                                   |

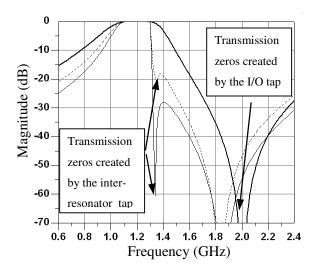

| Fig. 4-12: Circuit to determine the coupling coefficient between two resonators                   |

| Fig. 4-13: Insertion loss of simulated two-pole (solid bold line), three-pole (dashed line), and  |

| four-pole (solid thin line) filters61                                                             |

| Fig. 4-14: Simulated results of the 42.6% bandwidth filter using the proposed configuration.      |

|                                                                                                   |

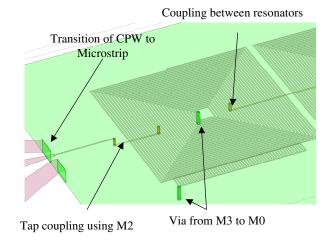

| Fig. 4-15: Image of the microstrip filter63                                                       |

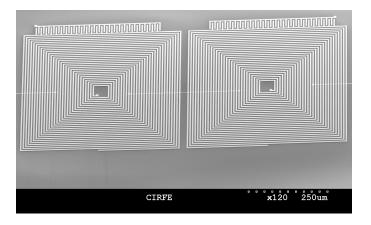

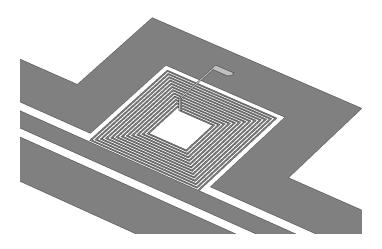

| Fig. 4-16: SEM image of the two-pole microstrip filter63                                          |

| Fig. 4-17: Image of the three-pole microstrip filter                                              |

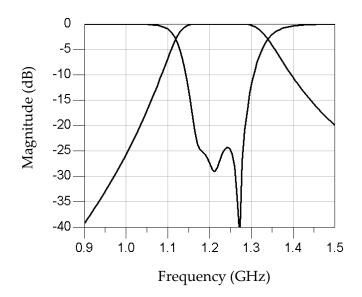

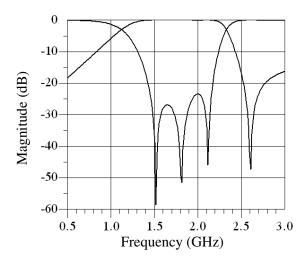

| Fig. 4-18: EM simulated results of the two-pole microstrip filter                                 |

| Fig. 4-19: Measured results of the two-pole microstrip filter                                                                                                                                                                                                                                                         |

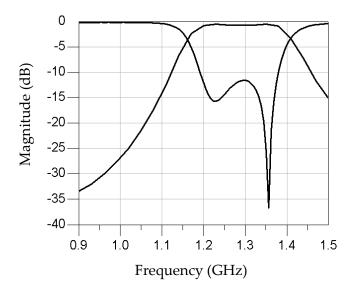

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4-20: Measured results of the three-pole microstrip filter                                                                                                                                                                                                                                                       |

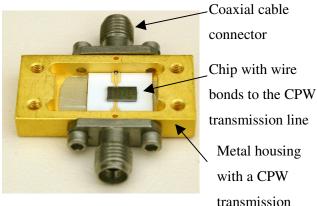

| Fig. 4-21: Image of the housing used to test the superconducting chip                                                                                                                                                                                                                                                 |

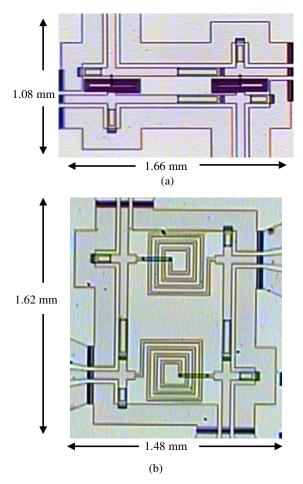

| Fig. 4-22: Image of the fabricated quadrature hybrids designed at a center frequency of (a)                                                                                                                                                                                                                           |

| 1.0 GHz and (b) 1.15 GHz67                                                                                                                                                                                                                                                                                            |

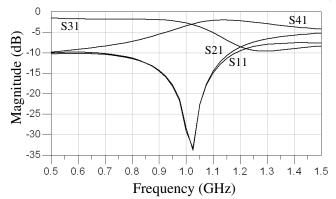

| Fig. 4-23: Measured response of the hybrid designed at 1.0 GHz68                                                                                                                                                                                                                                                      |

| Fig. 4-24: EM simulation response of the hybrid designed at 1.0 GHz68                                                                                                                                                                                                                                                 |

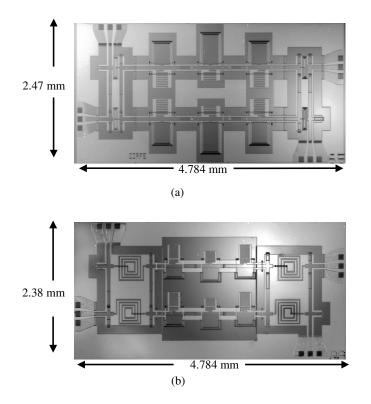

| Fig. 4-25: Images of the two channelizers designed at center frequency of (a) 1.0 GHz and at                                                                                                                                                                                                                          |

| (b) 1.15 GHz69                                                                                                                                                                                                                                                                                                        |

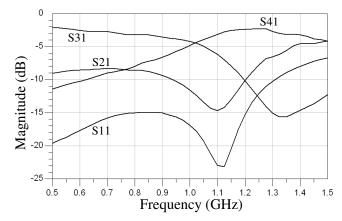

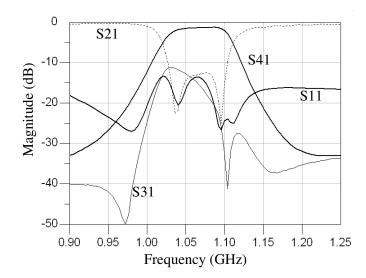

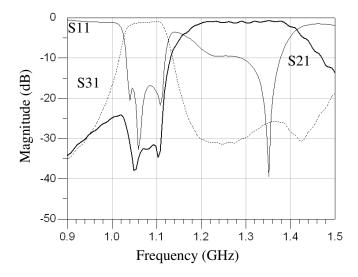

| Fig. 4-26: Measured results of the channelizer designed at 1.0 GHz70                                                                                                                                                                                                                                                  |

| Fig. 4-27: Measured response of the diplexer with the hybrid channelizer designed at 1.15                                                                                                                                                                                                                             |

| GHz and the filter designed at a center frequency 1.0 GHz at the channelizer output70                                                                                                                                                                                                                                 |

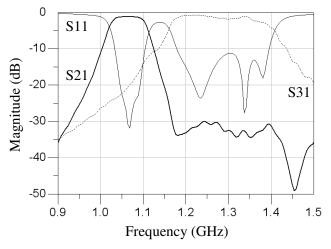

| Fig. 4-28: Measured response of the diplexer with hybrid channelizer designed at 1.0 GHz                                                                                                                                                                                                                              |

| and a filter designed at 1.15 GHz at the channelizer output71                                                                                                                                                                                                                                                         |

| Fig. 4-29: Ideal 3-pole bandstop filter72                                                                                                                                                                                                                                                                             |

| Fig. 4-30: Insertion loss (bold) and return loss (thin) circuit simulator results of the ideal                                                                                                                                                                                                                        |

| bandstop filter73                                                                                                                                                                                                                                                                                                     |

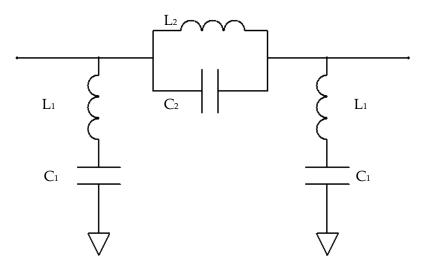

| Fig. 4-31: A 3-pole bandstop filter with all shunt resonators and impedance inverters                                                                                                                                                                                                                                 |

| between resonators74                                                                                                                                                                                                                                                                                                  |

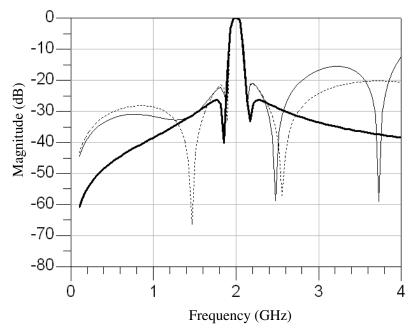

| Fig. 4-32: Return loss circuit simulator results of the first bandstop filter (bold), the second                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                       |

| bandstop filter with all shunt resonators and ideal transmission lines (dotted), and the                                                                                                                                                                                                                              |

| bandstop filter with all shunt resonators and ideal transmission lines (dotted), and the<br>third bandstop filter with all shunt resonators and low-pass filters used as impedance                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                       |

| third bandstop filter with all shunt resonators and low-pass filters used as impedance                                                                                                                                                                                                                                |

| third bandstop filter with all shunt resonators and low-pass filters used as impedance inverters (thin)                                                                                                                                                                                                               |

| third bandstop filter with all shunt resonators and low-pass filters used as impedance<br>inverters (thin)                                                                                                                                                                                                            |

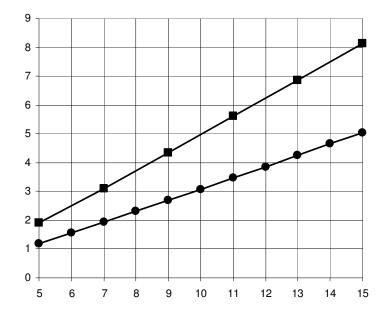

| <ul> <li>third bandstop filter with all shunt resonators and low-pass filters used as impedance inverters (thin).</li> <li>Fig. 4-33: Usable bandwidth of the low-pass filter for a bandstop filter with a center frequency of 1 versus the order of the low-pass filter for a Chebyshev response (square)</li> </ul> |

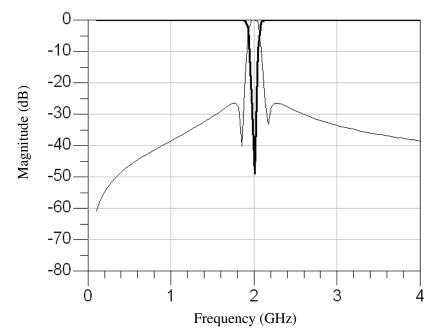

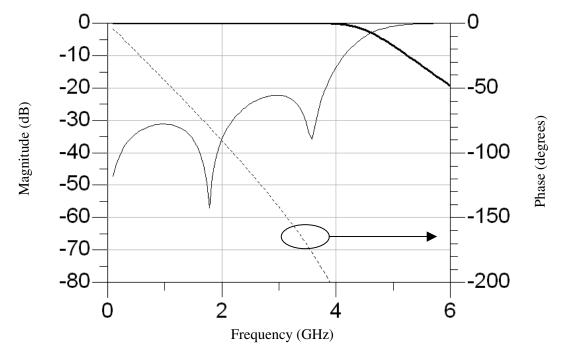

| Fig. 4-35: Return loss (thin), insertion loss (bold), and insertion phase (dotted) EM             |

|---------------------------------------------------------------------------------------------------|

| simulation results of the low pass filter78                                                       |

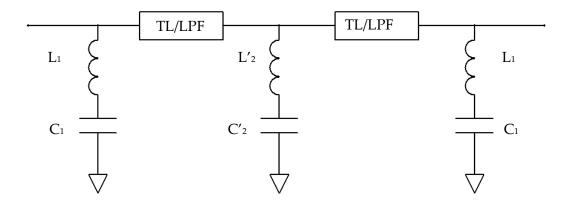

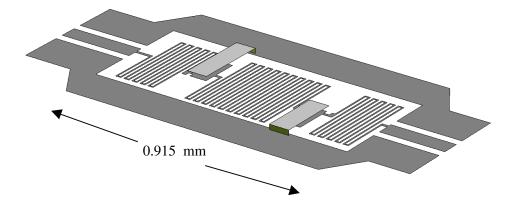

| Fig. 4-36: Image of the layout of the bandstop filter with low-pass filters as impedance          |

| inverters                                                                                         |

| Fig. 4-37: EM return loss (thin) and insertion loss (bold) simulation results of the 3-pole       |

| bandstop filter with low pass filters as 90° phase shifters. The return loss (dotted line)        |

| EM simulation of a design with revised resonators is also shown                                   |

| Fig. 4-38: Return loss (thin) and insertion loss (bold) measured results of the 3-pole bandstop   |

| filter with low pass filters as impedance inverters                                               |

| Fig. 4-39: Revised resonator design to improve the return loss characteristics near the           |

| rejection band (z-direction not to scale)                                                         |

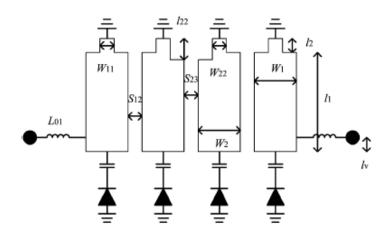

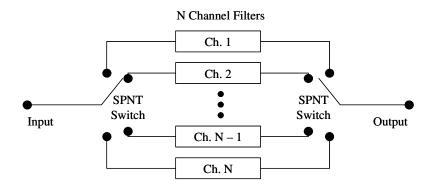

| Fig. 5-1: Architecture of a switched filter bank with N + 1 filtering options                     |

| Fig. 5-2: Architecture of a switched filter bank with reconfigurable multiplexers and $2^{N}$     |

| filtering options                                                                                 |

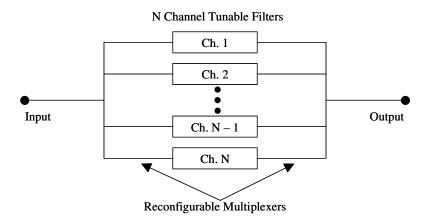

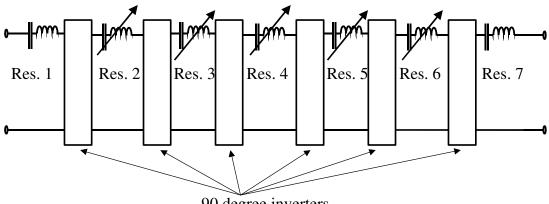

| Fig. 5-3: Diagram of a seven-pole filter with its middle resonators made tunable by               |

|                                                                                                   |

| embedded switches across the capacitors                                                           |

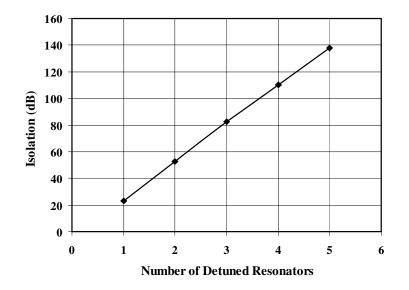

| Fig. 5-4: Isolation across a seven-pole filter versus the number of detuned resonators            |

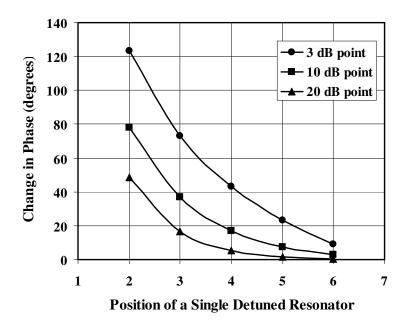

| Fig. 5-5: The change in out of band reflected phase for a seven-pole filter at different points   |

| of out of band rejection versus which resonator is detuned as seen from port 1 of the             |

| filter                                                                                            |

| Fig. 5-6: Diagram of the switched diplexer design                                                 |

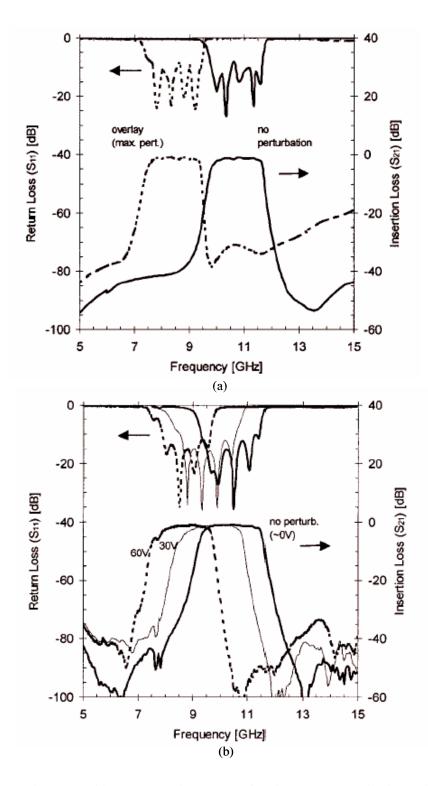

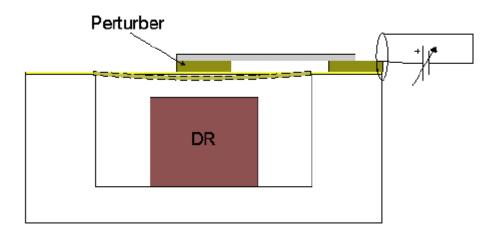

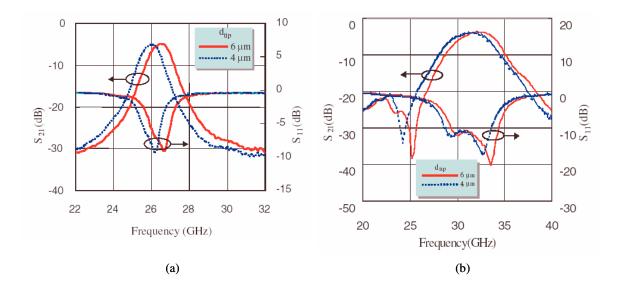

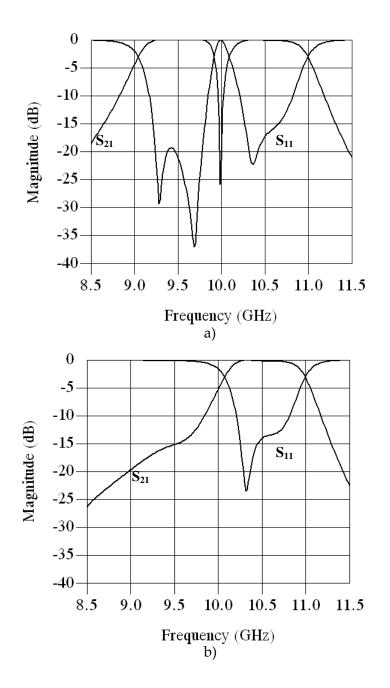

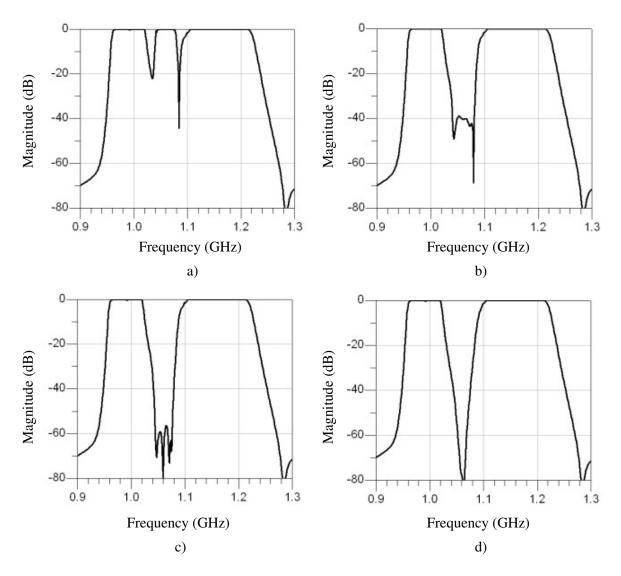

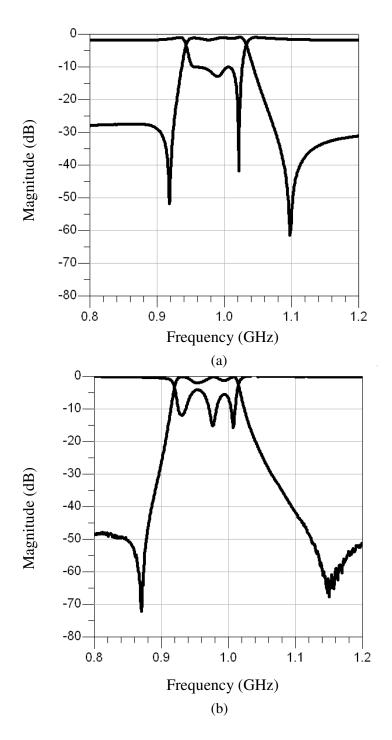

| Fig. 5-7: EM lossless response of the filter bank for the 3-pole filters. a) both channels ON, b) |

| only the higher channel ON, c) only the lower channel ON and d) both channels OFF. 89             |

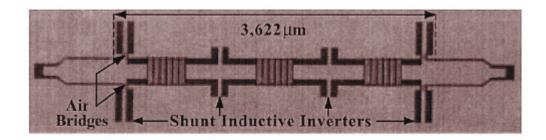

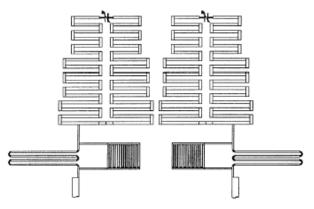

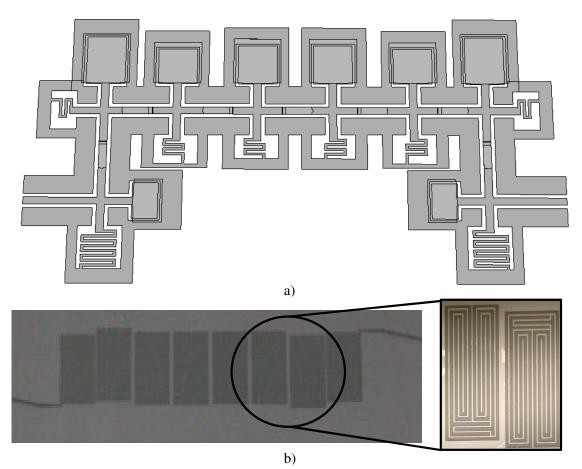

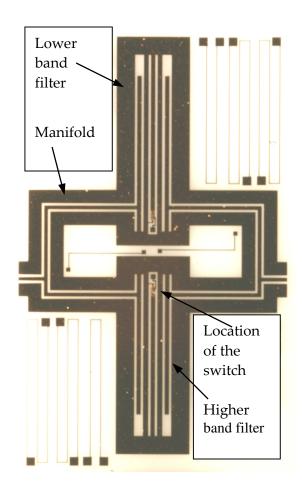

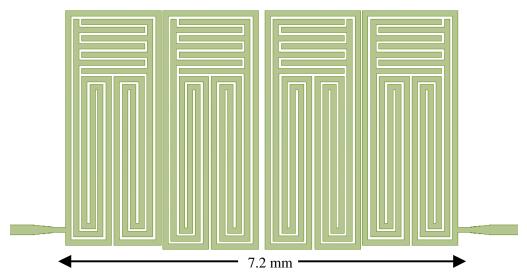

| Fig. 5-8: Image of the final switched filter bank design with the diplexers and the two filter    |

| channels                                                                                          |

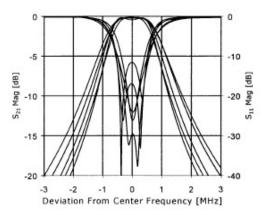

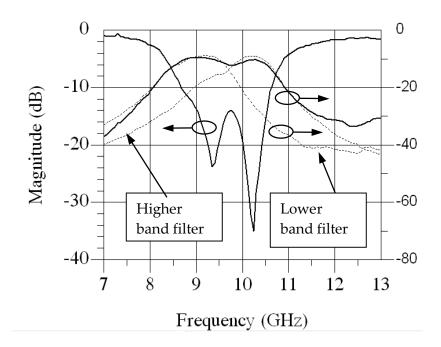

| Fig. 5-9: Measured response of the switched filter bank with both channels ON (bold) and          |

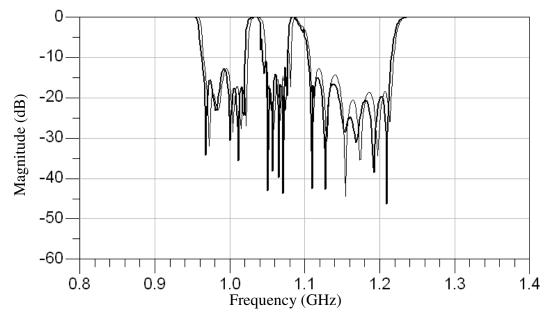

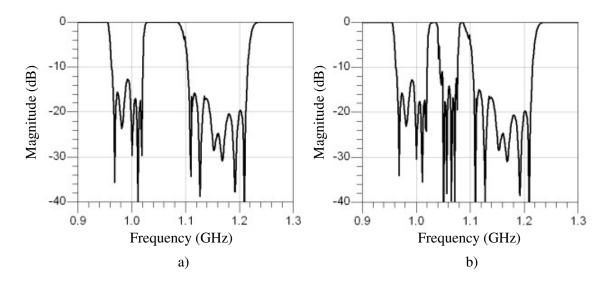

| the two filters tested individually (dashed) without being connected to the manifold91            |

|                                                                                                   |

| Fig. 5-10: Measured response of the switched filter bank with only the lower channel ON           |

|---------------------------------------------------------------------------------------------------|

| (bold), only the higher channel ON (dashed) and both channels OFF (thin)91                        |

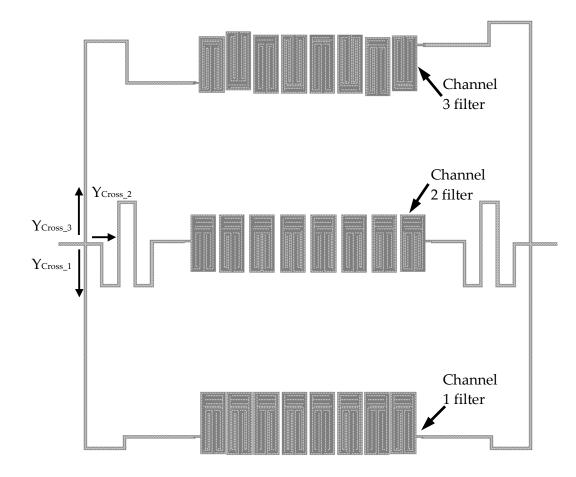

| Fig. 5-11: Layout of the two port triplexer                                                       |

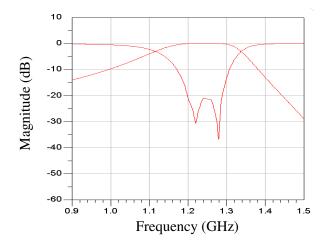

| Fig. 5-12: Insertion loss simulation results (bold line) and test results (thin line) of the 1-1  |

| multiplexer                                                                                       |

| Fig. 5-13: Return loss simulation results (bold line) and test results (thin line) of the 1-1     |

| multiplexer                                                                                       |

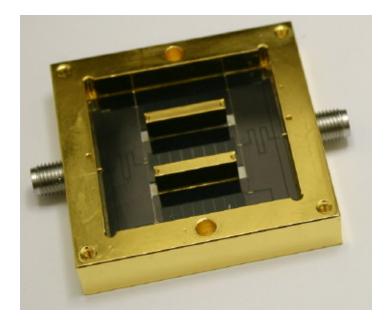

| Fig. 5-14: Image of the one input/one output three channel multiplexer                            |

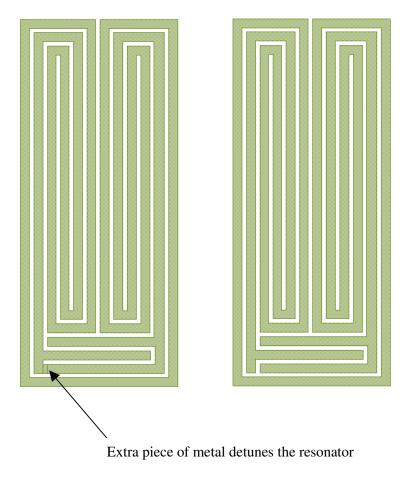

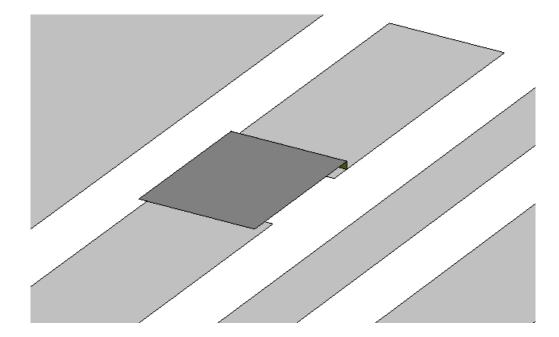

| Fig. 5-15: The regular resonator on the right and a detuned resonator on the left                 |

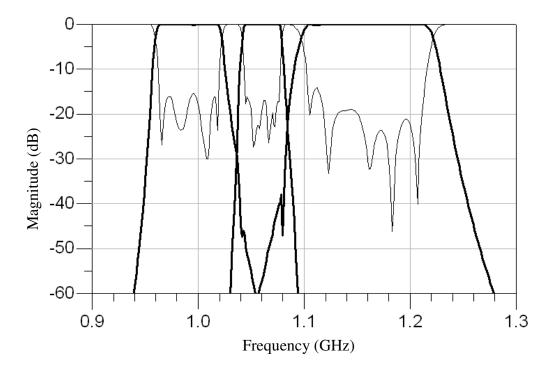

| Fig. 5-16: Insertion loss EM simulations results of the manifold-coupled switched                 |

| multiplexer with a) no detuned resonators, b) the two middle resonators of the middle             |

| channel detuned, c) the four middle resonators of the middle channel detuned d) and               |

| the six middle resonators of the middle channel detuned                                           |

| Fig. 5-17: Return loss EM simulations results of the manifold-coupled switched multiplexer        |

| with a) no detuned resonators and b) the six middle resonators of the middle channel              |

| detuned                                                                                           |

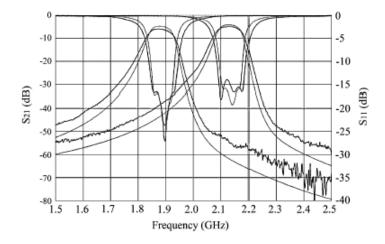

| Fig. 5-18: The simulation results of the three channel multiplexer with the return loss of the    |

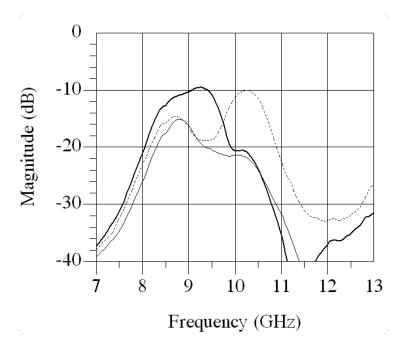

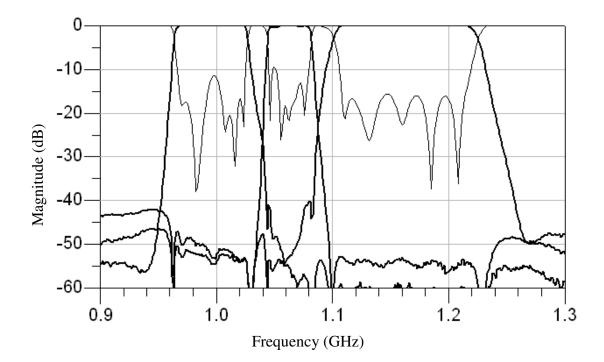

| common port (thin line) and the insertion loss of the three channels (bold lines) 101             |

| Fig. 5-19: The measured results of the three channel multiplexer with the return loss of the      |

| common port (thin line) and the insertion loss of the three channels (bold lines) 102             |

| Fig. 5-20: Return loss simulation results of the common port with all the channels on (thin       |

| line) and only the second channel on (bold line)103                                               |

| Fig. 5-21: Insertion loss simulation results of the second channel (bold line) which is on and    |

| the first and third channels (thin lines) which are off103                                        |

| Fig. 5-22:Image of the high temperature superconducting triplexer                                 |

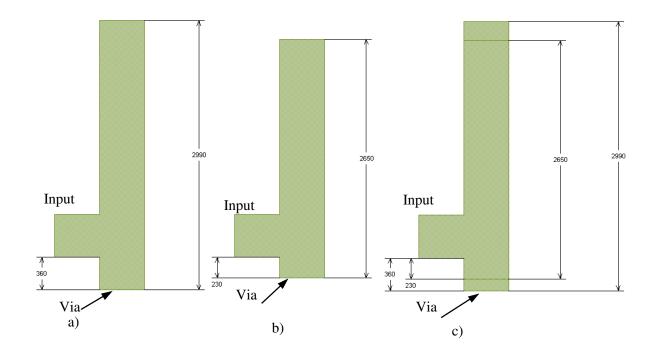

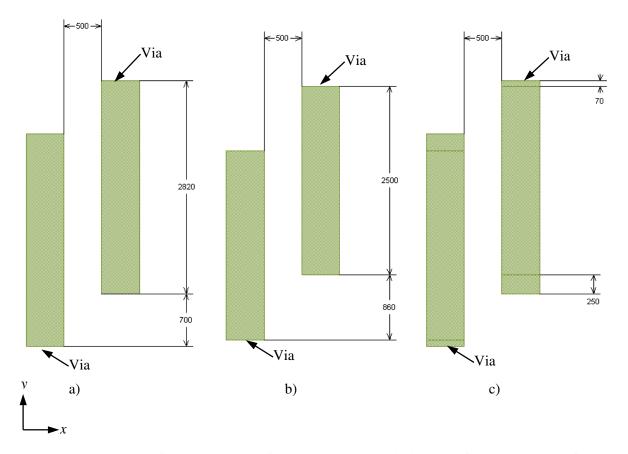

| Fig. 5-23: a) Layout of the first resonator at 9 GHz, b) layout of the first resonator at 10 GHz, |

| and c) the two layouts at 9 GHz and 10 GHz imposed on each other to demonstrate the               |

| position of the switches (dimensions are in $\mu$ m)                                              |

|                                                                                                   |

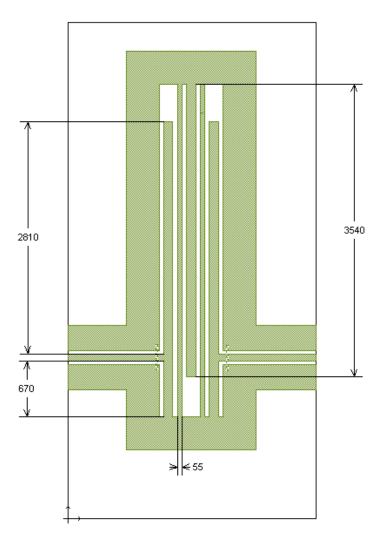

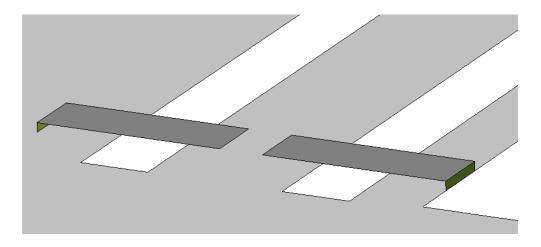

| Fig. | 5-24: a) Layout of two resonators for the lower band, b) layout of two resonators for the   | he  |

|------|---------------------------------------------------------------------------------------------|-----|

|      | higher for the same absolute bandwidth, and c) the two layouts superimposed to sho          | w   |

|      | the position of the switches (dimensions are in $\mu$ m)10                                  | 08  |

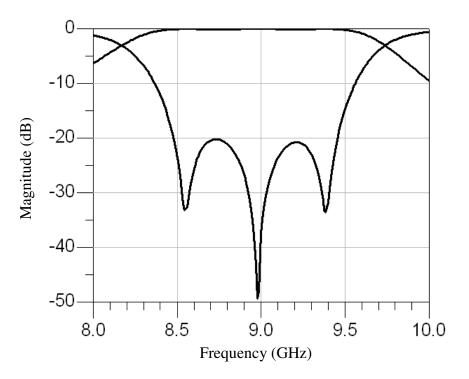

| Fig. | 5-25: Image of the 3-pole filter designed at 9 GHz with dimensions given in $\mu$ m 10      | 09  |

| Fig. | 5-26: EM simulation results of the 3-pole filter designed at 9 GHz                          | 10  |

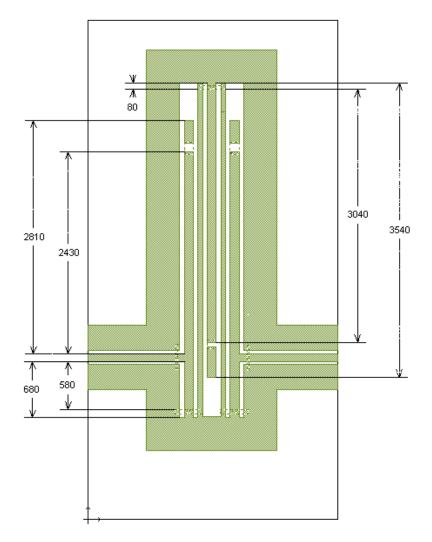

| Fig. | 5-27: Image of the two state 3-pole filter designed with dimensions given in $\mu$ m12      | 11  |

| Fig. | 5-28: Image of the MEMS switch at the open circuited end of a resonator with the to         | эp  |

|      | MEMS layer in dark gray12                                                                   | 12  |

| Fig. | 5-29: Image of the MEMS switches at the short circuited end of a resonator with the to      | эр  |

|      | MEMS layer in dark gray12                                                                   | 13  |

| Fig. | 5-30: EM simulations results of the two state filter in the lower frequency state (thin lin | le) |

|      | and the higher frequency state (bold line)12                                                | 13  |

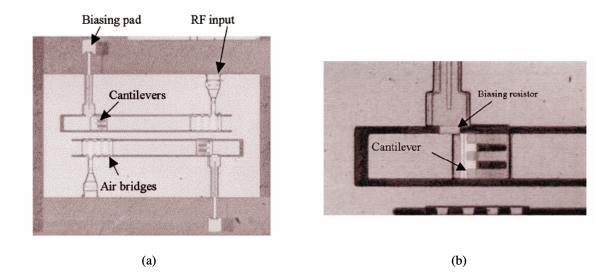

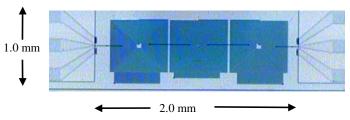

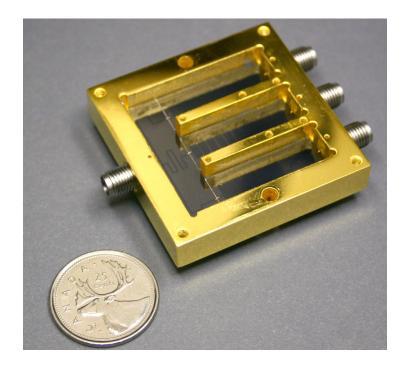

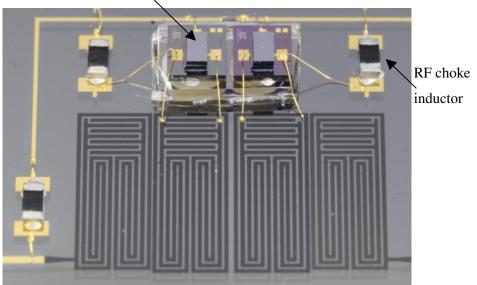

| Fig. | 5-31: Measured results of the assembled 4-pole filter                                       | 15  |

| Fig. | 5-32: Image of the assembled HTS filter integrated with MEMS switches                       | 15  |

| Fig. | 5-33: Measured return loss (thin gray) and return loss (bold black) of the 4-pole filt      | er  |

|      | with the MEMS switches in the closed state                                                  | 16  |

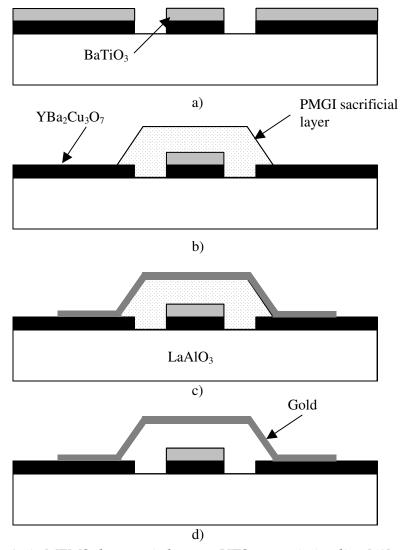

| Fig. | 5-34: The fabrication steps for the monolithic integration of HTS circuits and MEM          | 1S  |

|      | devices12                                                                                   | 20  |

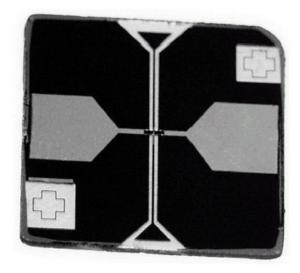

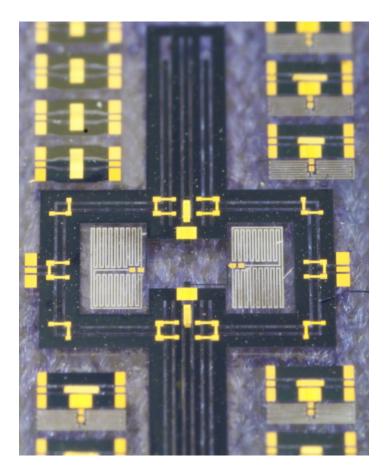

| Fig. | 5-35: Image of some devices from the monolithically integrated HTS and MEMS wafe            | er. |

|      |                                                                                             | 21  |

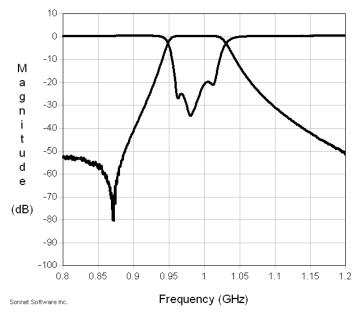

| Fig. | 5-36: An image of the 4-pole HTS filter used to determine the effect of the a-              | Si  |

|      | deposition12                                                                                | 23  |

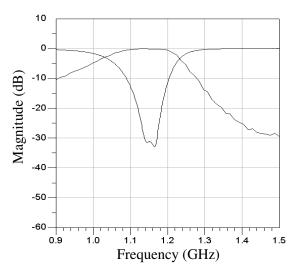

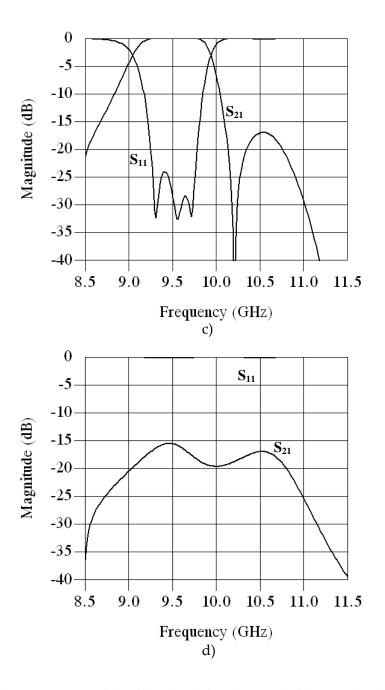

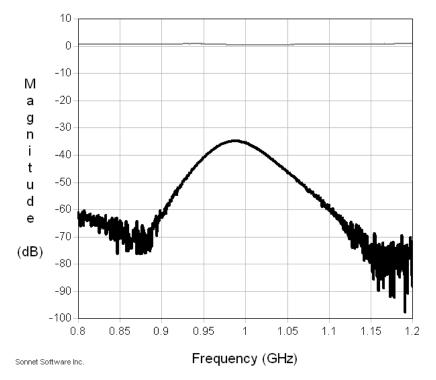

| Fig. | 5-37: The measured results of a) the 4-pole HTS filter before the a-Si deposition and       | b)  |

|      | the 4-pole HTS filter with 1 μm of deposited a-Si12                                         | 24  |

|      |                                                                                             |     |

### **List of Tables**

| Table 2-1: Comparison of different technologies to realize tunable bandpass filters         |

|---------------------------------------------------------------------------------------------|

| Table 3-1: Reflected group delay values at the center frequency of an inverter coupled      |

| bandpass filter [49]                                                                        |

| Table 3-2: Values in (pF) of the capacitors after optimizing each resonator of the 8-pole   |

| lumped element filter41                                                                     |

| Table 3-3: Lengths (in micrometers) of parameters after optimizing each resonator of the 8- |

| pole lumped element superconducting filter43                                                |

| Table 3-4: Values (in micrometers) of parameters after optimizing each resonator of the 8-  |

| pole HTS filter                                                                             |

| Table 5-1: Frequency range of the three channels                                            |

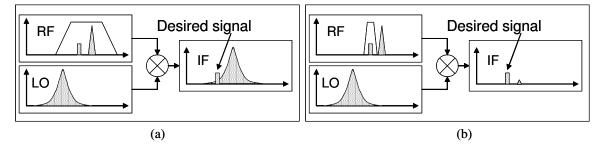

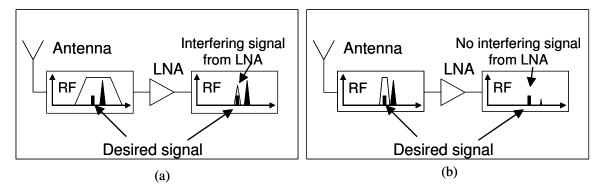

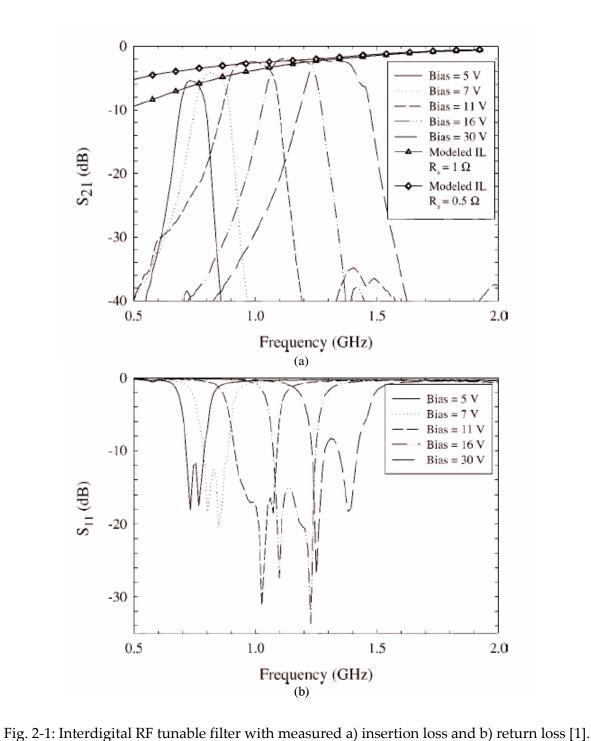

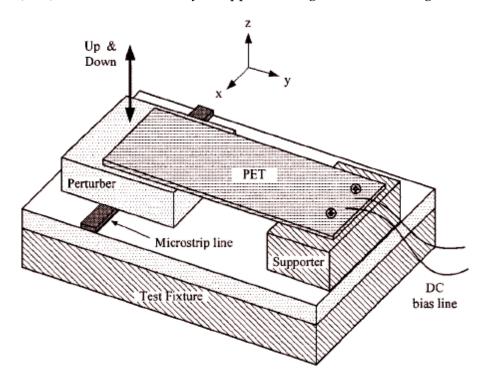

# Chapter 1 Introduction