# Assessing Au-Al Wire Bond Reliability Using Integrated Stress Sensors

by

Michael James McCracken

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Master of Applied Science

in

Mechanical Engineering

Waterloo, Ontario, Canada, 2010 © Michael James McCracken 2010

## **Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Wire bond reliability testing typically consists of aging bonds in a high temperature environment for long time periods, and removing samples at intervals to assess bond shear strength and characterize the bond cross sections. In this way, the degradation of the bond can be monitored at discrete time intervals, and it is determined whether the bond will be reliable during the specific service life. This process can be labour and time intensive. An alternative method is reported using an existing test chip that allows for contact resistance measurements and provides signals from piezoresistive integrated CMOS microsensors located around test bond pads. The sensors are sensitive to radial compressive or tensile stresses occurring on the bond pad due to intermetal-lic formation, oxidation, and crack formation at the bond interface.

Two sets of identical test chips are bonded with optimized Au ball bonds and aged for 2000 h at 175 °C. One set is connected to equipment which monitors signals from the stress sensors and the contact resistance of the bonds. The other set is destructively tested by shear tests and cross sectioning. It is found that the stress sensors are capable of indicating which stage of bond aging is experienced by relating the signal to the relative density of the intermetallic compounds (IMCs) and oxide which form during aging.

This research offers a valuable new method for accelerating bond process development. By using the sensors to determine the stage of aging experienced and the magnitude of changes happening to the bond, the initial bond quality and bond reliability can be roughly characterized. A useful application is in comparing large samples of bonds made under varying conditions, and determining relative reliabilities of the bonds. A small sample size is required, as the sensors allow for complete continuous aging histories of individual bonds, which was not previously possible.

A new test chip is designed for use in future studies which allows for contact resistance measurement, and provides stress signals for up to 55 bonds. A multiplexer integrated on the chip allows for measurements from one specified bond pad at a time. The chip is also equipped with x and y-force measurements which can be used to monitor bond process, and a resistive temperature detector for temperature measurement.

A miniaturized bond aging system is designed to facilitate future works where chips are subject to high temperature storage. A heating element fits over the cavity of a microelectronic package containing the test chip, and allows for precise temperature control, while using less power than a conventional oven, and maintaining a low temperature at electrical connections to the package.

### Acknowledgements

I wish to thank my supervisor, Dr. Michael Mayer for his assistance and support during my stay as a Masters student. I would also like to thank MK Electron and Microbonds for funding this project. I am grateful for the Ontario Graduate Scholarship and the University of Waterloo President's Scholarship which helped make this work possible. Additional funding was also provided by the Natural Sciences and Engineering Research Council of Canada (NSERC) and Ontario Centers of Excellence (OCE).

# **Table of Contents**

| De  | clarati              | on                                          |                                                 | ii  |

|-----|----------------------|---------------------------------------------|-------------------------------------------------|-----|

| Ab  | stract               |                                             |                                                 | iii |

| Ac  | knowl                | edgemen                                     | nts                                             | v   |

| Tal | ole of (             | Contents                                    |                                                 | vi  |

| Lis | t of Ta              | ıbles                                       |                                                 | x   |

| Lis | t of Fi              | gures                                       |                                                 | xi  |

| 1.  | Introduction         |                                             |                                                 | 1   |

|     | 1.1                  | l Reliability                               |                                                 |     |

|     | 1.2                  | 2 Motivation                                |                                                 |     |

|     | 1.3                  | .3 Non Destructive Reliability Test Methods |                                                 |     |

|     | 1.4                  | Object                                      | ive                                             | 3   |

|     | 1.5                  | Thesis                                      | Outline                                         | 3   |

| 2.  | Liter                | ature Re                                    | view                                            | 5   |

|     | 2.1                  | Wire B                                      | Sonding Process                                 | 5   |

|     |                      | 2.1.1                                       | Wire Bonding Materials                          | 7   |

|     |                      | 2.1.2                                       | Bonding Mechanisms                              | 8   |

|     |                      | 2.1.3                                       | Important Parameters for Wire Bond Optimization | 10  |

|     |                      | 2.1.4                                       | Bond Evaluation by Pull Test                    | 11  |

|     |                      | 2.1.5                                       | Bond Evaluation by Shear Test                   | 11  |

|     | 2.2                  | Wire B                                      | ond Reliability                                 | 12  |

|     |                      | 2.2.1                                       | Microstructure Evolution                        | 13  |

|     |                      | 2.2.2                                       | Voiding and Cracking                            | 18  |

|     |                      | 2.2.3                                       | Shear Strength During Aging                     | 19  |

|     |                      | 2.2.4                                       | Contact Resistance                              | 21  |

|     |                      | 2.2.5                                       | Integrated Stress Sensors                       | 23  |

|     | 2.3                  | Summa                                       | ary                                             | 24  |

| 3.  | Experimental Methods |                                             |                                                 | 26  |

|     | 3.1                  | Overall Experimental Plan                   |                                                 |     |

|     | 3.2                  | Die Attach                                  |                                                 |     |

|    | 3.3  | Prepara                   | ation of Wire Bonding Samples                                     | 28 |

|----|------|---------------------------|-------------------------------------------------------------------|----|

|    | 3.4  | Test Ch                   | nip                                                               | 37 |

|    | 3.5  | 5 Destructive Tests       |                                                                   |    |

|    | 3.6  | High To                   | emperature Storage for Accelerated Bond Aging                     | 40 |

|    | 3.7  | Bondin                    | g Plan for Contact Resistance and Stress Sensor Signal Monitoring | 41 |

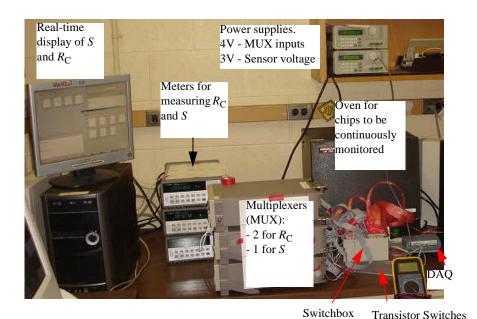

| 4. | Expe | erimental                 | Setups for Accelerated Bond Aging                                 | 45 |

|    | 4.1  | Setup A                   | A                                                                 | 46 |

|    |      | 4.1.1                     | Oven                                                              | 48 |

|    |      | 4.1.2                     | High Temperature Cabling                                          | 48 |

|    |      | 4.1.3                     | Rig to Hold Test Chips                                            | 49 |

|    |      | 4.1.4                     | Switch Box                                                        | 50 |

|    |      | 4.1.5                     | Devices                                                           | 51 |

|    |      | 4.1.6                     | Software                                                          | 51 |

|    | 4.2  | Setup E                   | 3                                                                 | 52 |

| 5. | Micr | icrostructural Analysis   |                                                                   |    |

|    | 5.1  | 1 Properties Evaluated    |                                                                   | 53 |

|    |      | 5.1.1                     | Quantitative Measures                                             | 53 |

|    |      | 5.1.2                     | Identification of IMCs                                            | 58 |

|    | 5.2  | Microstructural Evolution |                                                                   | 60 |

|    |      | 5.2.1                     | Unaged (As-bonded)                                                | 60 |

|    |      | 5.2.2                     | Half Hour Age                                                     | 61 |

|    |      | 5.2.3                     | One Hour Age                                                      | 61 |

|    |      | 5.2.4                     | Ten Hour Age                                                      | 62 |

|    |      | 5.2.5                     | Hundred Hour Age                                                  | 63 |

|    |      | 5.2.6                     | Three Hundred Hour Age                                            | 65 |

|    |      | 5.2.7                     | Six Hundred Hour Age                                              | 67 |

|    |      | 5.2.8                     | Nine Hundred Hour Age                                             | 68 |

|    |      | 5.2.9                     | One Thousand Three Hundred Hour Age                               | 69 |

|    |      | 5.2.10                    | Two Thousand Hour Age                                             | 69 |

|    | 5.3  | Measur                    | rements of Physical Changes                                       | 70 |

| 6. | Shea | ır Test Re                | esults                                                            | 71 |

|    | 6.1  | Shear                     | Strength of Ronds                                                 | 71 |

|     | 6.2                            | Shear I                                                               | nterfaces                                                          | 74  |  |

|-----|--------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----|--|

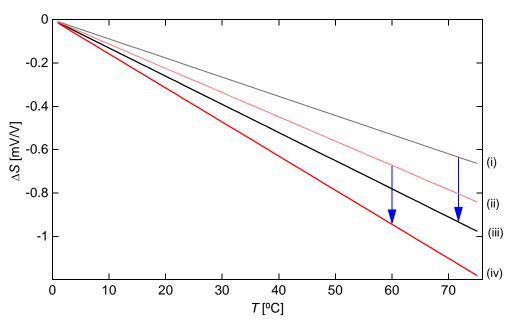

| 7.  | Conta                          | act Resis                                                             | stance Results                                                     | 75  |  |

|     | 7.1                            | Factors                                                               | Distorting RC Signal                                               | 76  |  |

|     | 7.2                            | Averag                                                                | e RC Signal                                                        | 78  |  |

|     | 7.3                            | Initial I                                                             | RC Decrease                                                        | 78  |  |

| 8.  | Stress                         | s Sensor                                                              | Results                                                            | 79  |  |

|     | 8.1                            | Averag                                                                | e Sensor Response to Aging                                         | 81  |  |

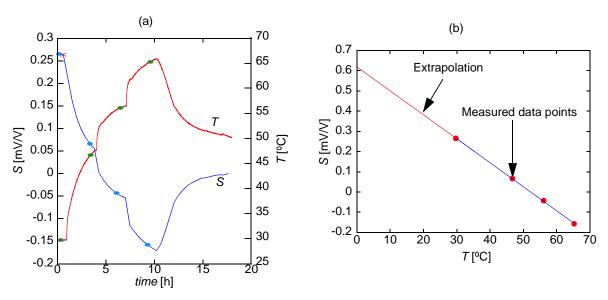

|     | 8.2                            | Sensor                                                                | Characterizations Before and After HTS                             | 82  |  |

|     | 8.3                            | Stresses                                                              | s Measured After 2000 h                                            | 85  |  |

| 9.  | Discu                          | ıssion                                                                |                                                                    | 86  |  |

|     | 9.1                            | The Ev                                                                | olution of Bond Aging                                              | 86  |  |

|     |                                | 9.1.1                                                                 | Stage (a)                                                          | 86  |  |

|     |                                | 9.1.2                                                                 | Stage (b)                                                          | 89  |  |

|     |                                | 9.1.3                                                                 | Stage (c)                                                          | 90  |  |

|     |                                | 9.1.4                                                                 | Stage (d)                                                          | 92  |  |

|     |                                | 9.1.5                                                                 | Stage (e)                                                          | 93  |  |

|     | 9.2                            | Eviden                                                                | ce of Contact Resistance Increase Primarily Due to Oxide Formation | 94  |  |

|     | 9.3                            | Sensor Signal and Contact Resistance as Possible Tools for Predicting |                                                                    |     |  |

|     | Bond Failure                   |                                                                       | 94                                                                 |     |  |

|     |                                | 9.3.1                                                                 | Relation of Stress Sensor Signal to Changes at Microstructure      | 94  |  |

|     |                                | 9.3.2                                                                 | Relation to Shear Strength                                         | 95  |  |

|     | 9.4                            | Applica                                                               | ation of Stress Sensors                                            | 96  |  |

|     | 9.5                            | Investig                                                              | gation of Additional Potential Correlations                        | 99  |  |

| 10. | Chip                           | Design f                                                              | for Future Studies                                                 | 100 |  |

| 11. | Miniaturized Bond Aging System |                                                                       |                                                                    |     |  |

|     | 11.1                           | .1 Design                                                             |                                                                    |     |  |

|     | 11.2                           | 1.2 Mini-Oven Design                                                  |                                                                    |     |  |

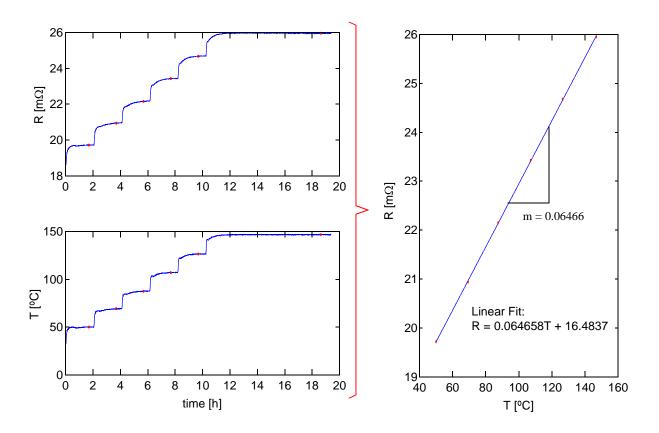

|     | 11.3                           | 11.3 Thermal Characterization                                         |                                                                    |     |  |

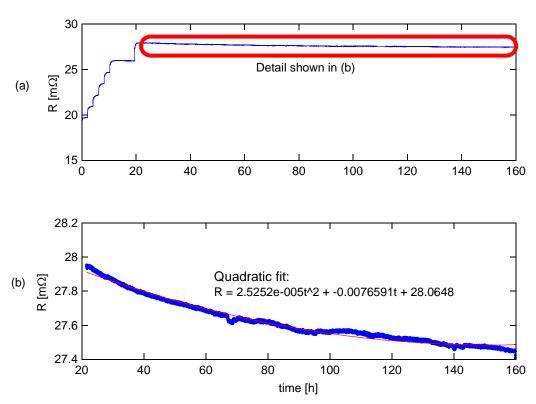

|     | 11.4                           | Burn In                                                               | Test                                                               | 107 |  |

|     | 11.5                           | Therma                                                                | al Cycling Test                                                    | 108 |  |

| 12. | Reco                           | ommenda                                                               | ations                                                             | 109 |  |

| 13. | Conc                           | lusions                                                               |                                                                    | 111 |  |

| Ref | erence                         | <b>1</b> C                                                            |                                                                    | 113 |  |

# Appendices

| Appendix A. Wiring Diagram for Switchbox                  | 117 |

|-----------------------------------------------------------|-----|

| Appendix B. Transistor Switches                           | 119 |

| Appendix C. Effect of Bond Location on Contact Resistance | 121 |

| Appendix D. Resistance of Empty Pad                       | 127 |

| Appendix E. Investigation of Possible Correlations        | 132 |

# **List of Tables**

| Table 1: Plan for Aging and Destructive Testing.                       | 27  |

|------------------------------------------------------------------------|-----|

| Table 2: Wire Loop Parameters                                          | 30  |

| Table 3: Wedge Bond Parameters                                         | 30  |

| Table 4: EFO Parameters                                                | 31  |

| Table 5: Geometry Results                                              | 33  |

| Table 6: Sample sizes                                                  | 53  |

| Table 7: Bond Properties                                               | 54  |

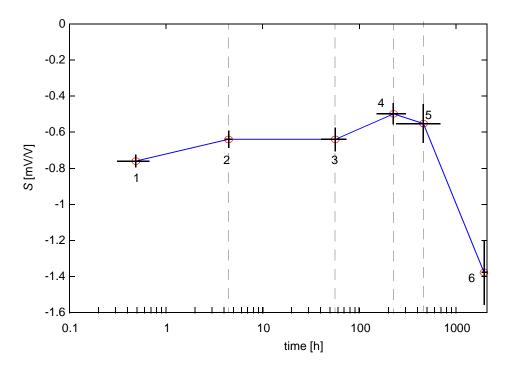

| Table 8: Average times and values of key signal changes                | 83  |

| Table 9: Temperature characterization of sensors                       | 84  |

| Table 10: Material Properties                                          | 88  |

| Table 11: Temperatures of Each Side of Mini-Oven Averaged over 6 Tests | 105 |

| Table 12: Mini-Oven temperature at various locations on surface        | 107 |

# **List of Figures**

| Figure 1: Wire bonding process.                                                                              | 6  |

|--------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Pull strength of Au bonds on Al metallizations with and without plasma cleaning                    |    |

| after 300°C high temperature storage for 4 h [1]                                                             | 9  |

| Figure 3: Microstructure evolution as reported in [13].                                                      | 15 |

| Figure 4: Microstructure dominated by Au5Al2                                                                 | 15 |

| Figure 5: Oxidized Au4Al layer [3]                                                                           | 16 |

| Figure 6: Au-Al binary phase diagram [15].                                                                   | 17 |

| Figure 7: Crack growth around Au "hook" [2].                                                                 | 18 |

| Figure 8: Interdiffusion and growth of intermetallics at shear interface.                                    | 20 |

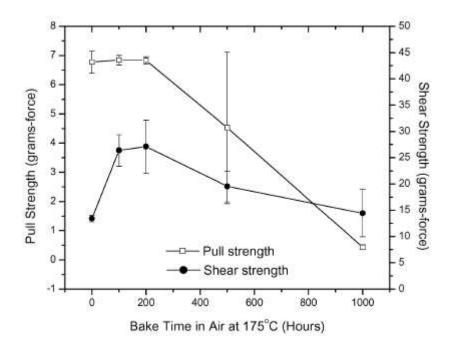

| Figure 9: Shear Test results from [18].                                                                      | 21 |

| Figure 10: Four wire connection.                                                                             | 21 |

| Figure 11: Contact resistance increases until either (a) the bond fails, or (b) the bond                     |    |

| becomes electrically isolated.                                                                               | 23 |

| Figure 12: Stress Sensors.                                                                                   | 24 |

| Figure 13: Intermetallics which are expected to form during aging [1].                                       | 25 |

| Figure 14: Experimental procedure                                                                            | 26 |

| Figure 15: Chips being plasma cleaned.                                                                       | 29 |

| Figure 16: Optimization results in less variance.                                                            | 29 |

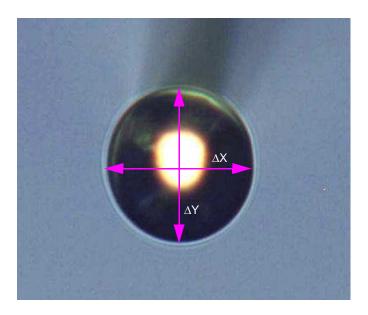

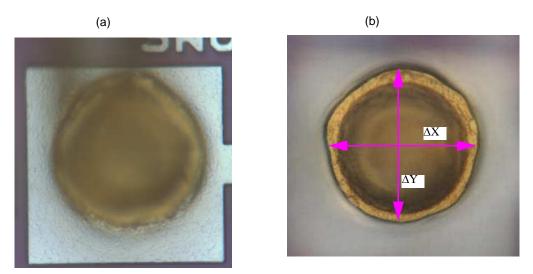

| Figure 17: FAB diameter measurements                                                                         | 32 |

| Figure 18: Ball Bond Measurements.                                                                           | 33 |

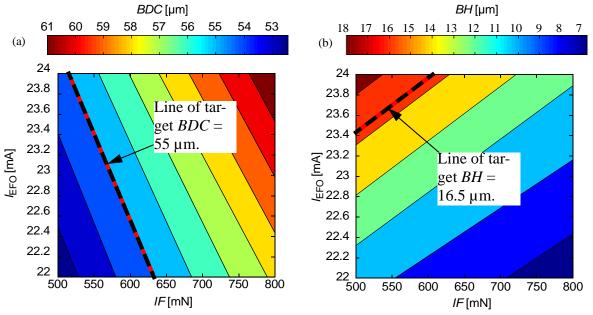

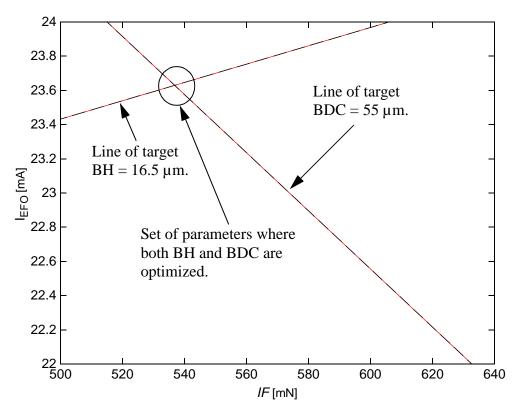

| Figure 19: (a) BDC plotted as a function of $I_{\mbox{\footnotesize EFO}}$ and $I_{\mbox{\footnotesize F'}}$ | 34 |

| Figure 20: Optimized parameters for bond geometry                                                            | 35 |

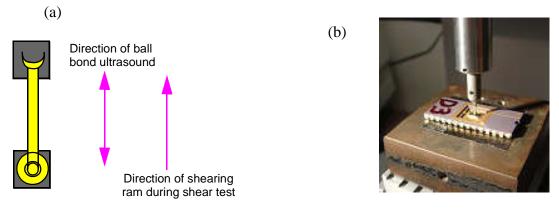

| Figure 21: (a) Direction of shear testing. (b) Bond on chip being sheared.                                   | 35 |

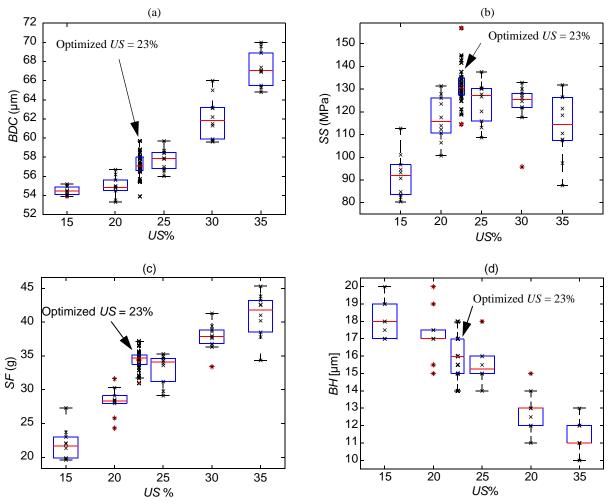

| Figure 22: (a) BDC for different US%.                                                                        | 37 |

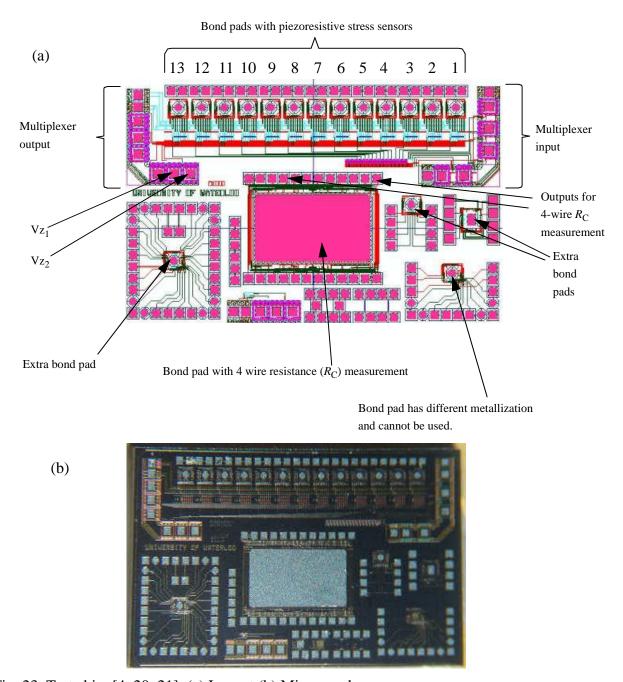

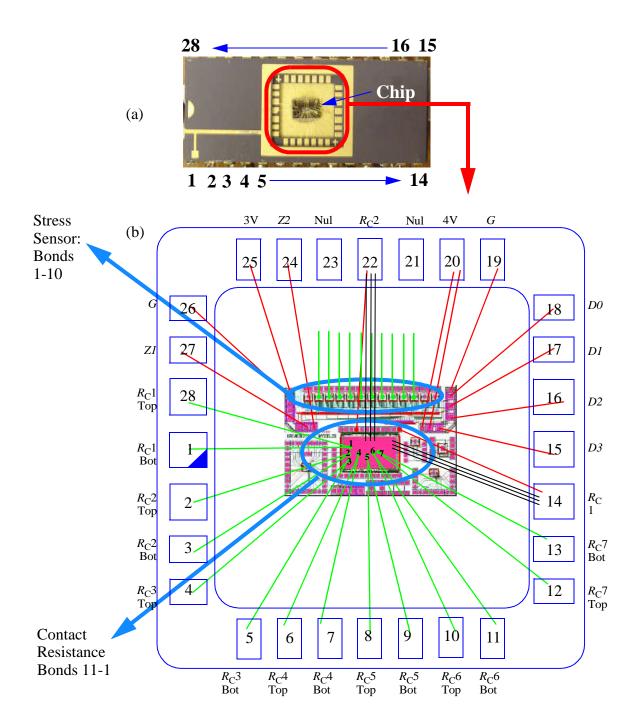

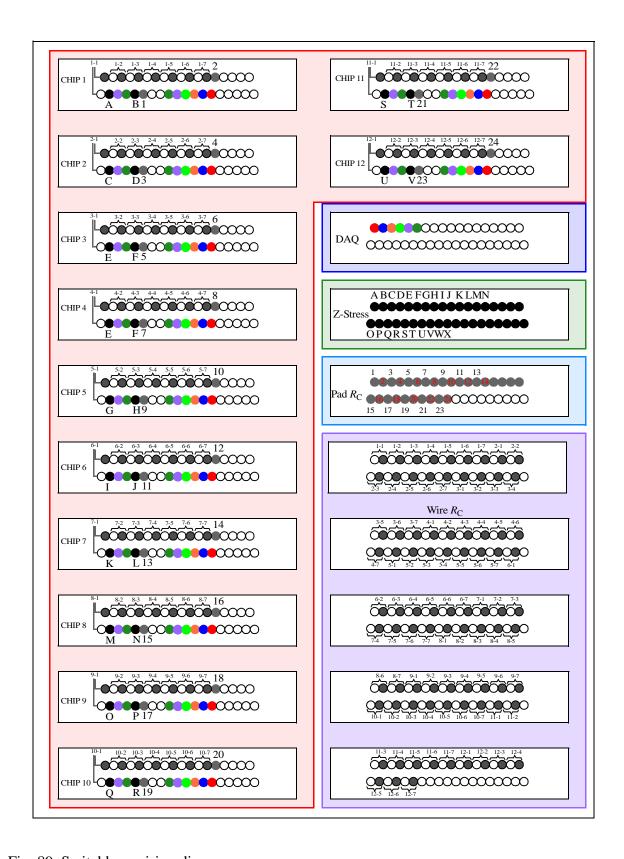

| Figure 23: Layout of test chip [4, 20, 21]                                                                   | 38 |

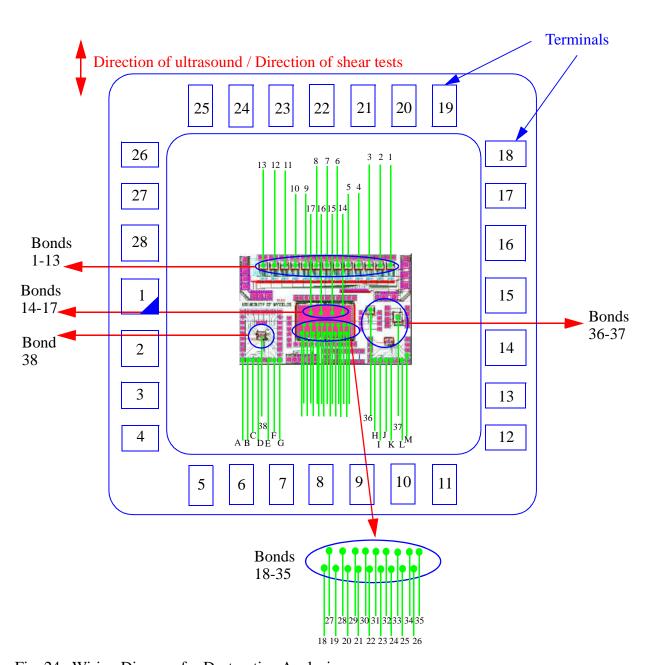

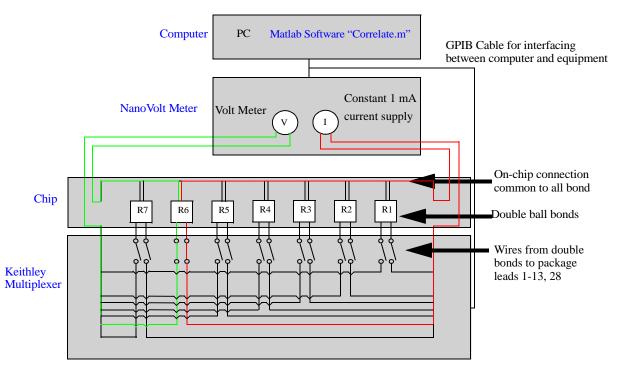

| Figure 24: Wiring Diagram for Destructive Analysis                                                           | 39 |

| Figure 25: Mounting of chip for sectioning.                                                                  | 41 |

| Figure 26: Non-Destructive Bonded Chip.                                                                      | 42 |

| Figure 27: Z Stress sensors arranged in Wheatstone bridge configuration                                      | 43 |

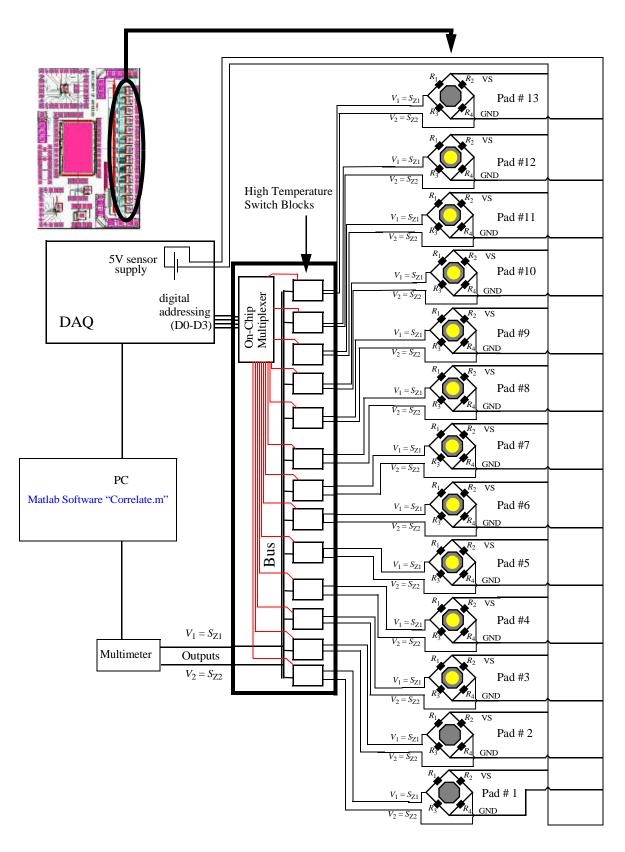

| Figure 28: Multiplexer Selection of Target Ball Bond for one chip.                                           | 45 |

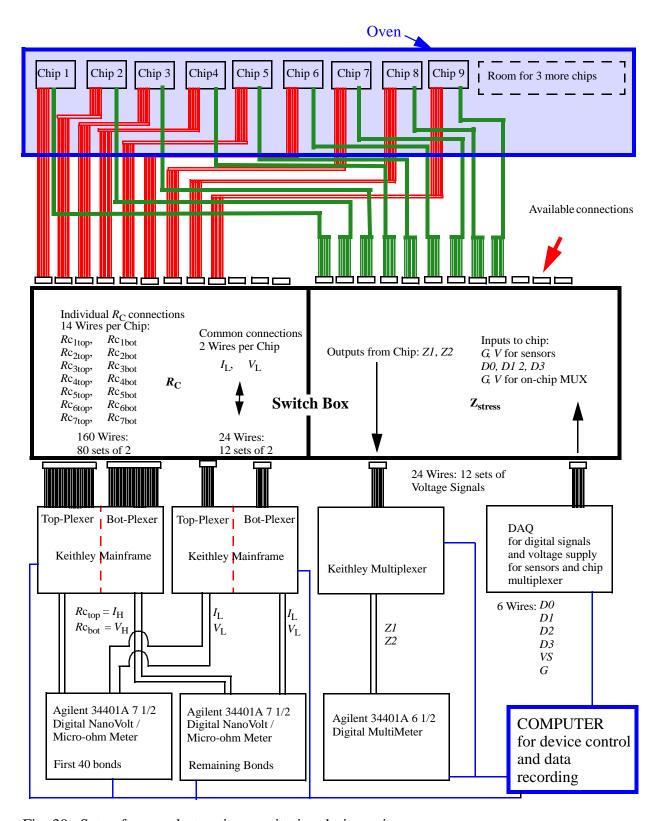

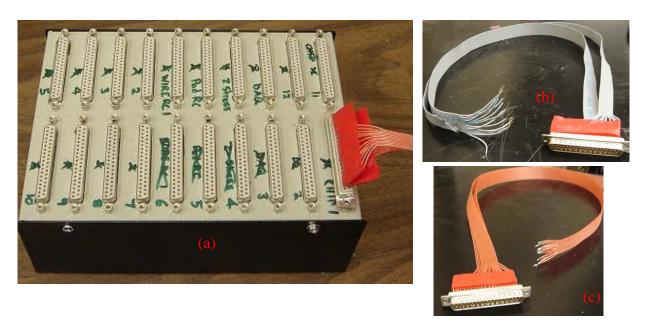

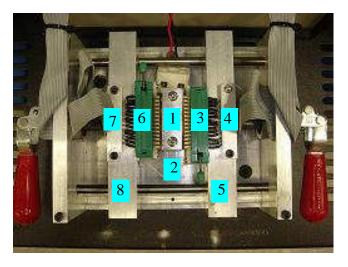

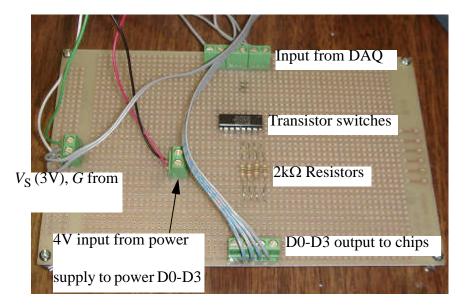

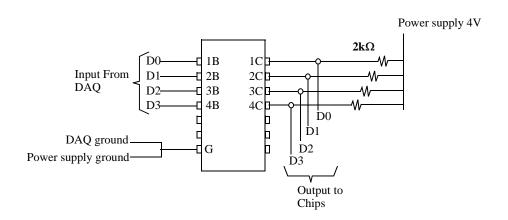

| Figure 29: Setup A                                                                       | 46 |

|------------------------------------------------------------------------------------------|----|

| Figure 30: Setup for non-destructive monitoring during aging                             | 47 |

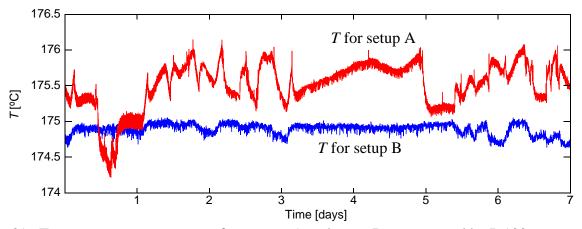

| Figure 31: Temperature measurements from Setup A and Setup B                             | 48 |

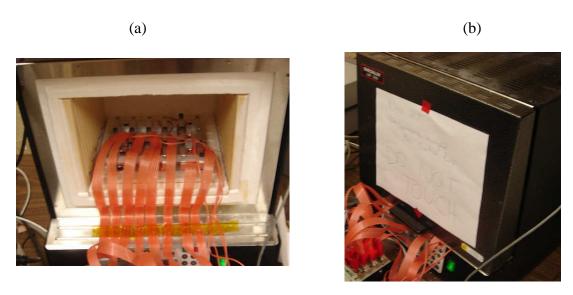

| Figure 32: (a) Chips fastened to the rig and placed in oven. (b) Oven door closed over   |    |

| cabling.                                                                                 | 49 |

| Figure 33: Package holder for oven                                                       | 49 |

| Figure 34: (a) Switchbox (b) Connector with band of wires (c) Connector with band of     |    |

| high temperature wires.                                                                  | 50 |

| Figure 35: Region 2. Chips on shelf in oven.                                             | 52 |

| Figure 36: Lateral IMC measurement.                                                      | 55 |

| Figure 37: Some lateral IMCs are not visible due to curvature of bond                    | 55 |

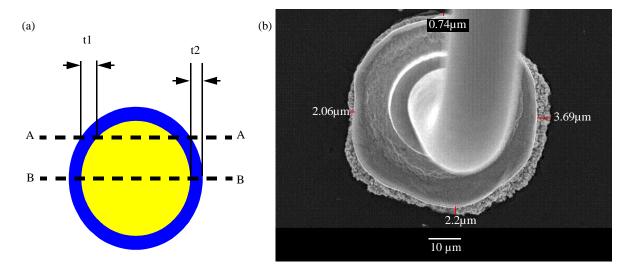

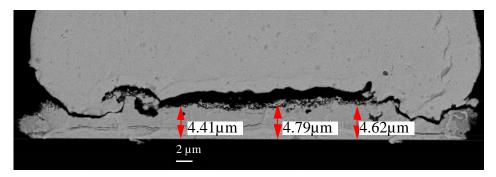

| Figure 38: IMC thickness measurements.                                                   | 56 |

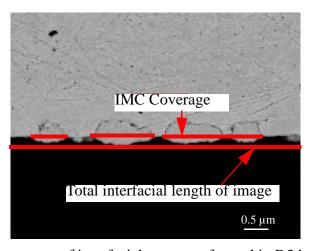

| Figure 39: Example measurement of interfacial coverage from chip D3 bond 3.              | 56 |

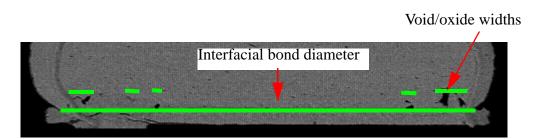

| Figure 40: Example void/crack/oxidation fraction measurement                             | 57 |

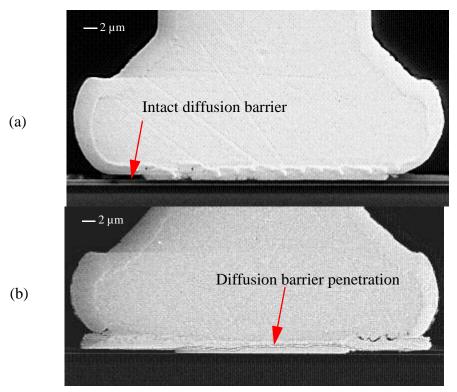

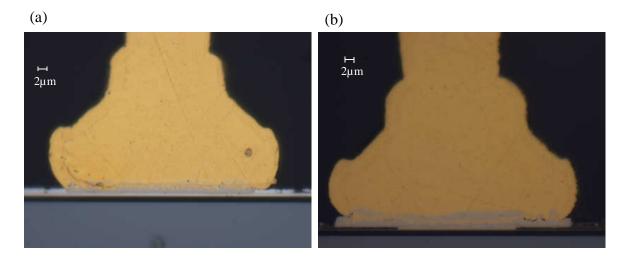

| Figure 41: (a) Bond J from chip D8. IMCs formed on top Al layer. No DBL penetration. (b) |    |

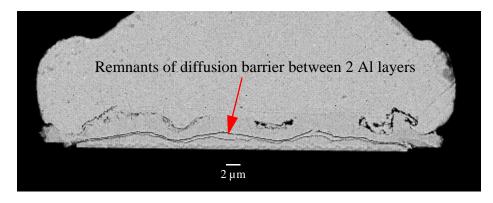

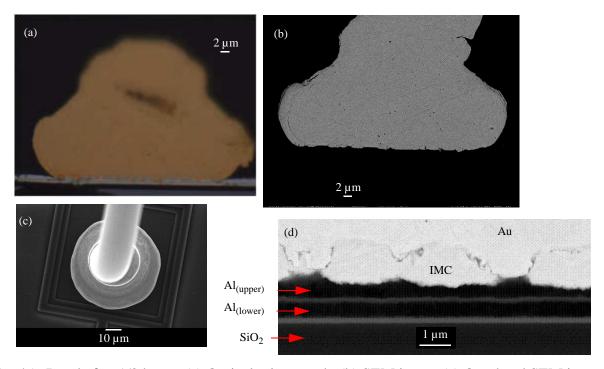

| Bond F from chip D10. DBL has been broken and IMCs have formed in lower Al layer         | 58 |

| Figure 42: Bond with All under-pad Al converted to IMCs.                                 | 58 |

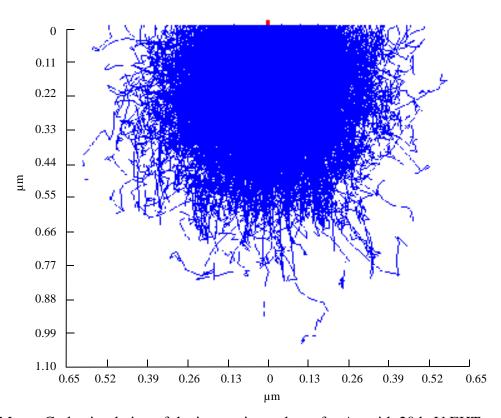

| Figure 43: Monte Carlo simulation of the interaction volume for Au with 20 keV EHT.      | 59 |

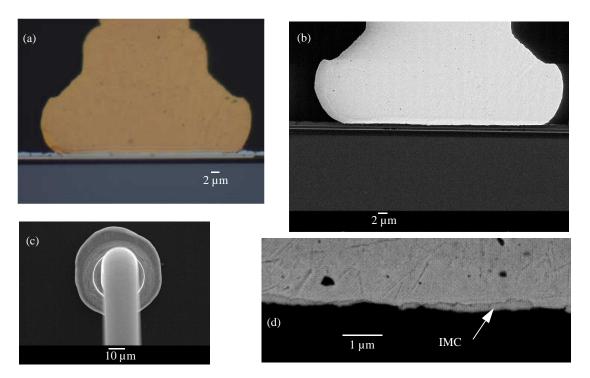

| Figure 44: Unaged bond.                                                                  | 60 |

| Figure 45: Bond after 1/2 h age.                                                         | 61 |

| Figure 46: Bond after 1 h age.                                                           | 62 |

| Figure 47: Typical bond aged for 10 h.                                                   | 63 |

| Figure 48: Initial IMC formation in the lower Al pad layer (after 100 h).                | 64 |

| Figure 49: Typical bond after 100h age.                                                  | 64 |

| Figure 50: Development of second Au4Al layer.                                            | 66 |

| Figure 51: Dark region next to Au4Al and exposed to air is likely oxide.                 | 66 |

| Figure 52: Bond aged 300 h.                                                              | 67 |

| Figure 53: Typical bond after 600 h age.                                                 | 68 |

| Figure 54: Bond after 900 h age.                                                         | 69 |

| Figure 55: Typical bond after 1300 h age.                                                | 70 |

| Figure 56: Typical bond after 2000 h age.                                                | 71 |

| Figure 57: Physical properties of aging bonds.                                           | 72 |

| Figure 58: Shear strength results over 2000 h                                            | 73 |

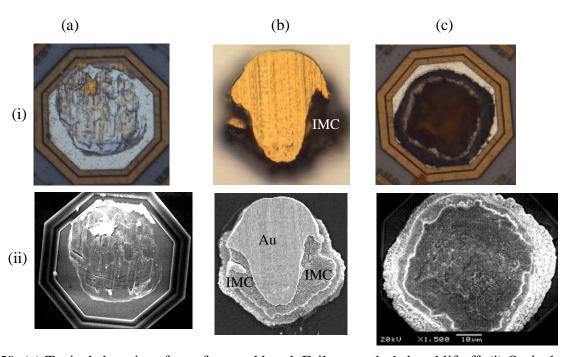

| Figure 59: (a) Typical shear interface                                                       | 74         |

|----------------------------------------------------------------------------------------------|------------|

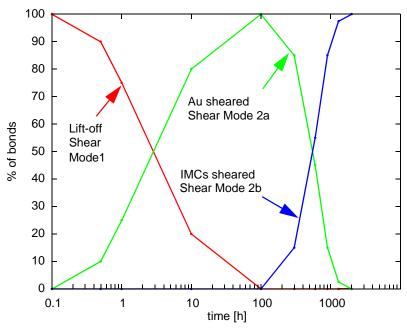

| Figure 60: Shear failure modes vs. time.                                                     | 75         |

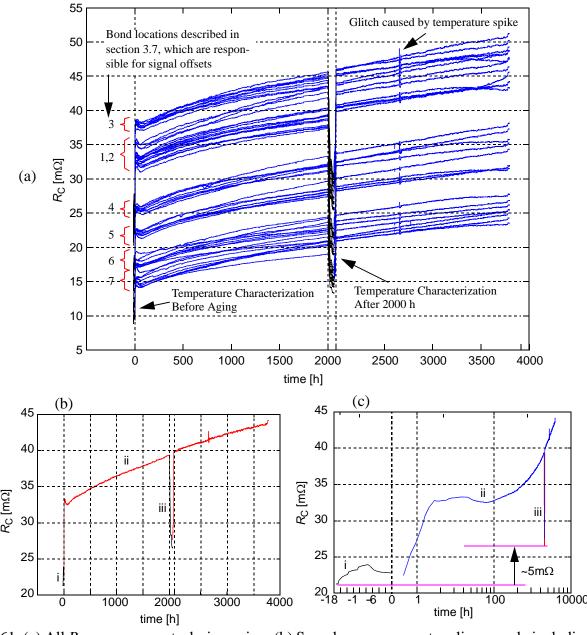

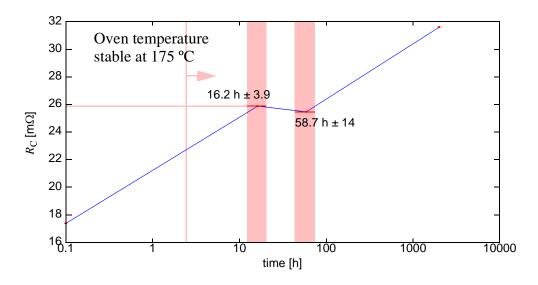

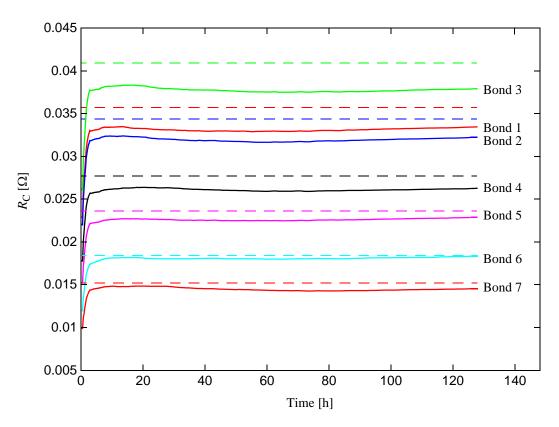

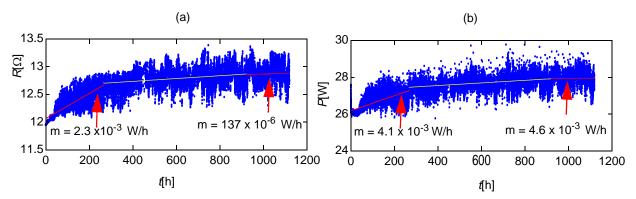

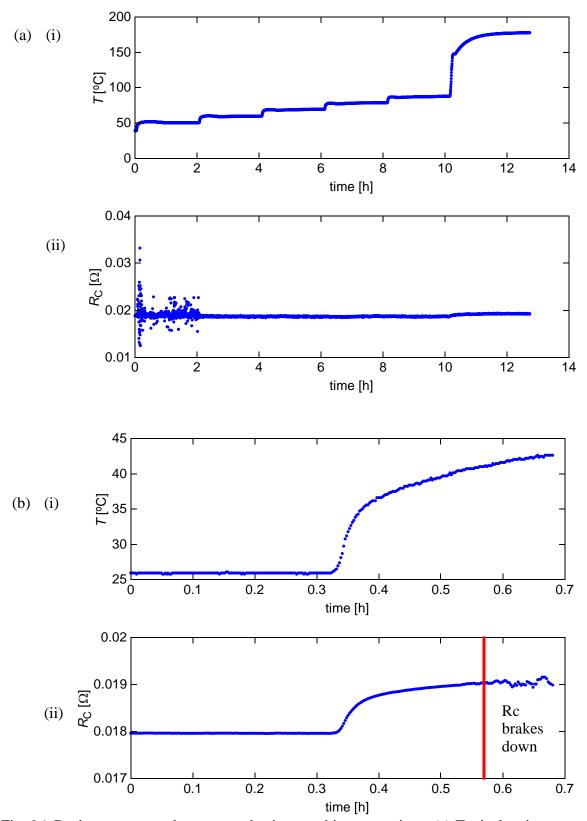

| Figure 61: (a) All R <sub>C</sub> measurements during aging.                                 | 7 <i>6</i> |

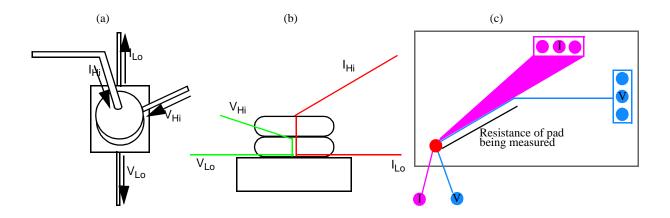

| Figure 62: (a, b) Contact resistance measured from a bond on small bond pad. All of the      |            |

| voltage drop occurs at the wire bond. (c) Contact resistance measured from bond on large     |            |

| rectangular pad used in this experiment. Part of the pad resistance is incorporated into the |            |

| measurement.                                                                                 | 77         |

| Figure 63: Average contact resistance for all bond locations.                                | 78         |

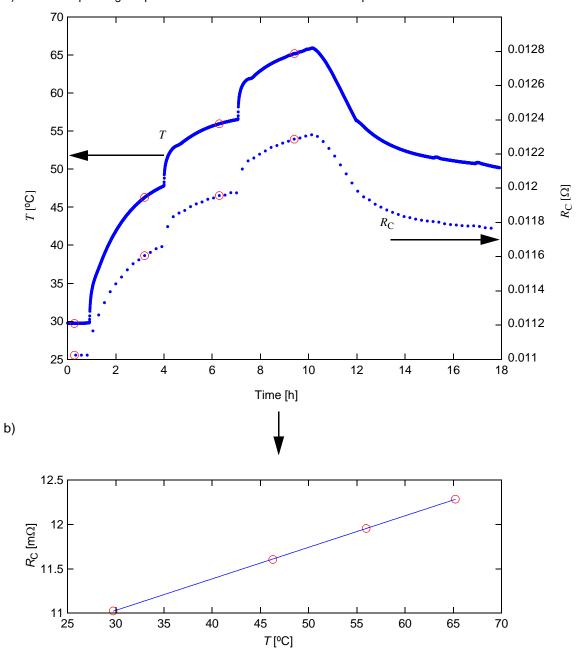

| Figure 64: Experimentally observed RC vs. TCR predicted resistance.                          | 79         |

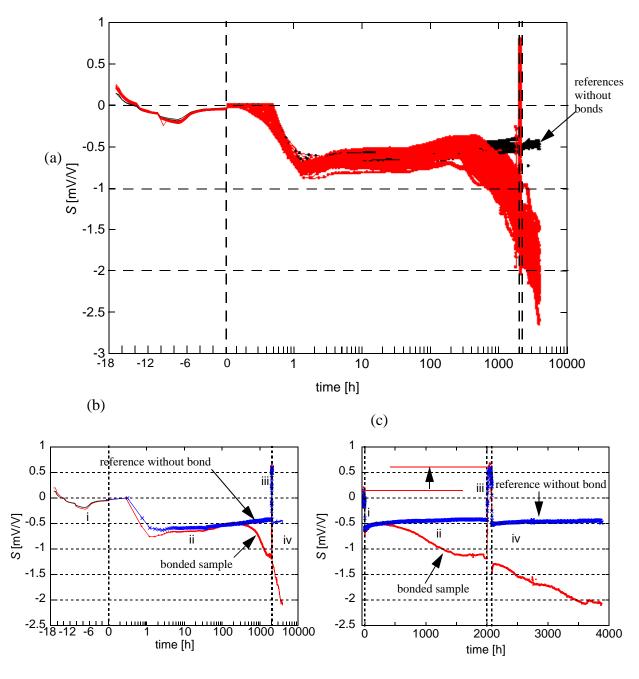

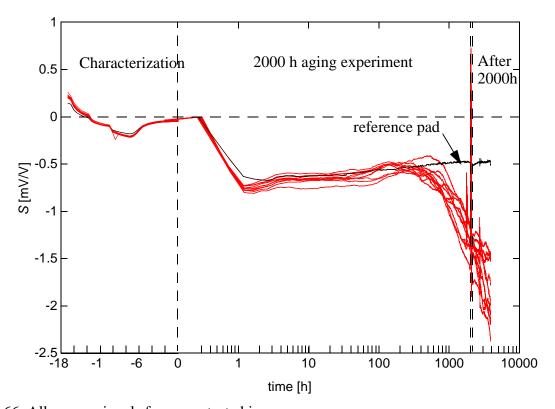

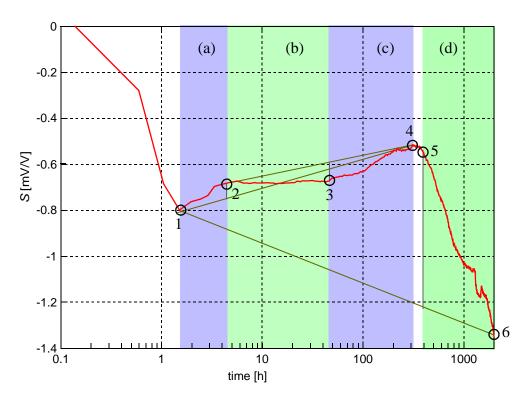

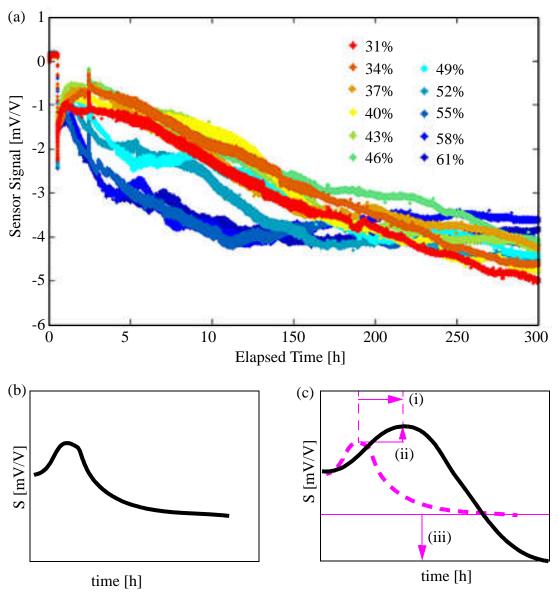

| Figure 65: (a) All sensor measurements during aging                                          | 80         |

| Figure 66: All sensor signals from one test chip                                             | 81         |

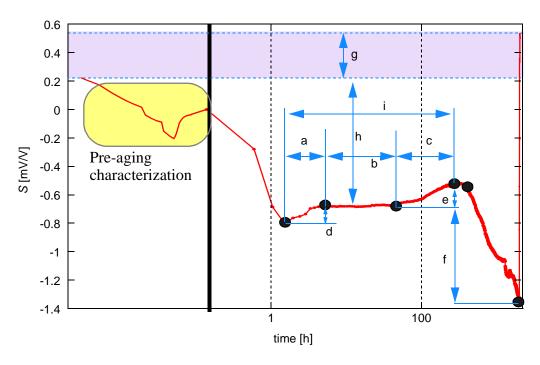

| Figure 67: Key points in stress signal profile.                                              | 82         |

| Figure 68: Stress signal, S, vs. lateral IMC growth.                                         | 83         |

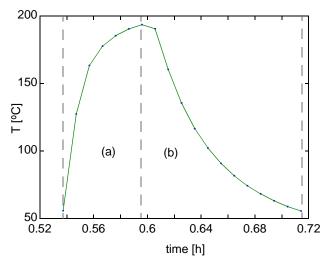

| Figure 69: Typical temperature ramp-up with measured S.                                      | 84         |

| Figure 70: Average S(T) before and after aging for reference pads, and bonded pads           | 85         |

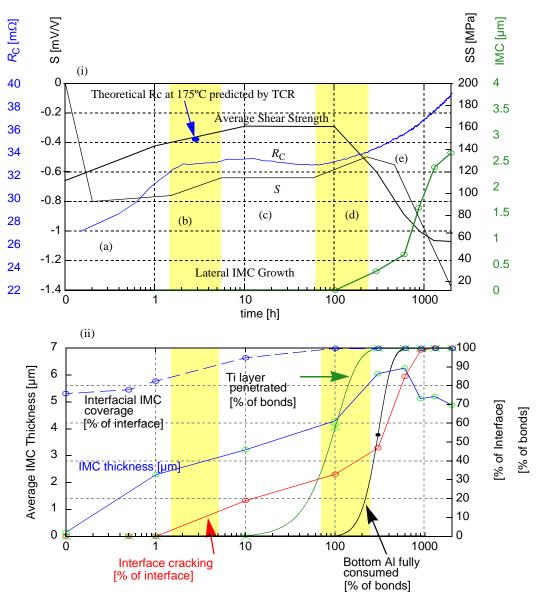

| Figure 71: Destructive and non-destructive measurements.                                     | 87         |

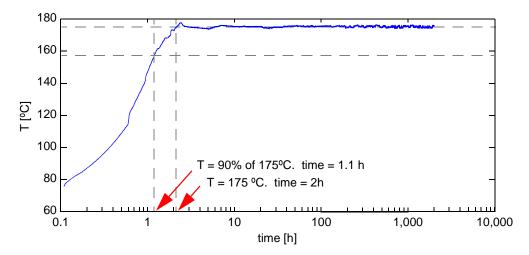

| Figure 72: Temperature profile during aging                                                  | 88         |

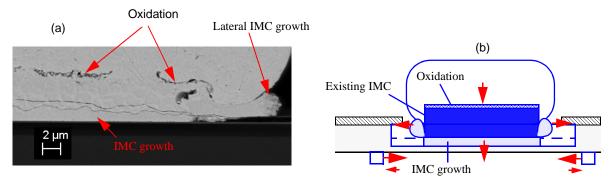

| Figure 73: Stage b.                                                                          | 89         |

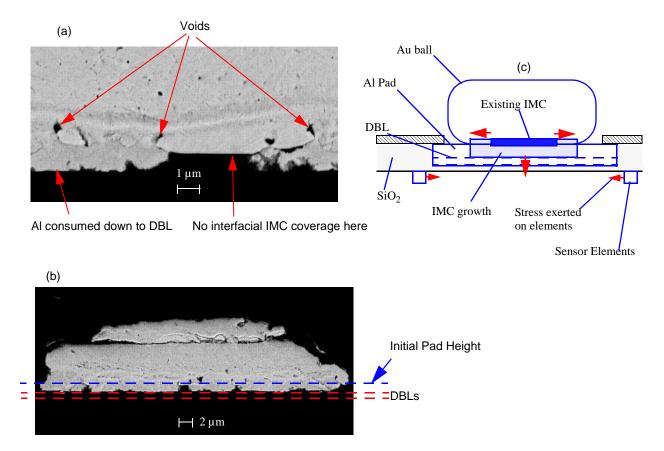

| Figure 74: Stage c.                                                                          | 91         |

| Figure 75: Typical cross sections.                                                           | 91         |

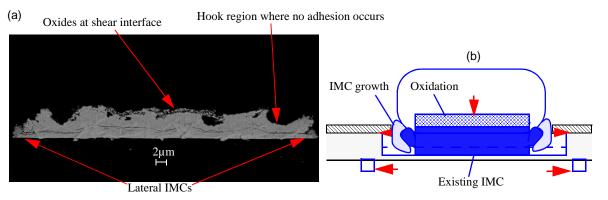

| Figure 76: Stage d.                                                                          | 92         |

| Figure 77: Stage e.                                                                          | 93         |

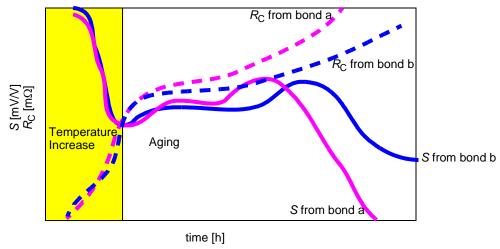

| Figure 78: Example of non-destructive signals for reliable and unreliable bonds              | 97         |

| Figure 79: (a) Bonds made at varying ultrasonic levels expressed as a percentage of          |            |

| maximum transducer amplitude, and aged at 200 °C. [30]                                       | 98         |

| Figure 80: Parameters used for early indicator correlation test.                             | 100        |

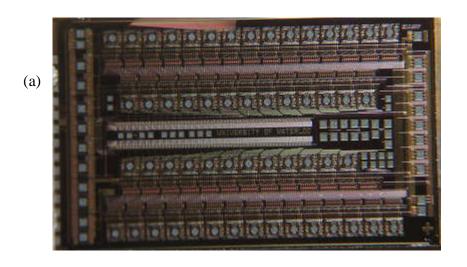

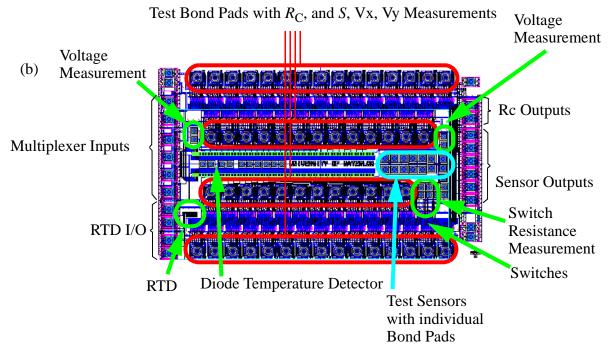

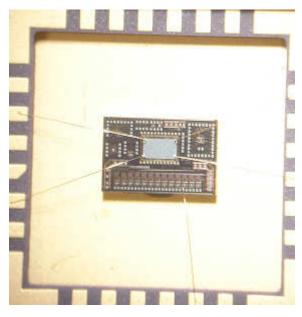

| Figure 81: Upgraded Test Chip.                                                               | 101        |

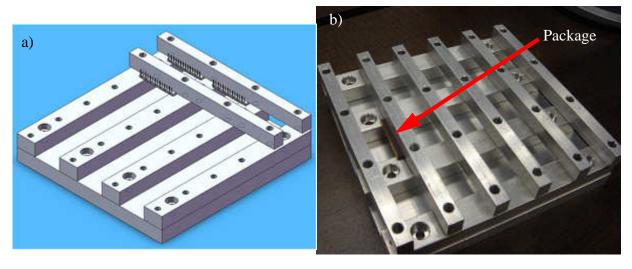

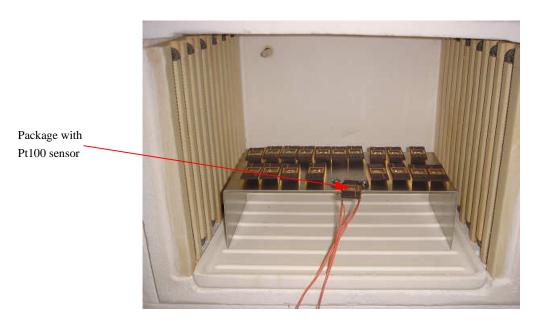

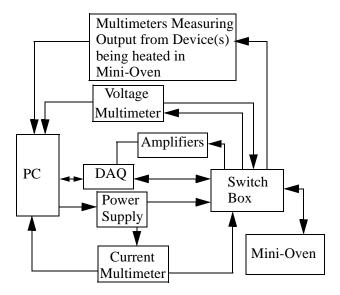

| Figure 82: Schematic of system                                                               | 102        |

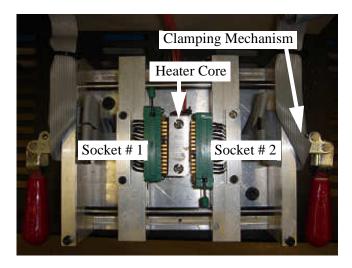

| Figure 83: Overview of mini-oven with components                                             | 103        |

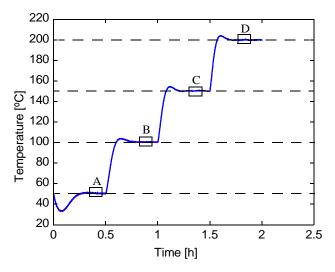

| Figure 94: Temperatures of both sides of the mini oven                                       | 105        |

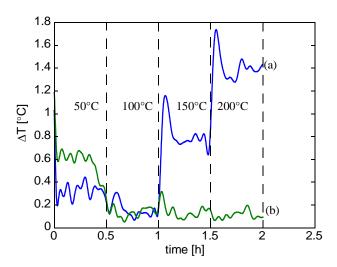

| Figure 85: (a) Largest and (b) smallest temperature differences between the two sides of |     |

|------------------------------------------------------------------------------------------|-----|

| the mini-oven at setpoint temperatures of 50°C, 100°C, 150°C, and 200°C                  | 106 |

| Figure 86: Locations of temperature measurements on mini-oven.                           | 106 |

| Figure 87: a) Resistance of heating wire during long term test                           | 108 |

| Figure 88: Temperature profile for thermal cycling test.                                 | 109 |

| Figure 89: Switchbox wiring diagram                                                      | 118 |

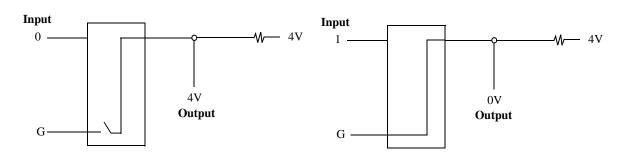

| Figure 90: Power amplification with transistor switches.                                 | 119 |

| Figure 91: Transistor Switch Operation.                                                  | 120 |

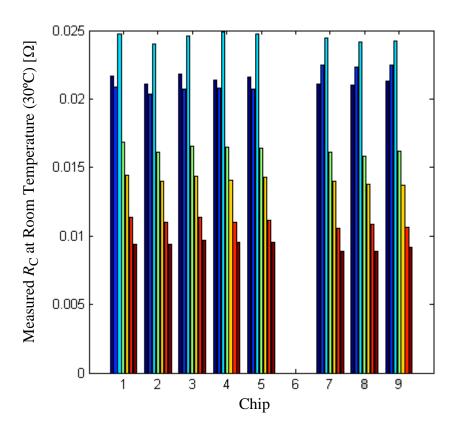

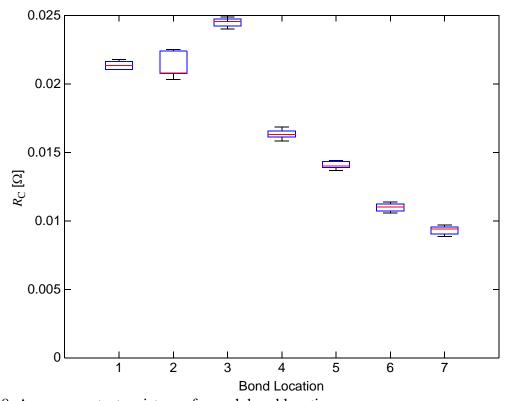

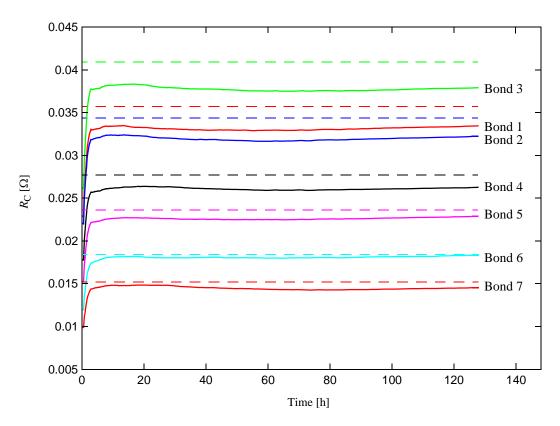

| Figure 92: Contact resistance variation between bonds                                    | 121 |

| Figure 93: Average contact resistance for each bond location                             | 122 |

| Figure 94: Temperature ramp-up used for TCR characterization.                            | 123 |

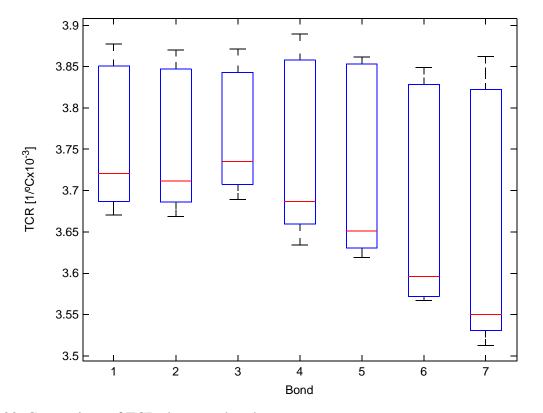

| Figure 95: Comparison of TCRs between bonds                                              | 124 |

| Figure 96: Experimentally observed RC vs. TCR predicted resistance.                      | 125 |

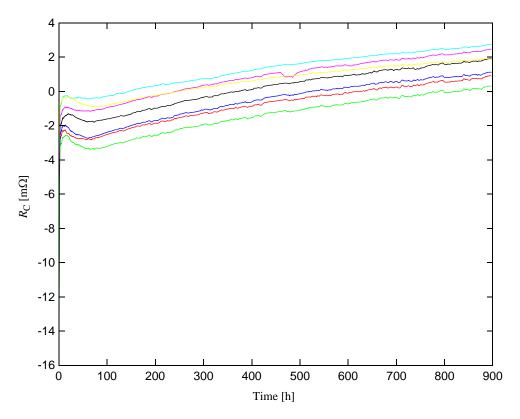

| Figure 97: Resistance data minus the TCR-predicted 175°C resistance                      | 126 |

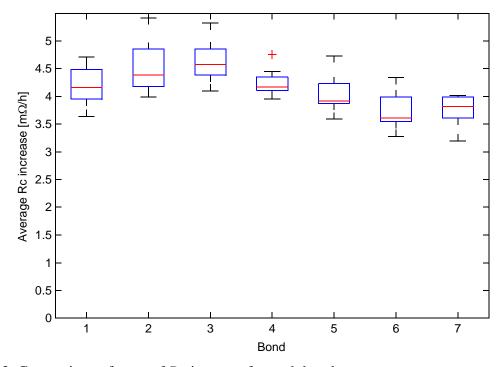

| Figure 98: Comparison of rates of RC increase for each bond                              | 126 |

| Figure 99: Wiring for pad resistance measurement.                                        | 127 |

| Figure 100: Resistance-temperature characterization for finding TCR of Al test pad       | 128 |

| Figure 101: Pad resistance drop experienced during 140 h of HTS at 175 °C                | 129 |

| Figure 102: Wiring diagram for measuring pad resistance using on-chip connections.       | 129 |

| Figure 103: Resistance can not be measured using on-chip connections.                    | 131 |

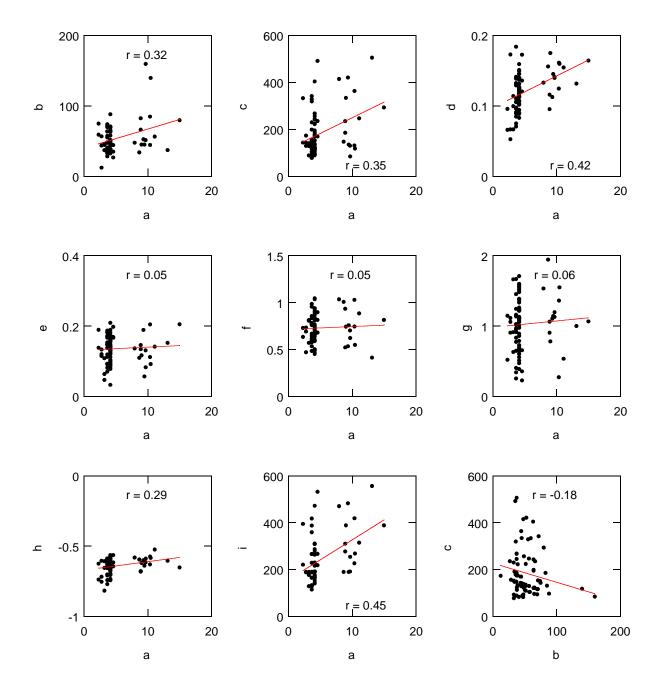

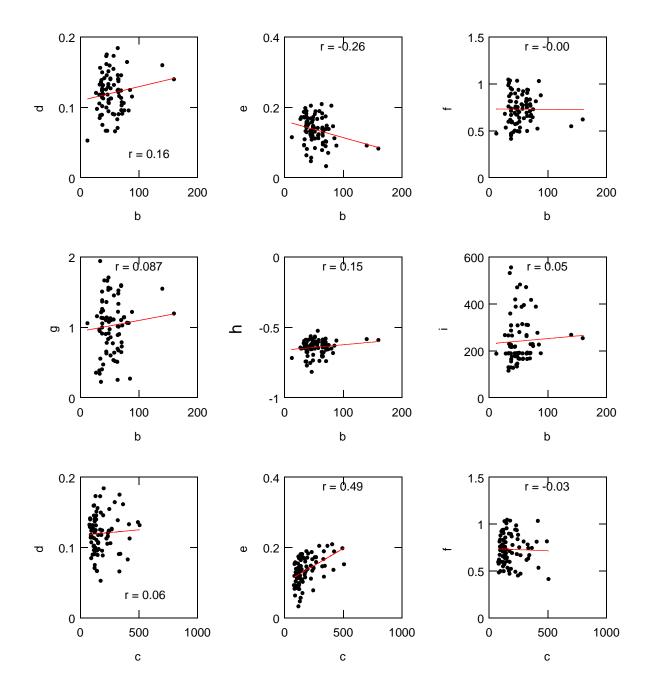

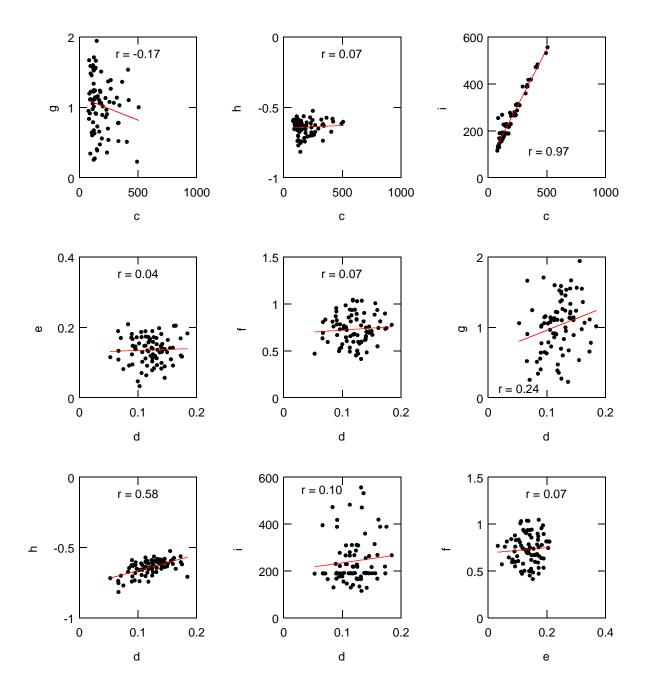

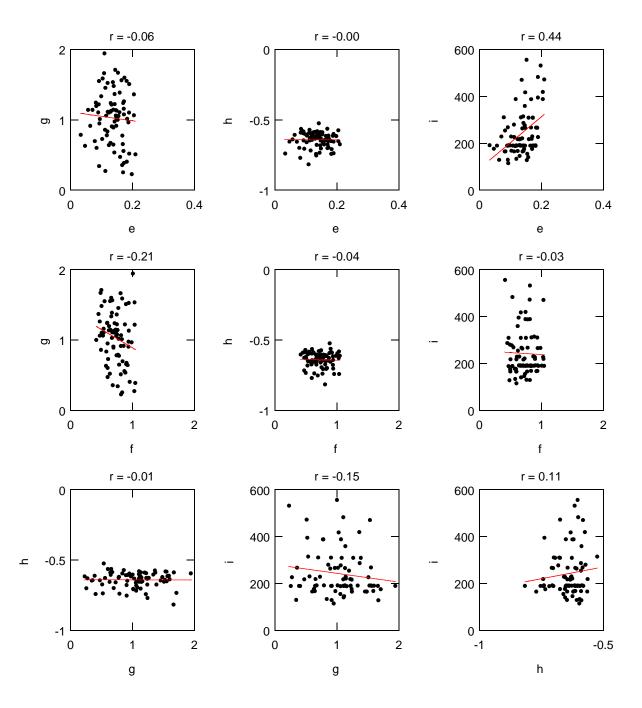

| Figure 104: Correlation tests for stress signal.                                         | 133 |

| Figure 105: Correlation tests for stress signal.                                         | 134 |

| Figure 106: Correlation tests for stress signal.                                         | 135 |

| Figure 107: Correlation tests for stress signal.                                         | 136 |

#### 1. Introduction

In microelectronic systems, computer chips are attached to substrates, electrically connected to the substrates, encapsulated, and then affixed to boards. The electrical interconnect between the chip and the substrate is most commonly made by the process of wire bonding where a thin wire is bonded first to pads on the chip and then to pads on the package.

#### 1.1. Reliability

Failure of key interconnections renders entire devices defective. As more than  $4x10^{12}$  wire bonds are made each year [1], it is of vital importance that wire bonds are reliable. Reliability depends on the structure of the bonding pad, the materials of the wire and the bond pad, contamination, and the process parameters used during bonding. When the process is optimized, reliability is greatly improved. Defect rates in industry using optimized bonds are typically 20 to 30 parts per million [1].

#### 1.2. Motivation

As the microelectronics industry evolves, there is an ever present need to increase the performance of devices while decreasing the cost. As integrated circuits become more complex, the I/O density increases, necessitating finer pitch of wire bonds. Due to the high cost of Au, different materials such as Cu are proposed for the wire bonding process as a means of cost savings. As a result, the wire bonding industry is faced with the challenge of optimizing the bonding process with a wide range of different wires so that the bond has a high initial strength and high long term reliability. As the initial strength of a bond is not necessarily related to its long term reliability, the reliability must be assessed by performing accelerated aging tests. In these tests, sample bonds are kept in high temperature storage for an extended period. Sometimes, sample bonds are periodically removed and evaluated for mechanical strength and sectioned in order to observe micro-

structural changes to explain the bond degradation. If the sample bonds are able to maintain an acceptable strength for a minimum time period then the process used is qualified as reliable. This qualification process is expensive and labour intensive, and provides a poor time resolution of results, as samples are destructively examined at discrete time intervals, or at the end of aging only. To learn more about reliability and find ways to increase it, the need exists for an alternative method of observing bond degradation which can monitor the bond interface in real time while providing results at a lower cost. Although standard qualification procedures will not be replaced, such an alternative gauge of reliability could prove useful for accelerating initial bond evaluation, and comparisons of bond materials, processes, and parameter values with respect to reliability.

#### 1.3. Non Destructive Reliability Test Methods

As a wire bond degrades, the interface between the bonded wire and the substrate undergoes various changes before electrically or mechanically failing. Intermetallic compounds (IMCs) form at the interface and on the adjacent pad material. As the pad metallization and bump interdiffuse and are consumed at different rates, the IMCs present at the interface grow and change over time [1]. Due to different interdiffusion rates, Kirkendall voids form both at the interface and in the pad material adjacent to the bond [2]. Due to coalescence of these voids and oxidation of IMCs [3], the bond weakens and cracks may develop.

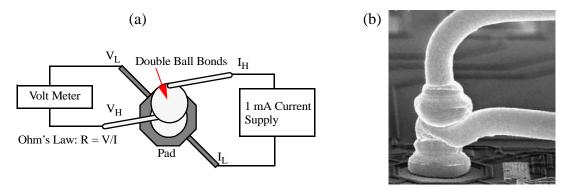

The two proposed methods of non-destructive bond monitoring are contact resistance measurements and stress measurements. Contact resistance measurements are performed by passing a current of 1 mA through the bond and measuring the voltage drop across the interface. Using Ohm's law, the contact resistance can be calculated. Contact resistance increases as bonds age which is attributed to reduced interface area and high resistance of IMCs [1].

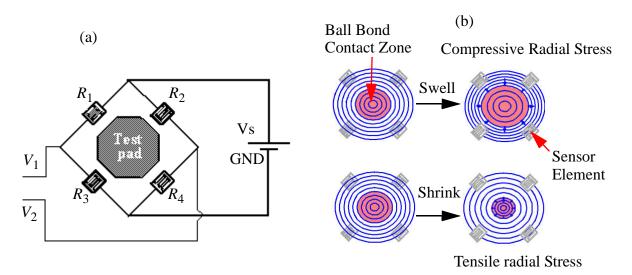

Stress measurements are accomplished by integrating piezoresistive stress sensors around bond pads in custom test chips [4]. As the bond interfaces expand or contract, a differential voltage signal generated by the stress sensor increases or decreases proportionally. These stresses are caused by volume changes due to interdiffusion and formation of IMCs with different densities. Both sensor signals and contact resistance may be monitored continuously and automatically, providing a high time resolution and requiring no additional labour once the aging process has started.

#### 1.4. Objective

The objective of this research is to characterize the usefulness of the integrated stress sensor to monitor bond aging in a typical wire bond product. To this end, multiple stress signals with contact resistance measurements are compared to shear test data and microstructural analysis of Au bonds on multilayer Al pads. Relationships between the non-destructive signals and destructive test data are investigated.

#### 1.5. Thesis Outline

In order to investigate the relationship between the non destructive signals and standard destructive tests, several steps are taken. Appropriate die attach, bonding processes, and accelerated aging regime are selected and setups are built to store the chips at high temperature and measure signals from integrated circuitry. In total, four sets of bonds are made on identical chips. Two sets are made for destructive analysis. One set is made for shear testing at discrete intervals and one set for cross sectioning and examining at the same intervals. Two sets are made for non-destructive testing. One set is made for contact resistance measurement and one for stress measurement. Once the chips are aged, samples from each interval are shear tested and sectioned. It is important to examine the bond cross sections as the microstructural changes occurring at the interface are used to explain the results from all other destructive and non destructive tests. These destructive

measurements are then compared to the non-destructive measurements and it is observed that microstructural changes such as IMC growth or oxide formation can be observed through stress signals and contact resistance measurements. While not enough data is available to directly correlate these results to standard bond failure criteria, the quality of a bond can still be estimated by observing the rates at which microstructural changes occur.

The final section of this thesis is the introduction of new methods to facilitate these measurements for future studies. A new test chip is designed which can take 55 contact resistance and stress measurements for the same bonds, while performing all multiplexing on-chip with integrated circuitry. This reduces the number of chips required and eliminates the need for dedicated multiplexers in the setup. A new miniaturized bond aging device is developed. This device heats the chip more rapidly than conventional ovens, while leaving all package connections at low temperatures and allowing for greater flexibility for setup changes.

#### 2. Literature Review

#### 2.1. Wire Bonding Process

The first level electrical interconnect between an integrated circuit and package or substrate can be achieved by a variety of methods such as flip chip, tape automated bonding (TAB), and wire bonding. The flip chip process involves deposition of solder balls or non-solder bumps onto chip pads, flipping the chip over and mounting it on external circuitry, and then achieving electrical connection through the bumps. This method creates the highest I/O density but is cost intensive and inflexible to process changes [1].

TAB was developed as an alternative to wire bonding in the 1960s when the wire bonding process was much slower and less efficient [1]. TAB uses solder or Au bumps to attach integrated circuits (IC)s to a thin tape which contains the circuitry for attachment to a PCB. Due to advances in wire bonding technology to increase speed and reduce pitch of wire bonds, this method is largely obsolete for mainstream applications, although still has a niche where high production volume and high chip cost make it economical, such as flat-panel displays [1].

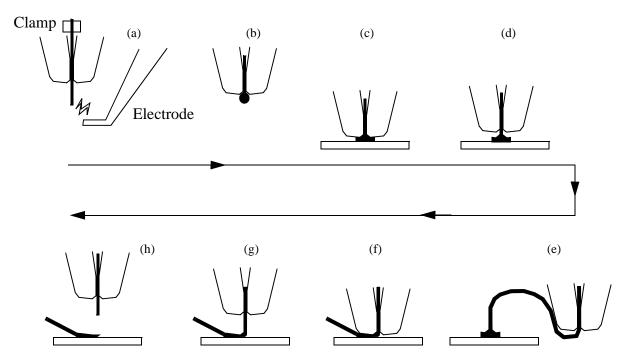

Wire bonding is the most common first level interconnect method accounting for approximately 90% of the total microelectronics packaging over the last decade [5]. It is popular due to its relative low costs, high speed, and flexibility of design changes. Wire bonds can be either wedgewedge bonds or ball-wedge bonds. Both processes use pressure and ultrasonic energy. In the ball bonding process, the device to be bonded is die-attached to a substrate or package and placed on a heater on the wire bonder. A wire is fed through a capillary and clamped in place with the end of the wire protruding from the capillary tip as shown in Fig. 1 a. An electrode then applies a spark known as the electrical flame off (EFO) which melts the end of the wire. Surface tension causes the molten metal to form a free air ball (FAB) which rapidly solidifies at the end of the wire as

illustrated in Fig. 1 b. The capillary presses the free air ball onto the bond pad with an impact force, deforming it to its final shape (Fig. 1 c). The deformed ball is then held in place with a bond force which is low enough to ensure that no further deformation takes place, as a transducer applies ultrasonic energy to the capillary tip creating a solid state bond between the ball and pad. The clamp holding the wire then relaxes (opens), and the capillary moves to the location of the second bond while the wire is fed through as shown in Fig. 1 d-e. The capillary presses the looped wire onto the bond pad of the package, and bonds it using pressure, heat and ultrasound. This bond is known as the second bond, and is also referred to as the wedge bond, stitch bond, or crescent bond. Then, the capillary and the open clamp move upwards by a certain distance, feeding out a defined length of wire before stopping. The clamp closes, preventing any more wire from feeding through the capillary. The capillary and clamp then move upwards again, causing the wire

Fig. 1 Wire bonding process. (a) FAB formation. (c) Impact deformation and thermosonic bonding. (e) Looping. (f) Second bond formation through heat, pressure and ultrasound. (g) Wire feed. (h) Tail breaking.

to break at its weakest point which is located where the wire is pinched after the second bond location as is seen in Fig. 1 h. This leaves a wire tail hanging from the capillary which is available for formation of the FAB of the subsequent bond.

The wedge-wedge wire bond process consists of 2 wedge bonds instead of one ball bond and one wedge bond. In this process the wedge bond loops must be oriented in the same direction as the ultrasonic transducer, requiring a dedicated rotational axis, while the second bond of a ball bonding process may be positioned at any angle. Wedge-wedge bonds are often used for bonding Al wire or ribbons onto Al bond pads, and are generally preferable where extremely low loop heights or room temperature Al bonds are required [1].

#### 2.1.1. Wire Bonding Materials

In a wire bonding process, the wire material must adhere to the bond pad materials for the first and second bonds. The most common wire material is Au due to its absence of oxide and good formability. The degree of purity is expressed as the percentage of Au in the wire. For example wire that is 99% pure Au is referred to as "2N" since the percentage is expressed with 2 nines. Wire that is 99.99% pure Au is referred to as "4N" which is the wire used in the experiments described in this thesis. The remaining 0.01% wire composition includes various dopants such as Cu, Be, Ni and Pd which although supplied in small amounts can greatly improve the wire properties. Interstitial dopants such as Be increase the mechanical strength of the alloy by hindering dislocation movement [5]. Substitutional dopants such as Pd, create much larger stress fields and strengthen the wire even more. With the exception of Pd, however, most dopants significantly reduce the conductivity of the wire [5].

Other wire materials used in industry include Cu wires, and insulated wires. Cu wires have the advantage of being less expensive, but oxidize quickly in air, and form harder FABs. Cu requires

greater bond force and ultrasound, increasing the likelihood of pad damage or chip cratering [6]. To prevent oxidation, the wires must be stored in an inert environment and a shielding gas must be supplied during bonding [6]. Although Cu oxide is removed from the ball during FAB formation, it remains on the wire and may interfere with reliable second bond formation.

Insulated wires are coated with a thin organic layer which burns off during the EFO process and flows out of the bond during ultrasonic application. These wires may touch each other without short circuiting, and the coating prevents Cu wires from oxidizing. With appropriate process adjustments, these wires reach standard bond quality by removing the insulation layer from the bond interface [7].

Wire bonds can be made on many substrates, including Ag metallizations [7], Au, or Al. When wire bonds are to be made between a chip and a ceramic dual in-line (CerDIP) package, as is the case for this thesis, the material of the chip bond pad is Al containing small amounts of dopants, typically Cu and Si [1, 3], and the final surface finish of the package lead is Au. Exact compositions of bond wires and bond pad metallizations are not disclosed by the manufacturers and are not essentially required for the conclusions of this study.

#### 2.1.2. Bonding Mechanisms

When the crystal lattices of two materials align, a solid state bond is formed. Main impediments to bond formation are roughness, lattice mismatch, and contamination. For chips manufactured with standard CMOS processes, surface roughness is not a problem. Roughness which may exist on bond pad or FAB surfaces is flattened out during the impact deformation of the ball, and during the application of ultrasound. Au and Al both have FCC crystal structures with lattice parameters of 4.07 Å and 4.05 Å respectively [8]; therefore lattice mismatch should pose no problem to bond formation. Contamination risks may be minimized by proper cleaning and storage of chips.

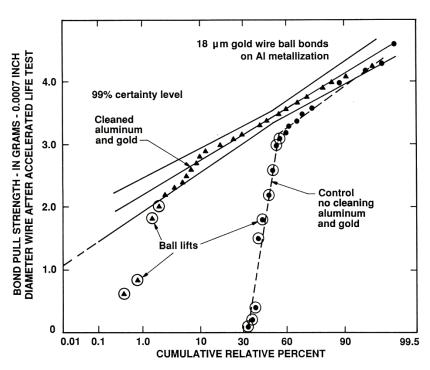

Plasma cleaning is a common method of cleaning chip pads where  $O_2$ , Ar, or  $H_2$  are typical plasma constituents. The ionized gas bombards the pad surface and can knock off contaminants by impact. When  $O_2$  is used, it can break down by the reaction  $O_2 \rightarrow 2O$ . The individual O atoms now react with hydrocarbons on the surface, removing them [1]. Fig. 2 shows the improvement in bond reliability which may be attained through plasma cleaning. Storage in a low humidity nitrogen environment may further protect the chip from contamination between the cleaning and bonding stages.

Plasma cleaning removes foreign contaminants, but the oxide which forms on the surface of the Al bond pad still remains and prevents bonding from occurring. This oxide is removed during the ultrasonic process. The friction of the Au ball breaks the oxide which then disperses away from the interface allowing Au to bond with the pure Al.

Fig. 2 Pull strength of Au bonds on Al metallizations with and without plasma cleaning after 300°C high temperature storage for 4 h [1].

An indication of a strong bond is the presence of intermetallic compounds (IMCs) at the interface. While IMC formation is not necessary for a solid state bond to form, IMCs indicate that extensive interdiffusion has occurred resulting in a metallurgical bond [1].

#### 2.1.3. Important Parameters for Wire Bond Optimization

Several process parameters are important for producing a bond of desired shape with optimized strength, which vary depending on the bonding method used. The standard method of ball bonding involves ball deformation through impact with the substrate before ultrasonic bonding begins and is known as the impact deformation process [1, 9]. This is the method used for experiments described in this thesis. An alternative method of ball deformation combines force and ultrasound in a process called ultrasound enhanced deformation (UED) [9]. For the impact force deformation process, the final bonded ball geometry, defined by bonded ball diameter and bond height, is a product of the impact force and the FAB diameter [9]. The FAB diameter in turn is a product of the EFO current, wire tail length, and the EFO time. All process times are typically fixed at standard values, and are not varied between processes. The wire tail length is also held constant, and only the EFO current is modified to optimize FAB size.

Optimized bond strength for a given geometry depends on bond force, bond time, temperature, and ultrasonic power which is varied to achieve the peak strength [1]. Bond temperature is one of the most important parameters for bond shear strength [1]. Typically, bonds are made at temperatures of at least 175°C in order to ensure formation of a strong bond. Once bond force, temperature, and bond time are established, the bond strength is maximized by optimizing the ultrasound. Maximizing bond strength reduces the chance of bond failure and extends the operating life of the bond. The quality of an optimized ball bond is also expected to vary less between samples than the quality of a non-optimized bond [1].

#### 2.1.4. Bond Evaluation by Pull Test

The pull test is a destructive method of bond strength evaluation developed in the 1960s in which a hook is placed under the wire loop, and pulls the wire upwards until failure occurs [1]. The pull force exerted is measured and indicates bond strength. In order to measure the strength of the wedge bond, the hook is located towards the middle of the loop. To measure the strength of the ball bond the hook is located as close to the ball as possible for a vertical pull direction [3]. While the pull force is an excellent indicator of wedge bond strength, it is not always ideal for evaluating ball bonds. If a minimum of approximately 15% of the interface is bonded, due to the large interfacial area of the ball, failure will occur at the heat affected zone of the ball neck rather than at the pad interface [1], and little information is provided on the ball bond interfacial strength.

#### 2.1.5. Bond Evaluation by Shear Test

The shear test directly measures the strength of the bond interface and is therefore more useful than the pull test in assessing interfacial strength. The shear test is a destructive test where a chisel shaped shearing ram pushes a ball bond off its bond pad at a constant speed, and the force required to break the bond is recorded. Shear strength can be calculated by dividing the required force by the bonded ball diameter to gauge the strength of the bond. Failure may occur according to six distinct modes [10]:

- Mode 1. Bond Lift: The entire bond is lifted off the surface leaving only an imprint.

- Mode 2. Bond Shear: Intermetallics are left on the bond pad or a large portion of the Au bond is left behind.

- Mode 3. Cratering: Pad material and insulating SiO<sub>2</sub> is removed along with the bond.

Mode 4. Bond surface contact: Shearing ram contacts chip and removes metallization layer.

Mode 5. Shearing skip: Shearing ram is too high and shears top of the bond near the wire.

Mode 6. Bonding surface lift: The bond pad metallization separates from the chip and is removed with the bond.

Mode 1 failure indicates lack of adhesion between bond and pad. Ideally bonds should exhibit mode 2 failure.

#### 2.2. Wire Bond Reliability

When a new bond process is developed, reliability is typically assessed by a number of standard aging tests, e.g. by aging the bonds at elevated temperature while shear testing and/or pull testing them at periodic intervals. Such high temperature storage (HTS) is performed at various temperatures above 150 °C. A temperature of 175 °C is often used because this is the curing temperature of common moulding compounds which are used in industry to encapsulate bonded dies [5, 3]. If hermetic package sealing is required, the bonds are exposed to temperatures up to 300°C for several mins; however for applications requiring hermetic packaging, Al wires are generally used instead of Au [5].

As wire bonds age in HTS, changes occur at the bond interface which over long periods of time (>1000 h) weaken the bond. This weakening is generally measured by shear tests or pull tests, and observed through cross sectional analysis. It is possible that the microstructural changes causing this weakness may be also observed through monitoring the contact resistance [1, 11, 4] and radial stress fields generated by the aging bonds [4].

#### 2.2.1. Microstructure Evolution

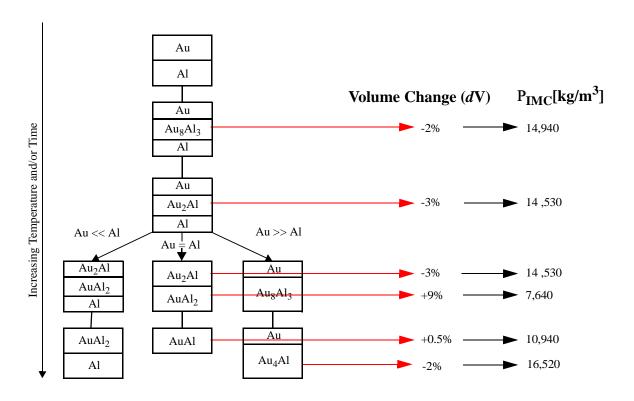

The driving force behind microstructural evolution is the diffusion which occurs between the Au wire bond and the Al pad. IMC formation starts during the bond process and is indicative of strong adhesion. As the metals interdiffuse, IMCs will form according to local availability of each metal. Au<sub>8</sub>Al<sub>3</sub> is expected to form first, followed by Au<sub>4</sub>Al, Au<sub>2</sub>Al, AuAl and AuAl<sub>2</sub>[1]. The exact composition of the IMC denoted Au<sub>8</sub>Al<sub>3</sub> is debated, and in some phase diagrams is identified as Au<sub>5</sub>Al<sub>2</sub>[1, 2].

Conditions of the bonds and environment during HTS influence the rate of microstructure evolution and bond failure. Important parameters are wire composition (2N or 4N), HTS temperature, contamination and atmosphere. 4N wires are used for their low resistivity and large bonding parameter windows, yet readily form IMCs during HTS. 2N wires are doped with Pd, Pt, or Cu which increase strength and slow IMC formation (and therefore bond degradation) [12]. HTS temperature is directly related to the rates of phase transformation and cavity growth. A higher temperature results in more rapid acceleration of the aging process.

Contamination on bond pads and wire reduces reliability. When contamination is severe, and too thick carbon or oxide layers are present on pad surfaces, bonds form less readily and have lower shear strengths. When contaminants are present in lower concentrations, the initial shear strength is unaffected. Koeninger et al [11] report that reliability is unaffected by addition of low levels of contaminants. Harman [1] however, reports that impurities concentrate ahead of the IMC growth and eventually form precipitates. These precipitates attract vacancies resulting from Au and Al diffusion, which eventually coalesce into cavities lowering reliability.

The aging atmosphere can reduce reliability by promoting corrosion or oxidation. Oxidation of IMCs which cannot occur in an inert atmosphere is prevalent in an air atmosphere. In a corrosive atmosphere (35 mbar HCl), failure is greatly accelerated [11].

In this work, 4N wire is used to make bonds aged at 175°C. Contamination is minimized by plasma cleaning and vacuum storage of chips, and an air atmosphere is used for HTS. The following are case studies from literature which evaluate microstructural evolution of bonds made and aged with similar conditions.

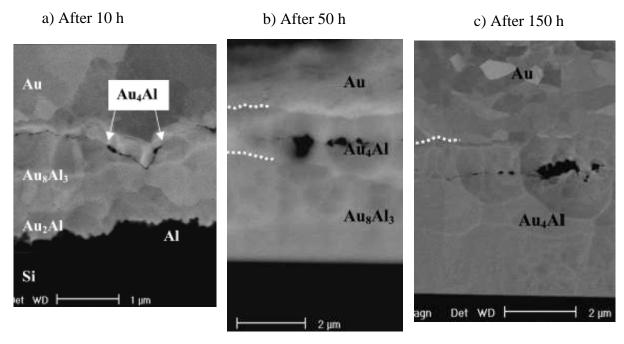

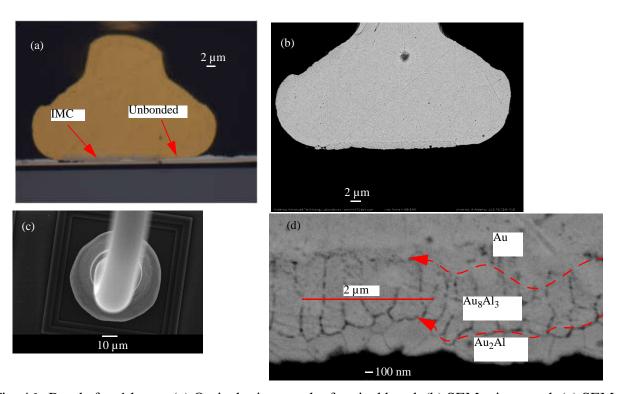

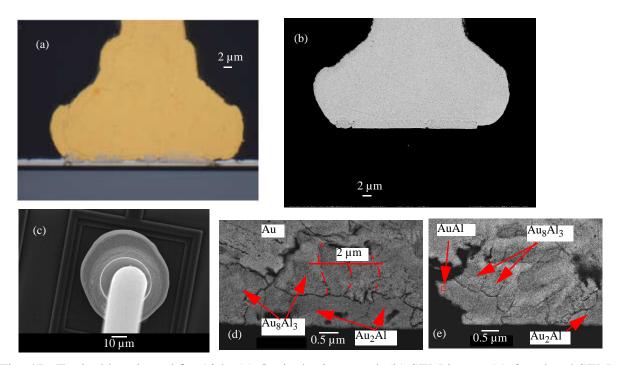

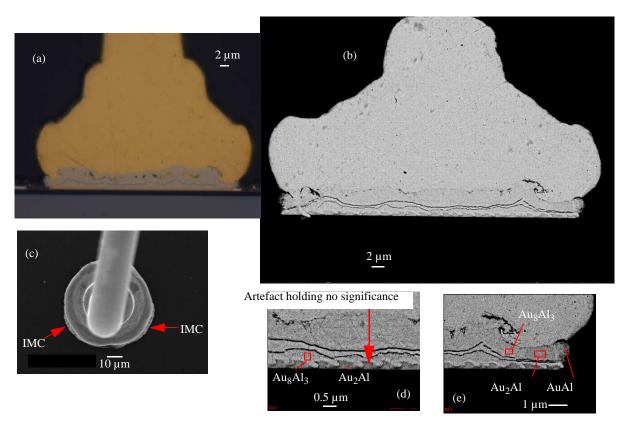

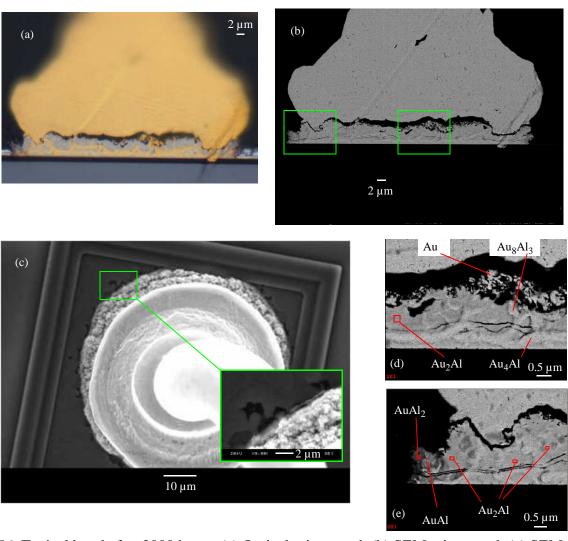

In [13], Noolu observes the formation of 3 intermetallic layers after 2 h of aging 4N Au wire bonds on Al pads at 175 °C. Underneath the ball there is a layer of Au<sub>4</sub>Al. Next is a layer of Au<sub>8</sub>Al<sub>3</sub>, followed by a layer of Au<sub>2</sub>Al, and finally the Al pad metal. After 10 h of aging, the Al pad under the ball bond is almost entirely consumed. Due to a large amount of Au, with decreasing Al supply, the Au-rich phases (Au<sub>4</sub>Al and Au<sub>8</sub>Al<sub>3</sub>) expand down towards the chip surface. After 50 h, the Au<sub>2</sub>Al phase has completely converted to Au<sub>8</sub>Al<sub>3</sub>. After 150 h, the Au<sub>4</sub>Al phase has completely replaced all other IMCs and is the only remaining phase. Microstructural evolution as observed by Noolu can be seen in Fig. 3. A minor EDS investigation is pursued to determine the formation of intermetallics lateral to the ball bond. In a cross section of a bond aged 150 h, Au<sub>2</sub>Al, AuAl and AuAl<sub>2</sub> phases were found between the IMCs under the bond and the remaining Al pad adjacent to the bond.

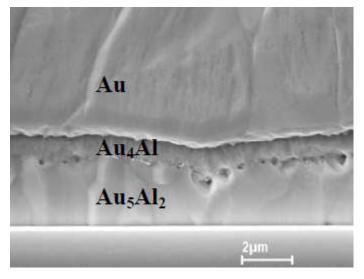

In Fig 4, a different microstructural evolution is observed in which the Au<sub>5</sub>Al<sub>2</sub> IMC eventually dominates and only a thin strip of Au<sub>4</sub>Al is present next to the Au ball after 1000 h HTS at 175°C [2]. In this case the Au<sub>4</sub>Al acts as a barrier preventing Au from diffusing into the Au<sub>5</sub>Al<sub>2</sub>.

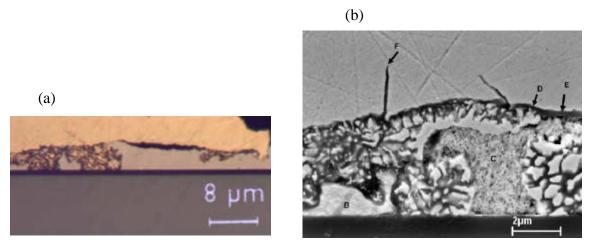

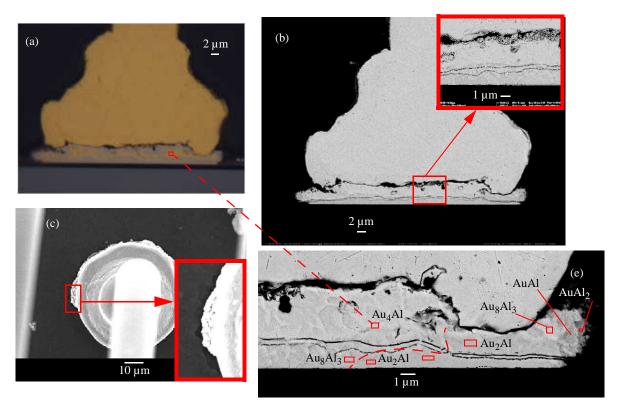

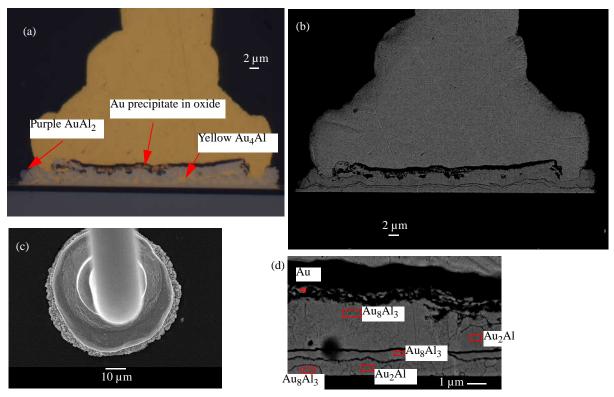

Another potential microstructural evolution is proposed that involves the oxidation of the Au<sub>4</sub>Al [3]. Optimized Au bonds on Al pads are aged at 175°C for 2000h. By 50 h, IMCs under the bond

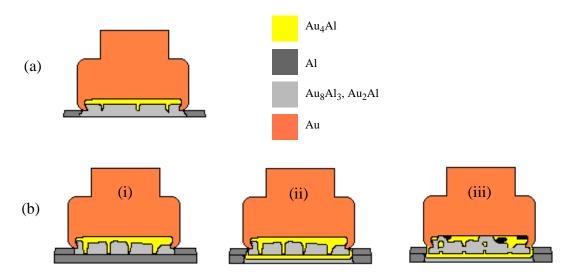

Fig. 3 Microstructure evolution as reported in [13]. (a) After 10h aging at 175 °C, IMCs have formed at the bond interface.  $Au_4Al$  is nearest the ball,  $Au_8Al_3$  comprises the majority of the IMC layer, and  $Au_2Al$  forms nearest the pad. (b) After 50 h aging, the entire pad is converted to IMCs. The majority of the IMC layer is  $Au_8Al_3$ , and  $Au_4Al$  is present near the bond. (c) After 150 h of HTS, the IMC layer has entirely converted to  $Au_4Al$ .

Fig. 4 Microstructure dominated by  $Au_5Al_2$  with only a thin layer of  $Au_4Al$  present [2]. Note that the IMC referred to here as  $Au_5Al_2$  is often reported as  $Au_8Al_3$ .

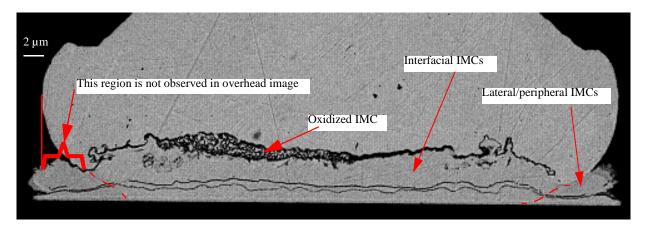

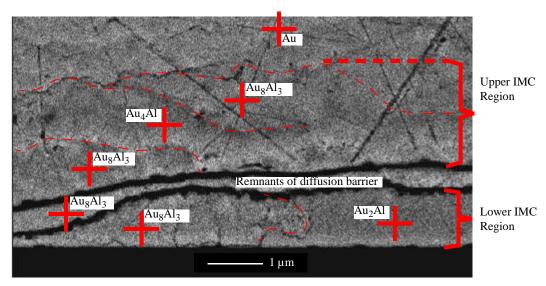

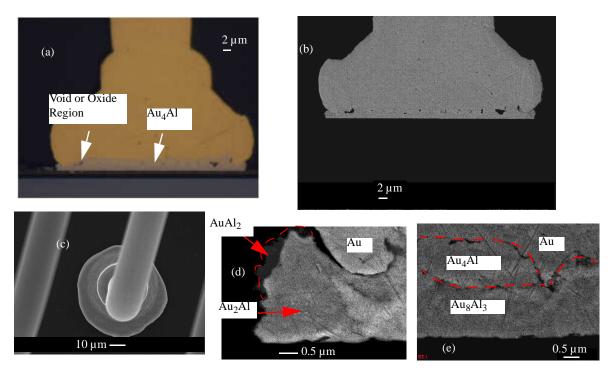

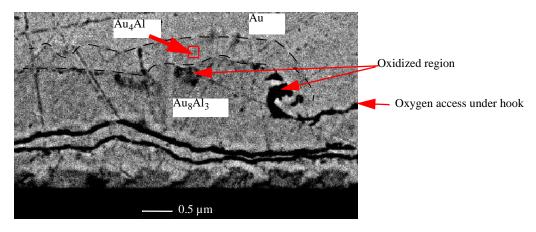

consist mainly of  $Au_8Al_3$  with  $Au_4Al$  bordering the ball and by 1000 h,  $Au_8Al_3$  has transformed into a second separate lower layer of  $Au_4Al$ . Between 1000 and 2000 h, the majority of the  $Au_4Al$  oxidizes. Oxygen absorbs onto surface of the peripheral  $Au_2Al$  and diffuses along the  $Au_4Al$  interface until it reaches the  $Au_4Al$  at the bond interface [3]. The original  $Au_4Al$  layer next to the ball forms an oxide layer that is well adhered to the ball. The bottom layer of  $Au_4Al$  transforms into a 2-phase composite with a dark oxide matrix and Au precipitates as shown in Fig. 5. During pull tests, failure occurs at the crack which forms between the top and bottom oxide layers. Sritharan et al. [14] confirm that the oxidation rate constant,  $k_p$  (which defines the increase of oxide mass per surface area per second [14]), is more than 2.5 times higher for  $Au_4Al$  than for any other IMC or for the base Al, so oxidation should occur more readily in this layer. The proposed oxidation reaction is:

$$4Au_4Al + 3O_2 \rightarrow 2Al_2O_3 + 16Au$$

(1)

It is estimated that this reaction will cause a 7% volume expansion [3] which generates stresses potentially resulting in cracks.

Fig. 5 Oxidized Au<sub>4</sub>Al layer [3]. (a) Optical image. (b) SEM image. Light Au precipitates in dark  $Al_2O_3$  matrix

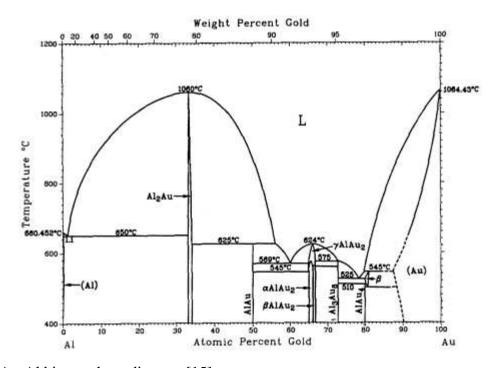

Controversy exists as to whether  $Au_8Al_3$  and  $Au_5Al_2$  reported in [15] and [1] respectively are the same phase, and if so as to which stoichiometry is correct. For simplicity, in this thesis all phases with an Au:Al ratio of 70:30 to 74:26 will be referred to as  $Au_8Al_3$  in accordance with the phase diagram reported by Okamoto [15] shown in Fig. 6.

Multilayer pads designed for increased reliability also include Ti which becomes introduced into the IMC microstructure. During HTS in [16], a 3 layer pad is used which consists of a top Al bonding layer, an intermediate Ti diffusion barrier, and a lower Al conduction layer. The Ti layer prevents diffusion of Al from the lower Al layer to the IMCs which form at the upper layer, and prevents electromigration. During aging at 450 °C, the Ti layer is broken, and assimilated into the microstructure as a Ti rich diffusion layer. Breaking of the Ti layer has no effect on bond contact resistance.

Fig. 6 Au-Al binary phase diagram [15]

#### 2.2.2. Voiding and Cracking

In [13], Noolu observes a row of discontinuous voids between the 4N Au and the small discontinuous regions of intermetallics which form between the Au ball and Al pad metal in unaged bonds. After 150 h aging at 175 °C, crack propagation due to coalescence of voids starts at the edge of the bonds. As the bond ages further, these cracks propagate towards the center. While it is proposed that the cracking is due to Kirkendall porosity [1, 5, 13], Noolu reports that cavities are formed due to stresses arising from volume changes as different IMCs form. Coalescence of cavities along the void line causes the bond to separate from the chip.

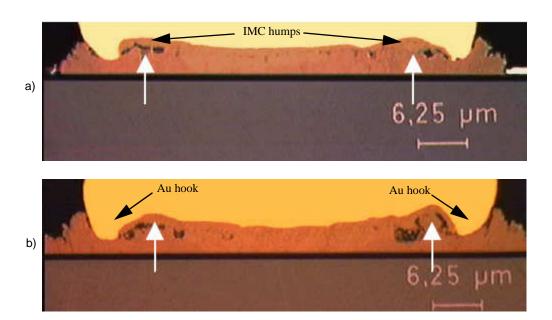

In [2], Breach notices that voids begin to form within 5 µm of the outer edge of the bond within 20 h of aging. After 200 h, the intermetallic layer has grown up in 2 humps at the same location. The Au metal hooks around the outside of the IMC humps, and cracks form around the humps progressing towards the center of the bond pad as shown in Fig.7. Although the cracks are not discussed in detail, it appears that they grow between the IMC layers as opposed to between the Au

Fig. 7 Crack growth around Au "hook" [2]. (a) Sample after ageing at 175°C for 500 h. (b) Sample after ageing at 175°C for 1000 h. Cracking appears to happen between 2 different IMC layers.

and IMC layers as reported by Noolu. Breach proposes that 2 forms of  $Au_4Al$  are present: a fine columnar grained cubic alpha phase next to the Au ball, and a thick coarse grained version of the  $\alpha$ -Au<sub>4</sub>Al phase next to the  $Au_5Al_2$  which forms later. Void formation at the interface between these two layers is credited to either the Kirkendall effect due to Au being transported to the lower  $Au_4Al$  layer [2] or by oxidation of the  $Au_4Al$  layers [3].

The Au hooking effect shown in Fig. 7 b is explained by Karpel [17] as a lack of bonding at the periphery of the deformed ball. When the bond force is applied, the majority of the force is transferred to the material under the capillary. The peripheral Au is subjected to the ultrasonic energy with a lack of bond force, resulting in minimal bonding and IMC formation in this area. When IMCs that formed under the bond grow upwards, the un-alloyed Au forms a hook with an incipient crack between the ball and substrate which allows oxygen to reach the interfacial IMCs.

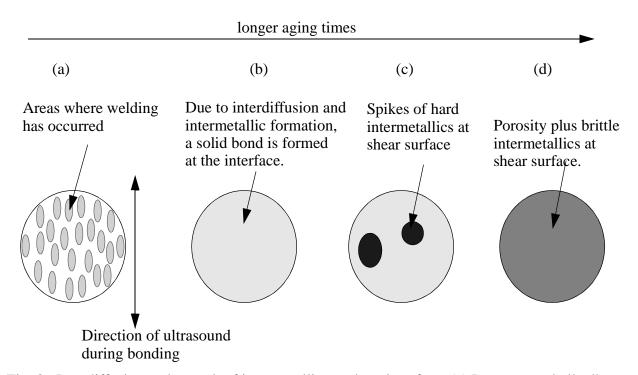

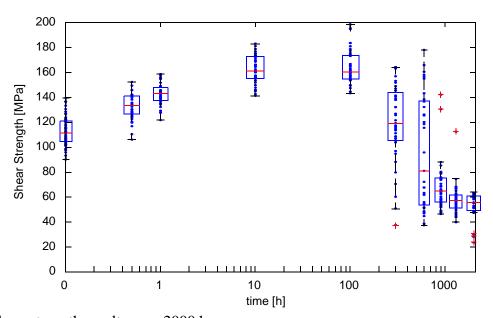

#### 2.2.3. Shear Strength During Aging

When a gold wire is thermosonically bonded to a pad, bonding between Au and Al occurs at discrete islands on the bond interface [1, 2]. Therefore, in bonds that have not been sufficiently aged, the weakest point is the bond interface, and during shear testing the bonds lift off, failing in shear mode 1. As the bond ages, the Al pad is consumed as interdiffusion takes place and IMCs form. The interface is now more bonded, and the IMCs provide much higher strengths than either of the base metals [1]. As a result, it is expected that after aging, sheared bonds fail by shear mode 2a: shearing through Au. Upon further aging, IMCs grow up into the Au ball, sometimes in spikes [1]. The samples made for this thesis experiment are bonded at the low temperature of 150°C, to prevent ageing while on the bonder. As a result, it can be expected that the initial bond quality would not be as high as bonds made at over 170°C, and this spiked growth of intermetallics occurs. If the intermetallics grow up to the same height as the shearing ram, much greater shear

force is required to break the bond and the apparent shear strength is very high [1]. As the aging process progresses, voids appear along the intermetallic layer. As these voids coalesce, forming cracks, the interface becomes much weaker. The shear strength drops, and the bonds now fail at the intermetallic layer defined as shear mode 2b. An evolution of expected shear modes over time can be seen in Fig. 8.

In [18], shear and pull strengths of bonds aged at  $175^{\circ}$  over 1000 h are measured. Shear strength increases up to 200 h and then decreases. As can be seen in Fig. 9, shear strength doubles from asbonded strength to its peak strength. This is due to the formation of chemically strong bonds by IMCs at the interface. Breach attributes the following decrease in shear strength to chemical degradation of the  $Au_4Al$  layer which lies directly below the Au.

Fig. 8 Interdiffusion and growth of intermetallics at shear interface. (a) Due to poor ball adhesion, ball fails by shear mode 1. (b, c) Ball shears through Au material and fails by shear mode 2a. (d) Shear interface at IMC/oxidation layer reveals shear mode 2b.

#### 2.2.4. Contact Resistance

Although the physical strength of the bond is the most common measure of bond quality, the contact resistance of the bond describes the electrical connection making it an important property. Resistance is measured by passing a current through the bond, measuring the voltage drop, and performing an Ohm's law calculation. Since the contact resistance is very low ( $\sim$ 2-3 m $\Omega$  [4]) accurate measurement requires the 4-wire method shown in Fig. 10 a, where 2 electrical connec-

Fig. 9 Shear Test results from [18]. Bonds have diameter of 40 µm. At their peak, the shear stress corresponds to approximately 200 MPa, which is much higher than the shear strength of Au.

Fig. 10 Four wire connection. (a) Schematic. (b) Double ball bond used for 4-wire measurement [18]

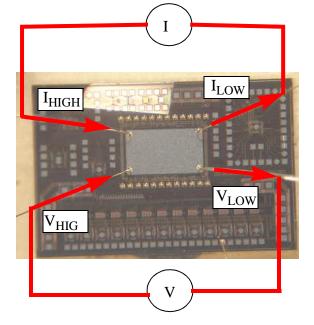

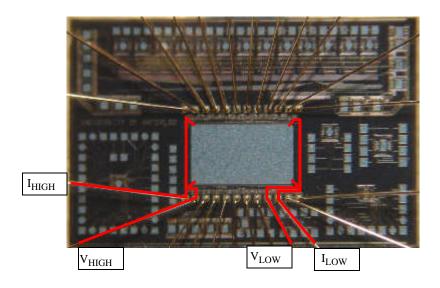

tions are provided to the ball, and 2 connections are provided to the pad. One pair of connections passes a constant current through the bond, while the other pair of connections measures the voltage induced across the bond. Since negligible current passes through the wires measuring the voltage due to the high resistance of the volt meter, only the bond resistance is measured. Existing literature offers cases where the contact resistance is measured at discrete intervals using probes to obtain a 4-wire measurement [18]. A double ball bond can be used to measure contact resistance where a second Au ball is bonded directly on top of a test bond to provide for the  $V_H$ ,  $I_H$  measurements, and a custom test chip is equipped with  $V_L$ ,  $I_L$  measurements [4] as shown in Fig. 10 b. This method is capable of providing real-time contact resistance monitoring during HTS. In [1], it is observed that resistance increases for the first 10,000 hours of a 200 °C age, afterwards plateauing at a the high value of between 1 and 10  $\Omega$

In [19] it is observed that after excessive aging and before the bond pops off the substrate, the contact resistance will oscillate wildly. The contact between the ball and substrate is reduced to tiny contact areas which connect and disconnect via local electromigration to cause this phenomenon. Electrical failure is often defined as a certain percentage increase of resistance and occurs well before such phenomena are observed [19].

While resistance increase is often blamed on voiding and cracking of the interface resulting in a reduced contact area [1, 2, 19], it has also been attributed to IMC formation [1]. Resistivities of the IMCs are significantly higher than of the base metals, so as the IMC volume increases, so does the contact resistance. Resistance increases of 8 m $\Omega$  in the absence of cracks or Kirkendall voids are attributed solely to IMC formation [1].

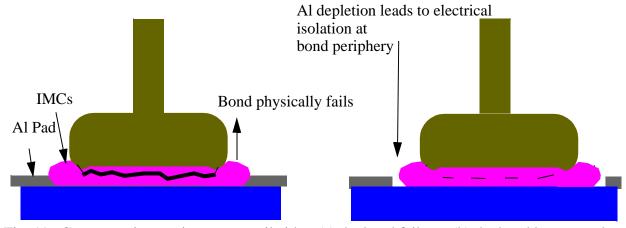

Electrical failure can occur in one of two ways. Internal voiding either between the Au and the IMC layer, or within the IMC layer can cause the bond contact area to reduce until both mechani-

cal and electrical failure. Alternatively, as IMCs grow lateral to the bond, the surrounding pad Al may deplete due to the Kirkendall effect [1]. This may eventually lead to electrical isolation of the bond, although the bond may remain physically robust as shown in Fig. 11 b.

### 2.2.5. Integrated Stress Sensors

Integrated stress sensors are introduced in [4, 20, 21]. The sensors are piezoresistive strain gauges made of n+ diffused Si arranged in a Wheatstone bridge configuration around the test pad shown in Fig. 12 a. The configuration is supplied with a voltage of 3V, and outputs a differential voltage which will increase upon experiencing a tensile force caused by the radial shrinking of the bond interface, and decrease when a compressive force (interfacial swelling) is observed as shown in Fig. 12 b.The sensor signal, *S*, is given by the differential voltage from either side of the bridge:

$$S = (V_2 - V_1)/V_S \tag{2}$$

where  $V_S$  is the sensing voltage of 3V. When Kirchoff's circuit laws are applied to the circuit, S can be expressed in terms of the resistance of each element by:

Fig. 11 Contact resistance increases until either (a) the bond fails, or (b) the bond becomes electrically isolated. In case (b) there is no physical failure between the bond and underlying pad. Rather, the pad Al adjacent to the IMCs becomes depleted due to the Kirkendall effect.

$$S = \frac{R_1 \cdot R_4 - R_2 \cdot R_3}{(R_1 + R_3) \cdot (R_2 + R_4)} \tag{3}$$

By using a Wheatstone bridge configuration, the sensor signal obtained is an average difference of resistance experienced between piezoresistors oriented to experience stresses tangentially ( $R_1$ ,  $R_4$ ) and radially ( $R_2$ ,  $R_3$ ). Since all resistors experience the same resistance change from an overall temperature change, no overall signal change is caused.

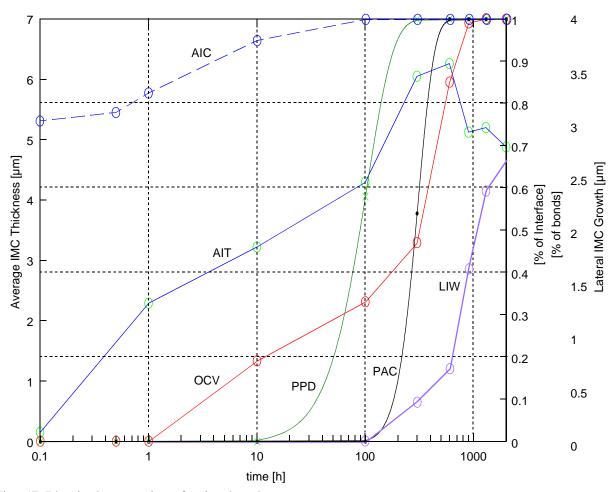

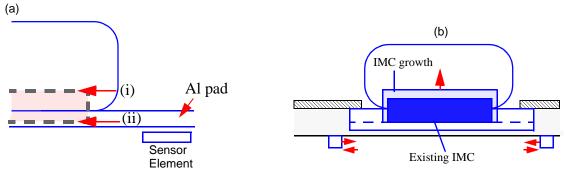

Fig. 13 shows the expected formation sequence of IMCs during aging, with relative IMC volume changes compared to base metal volumes [1]. During aging, sensor signals are measured which have been observed to roughly correspond to the volumetric changes resulting from expected IMC evolution [4].

### 2.3. Summary

In published studies of Au-Al wire bonds, interfacial IMCs dominated by Au<sub>8</sub>Al<sub>3</sub> and Au<sub>4</sub>Al typically form at the interface while AuAl<sub>2</sub>, Au<sub>2</sub>Al, and AuAl form lateral to the bond. During HTS

Fig. 12 Stress Sensors. a) A source voltage, Vs, of 3V is applied. The differential voltage between the sides of the Wheatstone bridge is detected [4]. b) When the interface region expands, compressive stresses are generated. When it contracts, tensile stresses result in the radial direction at the sensor element locations [22].

in an air atmosphere the  $Au_4Al$  layer is prone to oxidation which results in an  $Al_2O_3$  matrix with Au precipitates. Voiding occurs at the Au-IMC interface, or at the  $Au_4Al$ - $Au_4Al$  interface which may result from the Kirkendall effect or from oxidation. These voids coalesces into continuous cracks. This degradation will result in decreased bond strength as measured by the shear tester and increased contact resistance.

Fig. 13 Intermetallics which are expected to form during aging [1].

# 3. Experimental Methods

### 3.1. Overall Experimental Plan

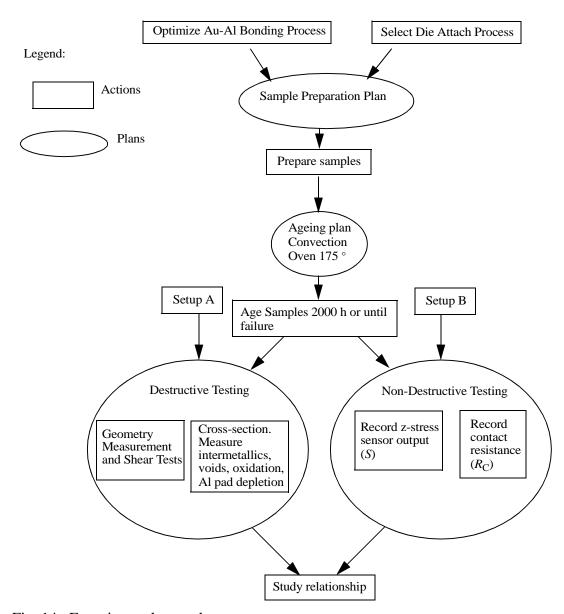

The experiment investigates any relationship that may exist between conventional destructive bond reliability tests and non-destructive methods of contact resistance ( $R_{\rm C}$ ) measurements and stress sensor measurements (S). The experimental procedure is outlined in Fig. 14.

Fig. 14 Experimental procedure

Sample preparation involves selecting an appropriate die-attach process, optimizing the ball bonding process, and bonding the test chips. Setups are constructed for aging chips and monitoring data. Four sets of samples are aged for 2000 h in a pair of Omegalux LMF-3550 ovens (OMEGA Engineering Inc., Stamford, Conneticut) at 175 °C. Set a contains a total of 380 bonds for shear testing, and set b contains 570 bonds for sectioning. These bonds are equally distributed among 19 chips which are destructively tested at periodic intervals listed in Table 1. Bond sets c and d consist of 61 bonds for  $R_{\rm C}$  monitoring and 82 bonds for continual S monitoring, repectively. Upon aging completion, the results of the destructive analysis are compared to the results of the non-destructive tests to investigate the relationship between all four sets of results. The same test chip is used for all experiments, but is prepared and aged differently for each set of chips as is explained in Sections 3.2-3.7.

Table 1: Plan for Aging and Destructive Testing. The identity of each chip is listed, along with its time of ageing,  $t_a$ , the maximum number of shear tests per chip, MS, and the maximum number of cross sections per chip, MC.

| Chip | <i>t</i> <sub>a</sub> [h] | MS | MC | Chip | <i>t</i> <sub>a</sub> [h] | MS | MC |

|------|---------------------------|----|----|------|---------------------------|----|----|

| 1    | 0                         | 20 | 30 | 11   | 300                       | 20 | 30 |

| 2    | 0                         | 20 | 30 | 12   | 300                       | 20 | 30 |

| 3    | 1/2                       | 20 | 30 | 13   | 600                       | 20 | 30 |

| 4    | 1/2                       | 20 | 30 | 14   | 600                       | 20 | 30 |

| 5    | 1                         | 20 | 30 | 15   | 900                       | 20 | 30 |

| 6    | 1                         | 20 | 30 | 16   | 900                       | 20 | 30 |

| 7    | 10                        | 20 | 30 | 17   | 1300                      | 20 | 30 |

| 8    | 10                        | 20 | 30 | 18   | 1300                      | 20 | 30 |

| 9    | 100                       | 20 | 30 | 19   | 2000                      | 20 | 30 |

| 10   | 100                       | 20 | 30 | 11   | 300                       | 20 | 30 |

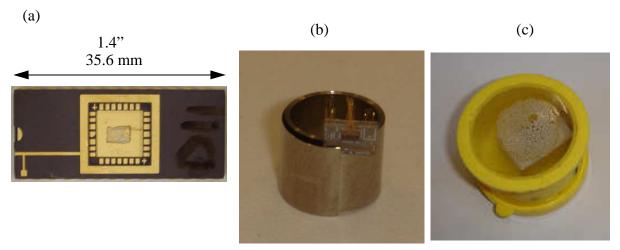

#### 3.2. Die Attach

Before chips can be bonded they are die attached to CerDIP packages. A standard die attach method uses silver filled epoxy (Ablebond 84, Ablestik, Rancho Doniniguez, California) to glue the chip in place, which is then cured in an oven. For this thesis, a colloidal silver (Pelco 16034 Colloidal Silver, Ted Pella Inc., Redding, California) comprised of 60% ± 1% Ag is used instead of the silver filled epoxy. The colloidal silver, which cures at room temperature over 24 h, is reported as reliable at service temperatures of 200 °C [23]. It also offers the advantage of being soluble by isopropanol, allowing for removal of the chip from relatively hard ceramic package for subsequent cross sectioning. In a preliminary test, a chip die attached with colloidal silver is removed from a package after 48 h exposure to isopropanol, whereas a chip die attached with silver filled epoxy is still firmly attached after 72 h of exposure to isopropanol.

After die attach, the chips are plasma cleaned to remove organic contaminants from bond pads and reduce surface oxide. All samples are placed in a plasma cleaner (plasma cleaner located at Microbonds, Markham, Canada) which is evacuated to < 90 mtorr, and a gas mixture of 90% Ag, 10% H is pumped into the cleaner until the pressure is increased back up to 270 mtorr. A radio frequency (RF) generator operating at 380W creates the plasma inside the cleaner (Fig. 15) which is maintained for 15 min. After plasma cleaning, the chips are immediately removed and vacuum sealed in a container which is placed in nitrogen storage.

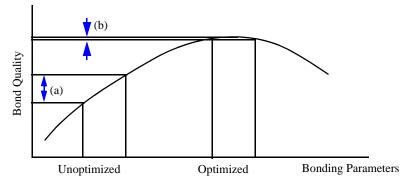

## 3.3. Preparation of Wire Bonding Samples

Prior to bonding the test chips, the bonding process is optimized for two reasons. First, it is desirable for the bond to be as strong as possible so that it endures aging for as long as possible. Second, the quality of an optimized ball bond is expected to vary less between samples than the quality of a non-optimized bond as illustrated in Fig. 16.

All bonding is performed on the ESEC 3088 wire bonder (ESEC, Cham, Switzerland). The capillary used is a SBNE-35BD-AZM-1/16-XL (Small Precision Tools, Petaluma, California), which is made for 1 mil wire, and has a chamfer diameter of 51 µm. The wire used is 1 mil 4N Au wire which has a breaking load of 10 gf, elongation of 2.8%, and a Vickers Hardness of 50. Wire bonding test chips used for process optimization are supplied by ESEC and attached to PLCC44 lead-frames. The bonding pads for the ball bonds are made of standard bond pad Al (with Si and Cu dopants), and the metallization to which the wedge bonds are made to is Ag.

Fig. 15 Chips being plasma cleaned.

Fig. 16 Optimization results in less variance. Equal variations in bonding parameters will produce greater change in bond quality of (a) unoptimized bonds compared to (b) optimized bonds

A low bonding temperature is desired to minimize any ageing effects while in process. The bond temperature is 150 °C with an offset temperature of 20°C and a temperature deviation of 5°C. Wire loop parameters are shown in Table 2.