# Mitigation of Memory Effects in High Power Microwave Amplifiers

by

### Nizar Messaoudi

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2009 ©Nizar Messaoudi 2009

# **Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

This thesis expounds on the application of Doherty Power Amplifiers (DPA) along with baseband Digital PreDistortion (DPD) techniques to tackle the antagonistic demands of high power efficiency and linearity imposed by modern communications.

Memoryless modeling is firstly introduced and its limitations when dealing with PAs driven with realistic devices. Therefore, electrical memory effects are explored in greater detail and a mathematical model showing the relation between the various harmonic components in the output and how they can re-mix back into the fundamental band is developed. The importance of the output bias network in the reduction of memory effects is highlighted. A memory polynomial (MP) based DPD is shown to be a good solution for the linearization of wideband DPA which exhibit strong memory effects. To further improve this solution, the complexity of the MP-DPD is reduced. For that, the even-order terms in the MP branches were first removed. Then, the PA memory effects theory was used to further reduce the number of coefficients of the MP-DPD by decreasing the nonlinearity orders in the different branches individually. These two steps allowed for a reduction of the number of coefficients to almost one-third and the conditioning number by three orders of magnitude while maintaining the same linearization capability. This substantially alleviates the requirements on the digital signal processors and the time needed to construct and implement the MP-DPD in real environment. Experimental validation carried out using a 400 Watt DPA, driven with 4-Carrier WCDMA signal, showed excellent linearization capability by achieving an ACPR of better than 50 dBc with a power efficiency of better than 42.4%. Despite this, the depth of the memory effects in the DPA was still significant.

While an effort was made to reduce further the memory effects, the discrepancy between the simulated behavior of the DPA and that observed in simulation was significant. In an attempt to rule out the DPA structure as the cause of the discrepancy between the measured results and the behavior predicted in simulation, a single branch class AB PA was designed using the transistor model. The PA behavior was well predicted when driven with a Continuous Wave (CW) signal, however the simulated and measured behavior differed greatly when the PA was driven by a two tone signal. This rendered the desired reduction of the memory effects impossible at the design stage.

# **Acknowledgments**

I would like to thank Dr. Slim Boumaiza for his help during this project. His patience and financial support were essential to the completion of this thesis. During these last three years his experience in the area of microwave theory and power amplifiers has been invaluable.

I would also like to thank Marie-Claude Fares who collaborated in several of my projects and was an extremely supportive and encouraging colleague.

Many thanks also go Nicola Gill of Agilent technologies whose help was crucial during the first year in Waterloo.

I would also like to thank Dr. John Wood of Freescale semiconductors for his help in providing the materials and models necessary for the completion of this project.

Many thanks to Dr. Jim Haslett and Dr. David Westwick of the University of Calgary who ignited my interest in research.

I also need to thank Dr. Michal Okioniewski without whom I would have never pursued graduate studies.

Finally, I would like to thank Michelle Ashburner, Fathia Messaoudi and Ilhem Messaoudi-Powers, for their support. I was extremely fortunate to have so many wonderful people who believed in me and encouraged me through this process.

# **Table of Contents**

| List of Table | es                                                                   | V11             |

|---------------|----------------------------------------------------------------------|-----------------|

| List of Figu  | res                                                                  | viii            |

| Introduction  |                                                                      | 1               |

| Chapter 1: E  | ackground                                                            | 4               |

| 1.1 Sing      | le Branch Power Amplifiers                                           | 4               |

| 1.2 Dohe      | erty Power Amplifier                                                 | 6               |

| 1.3 Metr      | ics of Nonlinear Distortion                                          | 8               |

| 1.3.1         | Single Tone Testing                                                  | 8               |

| 1.3.2         | Two-Tone Test                                                        | 10              |

| 1.3.3         | Modulated Signal Testing                                             | 10              |

| 1.4 Line      | arization techniques                                                 | 12              |

| 1.4.1         | Feedback Techniques                                                  | 12              |

| 1.4.1         | .1 Indirect Feedback                                                 | 13              |

| 1.4.1         | .2 Cartesian Loop Feedback System                                    | 14              |

| 1.4.1         | .3 Polar Loop                                                        | 14              |

| 1.4.1         | .4 Summary of Feedback Linearization                                 | 15              |

| 1.4.2         | Feedforward                                                          | 15              |

| 1.4.3         | Predistortion                                                        | 16              |

| 1.4.4         | Performance Comparison                                               | 17              |

| 1.5 Prop      | osed Solution                                                        | 19              |

| Chapter 2: C  | Characterization of Power Amplifier Nonlinearity                     | 20              |

| 2.1 Mem       | oryless Behavior                                                     | 20              |

| 2.2 PA F      | Behavior With Memory Effects                                         | 23              |

| 2.2.1         | Thermal Memory Effects                                               | 23              |

| 2.2.2         | Electrical Memory Effects                                            | 24              |

| Chapter 3: L  | inearization of Multicarrier DPA using a Memory Polynomial Digital I | Predistorter 32 |

| 3.1 Moti      | vation                                                               | 32              |

|               | eling Techniques                                                     |                 |

| 3.2.1         | Volterra Series                                                      |                 |

| 3.2.2         | Weiner and Hammerstein Models                                        | 34              |

| 3.2.3        | Memory Polynomial Model                                        | 34 |

|--------------|----------------------------------------------------------------|----|

| 3.3 Mem      | ory Polynomial Digital Predistortion Complexity Reduction      | 37 |

| 3.3.1        | Memory Polynomial Over and Under-Fitting                       | 37 |

| 3.3.2        | Memory Polynomial Even Order Omission                          | 37 |

| 3.3.3        | Unequal Order Memory Polynomial                                | 38 |

| 3.3.4        | Performance Evaluation                                         | 39 |

| 3.4 Expe     | rimental Results                                               | 39 |

| 3.4.1        | Test Setup                                                     | 39 |

| 3.4.2        | Under and Over-Fitting Memory Polynomial Digital Predistorters | 40 |

| 3.4.3        | Even and Odd Order Digital Predistorters                       | 41 |

| 3.4.4        | Unequal MP Branch Orders DPD validation                        | 43 |

| 3.4.5        | Overall System Performance                                     | 44 |

| 3.5 Com      | parison of Measured and Simulated Two Tone Testing Results     | 44 |

| Chapter 4: D | Pesign and Validation of a Class AB Power Amplifier            | 47 |

| 4.1 Design   | gn of the Power Amplifier                                      | 47 |

| 4.1.1        | Source-Load-Pull Simulations                                   | 47 |

| 4.1.2        | Input and Output Matching Network Design.                      | 48 |

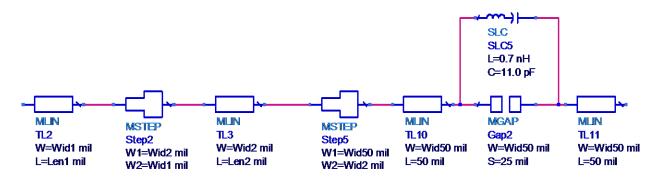

| 4.1.3        | Class AB Power Amplifier Design and Simulation                 | 50 |

| 4.2 Class    | AB Power Amplifier Layout and Fabrication                      | 56 |

| 4.3 Class    | AB Power Amplifier Validation under CW Signal                  | 57 |

| 4.4 Mem      | ory Effect Investigation                                       | 61 |

| 4.4.1        | Two Tone Measurements                                          | 61 |

| 4.4.2        | Modulated Signal Testing                                       | 64 |

| Conclusion.  |                                                                | 66 |

| References   |                                                                | 68 |

# **List of Tables**

| Table 1-1: Comparison of Linearization Techniques                            | 8          |

|------------------------------------------------------------------------------|------------|

| Table 2-1: Magitude and Frequency of the Power Amplifier Spectrum Components | 21         |

| Table 2-2: Frequency Components that Will Remix into the Right IMD3 Product  | 26         |

| Table 2-3: Frequency Components that Will Remix into the Right IMD5 Product  | 28         |

| Table 3-1: Summary of the Number of MP Coefficient                           | 39         |

| Table 3-2: MP Order Reduction                                                | <b>‡</b> 1 |

| Table 3-3: MP-DPD Complexity Reduction using Even Order Elimination          | 12         |

| Table 3-4: Unequal Odd Order Only MP                                         | 14         |

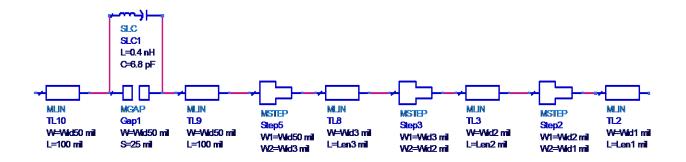

| Table 4-1: Input Matching Network Dimensions                                 | <b>1</b> 9 |

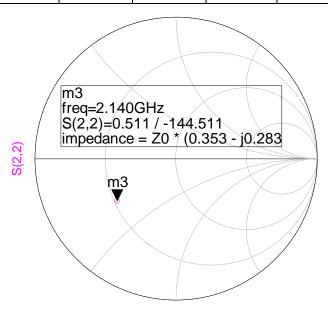

| Table 4-2: Output Matching Network Dimensions                                | 50         |

| Table 4-3: Single Carrier WCDMA Linearization                                | 55         |

# **List of Figures**

| Figure 1.1: PA Efficiency as a Function of the PA's Class of Operation                  | 4    |

|-----------------------------------------------------------------------------------------|------|

| Figure 1.2: PA Nonlinearity as a Function of the PA's Class of Operation                | 4    |

| Figure 1.3: Class AB Power Efficiency and Gain as a Function of Output Power            | 5    |

| Figure 1.4: Typical Doherty Power Amplifier Topology                                    | 6    |

| Figure 1.5: Simplified Doherty Power Amplifier Model                                    | 7    |

| Figure 1.6: Doherty PA Efficiency Compared to a Class AB PA Efficiency                  | 8    |

| Figure 1.7: Typical AM-AM Characteristics of a Power Amplifier                          | 9    |

| Figure 1.8: Typical AM-PM Characteristics of a Power Amplifier                          | 9    |

| Figure 1.9: Input and Output Spectrum of a Typical PA                                   | 10   |

| Figure 1.10 Typical PA Input and Output Spectrum                                        | 11   |

| Figure 1.11: Graphical Representation of an Error Vector                                | 12   |

| Figure 1.12: Typical Feedback Loop                                                      | 13   |

| Figure 1.13: A Basic Indirect Feedback Linearization for an RFPA                        | 13   |

| Figure 1.14: A Cartesian Loop Feedback System                                           | 14   |

| Figure 1.15: A Polar Loop Modulation System                                             | 15   |

| Figure 1.16: Basic Feed Forward Error Correction loop                                   | 16   |

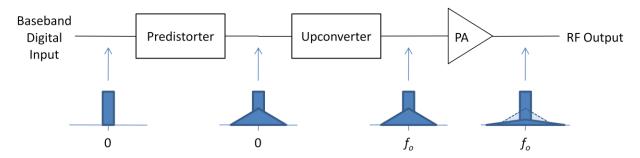

| Figure 1.17: Digital Predistortion Linearizer Setup with Signal Spectrums               | 17   |

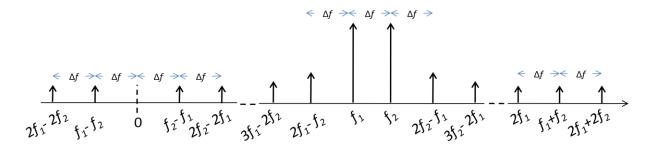

| Figure 2.1: Output Spectrum of a Nonlinear System when Stimulated with a Two Tone Input | t 21 |

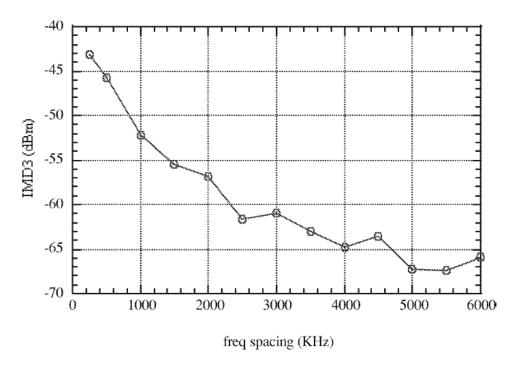

| Figure 2.2: IMD3 Amplitude due to Thermal Memory Effects Versus Frequency Spacing       | 24   |

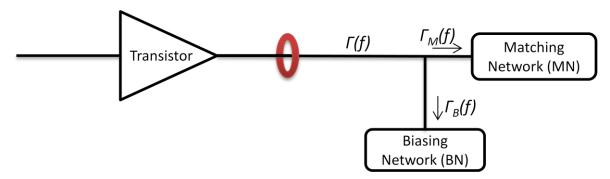

| Figure 2.3: Output Node Impedance Block Diagram                                         | 25   |

| Figure 2.4: Simplified Block Diagram of the PA Nonlinearity Mechanism                   | 25   |

| Figure 3.1: Typical Hammerstein PA Model                                                | 34   |

| Figure 3.2: Typical Memory Polynomial Structure.                                        | 35   |

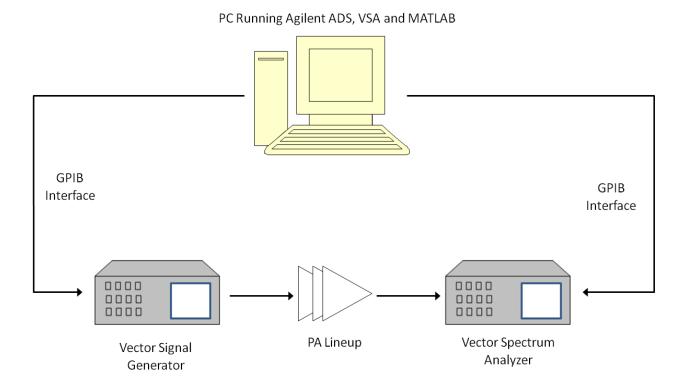

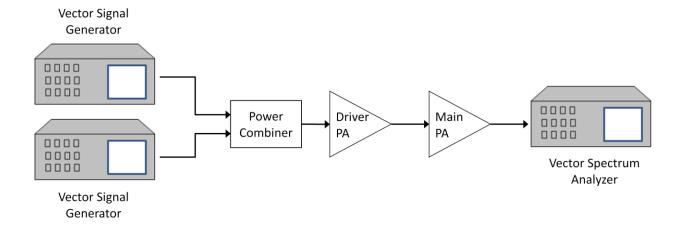

| Figure 3.3: Experimental Setup                                                          | 40   |

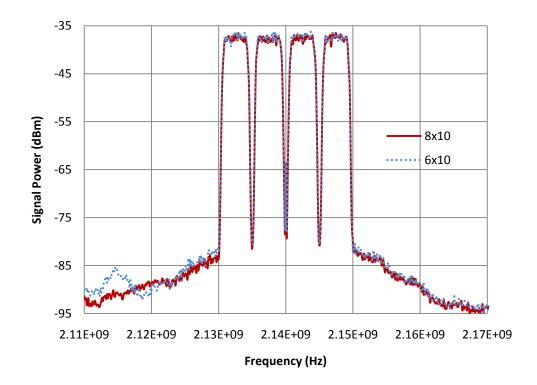

| Figure 3.4: Linearized DPA Output Spectrum Using Under and Over-Fitted MP-DPD        | 41 |

|--------------------------------------------------------------------------------------|----|

| Figure 3.5: Linearized DPA Output Spectrum Using Odd Only MP-DPD                     | 42 |

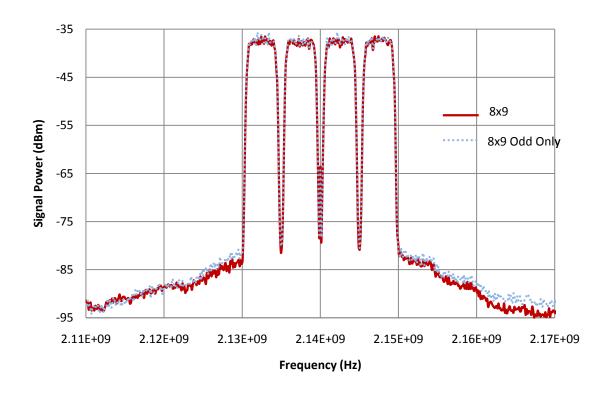

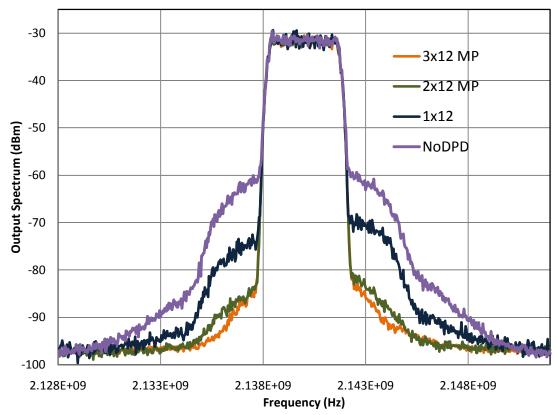

| Figure 3.6: Linearized DPA Output Spectrum Using Reduced MP Branch Orders            | 43 |

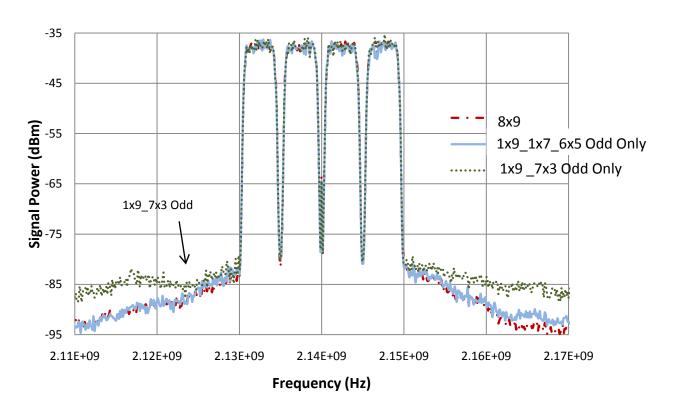

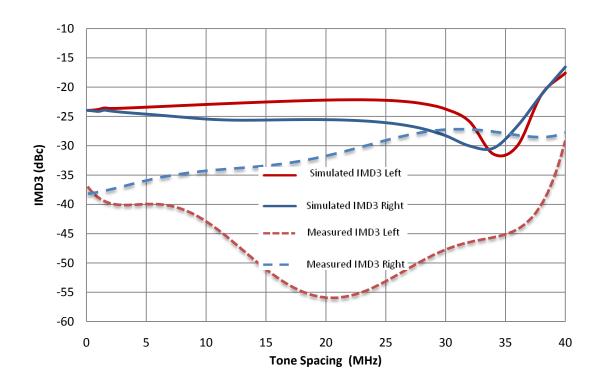

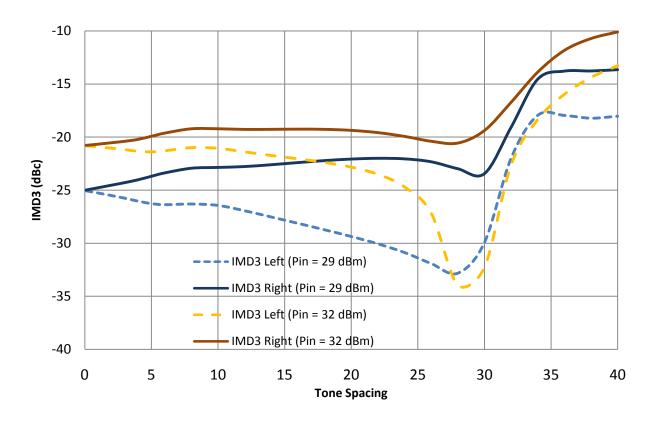

| Figure 3.7: Simulated and Measured IMD3 Levels vs Tone Spacing                       | 45 |

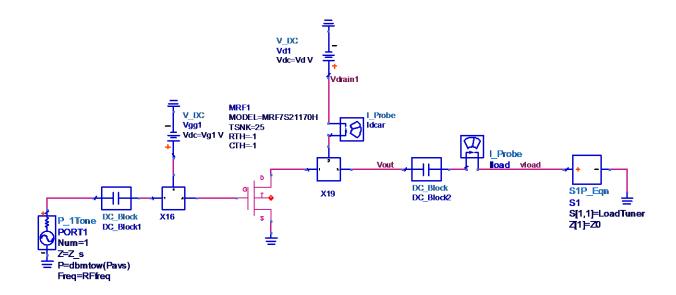

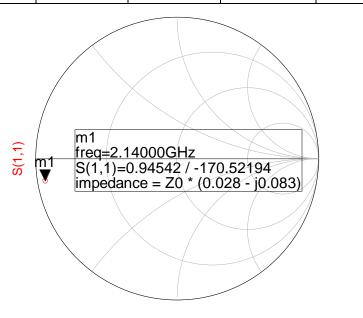

| Figure 4.1: ADS Load Pull Simulation Schematic                                       | 48 |

| Figure 4.2: ADS Schematic of the Input Matching Network                              | 49 |

| Figure 4.3: Simulated Response of the Input Matching Network                         | 49 |

| Figure 4.4: ADS Schematic of the Output Matching Network                             | 50 |

| Figure 4.5: Simulated Response of the Output Matching Network                        | 50 |

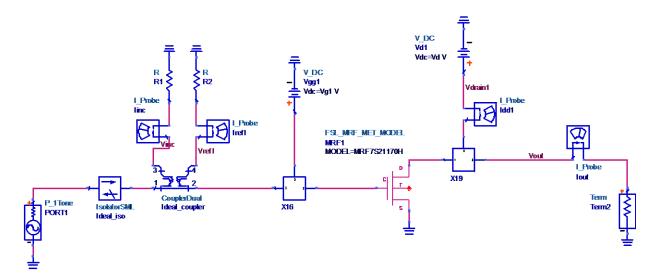

| Figure 4.6: ADS Schematic of the Designed Class AB PA                                | 51 |

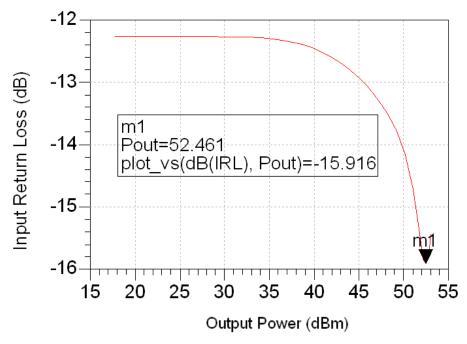

| Figure 4.7: Simulated IIRL of the PA as a Function of the Output Power               | 52 |

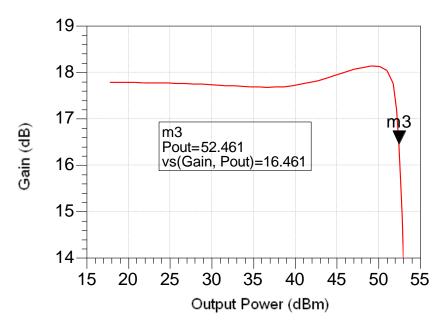

| Figure 4.8: Simulated Gain of the PA as a Function of the Output Power               | 52 |

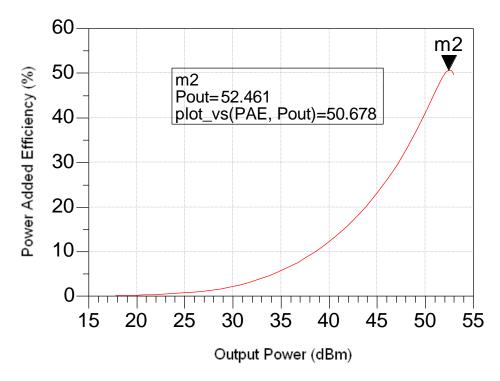

| Figure 4.9: Simulated PAE of the PA as a Function of the Output Power                | 53 |

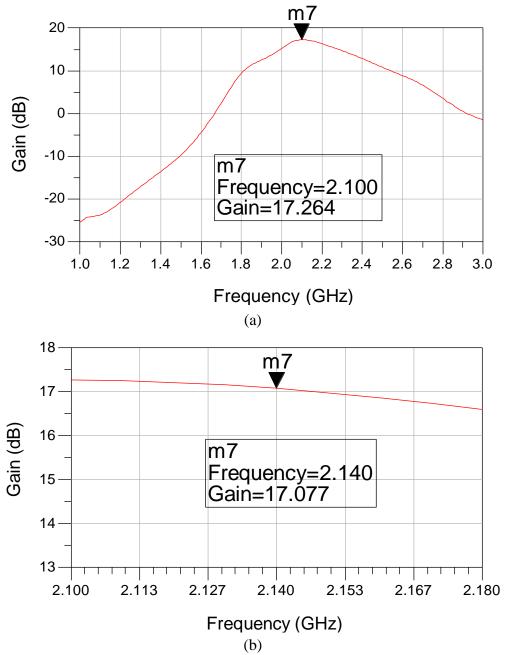

| Figure 4.10: Simulated Gain of the PA as a Function of the RF Input Frequency:       | 54 |

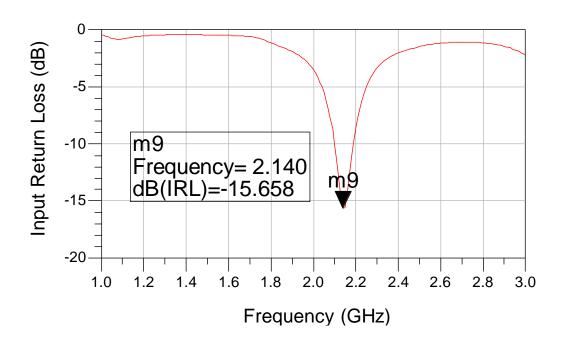

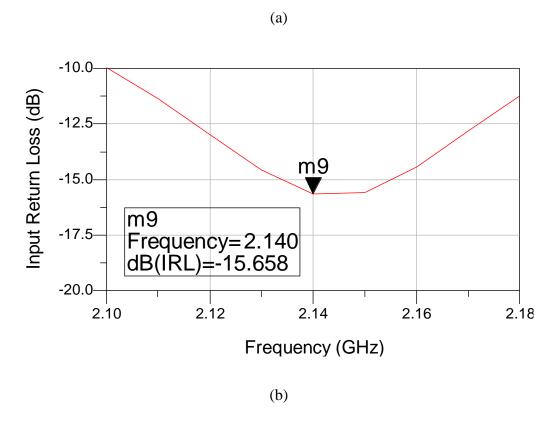

| Figure 4.11: Simulated IRL of the PA as a Function of the RF Input Frequency:        | 55 |

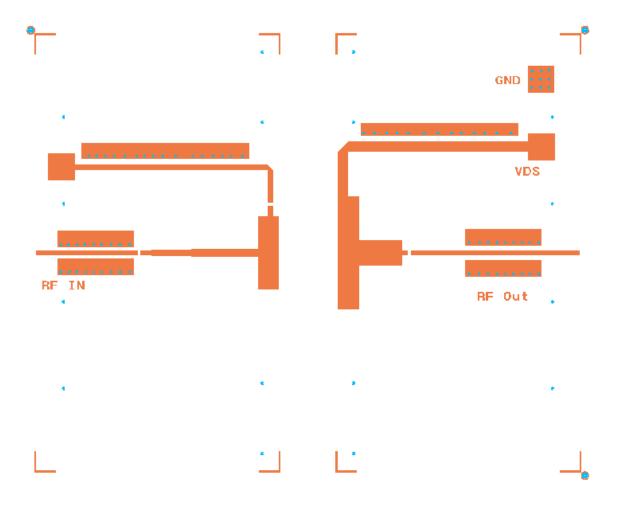

| Figure 4.12: Layout of the Fabricated Class AB PA                                    | 56 |

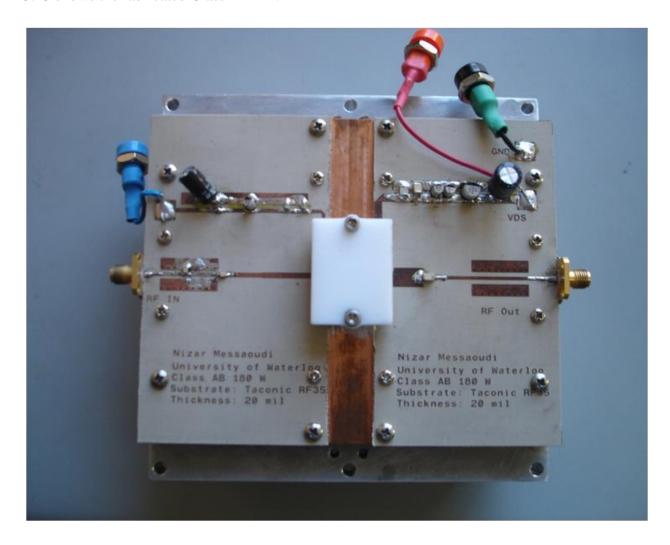

| Figure 4.13: Fabricated Class AB PA                                                  | 57 |

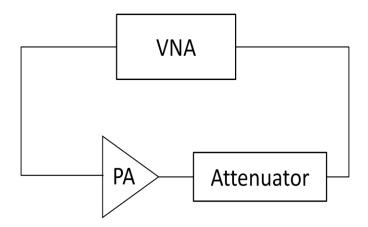

| Figure 4.14: Setup Used to Measure the Small Signal Parameters of the Class AB PA    | 58 |

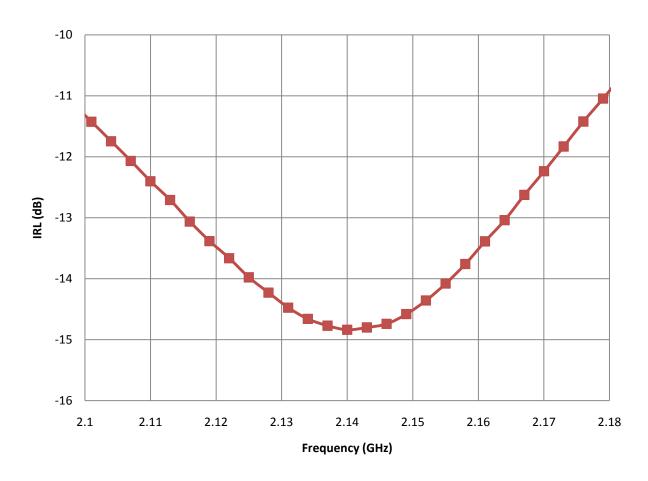

| Figure 4.15: Measured IRL of the Class AB PA as a Function of Input Frequency        | 58 |

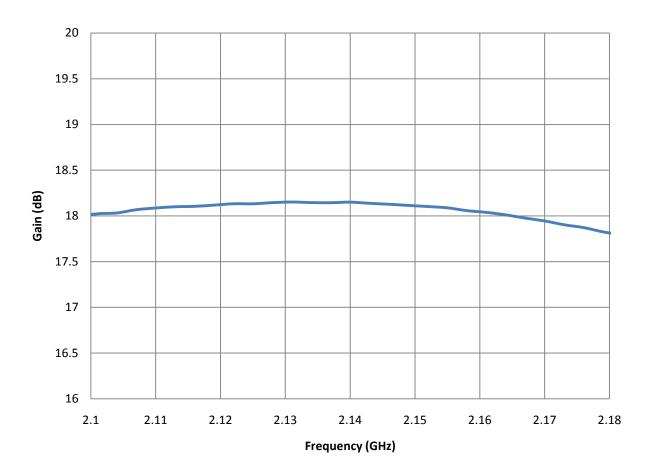

| Figure 4.16: Measured Gain of the Class AB PA as a Function of Input Frequency       | 59 |

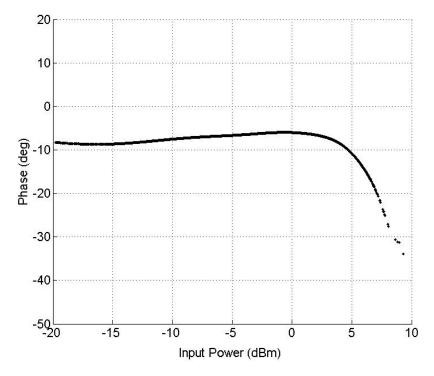

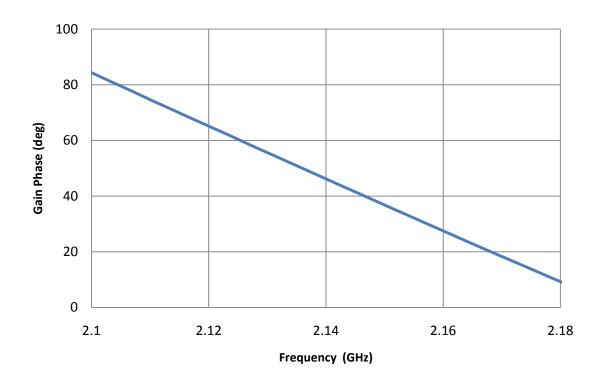

| Figure 4.17: Measured Gain Phase of the class AB PA as a Function of Input Frequency | 60 |

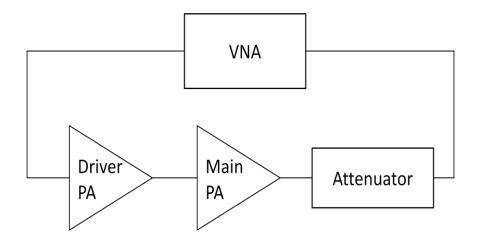

| Figure 4.18: Measured Setup Used to Measure the Gain Compression of the Class AB PA  | 60 |

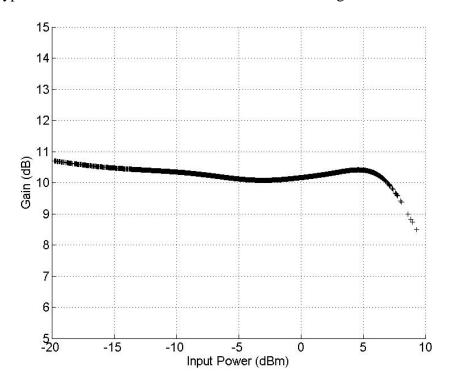

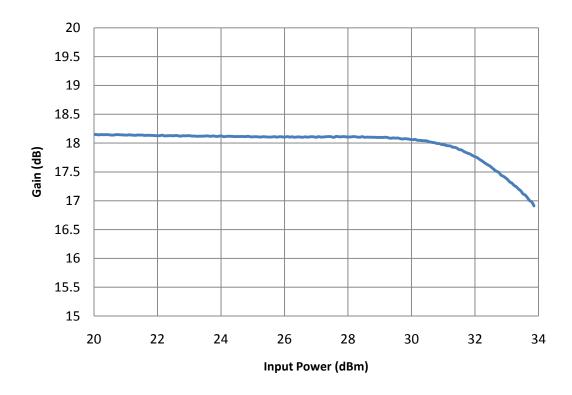

| Figure 4.19: Measured Gain of the Class AB PA as a Function of Input Power           | 61 |

| Figure 4.20: Experimental Setup Used for Two Tone Testing                            | 62 |

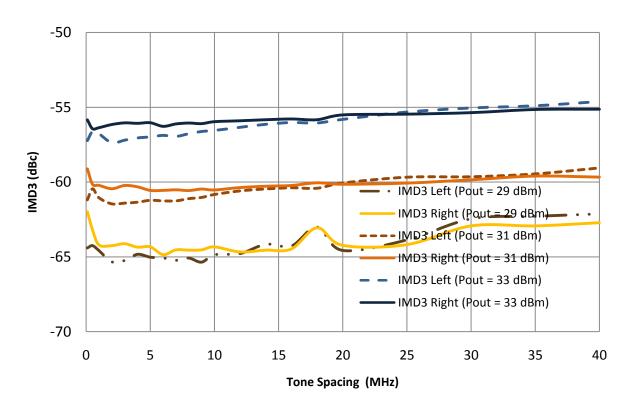

| Figure 4.21: Measured IMD3 of the Driver PA as a Function of Tone Spacing            | 63 |

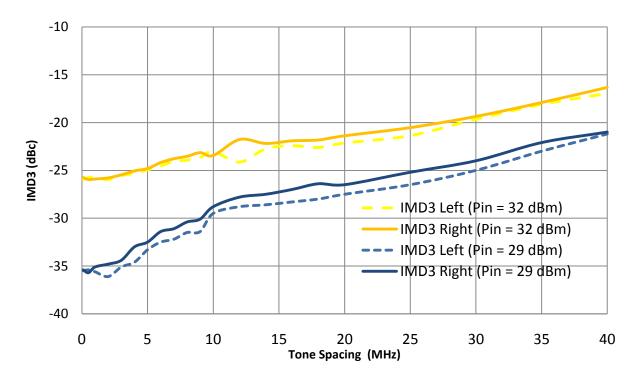

| Figure 4.22: Measured IMD3 of the Class AB PA as a Function of Tone spacing              | <u>i</u> 3 |

|------------------------------------------------------------------------------------------|------------|

| Figure 4.23: Simulated IMD3 of the class AB PA as a function of Tone spacing             | 54         |

| Figure 4.24: Frequency Spectrum of the PA Output With the Use of Various Predistorters 6 | 55         |

### Introduction

RF Power Amplifiers (PA) are essential components in wireless communications systems. Designed to operate at a multitude of frequency bands, at various power levels using a variety of architectures, their role is generally the same: amplify and send a signal to one or multiple antennas to be transmitted. Two fundamental and antagonistic performance criteria are used to benchmark all PAs.

Linearity has risen in importance in the last decade. In previous generations of RF devices Frequency Modulated (FM) and Gaussian Minimum Shift Keying (GMSK) signals were used to avoid linearity constraints, as they are characterized by a constant envelope and therefore did not require linear amplification. However, driven by consumer demand for more real-time, high data density media content, there is an increasing demand for spectral efficiency in wireless technology. This demand has led to the use of increasingly complex modulation schemes (Quadrature Amplitude Modulation (QAM), Orthogonal Frequency Division Multiplexing (OFDM)) and access technologies (Wideband Code Division Multiple Access (WCDMA), Worldwide Interoperability for Microwave Access (WiMAX)), which use both phase and amplitude modulation. These modulation schemes are characterized by high to Peak to Average Power Ratio (PAPR) signals while the access technologies are characterized by stringent linearity requirements. Hence, modern PAs need to be extremely linear over a large power range.

Competing with the demand for high linearity is the antagonistic demand for high power efficiency in modern transmitters. In mobile devices, greater power efficiency translates into longer lifetime. In base stations, higher power efficiency also reduces the size of the necessary cooling system, translating into significantly lower operating and deployment costs for service providers. Furthermore, satellite communications applications have very tight weight and energy budgets, so any way to reduce the energy consumption without increasing the mass of the transmitter is of critical importance.

Being the largest source of distortion and the most power hungry block in the transmitter chain, the power amplifier is at the centre of these conflicting antagonistic demands. To meet the linearity requirements set by the regulatory bodies over the large dynamic range necessary for high PAPR signals, service providers often use Pas biased in very linear classes of operation, such as class A and AB, and operate them in back-off. However, these classes of operation are

characterized by very poor efficiency in back-off. Conversely, more efficient classes of PAs are extremely non-linear and thus not a suitable solution. Hence, recent research efforts have focused on designing linear and efficient PAs.

The Doherty PA (DPA) architecture is one of the most promising solutions that has started to be deployed in the field. This dual branch architecture uses active load modulation to optimize the load impedance seen by the transistor, which greatly improves the efficiency of the PA at back-off.

Linearization techniques have shown various degrees of improvement in the linearity performance when applied to class AB PAs. However, techniques based on feedback have limited linearization bandwidth capability and are thus unsuitable for wideband base station applications. Baseband Digital PreDistortion (DPD) is an ideal complement to the DPA as it allows for high linearization capability and bandwidth while conserving the high power efficiency of the DPA. Unfortunately DPD the advantages of using DPD come at the cost of high complexity.

The primary focus of this thesis is to examine ways of reducing the complexity of a DPD required to linearize a high power, wideband, commercial DPA. This will be done by finding new ways to simplify the DPD scheme itself as well as trying to improve the design of the DPA to reduce the requirements for the DPD.

The thesis is divided into four chapters. The first chapter will present a quick review on PA classes, the DPA architecture and the most common metrics used to measure PA linearity. Different linearization techniques are also reviewed and compared in this section

The second chapter explores memoryless modeling and introduces the concept of memory effects. A mathematical model showing how various output harmonics re-mix back into the fundamental band is developed.

In the third chapter, a brief outline of various Volterra based modeling schemes is given. A Memory Polynomial (MP) based DPD is developed and its complexity is reduced by eliminating even-order terms in the MP branches and reducing the order of the subsequent branches. An effort is made to further reduce the complexity of the DPA, however a significant discrepancy between the measured and simulated behavior of the transistor is observed.

The fourth chapter deals with a single branch class AB PA designed in order to eliminate the active load modulation of the DPA architecture as the source of the discrepancy between predicted and measured transistor behavior. The single branch PA behavior continues to deviate significantly from the predicted model behavior when stimulated with a two-tone input. This leads to the conclusion that the transistor model is the source of the discrepancy, rendering further mitigation of the memory effects impossible.

# **Chapter 1: Background**

### 1.1 Single Branch Power Amplifiers

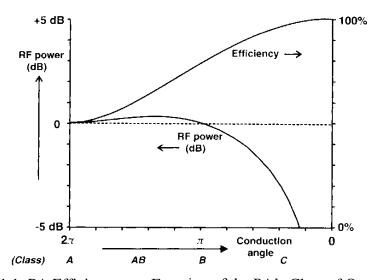

Several different classes of PA exist, each having its own tradeoff between linearity and power efficiency depending on how the transistor used in the PA is biased. This tradeoff is illustrated in Figures 1.1 and 1.2. It can be seen that while moving from a linear class of operation (Class A) to more nonlinear classes of operation (Class AB and Class B) by reducing the conduction angle does offer interesting improvements in efficiency, this improvement comes at the cost of increased harmonic components at the output, and hence stronger nonlinearity [1].

Figure 1.1: PA Efficiency as a Function of the PA's Class of Operation [1]

Figure 1.2: PA Nonlinearity as a Function of the PA's Class of Operation [1]

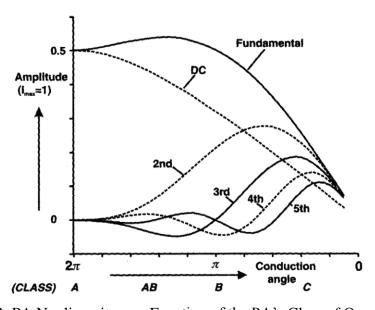

To ensure the linear behavior over a large dynamic range that is required by the high PAPR signals prevalent in modern communications, most commonly deployed PA architectures are biased in the quasi linear class AB and operated in deep back-off. While this class of operation does offer a good efficiency at peak output power, its efficiency decreases quickly in back-off, as shown by the linear region in Figure 1.3. One can see that the power efficiency of this PA drops from over 50% to around 20% when it is backed off 8 dB from peak output power. Furthermore, the region at which the PA achieves peak efficiency cannot be used due to the nonlinearity of the PA as shown by its gain compression. Hence, operating the PA in this manner leads to extremely poor average power efficiency (10 to 15%) when driven with modulated signals. Furthermore, operating the PA in class B or C, which offers significant efficiency improvement is not feasible due to the poor linearity of these classes of operation.

Figure 1.3: Class AB Power Efficiency and Gain as a Function of Output Power

Thus, the efficiency of the PA needs to be improved in the back off without significantly compromising its linearity. Furthermore, the use of linearization techniques would allow the use of the "high efficiency region" highlighted in Figure 1.3. Currently, highly efficient PA architectures such as those based on the load modulation technique are used to improve the PA's

inherent power efficiency. These techniques dynamically vary the load impedance seen by the PA as a function of its input power so as to present the optimal load impedance to maximize the PAs efficiency. In the literature, the most commonly used load modulation based amplifiers are Doherty amplifiers [2]–[8] and LINC (LInear amplification using Nonlinear Components) architectures [9]–[11]. Among these two techniques, Doherty amplifiers are currently being considered for handset devices whereas the LINC architecture is still in the R&D stage. In fact, Doherty amplifiers achieve relatively high power efficiency with a moderate linearity and the use of linearization techniques makes it possible to meet the regulatory linearity requirements.

### 1.2 Doherty Power Amplifier

The original Doherty PA (or DPA) was proposed in 1936 by William H. Doherty [2]. The original design dealt with very high power tube amplifiers for an Amplitude Modulation applications. While modern systems have output powers that are several orders of magnitude less than the original design, the efficiency enhancement that this technique offers remains extremely relevant.

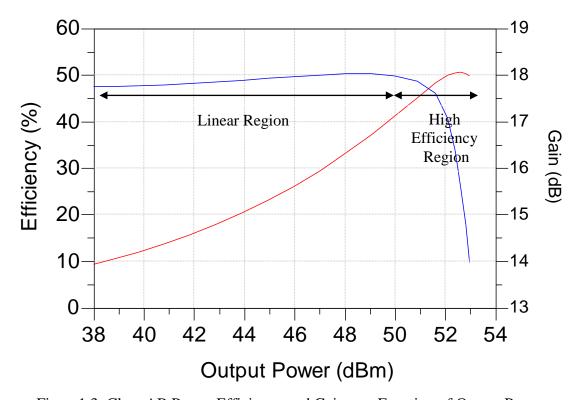

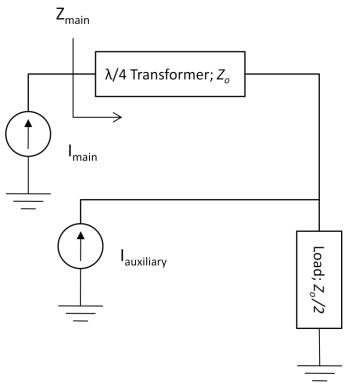

The Doherty PA is an architecture consisting of two parallel amplifiers, a main and peaking amplifier as shown in Figure 1.4, where  $Z_0$  is the characteristic impedance of the system and the load impedance.

Figure 1.4: Typical Doherty Power Amplifier Topology

The main amplifier is usually biased in class AB or class B, while the peaking amplifier is biased in class C. The output load is connected to the main amplifier through a quarter wave transformer and directly into the peaking amplifier. The peaking amplifier is biased so as to turn on at half of the maximum input voltage. A simplified analysis can be performed by representing both PAs as current sources as shown in Figure 1.5.

The DPA has two operating modes. When the input power is below half the maximum input voltage, only the main PA is turned on. Since the auxiliary PA is biased in Class C, it consumes no Direct Current (DC) power when it is in cut-off. Through the quarter wave transformer, the load seen by the main amplifier ( $Z_{main}$ ) is twice the load impedance. This increase in the impedance seen by the main amplifier allows it to reach saturation at half the maximum input voltage, achieving its peak efficiency much quicker.

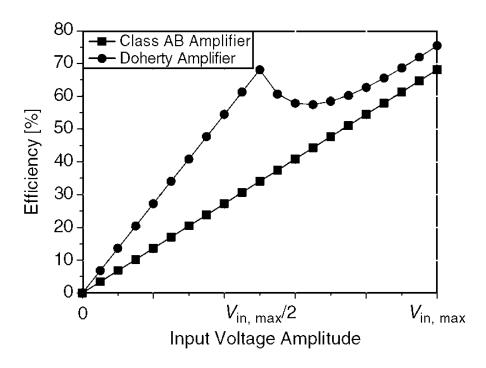

At higher power levels, the peaking amplifier is turned on and delivers power to the load in phase with the main PA. This serves to actively modulate the load seen by the main PA, increasing the impedance of the load. However, when seen through the quarter wave transformer, the impedance seen by the main PA is gradually reduced as the input drive increases to keep the main PA in saturation. This active load modulation allows the DPA to maintain high efficiency over a 6 dB dynamic range as seen in Figure 1.6.

Figure 1.5: Simplified Doherty Power Amplifier Model

A more detailed mathematical analysis of the Doherty design can be found in a variety of references [1]-[3], [12].

Figure 1.6: Doherty PA Efficiency Compared to a Class AB PA efficiency [12].

#### 1.3 Metrics of Nonlinear Distortion

One of the drawbacks of the DPA, relative to single branch implementations, is further degradation in transmitter linearity. This increase in nonlinear behavior can be observed in a variety of ways, however, the most common tests to characterize nonlinear behavior are the one and two tone test. While the simplicity of these two tests is ideal for debugging PA design, ultimately the PA must be tested under realistic drive conditions using a modulated signal.

### 1.3.1 Single Tone Testing

The one tone test consists of stimulating the Device Under Test (DUT) with a single sinusoidal tone. This test uses an extremely simple input signal and hence is an extremely easy test to perform and interpret. The most important metrics that are extracted from this test are the AM-AM and AM-PM response of the DUT. The AM-AM characterization describes the relation between the output amplitude of the fundamental frequency with the amplitude of the input signal. Hence, it describes the gain compression or expansion of the DUT as a function of the input drive level. This allows for the evaluation of the 1 dB compression point ( $P_{1dB}$ ), which is defined as the point at which the output is compressed by 1 dB as compared to an ideal linear

output. The AM-PM response of the DUT describes its phase deviation as a function of the input drive level. Typical AM-AM and AM-PM curves are shown in Figures 1.7 and 1.8.

Figure 1.7: Typical AM-AM Characteristics of a Power Amplifier

Figure 1.8: Typical AM-PM Characteristics of a Power Amplifier

#### 1.3.2 Two-Tone Test

The two-tone is a better representation of true telecommunications signal excitation. The DUT is stimulated with two sinusoids with frequencies  $f_1$  and  $f_2$ . This test allows for a better characterization of the DUT as the test signal used begins to resemble a realistic test signal, however, the results are simple enough to allow great insight into the source of the nonlinear behavior.

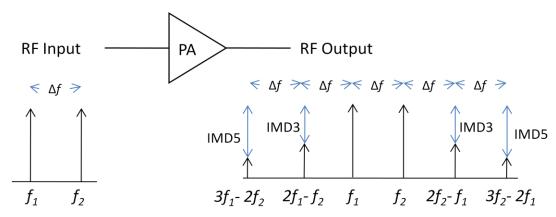

The spacing between the two tones,  $\Delta f = f_2 - f_1$ , is analogous to the bandwidth of a modulated signal used in modern communication systems. This test enables the characterization of generated harmonics, specifically the mixing components close to the fundamental. These mixing components are the dominant sources of nonlinear interference in bandpass systems as they are much harder to filter out. These mixing products are classified as third and fifth order intermodulation products or IMD3 and IMD5 respectively. The IMD3 products occur at  $2f_1 - f_2$  and  $2f_2 - f_1$  while the IMD5 products will occur at  $3f_1 - 2f_2$  and  $3f_2 - 2f_1$ , as shown in Figure 1.9.

Figure 1.9: Input and Output Spectrum of a Typical PA

The IMD products are usually expressed as the power ratio of these mixing products to that of the fundamental tones. This ratio provides a good first guess to see if the DUT will meet the spectral mask requirements of the telecommunications regulatory body. These requirements usually specify the Adjacent Channel Power Ratio (ACPR) for several frequency bands around the transmit frequency. This metric is explained in further detail in the following section.

#### 1.3.3 Modulated Signal Testing

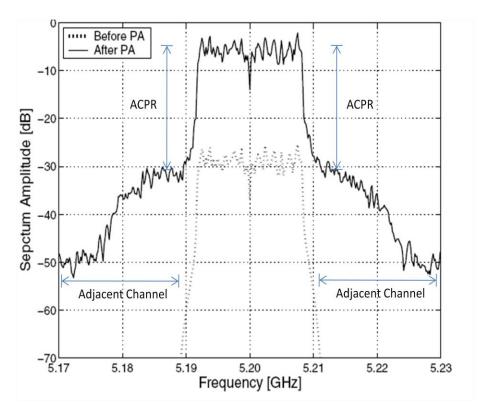

The ACPR is a metric that can only be used when the DUT is being driven with a modulated input signal and is extremely useful for understanding the nonlinear behavior of the

DUT and how it can interfere with adjacent signals. ACPR is defined as the power ratio of the average power in the adjacent frequency channel to the average power in the transmit frequency channel, and is analogous to the IMD3 in the simple two tone case. Similarly, the alternate channel ratio, is defined as the power ratio of the power in a bandwidth two channels away from the main signal to the average power in the main signal bandwidth, and is analogous to IMD5. A typical ACPR measurement is shown in Figure 1.10

Figure 1.10 Typical PA Input and Output Spectrum

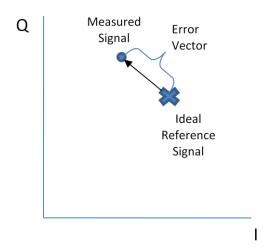

However, the ACPR does not provide any information on how the transmitted signal is distorted within the transmission channel. For this, the Error Vector Magnitude (EVM) metric is needed. EVM is the most commonly used metric to measure how the transmitter distorts the desired output. An error vector is a vector in the I-Q plane between the ideal constellation point and the point received by the receiver as shown in Figure 1.11. The EVM is defined as the ratio of the power of the error vector to the Root Mean Square (RMS) power of the reference. It is described in dB as:

$$EVM(dB) = 10log_{10} \left( \frac{P_{error}}{P_{reference}} \right)$$

(1-1)

where  $P_{error}$  is the RMS power of the error vector, and  $P_{reference}$  is the RMS power of ideal transmitted signal. EVM can be written as a percentage similarly:

$$EVM(\%) = \sqrt{\frac{P_{error}}{P_{reference}}} *100\%$$

(1-2)

Figure 1.11: Graphical Representation of an Error Vector

#### 1.4 Linearization techniques

Despite the interesting power efficiency gains that DPAs offer, this architecture usually presents a slight decrease in linearity from the previous generation of less efficient class AB amplifiers. To meet the stringent linearity requirement of modern communication standards, different linearization techniques are applied to Doherty PAs. Furthermore, linearization allows us to use the PA as its gain begins to compress allowing us to operate it in peak efficiency, despite the increase in nonlinearity in this region. This section describes the three most well established linearization techniques: feedback, feedforward, and predistortion.

#### 1.4.1 Feedback Techniques

Feedback is a control technique that uses the current output of a system to adjust the future output of the system. Generally this is done by comparing the output signal to a desired output and generating an error signal. This error signal is then used to adjust the system parameters to generate the desired output signal. The signal path from the output of the system back to the system is referred to as the feedback loop [13].

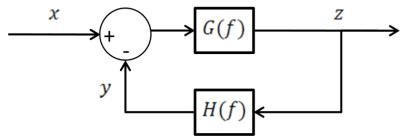

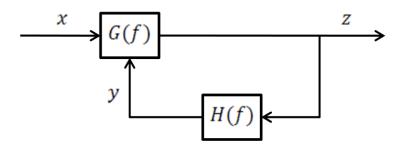

A typical feedback loop is shown in Figure 1.12, where x and z are the time domain input and output of the system respectively. The general equation for this loop can be described as

$$\frac{Z(f)}{x(f)} = \frac{G(f)}{1 + G(f)H(f)} \tag{1-3}$$

where X(f) and Z(f) are the Fourier transforms of the input and output of the system respectively

Figure 1.12: Typical Feedback Loop

This section presents 3 common applications of feedback to PA linearization.

#### 1.4.1.1 Indirect Feedback

Feedback linearization can be distinguished into three commonly used techniques: indirect feedback, the Cartesian Loop, and Polar Loop. A basic indirect feedback is shown in Figure 1.13.

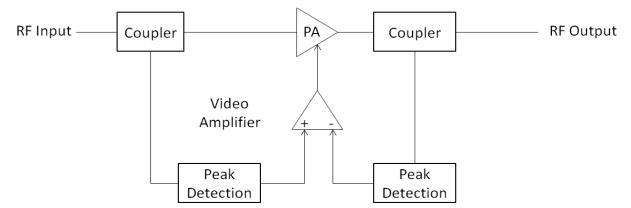

Figure 1.13: A Basic Indirect Feedback Linearization for an RFPA

A conventional RFPA has envelope detectors coupled to its input and output ports. These envelope detectors are used in conjunction with a differential video amplifier to form an error correction signal which is used to control the gain of the PA. This method only corrects for AM/AM distortion and cannot correct AM/PM effects.

#### 1.4.1.2 Cartesian Loop Feedback System

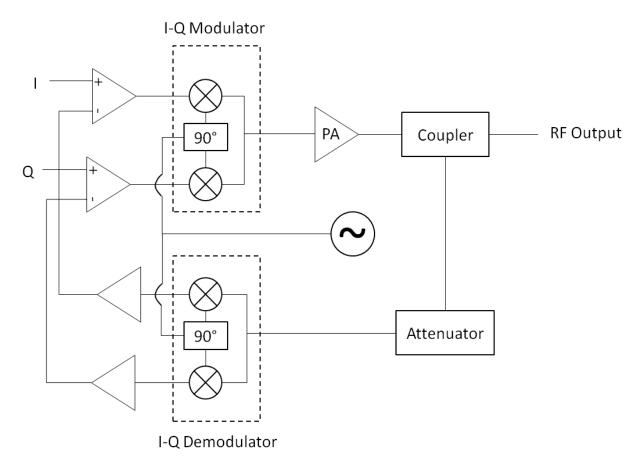

Cartesian Correction is a transmitter rather than a PA linearization technique and requires the signal in its baseband form. The basic Cartesian Loop feedback system is shown in Figure 1.14. In this architecture, the I and Q signals are fed through differential correcting amplifiers. The output of these amplifiers is then fed into a vector modulator which feeds the RF PA. The PA output is sampled, downconverted back into separate I and Q signals. The sampled output I and Q signals are then compared with the original input baseband signals. The error signal is then re-injected at the input of the PA to yield linear output.

Figure 1.14: A Cartesian Loop Feedback System

#### 1.4.1.3 *Polar Loop*

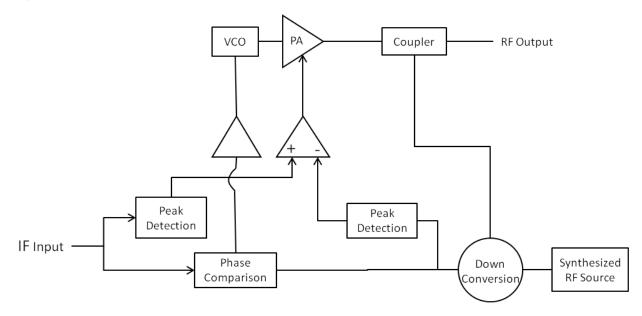

The Polar Loop, as shown in Figure 1.15, would be better classified as a modulator rather than as a linearizer. The input to the modulator is a fully modulated IF signal. An RF PA in a supply modulated envelope restoration configuration creates the AM portion of the output RF signal, while a Voltage Controlled Oscillator (VCO) phase-locked to the IF input creates the PM

on the RF carrier. The PA output is sampled, down converted and then compared to the input to create an error signal. This error signal is used to adjust the gain of the envelope restoration RF PA.

Figure 1.15: A Polar Loop Modulation System

#### 1.4.1.4 Summary of Feedback Linearization

While all feedback techniques offer some improvement in the linearity of the RF output, they all face the bottleneck presented by BandWidth (BW) limitations in the feedback loop. Hence, they are more suitable to narrowband and single carrier applications.

#### 1.4.2 Feedforward

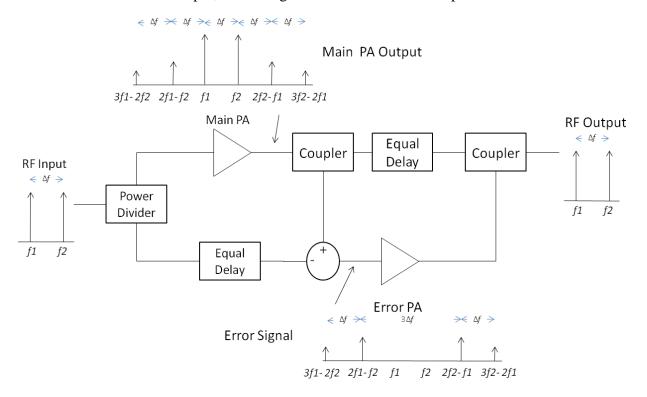

Feedforward is a well established linearization technique that is used for wideband PA applications. The basic feedforward architecture, along with signal spectra at the input, main PA, error PA and output are shown in Figure 1.16. The feedforward architecture consists of two loops: a main signal loop and an error cancellation loop.

The input is divided into both signal paths. In the main path, the input is amplified by the main PA, generally a highly efficient but nonlinear PA that will generate harmonics and intermodulation products. In the error cancellation path, the signal is delayed by an equal amount of time. The distortion generated by the main PA is extracted by subtracting the delayed version of the undistorted input from a sampled version of the main PA's output. If there is no error, then input to the error PA is zero. However, if there is any distortion, the error PA amplifies it back to the power level of the output. The output of the main PA is delayed to ensure that the delay in

the main path is equal to that in the error cancellation loop. The amplified distortion is then recombined with the PA output, cancelling out the inter-modulation products.

Figure 1.16: Basic Feedforward Error Correction Loop

#### 1.4.3 Predistortion

Predistortion consists of adjusting the magnitude and phase of the input signal before the PA, such that the PA-predistorter (PD) pair appears as linear device. One aspect that is often overlooked is that the use of a PD will always create new distortion components not present in the original un-predistorted PA response. Thus, the output of the PD will display a spectrum of distortion products which exceed the spectral BW of the uncorrected PA. Analog predistorters are often crude and consist of using attenuators with an expansive insertion loss characteristic [1]. With the advent of Digital Signal Processing (DSP), analog predistortion has become a much more complex method of accomplishing what can be easily done using digital techniques.

Hence, this section focuses on the significantly more popular and useful Digital PreDistortion (DPD). Indeed, thanks to developments in high speed DSP, baseband DPD is the most actively researched area of linearization. The basic principle behind DPD consists of creating an inverse function for the PA and using this function in series with the PA as shown in

Figure 1.17. This means that an accurate behavioral model is crucial to the implementation of the DPD. The predistorter usually consists of a series of Look Up Tables (LUT).

Unfortunately, early versions of linearizers using this technique achieved very modest results (10 dB to 15 dB reductions of ACPR). The reason for these poor results was found to be short-term variations in PA characteristics, called memory effects. This leads to more complicated DPD algorithms, which use previous signal values to determine the appropriate correction. Further improvement, can be achieved, by adding an adaptation loop in the DPD system.

Figure 1.17: Digital Predistortion Linearizer Setup with Signal Spectrums

### 1.4.4 Performance Comparison

The indirect feedback linearization system has several limitations, notably it cannot increase the intrinsic power saturation of the device. Additionally, AM-PM effects are not corrected with this method. Furthermore, delays in the detection and signal processing become severe for stable operation when linearizing signals with large bandwidths.

The advantage of the Cartesian Loop method is that the symmetry of gain and bandwidth in the I and Q paths reduces the phase shifts between AM-AM and AM-PM processes which are principally responsible for asymmetrical inter-modulation products. Moreover, the use of a synthesized RF source enables the Cartesian Loop to be a frequency agile solution. While reductions of 30 dB in the IM products have been reported, the video bandwidth and stability of this architecture limit its use to signal modulation bandwidths under 100 KHz.

In the case of the Polar Loop modulator, while it has shown the ability to greatly improve lower inter-modulation products, such as IMD3 and IMD5, higher order products can be uncorrected or even increased. This is due to the limitations on video bandwidth and stability. Additionally, these limitations restrict the usefulness of this technique to single carrier

applications. Nevertheless, when limited to single carrier applications, average efficiencies of greater than 50% and IMD3 products of 50 dBc have been reported [14]. Although difficult to implement, this scheme is becoming more popular, especially in handset applications using challenging modulation schemes such as EDGE, which has taxing demands on the linearity-efficiency tradeoff in traditional Class AB architectures.

The key advantage in the feedforward process is that both amplitude and phase errors are corrected. The major drawback of this solution is that the Error PA needs to be extremely linear, which limits the overall power efficiency of the overall solution to 10% to 15%. Furthermore, variations in frequency and temperature cause gain and phase alignment errors in the error PA. Moreover, the gain and phase tracking requirements for the error PA to obtain significant linearity improvements are extremely stringent: less than 0.01 dB of Gain error and less than 1degree of phase error to obtain a reduction of 40 dB in the IMD3. Thus, while feedforward does offer some advantages, the power efficiency limitations do not make it an attractive solution for multi-carrier base station applications.

Modern DPD linearizers yield a 20 dB to 30 dB improvement in ACPR of the PA over a significant bandwidth. Additionally, due to the low power consumption of the DPD relative to the PA, there is no significant degradation in the transmitter's power efficiency. Furthermore, DPDs are extremely flexible. However, the DPD is the only system which requires thorough behavioral modeling of the PA, which can significantly increase its implementation complexity.

A summary of these results is shown in Table 1.1.

TABLE 1-1: COMPARISON OF LINEARIZATION TECHNIQUES

| Linearization     | C14        | Power      | D 1 141-  | Cancellation |

|-------------------|------------|------------|-----------|--------------|

| Technique         | Complexity | Efficiency | Bandwidth | Performance  |

| Indirect Feedback | Low        | Moderate   | Low       | Low          |

| Cartesian Loop    | Moderate   | High       | Low       | High         |

| Polar Loop        | High       | High       | Low       | High         |

| Feed Forward      | High       | Moderate   | High      | High         |

| DPD               | High       | High       | High      | High         |

#### 1.5 Proposed Solution

Since the focus of this project is a base station application, the three most important criteria when evaluating the proposed solution are power efficiency, bandwidth and cancellation performance. The only linearization technique that can achieve high performance in all these criteria is the DPD. Thus, a DPA when coupled with a DPD should display good average efficiency over a large dynamic range while meeting the stringent linearity requirements for multiple carriers. In fact it has been shown in the literature that this is a promising solution for wideband multi-carrier applications.

Nevertheless, it is desirable to reduce the complexity of the algorithms necessary for DPDs to meet the linearity requirements. Thus, it is necessary to reduce memory effects through more careful design. Therefore, it becomes necessary to build a systematic design approach that can be used to minimize memory effects which is universally applicable.

# Chapter 2:

# **Characterization of Power Amplifier Nonlinearity**

This chapter reviews memory effects and where they originate from in power amplifiers. Section 2.1 examines some basic non-linear modeling of Power Amplifiers and how this can be used to gain a greater understanding of the motivation behind early DPD linearization attempts. Sections 2.2 and 2.3 examine memory effects, which have led to more complex models being used for state-of-the-art DPD linearizers with more success.

#### 2.1 Memoryless Behavior

Traditionally, Power Amplifiers are modeled as nonlinear, memoryless devices, often using a polynomial model because it allows for easy calculation of spectral components. Assuming the use of a fifth order polynomial to model the PA's behavior, the PA output can be described by

$$y = a_1 x + a_2 x^2 + a_3 x^3 + a_4 x^4 + a_5 x^5$$

(2-1)

where x and y are the PA input and output respectively, and  $a_1$  to  $a_5$  are the complex polynomial coefficients.

To quantify the undesired spectral component the PA will produce as a function of the instantaneous bandwidth of the input signal, x, a two tone input signal consisting of two pure sinusoids at  $f_1$  and  $f_2$  is used, where

$$x = A(\cos(f_1 t + \emptyset_1) + \cos(f_2 t + \emptyset_2))$$

(2-2)

where A is the signal magnitude,  $\emptyset_1$  and  $\emptyset_2$  are the phase shifts of the first and second tone respectively.

While the input signal may be band-limited, the output of the PA will consist of numerous inter-modulation products in several frequency bands. Figure 2.1 shows some of the output frequency products at baseband, fundamental and second harmonic frequency bands.

Figure 2.1: Output Spectrum of a Nonlinear System When Stimulated with a Two Tone Input

By expanding Equation (2-1) and simplifying for the spectral components, one can obtain the magnitude of all the spectral components. The results of this operation are shown in Table 2.1.

TABLE 2-1: MAGITUDE AND FREQUENCY OF THE POWER AMPLIFIER SPECTUM COMPONENTS

| Frequency     | Name                            | Magnitude                                           |

|---------------|---------------------------------|-----------------------------------------------------|

| 0             | DC                              | $A^2a_2 + A^4a_4 \frac{9}{4}$                       |

| $f_2 - f_1$   | 2 <sup>nd</sup> Order Envelope  | $A^2a_2 + A^4a_43$                                  |

| $2f_2 - 2f_1$ | 4 <sup>th</sup> Order Envelope  | $A^4\left(a_4\frac{3}{4}\right)$                    |

| $3f_1 - 2f_2$ | IMD5 Left                       | $\frac{5}{8}a_5A^5$                                 |

| $2f_1 - f_2$  | IMD3 Left                       | $\frac{3}{4}a_3A^3 + \frac{25}{8}a_5A^5$            |

| $f_1$         | Fundamental Left                | $a_1A + \frac{9}{4}a_3A^3 + \frac{25}{4}a_5A^5$     |

| $f_2$         | Fundamental Right               | $Aa_1 + A^3 a_3 \frac{9}{4} + A^5 a_5 \frac{25}{4}$ |

| $2f_2 - f_1$  | IMD3 Right                      | $A^3a_3\frac{3}{4} + A^5a_5\frac{25}{8}$            |

| $3f_2 - 2f_2$ | IMD5 Right                      | $A^5\left(a_5\frac{5}{8}\right)$                    |

| $3f_1 - f_2$  | Second Harmonic Difference Left | $A^4\left(a_4\frac{1}{2}\right)$                    |

| $2f_1$                  | Second Harmonic Left             | $A^2a_2\frac{1}{2} + A^4a_42$             |

|-------------------------|----------------------------------|-------------------------------------------|

| $f_1 + f_2$             | Second Harmonic Sum              | $A^2a_2 + A^4a_43$                        |

| 2f <sub>2</sub>         | Second Harmonic Right            | $A^2a_2\frac{1}{2} + A^4a_42$             |

| $3f_2 - f_1$            | Second Harmonic Difference Right | $A^4\left(a_4\frac{1}{2}\right)$          |

| $4f_1 - f_2$            | Third Harmonic Difference Left   | $A^5\left(a_5\frac{5}{16}\right)$         |

| $3f_1$                  | Third Harmonic Left              | $A^3a_3\frac{1}{4} + A^5a_5\frac{25}{16}$ |

| $2f_1 + f_2$            | Third Harmonic Sum Left          | $A^3a_3\frac{3}{4} + A^5a_5\frac{25}{8}$  |

| $2f_2 + f_1$            | Third Harmonic Sum Right         | $A^3a_3\frac{3}{4} + A^5a_5\frac{25}{8}$  |

| $3f_2$                  | Third Harmonic Right             | $A^3a_3\frac{1}{4} + A^5a_5\frac{25}{16}$ |

| $4f_2 - f_1$            | Third Harmonic Difference Right  | $A^5\left(a_5\frac{5}{16}\right)$         |

| $4f_1$                  | Fourth Harmonic Left             | $A^4\left(a_4\frac{1}{8}\right)$          |

| $3f_1 + f_2$            | Fourth Harmonic Sum Left         | $A^4\left(a_4\frac{1}{2}\right)$          |

| $2f_1 + 2f_2$           | Fourth Harmonic Sum Centre       | $A^4\left(a_4\frac{1}{2}\right)$          |

| $3f_2 + f_1$            | Fourth Harmonic Sum Right        | $A^4\left(a_4\frac{1}{2}\right)$          |

| $4f_2$                  | Fourth Harmonic Right            | $A^4\left(a_4\frac{1}{8}\right)$          |

| 5 <i>f</i> <sub>1</sub> | Fifth Harmonic Left              | $A^5\left(a_5\frac{1}{16}\right)$         |

| $4f_1 + f_2$            | Fifth Harmonic Sum Outer Left    | $A^5\left(a_5\frac{5}{16}\right)$         |

| $3f_1 + 2f_2$           | Fifth Harmonic Sum Inner Left    | $A^5\left(a_5\frac{5}{8}\right)$          |

|                         |                                  |                                           |

| $3f_2 + 2f_1$           | Fifth Harmonic Sum Inner Right | $A^5\left(a_5\frac{5}{8}\right)$  |

|-------------------------|--------------------------------|-----------------------------------|

| $4f_2 + f_1$            | Fifth Harmonic Sum Outer Right | $A^5\left(a_5\frac{5}{16}\right)$ |

| 5 <i>f</i> <sub>2</sub> | Fifth Harmonic Right           | $A^5\left(a_5\frac{1}{16}\right)$ |

This table shows that in a nonlinear, memoryless device, the magnitudes of the intermodulation components are not dependent on the instantaneous bandwidth of the signal. However, we know that in real devices, the magnitude of the third and fifth order intermodulation products exhibits a dependence on the instantaneous bandwidth of the signal. This indicates the presence of bandwidth dependent nonlinear effects with memory. These nonlinear effects are described as memory effects and are further classified into two distinct categories: thermal memory effects and electrical memory effects.

#### 2.2 PA Behavior With Memory Effects

This section explores the two different sources of memory effects in PA behavior.

#### 2.2.1 Thermal Memory Effects

A power amplifier's performance is affected by several factors. One of the factors that is sometimes overlooked is the dynamic temperature variation and its effect on the electrical properties of the transistor. While much effort is put into cooling systems for high power amplifiers, it is impossible to obtain a perfectly a constant temperature due to fluctuations in the drive level in the input signals. Figure 2.2 illustrates the IMD3 contribution of thermal memory effects as a function of tone spacing in a typical LDMOS amplifier. One can see that the contribution drops by almost 20 dB over 4 MHz

As discussed earlier, one of the simplest tests to detect memory effects is the two tone test. Examining the IMD3 of a PA as the tone spacing is varied in a two-tone test can help reveal the source of the memory effects. If the PA's IMD3 levels vary significantly when the tone spacing is 100 KHz to a few MHz, then thermal memory effects are the likely culprit.

Figure 2.2: IMD3 Amplitude due to Thermal Memory Effects Versus Frequency Spacing

### 2.2.2 Electrical Memory Effects

To determine how electrical memory effects originate, it is crucial to understand how real power amplifiers differ from the memoryless polynomial model presented in the earlier section. This section explores the causes of electrical memory effects which are prevalent at modulation bandwidths of greater than 1 MHz. First, a qualitative understanding of the node impedances of power amplifiers is explored. The effect of these impedances on the distortion components is examined. Finally, the relation between the power amplifier design and memory effects is discussed.

Figure 2.3 shows a simplified block diagram of a power amplifier's output node. From this diagram, we can see that there are three factors that will determine the output node impedance:

- The transistor's bias dependent output impedance

- The Matching Network (MN) impedance

- The Bias Network (BN) impedance

Figure 2.3: Output Node Impedance Block Diagram

The transistor's output impedance is generally fixed when the class of operation of the PA is decided. The Matching Network (MN) is generally designed as a band pass network and as such has the most impact on the fundamental band and will generally reflect all other harmonics back into the transistor. Similarly, the Biasing Network (BN) is designed as a lowpass filter to allow DC power to flow to the transistor while blocking all RF signals. As such, the BN has the most significant impact on intermodulation products in the baseband frequency range. As a note, the preferred bias topology in today's RF PA usually involves the use of a quarter wavelength transformer. This topology, which is usually designed to present an open circuit at the fundamental frequency, will present a short circuit at all even harmonics. Therefore, the bias network will influence the output node impedance at all even harmonics if this topology is used.

To understand how these impedances contribute to memory effects the PA can be modeled using the simplified block diagram shown in Figure 2.4, where G(f) represents a memoryless nonlinearity produced by the power amplifier, H(f) is a linear function representing the reflection coefficient of the output node, and x, y and z are the PA input, signal components reinjected into the PA, and the PA output respectively.

Figure 2.4: Simplified Block Diagram of the PA Nonlinearity Mechanism

The reflected signal components are remixed via the nonlinearity in the PA back into the fundamental frequency band. If we begin with an initial assumption that H is an all pass filter to simplify the analysis, the coefficients of these reflected components can be calculated using simple trigonometric identities. Table 2.2 illustrates all of the frequency combinations that will result in creating a product that is at the same frequency as the right IMD3 product. For example, the second harmonic left component  $(2f_2)$  will mix with the right fundamental  $(f_1)$  to produce an additional right IMD3 component via a  $2^{nd}$  order nonlinearity. Note here that some frequency components appear to be replicated, this is not the case. For example the second entry in Table 2-2 is a third order recombination product which can be obtained from developing the expression  $\cos^2(f_2 - f_1)\cos\mathcal{C}(f_1)$  and separating it into its various frequency components. Conversely the third entry is obtained from developing the second order expression  $\cos(2f_2 - 2f_1)\cos\mathcal{C}(f_1)$ .

TABLE 2-2: FREQUENCY COMPONENTS THAT WILL REMIX INTO THE RIGHT IMD3 PRODUCT

| Frequency 1   | Frequency 2    | Nonlinearity Mixing Order | Coefficient                          |

|---------------|----------------|---------------------------|--------------------------------------|

| $f_2 - f_1$   | $f_2$          | 2 <sup>nd</sup> Order     | $A^3a_1a_2^2$                        |

| $2(f_2-f_1)$  | $f_1$          | 3 <sup>rd</sup> Order     | $\frac{3}{4}A^5a_1a_2^2a_3$          |

| $2f_2 - 2f_1$ | $f_1$          | 2 <sup>nd</sup> Order     | $\frac{3}{4}A^5a_1a_2a_4$            |

| $3f_1 - 2f_2$ | $4(f_2-f_1)$   | 5 <sup>th</sup> Order     | $\frac{25}{128}A^{13}a_2^4a_5^2$     |

| $3f_1 - 2f_2$ | $2(2f_2-2f_1)$ | 3 <sup>rd</sup> Order     | $\frac{45}{128}A^{13}a_3 \ a_4^2a_5$ |

| $2f_1 - f_2$  | $3(f_2-f_1)$   | 4 <sup>th</sup> Order     | $\frac{3}{8}A^9a_2^3a_3 a_4$         |

| $3f_2 - 2f_1$ | $-(f_2-f_1)$   | 2 <sup>nd</sup> Order     | $\frac{5}{8}A^7a_2^2a_5$             |

| $-(3f_1-f_2)$ | $2f_1 + f_2$   | 2 <sup>nd</sup> Order     | $\frac{3}{8}A^7a_2\ a_3\ a_4$        |

| $-(2f_1)$     | $2f_2 + f_1$   | 2 <sup>nd</sup> Order     | $\frac{3}{8}A^5a_2^2a_3$             |

| $-2(f_1)$     | $2f_2 + f_1$   | 3 <sup>rd</sup> Order     | $\frac{9}{16}A^5a_2\ a_3^2$          |

| $f_2 + f_1$         | $-(2f_1 + f_2)$   | 2 <sup>nd</sup> Order | $\frac{3}{4}A^5a_2^2a_3$         |

|---------------------|-------------------|-----------------------|----------------------------------|

| $2f_2$              | $-f_1$            | 2 <sup>nd</sup> Order | $\frac{1}{2}A^3a_1 \ a_2^2$      |

| 2(f <sub>2</sub> )  | $-f_1$            | 3 <sup>rd</sup> Order | $\frac{3}{4}A^3a_1^3a_2$         |

| $3f_2 - f_1$        | $-f_2$            | 2 <sup>nd</sup> Order | $\frac{1}{2}A^5a_1 \ a_2 \ a_4$  |

| $-(4f_1-f_2)$       | $3f_1 + f_2$      | 2 <sup>nd</sup> Order | $\frac{5}{32}A^9a_2a_4a_5$       |

| $3f_1$              | $-2(2f_1-f_2)$    | 3 <sup>rd</sup> Order | $\frac{27}{256}A^9a_3^4$         |

| 3(f <sub>1</sub> )  | $-2(2f_1-f_2)$    | 5 <sup>th</sup> Order | $\frac{45}{128}A^9a_1^3a_3^2a_5$ |

| 3f <sub>2</sub>     | $-(f_2+f_1)$      | 2 <sup>nd</sup> Order | $\frac{1}{4}A^5a_2^2a_3$         |

| $3(f_2)$            | $-(\omega_2+f_1)$ | 4 <sup>th</sup> Order | $\frac{1}{2}A^5a_1^3a_2\ a_4$    |

| $4f_2 - f_1$        | $-(2f_2)$         | 2 <sup>nd</sup> Order | $\frac{5}{32}A^5a_2^2a_5$        |

| $4f_2 - f_1$        | $-2(f_2)$         | 3 <sup>rd</sup> Order | $\frac{15}{64}A^5a_1^2a_3\ a_5$  |

| $2f_1 + 2f_2$       | $-(3f_1)$         | 2 <sup>nd</sup> Order | $\frac{1}{8}A^7a_2\ a_3\ a_4$    |

| $2(f_1 + f_2)$      | $-(3f_1)$         | 3 <sup>rd</sup> Order | $\frac{3}{16}A^7a_2^2a_3^2$      |

| $2(f_1 + f_2)$      | $-3(f_1)$         | 5 <sup>th</sup> Order | $\frac{5}{8}A^7a_1^3a_2^2a_5$    |

| $(2f_1 + 2f_2)$     | $-3(f_1)$         | 4 <sup>th</sup> Order | $\frac{5}{8}A^7a_1^3a_4^2$       |

| $3f_2 + f_1$        | $-(2f_1+f_2)$     | 2 <sup>nd</sup> Order | $\frac{3}{8}A^7a_2\ a_3\ a_4$    |

| $4f_2$              | $-(2f_2+f_1)$     | 2 <sup>nd</sup> Order | $\frac{3}{32}A^7a_2\ a_3\ a_4$   |

| 2(2f <sub>2</sub> ) | $-(2f_2+f_1)$     | 3 <sup>rd</sup> Order | $\frac{9}{64}A^7a_2^2a_3^2$      |

| 4(f <sub>2</sub> )      | $-(2f_2+f_1)$             | 5 <sup>th</sup> Order | $\frac{15}{64}A^7a_1^4a_3\ a_5$   |

|-------------------------|---------------------------|-----------------------|-----------------------------------|

| 5 <i>f</i> <sub>1</sub> | $-2(3f_1+f_2)$            | 3 <sup>rd</sup> Order | $\frac{3}{256}A^{13}a_3^3a_5$     |

| $-(4f_1+f_2)$           | $3(f_1+f_2)$              | 4 <sup>th</sup> Order | $\frac{5}{32}A^{11}a_2^3a_4\ a_5$ |

| $3f_1 + 2f_2$           | $-(4f_1)$                 | 2 <sup>nd</sup> Order | $\frac{5}{64}A^9a_2\ a_4\ a_5$    |

| $3f_1 + 2f_2$           | $-2(2f_1)$                | 3 <sup>rd</sup> Order | $\frac{15}{128}A^9a_2^2a_3\ a_5$  |

| $3f_1 + 2f_2$           | $-4(f_1)$                 | 5 <sup>th</sup> Order | $\frac{25}{128}A^9a_1^4a_5^2$     |

| $3f_2 + 2f_1$           | $-(3f_1+f_2)$             | 2 <sup>nd</sup> Order | $\frac{25}{64}A^9a_2\ a_4\ a_5$   |

| $4f_2 + f_1$            | $-\left(2f_1+2f_2\right)$ | 2 <sup>nd</sup> Order | $\frac{5}{32}A^9a_2\ a_4\ a_5$    |

| $4f_2 + f_1$            | $-2(f_1+f_2)$             | 3 <sup>rd</sup> Order | $\frac{15}{64}A^9a_2^2a_3\ a_5$   |

| 5 <i>f</i> <sub>2</sub> | $-(3f_2+f_1)$             | 2 <sup>nd</sup> Order | $\frac{1}{32}A^9a_2\ a_4\ a_5$    |

Similarly, Table 2-3 shows the frequency combinations that will produce distortion in the right IMD5 component.

TABLE 2-3: FREQUENCY COMPONENTS THAT WILL REMIX INTO THE RIGHT IMD5 PRODUCT

| Frequency 1    | Frequency 2  | Nonlinearity Mixing Order | Coefficient                        |

|----------------|--------------|---------------------------|------------------------------------|

| $f_2 - f_1$    | $2f_2 - f_1$ | 2 <sup>nd</sup> Order     | $\frac{3}{4}A^5a_2^2a_3$           |

| $2(f_2 - f_1)$ | $f_2$        | 3 <sup>rd</sup> Order     | $\frac{3}{4}A^5a_1 \ a_2^3$        |

| $2f_2 - 2f_1$  | $f_2$        | 2 <sup>nd</sup> Order     | $\frac{3}{4}A^5a_1 \ a_2 \ a_4$    |

| $-(3f_1-2f_2)$ | $f_1 + f_2$  | 2 <sup>nd</sup> Order     | $\frac{5}{8}A^7a_2^2a_5$           |

| $2f_1 - f_2$   | $4(f_2-f_1)$ | 5 <sup>th</sup> Order     | $\frac{15}{64}A^{11}a_2^4a_3\ a_5$ |

| $2f_1 - f_2$        | $2(2f_2-2f_1)$          | 3 <sup>rd</sup> Order | $\frac{81}{256}A^{11}a_3^2a_4^2$       |

|---------------------|-------------------------|-----------------------|----------------------------------------|

| $f_1$               | $3(f_2-f_1)$            | 4 <sup>th</sup> Order | $\frac{1}{2}A^4a_1\ a_2\ a_4$          |

| $-(3f_1-f_2)$       | $2f_2 + f_1$            | 2 <sup>nd</sup> Order | $\frac{3}{8}A^7a_2\ a_3\ a_4$          |

| $-(2f_1)$           | 3f <sub>2</sub>         | 2 <sup>nd</sup> Order | $\frac{1}{8}A^5a_2^2a_3$               |

| $-2(f_1)$           | 3 <i>f</i> <sub>2</sub> | 3 <sup>rd</sup> Order | $\frac{3}{16}A^5a_1^2a_3^2$            |

| $-2(f_1)$           | 3(f <sub>2</sub> )      | 5 <sup>th</sup> Order | $\frac{5}{8}A^5a_1^5a_5$               |

| $-(2f_1)$           | $3(f_2)$                | 4 <sup>th</sup> Order | $\frac{1}{4}A^5a_1^3a_2\ a_4$          |

| $2f_2$              | $-(2f_1-f_2)$           | 2 <sup>nd</sup> Order | $\frac{3}{8}A^5a_2^2a_3$               |

| 2(f <sub>2</sub> )  | $-(2f_1-f_2)$           | 3 <sup>rd</sup> Order | $\frac{9}{16}A^5a_1^2a_3^2$            |

| $3f_2 - f_1$        | -f <sub>1</sub>         | 2 <sup>nd</sup> Order | $\frac{1}{2}A^5a_1\ a_2\ a_4$          |

| $-(4f_1-f_2)$       | $2f_1 + 2f_2$           | 2 <sup>nd</sup> Order | $\frac{15}{64}A^9a_2\ a_4\ a_5$        |

| $-(4f_1-f_2)$       | $2(f_1 + f_2)$          | 3 <sup>rd</sup> Order | $\frac{15}{64}A^7a_2^2a_3\ a_5$        |

| $4f_1 - f_2$        | $-2(3f_1-2f_2)$         | 3 <sup>rd</sup> Order | $\frac{375}{4096}A^{15}a_3 a_5^3$      |

| $-3f_1$             | $3f_2 + f_1$            | 2 <sup>nd</sup> Order | $\frac{1}{8}A^{7}a_{2}^{2}a_{3} a_{4}$ |

| $-3(f_1)$           | $3f_2 + f_1$            | 4 <sup>th</sup> Order | $\frac{1}{2}A^{7}a_{1}^{3}a_{4}^{2}$   |

| $4f_2 - f_1$        | $-(f_1+f_2)$            | 2 <sup>nd</sup> Order | $\frac{5}{16}A^7a_2^2a_5$              |

| $4f_2$              | $-(2f_1+f_2)$           | 2 <sup>nd</sup> Order | $\frac{3}{32}A^7a_2\ a_3\ a_4$         |

| 2(2f <sub>2</sub> ) | $-(2f_1+f_2)$           | 3 <sup>rd</sup> Order | $\frac{9}{128}A^7a_2^2a_3^3$           |

| 4(f <sub>2</sub> )      | $-(2f_1+f_2)$    | 5 <sup>th</sup> Order | $\frac{15}{64}A^7a_1^4a_3\ a_5$   |

|-------------------------|------------------|-----------------------|-----------------------------------|

| -5f <sub>1</sub>        | $3(f_1 + f_2)$   | 4 <sup>th</sup> Order | $\frac{1}{32}A^{11}a_2^3a_4\ a_5$ |

| $-(4f_1+f_2)$           | $2(2f_2 + 3f_1)$ | 3 <sup>rd</sup> Order | $\frac{375}{4096}A^{15}a_3 a_5^3$ |

| $3f_2 + 2f_1$           | $-(4f_1)$        | 2 <sup>nd</sup> Order | $\frac{5}{64}A^9a_2\ a_4\ a_5$    |

| $3f_2 + 2f_1$           | $-2(2f_1)$       | 3 <sup>rd</sup> Order | $\frac{15}{512}A^9a_2^2a_3\ a_5$  |

| $3f_2 + 2f_1$           | $-4(f_1)$        | 5 <sup>th</sup> Order | $\frac{25}{128}A^9a_1^4a_5^2$     |

| $4f_2 + f_1$            | $-(3f_1+f_2)$    | 2 <sup>nd</sup> Order | $\frac{5}{32}A^9a_2\ a_4\ a_5$    |

| $5f_2$                  | $-(2f_1+2f_2)$   | 2 <sup>nd</sup> Order | $\frac{1}{32}A^9a_2\ a_4\ a_5$    |

| 5 <i>f</i> <sub>2</sub> | $-2(f_1+f_2)$    | 3 <sup>rd</sup> Order | $\frac{3}{64}A^9a_2^2a_3\ a_5$    |

While there is a significant number of combinations that will result in unwanted distortion in the fundamental band, most of them play a minor role in the distortion due to the frequency response of the linear element H(f) shown in Figure 2.4. The variation of the output node impedance as a function of frequency, as represented by the frequency response of H(f) is the cause of the frequency dependent electrical memory effects. While the output node impedance does vary to some degree in the each of the frequency bands, the frequency bands that will display the most variation are the baseband, fundamental and second harmonic bands. Hence, the distortion elements generated using frequency components from the third and higher frequency bands can be dismissed as trivial.

Assuming a centre frequency of 2.14 GHz and a modulation bandwidth of 20 MHz, the baseband response is important up to 40 MHz or beyond because of the 4<sup>th</sup> order envelope harmonic component. An important difference between the baseband frequency band and all others is that it is dependent on the modulation bandwidth and independent of the centre frequency. The fundamental band will be a 100 MHz, between 2.09 GHz and 2.19 GHz due to

the importance of the IMD5 distortion products. This bandwidth is a fairly significant design constraint as it represents 4.67% of the centre frequency. The second harmonic band is defined between 4.24 GHz and 4.32 GHz. While keeping this bandwidth does not seem to represent a significant portion of its centre frequency, the prevalence of the use of a second harmonic trap in the RF choke of the BN of most modern PAs is something that has not been examined in great detail.

Minimizing the memory effect generated from the baseband frequency harmonics becomes of pivotal importance as the band of interest is not dependent on the centre frequency of the transmitted signal. Conversely, the band of interest around the fundamental and second harmonic frequency bands on the centre frequency, is significantly more challenging. Hence, ensuring that the output node impedance is either very low or constant over this region through careful design of the bias network will minimize memory effects regardless of the intended frequency of operation of the PA.

# Chapter 3:

# Linearization of Multicarrier DPA using a Memory Polynomial Digital Predistorter

Chapters one and two demonstrated the need for a solution to the power efficiency and linearity problem that plagues modern PA designers. A Doherty power amplifier with digital predistortion was proposed as a solution to this problem. However, one must explore how this solution can offer the promised high average while meeting communication standards linearity requirements when stimulated with realistic test signals.

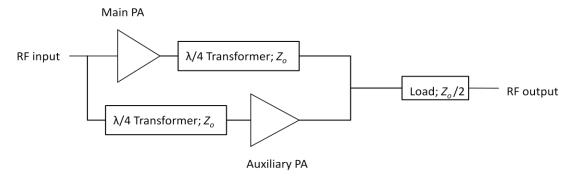

This chapter explores the various modeling techniques used to model PA nonlinearity and construct the corresponding DPDs. After some comparisons, a memory polynomial is chosen as the technique used for this thesis. The computation complexity of Memory Polynomial (MP) DPD is examined as well as ways to reduce it. Despite reducing the complexity of the required MP DPD, the fact remains that the DPA has strong memory effects. Hence, the MP DPD required to linearize the DPA to meet linearity requirements will be expensive from a computational standpoint. Therefore it becomes necessary to minimize memory effects at the design stage of the PA to reduce the complexity of the MP DPD required. ADS simulations and measurements were used to quantify the strength of the memory effects of the DPA using the linearity benchmarks described in Chapter 2. The results of these simulations show that ADS simulation cannot adequately predict memory effects at the design stage in the PA.

#### 3.1 Motivation

As discussed earlier, Doherty power amplifiers have shown significant power efficiency enhancements over the standard Class AB linear counterparts at the cost of slightly decreased linearity. For an RF transmitter which uses a DPA to meet communication standards' requirements, linearization techniques are required. Among these techniques, Baseband Digital Predistortion is currently the most suitable linearization scheme, as it preserves the overall efficiency of an RF system. Baseband DPD exploits the advances in Digital Signal Processors (DSP) and Field Programmable Gate Arrays (FPGA). However, the application of DPD poses some challenges attributed to significant memory effects especially when driven with wideband and multi-carrier signals.

To improve the quality of signals, the DPD has to compensate for both the nonlinearities and memory effects of the transmitter PA. Various comprehensive DPD schemes such as Volterra series and their derivations (memory polynomials, Hammerstein, Wiener) and Neural Networks [15] were introduced in the literature to linearize wideband PAs.

## 3.2 Modeling Techniques

This section examines the 3 most commonly used behavioral models used to model PAs or to construct DPDs.

#### 3.2.1 Volterra Series

A linear, causal system with memory can be described by the following:

$$y(t) = \int_{-\infty}^{\infty} h(\sigma)x(t - \sigma)d\sigma$$

(3-1)

where x(t) is the system's input, y(t) is its output and h(t) is its impulse response. A nonlinear system without memory can be described with a Taylor seies:

$$y(t) = \sum_{n=1}^{\infty} a_n [x(t)]^n$$

(3-2)

where x(t) is the system's input, y(t) is its output and  $a_n$  are the Taylor series coefficients.

A Volterra series combines the above two representations to describe a nonlinear system with memory as follows:

$$y(t) = \sum_{n=1}^{\infty} \frac{1}{n!} \int_{-\infty}^{\infty} du_1 \dots \int_{-\infty}^{\infty} du_n g_n(u_1, \dots, u_n) \prod_{r=1}^n x(t - u_r)$$

(3-3)

$$= \frac{1}{1!} \int_{-\infty}^{\infty} du_1 g_1(u_1) x(t - u_1)$$

(3-4)

$$+ \frac{1}{2!} \int_{-\infty}^{\infty} du_1(u_1) \int_{-\infty}^{\infty} du_2 g_2(u_1, u_2) x(t - u_1) x(t - u_2)$$

(3-5)

$$+ \frac{1}{3!} \int_{-\infty}^{\infty} du_1(u_1) \int_{-\infty}^{\infty} du_2 \int_{-\infty}^{\infty} du_3 g_3(u_1, u_2, u_3) x(t - u_1) x(t - u_2) x(t - u_3)$$

(3-6)

where x(t) is the system's input, y(t) is its output and  $g_n(u_1, ..., u_n)$  are the Volterra kernels of the systems.  $u_i$  represent time variables used to distinguish them better from t. One will recognize Equation (3-4) to be the familiar convolution shown in Equation (3-1), with  $g_1(u_1)$  as

the impulse response. Hence, the Volterra kernerls where n > 1 can be likened to " $n^{th}$  order impulse responses". [16]

While the Volterra representation is very powerful, its complexity makes it extremely cumbersome when used to model higher order non-linearities. Hence a number of approximations of the Volterra series have been proposed.

#### 3.2.2 Weiner and Hammerstein Models

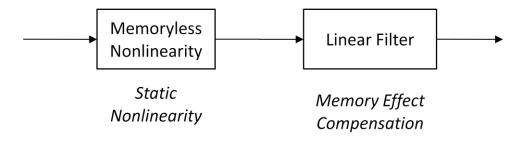

Hammerstein and Weiner models are examples of Volterra approximation that use two separate blocks to account for the nonlinearities and the memory effects. Also known as two-box-based models [17]-[21], these models are essentially permutations of each other. The Hammerstein model consists of a nonlinear block followed by a linear block, generally a filter, as shown in Figure 3.1. In the Weiner model, the linear block precedes the nonlinear one.

Figure 3.1: Typical Hammerstein PA Model

In the case of the PA, the first box of the Hammerstein scheme captures the static nonlinear behavior, while the second one is intended to account for the PA's memory effects. However, the limitations of conventional Hammerstein/Weiner schemes in mimicking wideband PA behavior have been demonstrated in [19]. While Parallel Hammerstein/Weiner models have been suggested [20] to address these limitations by stacking extra branches in parallel, parameter identification becomes extremely tedious.

## 3.2.3 Memory Polynomial Model

The memory polynomial is a comprehensive modeling scheme derived from the Volterra model. The multi-branch MP, as introduced by Kim et al. [21], requires less coefficients than the Volterra model while preserving its capability of accurately capturing memory and nonlinearity

effects. In fact the number of coefficients of a Volterra series of memory depth *K* and maximum polynomial order *P* can be written as:

number of coefficients =

$$(K+1)^P$$

(3-7)

where as the coefficients of a memory polynomial of equal memory depth and maximum polynomial order is given by:

number of coefficients =

$$P(K+1)$$

(3-8)

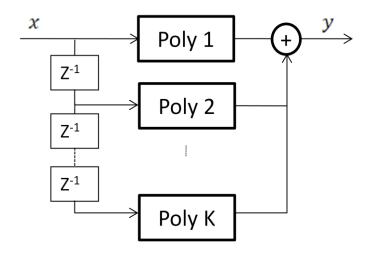

A typical memory polynomial structure is shown in Figure 3.2. Each branch is a polynomial Poly of degree *P* that can be expressed as:

$$Poly i = h_1 x + h_2 x |x| + h_3 x |x|^2 + \dots + h_p x |x|^{p-1}$$

(3-9)

The general model equation can be written as

$$y(n) = \sum_{k=0}^{K} \sum_{p=1}^{P} h_{p,k} |x(n-k)|^{p-1} x(n-k)$$

(3-10)

where x(n) and y(n) are the complex envelope signals at the predistorter input and output, respectively. K is the memory depth of the system, equivalent to the number of polynomial branches. P represents the polynomial order of the branches and  $h_{p,k}$  designates the polynomial coefficients of the kth branch.

Figure 3.2: Typical Memory Polynomial Structure.

The identification of the DPD coefficients is done by solving the Least Squares Error problem formulated as y = A B and detailed in [22]; where

$$\mathbf{y} = [y(0) \quad \cdots \quad y(N)]^T \tag{3-11}$$

$$\mathbf{B} = [h_{1,0} \quad \cdots \quad h_{P,0} \quad h_{1K} \quad \cdots \quad h_{P,K}]^T \tag{3-12}$$

$$\mathbf{A} = [\mathbf{a}(0) \quad \cdots \quad \mathbf{a}(N)]^T \tag{3-13}$$

$$\boldsymbol{a}(n) = \begin{bmatrix} \beta_1(x(n)) & \cdots & \beta_P(x(n)) & \beta_1(x(n-1)) & \cdots \\ \cdots & \beta_1(x(n-K)) & \cdots & \beta_P(x(n-K)) \end{bmatrix}$$

(3-14)

where  $\beta_p(x(n-k)) = |x^{p-1}(n-k)|x(n-k)$ .

The coefficients of B are determined using LSE optimization and are calculated using the following:

$$\mathbf{B} = pinv(\mathbf{A})\mathbf{y} \tag{3-15}$$

where  $pinv(A) = (A^H A)^{-1} A^H$  is the pseudo-inverse of the matrix A.

The computational complexity of the DPD resides in the LSE algorithm's complexity being proportional to  $(number\ of\ coefficients)^3$ . Each reduction in the number of unknown coefficients significantly improves the realizability of the scheme. Moreover, the accuracy of the solution reached by such an algorithm depends directly on the conditioning of the matrix A [23]. Higher polynomial orders yield higher conditioning numbers, which in turn decreases the stability and accuracy of the DPD coefficient solution.

Henceforth, for both realizability and efficiency of DPD, the MP's number of branches and the polynomial orders of each branch must be carefully chosen to optimize the linearization outcome of the DPD and avoid the adverse effects of over or under-fitting of the problem.

The Memory Polynomial model is widely used to compensate for the RF PA behavior characteristics as it offers a good tradeoff between modeling accuracy and complexity of DSP

implementation. The complexity of the MP scheme is dependent on two parameters: (i) the order of the polynomial and (ii) the number of memory branches needed to compensate for both the nonlinearity and memory effects of the PA behavior. The values of these parameters required for an efficient DPD depend directly on the PA induced nonlinearities and memory effects.

## 3.3 Memory Polynomial Digital Predistortion Complexity Reduction

This section examines two different approaches to reducing the number of coefficients and hence decreases the computational complexity of the MP DPD.

#### 3.3.1 Memory Polynomial Over and Under-Fitting

When evaluating a MP-DPD, it has been implied that increasing polynomial orders provides a better fit for the nonlinearities of the PA and improves the DPD's linearization capacity. This "over fitting" the PA behavior with higher orders of polynomials than are actually needed, not only decreases the stability of the DPD coefficient computations but also has no noticeable effect on the linearization outcome. Moreover, experimental results indicate that a MP having only odd orders can achieve similar linearization as a full odd and even order MP despite the reduced number of coefficients.

In this chapter, a Doherty power amplifier was used in conjunction with a complexity reduced MP-DPD to show the effects of over-fitting and under-fitting on a linearization capability when driven with a 4 carrier WCDMA test signal. Finding the lowest and satisfactory polynomial order is shown to be crucial in the system conditioning and thus the Least Square Error (LSE) solution accuracy, which in turn lowers the calculation and implementation requirements of the DPD.

## 3.3.2 Memory Polynomial Even Order Omission

In this section, the necessity of using the full even and odd orders in the MP-DPD is investigated. Experiments were performed to compare the linearization outcome of

- a MP-DPD using the full even and odd nonlinear terms

- a MP-DPD where the even-order terms are eliminated

The same polynomial orders and same number of branches were used in both cases. Even order terms, as shown in the experimental results of the next section, can be omitted from the