# Nano-Crystalline & Amorphous Silicon PhotoTransistor Performance Analysis

by

Yanfeng Zhang

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2009

©Yanfeng Zhang 2009

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

In this thesis, we compared electrical performance and stability of a novel nanocrystalline Si (nc-Si) thin film phototransistor (TFT) phototransistor and a regular amorphous silicon (a-Si:H) TFT phototransistor for large area imaging applications. The electrical performance parameters of nc-Si TFT phototransistor were extracted from the electrical (current-voltage) testing in dark and under illumination. The field-effect mobility is found to be around 1.2 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, the threshold voltage around 3.9V and the sub-threshold voltage slope around 0.47V/Dec. Optical properties of nc-Si TFT phototransistor have been evaluated under the green light illumination in the range of  $10^{14} - 10^{17}$  lum, and the photocurrent gain and the external quantum efficiency were extracted from the experimental results. By comparing the results with those for a-Si:H TFTs measured under the same conditions, we found that nc-Si TFT has higher photo current gain under low illumination intensity,  $5 \times 10^{14}$  to  $7 \times 10^{15}$  lum. This thesis shows the relations bewteen the photo current gain, the external quantum efficiency, TFT drain and TFT gate bias; the photo current gain and the external quantum efficiency can be controlled by the Vds and the Vgs.

#### **Acknowledgements**

I would like to express profound gratitude to my advisor, Professor Andrei Sazonov, and Dr Yuri Vygranenko for their invaluable support, encouragement, supervision and useful suggestions throughout this thesis project. Their moral support and continuous guidance enabled me to complete my work successfully.

I would also like to thank my family, who has given me unconditional love, and support during these years. Lastly, many thanks to all my professors, teaching assistants and colleagues for the direction they had given me in me thesis project.

### **Table of Contents**

| List of Figures                                                    | vii |

|--------------------------------------------------------------------|-----|

| Chapter 1 Introduction                                             | 1   |

| 1.1 Application Areas for Phototransistor Array                    | 1   |

| 1.2 Problems for Thin Film Imaging Pixels                          | 2   |

| 1.3 Nanocrystalline silicon thin film phototransistor              | 2   |

| 1.4 Goal of the Research                                           | 3   |

| Chapter 2 Background Study                                         | 4   |

| 2.1 Imaging Application                                            | 4   |

| 2.2 Issues for Comparing Photo Transistor Performance              | 7   |

| 2.3 Amorphous Silicon & Nano-crystalline Silicon Photo Transistors | 8   |

| 2.3.1 Amorphous Silicon Transistors                                | 8   |

| 2.3.2 Nano-Crystalline Silicon Transistors                         | 10  |

| Chapter 3 Experiments and Procedures                               | 13  |

| 3.1 Introduction                                                   | 13  |

| 3.2 Photo-TFT Fabrication Process                                  | 13  |

| 3.3 Measurements and Calculations                                  | 19  |

| 3.3.1 Electrical performance                                       | 19  |

| 3.3.2 Performance Measurement under illumination                   | 23  |

| 3.3.3 Stability Test                                               | 25  |

| Chapter 4 Performance Analysis                                     | 27  |

| 4.1 Electrical Performance Analysis                                | 27  |

| 4.1.1 Transfer Characteristic                                      | 27  |

| 4.1.2 Mobility Analysis                                            | 28  |

| 4.1.3 Threshold Voltage Analysis                                   | 30  |

| 4.1.4 Sub-Threshold Slope Analysis                                 | 32  |

| 4.1.5 Off-current Analysis                                         | 34  |

| 4.1.6 Channel Length Vs Series Resistance Analysis                 | 34  |

| 4.2 Performance under Illumination Analysis                        | 36  |

| 4.2.1 Characteristic Photocurrent                                  | 36  |

| 4.2.2 Photocurrent Analysis                                        | 38  |

| 4.2.3 Analysis of the Effect of Light Intensity                              | 45 |

|------------------------------------------------------------------------------|----|

| 4.2.4 Vgs Effect Analysis                                                    | 46 |

| 4.2.5 Photo Current Gain Analysis                                            | 48 |

| 4.2.6 Analysis of the Effect of Vds                                          | 55 |

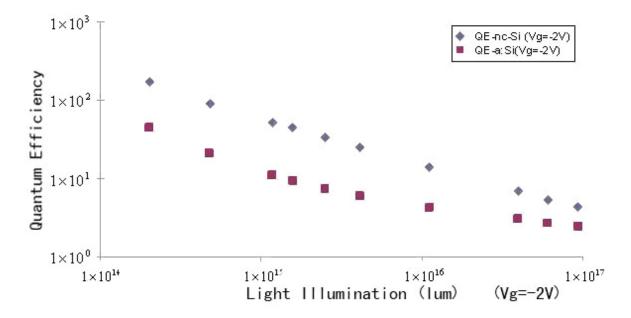

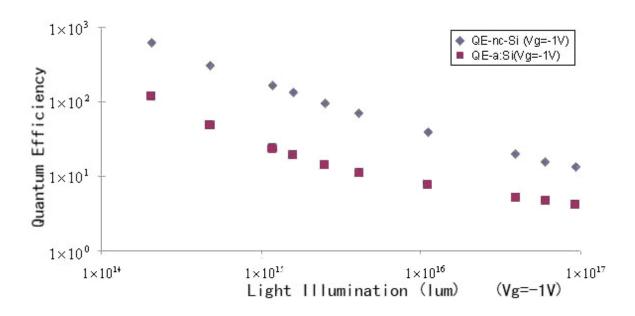

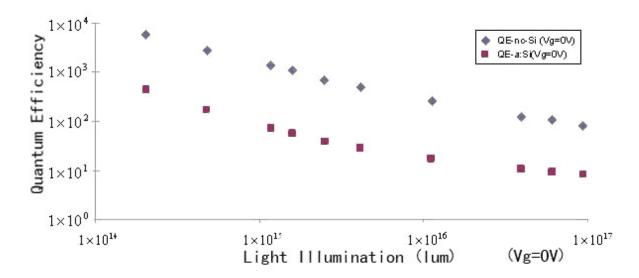

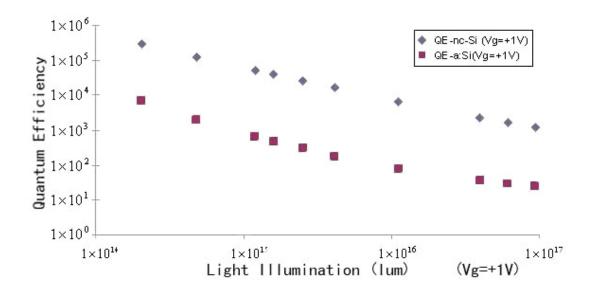

| 4.2.7 Quantum Efficiency Analysis.                                           | 57 |

| 4.2.8 Effect of Vds, Vgs on Quantum Efficiency & Photo Current Gain Analysis | 63 |

| 4.3 Stability Analysis                                                       | 65 |

| Chapter 5 Conclusions.                                                       | 68 |

| 5.1 Summary                                                                  | 68 |

| 5.2 Future Research and Work                                                 | 69 |

| Appendix A Abbreviation Check List                                           | 70 |

| References                                                                   | 71 |

## **List of Figures**

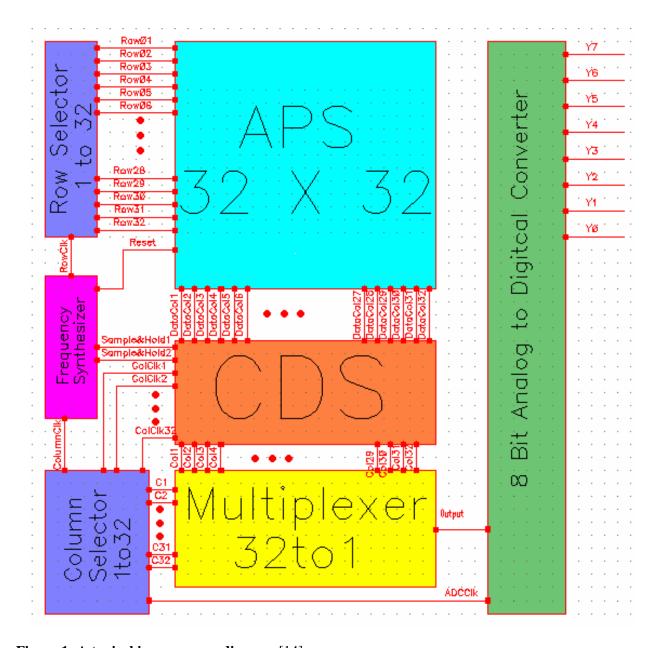

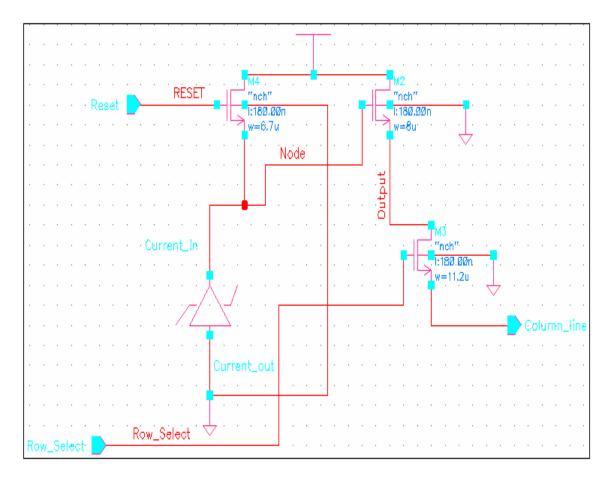

| Figure 1: A typical image sensor diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 2: one APS pixel schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6       |

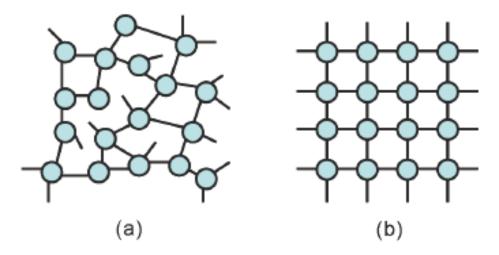

| Figure 3: Two dimensional structure of atomic bonding in (a) a-Si:H and (b) crystalline silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8       |

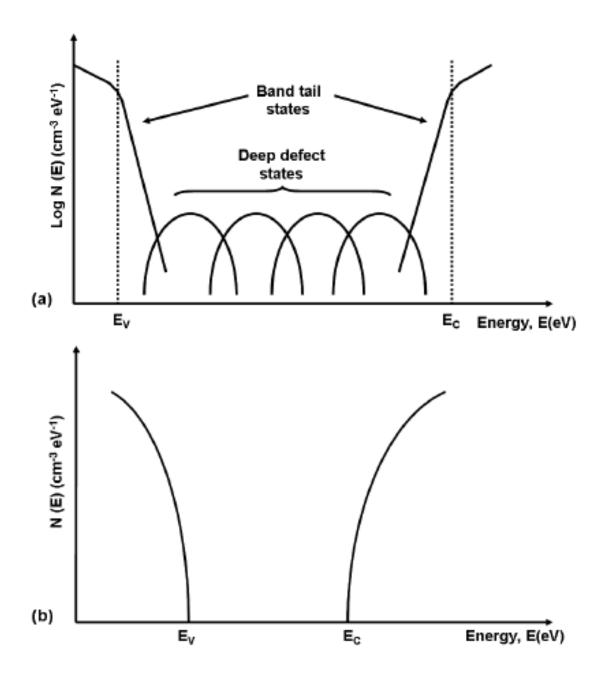

| Figure 4: Distribution of density of states in (a) a-Si:H and (b) crystalline silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9       |

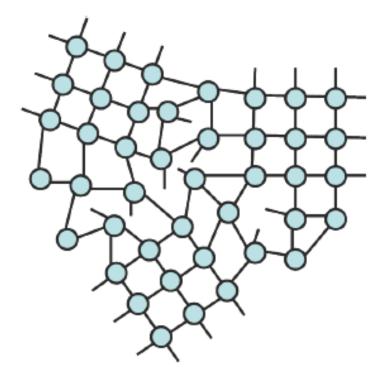

| Figure 5: Two dimensional representation of atomic bonding in nc-Si.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 11      |

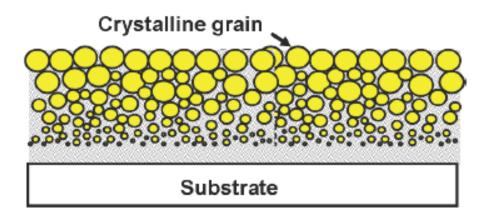

| Figure 6: Material structure of nc-Si. It is inhomogeneous and comprises of smallgrains near                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ar the  |

| substrate and larger grains when thickness increases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12      |

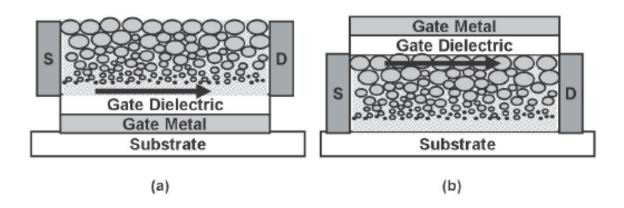

| Figure 7: Two nc-Si TFT structures, (a) bottom-gate and (b) top-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12      |

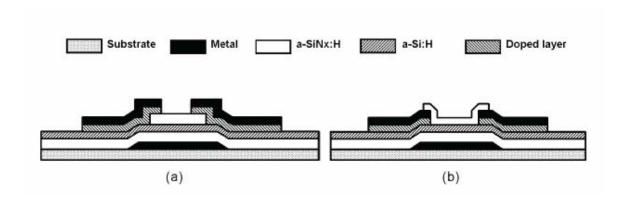

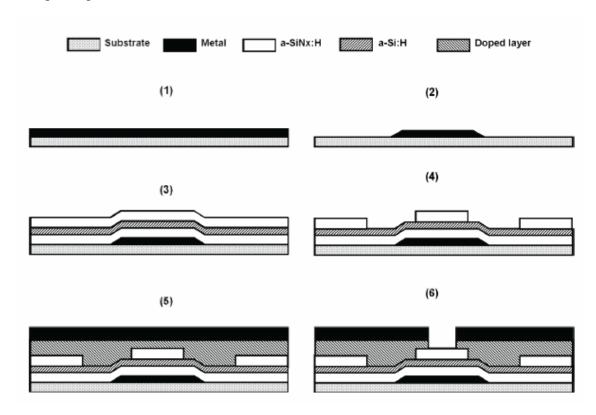

| Figure 8: Bottom-gate inverted-staggered TFT structures, (a) trilayer and (b) back channel etched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | d14     |

| Figure 9: PECVD fabrication process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14      |

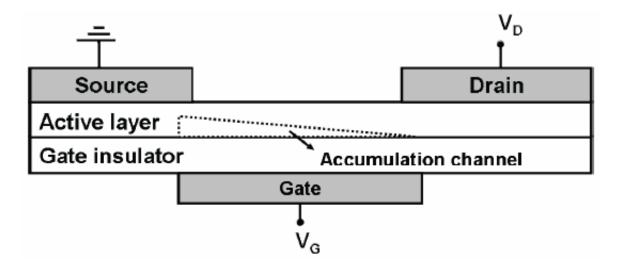

| Figure 10: Illustration of operation of a bottom-gate TFT when gate and drain biases are applied.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16      |

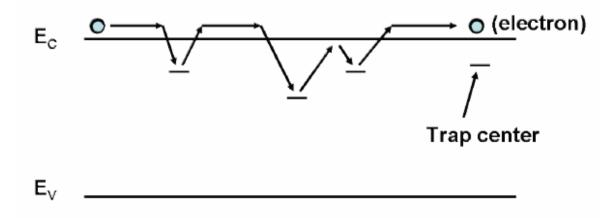

| Figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons that are frequently trapped to the figure 11: A one-dimensional model showing the motion of electrons the figure 11: A one-dimensional model shows the figure 11: A one-dimen | ped in  |

| and released from band tail states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16      |

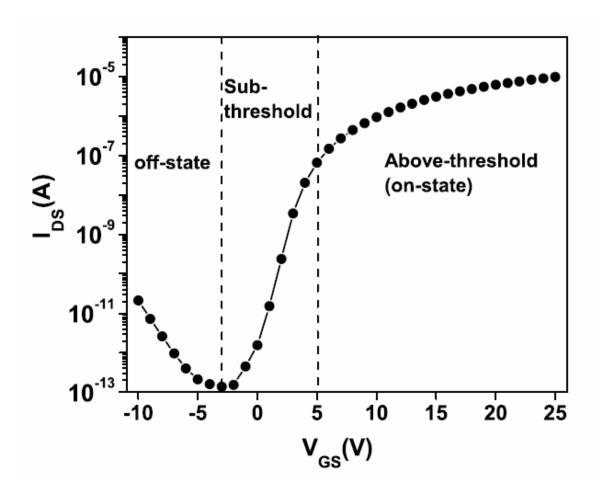

| Figure 12: Typical I-V curve of a bottom-gate nc-Si or a-Si:H TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17      |

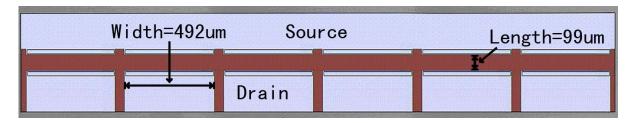

| Figure 13 : Bottom Gate Photo Transistor Length=99um and Width=492 um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18      |

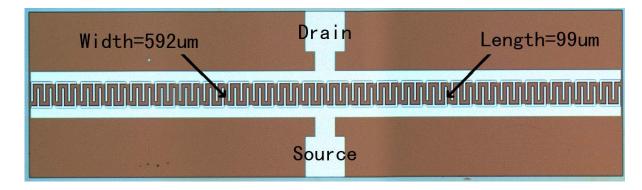

| Figure 14: Bottom Gate Photo Transistor Length=99um and Width=592 um                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 18      |

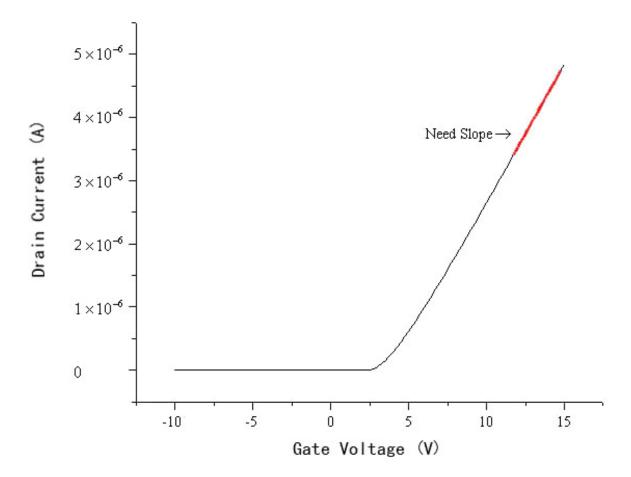

| Figure 15: Field-Effect Mobility and Vt calculation Method.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20      |

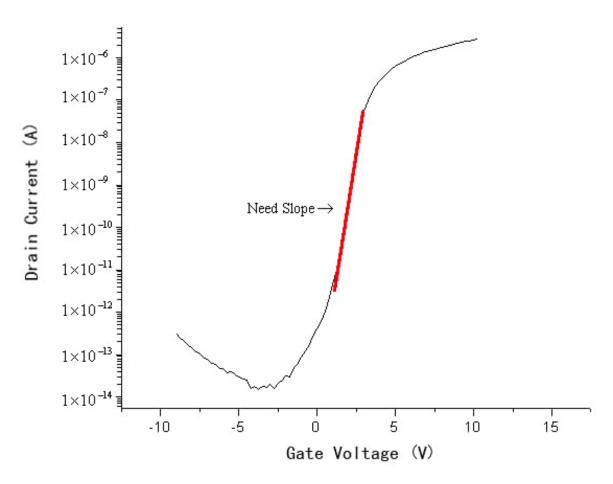

| Figure 16: Sub-threshold Voltage Slope Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22      |

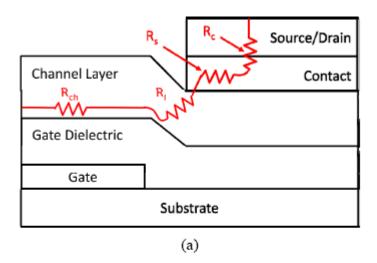

| Figure 17: (a) Parasitic components in staggered bottom gate nc-Si:H TFT and (b) equivalent of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | circuit |

| for parasitic resistance analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23      |

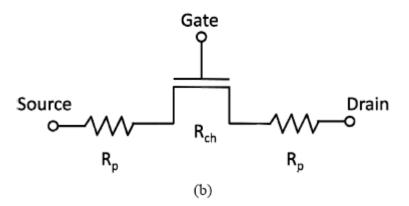

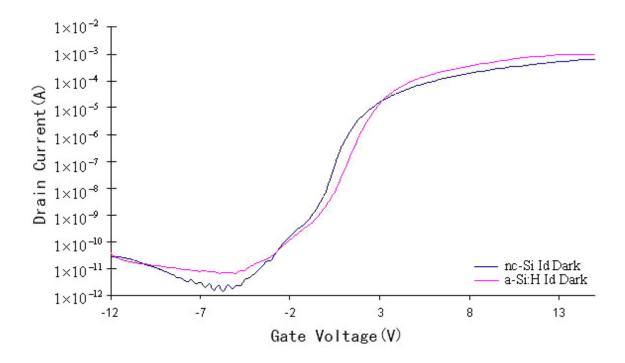

| Figure 18: nc-Si Vs a-Si:H Transfer Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27      |

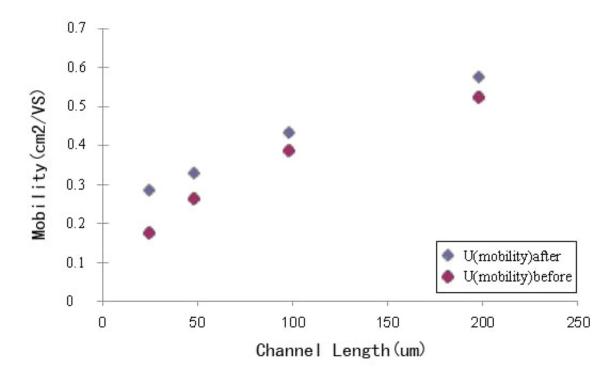

| Figure 19: Mobility of a-Si:H TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28      |

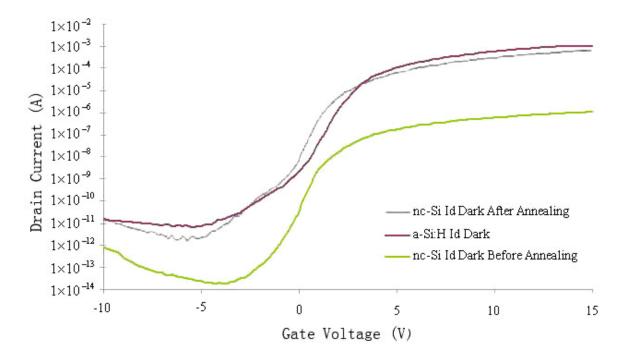

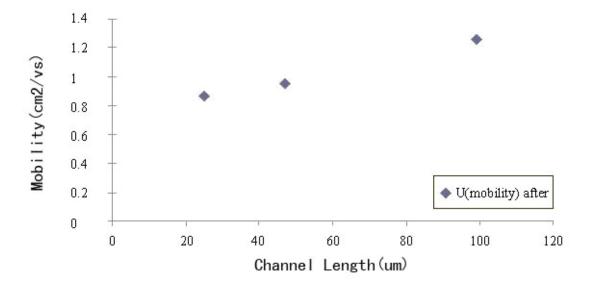

| Figure 20: Mobility of nc-Si TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29      |

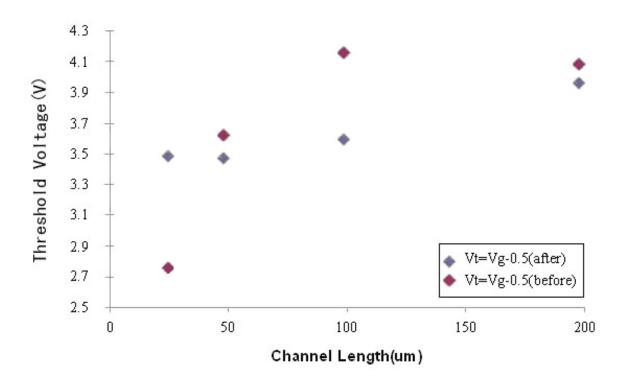

| Figure 21: Threshold Voltage of a-Si:H TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30      |

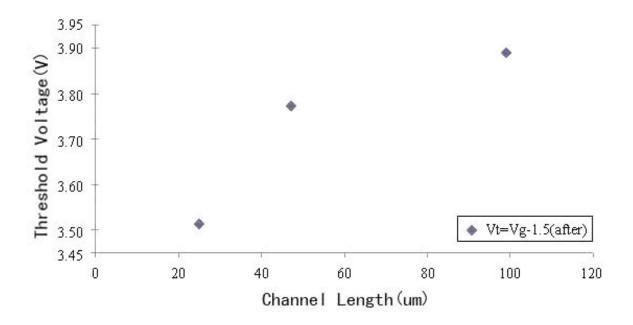

| Figure 22: Threshold Voltage of nc-Si TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31      |

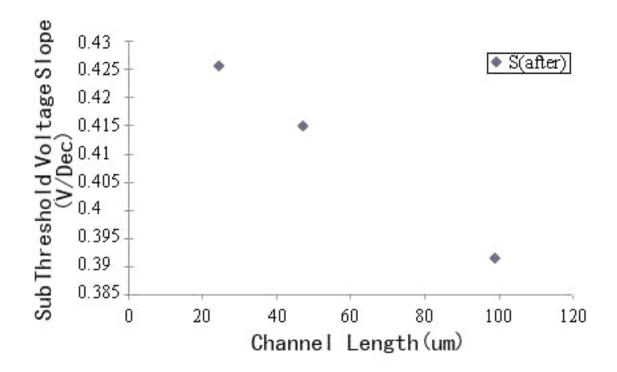

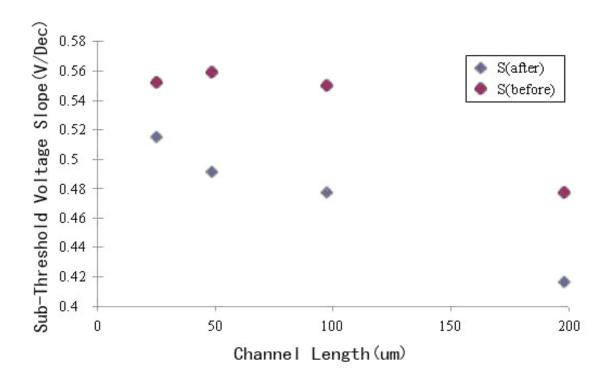

| Figure 23: Sub-Threshold Slope of a-Si:H TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32      |

| Figure 24: Sub-Threshold Slope of nc-Si TFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33      |

| Figure 25: nc-Si Vs a-Si:H Dark Current (Id)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 34      |

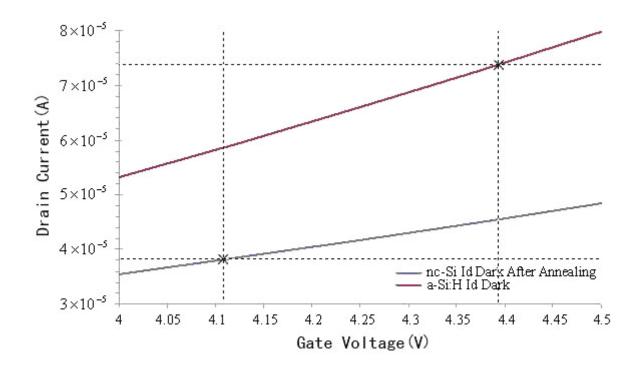

| Figure 26: Drain current dependence on Vg of nc-Si and a-Si:H devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36      |

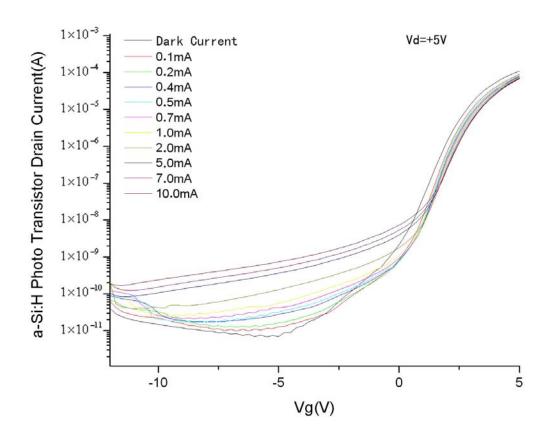

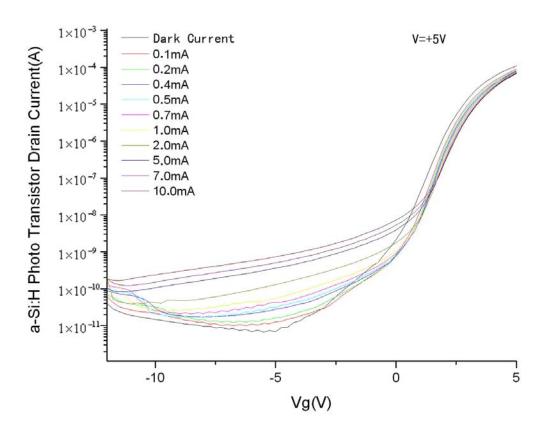

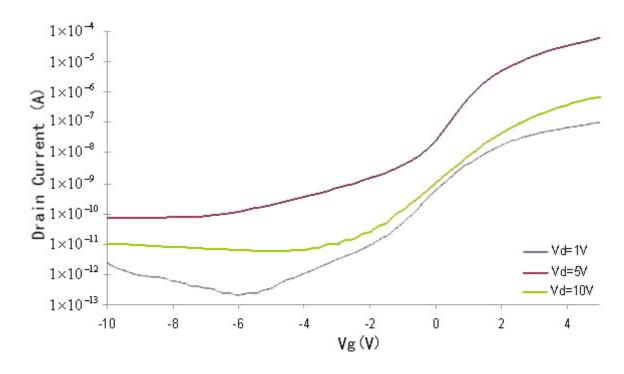

| Figure 27: a-Si:H TFT Transfer Characteristic under various illumination intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37      |

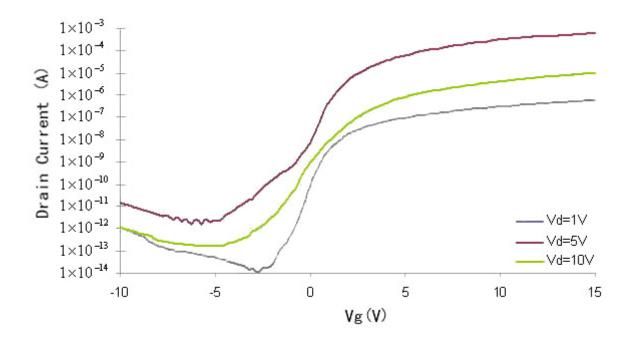

| Figure 28: nc-Si TFT Transfer Characteristic under various illumination intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38      |

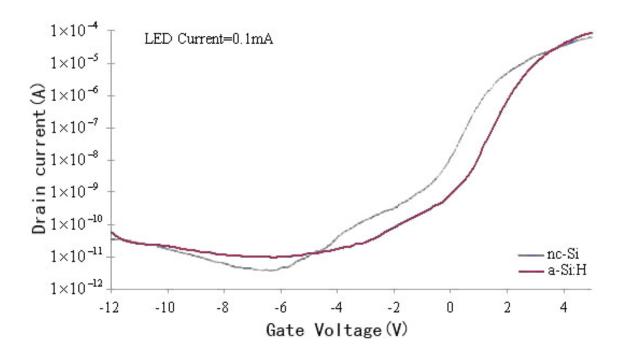

| Figure 29: nc-Si Vs a-Si:H Id photo current at the LED current =0.1mA                          | 39 |

|------------------------------------------------------------------------------------------------|----|

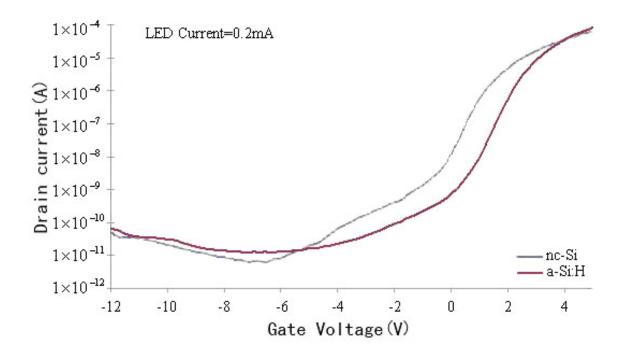

| Figure 30: nc-Si Vs a-Si:H Id photo current at the LED current =0.2mA                          | 40 |

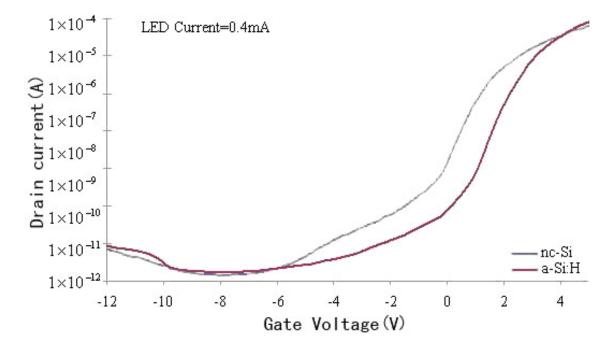

| Figure 31: nc-Si Vs a-Si:H Id photo current at the LED current =0.4mA                          | 40 |

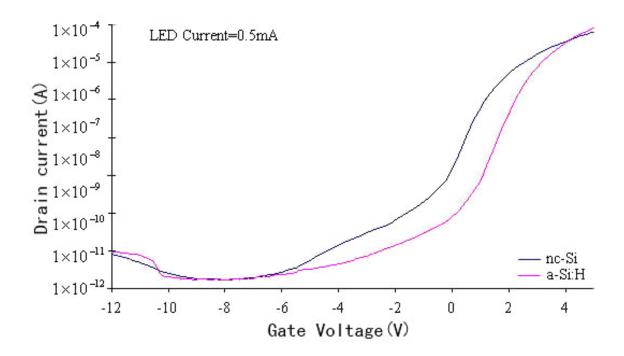

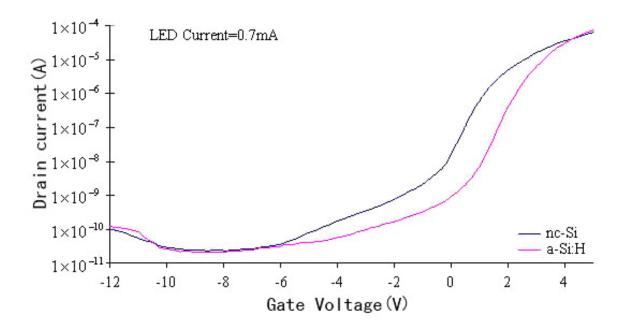

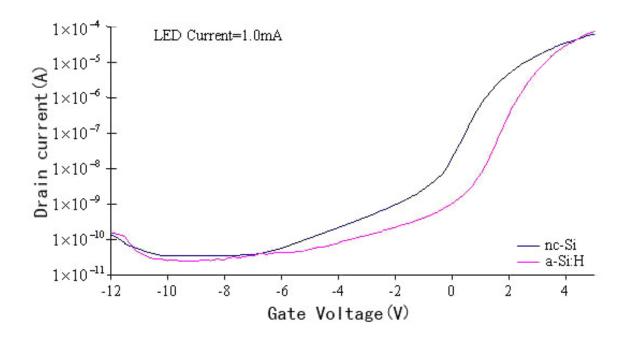

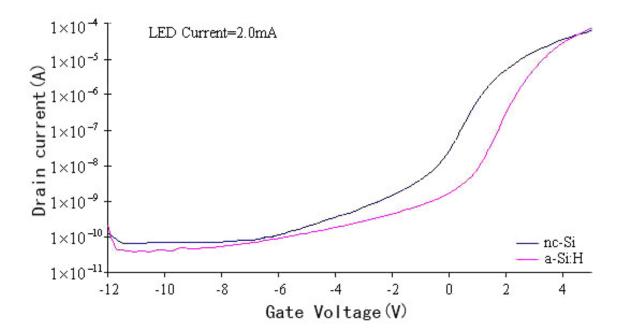

| Figure 32: nc-Si Vs a-Si:H Id photo current at the LED current =0.5mA                          | 41 |

| Figure 33: nc-Si Vs a-Si:H Id photo current at the LED current =0.7mA                          | 41 |

| Figure 34: nc-Si Vs a-Si:H Id photo current at the LED current =1.0mA                          | 42 |

| Figure 35: nc-Si Vs a-Si:H Id photo current at the LED current =2.0mA                          | 42 |

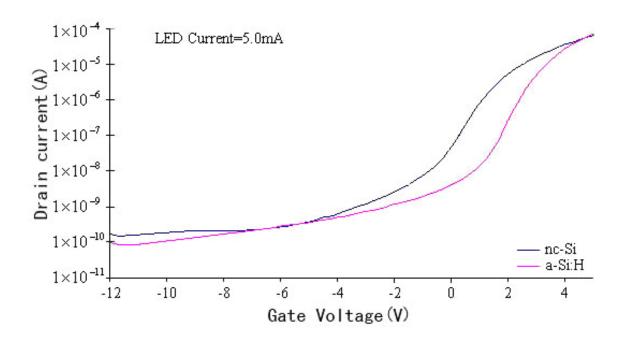

| Figure 36: nc-Si Vs a-Si:H Id photo current at the LED current =5.0mA                          | 43 |

| Figure 37: nc-Si Vs a-Si:H Id photo current at the LED current =7.0mA                          | 43 |

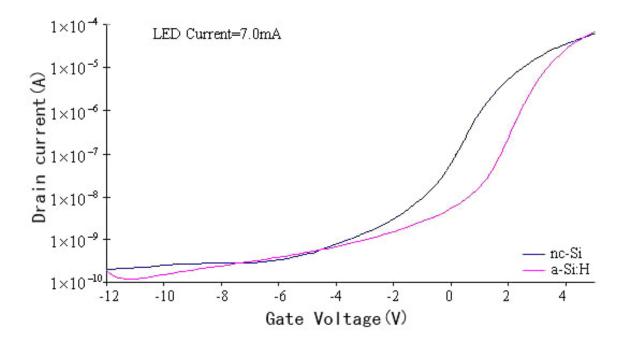

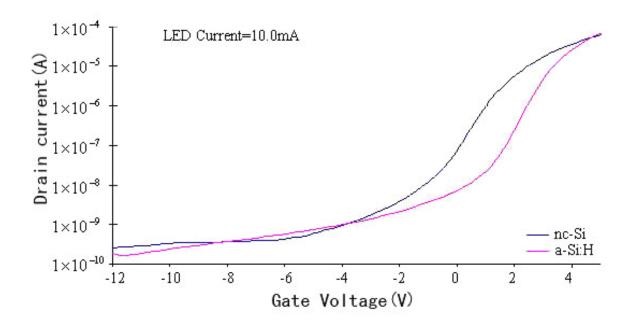

| Figure 38: nc-Si Vs a-Si:H Id photo current at the LED current =10.0mA                         | 44 |

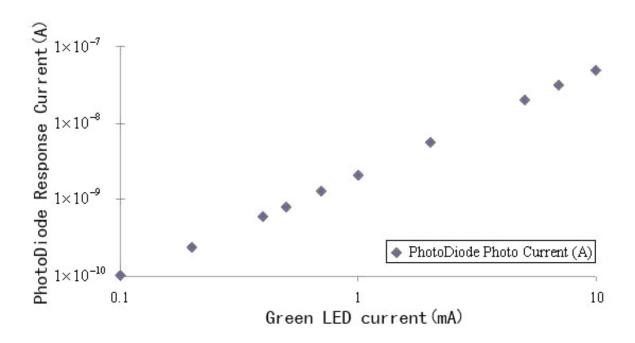

| Figure 39: PhotoDiode photo current Vs Green LED current                                       | 46 |

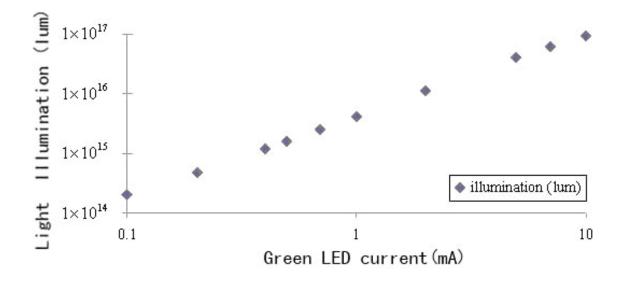

| Figure 40: Light Illumination Vs Green LED current                                             | 46 |

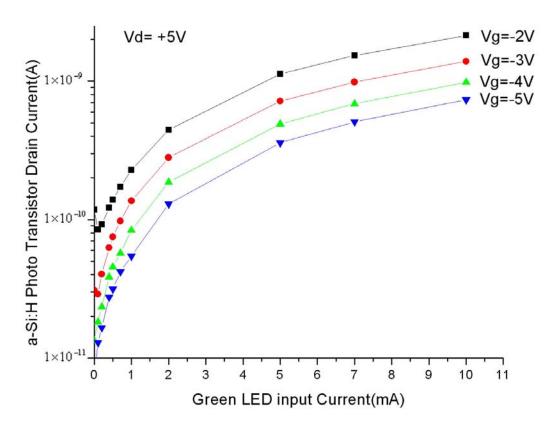

| Figure 41: a-Si:H Photo Transistor Drain Current at Different Vgs                              | 47 |

| Figure 42: nc-Si Photo Transistor Drain Current at Different Vgs                               | 48 |

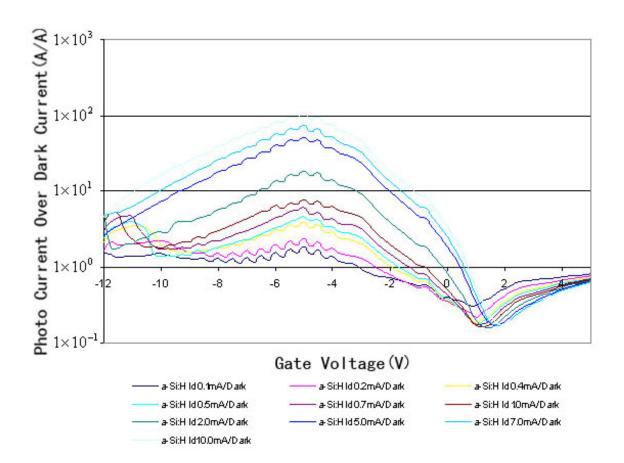

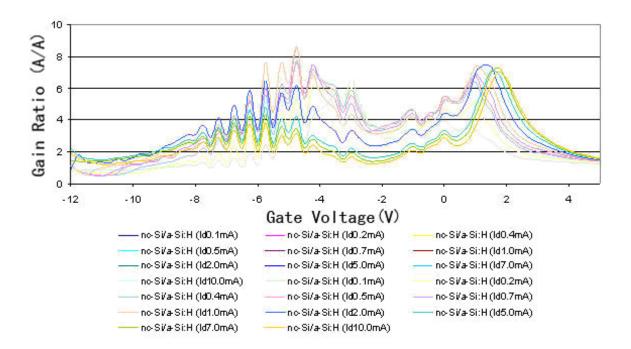

| Figure 43: The a-Si:H Photo Current Gain.                                                      | 49 |

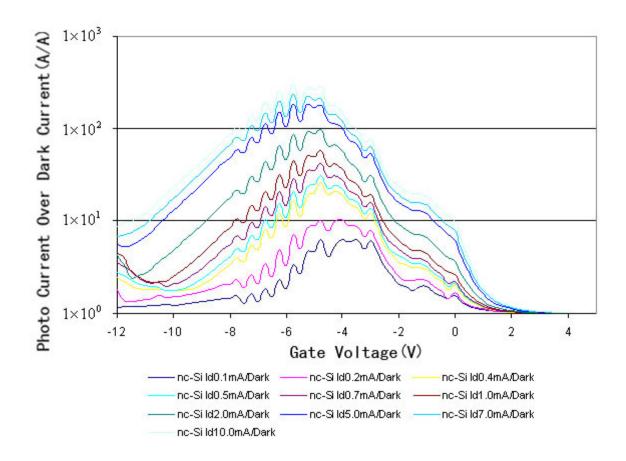

| Figure 44: The nc-Si TFT Photo Current Gain.                                                   | 50 |

| Figure 45: the ratio of the nc-Si device current gain over the a-Si:H device current gain      | 51 |

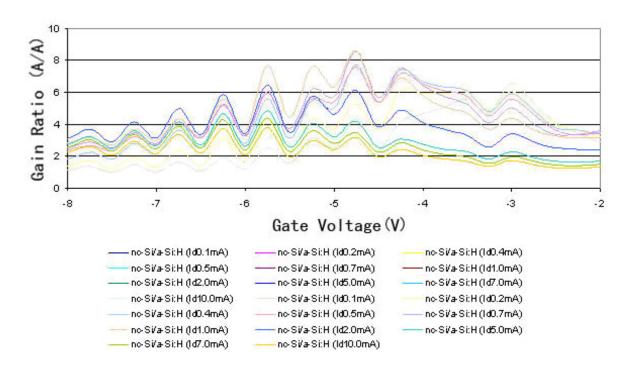

| Figure 46: ratio of the nc-Si device current gain over the a-Si:H device current gain(Zoom in) | 52 |

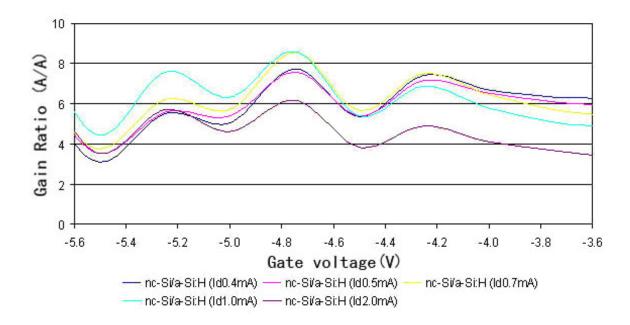

| Figure 47: ratio of the nc-Si device current gain over the a-Si:H device current gain(Zoom in) | 52 |

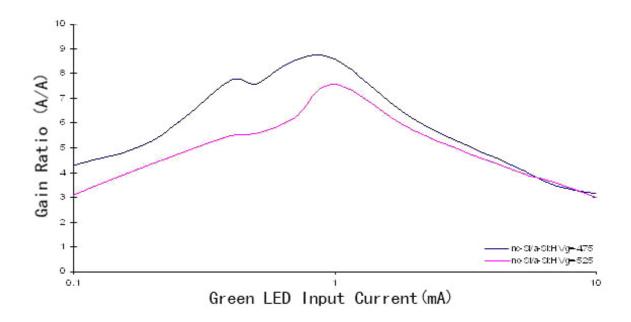

| Figure 48: Photo Current Gain Ratio (nc-Si/a-Si:H) when Vg=-4.75V and Vg=-5.25V                | 53 |

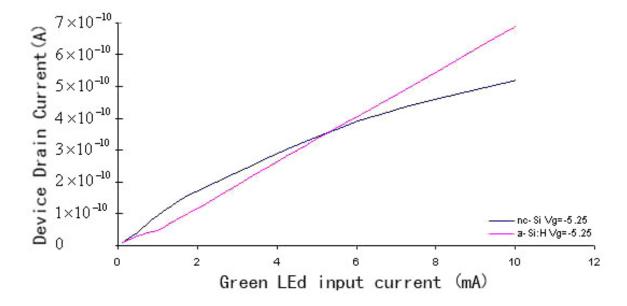

| Figure 49: Comparison of the nc-Si TFT and the a-Si:H TFT drain current when Vg=-5.25V         | 53 |

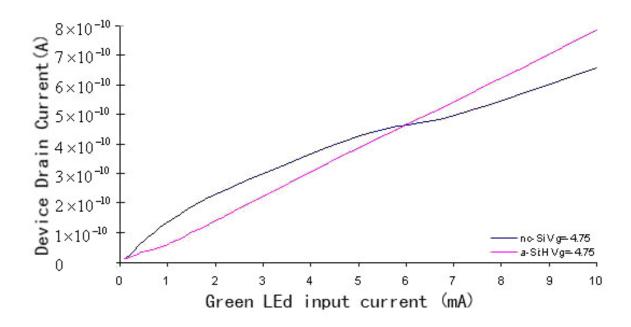

| Figure 50: Comparison of the nc-Si TFT and the a-Si:H TFT drain current when Vg=-4.75V         | 54 |

| Figure 51: nc-Si TFT Dark Current with Different Vds.                                          | 55 |

| Figure 52: nc-Si TFT Current under Illumination with Different Vds                             | 56 |

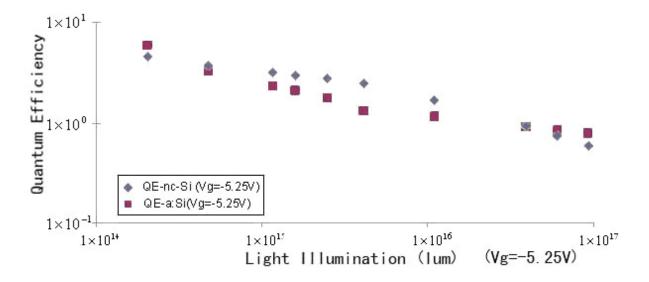

| Figure 53: Light Illumination Vs Quantum Efficiency when Vg=-5.25V                             | 57 |

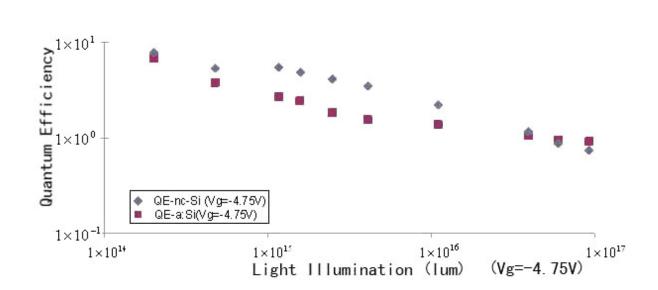

| Figure 54: Light Illumination Vs Quantum Efficiency when Vg=-4.75V                             | 58 |

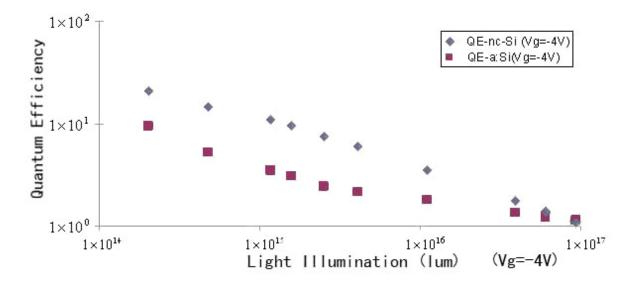

| Figure 55: Light Illumination Vs Quantum Efficiency when Vg=-4V                                | 58 |

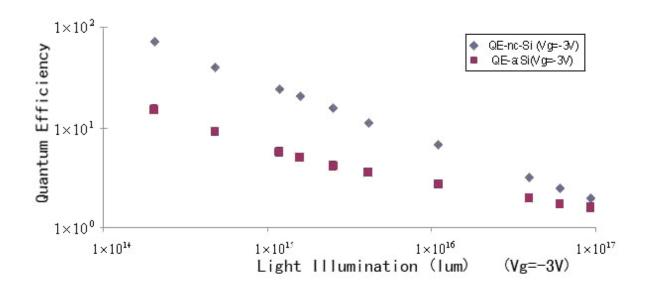

| Figure 56: Light Illumination Vs Quantum Efficiency when Vg=-3V                                | 59 |

| Figure 57: Light Illumination Vs Quantum Efficiency when Vg=-2V                                | 59 |

| Figure 58: Light Illumination Vs Quantum Efficiency when Vg=-1V                                | 60 |

| Figure 59: Light Illumination Vs Quantum Efficiency when Vg=0V                                 | 60 |

| Figure 60: Light Illumination Vs Quantum Efficiency when Vg=+1V                                | 61 |

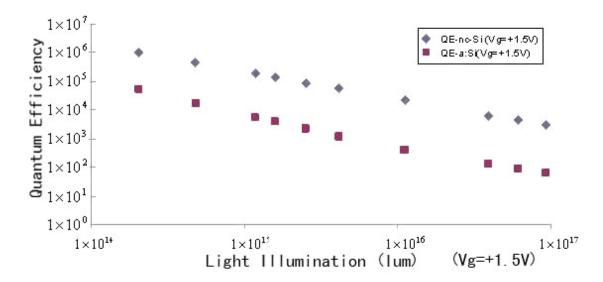

| Figure 61: Light Illumination Vs Quantum Efficiency when Vg=+1.5V                    | 61 |

|--------------------------------------------------------------------------------------|----|

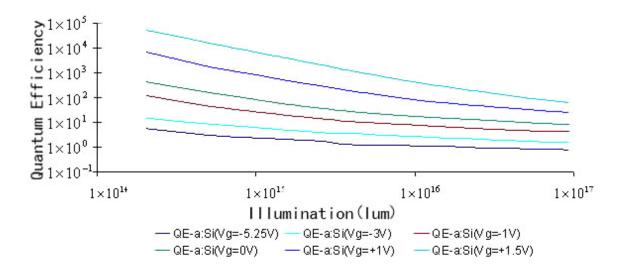

| Figure 62: a-Si:H Quantum Efficiency with different gate voltages                    | 62 |

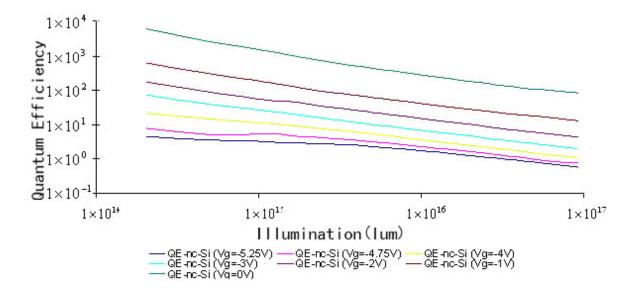

| Figure 63: nc-Si Quantum Efficiency with different gate voltages                     | 63 |

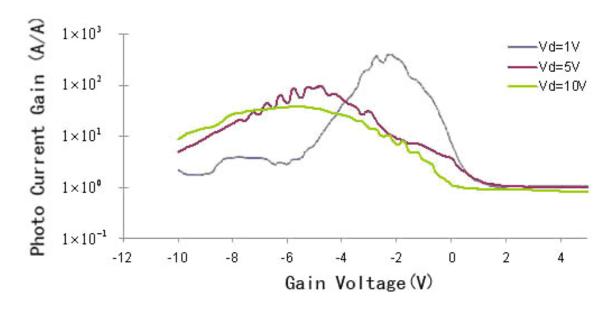

| Figure 64: nc-Si Gain Vs Vds                                                         | 63 |

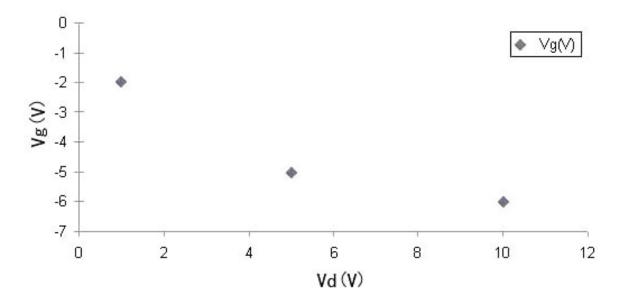

| Figure 65: Vd Vs Vg at nc-Si Device Maximum Photo Current Gain                       | 63 |

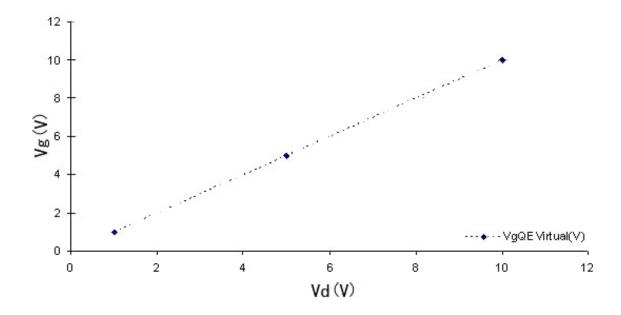

| Figure 66:The relation between Vd and Vg at QE(A/A)=constant                         | 64 |

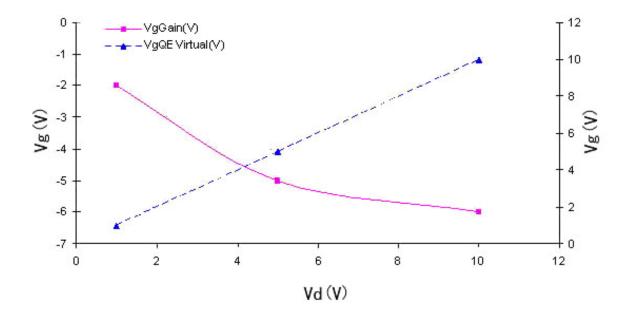

| Figure 67:Estimation Vds effect of Maximum Photo Current Gain and Quantum Efficiency | 65 |

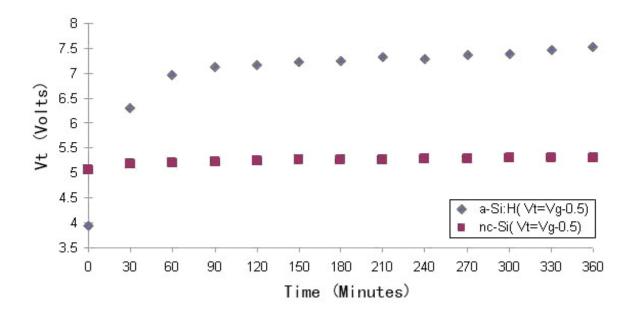

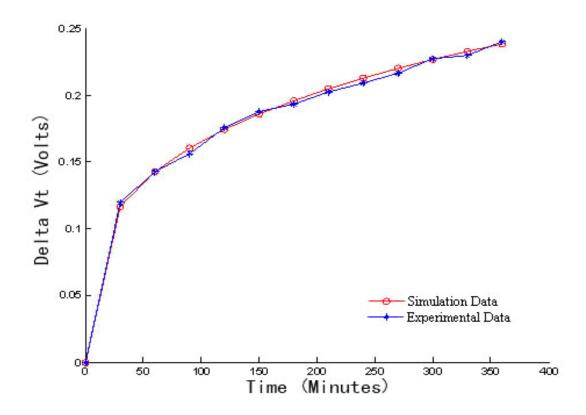

| Figure 68: Threshold voltage shift of nc-Si TFT and a-Si:H TFT                       | 66 |

| Figure 69: Threshold voltage shift of nc-Si TFT Data                                 | 67 |

#### **Chapter 1**

#### Introduction

#### 1.1 Application Areas for Phototransistor Array

Large area thin film phototransistor arrays have been developed since the 1990s, for such applications as flat-bed (line) scanners or large area imagers. A flat-bed scanner can scan a two-dimensional image by carrying out line scanning (Y direction) with a line sensor (such as a CCD line sensor), having pixels aligned in a linear pattern (X direction). However, the scanning speed is limited by the mechanical components for scanning a two-dimensional image, which makes it hard to reduce the scanner thickness and weight. Therefore, in order to reduce the scanner thickness and weight, and increase it's scanning speed, a matrix-type twodimensional image sensor is an option. A two-dimensional photosensor is also suited as the data reader of a personal computer, word processor, or work station. This two-dimensional photosensor array requirements are a large area, a high sensitivity, and a rapid-response. Most of these requirements can be fulfilled by use of amorphous silicon (a-Si:H) and its alloys used in large-area applications such as backplane electronics for photodectors [1-4]. The high photoconductivity and fairly low cost of a large-area deposition setup have made the hydrogenated a-Si:H an attractive materials in large area photodetector research and industry [5, 6].

#### 1.2 Problems for Thin Film Imaging Pixels

A typical photo imaging pixel (The Active Pixel Sensor(APS)) consists of a photodiode and several transistors. In thin film electronics, p-i-n photodiodes are used as sensing elements, and thin film transistors as switching elements, hence the process to fabricate this type of pixel will require two-process sequences: the transistors will be fabricated first followed by the photodiode fabrication. Therefore, the cost of the process for a photo pixel array is much higher than the cost of the process of a TFT array. Moreover, most foundries are built to manufacture TFT backplanes for the flat panel displays (where only n+ doped films are used for TFT source/drain contacts) and simply do not have p+ layer deposition capabilities essential for thin film p-i-n photodiode fabrication. Furthermore, the photosensitivity of a photodiode is hard to adjust just electrically by adjusting its operation point- a device layout change or fabrication process has to be adjusted for that. To reduce the process cost and simplify photosensitivity control, thin film phototransistor can be used as a photo-sensor that can be fabricated within the same process sequence as switching TFTs. However, the low field effect mobility (0.1-1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) and the low stability of the amorphous phototransistor have prevented the applications from being used in industry[7]. Hence the quest for the large area thin film phototransistors, which have higher mobility and stability.

#### 1.3 Nanocrystalline silicon thin film phototransistor

In order to compensate for low field effect mobility and get sufficient drain current, the typical solution would be increasing the ratio of TFT Width to Length(W/L) ratio. With the fixed length, the width will increase, which means the TFT footprint will increase. The

mobility of an amorphous TFT is 0.1-1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>[7]; whereas the mobility of a nanocrystalline TFT is 0.5 -3 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>[8, 9] and has potential to be further improved [8, 9]. Furthermore, the use of nanocrystalline silicon as TFT active layer reduces threshold voltage shift, hence increasing TFT stability[10] compared to a-si:H counterpart. Therefore, the use of nc-Si active layer leads to smaller footprint and stable photo-TFTs.

#### 1.4 Goal of the Research