# Bluenose II: Towards Faster Design and Verification of Pipelined Circuits

by

#### Ca Bol Chan

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2008

© Ca Bol Chan 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The huge demand for electronic devices has driven semiconductor companies to create better products in terms of area, speed, power *etc.* and to deliver them to market faster. Delay to market can result in lost opportunities. The length of the design cycle directly affects the time to market. However, inadequate time for design and verification can cause bugs that will cause further delays to market and correcting the error after manufacturing is very expensive. A bug in an ASIC found after fabrication requires respinning the mask at a cost of several million dollars. Even as the pressure to reduce the length of the design cycles grows, the size and complexity of digital hardware circuits have increased, which puts even greater pressure on design and verification productivity. Pipelining is one optimization technique which has contributed to the increased complexity in hardware design. Pipeline increases throughput by overlapping the execution of instructions. It is a challenge to design and verify pipelines because the specification is written to describe how instructions are executed in sequence while there can be multiple instructions being executed in a pipeline at one time. The overlapping of instructions adds further complexity to the hardware in the form of hazards which arise from resource conflicts, data dependencies or speculation of parcels due to branch instructions.

To address these issues, we present *PipeNet*, a metamodel for describing hardware design at a higher level of abstraction and Bluenose II, a graphical tool for manipulating a *PipeNet* model. *PipeNet* is based on a pipeline model in a formal pipeline verification framework. The pipeline model contains arbiters, flow-control state machines, datapath and data-routing. The designer describes the pipeline design using *PipeNet*. Based on the *PipeNet* model, Bluenose II generates synthesizable VHDL code and a HOL verification script. Bluenose II's ability to generate HOL scripts turns the HOL theorem prover into Bluenose II's external verification environment. A direct connection to HOL is implemented in the form of a console to display results from HOL directly in Bluenose II. The data structures that represent *PipeNet* are evaluated for their extensibility to accommodate future changes. Finally, a case study based on an implementation of a two-wide superscalar 32-bit RISC integer pipeline is conducted to examine the quality of the generated codes and the entire design process in Bluenose II. The generation of VHDL code is improved over that provided in Bluenose I, Bluenose II's predecessor.

#### Acknowledgements

A heartfelt thanks to Professor Mark Aagaard who not only gave me the opportunity to experience firsthand what research is all about but also the opportunity to work with a great supervisor. He is always full of encouragement (when I did not do a good job), patience (when I did not know how to do the job), and motivation (for his students to strive to do the best possible job!)

I would also like to thank Vlad Ciubotariou for helping me out with his Eclipse expertise.

Thanks to all the friends who have helped me along the way. Non-technical help is equally important in the completion of this thesis.

I thank my parents and my brother for their unconditional love and support which have allowed me to reach this point in my life.

To my mom, dad and brother

# Contents

| $\mathbf{Li}$ | List of Tables ix |                                      |           |  |  |  |

|---------------|-------------------|--------------------------------------|-----------|--|--|--|

| $\mathbf{Li}$ | st of             | Figures                              | x         |  |  |  |

| 1             | Intr              | roduction                            | 1         |  |  |  |

|               | 1.1               | Overview of Pipelines                | 2         |  |  |  |

|               | 1.2               | Research Overview                    | 3         |  |  |  |

|               | 1.3               | Thesis Statement and Contributions   | 4         |  |  |  |

|               | 1.4               | Thesis Outline                       | 4         |  |  |  |

| <b>2</b>      | Bac               | kground                              | 6         |  |  |  |

|               | 2.1               | A Pipeline Model                     | 6         |  |  |  |

|               | 2.2               | Model Driven Development             | 10        |  |  |  |

|               | 2.3               | Eclipse Graphical Modeling Framework | 11        |  |  |  |

|               | 2.4               | The HOL Theorem Prover               | 14        |  |  |  |

|               | 2.5               | Bluenose I                           | 15        |  |  |  |

|               | 2.6               | Related Work                         | 16        |  |  |  |

|               | 2.7               | Summary                              | 20        |  |  |  |

| 3             | Pip               | eline Design with Bluenose II        | <b>21</b> |  |  |  |

|               | 3.1               | Overview                             | 21        |  |  |  |

|               | 3.2               | PipeNet                              | 22        |  |  |  |

|               | 3.3               | Design Flow in Bluenose II           | 26        |  |  |  |

|               | 3.4               | User Interface                       | 27        |  |  |  |

|               |                   | 3.4.1 Reducing Clutter               | 28        |  |  |  |

|               |                   | 3.4.2 Changes from Bluenose I        | 29        |  |  |  |

|              | 3.5                 | VHDL PipeLib                                                                                                  |    |  |  |

|--------------|---------------------|---------------------------------------------------------------------------------------------------------------|----|--|--|

|              |                     | 3.5.1 Changes from Bluenose I                                                                                 |    |  |  |

|              | 3.6 VHDL Generation |                                                                                                               |    |  |  |

|              |                     | 3.6.1 Conversion Function Templates                                                                           | 38 |  |  |

|              |                     | 3.6.2 Changes from Bluenose I                                                                                 | 40 |  |  |

|              | 3.7                 | Summary                                                                                                       | 43 |  |  |

| 4            | Pip                 | eline Verification with Bluenose II                                                                           | 44 |  |  |

|              | 4.1                 | HOL PipeLib                                                                                                   | 45 |  |  |

|              | 4.2                 | HOL Generation                                                                                                | 48 |  |  |

|              | 4.3                 | HOL Console                                                                                                   | 53 |  |  |

|              | 4.4                 | Summary                                                                                                       | 54 |  |  |

| <b>5</b>     | Blu                 | enose II Core                                                                                                 | 55 |  |  |

|              | 5.1                 | Data Structures                                                                                               | 55 |  |  |

|              |                     | 5.1.1 Block                                                                                                   | 56 |  |  |

|              |                     | 5.1.2 Connection                                                                                              | 56 |  |  |

|              | 5.2                 | Implementation                                                                                                | 59 |  |  |

|              |                     | 5.2.1 Java Generation                                                                                         | 60 |  |  |

|              |                     | 5.2.2 Customization $\ldots$ | 61 |  |  |

|              | 5.3                 | Summary                                                                                                       | 63 |  |  |

| 6            | $\mathbf{Cas}$      | e Study                                                                                                       | 64 |  |  |

|              | 6.1                 | The OpenRISC Design                                                                                           | 64 |  |  |

|              | 6.2                 | Observations                                                                                                  | 69 |  |  |

|              | 6.3                 | Performance Comparison                                                                                        | 70 |  |  |

|              |                     | 6.3.1 Speed and Area                                                                                          | 70 |  |  |

|              |                     | $6.3.2  \text{Code Quality}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                 | 71 |  |  |

|              | 6.4                 | Summary                                                                                                       | 74 |  |  |

| 7            | Cor                 | nclusions and Future Work                                                                                     | 76 |  |  |

|              | 7.1                 | Conclusions                                                                                                   | 76 |  |  |

|              | 7.2                 | Future Work                                                                                                   | 77 |  |  |

| $\mathbf{A}$ | ppen                | dix                                                                                                           | 80 |  |  |

| A DiffAdd Code Generated by Bluenose I      | 80 |

|---------------------------------------------|----|

| B Reference Model Testbench                 | 82 |

| C Generated HOL Script Based on OR1200-BNv3 | 84 |

| Glossary of Terms                           | 87 |

| References                                  | 88 |

# List of Tables

| 2.1 | Pipe stage components                                                                          | 8  |

|-----|------------------------------------------------------------------------------------------------|----|

| 2.2 | Description of instantiations of Arbiter                                                       | 8  |

| 2.3 | Description of instantiations of $MkR/A$                                                       | 9  |

| 3.1 | Description of main modules in Bluenose II                                                     | 23 |

| 3.2 | Lines of code for the DiffAdd project                                                          | 43 |

| 5.1 | Attributes of the $Block$ class $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 59 |

| 5.2 | Attributes of the <i>Connection</i> class                                                      | 59 |

| 6.1 | Stage instantiation parameters for OR1200-BNv3                                                 | 67 |

| 6.2 | Performance Comparison                                                                         | 71 |

| 6.3 | Lines of code for the OpenRISC project                                                         | 74 |

# List of Figures

| 2.1 | Aagaard's pipeline stage decomposition                                               | 7  |

|-----|--------------------------------------------------------------------------------------|----|

| 2.2 | Overview of the Graphical Modeling Framework                                         | 12 |

| 2.3 | Basic steps for developing a graphical editor with the Graphical Modeling Framework  | 13 |

| 2.4 | Relationship between (meta)models                                                    | 13 |

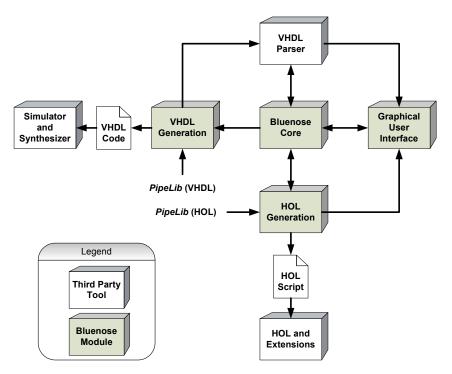

| 3.1 | The main modules of Bluenose II                                                      | 23 |

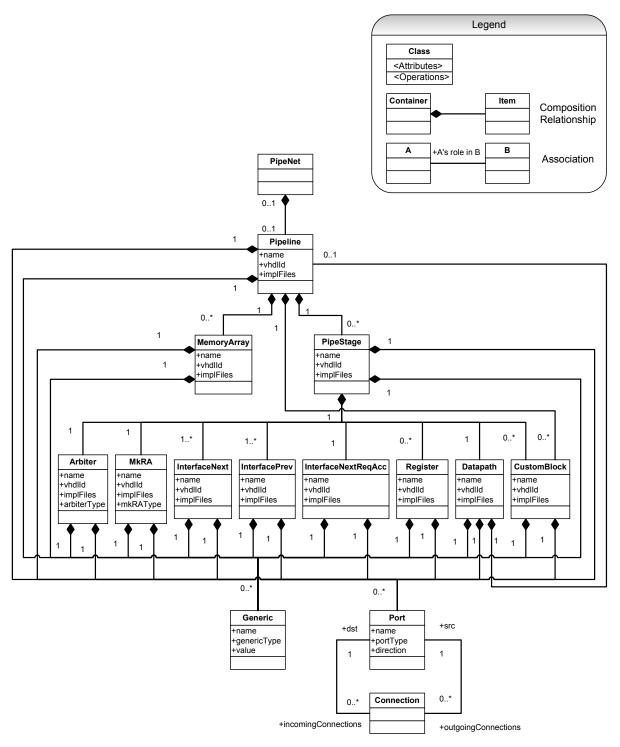

| 3.2 | PipeNet                                                                              | 24 |

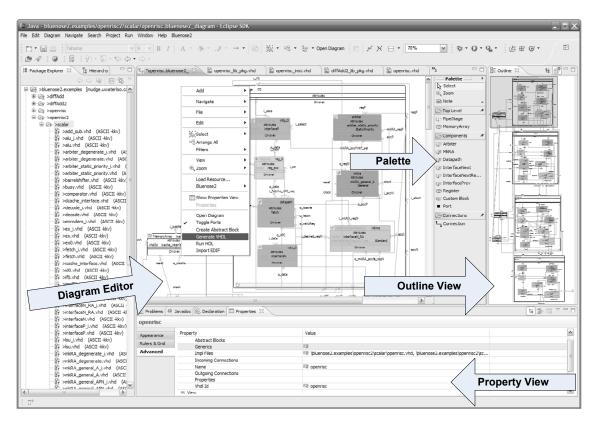

| 3.3 | Bluenose II screenshot with labels                                                   | 27 |

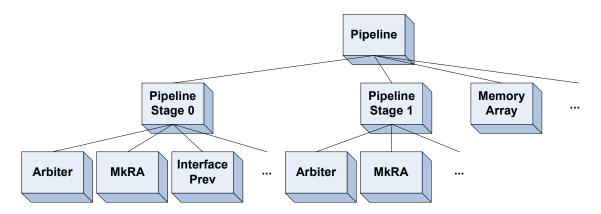

| 3.4 | A tree view of a Bluenose II pipeline model                                          | 37 |

| 3.5 | Conversion functions for a stage                                                     | 39 |

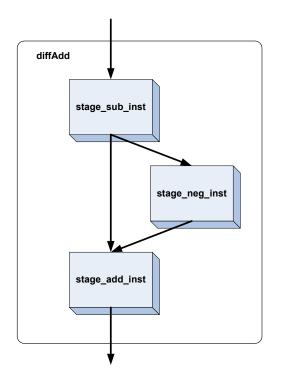

| 3.6 | The diffAdd entity                                                                   | 41 |

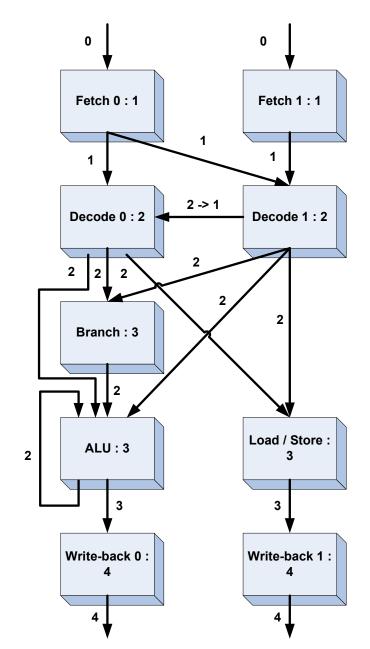

| 4.1 | Two-issue superscalar pipeline with numbers denoting stage order<br>and signal types | 52 |

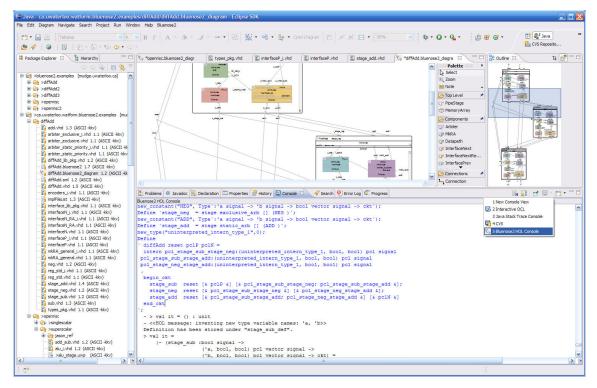

| 4.2 | Bluenose II with HOL console                                                         | 53 |

| 4.3 | HOL console                                                                          | 54 |

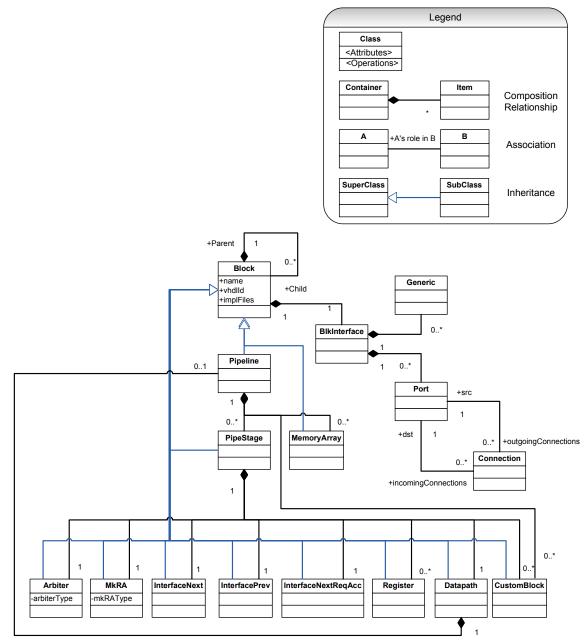

| 5.1 | Simplified class diagram for the pipeline metamodel                                  | 57 |

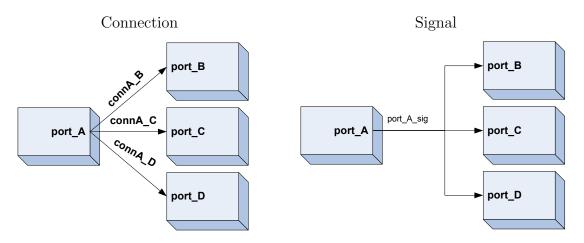

| 5.2 | Comparison between connection and signal                                             | 58 |

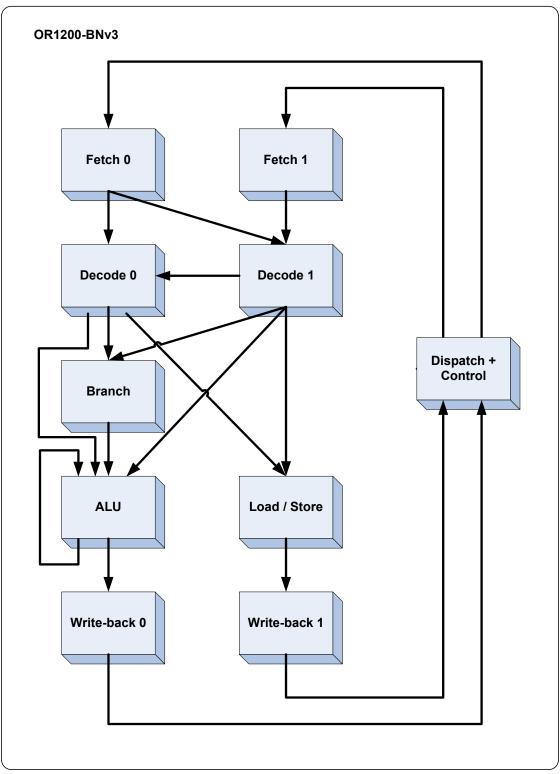

| 6.1 | OR1200-BNv3                                                                          | 66 |

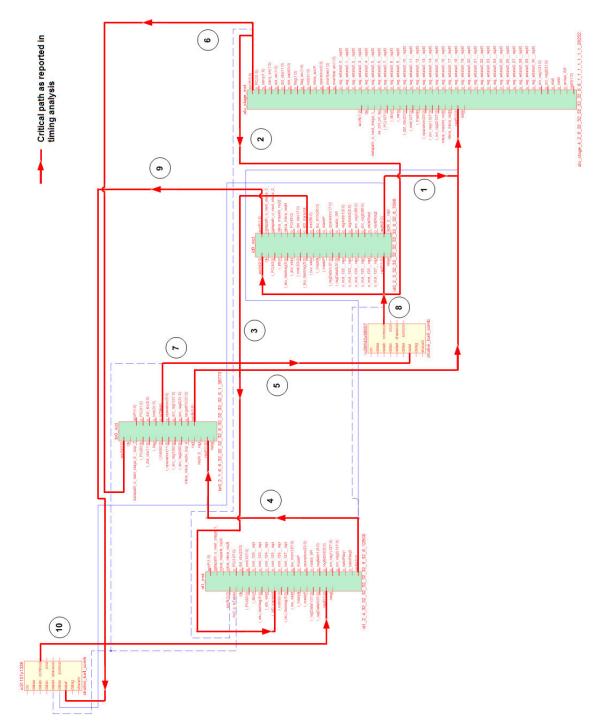

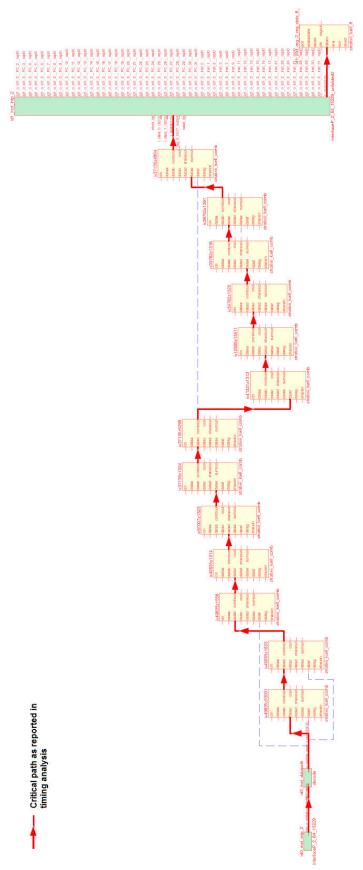

| 6.2 | Critical path of OR1200-BNv2                                                         | 72 |

| 6.3 | Critical path of OR1200-BNv3                                                         | 73 |

## Chapter 1

## Introduction

Without looking at the statistics, it is not hard to tell that the use of electronic devices has greatly increased. Headlines such as "Worldwide PC processor market hits record levels of unit shipments again" [1], "Cell phone sales hit 1 billion mark" [2] and "1 million iPhone 3Gs sold in 3 days" [3] are not uncommon these days. The huge consumer appetite for electronic devices was made more evident when an article described them as physical nourishment to college students [4]. Semiconductor companies are competing to fulfill this increasing demand by creating better products in terms of area, speed, power *etc.* and delivering them to the market faster.

Delay to market can result in lost opportunities. The length of the design cycle directly affects the time to market. However, inadequate time for design and verification can cause bugs that will cause further delays to market and correcting the error after manufacturing is very expensive. A bug in an ASIC found after fabrication requires respinning the mask at a cost of several million dollars. Even as the pressure to reduce the length of the design cycles grows, the size and complexity of digital hardware circuits have increased, which puts even greater pressure on design and verification productivity.

Driven by the demand for better (smaller, faster *etc.*) products, highly advanced architectural ideas are developed which result in more complex designs. An example is pipelining which increases the throughput at the price of increased design and verification complexity. In the last 15 years, designs have grown in size and complexity by 1 to 2 orders of magnitude. Many hardware intellectual property (IP) blocks today are larger than an entire chip back then [5]. Engineers were reported working on multiple projects at once although the average size of a design team has grown [6]. An engineer can write only so many lines of code a day; therefore, in the face of increasing size and complexity in hardware design, each line has to be worth "more" than before. More "value" can be added to the code in several ways. One way is to raise the level of abstraction so a line in a high-level hardware description language can be synthesized into more lines of code at the register transfer level (RTL). Another way is to incorporate verification into the design process to achieve "first-time-right" functional correctness in a shorter time. Such are the motivations for the Bluenose II project. Bluenose II aims to increase designer productivity and reduce verification effort by raising design abstraction, focusing on pipelined circuits in particular.

With these goals in mind, we take a more detailed look at pipelines and explain why it is a challenge to design and verify them. Following that, we present the research overview, thesis statement and research contributions. The chapter is ended with an outline of the major sections in this thesis.

#### **1.1** Overview of Pipelines

Pipelining is an optimization technique in hardware design that overlaps the execution of instructions. A hardware pipeline can be viewed as an assembly line for instructions. Each pipeline stage processes an instruction and passes the instruction to the next stage. This process occurs in all pipeline stages simultaneously, thus allowing multiple instructions to be processed concurrently. An advantage of a pipelined design is the increase of throughput since each instruction gets processed sooner compared to a non-pipelined design in which each instruction has to wait for the previous one to finish. However, the overlapping of instructions adds complexity to the hardware in the form of hazards. Three types of hazards are present in pipelined designs. Structural hazards arise from resource conflicts among overlapped execution of instructions. Data hazards are caused by data dependencies between overlapping instructions. Finally, control hazards deal with speculation of parcels due to branch instructions. These concepts are explained in depth by Hennessy and Patterson in [7]. Many design complexities arise from trying to resolve these hazards properly. And to verify that these complex pipelined designs are correct further adds to the overall challenge.

Even without these complexities, a pipelined implementation by itself is hard to verify formally. The challenge stems from the fact that the specification is written to describe how instructions are executed in sequence while there can be multiple instructions being executed in a pipeline at one time. Many techniques have been developed to verify a pipelined implementation against its non pipelined specification. A well-known correctness statement known as Burch-Dill flushing was proposed in [8]. For small scale designs, *e.g.*, in-order pipelines with a small depth, Burch-Dill flushing can be fully automated. For realistic designs like Intel's Core microarchitecture which has 14 stages with out-of-order execution [9], Burch-Dill flushing suffers from the state explosion problem as do other model checking techniques. Many other formal verification techniques have been developed since then and applied in the industry. Although companies reported that formal verification has led to the discovery of subtle design bugs [10], it is still not widely adopted since formal verification requires specialized expertise which most designers do not have. In view of these challenges, Aagaard developed a pipeline verification framework which structures and simplifies the proof of the pipelining circuitry for structural hazards [11]. The framework provides a stage template which consists of a set of components and techniques for how to verify these components. By mapping a pipeline design into these components, the verification is in effect divided into smaller tasks. It was recognized that in addition to easing the verification effort, a designer can also use these components to design a pipeline. From this realization, Higgins created Bluenose I [12]. Bluenose I demonstrated that the stage template from Aagaard's verification framework could be applied to pipeline design [12]. It showed that the stage template used in combination with a graphical user interface simplified the design and verification of pipelines. Building on the work of Bluenose I, Bluenose II is created, which is the topic of this thesis.

#### 1.2 Research Overview

Bluenose II continues in the direction taken by its predecessor to increase automation in pipeline design and verification. One particular area that we explore in this thesis is the model driven development methodology. We examine the applicability of the methodology not only to the development of Bluenose II but also to the pipeline design process. For this, we created a pipeline metamodel called *PipeNet* based on Aagaard's stage template. A metamodel is literally a model that describes another model. Since a model represents concepts from a domain, the metamodel for that model provides a modeling language for that domain. Consequently, a metamodel can also be considered a domain specific language [13].

We use Eclipse and its modeling plugins to build Bluenose II based on *PipeNet*. Bluenose II can be viewed as a domain specific tool for instantiating and configuring the *PipeNet* metamodel. In turn, the designer creates a pipeline model using the *PipeNet* "language". The *PipeNet* language should be expressive enough to capture all the relevant characteristics of a pipeline design. The effectiveness can be evaluated by the ease to generate codes. If the metamodel is not expressive enough, it will be difficult to retrieve or derive information needed for code generation. Bluenose II generates synthesizable VHDL code and a HOL verification script based on the pipeline model entered by the designer. The data structures that represent *PipeNet* are then evaluated for their extensibility to accommodate future changes. Finally, a case study based on the OpenRISC architecture [14, 15] is conducted to examine the quality of the generated codes and the entire design process in Bluenose II. Ultimately, Bluenose II should pave the road to faster design and verification of pipelined circuit that was started in Bluenose I.

#### **1.3** Thesis Statement and Contributions

In this thesis, we propose that not only can model driven development be applied to the development of a tool for pipeline design, it can also be applied to the pipeline design process. The pipeline metamodel, which forms the basis of Bluenose II, can capture all the relevant characteristics of a pipeline design. This is demonstrated through the ease to generate codes from the pipeline model instantiated from the metamodel. Harnessing the power of Eclipse's modeling framework and its code generation facility, Bluenose II is a full featured environment for pipeline design and verification. Altogether, Bluenose II improves upon the work started by Bluenose I and paves the road to faster design and verification of pipelined circuits.

This work makes the following contributions to the area of hardware design and verification.

- We create *PipeNet*, a pipeline metamodel, which is suitable for capturing pipeline designs.

- Extensible data structures that implement *PipeNet* are developed.

- We develop Bluenose II which implements the *PipeNet* data structures in Eclipse with full-featured user interface. Bluenose II is developed using the model driven engineering approach. We show how a designer can apply the same approach to pipeline design using Bluenose II.

- The generation of VHDL code is improved over that provided in Bluenose I in terms of conciseness.

- We enhance the Bluenose tool with the HOL generation feature for verification. A direct connection from Eclipse to HOL in the form of a console in Eclipse is implemented. The HOL console displays HOL's output directly in Bluenose II.

#### 1.4 Thesis Outline

The remainder of the thesis is organized as follows.

- Chapter 2 introduces the pipeline model and provides details on the technologies used in Bluenose II. Related work is also described in this chapter.

- Chapter 3 outlines the design flow in Bluenose II and the implementation of design related features.

- Chapter 4 describes HOL related modules which are used in pipeline verification.

- Chapter 5 presents the data structures and discusses some implementation issues that arose in the development of Bluenose II.

- Chapter 6 provides the results of a case study based on an implementation of a two-wide superscalar 32-bit RISC integer pipeline in Bluenose II.

- Chapter 7 contains the conclusions of the thesis and directions for future work.

# Chapter 2

## Background

In the previous chapter, we discussed the challenges in the design and verification of pipelined circuits; we also gave an overview of Bluenose II, a design and verification tool for the pipelines. This chapter gives the background that will help in understanding the inner working and philosophy of Bluenose II.

The pipeline model which Bluenose II is based on is presented in Section 2.1. The model driven development approach that we took to develop Bluenose II is discussed in Section 2.2. The Eclipse Graphical Modeling Framework and the HOL theorem proving system, which were used in the development of Bluenose II, are described in Section 2.3 and Section 2.4 respectively. Bluenose I, the predecessor to Bluenose II, is discussed in Section 2.5. Finally, we relate and contrast our work to others in Section 2.6.

#### 2.1 A Pipeline Model

Aagaard's solution (modified by Higgins in [12]) to the design complexity is to view a pipeline as a system of stages that follows a request/accept protocol [11]. Instructions are treated as parcels and are transfered from one stage to the next based on this protocol. In order for a pipeline stage to send a parcel, it first sends a request to the next stage. The stage will only send the parcel upon the receipt of an accept signal from the next stage. The receiving stage sends an accept signal when it has received a request and when it is ready to accept a parcel. Aagaard defined a variety of instantiations of this request/accept protocol that allows for efficient implementations in many pipelines.

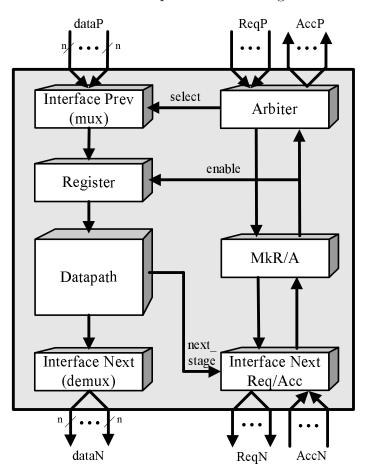

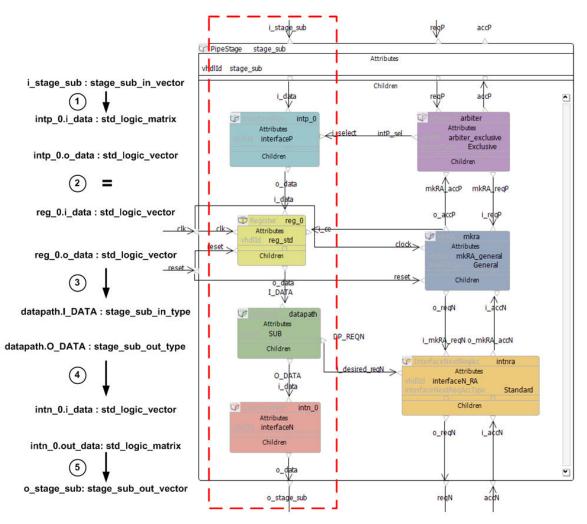

The decision to request or accept is decentralized and distributed to the stages themselves. The transferring of parcels and the decision-making are coordinated by the components inside each stage. These components are shown in Figure 2.1. Table 2.1 describes the role and the number of instances allowed in a stage for each component. The first group of components (*Interface Prev* and *Interface Next*) make up the interface of the stage for transferring parcels. One instance of Interface Prev (Interface Next) is needed per incoming (outgoing) signal to (from) a stage. The second group of components (*Register* and *Datapath*) form the datapath of the stage. One instance of *Register* is required per incoming signal that needs to be registered, while the datapath of a stage is encapsulated in one *Datapath*. The components in the third group together act as the control center for the stage. Since each stage needs only one "control center", only one instance of each component in this group is allowed. The interface and datapath components are placed on the left of Figure 2.1 and the control components on the right.

Figure 2.1: Aagaard's pipeline stage decomposition

There are different instantiations for Arbiter and MkR/A that a designer can choose from. The set of instantiations allows a designer to design pipelines with different behaviours. The choice for Arbiter depends on the number of upstream pipeline stages that are connected to the stage containing the Arbiter and the expected request behaviour. The choice for MkR/A is based on the behaviour of the Datapath of the containing stage, and the request and accept behavoiurs of the upstream and downstream stages respectively. Descriptions of each instantiation of Arbiter and MkR/A are given in Table 2.2 and Table 2.3.

Higgins provided mathematical descriptions of the instantiations in [12]. The definition of *General MkR/A* is reproduced in Definition 2.1 as an example. All

| Component                         | Description                                                             | Cardinality |

|-----------------------------------|-------------------------------------------------------------------------|-------------|

| Interface Prev                    | Receives datapath values from the neigh-                                | 1 to many   |

| Interface Next                    | boring stages<br>Sends datapath values from the neighbor-<br>ing stages | 1 to many   |

| Register                          | Pipe stage register                                                     | 0 to many   |

| Datapath                          | Pipe stage datapath                                                     | 1           |

| Arbiter                           | Arbitrates requests from the upstream                                   | 1           |

| MkRA                              | pipe stages<br>Keeps track of the state of the pipeline<br>stage        | 1           |

| Interface Next Re-                | Interface Next Re- Monitors the request and accept signals              |             |

| q/Acc from downstream pipe stages |                                                                         |             |

Table 2.1: Pipe stage components

| Degenerate :     | There is only one input, so forwards the request directly.      |

|------------------|-----------------------------------------------------------------|

| Exclusive :      | There is more than one input, but there will be at most one     |

|                  | request at any time.                                            |

| StaticPriority : | There is more than one input and there may be more than         |

|                  | one request at a time. The request with the highest priority is |

|                  | forwarded.                                                      |

input and output signals are prefixed with  $i_{-}$  and  $o_{-}$ ; the rest are internal signals. The signals in parentheses are logical groupings of the input and output signals according to their usage. They also represent the interface of *General MkR/A*. The description is quantified over time and the time is indicated with the subscripts. The " $\wedge$ " and " $\vee$ " operators represent the logical AND and OR of two signals respectively. The conjunction of the signal assignments is indicated by the "&" symbol. Together these signal assignments make up the definition of *General MkR/A*.

#### **Definition 2.1:** General MkR/A

$$\begin{split} mkReqAccGeneral(i\_reqP, o\_accP)(o\_reqN, i\_accN) \\ (i\_maskP, i\_maskN, i\_abort, i\_loopMstrReq) \equiv \\ \exists \ reqP, accN, reqN, accP \ . \ \forall \ t \ . \\ reqP_{(t)} &= i\_reqP_{(t)} \land i\_maskP_{(t)} \& \\ accN_{(t)} &= (i\_accN_{(t)} \lor i\_loopMstrReq_{(t)}) \land i\_maskN_{(t)} \& \\ reqN_{(t+1)} &= [reqP_{(t)} \lor (reqN_{(t)} \land \neg accN_{(t)} \land \neg i\_abort_{(t)})] \land \neg i\_reset_{(t)} \& \\ accP_{(t)} &= accN_{(t)} \lor \neg reqN_{(t)} \lor i\_abort_{(t)} \& \\ o\_reqN_{(t)} &= reqN_{(t)} \land i\_maskN_{(t)} \land i\_abort_{(t)} \& \\ o\_accP_{(t)} &= accP_{(t)} \land i\_maskP_{(t)} \end{split}$$

| Degenerate :This instantiation of $MkR/A$ assumes that there is a request<br>from the previous stage in every clock cycle and the next stage<br>always accepts. In other words, the Degenerate $MkR/A$ sends<br>an accept signal to the previous stage and a request to the next<br>stage in every clock cycle.General :There is a unit delay through the current stage. There may or<br>may not be a new request from a previous stage and the next<br>stage may or may not accept.MultiDelay :The current stage may take multiple cycles to process a parcel.<br>There may or may not be a new request from a previous stage<br>and the next stage may or may not accept.UnitDelay :There is a unit delay through the current stage. There may or<br>may not be a new request from a previous stage<br>and the next stage may or may not accept.UnitDelay :There is a unit delay through the current stage. There may or<br>may not be a new request from a previous stage and the next<br>stage always accepts.ZeroDelay :There is a unit delay through the current stage. This instantiation<br>of $MkR/A$ merely connects the request (accept) signal from (to)<br>the previous stage to (from) the next stage. |              | Table 2.3: Description of instantiations of $MkR/A$               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------|

| <ul> <li>always accepts. In other words, the Degenerate MkR/A sends an accept signal to the previous stage and a request to the next stage in every clock cycle.</li> <li>General : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel. There may or may not be a new request from a previous stage and the next stage and the next stage may or may not be a new request from a previous stage and the next stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of MkR/A merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                          | Degenerate : | This instantiation of $MkR/A$ assumes that there is a request     |

| <ul> <li>an accept signal to the previous stage and a request to the next stage in every clock cycle.</li> <li>General : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel. There may or may not be a new request from a previous stage and the next stage may or may not be a new request from a previous stage and the next stage may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                           |              | from the previous stage in every clock cycle and the next stage   |

| <ul> <li>General : Stage in every clock cycle.</li> <li>General : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                    |              | always accepts. In other words, the Degenerate $MkR/A$ sends      |

| <ul> <li>General : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              | an accept signal to the previous stage and a request to the next  |

| <ul> <li>may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel. There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of MkR/A merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              | stage in every clock cycle.                                       |

| <ul> <li>stage may or may not accept.</li> <li>MultiDelay : The current stage may take multiple cycles to process a parcel.<br/>There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | General :    | There is a unit delay through the current stage. There may or     |

| <ul> <li>MultiDelay : The current stage may take multiple cycles to process a parcel.<br/>There may or may not be a new request from a previous stage<br/>and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or<br/>may not be a new request from a previous stage and the next<br/>stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation<br/>of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | may not be a new request from a previous stage and the next       |

| <ul> <li>There may or may not be a new request from a previous stage and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | stage may or may not accept.                                      |

| <ul> <li>and the next stage may or may not accept.</li> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of <i>MkR/A</i> merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MultiDelay : | The current stage may take multiple cycles to process a parcel.   |

| <ul> <li>UnitDelay : There is a unit delay through the current stage. There may or may not be a new request from a previous stage and the next stage always accepts.</li> <li>ZeroDelay : There is zero delay through the current stage. This instantiation of MkR/A merely connects the request (accept) signal from (to)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              | There may or may not be a new request from a previous stage       |

| may not be a new request from a previous stage and the next<br>stage always accepts.ZeroDelay :There is zero delay through the current stage. This instantiation<br>of $MkR/A$ merely connects the request (accept) signal from (to)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |              | and the next stage may or may not accept.                         |

| ZeroDelay :Stage always accepts.ZeroDelay :There is zero delay through the current stage. This instantiation<br>of $MkR/A$ merely connects the request (accept) signal from (to)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | UnitDelay :  | There is a unit delay through the current stage. There may or     |

| ZeroDelay : There is zero delay through the current stage. This instantiation of $MkR/A$ merely connects the request (accept) signal from (to)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              | may not be a new request from a previous stage and the next       |

| of $MkR/A$ merely connects the request (accept) signal from (to)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              | stage always accepts.                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ZeroDelay :  | There is zero delay through the current stage. This instantiation |

| the previous stage to (from) the next stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              | of $MkR/A$ merely connects the request (accept) signal from (to)  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | the previous stage to (from) the next stage.                      |

The request/accept protocol, components and their instantiations are derived from Aagaard's pipeline verification framework for structural hazards [11]. In Aagaard's framework, the instantiations of the components characterize the pipelining circuitry that is to be verified. The framework provides a verification strategy based on these components. Therefore, mapping the pipeline design into these components eases the task of verification.

The request/accept protocol, components and their instantiations together form a template of a pipeline stage. The designer instantiates and configures the template for each stage in the pipeline to describe the overall structure and behaviour of the pipeline. The benefits of using this stage template are as follows:

- 1. The behaviours of these components are in terms familiar to pipeline designers therefore the learning curve is less daunting.

- 2. The components encapsulate and abstract away the low level mechanisms used in hardware to stall stages and to route parcels from one stage to the next.

- 3. The encapsulation of details also means that the structure of the pipeline is available at the same time as the designer completes the design of the behaviour of the pipeline.

- 4. The components which implement the request/accept protocol allow the designer to create pipelines that handle structural hazards correctly.

5. The mapping between the pipeline model and Aagaard's verification framework allows the designer to design for verification.

This conceptual model is the foundation of Bluenose II. From it, a metamodel which we named *PipeNet*, is created to be used in Bluenose II. Using Bluenose II, the designer describes the pipeline design in *PipeNet* and the pipeline model created from *PipeNet* allows the design to be reasoned about. *PipeNet* is described further in Section 3.2. The model leads us to take advantage of the model driven development approach. Model driven development and metamodels are explained in Section 2.2.

#### 2.2 Model Driven Development

There are different standards and methodologies for model driven development (MDD) [16, 17]. Each has its own terminology but in generic terms, model driven development is an approach to develop software or any other system by using a model or models which abstract some concepts of the problem domain. We focus our discussion of model driven development to the scope of Model Driven Architecture (MDA), a framework proposed by the Object Management Group (OMG) [17].

MDA supports model driven development by providing standards to define and transform models. An application is first specified using one or more Platform Independent Models (PIM). As its name implies, the model is independent from platform details such as a programming language. The model's independence allows it to be transformed into different Platform Specific Models (PSM). It may take multiple transformations to map a high level model to executable code for a given platform [13]. Therefore, the role of a model, whether it is a PIM or a PSM, is relative to the other models. For example, a C++ program is a PSM to the Unified Modeling Language (UML) model that it implements, but it is a PIM to the corresponding assembly code which is executed on specific processors. Model, be it PIM or PSM, is specified with the modeling constructs defined in its metamodel. A model is an instantiation of its metamodel. A metamodel is just like any other model that abstracts the concepts in a domain, except the domain of a metamodel is another model. Therefore, the concept of a metamodel is also relative to the model that it is being related to. A model can be a metamodel to another model, while it itself conforms to another metamodel. This "chain" of models is also referred to as meta-layers or metalevels [18]. In the previous example of UML, C++ and the assembly language, there are three layers. Since a model represents the concepts from a domain, the metamodel for that model provides a modeling language for that domain. In this way, a metamodel can also be considered a domain specific language (DSL).

A DSL provides the syntax to express ideas in a particular domain. A DSL offers the following benefits:

- The specialized notation provides domain specific abstraction. The layer of abstraction provides the ability to capture an idea in the domain more concisely.

- A DSL allows its user to identify and communicate ideas that are too abstract to express in a general purpose programming language.

- The domain information captured by the language coupled with domain knowledge enables domain specific error checking and optimization. This leads to the creation of domain intelligence tools that provide support to facilitate domain specific activities.

To illustrate the benefits of a DSL, consider the example of a database query language which is a DSL for a structured collection of data. A *table* in the database query language is known to refer to a set of data that is organized in rows and columns. The database query languages also provide the syntaxes to describe operations on a *database* such as creating and removing a *table*. Domain abstractions such as rows, columns, and table creation make up a language for describing the organization and manipulation of data. A DSL is not confined to text and to be standalone; it can also be visual or embedded in another programming language [13].

In MDA, models or metamodels have to be expressed in a Meta-Object Facility (MOF) based language [17]. MOF is an OMG standard for defining modeling languages. A benefit of expressing a model in a MOF-based modeling language is that the model can be transformed and manipulated by MOF-compliant tools [18]. The Eclipse Modeling Framework (EMF), part of the Eclipse Graphical Modeling Framework (GMF) that we used to develop Bluenose II, is compatible with a subset of the MOF metamodel called the Essential Meta-Object Facility (EMOF) metamodel. EMF can be thought of as a EMOF tool for defining metamodels. It has the generative functionality to produce a set of Java classes for the metamodel based on its specification. To distinguish from the EMOF metamodel, the core metamodel in EMF is called Ecore [19]. EMF is discussed further in Section 2.3.

We adopted the model driven development approach to harness the generative functionality of EMF and GMF. The generative functionality of these Eclipse plugins allows us to focus on implementing features for manipulating the pipeline model instead of basic editor functionalities like file management. GMF is discussed in Section 2.3.

#### 2.3 Eclipse Graphical Modeling Framework

Eclipse is an open source integrated development environment. It was originally created by IBM and has evolved into a platform supported by an open source community [20]. Eclipse can be customized and extended through plug-ins. Bluenose II

runs on the Eclipse platform as a plug-in. Bluenose II was implemented also using other Eclipse plug-ins; an important one is GMF.

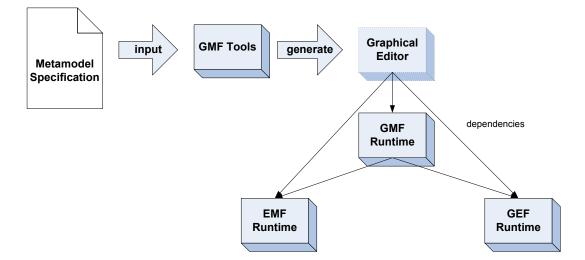

GMF is a model driven tool set for developing graphical editors. It includes a generative component for generating the graphical editor and a runtime infrastructure which provides services to the graphical editor during runtime [21]. GMF is based on two other plug-ins: EMF and the Eclipse Graphical Editing Framework (GEF). GMF integrates the modeling functionalities of EMF into the model-viewcontroller architecture of GEF. The model-view-controller architecture is a design pattern that decouples the model from the view so that more than one view can be implemented to display the data of the model. An overview of GMF is shown in Figure 2.2.

Figure 2.2: Overview of the Graphical Modeling Framework

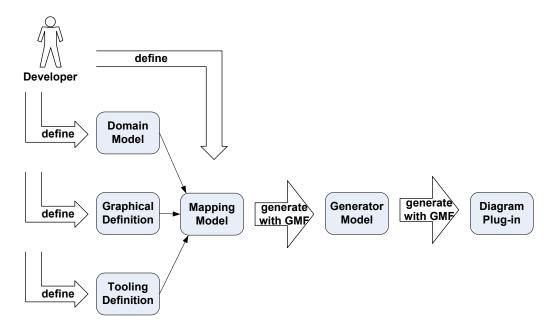

The basic steps for developing a graphical editor with GMF are illustrated in Figure 2.3. The developer first develops the domain model, graphical definitions and tooling definitions. The domain model defines the abstract syntax of the modeling language that will be available in the graphical editor. It is expressed using the Ecore metamodel. The graphical definitions describe the graphical elements (e.g.,figures and connectors) that will appear in the editor. The tooling definitions specify tools (e.q., palette and toolbars) that will be available in the editor. These models are fit together in the mapping model such that the graphical elements are linked to the concrete aspect of the domain model and tools in the editor. The mapping model is transformed into a generator model which contains modifiable code generation parameters (e.q., plug-in name). Finally, the diagram code (Java code) for the editor plug-in is generated from the generator model. The generated plug-in reuses components from the GMF runtime infrastructure and runs on the Eclipse platform. The editor persists the data which represent the models created by the end user, in XML Metadata Interchange (XMI), a standard also defined by OMG [21].

Figure 2.3: Basic steps for developing a graphical editor with the Graphical Modeling Framework

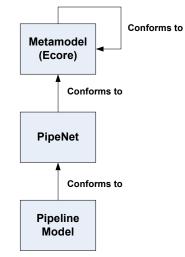

We are involved in the model driven development field both as a modeler and a model user. We used the Ecore metamodel to specify *PipeNet*, a pipeline metamodel. In turn, the pipeline designer uses *PipeNet* to describe the pipeline design. The relationship between these models is shown in Figure 2.4. We used GMF to develop Bluenose II, a graphical editor to manipulate the pipeline model. GMF's generative functionality and the reusability of its runtime components allow us to derive the benefit of adopting the model driven development approach.

Figure 2.4: Relationship between (meta)models

#### 2.4 The HOL Theorem Prover

Formal verification involves proving that the implementation satisfies the specification using mathematical reasoning. One formal verification approach is logic inference. The specification, implementation and their relation are expressed in some type of logic. The verification then becomes proving a theorem in that specific logic [22]. Theorem provers are used to keep track of this type of proofs. Other benefits of the theorem prover are explained as part of the description of HOL. Bluenose II generates a HOL script to enable the verification of pipeline designs.

The HOL system is a theorem prover for the theory that it is named after, higher order logic. In higher order logics, functions can take functions as arguments, and quantifiers can range over functions [23]. Therefore, higher order logic supports modeling a digital system as a relation between its input and output signals and models a signal as a time-to-value function. The signal function, when given a time, returns the state of the signal. With this in mind, HOL was originally created for hardware verification at the register transfer level, modified from the Cambridge LCF (Logic for Computable Functions) system. LCF-style theorem provers have terms from the typed  $\lambda$ -calculus and formulae from predicate calculus [24].

Some benefits of using theorem provers like HOL are that the system keeps track of the proof, ensures the proof's soundness, automates the proof when possible and allows extensibility. In LCF-style theorem provers, a small core of axioms and inference rules are encoded. New theorems can only be constructed by applying a sequence of inference rules on the axioms, thereby ensuring soundness of the proof — if the system proved something is true, then it really is true. Furthermore, since theorems are represented as an abstract data type, strict type checking prevents any violation of the soundness of the system. The HOL system supports both forward and goal oriented proofs. A step in a forward proof can only be derived with the rules of inference from results of other proofs, namely theorems, previous steps in the proof, or axioms. In a goal oriented proof, the proof goal is decomposed into subgoals with tactics or tacticals which are combinations of tactics. A tactic matches a goal or a subgoal with an axiom or a proven theorem. A goal is solved when there are no more subgoals to be proven; the goal itself or all of its subgoals are matched with axioms or theorems. Proven theorems can be stored in theories for future use [23].

The extensibility of HOL is enabled by the separation of the meta language and object language. HOL is written in the programming language ML (Meta Language) which is a functional language, designed by the same creator as the original LCF system. ML is strictly typed to implement type checking. The separation of the meta language (ML) and object language (HOL) allows the logic to be extended. New proof procedures can be developed through ML and theories can be added to HOL. HOL supports the development of application specific tools [23] — in this case, the application specific constructs become the object language and HOL becomes the meta language. There is research to embed hardware description languages into formal logics to give formal semantics to these languages [24]. Lastly, HOL can be extended by dynamic loading and calling of external C functions, a feature provided by ML [25]. This allows HOL to harness the power of other verification tools.

HOL is used in hardware verification to model specifications and implementations. An implementation can then be reasoned about with HOL. For example, an implementation can be proven to conform to a specification, and if the specification can be proven to satisfy a property then we can say the implementation also satisfies the property. To facilitate pipeline verification in HOL, we have established a connection between Bluenose II and the HOL system, and from HOL to other verification tools. Bluenose II generates HOL script based on the pipeline design entered by the user. The user can then reason about the design with HOL and its extensions. In this thesis, we focus on the connection between Bluenose II and HOL because the Bluenose II connections from HOL to external tools are not fully mature.

#### 2.5 Bluenose I

Bluenose I is the predecessor to Bluenose II. Bluenose II builds on the same mathematical model (described in Section 2.1) as Bluenose I. As the main purpose of both tools is to provide a means to manipulate the mathematical model, they have the components that a designer uses to build a pipeline. However, many differences exist between these two tools in how the designer uses and manipulates the components.

The language of implementation is one reason for the differences. Bluenose I was implemented in Moscow ML, which is a functional language [25]. Bluenose II was implemented in Java, which supports the object-oriented paradigm. Another reason for the differences was the different approach to the development of the two tools. The model driven development approach was adopted for the development of Bluenose II as described in Section 2.2. This has led to the definition of a more explicit pipeline model, which is described in Section 3.2. This explicit pipeline model did not exist in Bluenose I.

The verification task is delegated to third party tools in both Bluenose I and Bluenose II. Bluenose I generates queries for Cadence FormalCheck, a commercial model-checking tool. The queries are used to assert certain properties in the pipeline design. On the other hand, Bluenose II generates a HOL script that models the user's pipeline design. The designer can then reason about the pipeline design in HOL. We have chosen to integrate HOL and Bluenose II because HOL offers a general purpose verification environment which can be extended with other verification tools.

Some features in Bluenose I are improved in Bluenose II. More basic editor functionalities such as file management are enabled in Bluenose II due to the Eclipse platform and its plug-ins. The VHDL code generation is also improved in Bluenose II. The differences between Bluenose II and Bluenose I listed in this section are an overview. The specific changes between Bluenose II and Bluenose I are discussed in detail in corresponding sections.

#### 2.6 Related Work

Due to the enormous amount of detail in the register transfer level (RTL) of hardware design, many languages and tools have been created to raise the level of abstraction to different degrees. The abstraction increases the designer's productivity by showing only the details of interest. The abstraction level where system design and verification are carried out is also known as the electronic system level (ESL) [5]. These languages and tools model different aspects of the hardware architecture ranging from the behaviour to the structure. They also represent the models in different ways, from visual to textual. Although they all serve the purpose of capturing certain aspects of the architecture, some are meant only for simulating functionalities, some for design space exploration and some generate RTL that produces hardware with comparable performance as the hand-written RTL. In the latter case, these tools are also called high-level synthesis (HLS) tools. In this section, we discuss a subset of this work most related to Bluenose II and *PipeNet*.

The block based approach taken by Bluenose II is employed by many commercial and academic tools, be they graphical or textual. They include Mentor Graphics' HDL Designer [26], Altera's Quartus II [27] and the X language [28], to name a few. This is not surprising as hardware designers often used blocks as a high level representation to describe and visualize different entities and their relationship to each other. In Bluenose II, the purpose of the blocks is more than just to hide the details, the blocks represent elements in the *PipeNet* model and their identities are used for different types of analysis. In this model driven development aspect, MCF [29] and MMV [30] are very similar to Bluenose II.

The Metamodeling-driven Component Composition Framework (MCF) is developed by Mathailkutty *et al.* to harness the power of a metamodel based framework to create system-level models [29]. In MCF, the user creates a design by instantiating, configuring and connecting components which represent SystemC intellectual property (IP) cores. MCF then checks for inconsistencies in the model and generates the appropriate glue-logic for the components. The Metamodeling Based Microprocessor Validation Environment (MMV) is also developed by Mathailkutty *et al.* [30]. MMV is a validation environment based on metamodeling. In MMV, the user models the design at the system level and continually refines it to a lower abstraction. The user specifies the models in each abstraction level using the respective MMV metamodels. MMV then generates code for specific validation targets based on the translators customized by the user.

A metamodel is characterized by the domain concepts that it can express. The MCF metamodel allows the modeling of system-level components for design space exploration. On the other hand, the MMV metamodel is intended for microprocessor validation and provides specialized elements such as *Pipeline*, *Stages* and instruction registers. While *PipeNet* focuses on the modeling of pipelines, it can also be used to describe system-level components. Furthermore, *PipeNet* is intended to be used in both design and verification. There appears to be no direct mapping between the MCF and MMV metamodels.

Bluenose II, MCF and MMV are similar in a number of ways. The tools promote model driven development. MCF and MMV are both built on a metamodeling framework called the Generic Modeling Environment (GME) [31] which is much like GMF to Bluenose II. GME, like GMF, is a toolkit for creating visual domain specific languages. Instead of Ecore, the metamodel is specified in UML [32]. The component model of GME is built upon Microsoft's technology; therefore, although Java access is available, its primary languages of integration are C++ and Visual Basic. The metamodels in these tools impose structural constraints on the construction of the model. MCF and MMV enforce additional constraints on the static semantics of the model by checking the model against rules specified in the Object Constraint Language (OCL) [33]. As GMF has built-in support for OCL and other validation facilities, our future work includes providing additional validation in Bluenose II to guide the designer in the modeling process.

The differences between Bluenose II, MCF and MMV are as follows. The influence of SystemC can be seen in the metamodel used by MCF. For example, the type *Argument* is used in MCF for representing arguments in a function call at transaction level in SystemC. Although the design of Bluenose II's *PipeNet* is inspired by some constructs in VHDL, we are confident that the concepts in *PipeNet* are universal to hardware design languages. The models specified in *PipeNet* are independent of implementation language. As a result, we can easily implement a generator that walks through the model and outputs a different language. The HOL generator in Bluenose II is an example of one such generator. It is not clear whether MCF can easily be extended to support other languages or not. In this regard, MMV is more similar to Bluenose II, since it stresses a language-independent representation to enable multi-target code generation.

Type mismatch between ports in a connection is handled differently between Bluenose II and MCF. Bluenose II generates a conversion function template for the designer to implement when a type mismatch is encountered. MCF labels any type mismatch as a type conflict that needs to be fixed. Furthermore, MCF only supports a fixed set of C++ and SystemC types and does not support composite and user defined types. On the contrary, composite and user defined types are used extensively in Bluenose II. Type handling in Bluenose II is discussed in detail in Section 3.6.

Besides its use in the specification of other domain specific languages such as the ones used in MCF and MMV, the direct application of UML in ESL design has also been studied by Mueller *et al.* [34]. The UML notation defines a set of diagrams that are used to describe the structure or behaviour of a system [32]. Not all of UML's modeling capabilities are useful in hardware design. Most tools support a subset of UML that is applicable to the respective domains that are being modeled. A tool may further customize UML for its domain through profiling. From the perspective of a metamodel designer, using a DSL design tool such as GMF may be more straightforward than creating UML profiles and defining constraints on them.