# Automatic Parallelization for Graphics Processing Units in JikesRVM

by

Alan Chun-Wai Leung

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Mathematics in

Computer Science

Waterloo, Ontario, Canada, 2008

© Alan Chun-Wai Leung 2008

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Accelerated graphics cards, including specialized high-performance processors called Graphics Processing Units (GPUs), have become ubiquitous in recent years. On the right kinds of problems, GPUs greatly surpass CPUs in terms of raw performance. However, GPUs are currently used only for a narrow class of special-purpose applications; the raw processing power available in a typical desktop PC is unused most of the time.

The goal of this work is to present an extension to JikesRVM that automatically executes suitable code on the GPU instead of the CPU. Both static and dynamic features are used to decide whether it is feasible and beneficial to off-load a piece of code to the GPU. Feasible code is discovered by an implementation of data dependence analysis. A cost model that balances the speedup available from the GPU against the cost of transferring input and output data between main memory and GPU memory has been deployed to determine if a feasible parallelization is indeed beneficial. The cost model is parameterized so that it can be applied to different hardware combinations.

We also present ways to overcome several obstacles to parallelization inherent in the design of the Java bytecode language: unstructured control flow, the lack of multi-dimensional arrays, the precise exception semantics, and the proliferation of indirect references.

#### Acknowledgements

First and foremost I would like to express my gratitude to my supervisor, Ondřej Lhoták, for all his patience, support and guidance. Without him, this work would not be possible.

I would like to thank Rose, Telson, Helen, Joanna, my family and friends who provided love and care before and during my academic studies.

I would also like to thank Ghulam Lashari for his help in the subject of GPU programming and developers of JikesRVM for their research platform as well as friendly assistance on the mailing list.

# Contents

| 1            | Introduction |                               |    |  |  |

|--------------|--------------|-------------------------------|----|--|--|

|              | 1.1          | Motivation                    | 1  |  |  |

|              | 1.2          | Goal                          | 2  |  |  |

|              | 1.3          | Contributions                 | 3  |  |  |

| 2 Background |              |                               |    |  |  |

|              | 2.1          | GPU Overview                  | 5  |  |  |

|              | 2.2          | JikesRVM Overview             | 10 |  |  |

|              | 2.3          | Dependence Overview           | 12 |  |  |

|              | 2.4          | Related Work                  | 18 |  |  |

| 3            | Imp          | blementation 2                | 21 |  |  |

|              | 3.1          | Overview                      | 21 |  |  |

|              | 3.2          | Dependence Analysis           | 23 |  |  |

|              | 3.3          | Algorithm                     | 29 |  |  |

|              |              | 3.3.1 Parallelization         | 29 |  |  |

|              |              | 3.3.2 Vectorization           | 30 |  |  |

|              |              | 3.3.3 GPU Parallelization     | 31 |  |  |

|              |              | 3.3.4 Classification of Loops | 33 |  |  |

|              |              | 3.3.5 Identifying Loop Types  | 34 |  |  |

| Re | References 74          |        |                         |    |  |  |  |

|----|------------------------|--------|-------------------------|----|--|--|--|

| A  | Command Line Options 7 |        |                         |    |  |  |  |

| 5  | Con                    | clusio | ns                      | 71 |  |  |  |

| 4  | Res                    | ults   |                         | 63 |  |  |  |

|    | 3.6                    | Impler | nentation Summary       | 61 |  |  |  |

|    |                        | 3.5.5  | Recovering Control Flow | 58 |  |  |  |

|    |                        | 3.5.4  | Bounds Checks           | 54 |  |  |  |

|    |                        | 3.5.3  | Intra-array Aliasing    | 48 |  |  |  |

|    |                        | 3.5.2  | Inter-array Aliasing    | 47 |  |  |  |

|    |                        | 3.5.1  | Java Arrays             | 44 |  |  |  |

|    | 3.5                    | Java S | pecific Issues          | 44 |  |  |  |

|    | 3.4                    | Multi- | pass Extension          | 40 |  |  |  |

|    |                        | 3.3.6  | Data Transfer           | 37 |  |  |  |

# List of Figures

| 1.1  | GPU performance [38]                                                 | 2  |

|------|----------------------------------------------------------------------|----|

| 2.1  | GPU Pipeline                                                         | 6  |

| 2.2  | Stream Programming Model                                             | 9  |

| 2.3  | Examples of different dependences                                    | 16 |

| 3.1  | Overall Architecture                                                 | 22 |

| 3.2  | Example dependence graph output                                      | 24 |

| 3.3  | Parallelization scenario                                             | 30 |

| 3.4  | Vectorization scenario                                               | 31 |

| 3.5  | GPGPU code pattern                                                   | 32 |

| 3.6  | Sample output of the dependence graph after parallelization $\ldots$ | 37 |

| 3.7  | Plain matrix multiplication on GPU and CPU                           | 38 |

| 3.8  | Estimated cost vs. actual cost of execution                          | 40 |

| 3.9  | Multi-pass loop with redundant copying                               | 43 |

| 3.10 | Multi-pass loop without redundant copying                            | 43 |

| 3.11 | SOR performance                                                      | 44 |

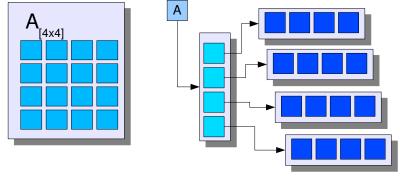

| 3.12 | Array Implementations                                                | 45 |

| 3.13 | AliasOnly edges in dependence graph dump                             | 49 |

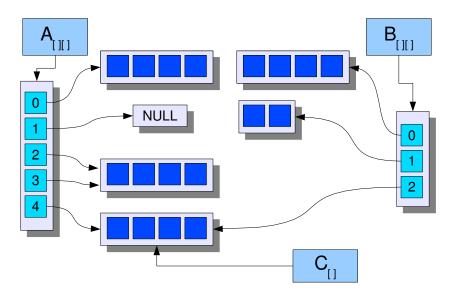

| 3.14 | Irregularities of Java arrays                                        | 49 |

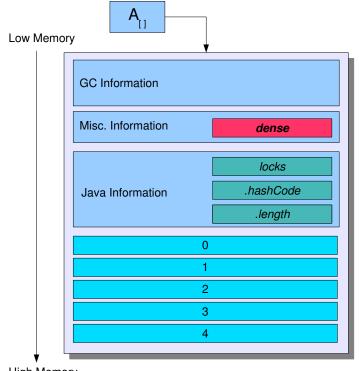

| 3.15 | JikesRVM array layout            | 51 |

|------|----------------------------------|----|

| 3.16 | Simple GOTO control flow         | 59 |

| 3.17 | Sharing of else blocks           | 60 |

| 3.18 | Cloning else blocks              | 61 |

|      |                                  |    |

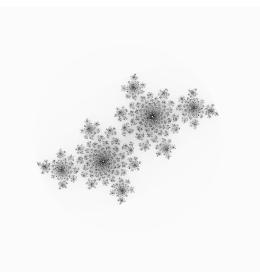

| 4.1  | Image of Julia set by the CPU    | 66 |

| 4.2  | Image of Julia set by the GPU    | 66 |

| 4.3  | Running Time of matrix           | 67 |

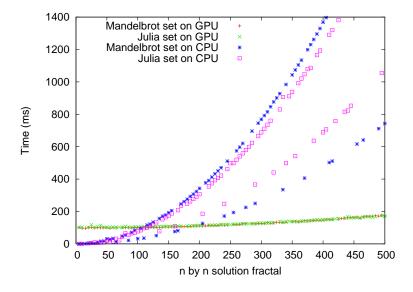

| 4.4  | Running Time of mandel and julia | 68 |

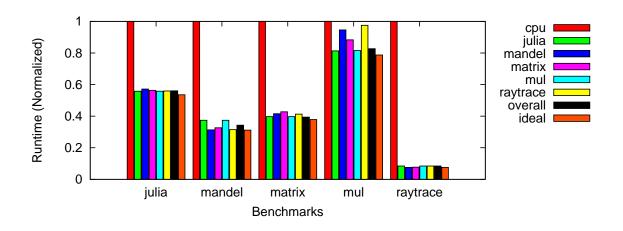

| 4.5  | Execution Time Comparison        | 68 |

| 4.6  | Overall cost model accuracy      | 69 |

## Chapter 1

## Introduction

#### 1.1 Motivation

The graphics card in a typical modern desktop personal computer has significantly more raw processing power and memory bandwidth than the general purpose Central Processing Unit (CPU). In addition to being used for displaying graphics with a monitor, newer generations of these graphics cards are capable of offloading many general-purpose computations from the CPU. For that reason, modern graphics cards are usually referred to as Graphics Processing Units (GPUs).

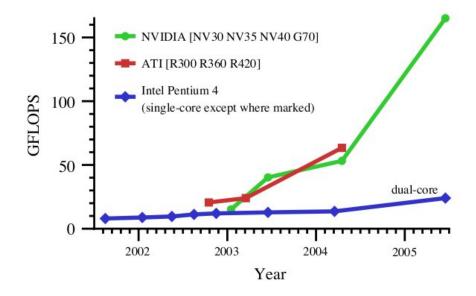

GPUs can also have significantly high raw performance than CPUs. For example, the NVIDIA GeForce 7800 GTX can perform 165 Giga Floating Point Operations Per Second (GFLOPS), while the theoretical peak rate of a dual-core 3.7 GHz Intel Pentium 965 is 25.6 GFLOPS [38]. Figure 1.1 shows a performance growth comparison between GPUs and CPUs in recent years. The performance gap between GPUs and CPUs has been widening and is likely to continue to increase, even as the number of CPU cores increases. Adding CPU cores requires duplicating control logic and implementing expensive cache-coherency protocols. In contrast, increasing the processing power of a GPU-like tiled SIMD architecture requires significantly fewer hardware resources.

However, the processing power provided by the GPU is unused most of the time, except in very specific applications. In recent years, a "general-purpose"

Figure 1.1: GPU performance [38]

GPU (GPGPU) community has sprung up, which applies GPUs to problems other than rendering three-dimensional scenes [38]. Despite the term "general-purpose", the GPGPU community focuses on adapting specific algorithms for execution on GPUs, although there has been some work on programming systems targetting a range of applications.

Although GPU vendors are progressively increasing the ease of use of their GPUs in general purpose computation, programming for GPUs remains a difficult task. Many application programmers for domain specific applications have not been trained to program parallel architectures.

### 1.2 Goal

The goal of this thesis is to describe our prototype implementation of an autoparallelizing compiler that takes advantage of GPU resources even for code that has not been explicitly implemented with GPUs in mind. This is accomplished by extending a Java JIT compiler to detect loops which can be parallelized, and which can be executed more quickly on the GPU than on the CPU. The higher raw performance of the GPU must be weighed against the cost of transferring the input and output between main memory and GPU memory. We propose a parameterized cost model to weigh these costs and decide when it is beneficial to execute code on the GPU. The parameters are used to tune the cost model to the specific hardware on which the code runs.

### **1.3** Contributions

Our work makes the following contributions:

- It proposes a new loop parallelization algorithm tailored to the programming model exposed by common GPU hardware. The GPU programming model combines some characteristics of both the vector and multi-processor execution models targetted by traditional parallelization algorithms, but is distinct from both of these models.

- It describes the prototype implementation that was built on top of an existing research Java virtual machine.

- It identifies obstacles to parallelization that are specific to Java bytecode, and briefly discusses the solutions that we have implemented to overcome them. The use of Just-in-Time compilation makes it possible to overcome these difficulties with simple but effective techniques.

- It introduces a technique for minimising the number of data transfers between the system's memory and the GPU's memory.

- It proposes and evaluates a cost model for deciding whether it is profitable to run a given loop on the GPU rather than the CPU. In particular, the cost model balances the data transfer overhead against the faster computation possible on the GPU.

The rest of the thesis is organized as follows: Chapter 2 provides background on GPUs, JikesRVM, dependence analysis and related work. Chapter 3 describes the core implementation of the dependence analysis, the GPU parallelization algorithm, other challenges faced and improvements made. Chapter 4 reports on an experimental evaluation of the cost model. Lastly, Chapter 5 concludes.

### Chapter 2

## Background

#### 2.1 GPU Overview

This section of the thesis will first explain the programming model presented by GPUs to programmers, and how it is intended to be used for rendering 3D images. Later, we will explain how the programming model can be used for other general purpose applications.

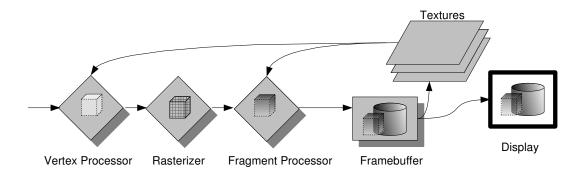

Under graphics application programming interfaces (APIs), the GPU programming model is organized as a pipeline of several stages, as shown in Figure 2.1. The figure shows a conceptual view of the pipeline exposed by the APIs. Actual hardware implementation can vary. The first stage of the pipeline is the geometry stage, and is implemented by the vertex processor. The input to this stage is a list of vertices in a three-dimensional local coordinate space describing the scene to be rendered. For each vertex, this stage translates it to global coordinates, calculates lighting information, and maps it to its two-dimensional position on the screen.

The second stage is the rasterizer. The rasterizer produces a bitmap with the same number of elements (called *fragments*) as the number of pixels in the image being rendered. On this bitmap, the rasterizer draws the polygons described by the two-dimensional vertices that were computed in the geometry stage. Each fragment contains a fixed amount of information such as color, texture coordinates and depth. Parameters generated by the vertex processor are also interpolated to

Figure 2.1: GPU Pipeline

each fragment.

The third stage is fragment processing. From the information stored in each fragment, the fragment processor computes a colour for the corresponding pixel. In addition to reading the information for the current fragment, the fragment processor may also perform random-access reads from *textures*, which are additional input arrays distinct from the fragment bitmap. The colours computed by the fragment processor may be written either to the frame buffer to be shown on the screen, or to a texture, from which they can be read again in subsequent fragment stage passes. However, it is not possible to read and write to the same texture in one pass.

In older GPUs, the transformations performed by these stages were fixed by the hardware, but in recent years, the vertex processing and fragment processing stages have become fully programmable and have been unified into a single hardware component. Non-graphical applications usually use only the fragment processor because of the convenient feedback loop provided by its ability to write to and read from textures. However, the vertex processor does expose a scatter operation.

The computation to be performed is specified to the GPU in the form of a fragment program, which traditionally performs floating point operations on a set of registers local to each fragment. Although early GPUs executed only straight-line code, current models support control flow within the fragment program, including loops. The fragment program may also perform an arbitrary number of random access reads from textures, but it may only output a fixed, small number of floating point numbers as its output, and to fixed output locations. The GPU executes the fragment program many times (i.e.,once for each output fragment), and records the output values generated by each execution in an element of the output texture. Because of the limitation on the output of a fragment program, a common GPGPU technique is to divide an algorithm into a sequence of passes, with each pass reading the texture generated by the preceding pass.

#### Listing 1 Matrix-vector Example

```

public static float[]

fix(float[][] A, float[] B) {

float [] Bn = new float [100];

for (int \mathbf{k} = 0; \mathbf{k} < 10; \mathbf{k}++) { // Loop 1

for (int x = 0; x < 100; x++) { // Loop 2

float \mathbf{s} = 0;

for (int y = 0; y < 100; y++) { // Loop 3

s += A[x][y] * B[y];

Bn[x] = s;

}

float[] tmp = Bn;

Bn = B;

B = tmp;

}

return B;

}

```

We use an example to demonstrate how computations are mapped to the GPU. Figure 1 shows Java code for an example program that multiplies a matrix by a vector 10 times. There are three ways in which a loop can be implemented when using a GPU, and we will use the three nested loops in the example program to demonstrate them. Figure 2 shows a GPU fragment shader program, written in Cg [26], used to implement the computation. The outermost loop ( $Loop_1$ ) is still executed on the CPU, and triggers the GPU program 10 times (the CPU code is not shown). The body of the middle loop ( $Loop_2$ ) becomes the fragment program. The GPU will execute the fragment program once for each element of the output array, thereby implementing the middle loop. Neither the CPU program nor the

Listing 2 matrix-vector code for GPU

```

float iteration (

in float2 coords : TEXCOORDO,

uniform samplerRECT textureA,

uniform samplerRECT textureB,

) : COLOR {

float s = 0.0;

for (float y = 0; y < 100; y++) {

float x = coords.x;

s += texRECT(

textureA, float2(x,y)) *

texRECT(textureB, float2(0,y))

);

}

return s;

}</pre>

```

GPU fragment program implements the middle loop; its implementation is implicit in the data-parallel programming model exposed by the GPU. The innermost loop  $(Loop_3)$  is encoded in the fragment program, since it is inside the body of the middle loop.<sup>1</sup> We call these three implementations of loops CPU, GPU-Implicit, and GPU-Explicit, respectively. In Section 3.3.4, we will give an algorithm to deciding how each loop in a program should be implemented.

Unfortunately, most graphics cards can only be used with a graphics API such as OpenGL [48] and shaders such as the Cg program shown in Listing 2. We must set up the graphics card so that when the fragment program is run, it will compute the desired result. First, any array data must be stored as textures. In the example shown in Listing 1, A and B should occupy two textures. Initial values of the two arrays should be copied into the texture before execution. The programmer should then instruct the graphics API to draw a quad primitive that is the size of B somewhere in the scene. The view should be set so that the quad is the only object drawn to the viewport. Finally, the programmer must also instruct the API to apply the shader given in Listing 2 after binding the textures accordingly. The end result will be that the value of the frame buffer will contain the results of one

<sup>&</sup>lt;sup>1</sup>This example could be implemented more efficiently if a loop interchange transformation was first applied; however, the purpose of the example is to demonstrate the three kinds of loops.

iteration of the matrix vector multiplication. The same procedure can be repeated after storing the framebuffer as the new texture B.

This technique is the more traditional GPGPU programming model that is widely applicable to many GPUs. Some newer GPGPU specific programming languages are described in Section 2.4. However, regardless of the programming method used, the GPU can be viewed as a stream processor as shown here:

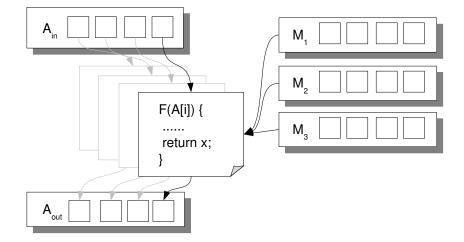

Figure 2.2: Stream Programming Model

We will call this programming model the Single Program Multiple Data (SPMD) stream programming model. A programmer can view the GPU as a machine that applies a small identical program (kernel) in parallel to every element of an array and stores the result to an output array. In figure 2.2, the program F is applied to every single element of  $A_{in}$  and output is stored in corresponding entries of  $A_{out}$ . Also, F is allowed to access other data randomly.

There are many other differences between GPUs and CPUs. Most GPUs are tailored to render graphics in real time, so certain tradeoffs are made in their design that hinder other applications.

In the standard GPU pipeline, fragment programs can perform data gathering operations (i.e., reading from arbitrary data-dependent locations in texture memory), but they cannot perform data scattering operations (i.e., writing to arbitrary data-dependent locations in texture memory). Several workarounds are possible. NVIDIA's new CUDA programming model allows arbitrary writes [2]. The latest generation of GPUs supporting the Direct3D 10 programming model have a programmable rasterizer which could be used to perform scatter operations in between passes of a fragment program [21]. However, hardware and drivers supporting these new programming models are not yet widespread. In this work, we target the GPUs that are widely available today using the ubiquitous OpenGL programming model. For that reason, our stream programming model shown in Figure 2.2 is able to read any textures available but can only to write to the output element associated with the current kernel instance.

For reasons of hardware cost, some current GPUs also do not fully respect IEEE standards when performing floating point arithmetic. Our implementation does not transform code marked with the Java strictfp modifier, which is intended to mark expressions which must be evaluated in strict compliance with the IEEE 754 standard. However, for code not marked with strictfp, it is possible that the result computed by a given GPU does not comply even with the looser Java standard for floating point arithmetic.

More information about the graphics pipeline and 3D graphics programming can be found in the OpenGL Programming Guide [48].

### 2.2 JikesRVM Overview

Our implementation is built on top of an existing research Java virtual machine called JikesRVM (Jikes Research Virtual Machine). JikesRVM (formally known as Jalapeño) provides a flexible open testbed to prototype virtual machine technologies and experiment with a large variety of design alternatives [6]. This subsection of the thesis will provide some background information on JikesRVM itself.

The most distinctive design feature of JikesRVM compared to other Java virtual machine is the language JikesRVM is written in. Much of the core functionality is written in Java while roughly 3% is written in C++ [11]. All applications written in Java require a VM (virtual machine) to execute. However, instead of requiring another VM to run JikesRVM, JikesRVM is actually executing on itself. There are a few special implementation choices made in order to facilitate this goal.

First, unlike most other VMs, JikesRVM never interprets the Java bytecode. Instead, it relies only on the Just-in-Time (JIT) compilation. JikesRVM has two different compilers: baseline and optimizing. The baseline compiler offers a quick bytecode to machine code compiler for most initial compilation of Java methods. The optimizing compiler, on the other hand, offers a multi-level optimizing compiler that requires more compilation time but which is suitable for recompilation of frequently executed methods. Currently JikesRVM supports the x86 and the PowerPC CPU architectures.

The build process also differs from normal Java programs. First, a static compiler is invoked to build each Java source file and generate all the required class files.

One of the JIT compilers within JikesRVM is chosen to run on an external VM to bootstrap the VM itself. Sun Microsystems' HotSpot, for example, has been used as the external VM. The bootstrapping process involves compiling a minimal subset of class files needed for elementary functions of the RVM to the machine language of the target machine. The list of class files required (called the *primordial list*) will be saved as a single image on disk. When JikesRVM runs, this image is loaded from disk, and is used to compile and run the other class files of JikesRVM and the application begin executed. More information about the bootstrapping and build system of JikesRVM can be found in *Implementing Jalapeño in Java* [10].

The self executing VM design enables many interesting optimizations. Not only does JikesRVM perform optimization of the running application, it can optimize itself while it is running if necessary. Recompilation decisions are made using the adaptive optimization system. JikesRVM collects information about the executing application by means of instrumenting and profiling branches. Based on statistics gathered by instrumenting the generated code, the VM will decide on a recompilation plan as well as use the information as an aid to optimizations. More information about the adaptive optimization system in JikesRVM can be found in *Adaptive optimization in the Jalapeño JVM* [13].

The optimizing compiler works on three intermediate representations (IR) similar to those of Advanced Compiler Design and Implementation [35]: High-level Intermediate Representation (HIR), Low-level Intermediate Representation (LIR) and Machine-level Intermediate Representation (MIR). Much of our extension resides in optimization passes that work on the HIR representation. In particular, the Static Single Assignment (SSA) variation of HIR is where the core parallelization phrases are implemented.

Although not directly used in our work, there are many more interesting design decisions and implementations within JikesRVM. For example, JikesRVM deploys a virtual processor approach for threads where threads are multiplexed onto one or more virtual processors. The VM then schedules virtual processors to physical ones. A "quasi-preemption" scheduling scheme is used to allow context switching only in specific instructions of the running program called *yield points*. This allows the implementation of parallel garbage collectors. For more information related to internals of JikesRVM and other research projects that use JikesRVM, a comprehensive list of all publications that involve JikesRVM can be found in the JikesRVM publications website [7].

#### 2.3 Dependence Overview

This section provides an overview of data dependence analysis which is essential when determining which sections of the source code can be executed in parallel in the GPU. An overview of dependence analysis as well as numerous definitions that are key to understanding our implementation are discussed in this section. More comprehensive treatments of dependence analysis can also be found in many textbooks [51, 47, 8].

Like all optimizations, parallelization must preserve the semantics of the original program. Consider the following example:

```

Listing 3 Simple Sequential Example

```

```

int x = 0;

x = 1; // S1

System.out.println(x); // S2

```

Suppose we would like to execute both  $S_1$  and  $S_2$  in parallel, possibly in two different processors. Depending on which processor finishes executing its corresponding instruction first, the output can vary. We might say that  $S_2$  depends on the execution of  $S_1$  to be completely finished. The relative ordering of  $S_1$  and  $S_2$ , therefore, must be preserved.

The study of the dependence relationship between instructions is called **dependence analysis**. The primary focus of dependence analysis is to identify possible control or data interference relationships between pairs of instructions such as those displayed in Listing 3. Dependence exists between specific executions of statements. Before we can define formally what data dependence is, we must be able to classify specific executions of a statement as a single statement might be executed multiple times. To do that we will use **iteration vectors**. Consider the following program:

Listing 4 Dependence across iterations

```

for(int i = 0; i < 100; i++) {

for(int j = 0; j < 100; j++) {

... // S0

}

}</pre>

```

The execution of  $S_0$  when the induction variables have the values i = 5 and j = 6 is said to have an iteration vector of  $\vec{v} = (5, 6)$ . Formally we define the iteration vector as follows:

**Definition 1** (Iteration Vector). Suppose L is a set of n nested loops  $L_0, L_1, L_2...L_n$ with loop induction variables  $i_0, i_1, i_2...i_n$  respectively. The execution of a statement S in L when  $i_0 = v_0, i_1 = v_1, i_2 = v_2, ...i_n = v_n$  is represented by  $S[\vec{v}]$  where  $\vec{v}$  is the **iteration vector**  $(v_0, v_1, v_2, ...v_n) \in \mathbb{Z}^n$ .

**Definition 2** (Iteration Space). The set of all possible iteration vectors of a loop nest is called the **iteration space** of the loop nest.

**Definition 3** (Iteration Vector Ordering). Given vectors  $\vec{v_0} = (v_0, v_1, v_2...v_{n-1})$  and

$\vec{v_1} = (v'_0, v'_1, v'_2 \dots v'_{n'-1})$ , we define the partial orders  $<_c$ , < and = as follows:

$$\vec{v} = \vec{v'} \iff v_0 = v'_0, v_1 = v'_1, \dots v_{\min(n,n')-1} = v'_{\min(n,n')-1}$$

$$\vec{v} <_c \vec{v'} \iff v_0 = v'_0, v_1 = v'_1, \dots v_{c-1} = v'_{c-1}, v_c < v'_c$$

$$\vec{v} < \vec{v'} \iff \exists_{c < n} | \ \vec{v} <_c \ \vec{v'}$$

We say  $\vec{v} >_c \vec{v'}$  or  $\vec{v} > \vec{v'}$  if  $\vec{v'} <_c \vec{v}$  or  $\vec{v'} < \vec{v}$  respectively.

The  $<_c$  relationship between iteration vectors creates a partial ordering in  $\mathbb{Z}^n$ . We can now formally define the execution of a statement to be the following:

**Definition 4** (Execution of Order Statements). If the execution of  $S_0[\vec{v}]$  occurs before  $S_1[\vec{v'}]$ , we will write  $S_0[\vec{v}] \ll S_1[\vec{v}]$ .

Also, given two vectors  $\vec{v}$  and  $\vec{v'}$ ,  $\vec{v} < \vec{v'}$  implies that  $S_0[\vec{v}]$  executes before  $S_1[\vec{v'}]$ regardless of the lexical order of  $S_0$  and  $S_1$  in the source code [51, Theorem 4.1]. Using Definition 4, we can identify the specific execution of any statement that is nested within loops. For statements that are outside of loops, we can define the function body as a single loop that iterates only once. The execution of  $S_0$  when the induction variables have the values i = 5 and j = 6 in Listing 4 will be written as S[(0,5,6)]. Since our work focuses on loops, we will abbreviate execution as S[(5,6)].

With a formal definition of execution of statements, we can formally define dependence.

**Definition 5** (Data Dependence). A data dependence between the execution of statements  $S_0[\vec{v}]$  and  $S_1[\vec{v'}]$  occurs when  $S_1[\vec{v}]$  accesses the same data as  $S_0[\vec{v}]$  and  $S_0[\vec{v'}] \ll S_1[\vec{v'}]$ . We will write  $S_0[\vec{v}] \to S_1[\vec{v'}]$  if such a dependence exists. If not, we will write  $S_0[\vec{v}] \neq S_1[\vec{v'}]$ . Furthermore, we will write  $S_0 \to S_1$  if there exist  $\vec{v}$  and  $\vec{v'}$  in the iteration space such that  $S_0[\vec{v}] \to S_1[\vec{v'}]$ . Otherwise, we will write  $S_0 \neq S_1$ if for all  $\vec{v}$  and  $\vec{v'}$  in the iteration space,  $S_0[\vec{v}] \neq S_1[\vec{v'}]$ .

The type of a dependence can be further classified as **true dependence**, **antidependence**, **output dependence** or **artificial dependence**. Table 1 shows the classifications of data dependences according to whether the accesses are reads or writes. Figure 2.3 demonstrates an example of each dependence. In the first three examples, at least one access is a write, so rearranging the relative order of  $S_0$  and  $S_1$  will definitely alter the program's semantics. In some memory models, two reads may be considered to interfere. However, in our work, we assume that pairs of reads are not considered a dependence. We shall redefine data dependence as follows:

**Definition 6** (Data Dependence (with Interference)). A data dependence between the execution of statements  $S_0[\vec{v}]$  and  $S_1[\vec{v'}]$  occurs when  $S_1[\vec{v'}]$  accesses the same data as  $S_0[\vec{v}]$ , at least one of the instruction writes to that data, and  $S_0[\vec{v}] < S_1[\vec{v'}]$ .

| Table | 1 | Data | depend | ence | types. |

|-------|---|------|--------|------|--------|

|-------|---|------|--------|------|--------|

| $S_0$     | $S_1$     | Name                  |  |  |  |

|-----------|-----------|-----------------------|--|--|--|

| WRITE $x$ | READ $x$  | True Dependence       |  |  |  |

| READ $x$  | WRITE $x$ | Anti-dependence       |  |  |  |

| WRITE $x$ | WRITE $x$ | Output Dependence     |  |  |  |

| READ $x$  | READ $x$  | Artificial Dependence |  |  |  |

When dealing with dependence relationships between instructions across iterations, we can further classify data dependences as **loop-carried** and **loopindependent**.

**Definition 7** (Loop-carried Dependence). A data dependence is **loop-carried** if there exist iterations  $\vec{v}$  and  $\vec{v'}$  such that  $S_0[\vec{v}] \to S_1[\vec{v'}]$  and  $\vec{v} < \vec{v'}$ .

**Definition 8** (Dependence Carried by a Loop). Let  $S_0[\vec{v}] \to S_1[\vec{v'}]$  be a loop-carried dependence with  $\vec{v} <_c \vec{v'}$ . We denote this dependence as  $S_0 \to_c S_1$  and we say that the loop-carried dependence is **carried by** the loop at depth c. Alternatively, we can also write the dependence as  $S_0 \to_L S_1$  if loop L is the loop at depth c.

**Definition 9** (Loop Independent Dependence). A data dependence is **loop-independent** if there exists  $\vec{v}$  such that  $S_0[\vec{v}] \to S_1[\vec{v}]$  and for all  $\vec{w}, \vec{w'} w \neq w' \longrightarrow$  $S_0[\vec{w}] \neq S_1[\vec{w'}]$ . To distinguish this from loop-carried dependence, we will denote this type of dependence as  $S_0 \to_{\infty} S_1$ . (a) True Dependence

(b) Anti Dependence

```

x = 0;

x = 2; // S0

x = 1; // S1

(c) Output Dependence

x = 0;

```

Figure 2.3: Examples of different dependences

Consider the following code segment:

Listing 5 Dependence across iterations

```

int x = 0;

for(int i = 0; i < 100; i++) {

System.out.println(x); // S0

x = i; // S1

}

```

There is a loop-independent anti-dependence  $S_0 \to_{\infty} S_1$  as well as true loopcarried dependences on  $S_1[0] \to S_0[1], S_1[1] \to S_0[2], S_1[2] \to S_0[3]...S_1[98] \to S_0[99]$  which can simply be denoted by  $S_1 \to_1 S_0$ .

Given a loop body, it is known that individual iterations of the body can be executed in parallel if each iteration does not depend on the outputs of other iterations [8, Theorem 2.8].

**Theorem 1** (Dependence and Parallel Execution of Loop Iterations). Given a set of instructions  $S = \{S_0, S_1, ..., S_{n-1}\}$  within a loop of depth c, iterations of the loop can be executed in parallel if  $\forall_{i,j \in [0:n-1]} S_i \not\rightarrow_c S_j$ .

**Definition 10.** A dependence graph of a program is graph G = (V, E) where  $v \in V$ are the nodes representing instructions of the program and the labeled edges  $e_{\omega} =$  $(v_0, v_1) \in E$  implies  $v_0 \rightarrow_{\omega} v_1$  may be true.  $\omega$  is the loop that carries the dependence and  $\omega$  is  $\infty$  if the dependence is not loop carried.

Theorem 1 show that a loop is parallelizable if there are no loop-carried dependences between its iterations. For that reason, our implementation must provide an analysis that will compute all possible dependence across loops. The result will be stored in form of a graph called the **dependence graph** that is defined in Definition 10. Edges of the dependence graph shows possible dependence relationship between instructions. Because these edges represent a "may be" dependent relationship, it is important to create a dependence graph that is as precious as possible.

### 2.4 Related Work

Most existing parallelization approaches fall into two categories, depending on the hardware features that they exploit: task-level parallelism [39, 20, 42, 15, 12] and vectorization [25, 17, 31, 19, 23, 29, 37, 36, 51, 8, 47].

Task-level parallelism is supported by multiple instances of a fully-functional processor. The overhead of creating threads can be high, but each thread can execute an arbitrary program. Generally, the outermost loop is parallelized, resulting in long tasks and few thread creations. In the context of parallelizing Java, three examples of this technique are JAVAR [18], JavaSpMT [28], and SableSpMT [41].

Vectorization, on the other hand, is supported by a SIMD architecture in which multiple computational units are controlled by a single control unit, so they execute the same instruction. Although SIMD instructions are limited to specific types of computations, they have little overhead, to the point that it is feasible to mix individual SIMD instructions with sequential computations. As a result, vectorization generally targets innermost loops. Vectorization can be categorized into two principal approaches: the traditional loop-based parallelization [19, 37, 46, 32] and the basic block approach [31, 27, 44].

The loop-based vectorization technique proceeds by stripmining the loop. A single loop will be replaced by two nested loops where the number of iterations in the inner loop is same as the vector length. Each scalar instruction in the inner loop body will then be replaced by a corresponding vector instruction. The basic block approach, on the other hand, unrolls the loop by a multiple of the vector length and packs each group of isomorphic scalar instructions into a vector instruction. The loop-based approach requires complicated loop transformations like loop fission (splitting up a single loop to multiple loops) and scalar expansion (replacing scaler variables with an array) and is inhibited by loop carried dependences, especially true data dependences shorter than the vector length. The basic block approach, on the other hand, requires simpler analyses but incurs overhead due to packing and unpacking of the operands of isomorphic statements. Vectorization in general requires very sophisticated analyses and faces numerous challenges including the difficult problem of supporting control flow in vector code [45]. In contrast, our

target architecture (the GPU) requires a simple loop analysis and offers a more flexible programming model than the traditional SIMD machines.

Current GPUs cannot be decisively categorized as either multi-processor or vector processors; they share some characteristics of both. The fragment processor has traditionally been a SIMD processor with a limited instruction set. In recent years, hardware for support strictly nested control flow has been added, but it is not intended to support highly divergent control flow. The overhead required to start a computation makes the GPU more similar to a multi-processor system.

The CUDA architecture [2] moves even further towards a general multi-processor style of parallelism. The CUDA programming framework further exposes the GPU to general purpose programmers. No longer do the programmers have to express computation through a graphical API like OpenGL, thus eliminates a lot of unnecessary graphic initialization overhead. The programmers are given a lot of control of the NIVDIA 8800 GPUs in terms of GPGPU programmability. They are allowed to manage thread blocks within the GPU themselves with a C like programming language. Unlike earlier graphics cards, CUDA compatible GPUs allow synchronization like mechanism. However, much like traditional OpenGL based GPGPU techniques, the responsibility to discover parallelism is left to the programmer.

Parallelizing an inner loop would incur high kernel startup overhead, while an outer loop is likely to contain divergent control flow and computations not supported by the GPU. The hybrid nature of GPUs suggests a new kind of parallelization algorithm targeting loops in the middle of a loop nest. In this thesis, we present one such algorithm.

Another parallelization system targeting GPUs is that of Cornwall et al. [24], which performs source-to-source translations to help domain experts retarget an image processing library written in C++ to GPUs. Somewhat similar to the approach described later in this thesis, their translator aims to discover potentially-parallel assignments (PPAs) in loops by walking the abstract syntax tree of the program. Enclosing loops whose induction variables affect the index of array assignments of the PPAs are considered to be potentially-parallel loops (PPLs). Optimizations such as hoisting of parallelization-preventing instructions are then applied to the PPLs and eventually be translated into GPU executable code. This approach works well with programs that are known to have a specific structure. Our approach described here follows the more traditional approach to parallelization in which parallelization attempts occur as high as possible in the loop nest tree. This approach should facilitate extraction of more parallelism.

RapidMind is a C++ GPU metaprogramming framework which consists of two parts [3]. The front-end is a C++ template library that provides data types and overloads operators to generate code in the RapidMind intermediate representation (IR) data structures. The back-end optimizes the IR and emits code for one of the supported target architectures (GPU, Cell BE, multi-core CPU). A programmer can embed a kernel intended to run on the GPU as a suitably delimited piece of C++ code directly in the C++ program. Executing such a kernel requires two steps. In the first step, the C++ code that the programmer has written is executed on the CPU. At this stage, no computation is actually performed. Each overloaded operator, instead of performing a computation, generates the IR instruction that would perform the corresponding computation. Thus, the code that the programmer has written is code that writes the code that will run on the GPU. Once all the code has run and the entire IR has been generated, the RapidMind back-end processes the IR and generates suitable GPU code which can then be executed.

ASTEX [1] takes a run-time approach, in that it searches for hot traces at run time that are amenable to GPU execution [40]. The target program is initially instrumented with monitoring code and executed. Runtime memory access information is gathered and analyzed off-line. Favorable code segments will then be recompiled into Hybrid Multi-core Parallel Programming (HMPP) *codelets*. Similar to RapidMind, HMPP [43] aims to provide a general purpose programming environment for numerous architectures. Unlike RapidMind, however, HMPP codelets rely on compiler directives such as C pragmas.

Recently, interest in using JikesRVM for parallelization has grown. Zhao et al. [50, 49] have also implemented loop parallelization in the context of Jikes-RVM. However, rather than GPUs, their intended target is JAMAICA [4], a multiprocessor parallel architecture.

## Chapter 3

### Implementation

#### 3.1 Overview

We have implemented GPU parallelization within an existing Java Just-In-Time (JIT) compiler, JikesRVM [9]. In order to minimize the overhead of parallelization, the compiler must focus on hot (frequently executed) methods of the program. JikesRVM uses an adaptive optimization system [13] with multiple optimization levels; optimizations at higher levels are applied only to methods observed to be hot. GPU parallelization is done at the highest optimization level (-O2), and only on code that is expected to be executed frequently.

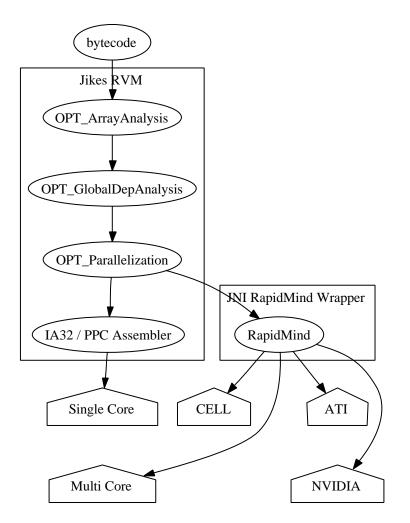

Figure 3.1 shows the overall architecture of the implementation. The parallelization algorithm is preceded by two preparatory stages. The first stage,  $OPT\_Array$ -AccessAnalysis, recovers information about multi-dimensional array accesses that is lost in Java bytecode (see Section 3.5.1). Such information will be stored within  $OPT\_ArrayAccessDictionary$  in the form of  $OPT\_ArrayAccess$  objects. The second stage,  $OPT\_GlobalDepAnalysis$ , performs dependence analysis on array accesses to construct a dependence graph of type  $OPT\_GlobalDepGraph$  (see Section 2.3). The third stage,  $OPT\_Parallelization$ , implements GPU parallelization, which generates code that will run on the GPU (see Section 3.3).

The primary back-end used by the third stage is the RapidMind platform [3]. RapidMind is a C++ programming framework for expressing data parallel algo-

Figure 3.1: Overall Architecture

rithms in a hardware-independent way. Our code generator accesses RapidMind using a Java Native Interface (JNI) wrapper. RapidMind is designed to generate appropriate code at run-time for the chosen hardware. Currently, RapidMind can generate code for GPUs from major vendors, the Cell BE processor, and multi-core CPUs. So far, we have evaluated the system on GPUs only.

This chapter is organized as follows: Section 3.2 will describe the importance of  $OPT_GlobalDepGraph$  in parallelization and the implementation of  $OPT_Global-$ DepAnalysis. Section 3.3 will describe the parallelization process and the implementation of  $OPT_Parallelization$ . Section 3.4 will describe an extension to the parallelization algorithm to eliminate data transfer overhead. Section 3.5 will describe some of the Java specific challenges and how the implementation solves these challenges. Since  $OPT_ArrayAccessDictionary$  is a Java specific requirement, it will be discussed in section 3.5.

### **3.2** Dependence Analysis

This section provides an overview of the data dependence analysis implemented by  $OPT_GlobalDepAnalysis$ . Using the theory described in Section 2.3, this compilation phase will compute a dependence graph that will be used in the parallelization pass.

Before the core  $OPT_Parallelization$  phase begins,  $OPT_GlobalDepAnalysis$  is run to create the dependence graph of the method currently being compiled. The entire dependence graph is stored in an object of type  $OPT_GlobalDepGraph$ ; it can be displayed with an added compiler flag (see Appendix A). Nodes of the graph  $(OPT_GlobalDepGraphNode)$  represent JikesRVM High-level Intermediate Representation (HIR) instructions of the current method. Given an  $OPT_Instruction$  the corresponding  $OPT_GlobalDepGraphNode$  can be retrieved by the scratchObject of the instruction. The scratchObject reference is a common way to annotate instructions to pass information between passes within JikesRVM.

Figure 3.2 shows an example dependence graph printed using the debug flag. Each node in the graph represents a JikesRVM HIR instruction. Green edges represent loop-independent dependences, red edges represent loop-carried dependences while blue edges represent the loop-carried dependences on the loops' induction variables.

Figure 3.2: Example dependence graph output

The rest of this section will explore how dependence relationships are computed in the  $OPT_GlobalDepAnalysis$  phrase. One interesting fact about dependence computation is that extra spurious edges between instructions in the dependence graph will not affect the soundness of the parallelization process. However, they do prevent parallelization opportunities. The general approach we use is to start by assuming all dependences exist and remove dependence edges by disproving their existence.

**Definition 11** (Spurious Edges of Dependence Graphs). An edge  $E_{\omega}$  between  $S_0$ and  $S_1$  is spurious if for all plausible execution of the program  $S_0 \not\rightarrow_{\omega} S_1$ .

Given two instructions  $S_0$  and  $S_1$ , the first step is to examine dependences related to scalars. The use of SSA within JikesRVM HIR simplifies this process greatly. Two instructions will have a scalar data dependence if both  $S_0$  and  $S_1$ access the same register and one of them defines a register while the other reads it. The dependence  $S_0 \to S_1$  will be loop carried if  $S_1$  is a SSA form  $\phi$  instruction that reads a variable x in the header of a loop L while  $S_0$  is a instruction that defines x within L. Otherwise,  $S_0 \to S_1$  is loop independent.

A dependence that results from accessing array elements requires a more sophisticated test. Array element accesses are indexed by variables. In many cases the values of the indices are not compile-time constants. For example:

| Listing 6 Array indices example          |  |  |  |  |

|------------------------------------------|--|--|--|--|

| x = A[f(c)]; // S0<br>A[g(c)] = y; // S1 |  |  |  |  |

If both  $\mathbf{f}(\mathbf{c})$  and  $\mathbf{g}(\mathbf{c})$  are known to be distinct constants, we can prove they are independent. However, when  $\mathbf{f}(\mathbf{c})$  and  $\mathbf{g}(\mathbf{c})$  are not constants, it would seem that the only option is to be conservative and create k + 1 edges between  $S_0$  and  $S_1$  as  $S_0 \to_m S_1, m \in [1, 2, ..., k, \infty]$  where k is the depth the innermost loop that contains  $S_0$  and  $S_1$ . To conserve memory, a special  $OPT_GlobalDepGraphEdge$ flagged UNKNOWN is used to represent k edges within the  $OPT_GlobalDepGraph$ .

UNKNOWN edges prevent parallelization due to the fact that we are assuming the existence of a loop carried dependence. A large number of parallelization opportunities will be missed due to this limitation. Consider the following program:

| Listing 7 Dependence across iterations                                                                                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <pre>for(int i = 1; i &lt; 100; i++) {     for(int j = 1; j &lt; 100; j++) {         A[f(i,j)] = A[(g(i,j)]; //S      } }</pre> |  |  |  |  |

This is a frequently seen array access pattern in which the index is a function of the loop induction variable. Because i and j are induction variables, they will not be compile-time constants and an UNKNOWN edge might seem unavoidable. Luckily, there are known algorithms that can be used to prove independence in many cases.

Suppose we are interested in knowing whether S has a true loop-carried dependence on itself. What we want to determine is if there exists some  $\vec{v_0} = (x, y)$  and  $\vec{v_1} = (x', y')$  such that A[f(x, y)] is addressing the same value as A[(g(x', y')]] while  $\vec{v_0} < \vec{v_1}$ . Formally:

**Theorem 2** (Loop-carried Dependence from Array Access). Let  $S_0$  and  $S_1$  be in a common loop nest with induction variables  $i_0, i_1, ... i_{n-1}$ . Also let  $S_0$  reference  $A[f(i_0, i_1, ... i_{n-1})]$  and  $S_1$  reference  $A[g(i_0, i_1, ... i_{n-1})]$ , assuming that one of the references be a write and let no other common data be accessed.  $S_0 \rightarrow_c S_1$  holds if and only if there exist  $\vec{v_0}$  and  $\vec{v_1}$  in the iteration space such that  $\vec{v_0} <_c \vec{v_1}$  and  $f(\vec{v_0}) = g(\vec{v_1})$ .

*Proof.* This is a straight application of Definition 7 in the special case where the common data is an array element indexed by a function of the induction variables.

If f and g are pure functions, we could examine the possible values that the functions return for all possible x, x', y, y'. In practice, we need more efficient ways to determine dependence. However, in doing so, we need to make some assumptions that sacrifice completeness. First, the array addressing index value must be **admissible**.

**Definition 12** (Admissible Function). A function is admissible if the only unknowns are induction variables of the loop nest.

Second, we attempt to disprove a dependence only when the index expressions are affine functions of the induction variables of the loop nest. These two requirements appear to be restrictive at first glance. In practice, however, many loops are written in this way. The previous dependence can now be generalized as follows:

Given a loop nest with induction variables  $i_0, i_1, i_2, ..., i_n$  with constant lower bounds  $L_0, L_1, L_2, ..., L_n$ , constant upper bounds  $U_0, U_1, U_2, ..., U_n$ , and loop invariant constants  $a_0, a_1, a_2, ..., a_n, a_{n+1}, b_0, b_1, b_2, ..., b_n, b_{n+1}$ , the instructions  $S_0$  accessing  $A[a_0i_0 + ..., a_ni_n + a_{n+1}]$  and  $S_1$  accessing  $A[b_0i_0 + ..., b_ni_n + b_{n+1}]$  do not have a loop carried dependence if the following system of inequalities in 2n unknowns  $(x_0, x_1, x_2, ..., x_n, x'_0, x'_1, x'_2, ..., x'_n)$  has no solution:

$$a_0x_0 + a_1x_1 + a_2x_2 + \dots + a_nx_n + a_{n+1} = b_0x'_0 + b_1x'_1 + b_2x'_2 + \dots + b_nx'_n + b_{n+1}$$

$$(x_0, x_1, x_2, \dots + x_n) < (x'_0, x'_1, x'_2, \dots + x'_n)$$

$$L_0 \le x_0 \le U_0, L_1 \le x_1 \le U_1, L_2 \le x_2 \le U_2, \dots, L_n \le x_n \le U_n$$

To try to prove that the system has no solution, we apply a sequence of successively stronger tests. Within our implementation in JikesRVM, the initial test for the nonexistence of a solution is the **strong separability test** [51]. If the function is not strongly separable, the weak separability test will be used. Although strong separability test is the weakest of all tests due to its strong assertion, it is actually applicable in many practical applications, and is inexpensive to evaluate.

**Definition 13.** (Separability) Given two linear functions  $f(\vec{x}) = a_0x_0 + ...a_nx_n + a_{n+1}$  and  $g(\vec{x'}) = b_0x'_0 + b_1x'_1 + b_2x'_2 + ...b_nx'_n + b_{n+1}$  where  $a_0, a_1, a_2, ...a_n, a_{n+1}, b_0, b_1, b_2, ...b_n, b_{n+1}$  are constants,  $f(\vec{x})$  and  $g(\vec{x'})$  are **separable** if there exists  $c \in [0:n]$  such twee for all  $i \in [1:n]i \neq c \longrightarrow a_i = 0, b_i = 0.$

In this case,  $f(\vec{x})$  can be written as  $f(x) = a_0 + a_c x_c$  and  $g(\vec{x}')$  can be written as  $f(x') = b_0 + b_c x'_c$ .

Furthermore,  $f(\vec{x})$  and  $g(\vec{x}')$  are strongly separable if  $a_c = 0$ ,  $b_c = 0$  is true or if  $a_c = b_c$  is true. Otherwise, they are weakly separable.

| Table 2 Strong separability test |                       |                                                                                                                                                                                        |  |  |  |  |

|----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                  | Condition             | No Solution                                                                                                                                                                            |  |  |  |  |

|                                  | $a_c = 0, b_c = 0$    | $ \begin{array}{c}  a_{0} \neq b_{0} \\  a_{c} \nmid (b_{0} - a_{0}) \\  b_{c} \nmid (a_{0} - b_{0}) \\  a_{c} \nmid (a_{0} - b_{0}) \text{ or } a_{c} > (a_{0} - b_{0}) \end{array} $ |  |  |  |  |

|                                  | $a_c \neq 0, b_c = 0$ | $a_c \nmid (b_0 - a_0)$                                                                                                                                                                |  |  |  |  |

|                                  | $a_c = 0, b_c \neq 0$ | $b_c \nmid (a_0 - b_0)$                                                                                                                                                                |  |  |  |  |

|                                  | $a_c = b_c \neq 0$    | $a_c \nmid (a_0 - b_0) \text{ or } a_c > (a_0 - b_0)$                                                                                                                                  |  |  |  |  |

Table 2 provides an algorithm for proving nonexistence of a solution of two linear functions that are strongly separable. The first column specifies the values of  $a_c$  and  $b_c$  and the second column provides the sufficient conditions for the system to have no solution. The first case is trivial. Given both  $a_c = 0$  and  $b_c = 0$ , the array access is strictly  $A[a_0]$  and  $A[b_0]$  where both  $a_0$  and  $b_0$  are constants. Independence follows from the fact that  $a_0 \neq b_0$ .

The second case follows from the fact that if  $a_0 + a_c x_c = b_0$ , we can rewrite the equation as  $a_c x_c = b_0 - a_0$ , which implies that solution exists if and only if  $a_c \mid (b_0 - a_0)$ . The third case follows the same argument as well.

The last case can be written as  $a_0 + a_c x_c = b_0 + a_c x'_c$ . Again, we can rewrite the equation as  $a_c(x'_c - x_c) = (a_0 - b_0)$ . If a solution exists, then  $a_c$  must divide  $(a_0 - b_0)$ . Also, since  $x_c < x'_c$  must be true, then we know that  $a_c \le (a_0 - b_0)$  has to hold as well.

If the two equations are weakly separable, we can conclude that  $a_0 + a_c x_c = b_0 + a_c x'_c$  has no solution if  $gcd(a, -b) \nmid (b_0 - a_0)$  [51].

This concludes the two tests currently implemented within  $OPT_GlobalDep-Analysis$ . Although the tests are not comprehensive, they do cover all the applications we targetted. Many improvements could be introduced to increase the power of the analysis and further disprove dependence.

$OPT_GlobalDepAnalysis$  treats  $a_0, a_1, a_2, ..., a_n, a_{n+1}, b_0, b_1, b_2, ..., b_n, b_{n+1}$  of  $f(\vec{x})$ and  $g(\vec{x}')$  as constants only if they are actually compile time constants. In cases where these variables are not known constants, JikesRVM provides a loop analysis that can prove that they are loop invariant. In that case, we can symbolically evaluate some of the dependence tests and disprove dependence by means of a runtime check.

As shown in a later section, the whole dependence graph does not need to be fully available before the parallelization process begins. A suggested improvement to the implementation would be to improve execution time of the (just-in-time) compilation process by computing dependences lazily in a demand-driven fashion. Computation of dependence within a loop can be reserved to the cases where the loop is GPU execution favorable.

Other possibilities for future work are to add additional tests if the separability test fails. Next, the full *GCD Test* could be applied. Banerjee [16] provided many

more dependence tests suitable for different types of loops. Loop iteration spaces shaped like triangles or trapezoids are not covered in our implementation and can be added. In general, a system with ranged inequalities can be difficult to solve and may require more powerful yet computationally intensive approaches such as integer programming.

## 3.3 Algorithm

This section describes the core parallelization process of the compiler implemented in *OPT\_Parallelization*. Using the dependence graph described in the previous section, we can identify independent loop iterations that can be executed in parallel. The algorithm that we use is based on a very well known algorithm (*parallelize* [51]). However, because the GPU programming model differs from that of CPUs and vector units, the existing algorithm needs to be modified.

There are two major approaches to automatic parallel execution. They are usually called **parallelization** and **vectorization**. While both focus on loop iterations of a program, they have a slightly different goal.

## 3.3.1 Parallelization

Parallelization is usually referred to as execution of a single program on multiple CPUs. Programmers who have a very firm understanding of the high level intention of the program, usually express explicit parallelism by means of **task-level parallelism**. Multiple threads performing identical as well as different tasks are created to operate on different data sets. However, task-level parallelism is often difficult to discover automatically since the compiler knows very little about the high level concepts of the program. In most cases, an auto-parallelizing compiler will focus on loop structures.

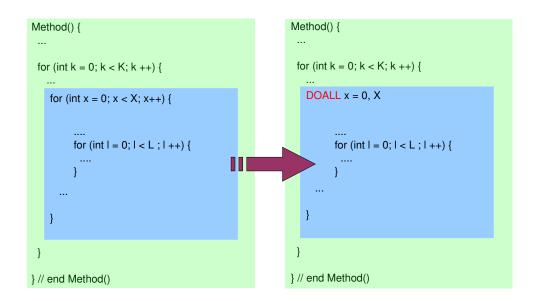

The basic idea is to find loop-level parallelism between iterations. Because thread creation is usually an expensive process, the compiler should always try to parallelize as many instructions as possible. Therefore, the traditional algorithm

Figure 3.3: Parallelization scenario

operates on the loop tree by greedily attempting to parallelize the outer loops before recursively searching in child loops. However, aggressively distributing a large code portion to each CPU can result in a higher chance of loop-carried data dependences. Fortunately, threads can be synchronized by means of locks or barriers. Figure 3.3 shows a possible auto-parallelization scenario where the outermost *for* loop is translated into a Fortran-like *DOALL* loop that is executed in parallel.

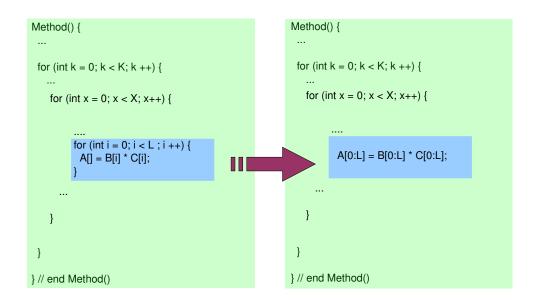

## 3.3.2 Vectorization

Vectorization, on the other hand, refers to the use of vector instructions of the target machine architecture to perform otherwise scalar operations. For example, the instruction ADDPS from the Intel Streaming SIMD Extensions is capable of adding two vectors of size four in parallel [5]. Vectorization mainly exploits data parallelism, meaning that the programmer's intention is to perform the same operation to each element of a group of data. Vector instructions are often multiples of a single operation with no control structures. Execution is always parallel. Each single operation must be independent. Figure 3.4 demonstrates a typical loop based vectorization process performed by an auto-vectorizing compiler. Instead of iterating through each element of an array A, the whole loop has been replaced with a

Figure 3.4: Vectorization scenario

single vector instruction that operates on A.

## 3.3.3 GPU Parallelization

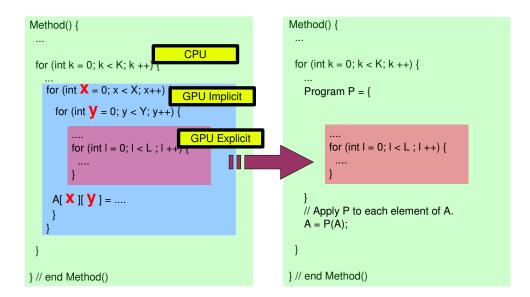

From the SPMD programming model programming model described earlier, we can see that current GPU architecture is not strict data parallelism as in vectorization nor is it strict task-level parallelism as in multi-threading. Current GPGPU techniques operate on data streams so one might that consider such programming model relates closely to SIMD applications. However, because the GPU is capable of control flow, it should not be viewed as a SIMD machine. While the GPU can handle complicated control flow like a threaded CPU, it is still limited by the data stream model. Much like a threaded CPU where thread creation is a significant overhead, GPU initialization is also a source of overhead. Finally, most GPUs are not capable of performing synchronization of data, making it less task oriented.

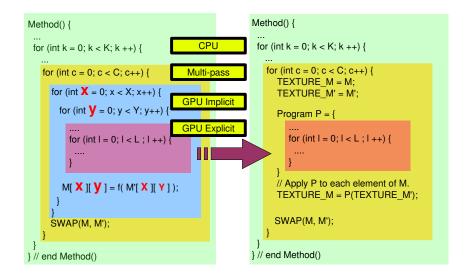

Figure 3.5 demonstrates a typical program parallelized using GPGPU techniques. In many cases, the programmer's goal is to perform similar computationally intensive operations on each element of some input data and store the result in another data set. The program on the left illustrates the programmer's intent

Figure 3.5: GPGPU code pattern

when no parallel hardware is available. She must iterate through each element of the loop.

The program on the right illustrates a GPGPU version of the same program. The two data iterating loops have been removed. Instead, iterations of the loop have been replaced by a single fragment program. The program will be invoked by passing a two-dimensional input array to the program. The GPU will apply the program to all individual data elements of the array. Results will be stored in the output array. This programming model closely reflects the SPMD programming model used to describe the GPU in figure 2.1.

Almost all GPU execution favorable programs will exhibit this type of pattern. The most interesting part of this transformation is that the x and y loops no longer exist in the final program. Instead, they are implicit within the GPU program. For that reason, we are going to label such loops as *GPU-Implicit*. On the other hand, loops that are inside *GPU-Implicit* loops become loops of the GPU executable program. They will be labeled as *GPU-Explicit*. Finally, non-parallelizable outer parents of the GPU loops will be labeled as *CPU* loops.

## **3.3.4** Classification of Loops

A compiler targeting the GPU must not only identify parallelizable loops, but it must also decide, for each loop, whether to implement it on the CPU, to make the GPU implement it implicitly by directing it to execute a fragment program once for each iteration of the loop, or to implement it explicitly inside the fragment program. In this section, we formulate constraints that these decisions must satisfy for a collection of nested loops, and in the next section, we give an algorithm that computes a solution to these constraints.

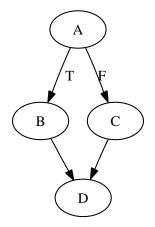

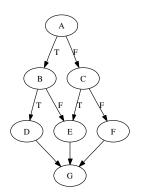

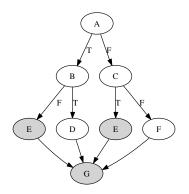

The constraints are defined on a loop nesting tree. The root of the tree represents the whole program as a loop that is iterated exactly once. In addition, each loop in the program is represented by a tree node. For each loop, the loops nested directly within it become its children in the loop nesting tree. Each node in the tree must be classified as either *CPU*, *GPU-Implicit*, or *GPU-Explicit*.

There are no limitations on the kinds of loops that may be classified as CPU loops. Thus, a safe (but perhaps inefficient) solution is to classify all loops as CPU loops.

A *GPU-Implicit* loop, as the name suggests, is implemented by directing the GPU to execute a fragment program once for each iteration of the loop. In order for a loop L to be *GPU-Implicit*, it must fulfill the following requirements.

**Restriction 1.** The parent of GPU-Implicit loop L in the nesting tree must be either CPU or GPU-Implicit.

The outermost *GPU-Implicit* loop will be the control change from CPU to GPU. Once a *GPU-Implicit* loop starts, the GPU will be in charge of the program until the end of the loop. Within a *GPU-Implicit* loop, there can be no more *CPU* loops.

**Restriction 2.** If the parent L' of L is also GPU-Implicit, L must be tightly nested within L' (i.e., L must be the entire body of L').

Multiple loops may be implemented implicitly by the GPU, but only if all of them are tightly nested immediately within one another. This way, the body of the innermost *GPU-Implicit* loop becomes the GPU executable program used in the SPMD model.

**Restriction 3.** No loop-carried true data dependence can exists between instructions of L.

Iterations of L will be the fragment program that the GPU executes implicitly for each value of the induction variable. The order of execution is not necessarily preserved as the GPU executes iterations in parallel. Restriction 3 ensures that changing the order does not change the semantics because of Theorem 1. Surprisingly, anti-dependence between loop iterations is allowed. The reason is that before GPU execution begins, all the array data must be copied into the GPU. The data copying, which will be discussed further in Section 3.3.6, has the same effect as renaming, which breaks any anti-dependence.

**Restriction 4.** For each array store  $A[i_1, i_2, ..., i_n]$  inside a GPU-Implicit loop, the dimension n of the store must equal the number of GPU-Implicit loops, and the  $i_k$  must be the induction variables of the GPU-Implicit loops, in order of nesting, with  $i_1$  being the induction variable of the outermost GPU-Implicit loop.

This final and perhaps the strongest restriction ensures that any program in the GPU will not have any scatter memory write. Every *GPU-Implicit* iteration can write only to the memory location associated with that iteration.

Finally, a *GPU-Explicit* loop is implemented explicitly in the code of the fragment program. The only requirement is that it must be nested (not necessarily tightly) inside a *GPU-Implicit* loop or an other *GPU-Explicit* loop. However, since a *GPU-Explicit* loop is part of the body of a *GPU-Implicit* loop, Restriction 4 must still hold. Within the *GPU-Explicit* loop, there should be no true data dependences carried by any of the *GPU-Implicit* loops (Restriction 3), but dependences carried by the *GPU-Explicit* loops are allowed.

## 3.3.5 Identifying Loop Types

The algorithm to decide whether each loop should be executed on the CPU or implicitly or explicitly on the GPU begins by identifying the index expressions occurring in stores in each loop. It applies the following definition to each loop.

**Definition 14.** For a loop L in the loop nesting tree, WRITEINDICES(L) is defined as follows. If the body of L contains an instruction that cannot be supported on the GPU, then WRITEINDICES $(L) = \top$ . Otherwise, if the body of L contains no array writes, then WRITEINDICES $(L) = \bot$ . Otherwise, if all array writes in the body of L have the same index vector  $(i_1, \ldots, i_n)$  and all the  $i_k$  are induction variables of distinct loops, then WRITEINDICES $(L) = (i_1, \ldots, i_n)$ . Otherwise, WRITEINDICES $(L) = \top$ .

Listing 8 WriteIndices example

```

int x = 0;

for(int i = 0; i < 100; i++) {

for(int j = 0; j < 100; j++) {

A[i][j] = ...;

}

}

for(int i = 0; i < 100; i++) {

for(int j = 0; j < 100; j++) {

A[i][j] = ...;

B[0][j + j] = ...;

}

}

```

In Listing 3.3.5, the first loop clearly has *WriteIndices* of (i, j). The second loop contains two array writes of different indices so the *WriteIndices* is  $\top$ .

A loop that cannot be implemented on the GPU because it contains unsuitable instructions or because it writes to arrays using inconsistent indices will have  $WRITEINDICES(L) = \top$ . Otherwise, WRITEINDICES of a loop is the unique index vector used for array writes in the loop.

Next, the algorithm computes, for each loop, the maximal set of loops that are tightly nested within it, using the following definition.

**Definition 15.** For a loop L in the loop nesting tree, TNLOOPS(L) is defined

as follows. If the entire body of L is another loop L', then  $\text{TNLOOPS}(L) = \text{TNLOOPS}(L') \cup \{L\}$ . Otherwise,  $\text{TNLOOPS}(L) = \{L\}$ .

Finally, the algorithm traverses the loop nesting tree searching for loops that will become the outermost *GPU-Implicit* loops. When there are multiple possibilities, it is preferable to select the outermost loop possible to maximize the amount of processing moved to the GPU. Therefore, the traversal proceeds from the root of the tree to the leaves, so that it considers outer loops before inner loops. When considering a given loop, the algorithm checks that the loop and other loops tightly nested within it cover the induction variables needed for array stores occurring in the loop, and that the candidate loops do not carry dependences. The algorithm also considers the possibility of interchanging the tightly-nested loops. This makes parallelization possible even if the original nesting order is inconsistent with the array store index vector, or extra loops are nested in between those that define the induction variables used in array store indices. To determine whether loops can be interchanged, the algorithm uses the standard technique of identifying interchange-preventing dependences [51]. The overall parallelization algorithm is shown in Listing 9. it is invoked on the root of the loop nesting tree.

#### Listing 9 GPU parallelization algorithm

| <b>Algorithm</b> PARALLELIZE(loop $L$ ):                                                      |

|-----------------------------------------------------------------------------------------------|

| 1: <b>if</b> WRITEINDICES $(L) = (i_1, \ldots, i_n)$                                          |

| and $\{i_1, \ldots, i_n\} \subseteq \text{TNLOOPS}(L)$                                        |

| <b>and</b> no dependences are carried by loops $i_1, \ldots, i_n$                             |

| and $\text{TNLOOPS}(L)$ can be interchanged so the outermost n loops are $i_1, \ldots, i_n$ , |

| in this order <b>then</b>                                                                     |

| 2: interchange $\text{TNLOOPS}(L)$ in this way                                                |

| 3: generate GPU program for body of loop $i_n$                                                |

| 4: replace loop $L$ with code to execute GPU program                                          |

| 5: else                                                                                       |

| 6: for each child loop $L'$ of $L$ in the loop nesting tree do                                |

| 7: $PARALLELLIZE(L')$                                                                         |

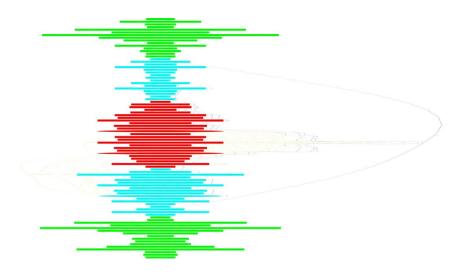

Figure 3.6 shows the dependence graph output after the parallelization phase. Besides the dependence information shown by the edges, each node has been color coded to represent the loop classification process. For this example, the algorithm

Figure 3.6: Sample output of the dependence graph after parallelization

discovered two *GPU-Explicit* loops and the sole loop nested inside them becomes the *GPU-Implicit* loop. The green colored nodes are instructions that have not been parallelized and remain a *CPU* loop. Cyan colored nodes are instructions that have been classified as *GPU-Implicit* loops. The red colored nodes are classified as the *GPU-Explicit* loops (which also are part of *GPU-Implicit* loops). Not only is this final graph representation of the parallelization process useful for debugging the compiler's parallelization phase, it is helpful for providing feedback to the users of the compiler. An Integrated Development Environment (IDE), for example, could use the information provided by this graph to inform the user which parts of their code is GPU parallelizable and which dependences are preventing parallelization.

## 3.3.6 Data Transfer

Graphics cards have dedicated memory with a very high transfer rate to the graphics processor. However, GPU computations cannot directly access main memory, and CPU instructions cannot directly access GPU memory. The speed-up of using the GPU may be limited by the overhead of copying data between main memory and GPU memory. This section proposes a cost model to determine whether executing code on the GPU is beneficial despite the copying overhead.

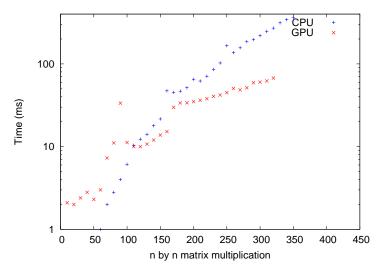

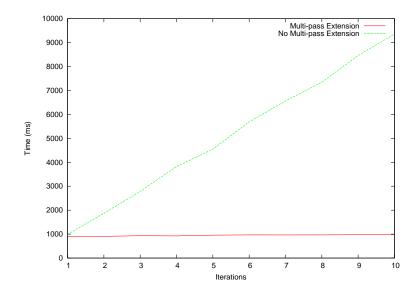

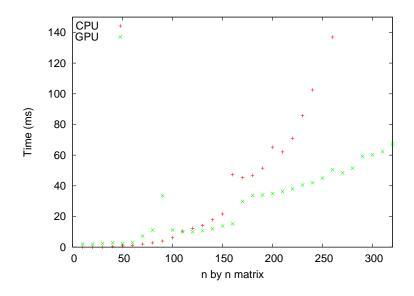

Figure 3.7 shows the execution time of a matrix multiplication benchmark. The set of plots in blue is the execution of a plain CPU execution. The set of plots

in red shows a parallelized version for the GPU using our compiler. The graph shows that for matrices of size  $120 \times 120$  or less, the CPU outperforms the GPU due to the overhead associated with using the GPU. We will propose a execution cost model to estimate the execution time needed for CPU execution and GPU execution. At runtime, we will decide whether the speed-up from the parallel GPU execution overcomes the associated overhead.

Figure 3.7: Plain matrix multiplication on GPU and CPU

The model estimates the time that a loop nest will take to execute on both the CPU and the GPU (including copying overhead). With hundreds of models of CPUs and GPUs in use today, no single formula is suitable for all configurations. Therefore, we propose a parameterized formula, in which the parameters can be tuned to the specific target hardware on which the code will execute.

The value of each of the parameters to the model becomes available at one of three different stages of compilation: when the JIT compiler is installed on the machine, when the JIT compiler compiles the loop, and whenever the compiled code executes the loop. When the JIT compiler is installed, micro-benchmarks are executed to estimate the processing power of the CPU and the GPU. These parameters remain constant for all programs. The estimated number of instructions in the body of the loop becomes known either when the loop is compiled or when the loop executes (if other loops are nested within it and their iteration counts depend on runtime values). Whenever the compiled code prepares to execute the loop, the number of iterations and the size of the input and output data become known. At that point, all the parameters are known, and the compiled code uses the model to decide whether to execute that instance of the loop on the CPU or the GPU.

| Listing 10 Cost estimation                                         |   |                                          |   |      |

|--------------------------------------------------------------------|---|------------------------------------------|---|------|

| $\overline{Cost_{cpu} = t_{cpu} \times insts \times A_{out}.size}$ |   |                                          |   |      |

| $Cost_{gpu} = t_{gpu} \times insts \times A_{out}.size$            | + | $copy \times \sum_{A \in Ainout} A.size$ | + | init |

$Cost_{cpu}$  estimates the time needed to execute all iterations of the loop on the CPU. The parameter  $t_{cpu}$  is the average time needed to execute one bytecode instruction as determined by the off-line micro-benchmarks. We assume that all instructions require the same amount of time, though a more precise model could divide instructions into different classes. The parameter *insts* is the expected number of instructions to be executed in the body of the loop. We assume that conditional branches are taken 50% of the time and that nested loops execute for ten iterations, unless their iteration count is a known constant. The parameter  $A_{out}.size$ , the size of the output array, becomes known when the loop is to be executed. The loop will iterate once for each element in the output array. The estimated cost is the product of these three parameters.

The GPU processing time  $Cost_{gpu}$  is modelled as a product of three similar parameters, but two additional terms are added to model data transfer. The parameter *copy* estimates the time needed to copy one floating point number to or from the GPU memory, and is multiplied by the number of elements in the input and output arrays. If the same array is both read and written, it is counted twice. The parameter *init* is a constant term estimating the time needed to set up the GPU to execute a given shader program.

To determine the fixed parameters of the model (i.e.  $t_{cpu}$ ,  $t_{gpu}$ , copy, and init), a benchmark is executed on both the CPU and GPU on a range of test inputs of different sizes and the actual execution times are recorded. Least squares regression is performed to determine the parameter values that most closely reflect the observed times. We will call these benchmarks the *training benchmarks*.

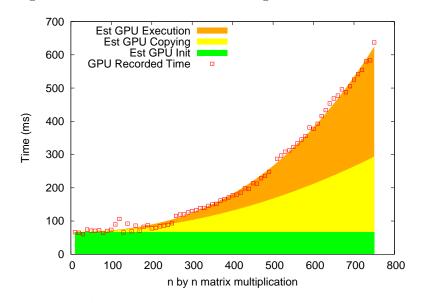

Figure 3.8 demonstrates a cost estimation of a matrix multiplication kernel. The