# Organic Thin Film Transistor Integration

by

## Flora M. Li

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2008

©Flora Man-Wah Li 2008

| I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including |

|---------------------------------------------------------------------------------------------------------|

| any required final revisions, as accepted by my examiners.                                              |

|                                                                                                         |

|                                                                                                         |

|                                                                                                         |

|                                                                                                         |

| I understand that my thesis may be made electronically available to the public.                         |

|                                                                                                         |

|                                                                                                         |

|                                                                                                         |

|                                                                                                         |

|                                                                                                         |

#### **Abstract**

This thesis examines strategies to exploit existing materials and techniques to advance organic thin film transistor (OTFT) technology in device performance, device manufacture, and device integration. To enhance device performance, optimization of plasma enhanced chemical vapor deposited (PECVD) gate dielectric thin film and investigation of interface engineering methodologies are explored. To advance device manufacture, OTFT fabrication strategies are developed to enable organic circuit integration. Progress in device integration is achieved through demonstration of OTFT integration into functional circuits for applications such as active-matrix displays and radio frequency identification (RFID) tags.

OTFT integration schemes featuring a tailored OTFT-compatible photolithography process and a hybrid photolithography-inkjet printing process are developed. They enable the fabrication of fully-patterned and fully-encapsulated OTFTs and circuits. Research on improving device performance of bottom-gate bottom-contact poly(3,3"'-dialkyl-quarterthiophene) (PQT-12) OTFTs on PECVD silicon nitride (SiN<sub>x</sub>) gate dielectric leads to the following key conclusions: (a) increasing silicon content in SiN<sub>x</sub> gate dielectric leads to enhancement in field-effect mobility and on/off current ratio; (b) surface treatment of SiN<sub>x</sub> gate dielectric with a combination of O<sub>2</sub> plasma and octyltrichlorosilane (OTS) selfassembled monolayer (SAM) delivers the best OTFT performance; (c) an optimal O<sub>2</sub> plasma treatment duration exists for attaining highest field-effect mobility and is linked to a "turnaround" effect; and (d) surface treatment of the gold (Au) source/drain contacts by 1octanethiol SAM limits mobility and should be omitted. There is a strong correlation between the electrical characteristics and the interfacial characteristics of OTFTs. In particular, the device mobility is influenced by the interplay of various interfacial mechanisms, including surface energy, surface roughness, and chemical composition. Finally, the collective knowledge from these investigations facilitates the integration of OTFTs into organic circuits, which is expected to contribute to the development of new generation of all-organic displays for communication devices and other pertinent applications. A major outcome of this work is that it provides an economical means for organic transistor and circuit integration, by enabling use of the well-established PECVD infrastructure, yet not compromising the performance of electronics.

### Acknowledgements

I feel truly blessed, honored, and thankful to be approaching the end of my Ph.D. studies. *Blessed*...to be granted the opportunity to pursue my doctoral degree. *Honored*...to have interacted with brilliant and talented individuals who have enlightened, inspired, and helped me through my studies. *Thankful*...to be surrounded by loving and kind souls who have offered constant support and encouragement.

My utmost appreciation goes to my supervisor, Professor Arokia Nathan, who has been a wonderful mentor, an inspiration, and a true visionary. His ingenious advices guided me to many extraordinary opportunities, invaluable experiences, and academic achievements. I am absolutely grateful for his guidance, support, friendship, encouragement, trust and countless stimulating discussions.

My deepest gratitude goes to my family. It is my greatest fortune/blessing to have extraordinarily amazing parents, David and Adda Li, who have offered unconditional love, support, understanding, and nourishment. I am truly thankful for the freedom and luxury to explore my academic endeavors. Special thanks go to my grandmother, my brother Ben, and my sister Christina for bringing me joy and laughter when most needed.

I am indebted to Professor Beng Ong and Dr. Yiliang Wu from Xerox Research Centre of Canada (XRCC), who have offered invaluable insights and constant support. Much of the work in this thesis could not have been possible without their help, their expertise, and their magical organic materials.

I like to express my sincere appreciation to my fellow researchers and colleagues at the Giga-to-Nano Research Laboratory for their contributions to this work, for sharing their insights and expertise, for their assistance, and their guidance. These talented individuals include Dr. Jackson Lai, Dr. Kai Wang, Dr. Mohammad R. Esmaeili-Rad, Dr. Reza Chaji, Maryam Moradi, Dr. Yuri Vyangrenko, Prof. Peyman Servati, Hyun-Jung Lee, Prof. Andrei Sazonov, Dr. Isaac Chan, Dr. Denis Striakhilev, Dr. Sarswati Koul, Richard Barber, Robert Mullins, and Eliza Ho. It has been my pleasure and my honor to work with you.

Many thanks go to all my dear friends in Toronto and my extended family in GoodLife, for your persistent support and encouragement. I sincerely thank Uncle Norman and Auntie Anna for their superb generosity and kindness. Special acknowledgement goes to my

superstar coach, Graham Patterson, for going the extra mile to keep me on track, positive, enthuse, and laser focus in thesis writing. Your daily motivation and words of wisdom will never be forgotten. I lovingly extend my gratitude to James for his adoring support and care during final stages of this work.

I acknowledge the financial support from Natural Sciences and Engineering Research Council (NSERC) of Canada, Ontario Centres of Excellence (OCE), and University of Waterloo.

Lastly, I want to thank everyone who have educated, inspired, and enlightened me along the way, to make my academic journey at University of Waterloo a truly remarkable and colorful experience.

<sup>&</sup>quot;Do not go where the path may lead, go instead where there is no path and leave a trail." ~Ralph Waldo Emerson

## To My Parents,

My achievements are your achievements.

## **Table of Contents**

| Abstı  | ract .   |                                                  | iii   |

|--------|----------|--------------------------------------------------|-------|

| Ackn   | owledg   | ements                                           | iv    |

| Table  | e of Cor | ntents                                           | vii   |

| List o | of Table | es                                               | xiv   |

| List o | of Figur | ·es                                              | xxiii |

| Chap   | ter 1 I  | ntroduction                                      | 1     |

| 1.1    | Organ    | ic Electronics: History and Market Opportunities | 3     |

|        | 1.1.1    | Large-Area Displays                              | 6     |

|        | 1.1.2    | Rollable Displays                                | 7     |

|        | 1.1.3    | Radio Frequency Identification (RFID) Tag        | 7     |

| 1.2    | Thesis   | s Motivation and Objectives                      | 8     |

|        | 1.2.1    | Technological Challenges                         | 9     |

|        | 1.2.2    | Research Scope and Approaches                    | 11    |

| 1.3    | Thesis   | s Organization                                   | 12    |

| Bibl   | iography | 7                                                | 13    |

| Chap   | ter 2 C  | Organic Thin Film Transistor (OTFT) Overview     | 16    |

| 2.1    | Organ    | ic Semiconductor Overview                        | 18    |

|        | 2.1.1    | Basic Properties                                 | 18    |

|        | 2.1.2    | Charge Transport                                 | 21    |

|        | 2.1.3    | Microstructure and Molecular Alignment           | 22    |

|        | 2.1.4    | Material Development and Classifications         | 25    |

|        | 2.1.5    | Sensitivity to Environmental Influences          | 30    |

| 2.2   | OTFT     | Operation and Characteristics                                            | 32      |

|-------|----------|--------------------------------------------------------------------------|---------|

|       | 2.2.1    | OTFT Parameter Extraction                                                | 35      |

|       | 2.2.2    | Contact Resistance Extraction                                            | 37      |

|       | 2.2.3    | Desirable OTFT Characteristics                                           | 40      |

| 2.3   | OTFT     | Device Architecture                                                      | 41      |

|       | 2.3.1    | Top-Contact and Bottom-Contact OTFTs                                     | 41      |

|       | 2.3.2    | Top-Gate, Bottom-Gate, and Dual-Gate OTFTs                               | 42      |

| 2.4   | OTFT     | Device Material Selection                                                | 44      |

|       | 2.4.1    | Organic Semiconductor                                                    | 45      |

|       | 2.4.2    | Gate Dielectric                                                          | 48      |

|       | 2.4.3    | Electrodes/Contacts                                                      | 50      |

|       | 2.4.4    | Substrate                                                                | 52      |

|       | 2.4.5    | Encapsulation Strategies                                                 | 54      |

| 2.5   | Summ     | nary                                                                     | 56      |

| Bibli | iography | 7                                                                        | 56      |

| Chap  | ter 3 C  | OTFT Integration Strategies                                              | 62      |

| 3.1   | Techn    | ological Challenge in OTFT Integration                                   | 63      |

| 3.2   | Overv    | iew of Processing and Fabrication Techniques                             | 65      |

|       | 3.2.1    | Deposition Methods for Organic Semiconductor                             | 68      |

|       | 3.2.2    | Patterning by Shadow Mask                                                | 70      |

|       | 3.2.3    | Patterning by Photolithography                                           | 73      |

|       | 3.2.4    | Patterning by Inkjet Printing                                            | 77      |

| 3.3   | OTFT     | Fabrication Schemes                                                      | 83      |

|       | 3.3.1    | Basic 1-Mask Processing Scheme for Bottom-Gate OTFT                      | 84      |

|       | 3.3.2    | Photolithography Scheme for Fully-Patterned and Fully-Encapsulated I     | 3ottom- |

|       |          | Gate OTFT                                                                | 85      |

|       | 3.3.3    | Hybrid Photolithography-Inkjet Printing Scheme for Fully-Patterned Botto | m-Gate  |

|       |          | OTFT                                                                     | 92      |

|       | 3.3.4    | Photolithography Scheme for Top-Gate and Dual-Gate OTFTs                 | 96      |

|       | 3.3.5    | Fabrication Scheme Comparisons                                           | 102     |

| 3.4   | Summ     | ary and Contributions                                                    | 104     |

| Bibli | iography | 7                                                                        | 106     |

| Chapt  | ter 4  | Gate     | Dielectric                | by      | Plasma       | Enhanced             | Chemical                | Vapor | Deposition |

|--------|--------|----------|---------------------------|---------|--------------|----------------------|-------------------------|-------|------------|

|        |        | (PEC     | (VD)                      | •••••   | •••••        | •••••                | •••••                   | ••••• | 110        |

| 4.1    | Expe   | eriment  | tal Details an            | d Cha   | racterizatio | on Methods           |                         |       | 112        |

|        | 4.1.1  | De       | position Con              | ditions | s of PECV    | D Silicon Nitr       | ide (SiN <sub>x</sub> ) |       | 112        |

|        | 4.1.2  | 2 Thi    | in Film Chara             | cteriz  | cation Meth  | ods                  |                         |       | 113        |

| 4.2    | Mate   | erial Cl | naracterizatio            | n of P  | ECVD Sil     | N <sub>x</sub> Films |                         |       | 116        |

|        | 4.2.1  | Bu       | lk/Structural             | Chara   | cterization  |                      |                         |       | 116        |

|        | 4.2.2  | 2 Sur    | rface Charact             | erizat  | ion          | •••••                |                         |       | 123        |

|        | 4.2.3  | Ele      | ectrical Chara            | cteriz  | ation        |                      |                         |       | 130        |

|        | 4.2.4  | Sui      | mmary                     |         |              |                      |                         |       | 134        |

| 4.3    | Elec   | trical C | Characterizati            | on of   | OTFTs wit    | th PECVD Ga          | te Dielectric           |       | 134        |

|        | 4.3.1  | 300      | 0°C SiN <sub>x</sub> Gat  | e Diel  | ectrics      |                      |                         |       | 136        |

|        | 4.3.2  | 2 150    | O°C SiN <sub>x</sub> Gat  | e Diel  | ectrics      |                      |                         |       | 142        |

|        | 4.3.3  | Sta      | cked SiN <sub>x</sub> Ga  | ate Di  | electrics    |                      |                         |       | 145        |

|        | 4.3.4  | 200      | O°C SiO <sub>x</sub> Gate | e Diel  | ectrics      |                      |                         |       | 148        |

|        | 4.3.5  | OT       | FTs on Plast              | ic Sub  | strates      |                      |                         |       | 151        |

| 4.4    | Sum    | mary a   | and Contribut             | ions    |              |                      |                         |       | 156        |

| Biblio | ograpl | ny       |                           |         |              |                      |                         |       | 158        |

| Chapt  | ter 5  | Diele    | ctric Interfa             | ice E   | ngineerin    | g                    | ••••                    | ••••• | 162        |

| 5.1    |        |          |                           |         | _            | _                    |                         |       | 163        |

|        | 5.1.1  | _        |                           |         |              |                      |                         |       | 163        |

|        | 5.1.2  | . Ox     | ygen Plasma               | Treat   | ment         |                      |                         |       | 167        |

| 5.2    | Expe   | eriment  | tal Details               |         |              |                      |                         |       | 170        |

| 5.3    | Impa   | act of I | Dielectric Sur            | face T  | reatments    |                      |                         |       | 172        |

|        | 5.3.1  | Ele      | ectrical Chara            | cteriz  | ation        |                      |                         |       | 172        |

|        | 5.3.2  | 2 Inte   | erface Charac             | teriza  | tion         | ••••                 |                         |       | 176        |

|        | 5.3.3  | S An     | alysis                    |         |              |                      |                         |       | 182        |

| 5.4    | Impa   | act of C | Oxygen Plasm              | na Exp  | oosure Con   | ditions              |                         |       | 184        |

|        | 5.4.1  | Ele      | ectrical Chara            | cteriz  | ation        |                      |                         |       | 184        |

|        | 5.4.2  | 2 Inte   | erface Charac             | eteriza | tion         |                      |                         |       | 189        |

|        | 5 4 3  | . An     | alvsis and Di             | scussi  | on           |                      |                         |       | 200        |

| 5.5   | Summ     | ary and Contributions                             | 203 |

|-------|----------|---------------------------------------------------|-----|

| Bibli | iography | ·                                                 | 204 |

| Chap  | ter 6 C  | Contact Interface Engineering                     | 207 |

| 6.1   | Backg    | round                                             | 208 |

|       | 6.1.1    | Charge Injection                                  | 208 |

|       | 6.1.2    | Alkanethiol SAM on Metals                         | 211 |

| 6.2   | Experi   | mental Details                                    | 213 |

| 6.3   | Impact   | t of Contact Surface Treatment by Thiol SAM       | 212 |

|       | 6.3.1    | Electrical Characterization.                      | 215 |

|       | 6.3.2    | Interface Characterization                        | 220 |

|       | 6.3.3    | Analysis                                          | 223 |

| 6.4   | Impact   | t of Execution Sequence of Surface Treatment      | 226 |

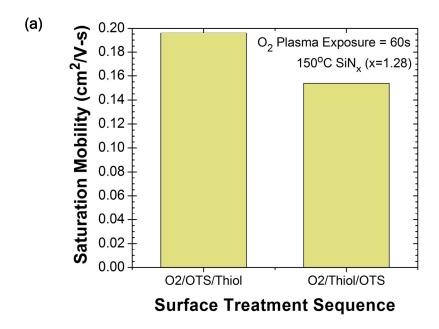

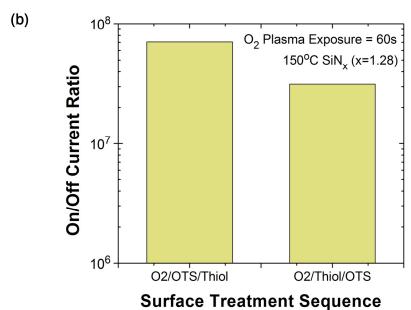

|       | 6.4.1    | Electrical Characterization.                      | 226 |

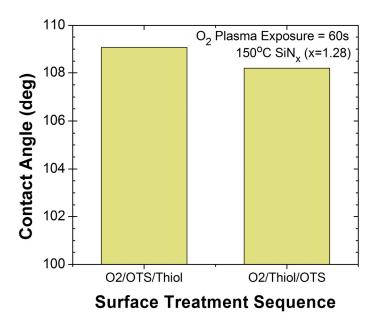

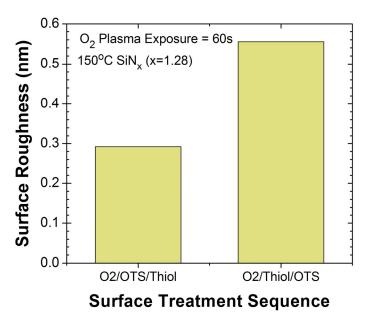

|       | 6.4.2    | Interface Characterization                        | 227 |

| 6.5   | Summ     | ary and Contributions                             | 231 |

| Bibli | iography | ·                                                 | 232 |

| Chap  | ter 7 O  | OTFT Circuits and Systems                         | 235 |

| 7.1   | OTFT     | Requirements for Circuit Applications             | 235 |

| 7.2   | Applic   | eations                                           | 240 |

|       | 7.2.1    | Displays                                          | 240 |

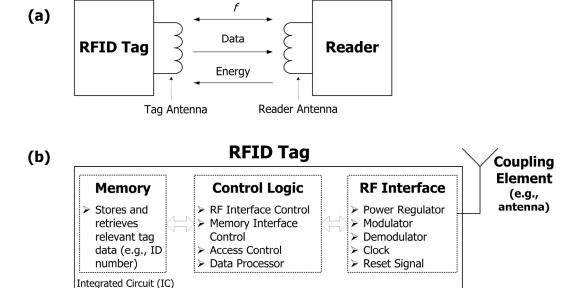

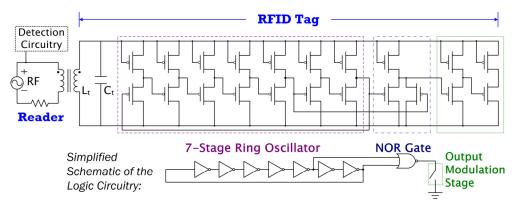

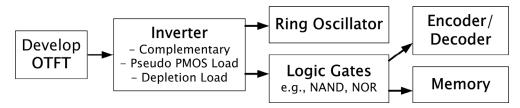

|       | 7.2.2    | RFID Tags                                         | 241 |

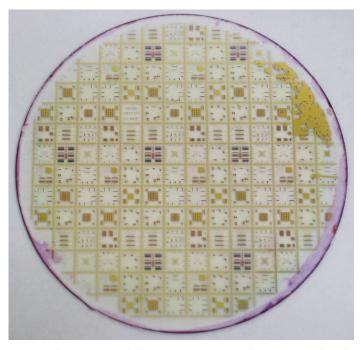

| 7.3   | Circuit  | t Demonstration                                   | 245 |

|       | 7.3.1    | Fabrication Schemes                               | 245 |

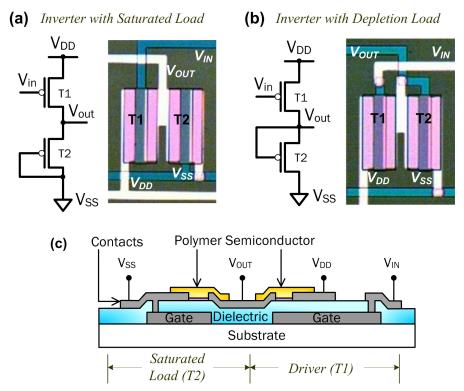

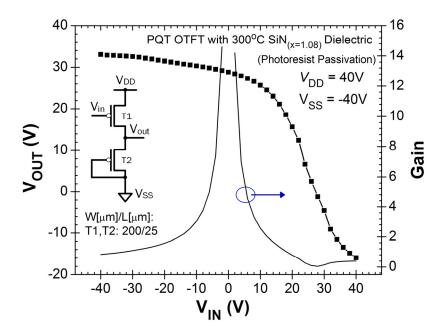

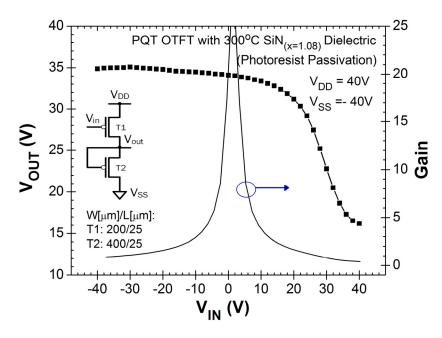

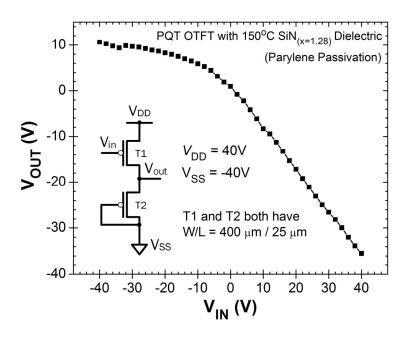

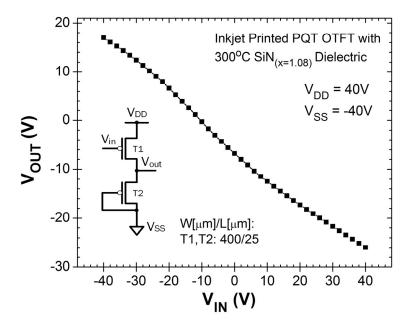

|       | 7.3.2    | Inverters                                         | 247 |

|       | 7.3.3    | Current Mirrors                                   | 251 |

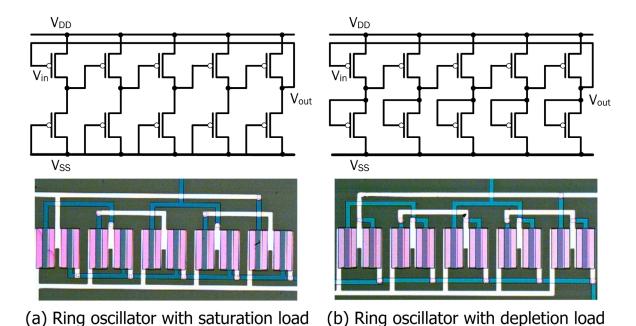

|       | 7.3.4    | Ring Oscillators                                  | 253 |

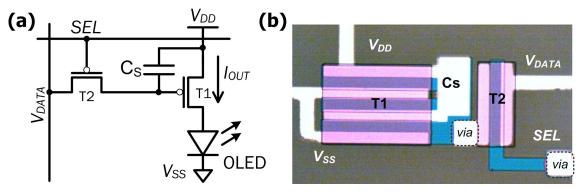

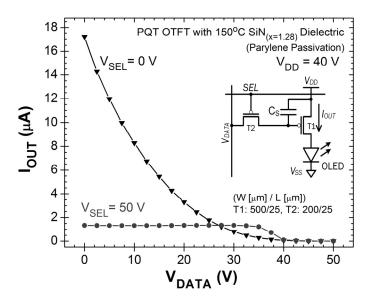

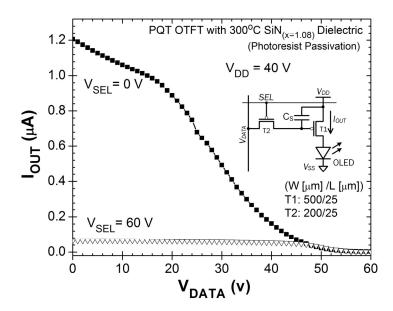

|       | 7.3.5    | Display Pixel Circuits                            | 254 |

| 7.4   | Summ     | ary, Contributions and Outlook                    | 262 |

|       | 7.4.1    | Active-Matrix Backplane Integration               | 262 |

|       | 7.4.2    | Back-End Process Integration: Bonding & Packaging | 263 |

| Rihli | iography |                                                   | 264 |

| Chapt  | ter 8 | Conclusions            | 268 |

|--------|-------|------------------------|-----|

| Chapt  | ter 9 | Research Contributions | 273 |

| 9.1    | List  | of Publications        | 277 |

| Glossa | arv   |                        | 278 |

## **List of Tables**

| Table 1.1. | Comparison of OTFTs and amorphous silicon (a-Si) TFTs.                                                                                                                                                                                   | 6   |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| cla        | Properties, representative chemical structure and typical mobility of the three main asses of organic semiconductors. The mobility of silicon is included for comparison                                                                 | 27  |

|            | [19]General requirements for a good TFT [47]                                                                                                                                                                                             |     |

|            |                                                                                                                                                                                                                                          |     |

| Table 2.3. | Device material consideration for the OTFT fabrication in this thesis                                                                                                                                                                    | 45  |

| Table 2.4. | Work function ( $\Phi_{M}$ ) of selected metals [63]                                                                                                                                                                                     | 51  |

| Table 2.5. | Properties of flexible substrate material candidates [68].                                                                                                                                                                               | 53  |

| Table 3.1  | Deposition and patterning techniques employed for OTFT fabrication in this research.                                                                                                                                                     |     |

|            | Key advantages of the inkjet printing process for the fabrication of organic electronics 9][31]                                                                                                                                          |     |

|            | Experimental summary of the impact of selected printing parameters on the quality of sjet printed PQT-12 organic semiconductor thin film.                                                                                                |     |

| de         | Summary of strengths and weaknesses of the various OTFT integration approaches veloped in this research. The approaches are grouped by the technique used for positing/patterning organic layer: photolithography and inkjet printing    | .03 |

| ap         | Comparing device performance of fully-patterned OTFTs fabricated by various proaches. Best values of field-effect mobility and on/off current ratio measured are own                                                                     | 03  |

|            | Comparison of the strengths and drawbacks of the fabrication/patterning techniques nsidered in this thesis.                                                                                                                              | 05  |

| 30         | Deposition conditions for PECVD SiN <sub>x</sub> films prepared at substrate temperature of 0°C and 150°C. SiN <sub>x</sub> films were deposited in a parallel-plate PECVD reactor operating an excitation frequency of 13.56 MHz.       | _   |

| ac         | Unique surface properties of silicon-rich $SiN_x$ (when compared to nitrogen-rich $SiN_x$ ) count for the improved mobility in PQT-12 OTFTs. The qualities quoted are measured $O_2$ plasma and OTS SAM treated Si-rich $SiN_x$ surfaces | d   |

| Table 4.3. | Impact of silicon-rich SiN <sub>x</sub> gate dielectric on OTFT and nc-Si TFT1                                                                                                                                                           | 41  |

| Table 4.4. | Description of stacked SiN <sub>x</sub> gate dielectric samples                                                                                                                                                                          | 46  |

| Table 4.5. Material characterization data for stacked SiN <sub>x</sub> films, including refractive index, [N]/[Si] ratio, and dielectric constant. Data for Si-rich SiN <sub>x</sub> and N-rich SiN <sub>x</sub> are included for comparison                                                                                                                                                                 | 47  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.6. Various plastic substrates and PECVD gate dielectric employed for PQT-12 OTFT fabrication in this study. The corresponding effective field effect mobility ( $\mu_{FE}$ ), on/off current ratio ( $I_{ON}/I_{OFF}$ ) and threshold voltage ( $V_T$ ), extracted in the saturation region, are shown                                                                                               | 51  |

| Table 4.7. Surface roughness of 150°C PECVD $SiN_x$ on $Si$ wafer and plastic substrate                                                                                                                                                                                                                                                                                                                      | 52  |

| Table 4.8. Summary of key observations on comparative study of OTFT with different PECVD gate dielectrics.                                                                                                                                                                                                                                                                                                   | 57  |

| Table 5.1. The impact of surface conditions on the molecular orientation of organic semiconduct (e.g., pentacene and P3HT)                                                                                                                                                                                                                                                                                   |     |

| Table 5.2. Dielectric-semiconductor interface engineering experiments                                                                                                                                                                                                                                                                                                                                        | 71  |

| Table 5.3. Dielectric surface treatment experiment: sample descriptions                                                                                                                                                                                                                                                                                                                                      | 72  |

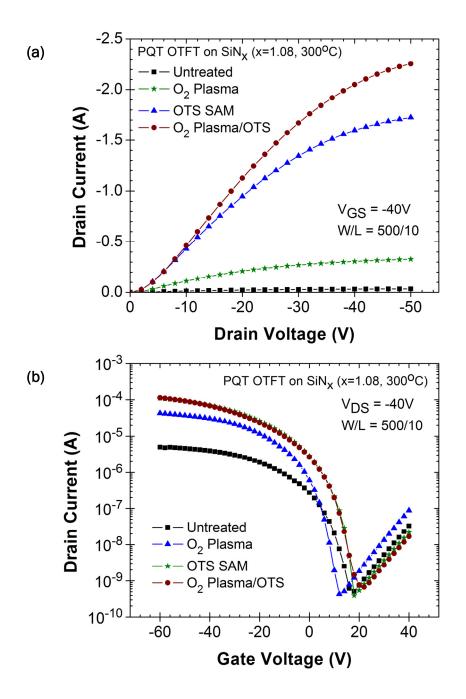

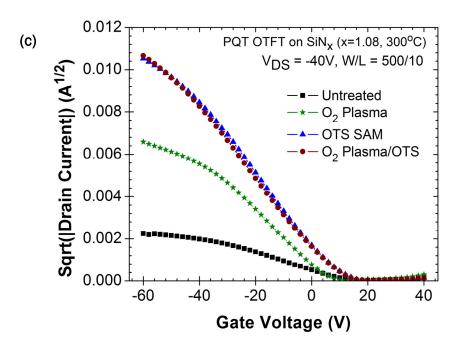

| Table 5.4. Changes in threshold voltage $V_{\rm T}$ , switch-on voltage $V_{\rm SO}$ , and inverse subthreshold slope $S$ of OTFTs with different dielectric surface treatments. Data are extracted from PQT-12 OTFTs on 300°C SiN <sub>x</sub> (x = 1.08) gate dielectric, with $W/L = 500 \ \mu \text{m} / 10 \ \mu \text{m}$ , in the saturation region ( $V_{\rm DS} = -40 \text{V}$ ) (see Figure 5.5). | 2   |

| Table 5.5. Comparison of effective field-effect mobility, contact angle and surface roughness for samples with different dielectric surface treatment. Data shown is obtained by averaging results from a number of samples.                                                                                                                                                                                 |     |

| Table 5.6. Various $O_2$ plasma recipes used in this experiment, with chamber pressure at 150 mTorr, and $O_2$ gas flow rate at 30 sccm. RIE and ICP is abbreviation for reactive ion etching and inductively coupled plasma, respectively. DC bias directly controls the RIE power.                                                                                                                         | 84  |

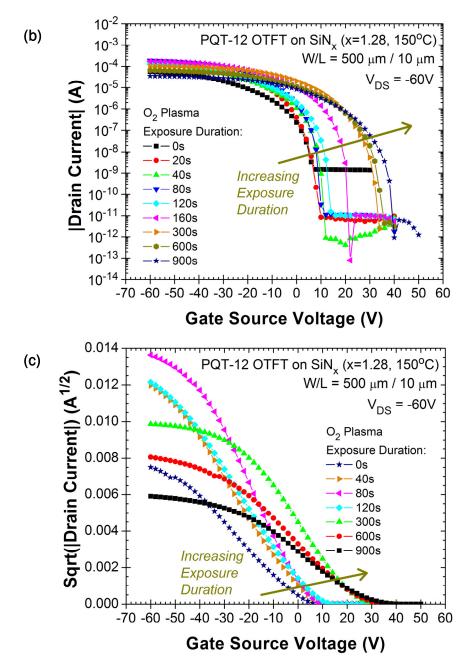

| Table 5.7. OTFT device parameters as a function of $O_2$ plasma exposure duration. Data are extracted from PQT-12 OTFTs on 150°C SiN <sub>x</sub> (x = 1.28) gate dielectric, with $W/L = 500$ $\mu$ m / 10 $\mu$ m, in the saturation region ( $V_{DS} = -60$ V) (refer to Figure 5.12)                                                                                                                     |     |

| Table 5.8. Summary of the impact of O <sub>2</sub> plasma exposure duration and RIE power on surface properties of SiN <sub>x</sub> and on OTFT device mobility. t* denotes the "turnaround point", defined as the exposure duration that generated maximum effective mobility                                                                                                                               | :03 |

| Table 5.9. Summary of key observations from dielectric interface engineering experiments2                                                                                                                                                                                                                                                                                                                    | .04 |

| Table 6.1. Source contact resistance $R_{\rm S}$ of bottom-contact P3HT and F8T2 OTFTs made with different metal contacts ( $T=300$ K, $V_{\rm GS}=-20$ V). IP <sub>S</sub> is the ionization potential of the semiconductor, $\Phi_{\rm M}$ is the measured work function of the metal, and $\phi_{\rm B}$ is the estimated Schottky barrier height at the metal/organic interface (adapted from [4])       | :09 |

| Table 6.2. Contact-semiconductor interface engineering experiments.                                                                                                                                                                                                                                                                                                                                          | 14  |

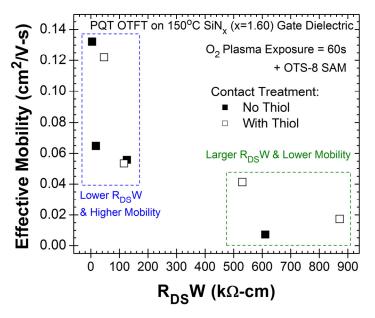

| Table 6.3. Percentage change in mobility and contact resistance for PQT-12 OTFT on 150°C SiN $(x = 1.60)$ , based on data in Figure 6.5 and Figure 6.6, respectively. % Change is calculated as "(Thiol – NoThiol)/NoThiol"                                                                                                                                                                                  |     |

| Table 6.4. Experiment on execution sequence of OTS and thiol surface treatments                                                                                                                                                                                                                                                                                                                              |     |

| Table 6.5. | Summary of key observations from contact interface engineering experiments                                                                               | 232 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            | A concise comparison of OTFT characteristics demanded by various applications. ost critical parameter(s) in each application is identified by the symbol |     |

| Table 7.2. | Calculation of maximum intrinsic switching frequency for OTFTs                                                                                           | 237 |

| Table 7.3. | Reported display prototypes using OTFTs [12].                                                                                                            | 240 |

| Table 7.4. | Frequency bands and applications of RFID systems [20].                                                                                                   | 241 |

| Table 9.1. | Summary of research contributions of this Ph.D. thesis.                                                                                                  | 274 |

# **List of Figures**

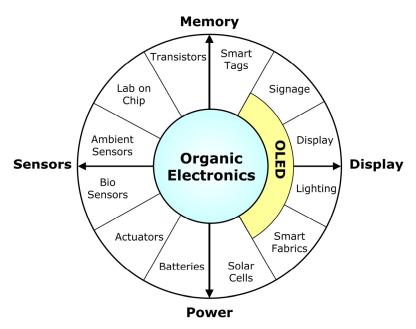

| Figure 1.1. | A broad range products and technologies inspired by organic electronics [2]                                                                                                                                                                                                                                                                                                          |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. | Examples of commercial opportunities for OTFTs.                                                                                                                                                                                                                                                                                                                                      |

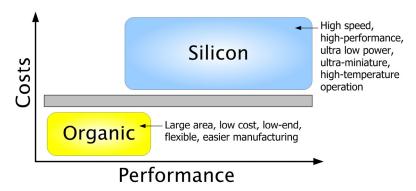

|             | Pictorial illustration on cost versus performance comparison between silicon hnology and organic semiconductor technology                                                                                                                                                                                                                                                            |

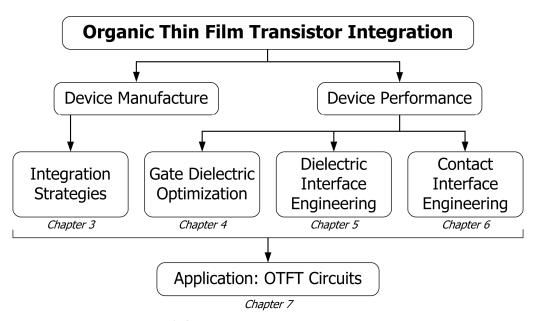

| Figure 1.4. | Flow chart on thesis organization.                                                                                                                                                                                                                                                                                                                                                   |

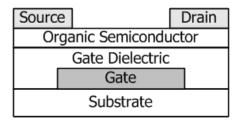

| Figure 2.1  | Cross section of a basic OTFT structure, in bottom-gate and top-contact configuration.                                                                                                                                                                                                                                                                                               |

|             | Chemical structure of three conjugated polymers: (a) polyacetylene, (b) polythiophene (c) polyphenylenevinylene [7].                                                                                                                                                                                                                                                                 |

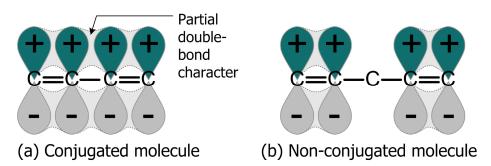

| Figure 2.3. | (a) Conjugated and (b) non-conjugated structure of an organic molecule [8]                                                                                                                                                                                                                                                                                                           |

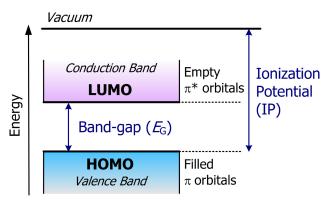

| Figure 2.4. | Representative energy band diagram of an organic semiconductor                                                                                                                                                                                                                                                                                                                       |

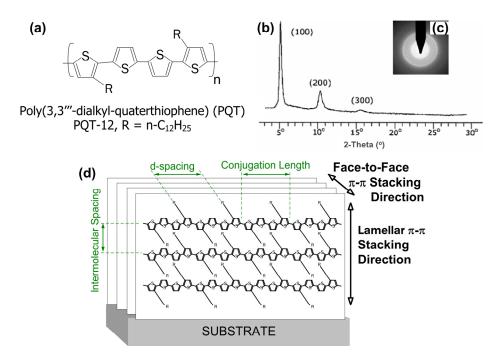

| trai        | (a) Chemical structure of PQT-12 organic semiconductor. (b) GIXRD and (c) as mission electron diffraction pattern of a PQT-12 film. (d) Schematic illustration of nellar $\pi$ - $\pi$ stacking in a PQT-12 film (adapted from [15])                                                                                                                                                 |

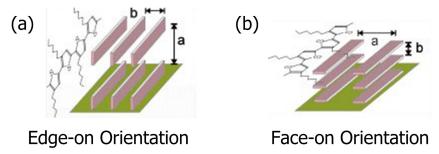

| •           | Two different orientations of ordered P3HT domains with respect to the dielectric estrate surface (adapted from [12])2                                                                                                                                                                                                                                                               |

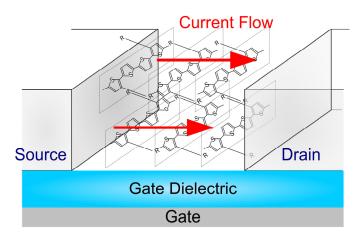

| -           | Schematics of ideal alignment of organic semiconductor building blocks with strong $\pi$ tacking in a TFT configuration (adapted from [13])2                                                                                                                                                                                                                                         |

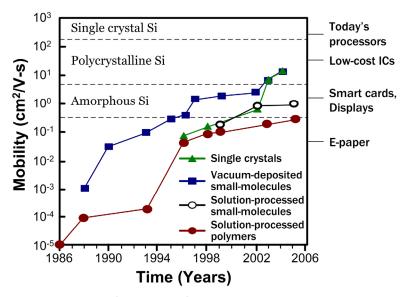

| Figure 2.8. | Progress in the performance of organic semiconductors (adapted from [3][18])2                                                                                                                                                                                                                                                                                                        |

| Figure 2.9. | (a) Two types of arrangements for P3HT. (b) Head-to-tail regionegular P3HT [19]2                                                                                                                                                                                                                                                                                                     |

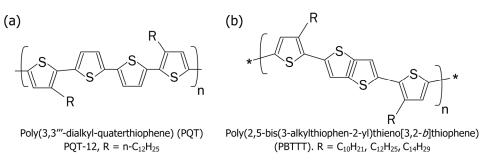

| Figure 2.10 | Chemical structure of (a) PQT and (b) PBTTT [15][31]2                                                                                                                                                                                                                                                                                                                                |

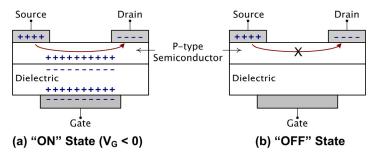

| Figure 2.11 | . Simplified illustration of the operation of a TFT with p-type semiconductor [7]3                                                                                                                                                                                                                                                                                                   |

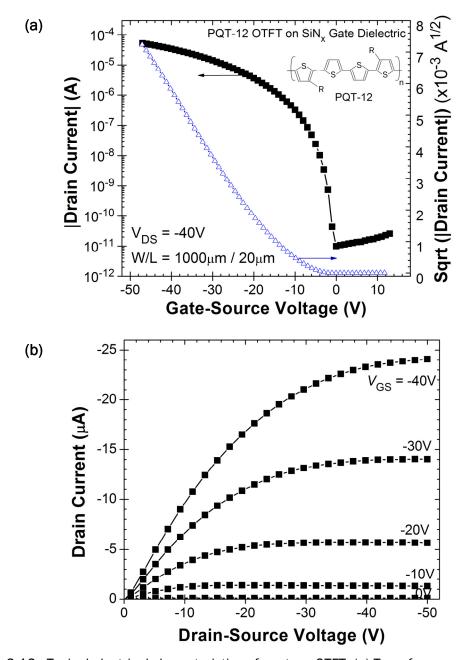

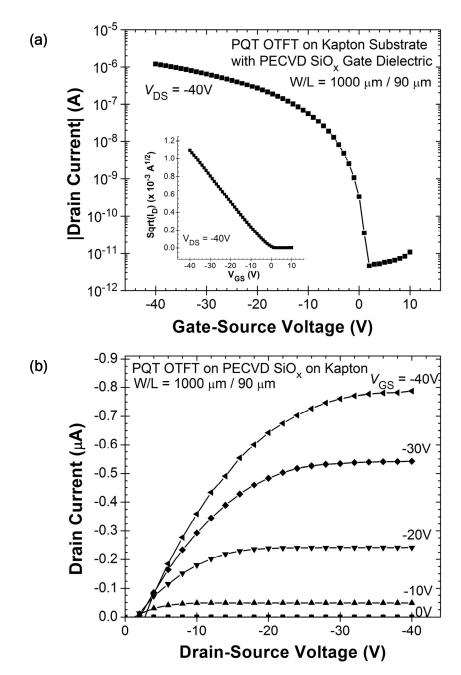

| sat<br>The  | Typical electrical characteristics of a p-type OTFT. (a) Transfer curve $(I_D-V_{GS})$ in the uration regime $(V_{DS}=-40\text{V})$ , and (b) output curves $(I_D-V_{DS})$ at different gate voltages. The device shown here is PQT-12 OTFT on PECVD SiN <sub>x</sub> gate dielectric. Inset of (a) was molecular structure of PQT-12, which serves as semiconductor in the device3. |

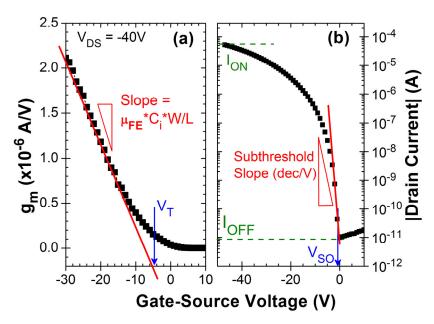

|             | . Extraction of OTFT device from electrical characteristics: (a) $g_m$ - $V_{GS}$ plot for racting $\mu_{FE}$ and $V_T$ , and (b) $I_D$ - $V_{GS}$ plot for deducing $I_{ON}/I_{OFF}$ and subthreshold slope3                                                                                                                                                                        |

|               | $V_{\rm GS}$ for an OTFT at a given $V_{\rm DS}$ , to extract $A$ and $B$ . (b) Exemplary plot of $B$ vs. $A$ at a given $V_{\rm DS}$ , to extract $A$ and $A$                                                                                                                                                                                                                                                                                                                                                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

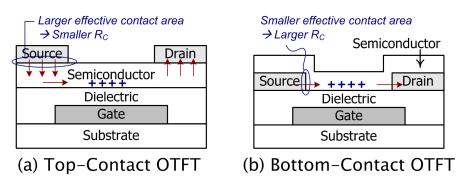

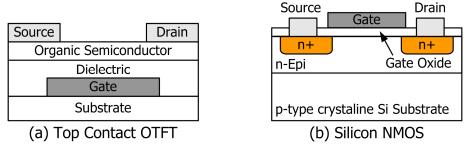

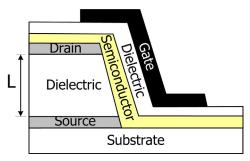

| •             | 2.15. Cross section of two bottom-gate OTFT configurations: (a) top-contact and (b) bottom-contact                                                                                                                                                                                                                                                                                                                                                                                                             |

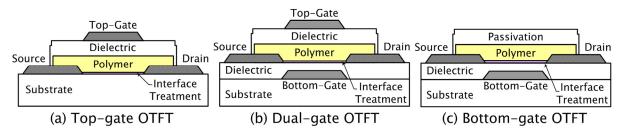

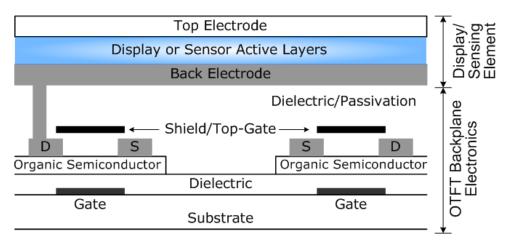

|               | 2.16. Cross-section of (a) top-gate, (b) dual-gate, and (c) bottom-gate OTFTs. Devices shown are in bottom-contact configuration                                                                                                                                                                                                                                                                                                                                                                               |

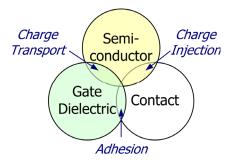

| Figure 2      | 2.17. Interaction between the three key device layers in an OTFT                                                                                                                                                                                                                                                                                                                                                                                                                                               |

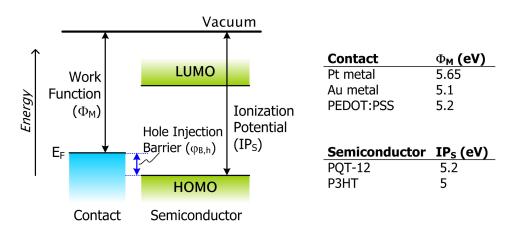

|               | 2.18. Energy band diagram at the contact-semiconductor interface, illustrating the concept of work function $(\Phi_M)$ , ionization potential (IP) and injection barrier $(\phi_B)$ at the contact. Representative values for p-type polymer semiconductor and contact material are shown.51                                                                                                                                                                                                                   |

| -             | 6.1. Cross sectional diagram of (a) top-contact OTFT and (b) silicon n-type MOSFET (NMOS)                                                                                                                                                                                                                                                                                                                                                                                                                      |

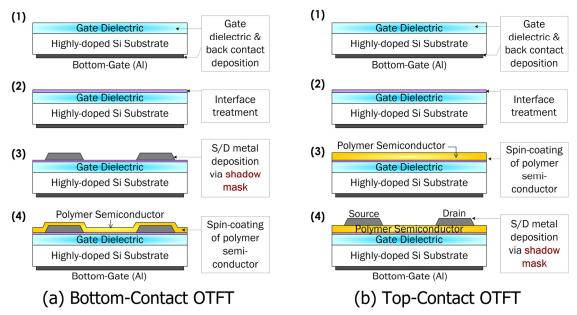

| $\mathcal{L}$ | 2.2. Fabrication sequence of bottom-gate OTFT by the shadow mask patterning approaches, for (a) bottom-contact and (b) top-contact configuration                                                                                                                                                                                                                                                                                                                                                               |

| _             | .3. Illustration of individually addressable gates on the same substrate, which is a basic requirement to enable circuit implementation                                                                                                                                                                                                                                                                                                                                                                        |

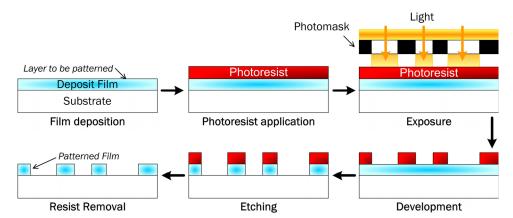

|               | .4. Basic photolithography process: the exposure and etching process that allows one to transfer a pattern to the film/wafer                                                                                                                                                                                                                                                                                                                                                                                   |

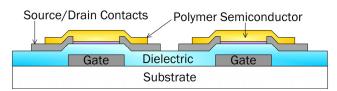

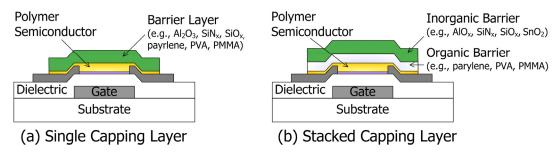

|               | 5.5. Cross section illustration of OTFTs with (a) single capping layer, and (b) stacked inorganic-organic capping layers                                                                                                                                                                                                                                                                                                                                                                                       |

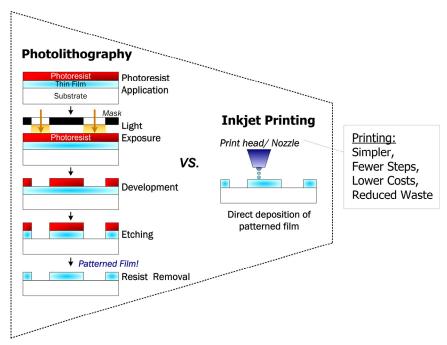

| Figure 3      | 6.6. Comparison on the process complexity of photolithography and inkjet printing78                                                                                                                                                                                                                                                                                                                                                                                                                            |

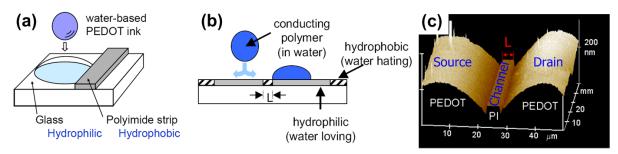

|               | i.7. Surface-energy-assisted inkjet printing to improve image resolution. (a) Schematic view of inkjet deposition of PEDOT solution along the hydrophobic PI strip. (b) Control of ink spreading by a "dewetting pattern" of hydrophobic lines that confines the organic ink to specific hydrophilic regions on the surfaces. (c) Topographic AFM image of the transistor channel defined by PI, and the PEDOT source and drain electrodes. The width of the strip (channel length) is 5 μm (adapted from [6]) |

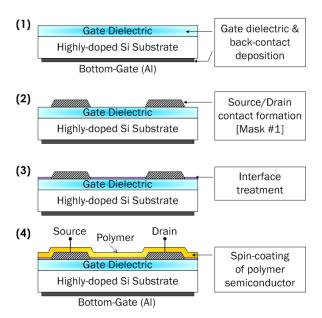

|               | s.8. Fabrication sequence of bottom-gate bottom-contact OTFT on highly-doped Si substrate with a 1-mask patterning step to define the source/drain contacts (by photolithography or shadow mask).                                                                                                                                                                                                                                                                                                              |

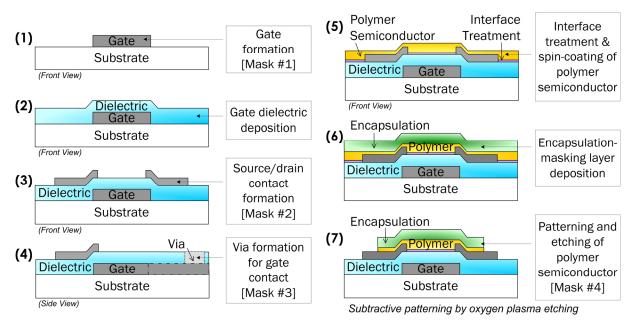

|               | 9.9. Fabrication sequence of fully-patterned fully encapsulated bottom-gate bottom-contact OTFT by a 4-mask photolithography process                                                                                                                                                                                                                                                                                                                                                                           |

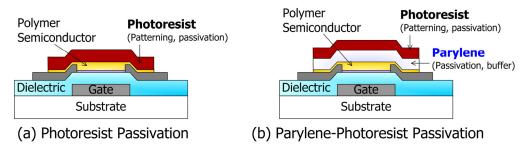

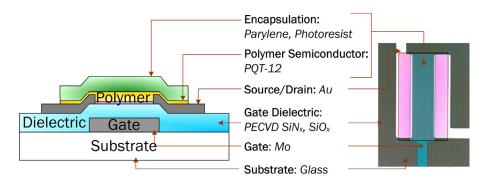

|               | 2.10. Two photolithographically-defined bottom-gate OTFT structures with (a) photoresist passivation and (b) parylene-photoresist passivation                                                                                                                                                                                                                                                                                                                                                                  |

|               | 1.11. Cross section illustration and photograph of a fully-patterned OTFT fabricated using 4-mask photolithography scheme with parylene-photoresist passivation                                                                                                                                                                                                                                                                                                                                                |

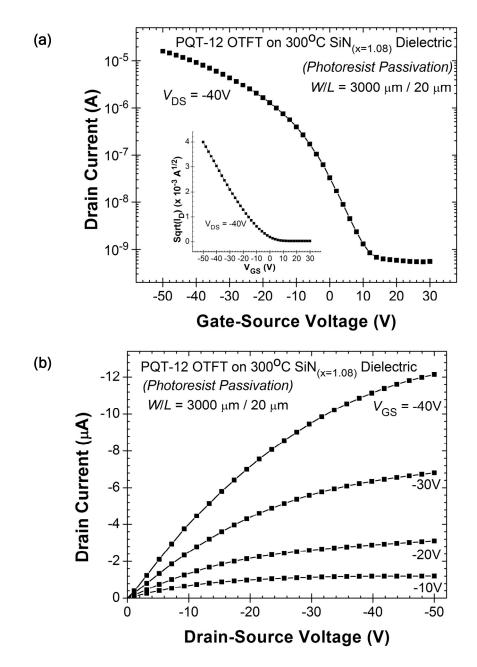

| _             | 6.12. (a) Transfer and (b) output characteristics of a fully-patterned bottom-gate bottom-contact PQT-12 OTFT with SiN <sub>x</sub> gate dielectric on glass substrate. Polymer semiconductor layer was directly patterned using photolithographically, with direct deposition of photoresist on PQT-12 layer90                                                                                                                                                                                                |

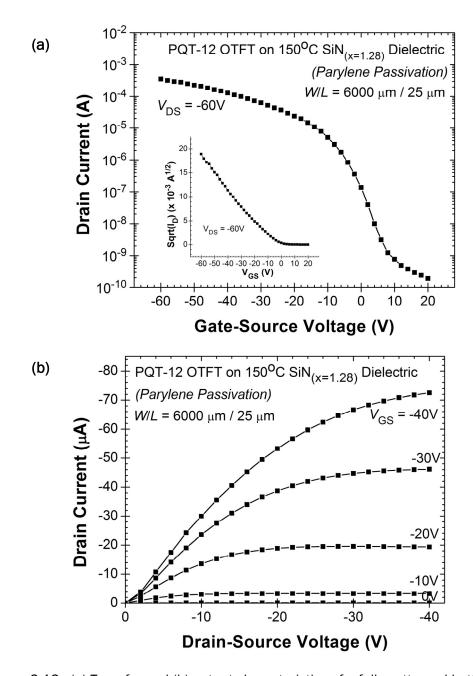

| Figure | 3.13. (a) Transfer and (b) output characteristics of a fully-patterned bottom-gate bottom-contact PQT-12 OTFT with SiN <sub>x</sub> gate dielectric on glass substrate. Polymer semiconductor layer was photolithographically patterned with parylene passivation layer91                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

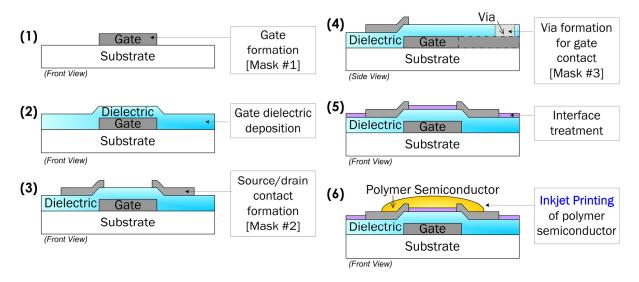

| Figure | 3.14. Hybrid photolithography-inkjet printing fabrication scheme for fully-patterned bottom-gate bottom-contact OTFT                                                                                                                                                                                                                |

| Figure | 3.15. Cross section illustration and photograph of a fully-patterned OTFT fabricated using hybrid photolithography-inkjet printing scheme93                                                                                                                                                                                         |

| Figure | 3.16. (a) Transfer and (b) output characteristics of a fully-patterned bottom-gate bottom-contact PQT-12 OTFT with SiN <sub>x</sub> gate dielectric on glass substrate. Organic semiconductor layer was deposited by inkjet printing94                                                                                              |

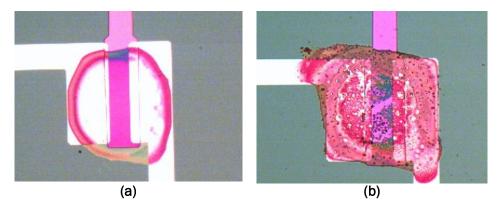

| Figure | 3.17. Photograph of OTFTs with inkjet printed organic semiconductor showing (a) a thin uniform layer and (b) a thicker non-uniform layer95                                                                                                                                                                                          |

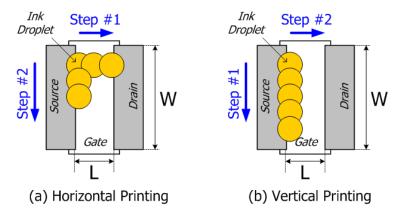

| Figure | 3.18. Illustration of inkjet printing direction: (a) horizontal and (b) vertical printing95                                                                                                                                                                                                                                         |

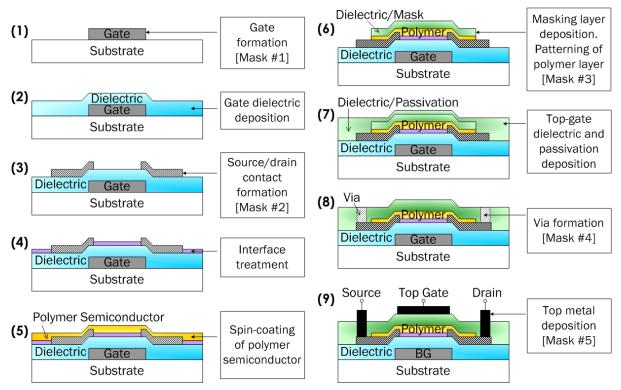

| Figure | 3.19. Fabrication sequence of dual-gate OTFT by a 5-mask photolithography process. Top-gate OTFT can be fabricated by excluding steps (1), (8) and (9)97                                                                                                                                                                            |

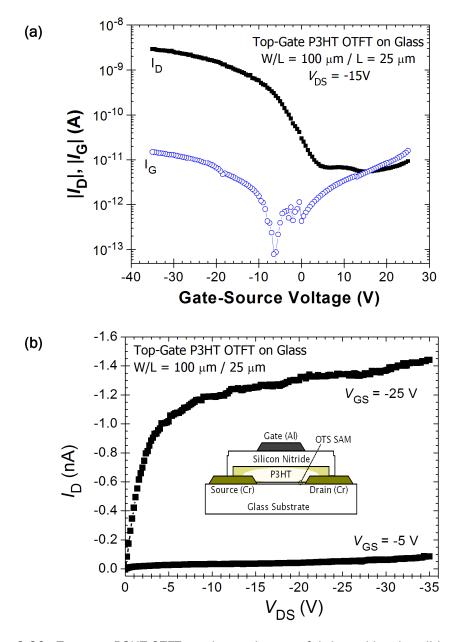

| Figure | 3.20. Top-gate P3HT OTFT on glass substrate, fabricated by photolithography. (a) Transfer characteristics ( $I_D$ - $V_{GS}$ ). (b) Output characteristics ( $I_D$ - $V_{DS}$ )                                                                                                                                                     |

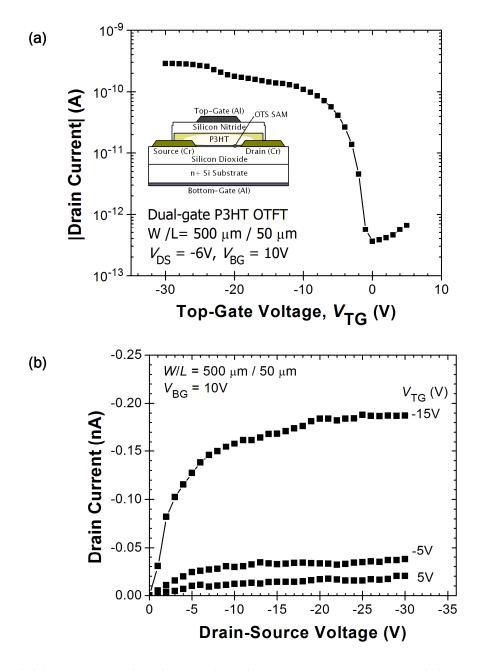

| Figure | 3.21. Dual-gate P3HT OTFT on Si wafer. Bottom-gate dielectric is $SiO_2$ , and top-gate dielectric is PECVD $SiN_x$ . (a) Transfer characteristics ( $I_D$ - $V_{TG}$ ) of the dual-gate OTFT as a function of top-gate voltage. (b) Output characteristics ( $I_D$ - $V_{DS}$ ) of the dual-gate OTFT at various top-gate voltages |

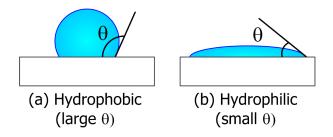

| Figure | 4.1. Contact angle $(\theta)$ of surfaces with different wettability: (a) water droplet on a hydrophobic surface showing large contact angle, and (b) water droplet on a hydrophilic surface showing small contact angle.                                                                                                           |

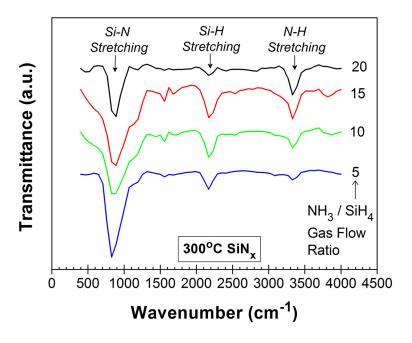

| Figure | 4.2. Fourier transform infrared (FTIR) spectroscopy of the 300°C PECVD SiN <sub>x</sub> films117                                                                                                                                                                                                                                    |

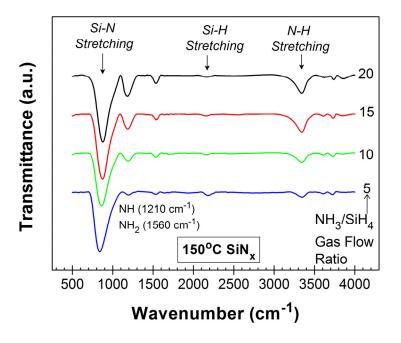

| Figure | 4.3. Fourier transform infrared (FTIR) spectroscopy of the 150°C PECVD SiN <sub>x</sub> films117                                                                                                                                                                                                                                    |

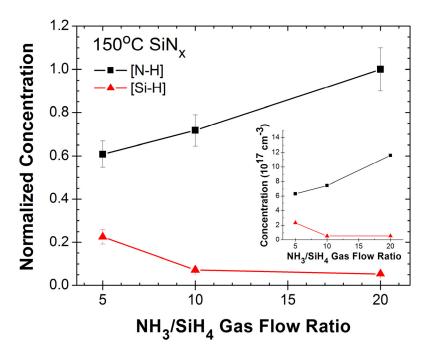

| Figure | 4.4. Normalized N-H and Si-H bond concentration as a function of NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio for SiN <sub>x</sub> films deposited at 150°C. Data is normalized to [N-H] value for the sample deposited with NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio of 20.                                            |

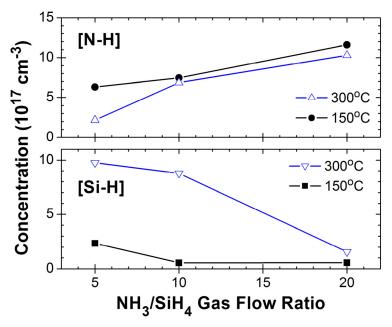

| Figure | 4.5. N-H and Si-H bond concentration as a function of $NH_3/SiH_4$ gas flow ratio for $SiN_x$ films deposited at substrate temperatures of 150°C and 300°C119                                                                                                                                                                       |

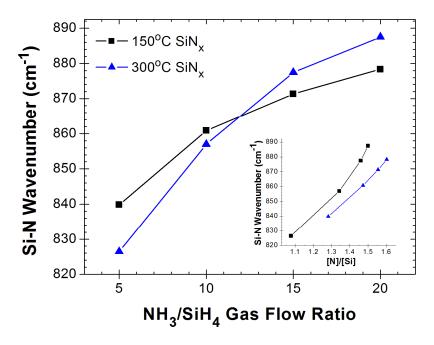

| Figure | 4.6. Wavenumber of the Si-N stretching band as a function of NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio for PECVD SiN <sub>x</sub> films. Inset plots the changes in Si-N wavenumber versus [N]/[Si] ratio of the films.                                                                                                      |

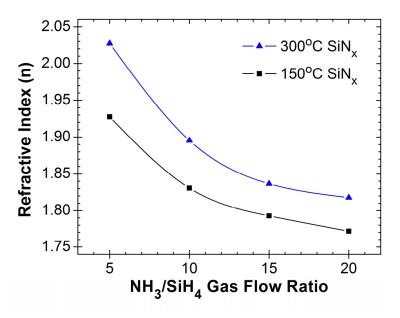

| Figure | 4.7. Refractive index at wavelength of 637 nm as a function of NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio for 300°C and 150°C SiN <sub>x</sub> samples                                                                                                                                                                        |

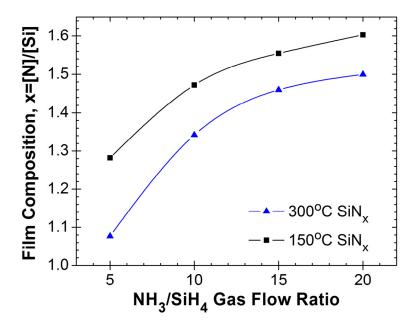

| Figure | 4.8. Nitrogen to silicon ratio ([N]/[Si]) of the 300°C $SiN_x$ and 150°C $SiN_x$ films as a function of gas flow ratio                                                                                                                                                                                                              |

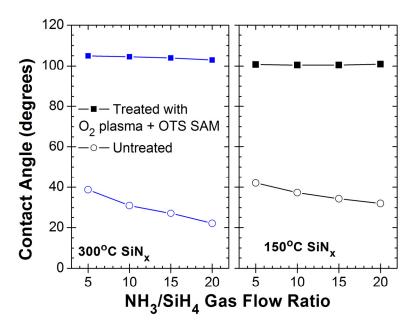

| Figure 4.9. Water contact angle of $SiN_x$ surface before ( $\bigcirc$ ) and after ( $\blacksquare$ ) surface treatment with oxygen plasma and OTS SAM, for four different $SiN_x$ films (denoted by $NH_3/SiH_4$ gas flow ratios)                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

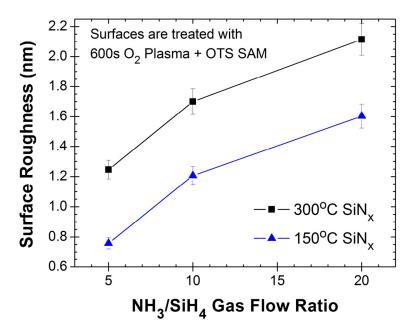

| Figure 4.10. Surface roughness of 150°C and 300°C $SiN_x$ films as a function of $NH_3/SiH_4$ gas flow ratios, after surface treatment with $O_2$ plasma and OTS SAM                                                                                                                                                                                                                                          |

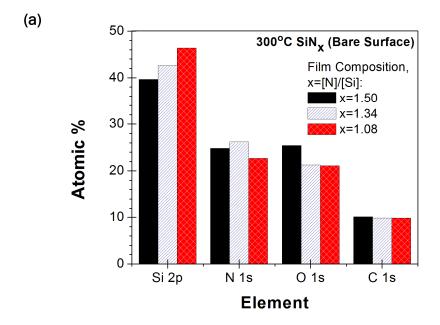

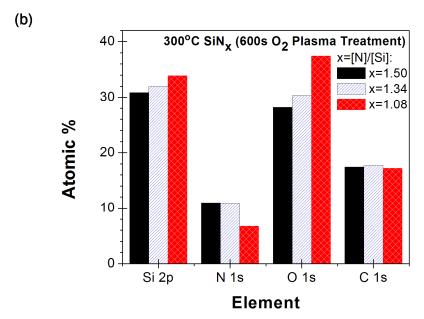

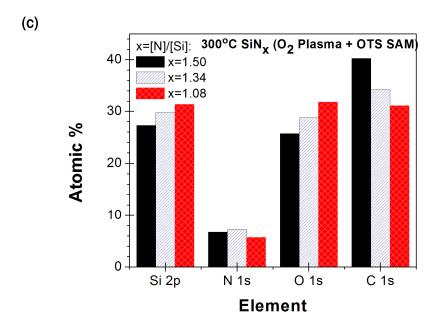

| Figure 4.11. Chemical composition of three different $300^{\circ}\text{C SiN}_x$ films ( $x = 1.50, 1.34, 1.08$ ), plotted as atomic distribution at the film surface as measured by XPS. Three surface conditions were considered for each of the $300^{\circ}\text{C SiN}_x$ films: (a) as-deposited (bare) surface, (b) $O_2$ plasma treated surface, and (c) $O_2$ plasma and OTS SAM treated surface 128 |

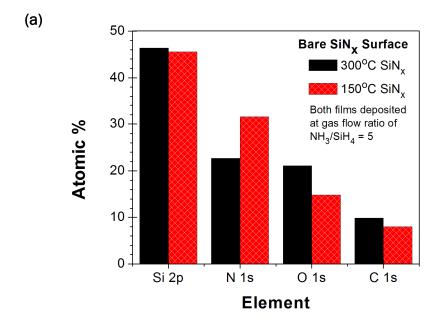

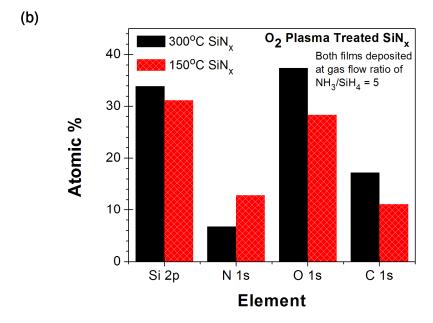

| Figure 4.12. XPS measurement comparing chemical composition of silicon-rich 300°C and 150°C $SiN_x$ films deposited at gas flow ratio of $NH_3/SiH_4 = 5$ . Two surface conditions are considered: (a) as-deposited (bare) and (b) $O_2$ plasma treated surface                                                                                                                                               |

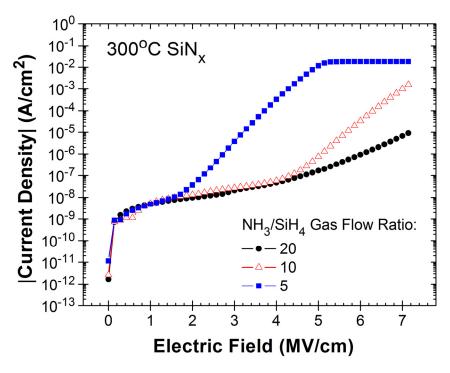

| Figure 4.13. Leakage current density as a function of electric field for $300^{\circ}\text{C SiN}_{x}$ dielectrics deposited at various NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio. The film thickness is approximately 300 nm. Measurements were performed using MIS capacitor structure                                                                                                               |

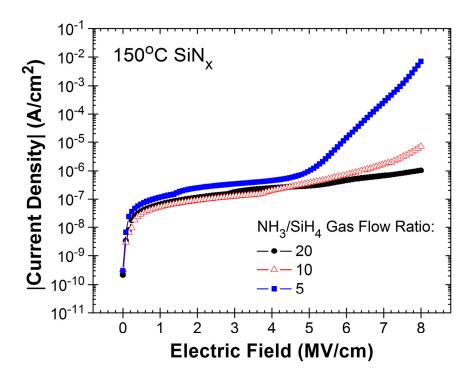

| Figure 4.14. Leakage current density as a function of electric field for $150^{\circ}\text{C SiN}_x$ dielectrics deposited at various NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio. The film thickness is approximately 300 nm. Measurements were performed using MIS capacitor structure                                                                                                                 |

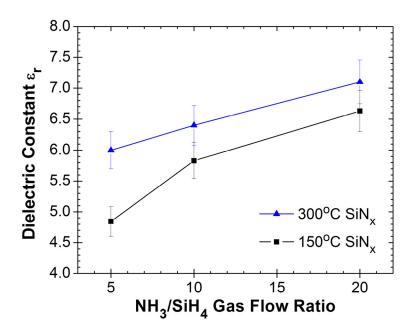

| Figure 4.15. Dielectric constant ( $\varepsilon_r$ ) for $SiN_x$ films as a function of $NH_3/SiH_4$ gas flow ratio 132                                                                                                                                                                                                                                                                                       |

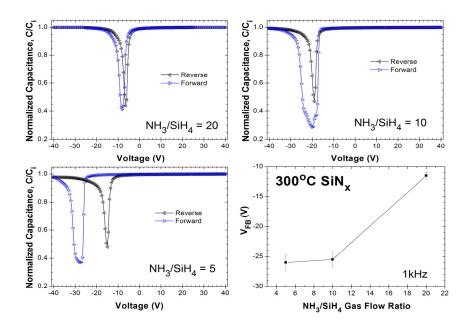

| Figure 4.16. $C\text{-}V$ characteristics of various 300°C SiN $_x$ dielectrics at 1kHz, in both forward (negative to positive) and reverse (positive to negative) sweep directions. Flatband voltage ( $V_{\text{FB}}$ ) is extracted from forward curves and is plotted as a function of NH $_3$ /SiH $_4$ gas flow ratio                                                                                   |

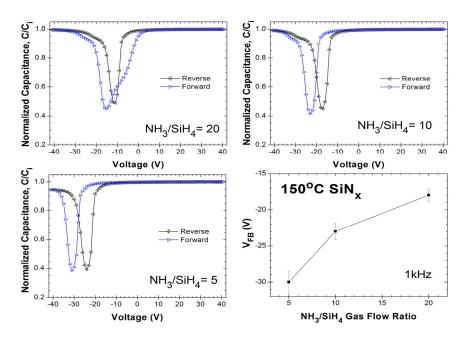

| Figure 4.17. <i>C-V</i> characteristics of various 150°C SiN <sub>x</sub> dielectrics at 1kHz, in both forward (negative to positive) and reverse (positive to negative) sweep directions. Flatband voltage ( <i>V</i> <sub>FB</sub> ) is extracted from forward curves and is plotted as a function of NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio                                                      |

| Figure 4.18. Chemical structure of poly(3,3"'-dialkylquarterthiophene) (PQT). In the case of PQT-12, alkyl side chain is $R = n-C_{12}H_{25}$ . (Adapted from [28].)                                                                                                                                                                                                                                          |

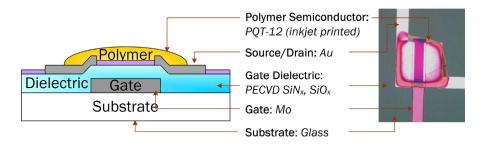

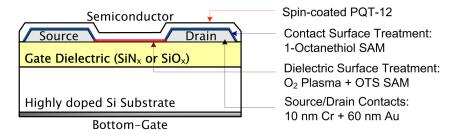

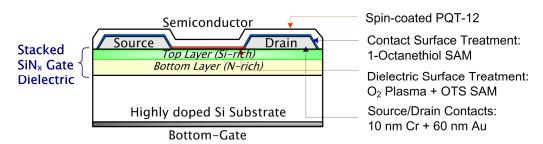

| Figure 4.19. Schematic cross-section of the OTFT structure considered in this study                                                                                                                                                                                                                                                                                                                           |

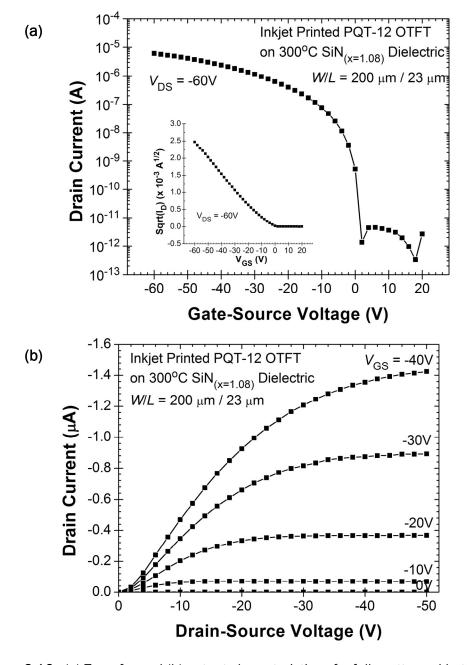

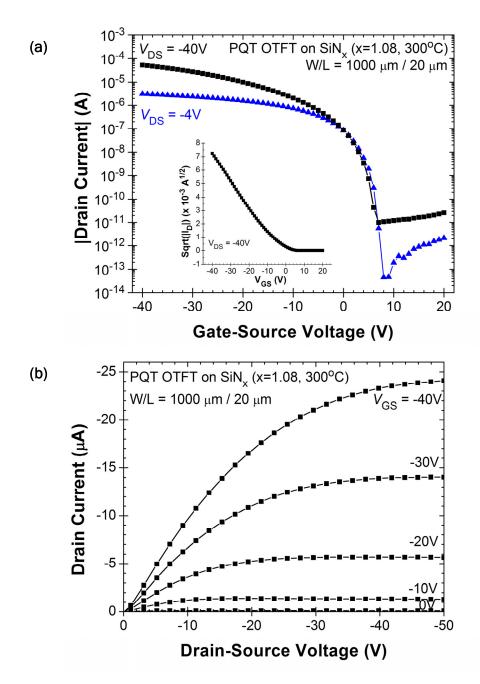

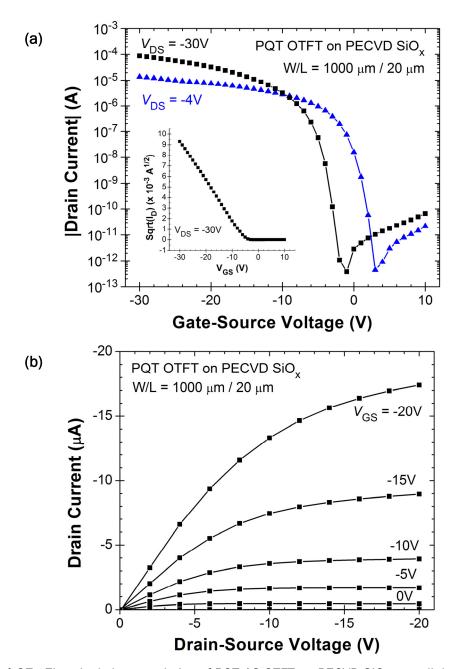

| Figure 4.20. Electrical characteristics of PQT-12 OTFT on 300°C SiN <sub>x</sub> ( $x$ = 1.08) gate dielectric with $W/L$ = 1000 $\mu$ m / 20 $\mu$ m: (a) Transfer characteristics (log  $I_D$  - $V_{GS}$ ) and (b) output characteristics ( $I_D$ - $V_{DS}$ ). Inset of (a) shows a well-behaved linear plot of $\sqrt{I_D}$ – $V_{GS}$ in the                                                            |

| saturation regime                                                                                                                                                                                                                                                                                                                                                                                             |

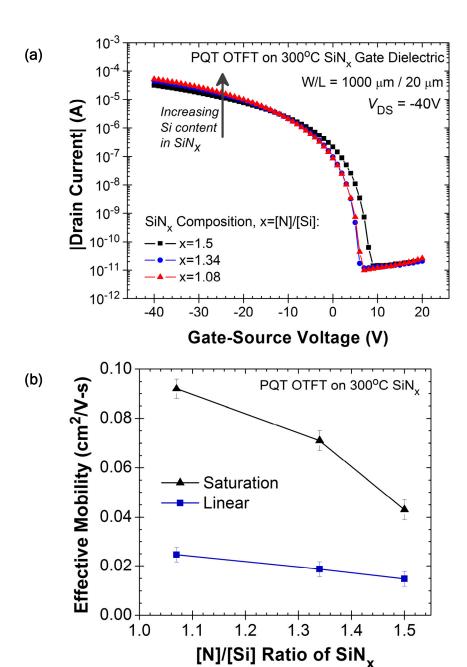

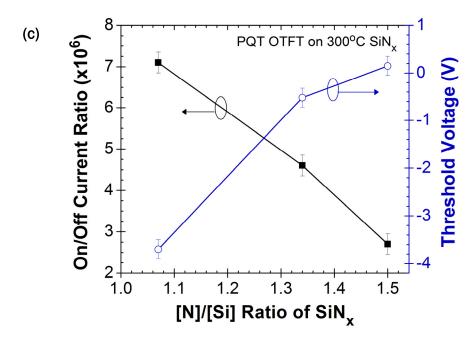

| Figure 4.21. Comparison of PQT-12 OTFT characteristics on 300°C SiN <sub>x</sub> gate dielectric of varying film composition. (a) Transfer characteristics, (b) effective field-effect mobility, (c) on/off current ratio and threshold voltage as a function of the [N]/[Si] ratio of SiN <sub>x</sub> film.                                                                                                 |

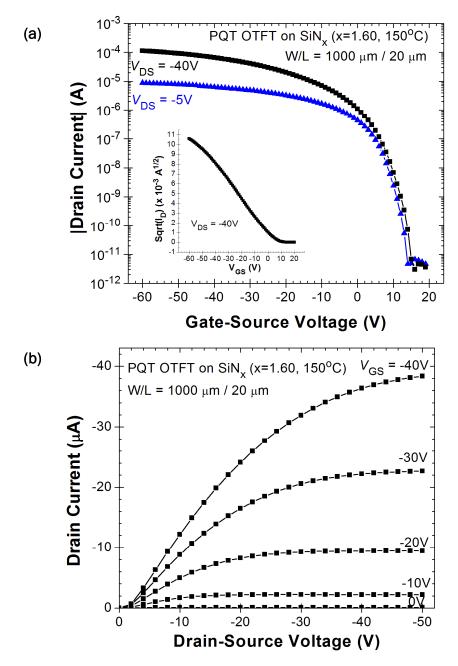

| Figure 4.22. Electrical characteristics of PQT-12 OTFT on 150°C PECVD SiN <sub>x</sub> ( $x = 1.60$ ) gate dielectric with $W/L = 1000 \mu \text{m} / 20 \mu \text{m}$ : (a) transfer characteristics (log  $I_D$  - $V_{GS}$ ) and (b)                                                                                                                                                                       |

| output characteristics ( $I_D$ - $V_{DS}$ ). Inset of (a) shows a well-behaved linear plot of $\sqrt{I_D}$ – $V_{GS}$ in the saturation regime.                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

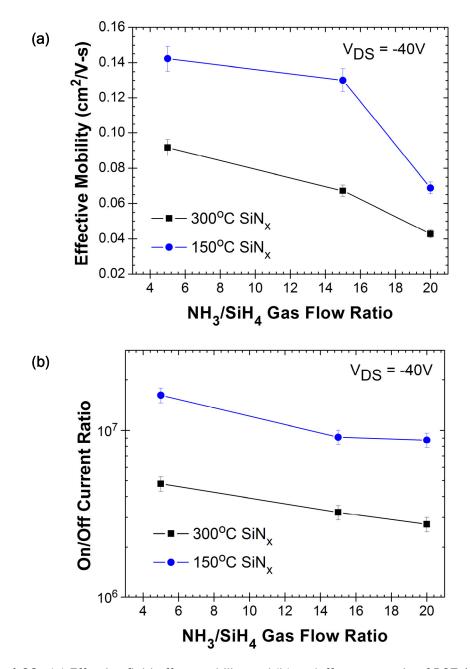

| Figure 4.23. (a) Effective field-effect mobility and (b) on/off current ratio of PQT-12 OTFT ( $W/L$ = 1000 $\mu$ m / 20 $\mu$ m) plotted as a function of NH <sub>3</sub> /SiH <sub>4</sub> gas flow ratio for 150°C and 300°C SiN <sub>x</sub> gate dielectric. Data corresponds to measurements in saturation ( $V_{DS}$ = -40V) region. |

| Figure 4.24. Schematic cross-section of the OTFT structure with stacked SiN <sub>x</sub> gate dielectric145                                                                                                                                                                                                                                 |

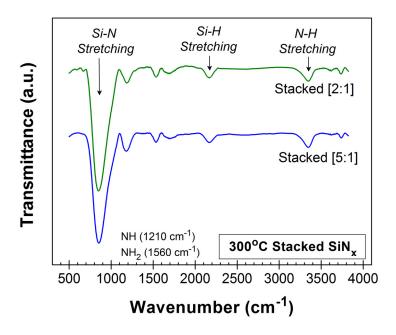

| Figure 4.25. Fourier transform infrared (FTIR) spectroscopy of the stacked SiN <sub>x</sub> films, deposited by PECVD at substrate temperature of 300°C146                                                                                                                                                                                  |

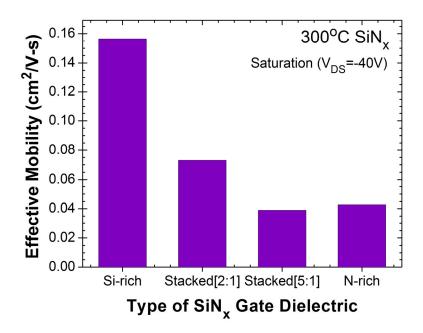

| Figure 4.26. Effective field-effect mobility of PQT-12 OTFT with stacked $SiN_x$ gate dielectrics. Mobility of OTFT with Si-rich $SiN_x$ ( $x = 1.08$ ) and N-rich $SiN_x$ ( $x = 1.50$ ) is also shown for comparison                                                                                                                      |

| Figure 4.27. Electrical characteristics of PQT-12 OTFT on PECVD SiO <sub>x</sub> gate dielectric with $W/L$ = 1000 $\mu$ m / 20 $\mu$ m: (a) transfer characteristics (log  $I_D$  - $V_{GS}$ ) and (b) output characteristics ( $I_D$ - $V_{DS}$ ). Inset of (a) shows a linear plot of $\sqrt{I_D}$ - $V_{GS}$ in saturation regime       |

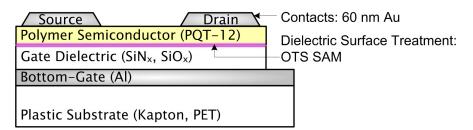

| Figure 4.28. Schematic cross-section of the bottom-gate top-contact OTFT on plastic substrate. 15                                                                                                                                                                                                                                           |

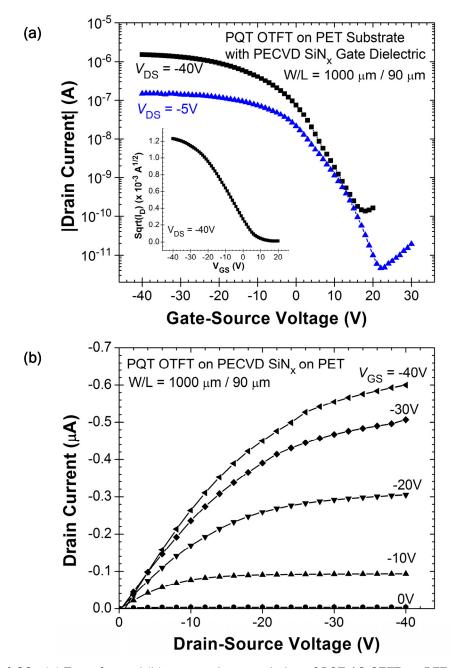

| Figure 4.29. (a) Transfer and (b) output characteristics of PQT-12 OTFT on PET substrate with PECVD $SiN_x$ gate dielectric ( $W/L = 1000 \ \mu m / 90 \ \mu m$ ).                                                                                                                                                                          |

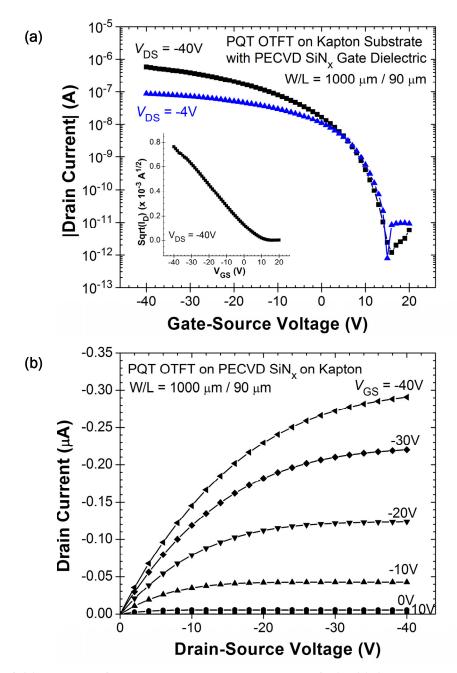

| Figure 4.30. (a) Transfer and (b) output characteristics of PQT-12 OTFT on Kapton substrate with PECVD $SiN_x$ gate dielectric ( $W/L = 1000 \mu m / 90 \mu m$ )                                                                                                                                                                            |

| Figure 4.31. (a) Transfer and (b) output characteristics of PQT-12 OTFT on Kapton substrate with PECVD SiO <sub>x</sub> gate dielectric ( $W/L = 1000  \mu \text{m} / 90  \mu \text{m}$ )                                                                                                                                                   |

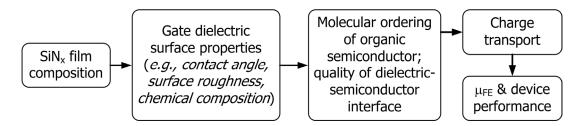

| Figure 4.32. Flowchart illustrating the relationship between SiN <sub>x</sub> film composition, interface properties, and OTFT performance                                                                                                                                                                                                  |

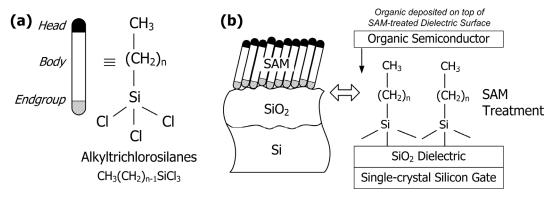

| Figure 5.1. (a) Simplified illustration of three main parts of a SAM system, and (b) the formation of alkylsiloxane SAM by adsorption of alkyltrichlorosilanes from solution on a Si-SiO <sub>2</sub> substrate (adapted from [9])                                                                                                          |

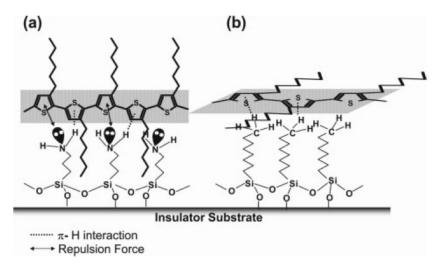

| Figure 5.2. Schematics of different P3HT chain orientations, (a) edge-on and (b) face-on, according to interfacial characteristics (adapted from [12])166                                                                                                                                                                                   |

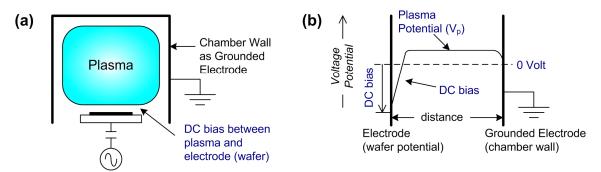

| Figure 5.3. (a) Diagram of a RIE system. (b) Potential distribution as a function of distance between electrodes. Wafer is placed on a smaller electrode, which is biased negatively relative to the plasma. Ions accelerate from plasma to wafer due to a DC bias electric field.                                                          |

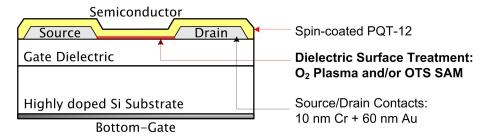

| Figure 5.4. Schematic cross-section of the OTFT structure considered in this dielectric-surface treatment study.                                                                                                                                                                                                                            |

| Figure 5.5. (a) Output and (b,c) transfer characteristics of PQT-12 OTFTs on 300°C PECVD SiN, $(x = 1.08)$ with different dielectric surface treatments. The transfer characteristics are shown on semi-logarithmic scale in (b) and as the square root of the drain current in (c).                                                        |

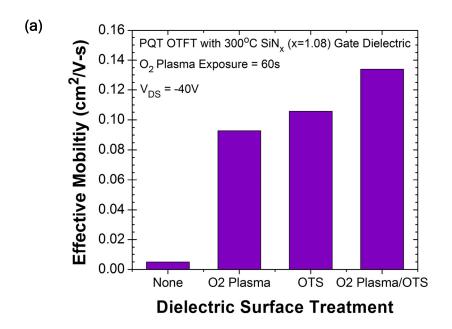

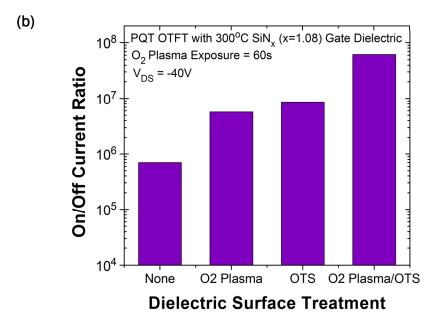

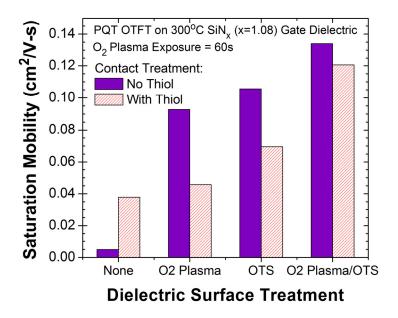

| Figure 5.6. (a) Effective mobility and (b) on/off current ratio of PQT-12 OTFT with SiN <sub>x</sub> gate dielectrics under various dielectric surface treatment conditions. Measurements were collected in saturation region. Each data point corresponds to an average value from three to six devices                                                                                      |

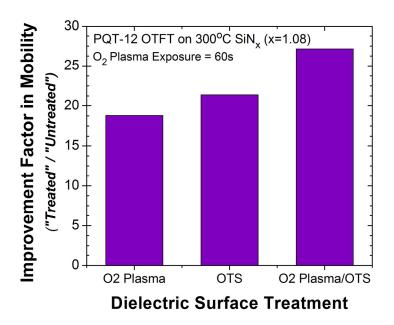

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.7. Factor of improvement in effective mobility, relative to untreated devices, for PQT-12 OTFT after various types of dielectric surface treatments. Measurements were collected in saturation region                                                                                                                                                                                |

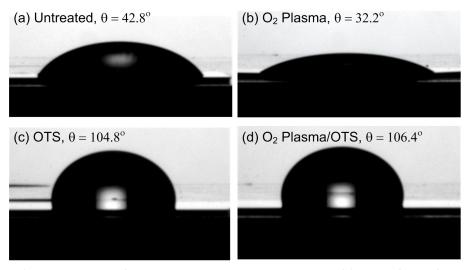

| Figure 5.8. Photographs from contact angle measurement of SiN <sub>x</sub> surface after various dielectric surface treatments                                                                                                                                                                                                                                                                |

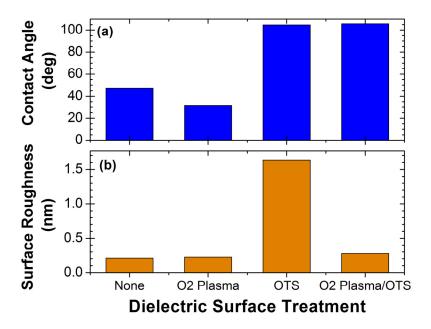

| Figure 5.9. (a) Water contact angle measurement and (b) mean surface roughness of SiN <sub>x</sub> surfaces after various dielectric surface treatments                                                                                                                                                                                                                                       |

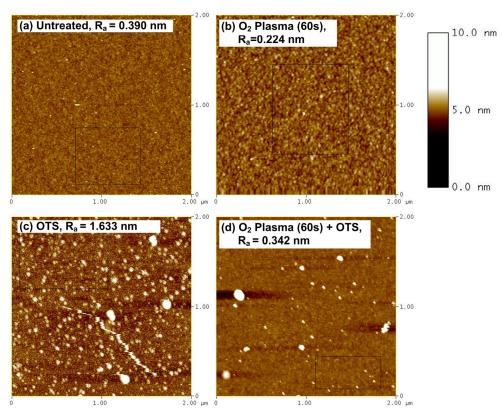

| Figure 5.10. AFM images showing surface topography of $SiN_x$ surface after various dielectric surface treatments. The mean surface roughness ( $R_a$ ) is indicated                                                                                                                                                                                                                          |

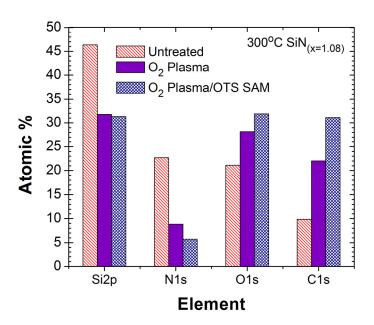

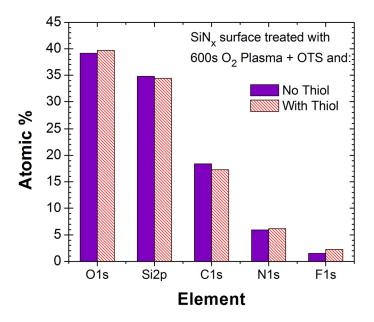

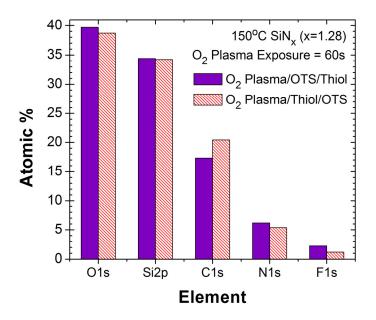

| Figure 5.11. Atomic composition from XPS measurements of SiN <sub>x</sub> surfaces with different surface treatments                                                                                                                                                                                                                                                                          |

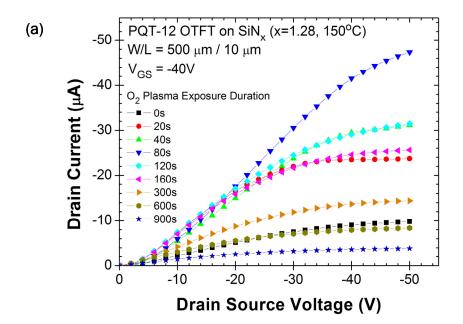

| Figure 5.12. (a) Output characteristics and (b,c) transfer of PQT-12 OTFTs on 150°C PECVD $SiN_x$ ( $x = 1.28$ ) gate dielectric treated with different $O_2$ plasma exposure duration. The transfer characteristics are shown on semi-logarithmic scale in (b) and as the square root of the drain current in (c). All samples were treated with $O_2$ plasma, OTS SAM and 1-Octanethiol SAM |

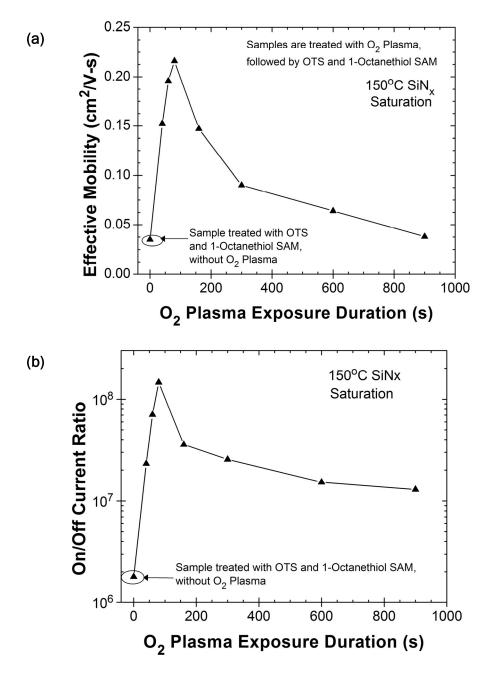

| Figure 5.13. (a) Effective mobility and (b) on/off current ratio as a function of $O_2$ plasma exposure duration of PQT-12 OTFT with 150°C $SiN_x$ ( $x = 1.28$ ) gate dielectric. Data was collected in the saturation region. All samples were treated with $O_2$ plasma, OTS, and 1-octanethiol. Here, each data point corresponds to an average value from three to six devices188        |

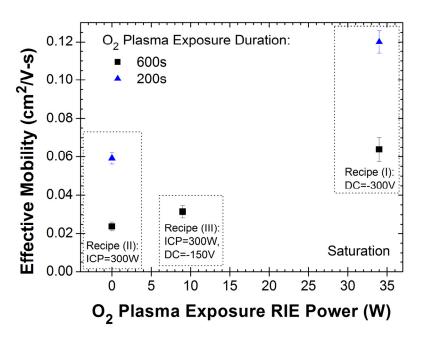

| Figure 5.14. Effective mobility as a function of $O_2$ plasma exposure power of PQT-12 OTFT with $SiN_x$ gate dielectric biased in saturation region. All samples were treated with $O_2$ plasma and OTS SAM                                                                                                                                                                                  |

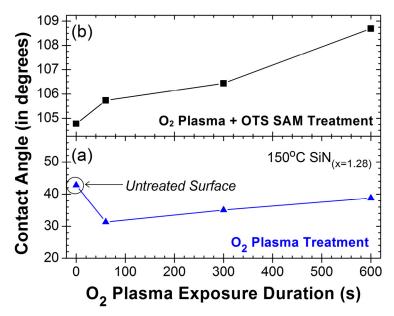

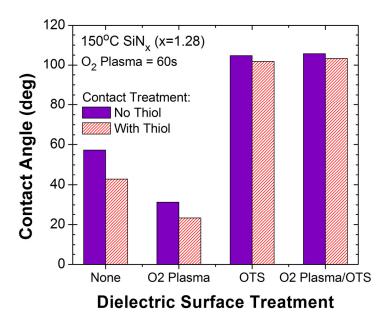

| Figure 5.15. Water contact angle of 150°C $SiN_x$ (x = 1.28) surface treated with (a) $O_2$ plasma only and (b) $O_2$ plasma/OTS SAM, as a function of $O_2$ plasma exposure duration                                                                                                                                                                                                         |

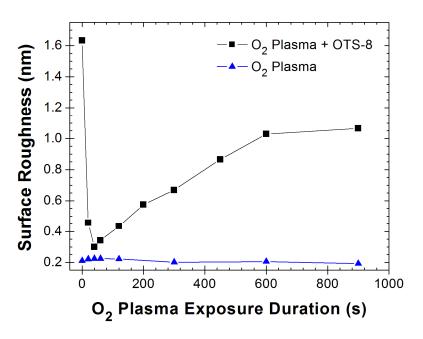

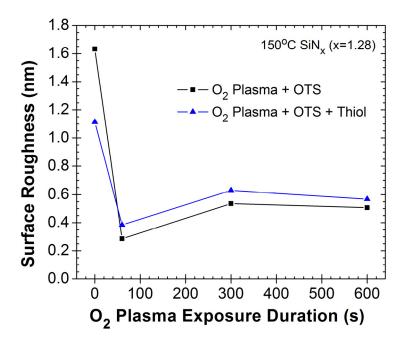

| Figure 5.16. Surface roughness as a function of $O_2$ plasma exposure duration for $SiN_x$ surface treated with $O_2$ plasma and OTS SAM. Measurements performed using tapping-mode AFM. These samples are treated with $O_2$ plasma Recipe (I) in Table 5.6                                                                                                                                  |

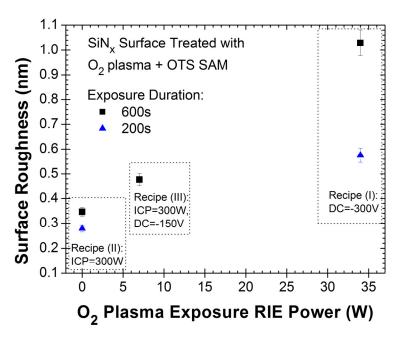

| Figure 5.17. Surface roughness as a function of $O_2$ plasma exposure power for $SiN_x$ surface treated with $O_2$ plasma and OTS SAM. Measurements performed using tapping-mode AFM192                                                                                                                                                                                                       |

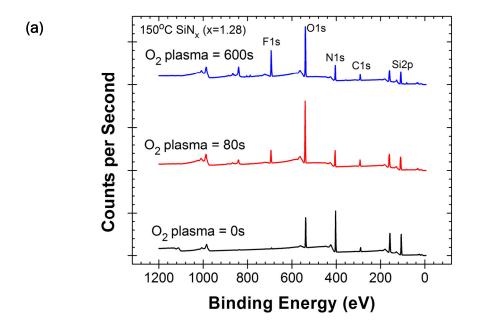

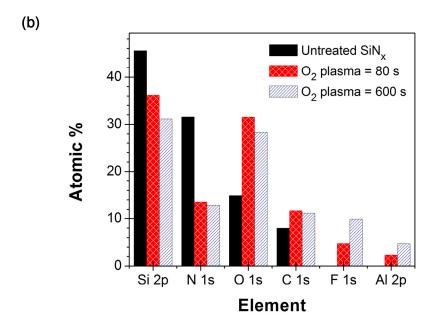

| Figure 5.18. (a) XPS spectrum in survey scan mode of an untreated $SiN_x$ surface and $O_2$ plasma treated $SiN_x$ surfaces after 80 sec and 600 sec exposure. (b) Chemical composition (represented by atomic percentage) of the $SiN_x$ top surface extracted from (a). $O_2$ plasma exposure was done using Recipe (I) in Table 5.6.                                                       |

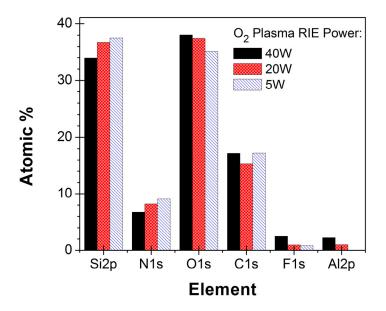

| Figure 5.19. Changes in chemical composition (represented by atomic percentage) of O <sub>2</sub> plasma treated SiN <sub>x</sub> surface at various exposure powers                                                                                                                                                                                                                          |

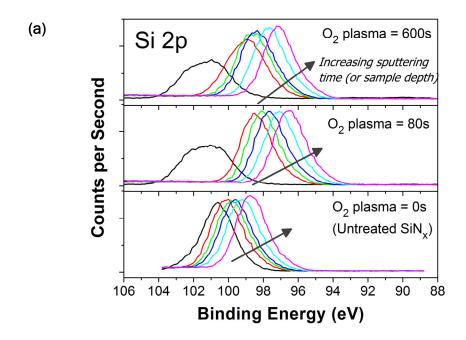

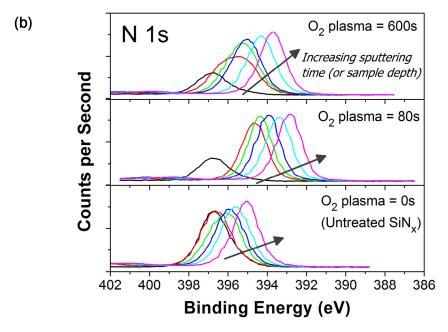

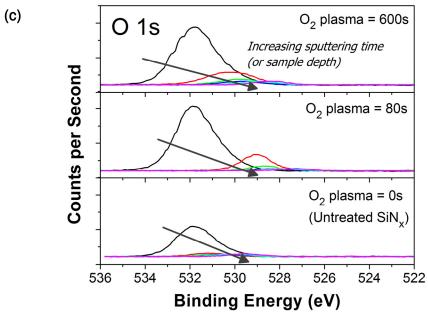

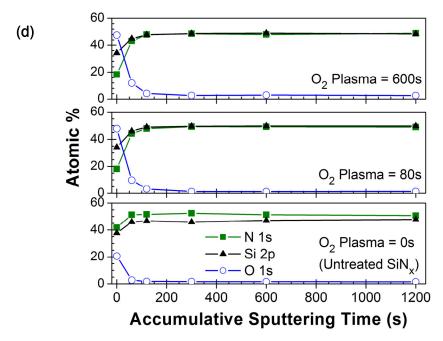

| Figure 5.20. (a) Si 2p, (b) N 1s, and (c) O 1s spectra of $150^{\circ}$ C SiN <sub>x</sub> ( $x = 1.28$ ) upon successive ion sputtering in XPS depth-profiling measurement. (d) Atomic percentage as a function of                                                                                                                                                                           |

|          | sputtering time, calculated based on XPS spectra in (a)-(c). Three SiN <sub>x</sub> samples were considered: as-deposited (untreated) SiN <sub>x</sub> , and 80 sec and 600 sec O <sub>2</sub> plasma treated SiN                                                                                                                                              | I <sub>x</sub> .<br>200 |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

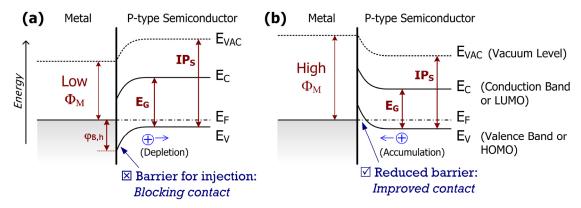

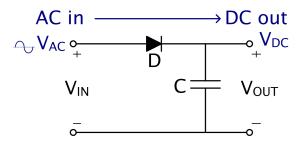

| ]        | 1.1. Energy level diagrams for metal and p-type semiconductor contact interface (assuming negligible interface states). (a) Small work function metal leads to interface barrier and poor contact. (b) Large work function metal leads to reduced interface barrier and improved contact.                                                                      | ng<br>209               |

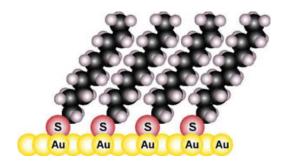

| Figure 6 | .2. Pictorial illustration of alkanethiol SAM on Au surface. (Adapted from [10].)                                                                                                                                                                                                                                                                              | 212                     |

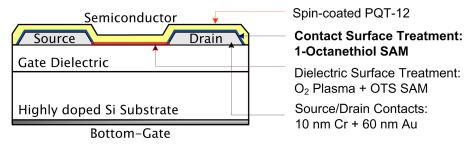

| -        | .3. Schematic cross-section of the OTFT structure considered in this contact surface treatment study.                                                                                                                                                                                                                                                          | 213                     |

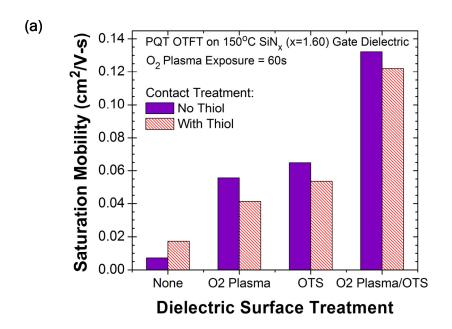

| :        | 4. (a) Effective mobility and (b) on/off current ratio of PQT-12 OTFT with 150°C SiN = 1.60) gate dielectrics in the absence ("no thiol") or presence ("with thiol") of 1-octanethiol SAM modification of Au contact surfaces. Four scenarios of gate dielectric surface treatments were considered. Measurements collected in saturation region               |                         |

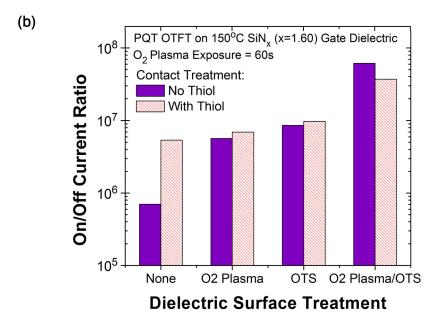

| ;        | absence ("no thiol") or presence ("with thiol") of 1-octanethiol SAM modification of Aucontact surfaces. Four scenarios of gate dielectric surface treatments were considered. Measurements were collected in saturation region of OTFT operation.                                                                                                             | 1                       |

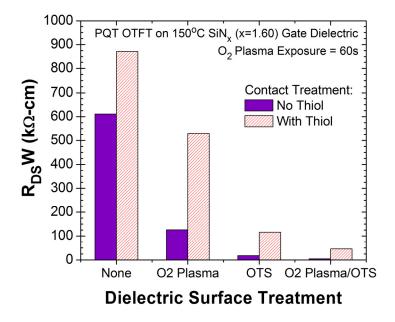

| ;        | 6. Contact resistance of PQT-12 OTFT on $150^{\circ}$ C SiN <sub>x</sub> ( $x = 1.60$ ) gate dielectrics in the absence ("no thiol") or presence ("with thiol") of 1-octanethiol SAM modification of Aucontact surfaces. Four scenarios of gate dielectric surface treatments were considered. Measurements were collected in linear region of OTFT operation. | 1                       |

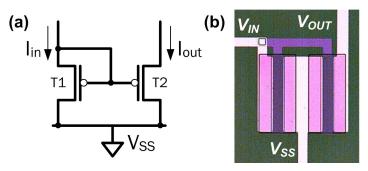

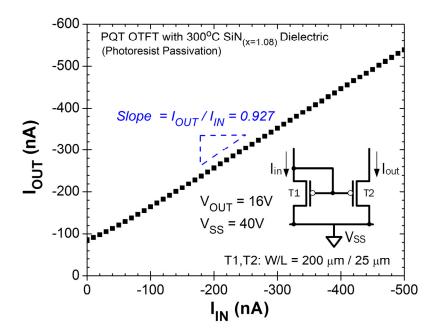

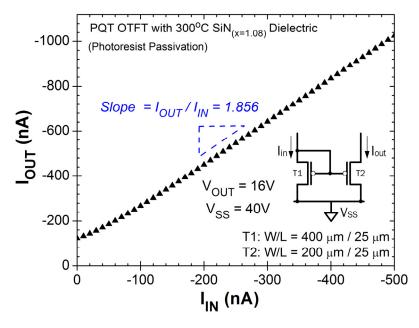

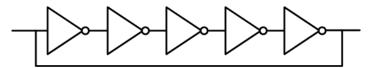

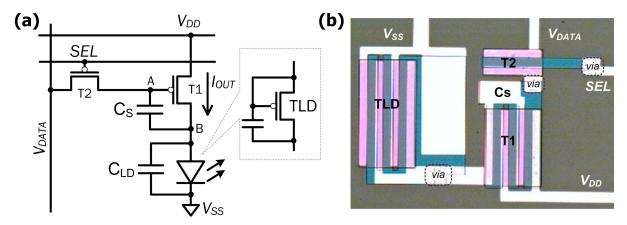

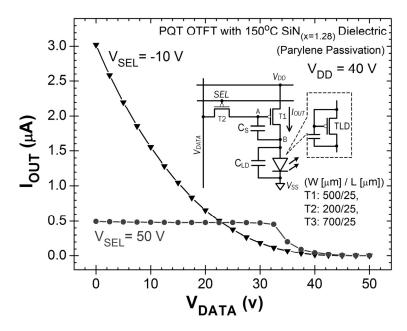

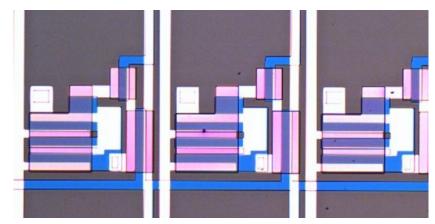

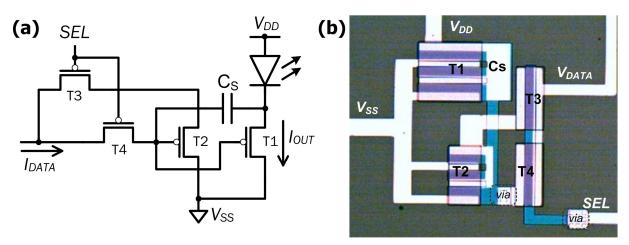

|          | .7. Saturation mobility versus contact resistance of PQT-12 OTFT on $150^{\circ}$ C SiN <sub>x</sub> ( $x = 1.60$ ) gate dielectrics.                                                                                                                                                                                                                          | 220                     |