# Low Power Clock and Data Recovery Integrated Circuits

by

Shahab Ardalan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2007

©Shahab Ardalan, 2007

#### **AUTHOR'S DECLARATION**

| I hereby  | declare | that I | am    | the  | sole  | author    | of t  | this | thesis. | This  | is a | true | copy | of the | thesis, |

|-----------|---------|--------|-------|------|-------|-----------|-------|------|---------|-------|------|------|------|--------|---------|

| including | any req | uired  | final | revi | ision | s, as acc | cepto | ed b | y my e  | xamii | ners |      |      |        |         |

Shahab Ardalan

I understand that my thesis may be made electronically available to the public.

Shahab Ardalan

#### **Abstract**

Advances in technology and the introduction of high speed processors have increased the demand for fast, compact and commercial methods for transferring large amounts of data. The next generation of the communication access network will use optical fiber as a media for data transmission to the subscriber. In optical data or chip-to-chip data communication, the continuous received data needs to be converted to discrete data. For the conversion, a synchronous clock and data are required. A clock and data recovery (CDR) circuit recovers the phase information from the data and generates the in-phase clock and data.

In this dissertation, two clock and data recovery circuits for Giga-bits per second (Gbps) serial data communication are designed and fabricated in 180nm and 90nm CMOS technology. The primary objective was to reduce the circuit power dissipation for multichannel data communication applications. The power saving is achieved using low swing voltage signaling scheme. Furthermore, a novel low input swing Alexander phase detector is introduced. The proposed phase detector reduces the power consumption at the transmitter and receiver blocks.

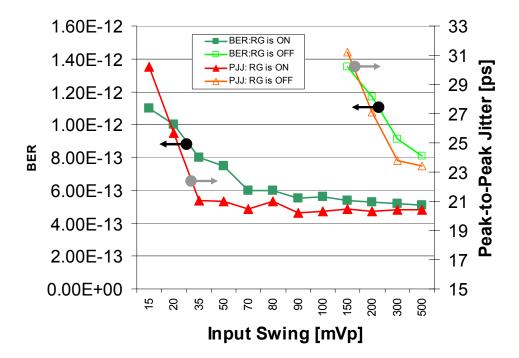

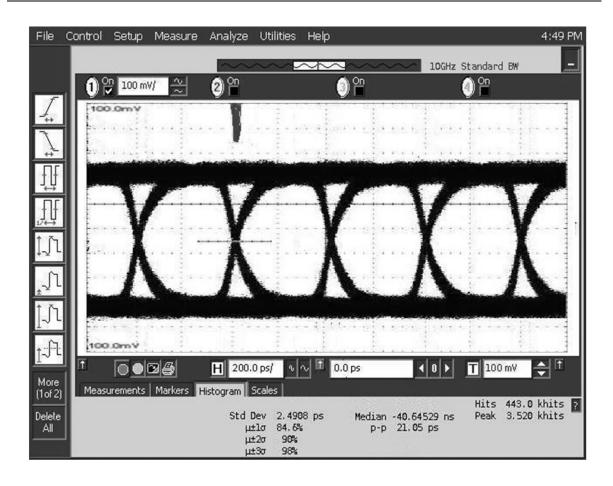

The circuit demonstrates a low power dissipation of 340µW/Gbps in 90nm CMOS technology. The CDR is able to recover the input signal swing of 35mVp. The peak-to-peak jitter is 21ps and RMS jitter is 2.5ps. Total core area excluding pads is approximately 0.01mm<sup>2</sup>.

#### Acknowledgements

I am grateful to many people who have made this work possible. First and foremost, I would like to express my great gratitude to Professor Sachdev, my thesis advisor, for his support and guidance throughout this work. I am very thankful to him for his constant encouragement, sincere care and vital advice.

I would like to give thanks to the members of my dissertation committee: Professor Mirabassi, Professor Vanderkuy, Professor Opal and Professor Gebotys for their insightful comments and constructive feedback.

With deepest appreciation, I wish to thank my brother, Kasra, for his advice, guidance, and technical comments. He leads me to the world of circuit design. His proficiency and enthusiasm is invaluable for me.

My sincere thanks also goes to my friends: Panthea Sepehrband, Amirali Khatibzadeh, Rubil Ahmadi, and Dr. Hossein Sarbishaei for continues support throughout my study.

I extend my thanks to my colleagues in CDR group at the University of Waterloo: Dr. David Rennie, Dr. Arman Vassighi, Dr. Bhaskar Chatterjee, Shahrzad Naraghi, Dr. Mohammad Sharifkhani, Dr. Nitin Mohan, Dr. Andrei Pavlov, and Dr. Mohammad Maymandi-Nejad. Thanks Dr. Afshin Rezayee and Dr. Mehrdad Ramezani from Snowbush Microelectronics for their guidance in system design.

In addition, I acknowledge the support from National Sciences and Engineering Research Council of Canada (NSERC).

My parents have been a constant source of encouragement during my studies. It is beyond my words to show my deep gratitude to them. This thesis, for all it is worth, is dedicated to them.

## Dedication

To My Mom, Dad and brother.

#### **Table of Contents**

| AUTHOR'S DECLARATION                               | ii   |

|----------------------------------------------------|------|

| Abstract                                           | 111  |

| Acknowledgements                                   | iv   |

| Dedication                                         | v    |

| Table of Contents                                  | vi   |

| List of Figures                                    | ix   |

| List of Tables                                     | X111 |

| Glossary                                           | xiv  |

| Chapter 1 Introduction                             |      |

| 1.1 Introduction                                   |      |

| 1.2 A Fiber Optic Transceiver System               | 5    |

| 1.3 Chip-to-Chip Communication                     |      |

| 1.4 Clock and Data Recovery Circuit                | 7    |

| 1.5 Power Awareness in Serial Data Communication   | 10   |

| 1.6 Summary and Motivation                         | 11   |

| Reference                                          | 13   |

| Chapter 2 CDR Architecture                         | 15   |

| 2.1 Introduction                                   | 15   |

| 2.1.1 Open-Loop CDR                                | 15   |

| 2.1.2 Phase-Locking CDR                            | 17   |

| 2.2 Pre-Amplifier and Limiter                      | 20   |

| 2.3 Phase Detector                                 | 22   |

| 2.3.1 Linear and Binary Phase Detector             | 22   |

| 2.3.2 Full-Rate and Fractional-Rate Phase Detector | 26   |

| 2.4 Voltage-Controlled Oscillators                 | 36   |

| 2.4.1 LC Based VCO                                 | 36   |

| 2.4.2 Ring Oscillator VCO                          | 38   |

| 2.5 Loop Filter and Charge pump             | 39  |

|---------------------------------------------|-----|

| Reference                                   | 42  |

| Chapter 3 Analysis of CDR Circuit           | 47  |

| 3.1 Introduction                            | 47  |

| 3.2 Analog CDR                              | 48  |

| 3.2.1 Analog CDR Type I                     |     |

| 3.2.2 Analog CDR Type-II                    |     |

| 3.3 Hybrid CDR                              | 63  |

| 3.3.1 First order hybrid CDR                | 64  |

| 3.3.2 Second-order hybrid CDR               | 66  |

| Reference                                   | 69  |

| Chapter 4 Power Reduction Strategies        | 70  |

| 4.1 Introduction                            | 70  |

| 4.2 Static CMOS Logic vs. CML               | 71  |

| 4.3 Low Input Swing Data Sampler            | 73  |

| 4.3.1 Normal D- Flip Flop                   | 74  |

| 4.3.2 Switched D- Flip Flop                 | 76  |

| 4.3.3 Switched-Buffered D-Flip Flop         | 79  |

| 4.3.4 Comparison                            | 80  |

| 4.4 Low substrate noise VCO                 | 81  |

| 4.4.1 Substrate Noise                       | 81  |

| 4.4.2 Substrate Noise in VCO                | 83  |

| 4.4.3 Low Substrate Noise Ring Oscillator   | 86  |

| Reference                                   | 91  |

| Chapter 5 Low Power CDR                     | 92  |

| 5.1 Introduction                            | 92  |

| 5.2 The 2 Gbps Low-Power CDR Implementation | 93  |

| 5.2.1 Phase Detector                        | 93  |

| 5.2.2 Charge Pump                           | 98  |

| 5.2.3 Voltage Controlled Oscillator         | 100 |

| 5.2.4 Pulse Generator                       | 103 |

| 5.2.5 Measurement Result                    | 105 |

|---------------------------------------------|-----|

| 5.3 The 5 Gbps Low Power CDR Implementation | 110 |

| 5.3.1 Alexander Phase Detector              | 110 |

| 5.3.2 Measurement Result                    | 112 |

| Chapter 6 Conclusion                        | 117 |

| 6.1 Conclusion                              | 117 |

| 6.2 Future Work                             | 119 |

| Reference                                   | 121 |

|                                             |     |

## List of Figures

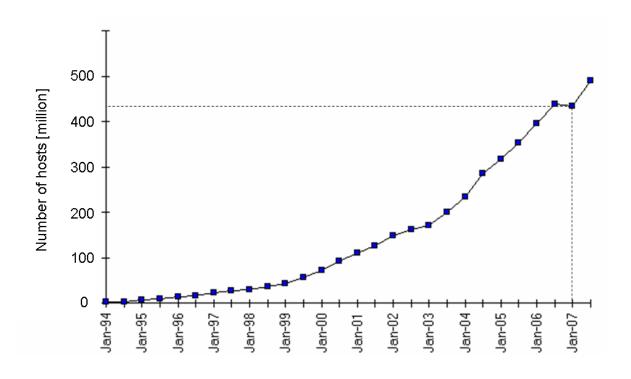

| Figure 1-1: Host count over years [1].                                                | 2  |

|---------------------------------------------------------------------------------------|----|

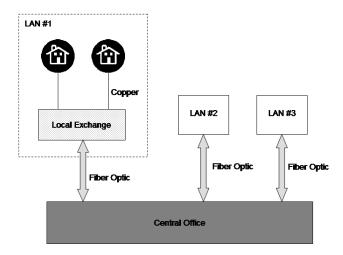

| Figure 1-2: Present day data distribution network.                                    | 3  |

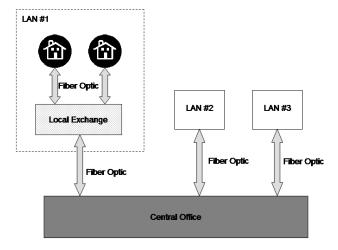

| Figure 1-3: Future data distribution network.                                         | 4  |

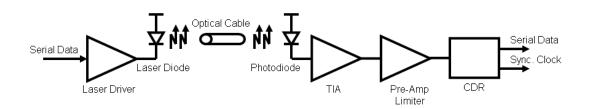

| Figure 1-4: Typical fiber optic transceiver.                                          | 5  |

| Figure 1-5: Optimum sample point.                                                     | 6  |

| Figure 1-6: NRZ and RZ data stream.                                                   | 7  |

| Figure 1-7: Power spectral density of random NRZ data.                                | 9  |

| Figure 1-8: Open loop CDR.                                                            | 10 |

| Figure 1-9: Reported power per data rate over years [10]                              | 10 |

| Figure 1-10: Serial data link receiver power break down [10].                         | 11 |

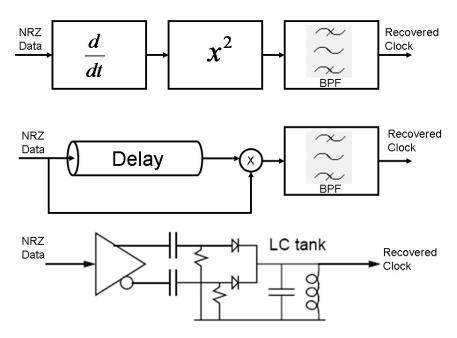

| Figure 2-1: Open-Loop CDR Architecture                                                | 16 |

| Figure 2-2: Signals of Open-Loop CDR.                                                 | 16 |

| Figure 2-3: Different architecture for Open loop CDR [2].                             | 17 |

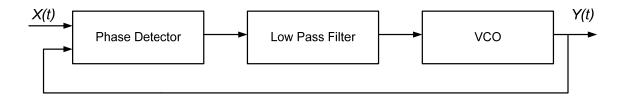

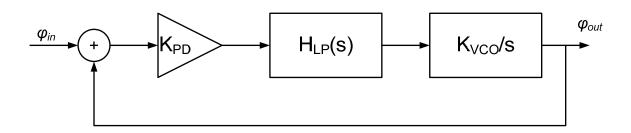

| Figure 2-4: Phase-Locking PLL architecture.                                           | 18 |

| Figure 2-5: PLL linear model.                                                         | 18 |

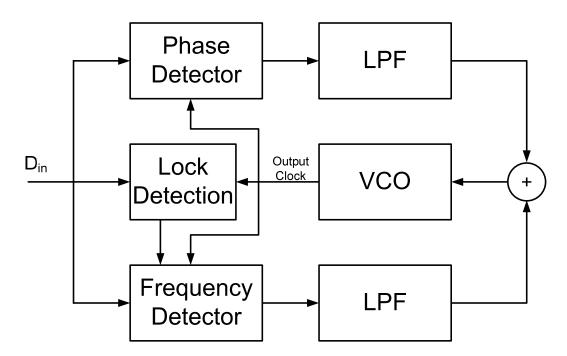

| Figure 2-6: Aided Acquisition with Frequency Detector.                                | 19 |

| Figure 2-7: Distributed amplifier.                                                    | 21 |

| Figure 2-8: Hogge linear phase detector.                                              | 23 |

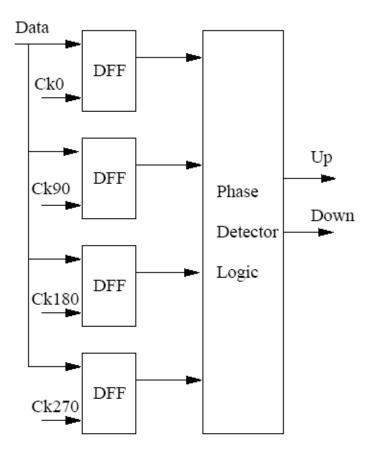

| Figure 2-9: Alexander's binary phase detector.                                        | 25 |

| Figure 2-10: Pottbakcer's binary phase detector.                                      | 26 |

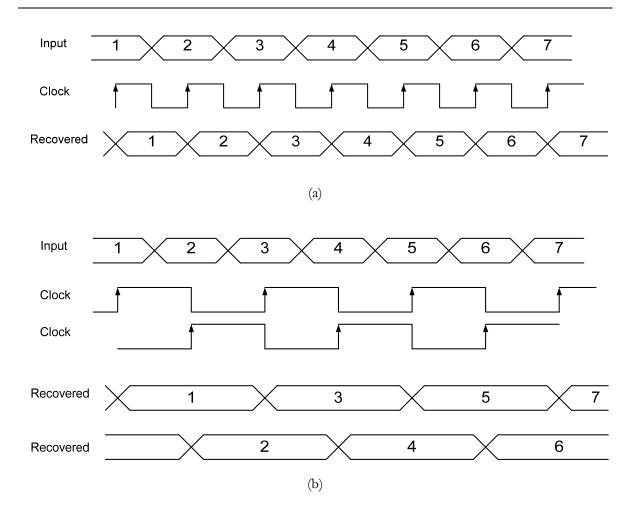

| Figure 2-11: Waveforms for full-rate and half-rate CDR: (a) full-rate, (b) half-rate. | 27 |

| Figure 2-12: Half-Rate Alexander phase detector.                                      | 28 |

| Figure 2-13: Haueneschild's phase detector.                                           | 29 |

| Figure 2-14: Ramezani's half-rate phase detector.                                     | 30 |

| Figure 2-15: Anderson's half-rate phase detector.                                     | 31 |

| Figure 2-16: Modified half-rate Anderson's phase detector                             | 32 |

| Figure 2-17: Lee's 1/4 Rate-Phase Detector.                                           | 33 |

| Figure 2-18: Linear 1/8 Rate-Phase Detector.                                          | 34 |

| Figure 2-19: Proposed binary 1/8-rate-phase detector.                                 | 35 |

| Figure 2-20: 10Gbps phase detector characteristic.                         | 36 |

|----------------------------------------------------------------------------|----|

| Figure 2-21: Schematic of an LC-tank oscillator.                           | 37 |

| Figure 2-22: Schematic of a four-stage differential ring oscillator.       | 39 |

| Figure 2-23: Simple Charge-Pump and Loop-Filter.                           | 40 |

| Figure 3-1: Linear model of an analog CDR.                                 | 49 |

| Figure 3-2: Bode plots for analog CDR.                                     | 51 |

| Figure 3-3: Step response for an analog CDR.                               | 52 |

| Figure 3-4: Bode diagrams of the error transfer function.                  | 53 |

| Figure 3-5: Charge pump and capacitor.                                     | 54 |

| Figure 3-6: Analog CDR linear model block diagram.                         | 55 |

| Figure 3-7: Bode diagram for analog CDR with charge pump.                  | 56 |

| Figure 3-8: charge pump with new loop filter.                              | 57 |

| Figure 3-9: Bode diagrams for system with zero and without zero            | 58 |

| Figure 3-10: Open loop transfer function with different loop gains.        | 60 |

| Figure 3-11: Close loop Bode diagram with different loop gains.            | 60 |

| Figure 3-12: Step response to close loop system with different loop gains. | 61 |

| Figure 3-13: Bode diagrams for error transfer function.                    | 62 |

| Figure 3-14: Filtering the input jitter and VCO jitter.                    | 63 |

| Figure 3-15: The first order hybrid CDR.                                   | 64 |

| Figure 3-16: Phase linear model of the 1st order hybrid CDR.               | 64 |

| Figure 3-17: Simulink simulation of 1st order hybrid CDR.                  | 66 |

| Figure 3-18: Block diagram of the 2 <sup>nd</sup> -order hybrid CDR [6].   | 67 |

| Figure 3-19: phase model for 2 <sup>nd</sup> -order hybrid CDR.            | 67 |

| Figure 4-1: power vs. performance over years [1].                          | 70 |

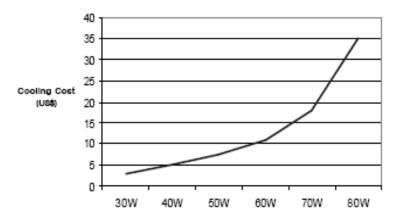

| Figure 4-2: Cooling cost vs. power dissipation [2].                        | 71 |

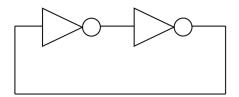

| Figure 4-3: Basic bi-stable circuit.                                       | 73 |

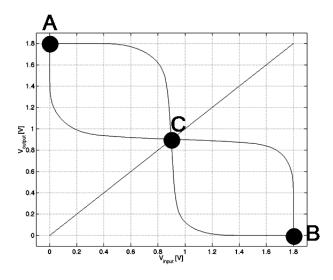

| Figure 4-4: bi-stable circuit voltage transfer characteristic.             | 73 |

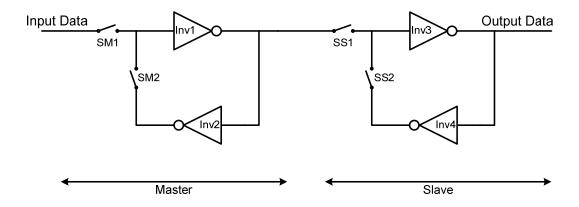

| Figure 4-5: Block diagram of master slave D-Flip-Flop.                     | 74 |

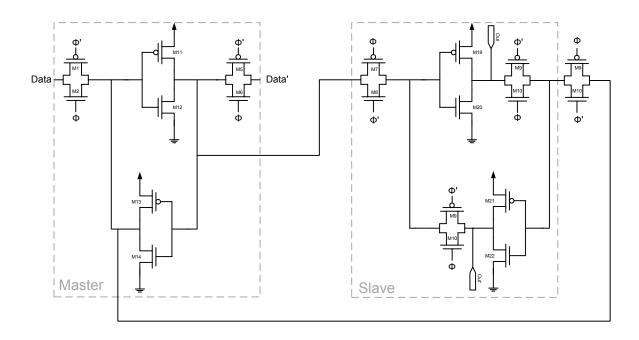

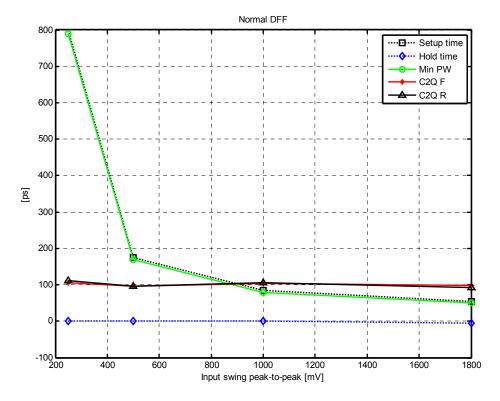

| Figure 4-6: Schematic diagram of master-slave D-Flip-Flop.                 | 75 |

| Figure 4-7: NDFF parameters vs. input data swing.                          | 75 |

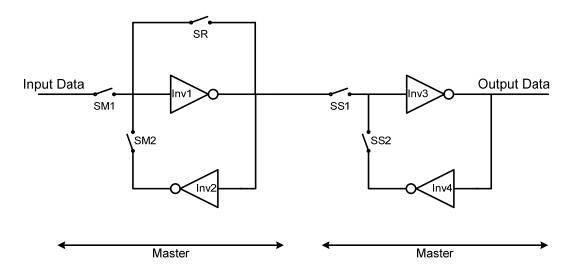

| Figure 4-8: Single-ended SDFF block diagram.                               | 76 |

|                                                                            |    |

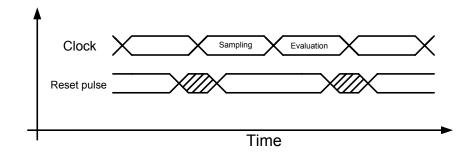

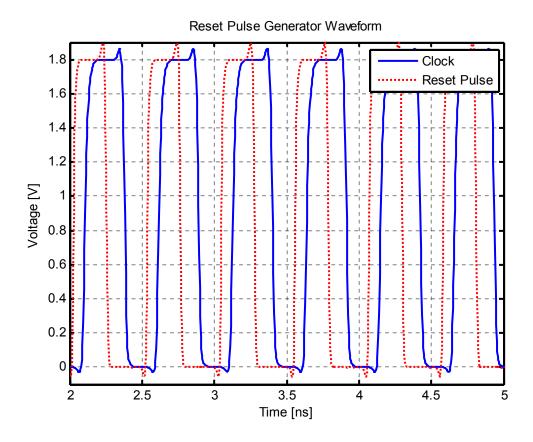

| Figure 4-9: Reset pulse timing wave form in the respect to clock                                        | 77  |

|---------------------------------------------------------------------------------------------------------|-----|

| Figure 4-10: Differential SDFF block diagram.                                                           | 77  |

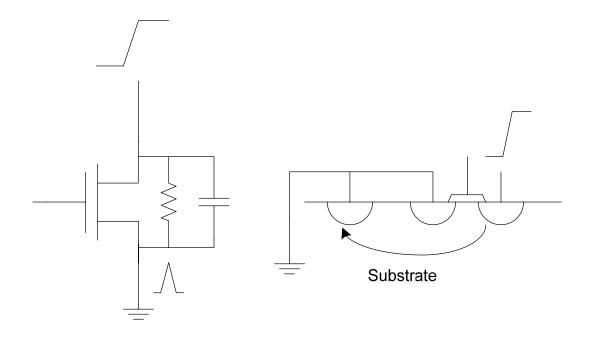

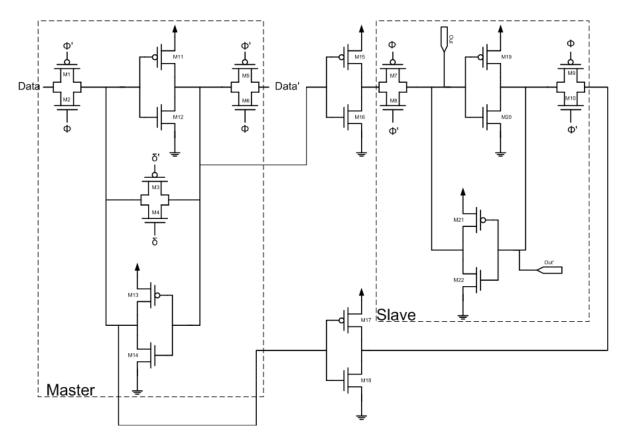

| Figure 4-11: Schematic diagram of master-slave SDFF.                                                    | 78  |

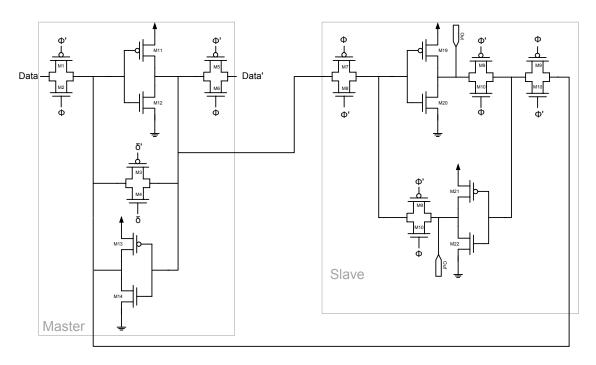

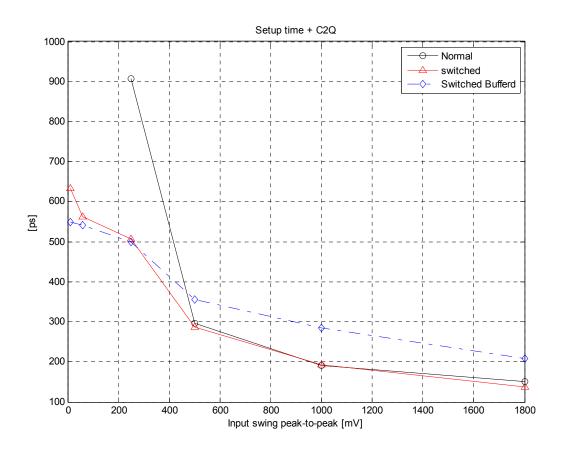

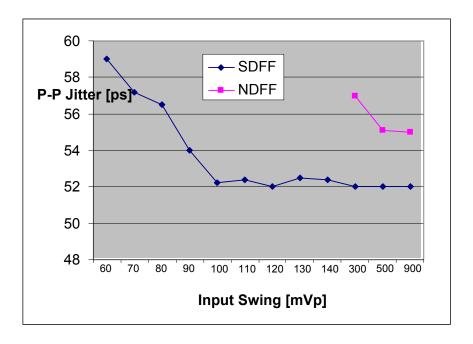

| Figure 4-12: SDFF parameters vs. input data swing.                                                      | 78  |

| Figure 4-13: SBDFF block diagram.                                                                       | 79  |

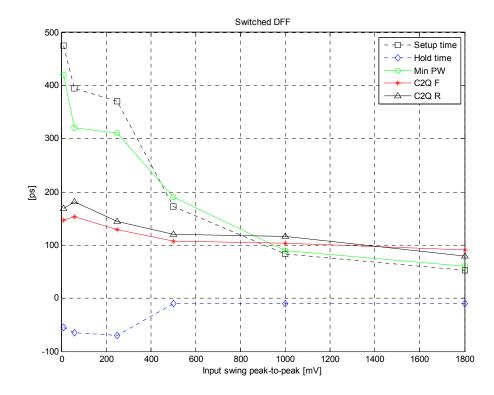

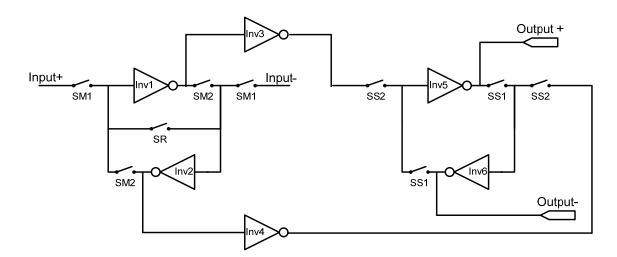

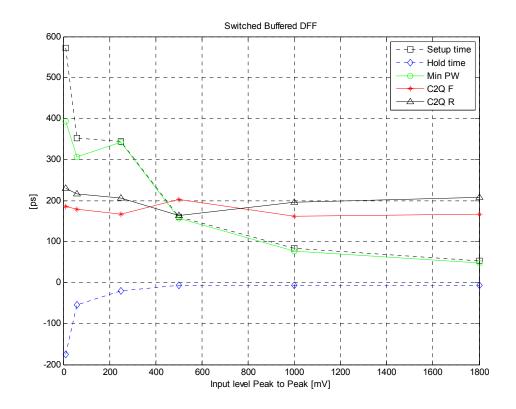

| Figure 4-14: SBDFF Parameter vs. Input Swing.                                                           | 80  |

| Figure 4-15: Delay comparison.                                                                          | 81  |

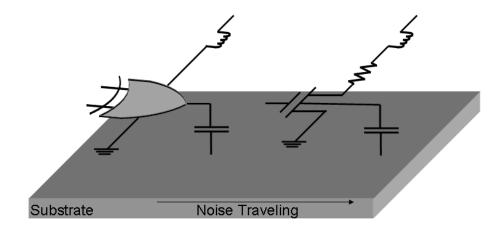

| Figure 4-16: Substrate noise propagation.                                                               | 82  |

| Figure 4-17: Substrate noise in mixed-signal circuits.                                                  | 83  |

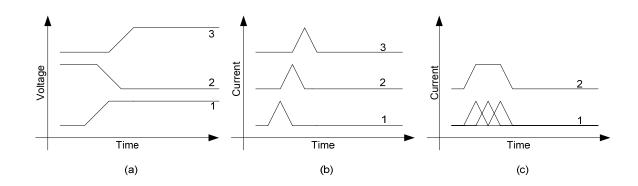

| Figure 4-18: (a) Single-Ended ring oscillator, (b) Differential ring oscillator                         | 84  |

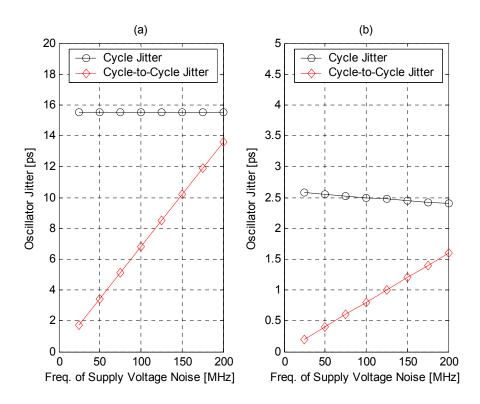

| Figure 4-19: Cycle jitter and cycle-to-cycle jitter of (a) the single-ended ring oscillator and (b) the |     |

| differential ring oscillator [4].                                                                       | 85  |

| Figure 4-20: Jitter of the three-stage and the six-stage of the differential ring oscillator [5]        | 85  |

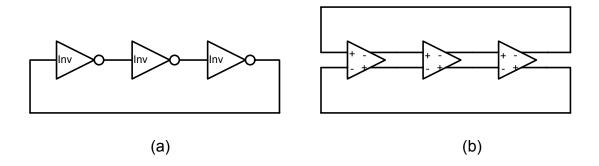

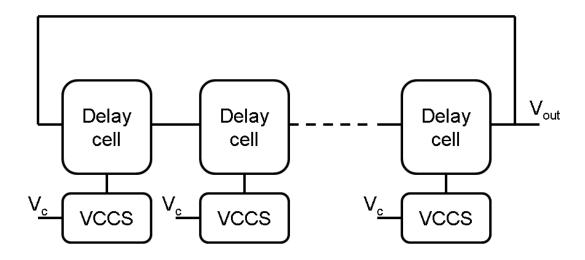

| Figure 4-21: Conventional single ended ring VCO.                                                        | 86  |

| Figure 4-22: Architecture for proposed VCO.                                                             | 87  |

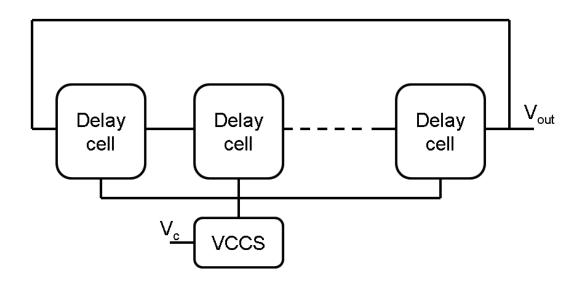

| Figure 4-23: Voltage and Current waveforms for a single ended VCO                                       | 88  |

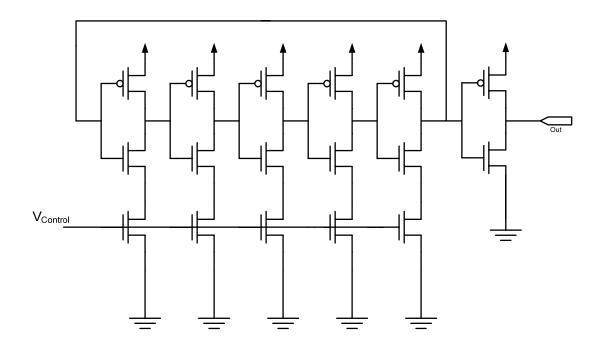

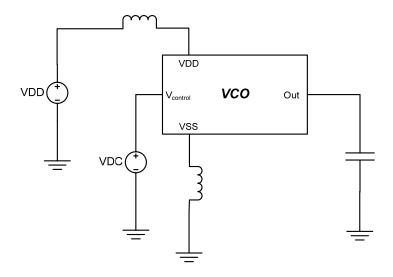

| Figure 4-24: Schematic for conventional ring VCO.                                                       | 89  |

| Figure 4-25: The schematic of proposed ring VCO.                                                        | 89  |

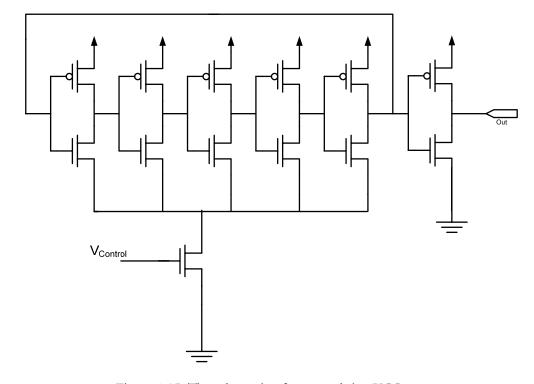

| Figure 4-26: Test bench schematic.                                                                      | 90  |

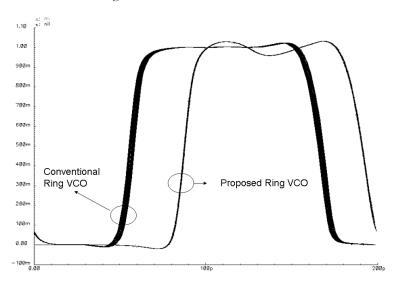

| Figure 4-27: Eye-diagrams for conventional and proposed VCOs.                                           | 90  |

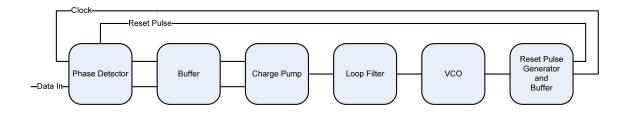

| Figure 5-1: Block diagram for the PLL based CDR.                                                        | 93  |

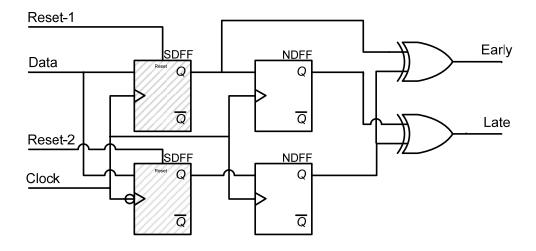

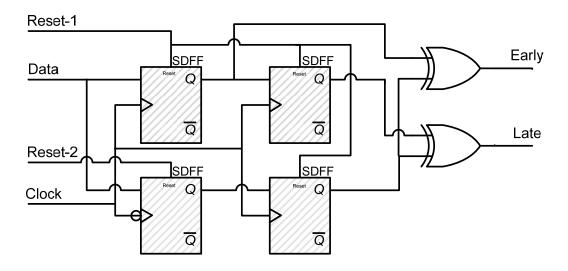

| Figure 5-2: Alexander phase detector.                                                                   | 94  |

| Figure 5-3: SDFF Schematic.                                                                             | 94  |

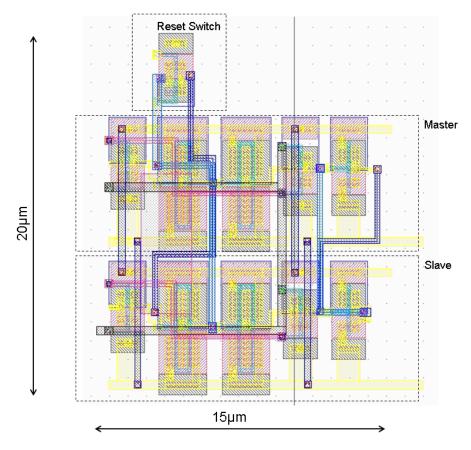

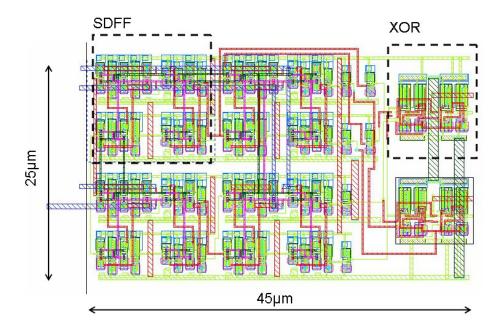

| Figure 5-4: SDFF Layout.                                                                                | 95  |

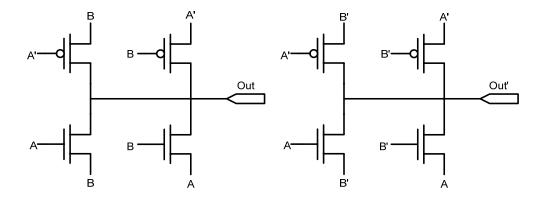

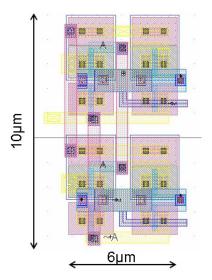

| Figure 5-5: Schematic for XOR.                                                                          | 96  |

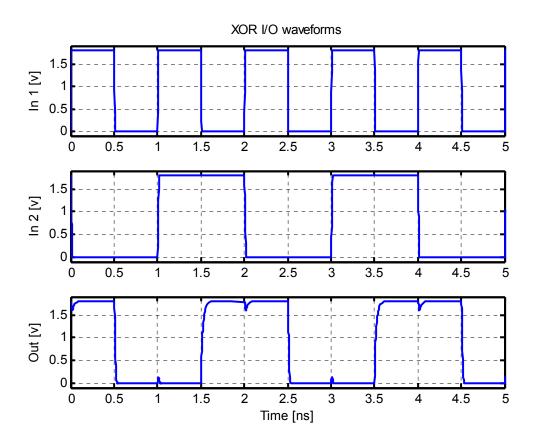

| Figure 5-6: Inputs and output wave forms of the XOR block.                                              | 96  |

| Figure 5-7: XOR layout.                                                                                 | 97  |

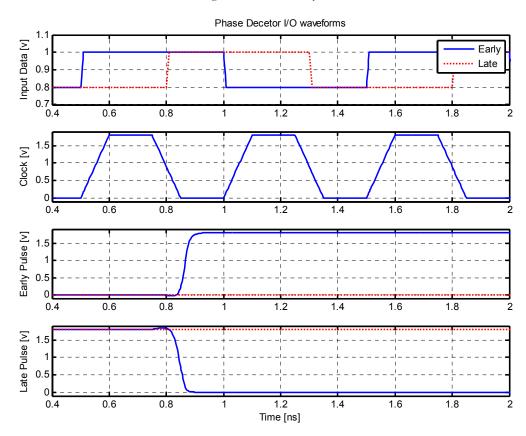

| Figure 5-8: Phase Detector input/output wave forms.                                                     | 97  |

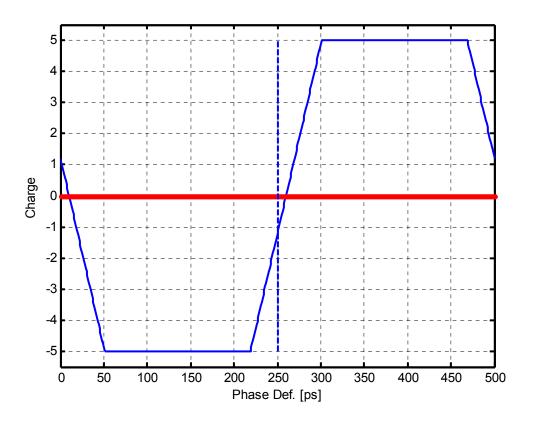

| Figure 5-9: Phase Detector characteristic graph.                                                        | 98  |

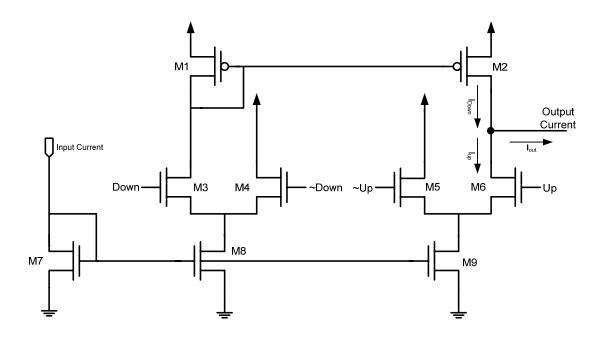

| Figure 5-10: Schematic of the charge pump.                                                              | 99  |

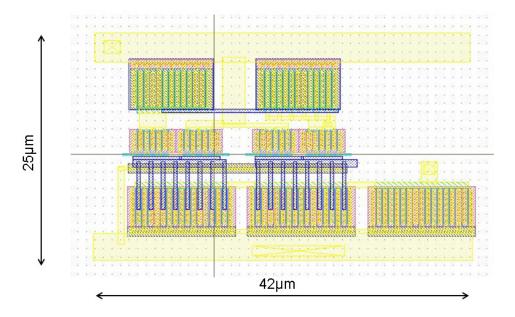

| Figure 5-11: The layout for charge-pump block.                                                          | 100 |

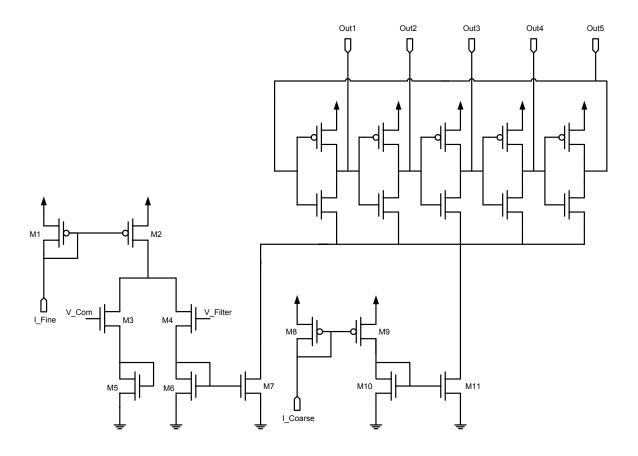

| Figure 5-12: Schematic of the VCO.                       | 101 |

|----------------------------------------------------------|-----|

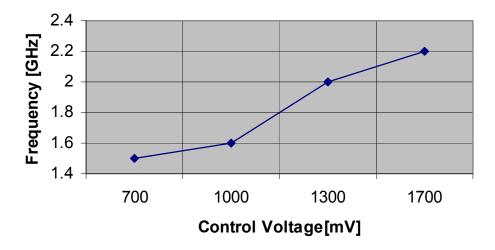

| Figure 5-13: VCO tuning characteristic.                  | 102 |

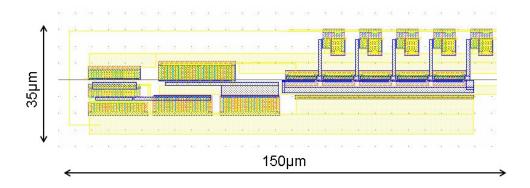

| Figure 5-14: Layout of the VCO.                          | 103 |

| Figure 5-15: Reset pulse generator.                      | 104 |

| Figure 5-16: Pulse generator and buffers layout.         | 104 |

| Figure 5-17: Reset pulse wave forms.                     | 105 |

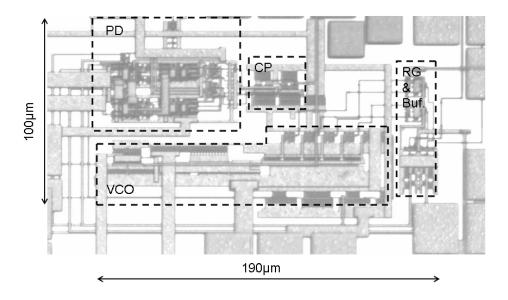

| Figure 5-18: Die photograph.                             | 106 |

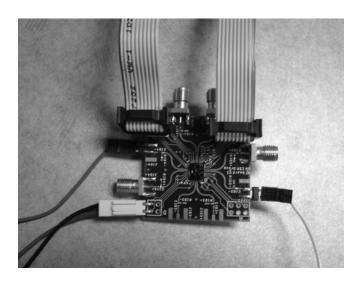

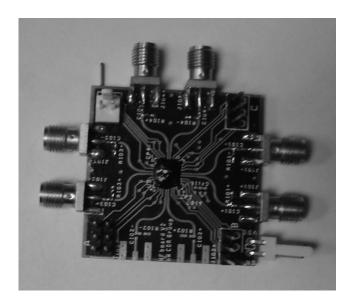

| Figure 5-19: PCB board.                                  | 107 |

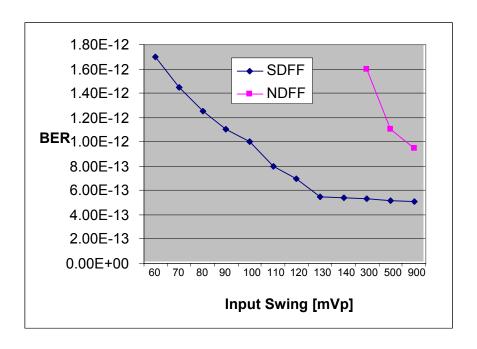

| Figure 5-20: BER vs. input data swing.                   | 108 |

| Figure 5-21: Peak-to-Peak jitter vs. input data swing.   | 108 |

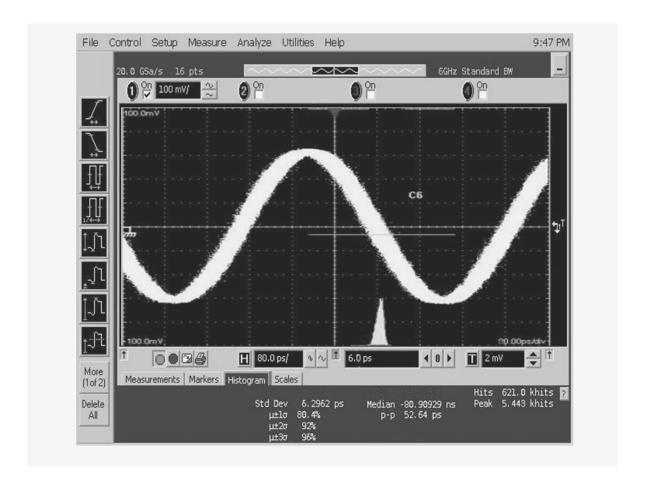

| Figure 5-22: Output eye diagram.                         | 109 |

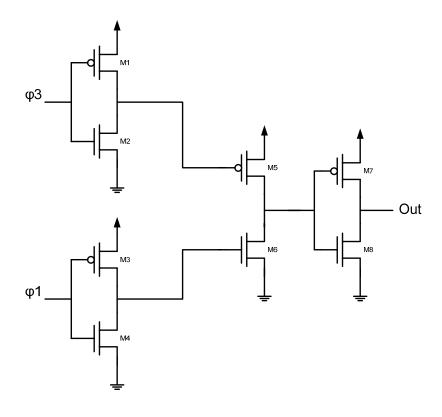

| Figure 5-23: Alexander phase detector.                   | 111 |

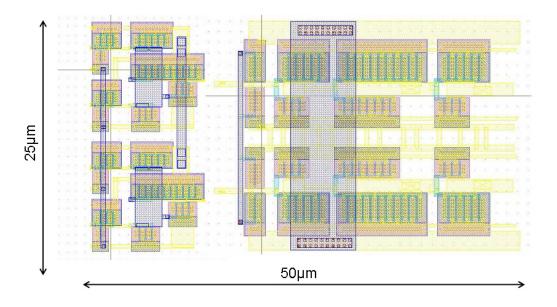

| Figure 5-24: Alexander phase detector layout in 90nm.    | 111 |

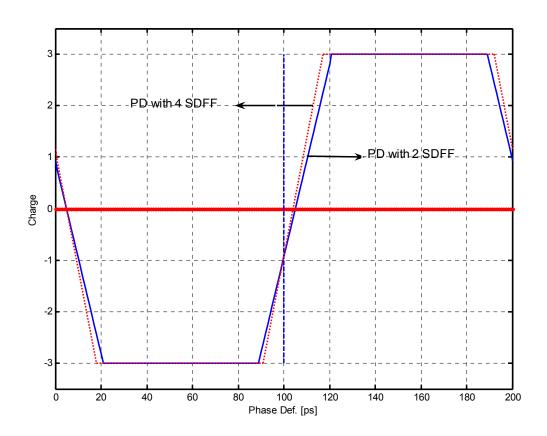

| Figure 5-25: 5Gbps binary phase detector characteristic. | 112 |

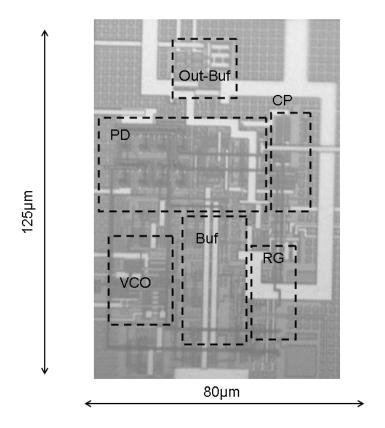

| Figure 5-26: 5Gbps CDR die photograph.                   | 113 |

| Figure 5-27: PCB board.                                  | 114 |

| Figure 5-28: RMS Jitter and BER vs. input data swing.    | 115 |

| Figure 5-29: Output eye diagram.                         | 116 |

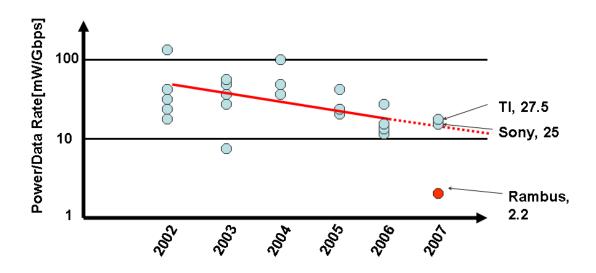

| Figure 6-1: Power to data rate ratio over years [1].     | 118 |

### List of Tables

| Table 2-1: Logic for a three-state Alexander Phase Detector | 25  |

|-------------------------------------------------------------|-----|

| Table 5-1: Transistor sizing for SDFF                       | 95  |

| Table 5-2: 2Gbps CDR parameter                              | 106 |

| Table 5-3: 5Gbps CDR parameter                              | 113 |

| Table 6-1: Rambus receiver and 90nm proposed CDR parameters | 119 |

#### Glossary

bps bit per second

CDR Clock and Data Recovery

CML Current Mode Logic

CMOS Complementary metal-oxide-semiconductor

DA Distributed Amplifier

DCT Data and Clock Transition

DFF D-Flip-Flop

DNS Domain Name Service

DSP Digital Signal Processing

FD Frequency Detector

I/O Input/Output

IC Integrated Circuit

IEEE Institute of Electrical and Electronics Engineers

ISI Inter Symbol Interference

LAN Local Area Network

LPF Low Pass Filter

NRZ Non-Return to Zero

PCB Printed Circuit Board

PD Phase Detector

PFD Phase and Frequency Detector

PLL Phase Locked Loop

RMS Root Mean Square

RZ Return to Zero

SAW Surface Acoustic Wave

SBDFF Switched Buffer D-Flip-Flop

SDFF Switched D-Flip-Flop

SNR Signal-to-Noise Ratio

SOC System on Chip

SONET Synchronous Optical Network

TIA Trans-Impedance Amplifier

TL Transmission Line

V/I Voltage to Current

VCCS Voltage Controlled Current Source

VCO Voltage Controlled Oscillator

WAN Wide Area Network

## Chapter 1

## Introduction

#### 1.1 Introduction

Advances in technology and the introduction of high-speed processors have increased the demand for fast, compact and commercial methods for transferring large amounts of data. People and businesses rely increasingly on the Internet for Web access, virtual private networks, e-commerce, video streams, training and customer support. According to the International Domain Survey made by Network Wizard, the number of hosts advertised in the domain name system (DNS) jumped from 4 million on January 1995 to 450 million on January 2007 (Figure 1-1)[1].

The amount of information traveling over a long haul wide-area-network (WAN) and a short reach local-area-network (LAN) is growing at the rate of 200 percent each year [2], [3].

Figure 1-1: Host count over years [1].

A LAN is a computer network covering a small geographic area, like a home, office, or group of buildings (distance less than 10km). The combination of several LANs generates a WAN, which covers larger distance (more than 100km). The block diagram of a present day communication access network is shown in Figure 1-2. The subscribers and local exchanges are connected by a LAN, and these LANs are connected to the central office through a WAN. Copper cables are used between the subscriber and the local exchange. The local exchange includes electronic cross point switches and electro/optical (E/O) converters [4].

Figure 1-2: Present day data distribution network.

A future communication access network is shown in

Figure 1-3. The optical fiber will extend all the way to the subscriber terminal replacing the current copper cable infrastructure [3]. Employing the high bandwidth media such as fiber optic in local area networks provides the ability of voice and video signal transition.

Figure 1-3: Future data distribution network.

Despite the fact that a completely optical transmission system is the objective, there is still need for E/O converters in the implementation of fiber optic transceiver systems. For example, an E/O converter is needed to connect electronic equipment, such as a computer to the other parts of the optical network. Also, E/O converters are used in moderate-speed (less than 10Gbps) single-wavelength fiber optic regenerators [5], [4]. In the high bandwidth media such as fiber optic, the electronic circuits dictate the limit of the data transmission.

Meanwhile when networking companies decide on a cabling system, they make a decision that is critical to the network infrastructure and long term in its horizon [6]. With the ratification of 1000BASE-T in June 1999 (IEEE 802.3 Ethernet Standard for Gigabit Ethernet on Category 5 copper), the one Gigabit Ethernet standard is already being deployed in large numbers in both corporate and public data networks. The 10 Gigabit Ethernet standards are being driven not only by the increase in normal data traffic, but also by the proliferation of new bandwidth-intensive applications. The standard for the 10 Gigabit Ethernet is significantly different in some respects from the earlier Ethernet standards, primarily in that it will only function over optical fiber, and only operate in full-duplex mode, meaning that collision detection protocols are unnecessary. Ethernet can now step up to 10 Gbps, however, it remains Ethernet. The packet format and the current capabilities are compatible with the old version. The 10 Gigabit Ethernet standard provides a significant increase in bandwidth while maintains maximum compatibility with the

installed base of 802.3 standard interfaces. At the present, researchers are designing building blocks for the 10 Gigabit Ethernet. The 10 Gigabit Ethernet does not obsolete current investments in network infrastructure. The standard enables Ethernet packets to travel across synchronous optical networking (SONET) links with very little inefficiency [7].

## 1.2 A Fiber Optic Transceiver System

In a typical fiber optic transceiver, the data is converted to light pulses by the transmitter and detected by the receiver (Figure 1-4). At the transmitter side of a typical fiber optic transceiver, the high speed digital data is converted to high frequency optical pulses with a laser driver. These ultra-fast laser pulses are transmitted over the fiber optic channel. An ultra-pure glass fiber is used to guide the light.

Figure 1-4: Typical fiber optic transceiver.

At the receiver side of a typical optical transceiver, a photo diode converts the optical signal to an electric signal. With a pre-amplifier and a limiter, the voltage pulses, with the appropriate logic levels, are produced at the receiver. A clock and data recovery circuit

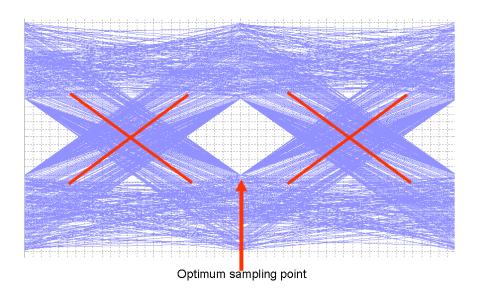

(CDR) extracts an in-phase clock from the data. The extracted clock is used to sample the analog waveforms at the optimum sampling time. Figure 1-5 shows the optimum sampling time at a given eye diagram.

Figure 1-5: Optimum sample point.

## 1.3 Chip-to-Chip Communication

The desire for higher chip-to-chip bit rates stems from the computer industry. For most of the history of the computer, system performance has been limited by the maximum clock frequency of the CPU. In recent years, improvements in integrated circuit (IC) fabrication technology have led to computer chips running at speeds approaching 4 GHz. This frequency is approximately equal to the bandwidth of a typical chip-to-chip channel on a printed circuit board (PCB). An important performance-limiting factor is the speed at which data can be sent between different chips in the same system. As the operation speed

of the chip increased over the past two decades, the aggregate chip-to-chip bit rate was typically grown by increasing the number of input/output (I/O) pins. Nevertheless, the the aggregate bit rate equals to bit rate per channel multiply by the number of channels [8].

## 1.4 Clock and Data Recovery Circuit

In order to sample the continuous-time received signal and convert it to a discrete-time sequence, the receiver needs an in-phase clock at the symbol rate. In some digital systems such as on-board chip-to-chip communication, the clock signal is transmitted separately. However, in most digital systems, transmission of a separate clock will increase the expense of the system and make it inefficient. Thus, the necessary timing information should be extracted from the data at the receiver side.

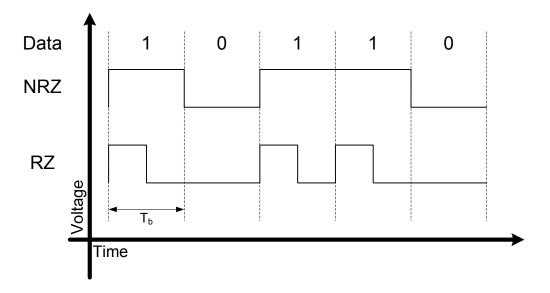

Figure 1-6: NRZ and RZ data stream.

If the spectral energy of the incoming data is not zero at the clock frequency, such as return-to-zero (RZ) signals (Figure 1-6), the timing reference can be extracted by simply passing the data through a band-pass filter with a center frequency equal to the symbol rate.

The autocorrelation function  $(R_X)$  of the signal with a null in its spectrum at the clock frequency, such as non-return-to-zero signals (Figure 1-6) is given by (1-1).

$$R_{X}(\tau) = \begin{cases} 1 - \frac{|\tau|}{T_{b}} & |\tau| < T_{b} \\ 0 & |\tau| > T_{b} \end{cases}$$

$$(1-1)$$

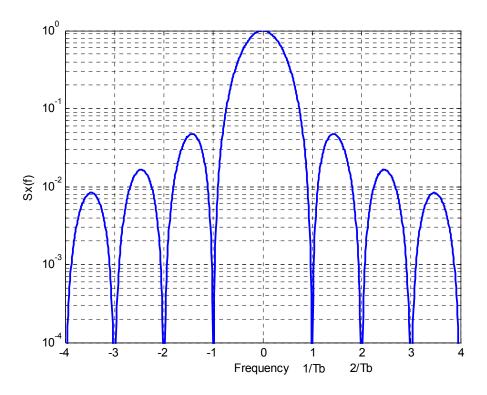

where  $\tau = t_1 - t_2$  and  $T_b$  is the bit time.  $R_x(\tau)$  results into a power spectral density (PSD) function given by the following equation [9]

$$S_X(f) = T_b \left[ \frac{\sin(\pi T_b f)}{\pi T_b f} \right]^2 \tag{1-2}$$

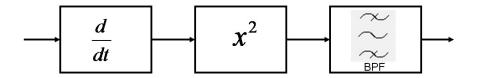

The power spectral density function of NRZ data is shown in Figure 1-7. If the input signal has a null in its spectrum at the clock frequency, such as non-return-to-zero (NRZ) signals shown in Figure 1-7, this spectral energy can be generated using a nonlinear element (Figure 1-8).

Page:9

Figure 1-7: Power spectral density of random NRZ data.

Edge detectors and squaring circuits are two of the commonly used nonlinearities. The required band-pass filter can be realized with an LC-tank or with a surface acoustic wave (SAW) filter. This filter is tuned to the desired frequency. Alternatively, this filter can be implemented using a phase-locked loop (PLL). The LC-tanks or SAW filters are neither tunable nor monolithic. A PLL can lock over a wide tuning range and it is also monolithic, making it preferable to the two other filters. This dissertation focuses on the phase-locking CDR architectures.

Figure 1-8: Open loop CDR.

## 1.5 Power Awareness in Serial Data Communication

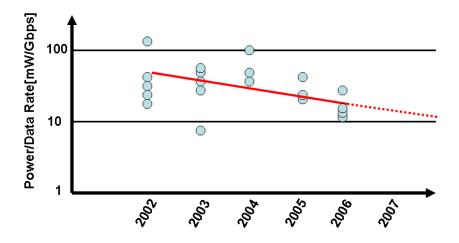

Reported serial data transceiver systems consume around 20 to 30mW/Gbps. Figure 1-9 shows the power reduction trend over the years, which has been achieved by CMOS scaling.

Figure 1-9: Reported power per data rate over years [10].

On the other hand, the power break down of a typical serial link receiver is shown in Figure 1-10.

Figure 1-10: Serial data link receiver power break down [10].

The CDR block dissipates around 30% of the total power consumption of the receiver block. High-speed operation in CMOS technology requires high power dissipation. Realizing multi-GHz logic in the phase detector block makes the CDR the most power consuming block among other blocks of the serial data link receiver.

In the last decade, cost and integration of CMOS technology encouraged designers to design high-speed CMOS circuits. However, designing CMOS transceivers faces multifold challenges such as noise, speed, voltage headroom, and substrate noise [9].

## 1.6 Summary and Motivation

The thesis started with an introduction to data communication and necessity of the CDR in data communication system. Next chapter includes the present clock and data recovery architectures and the building blocks of CDRs. Chapter 3 is devoted to system level

simulation of the different types of CDR systems. Proposed strategies for power reduction are disclosed in chapter 4. Chapter 5 presents the experimental results of two low power CDR circuits and chapter 6 concludes the thesis and suggested area for future work.

The main focus of the thesis is on power reduction of a high speed clock and data recovery. This goal has been achieved by implementing the CDR circuit in static CMOS circuit. However, a conventional static CMOS sampler (DFF) is not able to sense the small input swing data. A new architecture for static CMOS DFF, called Switched DFF (SDFF) has been introduced in chapter 4, and it is able to sample low input signal swing data. Future more to reduce the effect of substrate noise on VCO, a new architecture for low power single ended ring VCO has been disclosed on Chapter 4. The novel low substrate noise VCO uses current time sharing technique to keeps the switching current constant during operation and results in lower ground rail variation. The jitter performance is reduced due to less ground variation. The SDFF and low substrate noise VCO have been implemented in two different CMOS technology and the implementation results are presented in Chapter 5.

#### Reference

- [1] See: http://www.isc.org/index.pl?/ops/ds/

- [2] Frazier H., et al., "Ethernet Takes on the First Mile," Journal of Information Technology Professional, Vol. 3, pp. 17-23, Aug. 2001.

- [3] Voinigescu, S.; Popescu, P.; Banens, P.; Copeland, M.; Fortier, G.; Howlett, K.; Herod, M.; Marchesan, D.; Showell, J.; Sziiagyi, S.; Tran, H.; Weng, J., "Circuits and technologies for highly integrated optical networking ICs at 10 Gb/s to 40 Gb/s," Custom Integrated Circuits, 2001, IEEE Conference on., vol., no., pp.331-338, 2001.

- [4] Ramezani, M., "Gigabit/second Clock and Data Recovery Circuits for Local Area Networks," PhD Thesis, University of Toronto, 2004.

- [5] Keiser, G., "Optical Fiber Communications," McGraw Hill, 2000.

- [6] Gigabit Ethernet Alliance, "Running 1000Base-T: Gigabit Ethernet over Copper," white paper, Sep. 1999.

- [7] Gigabit Ethernet Alliance, "10 Gigabit Ethernet, Technology Overview," white paper, Apr. 2002.

- [8] Lee, M.-J.E.; Dally, W.J.; Chiang, P., "Low-power area-efficient high-speed I/O circuit techniques," Solid-State Circuits, IEEE Journal of, vol.35, no.11, pp.1591-1599, Nov 2000.

- [9] Razavi, B., "Design of Integrated Circuits for Optical Communications," McGraw Hill, 2003.

[10]Palmer, R.; Poulton, J.; Dally, W.J.; Eyles, J.; Fuller, A.M.; Greer, T.; Horowitz, M.; Kellam, M.; Quan, F.; Zarkeshvari, F., "A 14mW 6.25Gb/s Transceiver in 90nm CMOS for Serial Chip-to-Chip Communications," Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International, vol., no., pp.440-614, 11-15 Feb. 2007.

## Chapter 2

## **CDR** Architecture

#### 2.1 Introduction

The clock and data recovery (CDR) circuit architectures are categorized in two major groups; open-loop CDRs, and phase-locking CDRs [1].

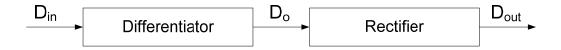

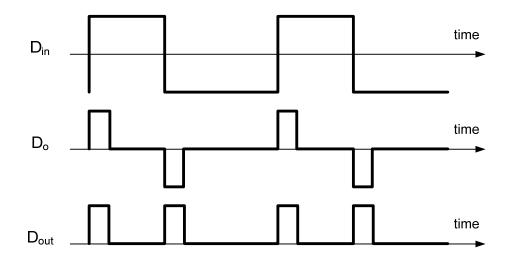

#### 2.1.1 Open-Loop CDR

The spectrum of an NRZ sequence does not carry a frequency tone at the data rate (Figure 1-7). However, the information about the frequency of the data can be extracted from the spacing between its transitions. These transitions appear as the rising and falling edges of the data signal. If a high-speed data sequence is passed through a differentiator, the resulting signal will carry positive and negative pulses for rising and falling edges of the clock signal, respectively. This differentiated signal does not provide a strong spectral line at the frequency of the data because the polarity of these pulses is random [1].

Figure 2-1: Open-Loop CDR Architecture.

Figure 2-2: Signals of Open-Loop CDR.

Figure 2-1 shows the open-loop CDR architecture. If the output of differentiator is passed through the rectifier, all edges will be converted to positive pulses, as shown in Figure 2-2 (no random polarity). There are some limitations for using this type of CDR in high-speed data commutation systems. Implementing a narrow band band-pass filter in silicon is a challenging task due to the process variation of fabrication. Different architectures, shown in Figure 2-3, had been used to implement the open loop CDR.

Figure 2-3: Different architecture for Open loop CDR [2].

#### 2.1.2 Phase-Locking CDR

A simple block diagram of a PLL is shown in Figure 2-4. The Voltage-Controlled Oscillator (VCO) attempts to produce a signal, Y(t), which tracks the phase of the input, X(t). The phase detector (PD) measures the phase error between X(t) and Y(t). This phase error is passed through a low-pass filter (LPF), thus producing the control voltage for the VCO. In the locked state, the output phase tracks the input phase with a constant phase difference. This constant phase error depends on the structure of the LPF and the PD.

The structure of the PLL is simple, but it is difficult to analyze. This is because the system is inherently nonlinear. For small phase errors, however, a linear model for studying the

PLL can be used (Figure 2-5). The behavior of an unlocked PLL is very nonlinear and complicated to analyze. Further work can be found with details in [3], [4].

Figure 2-4: Phase-Locking PLL architecture.

Figure 2-5: PLL linear model.

The PD is the most nonlinear block of the CDR. Most PDs have linear relationships between their average outputs and phase difference inputs for small phase errors (ignoring digital PDs) [3]. Using a simple feedback analysis, the ratio of the VCO phase to the input phase of a PLL that is, the jitter transfer function, can be obtained as:

$$H(s) = \frac{K_{PD}K_{VCO}H_{LP}(s)}{1 + K_{PD}K_{VCO}H_{LP}(s)}$$

(2-1)

where  $K_{PD}$  is phase detector gain,  $K_{VCO}$  is the VCO constant and  $H_{LP}(s)$  is loop filter transfer function.

The performance of a CDR is very dependent on its jitter transfer function and hence the choice of LPF. Temperature and process variations can cause significant changes in the VCO free-running frequency. These changes could be large such that the PLL may not achieve the locked state. The acquisition behavior of a CDR can be improved by employing a Frequency Detector (FD). In Figure 2-6, a block diagram of an aided acquisition PLL with frequency detector is shown. The FD must be turned off whenever the frequency error is small [5], which is controlled via a lock detector. Complexity of the circuit and extra required blocks are major drawbacks of this architecture.

Figure 2-6: Aided Acquisition with Frequency Detector.

## 2.2 Pre-Amplifier and Limiter

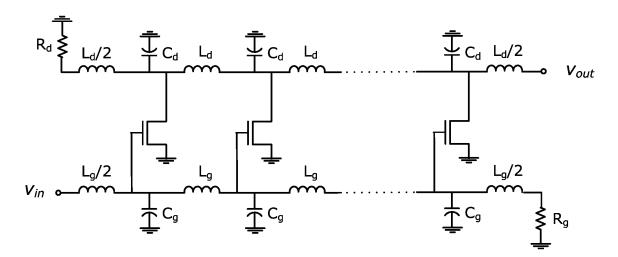

The signal traveling through the channel (wire or fiber) experiences loss before reaching a receiver. Therefore, the received signal needs to be amplified at the receiver before sampling and clock recovery. The amplifier must have a minimal bandwidth to reduce the total integrated noise. However, the limited bandwidth introduces intersymbol interference (ISI). Accordingly proper bandwidth selection is required. Nevertheless, the pre-amplifier must have enough gain to overcome the signal loss and make the signal level detectable. Thus, at high speed of operation and low supply voltage realizing pre-amplifier is a crucial task. Most of the limiters are designed using distributed amplifier concept [6], [7]. The theory of distributed or traveling-wave amplification using discrete transistors is a technique whereby the gain-bandwidth product of an amplifier may be increased. In this approach, the input and output capacitances of the transistors are combined with lumped inductors to form artificial transmission lines (TL). These lines are coupled by the transconductance of the devices. The amplifier can be designed to give a flat, low-pass response up to very high frequencies [8]. A distributed integrated circuit design is one of the effective approaches for the design of optical communication ultra-wideband circuits, particularly in CMOS technology [9]. Early distributed amplifiers were implemented using vacuum tubes and high-speed GaAs MESFETs [10]-[14]. Wide-band pre-amplifiers and gain-controlled amplifiers (or limiting amplifiers) are the key building blocks of optical receivers [15]. Since distributed amplifiers (DAs) have no gain-bandwidth trade-off, unlike other amplifier configurations, they can offer wide-band amplification for high speed application.

Conventional microwave DAs are constructed of two TLs that connect the drain and gate terminals of several field effect transistors. The CMOS interconnects with typical length (less than a few hundred micro meters) are not considered to be TLs at frequencies up to 80 GHz. Thus, the TLs are artificially constructed using a ladder of lumped-element inductors and capacitors in Figure 2-7.

Figure 2-7: Distributed amplifier.

The intrinsic capacitors of transistors – the main cause of bandwidth limitation – are separated by series on-chip inductors to form a low-pass filter topology. This structure provides a relatively low gain due its additive nature of the paralleled gain cell, but achieves wideband amplification due to distribution of the parasitic capacitors in a low-pass LC circuit topology. The main drawback of distributed amplifier topology is its large die area

because it requires several on-chip inductors. Similar to two cascaded low-pass LC filters, the maximum bandwidth of a DA is limited to the cutoff frequencies of the artificial gate and drain TLs. In practice, the bandwidth is further limited by the resistive loss of the TLs and by the output resistance of the amplifier cell gains.

### 2.3 Phase Detector

Phase detectors generate a DC component proportional to deviation of the sampling point from center of data cycle [2]. In this section different architecture for phase detector is explained.

## 2.3.1 Linear and Binary Phase Detector

Phase detectors for random NRZ data can be divided into two major groups: linear and digital (binary). For the linear phase detector, each data transition produces an error pulse whose width is linearly proportional to the phase error between the data edge and the clock edge. For small phase errors, the resulting pulse width will be small. This phenomenon makes the circuit design complicated and is often not practical in some technologies.

A digital phase detector produces only two states: clock up and clock down. If no data transition happens, the phase detector keeps its former state and may generate a large amount of data pattern dependent jitter. A three-state phase detector has zero output in the absence of any data transitions. This keeps the charge-pump output unchanged, and, hence, produces less jitter. During the locked state, the digital phase detector produces up

and down signals, which are random in nature, with an average that keeps the phase error zero. These random up and down pulses will increase the phase noise of the recovered clock.

#### 2.3.1.1 Hogge Linear Phase Detector

The Hogge phase detector [16] is popular in the literature and applications. Several modified versions of this phase detector have also been reported [17]. Figure 2-8 depicts the block diagram of Hogge phase detector. The data signal is sampled at clock with a D-flip-flop (DFF) to generate the error signal. The second DFF samples the error signal at opposite phase of the clock to produce the reference signal. The width of the reference signal is fixed at half of the clock period. The width of the error signal is proportional to the phase difference between the clock edge and the data edge.

Figure 2-8: Hogge linear phase detector.

The DC value of the difference between the error signal and reference signal is linearly proportional to the phase error. In the absence of any data transition, both error and reference signals become zero and the charge-pump output stays constant.

#### 2.3.1.2 Alexander's Binary Phase Detector

In a binary phase detector, the detected phase error is digitized. If the clock edge is leading the data edge, the down signal becomes high, regardless of the amount of leading phase. If the clock edge is lagging behind the data edge, the up signal becomes high, and the down signal becomes low. If no data transition occurs, the PD keeps its previous state. This phenomenon increases the recovered clock jitter for long periods following ones or zeros. Loop dynamics of a PLL with a binary phase detector are very complicated to analyze. Simplified analysis can be found in [21], [22].

A three-state PD adds a tri-state to the binary PD. Up and down signals are set to be pulses with fixed width. In case of a data transition, proper up or down pulses are generated. If no data transition happens, no up or down pulse is generated. In this case, the charge-pump is off and the charge on the LPF capacitors is not changed. This will keep the VCO control voltage constant and no excess jitter is produced.

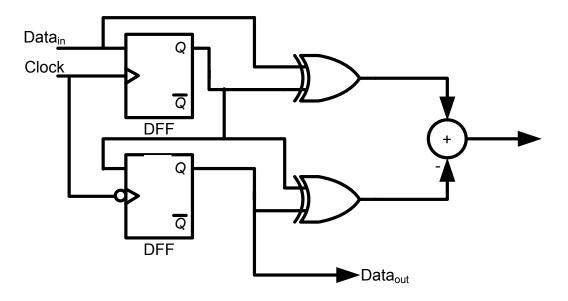

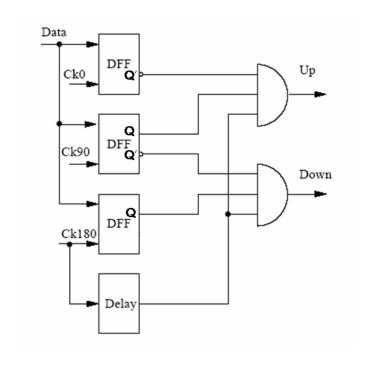

A simple algorithm for implementing a binary PD suitable for the NRZ data type was first suggested by Alexander [18]. A block diagram of Alexander's PD is shown in Figure 2-9. With proper selection of the PD logic, the Alexander's binary PD can be modified to a

three-state PD [23]. Table 2-1 shows the proper logic for a three-state Alexander phase detector.

Figure 2-9: Alexander's binary phase detector.

| A | В | С |               |

|---|---|---|---------------|

| 0 | 1 | 0 | Clock is fast |

| 1 | 0 | 1 | Clock is fast |

| 0 | 1 | 1 | Clock is slow |

| 1 | 0 | 0 | Clock is slow |

Table 2-1: Logic for a three-state Alexander Phase Detector

## 2.3.1.3 Pottbacker Binary Phase Detector

The Alexander phase detector samples the data signal on clock0 and clock180 edges. Then the PD logic block decides if the clock is early or late. As opposed to Alexander's PD,

Pottbacker's PD samples the clock with the data signal [5]. A simplified block diagram of this phase detector is shown in Figure 2-10.

Figure 2-10: Pottbakeer's binary phase detector.

#### 2.3.2 Full-Rate and Fractional-Rate Phase Detector

The architecture of the closed-loop CDR can be grouped into two main categories: full-rate and fractional-rate. The idea of fractional-rate phase detector started by half-rate phase detector. Figure 2-11 shows the signals (clock and data) for full-rate and 1/2 – rate phase detector. There have also been some half-rate linear phase detectors reported in papers [20], [28], [29].

Figure 2-11: Waveforms for full-rate and half-rate CDR: (a) full-rate, (b) half-rate.

In the fractional-rate phase detector the clock frequency is a fraction of the input data rate, hence, the phase detector can be implemented in a technology with a lower bandwidth. Using a fractional-N rate phase detector has the advantage of reducing the required clock frequency by a factor of N. Furthermore, without additional circuitry, the implementation provides a 1:N demultiplxing that simplifies the design of the demultiplexer which is usually needed at the output of a serial receiver.

In design of a fractional rate CDR the major concern is the clock duty cycle mismatch that causes an intrinsic static phase error between the clock and the data optimum sampling point [27].

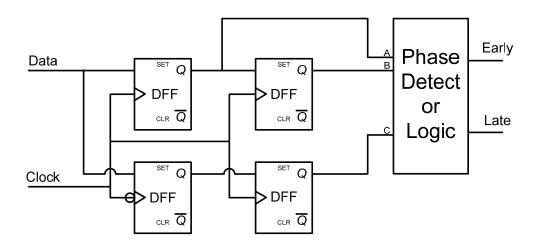

#### 2.3.2.1 Half-Rate Alexander Phase Detector

A half rate PD uses a clock with frequency equals to half of the bit rate. The key idea in a half-rate PD is to utilize the in-phase and quadrature phases of the half rate clock signal. A block diagram of a half-rate Alexander PD is shown in Figure 2-12.

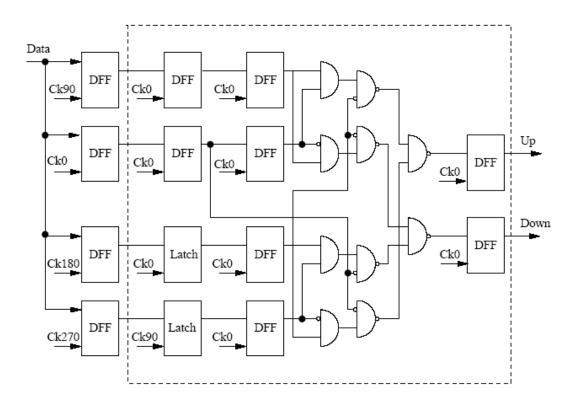

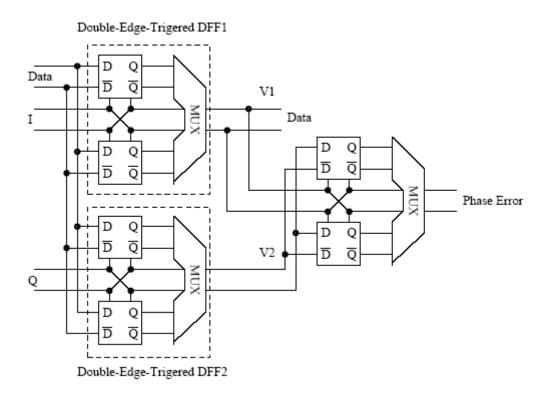

Figure 2-12: Half-Rate Alexander phase detector.

The proper selection of the PD logic is important for the operation of the circuit in high bit rates. The logic should be simple in order to decrease the delay in the loop. Also, the logic circuits should have a symmetric structure to make the delays in the PD matched. Haueneschild in [24] uses a complicated logic that increases the delays in the PLL loop (Figure 2-13). Haueneschild's phase detector has also been implemented in CMOS technology [21]. Ramezani [26] implements a half-rate Alexander PD with a simple logic (Figure 2-14). The AND gates inputs of this circuit are not symmetric, and, hence, it is difficult to match the signal paths through the AND gate.

Figure 2-13: Haueneschild's phase detector.

Figure 2-14: Ramezani's half-rate phase detector.

#### 2.3.2.2 Anderson's Phase Detector

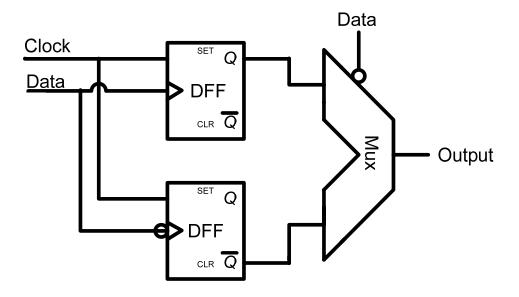

A binary version of Anderson's phase detector [19] was used by Savoj in [30]. This phase detector (shown in Figure 2-15) consists of two double-edge triggered DFFs. If during any two sequential in-phase clock edges, any data transition happens, the output of the upper DFF complements. Note that this transition is in-phase with the clock and triggers the output DFF.

The output DFF, using the information provided by DFF2, makes the *up* or *down* decision. Note that DFF2 samples the data at quadrature clock edges. If a data transition happens, the output of DFF2 identifies whether the data has gone from either high to low or from low to high.

Figure 2-15: Anderson's half-rate phase detector.

Savoj's version of Anderson's phase detector suffers from its two-state behavior. If no data transition occurs, the phase detector keeps its previous state and continually outputs either up or down signal. This causes a significant amount of data-dependent jitter. This phase detector can be modified as shown in Figure 2-16 [28]. This modified version of

Anderson's phase detector is a three-state PD and produces less data-dependent jitter. A linear version of Anderson's phase detector has also been implemented [20].

This phase detector utilizes sample and hold (SAH) blocks instead of DFF and hence has a linear behavior.

Figure 2-16: Modified half-rate Anderson's phase detector

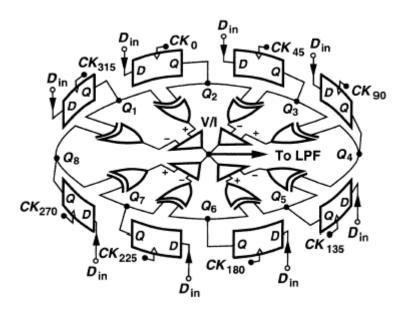

## 2.3.2.3 Binary 1/4 Rate-Phase Detector

Another fractional phase detector was published in [25], the proposed architecture employs a clock whose frequency is 1/4 of the full-rate phase detector frequency. This phase

detector (shown in Figure 2-17) is very similar to Alexander phase detector. The PD compares every two consecutive samples by means of an XOR gate, generating a 1 if an edge has occurred. To determine the polarity of the phase error from three consecutive samples, the outputs of two XORs are applied to a voltage to current (V/I) converter, which produces a net current if its inputs are unequal. In lock condition, every other sample serves as a retimed and demultiplexed output.

Figure 2-17: Lee's 1/4 Rate-Phase Detector.

It is important to note that, in the absence of data transitions, the DFFs generate equal outputs, and each V/I converter produces a zero current, in essence presenting a tri-state (high) impedance to the oscillator control. This is in contrast to other bang-bang topologies [32], [29] that continue to apply a high or low logic level to the VCO during long runs. Therefore, it creates a potentially high jitter at the output [25].

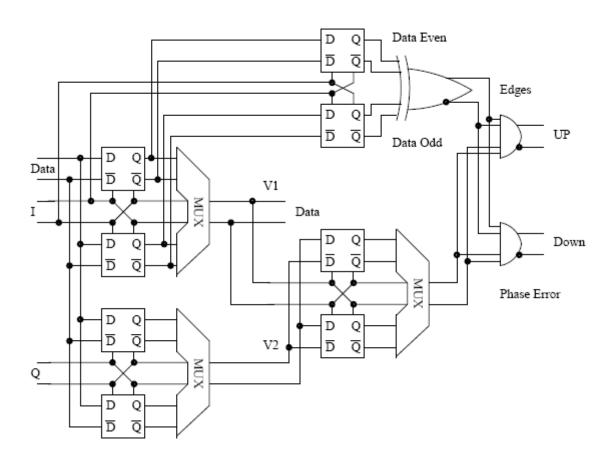

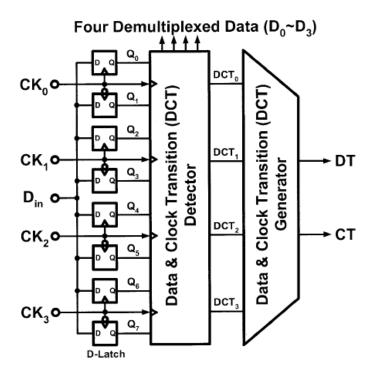

#### 2.3.2.4 Linear 1/8-Rate Phase Detector

Figure 2-18 shows the block diagram of the linear 1/8-rate PD. It consists of eight data sampling latches, a data and clock transition (DCT) detector, and a DCT generator. The linear 1/8-rate PD accomplishes three tasks with no systematic offset: data transition detection, linear phase error detection, and data regeneration. In the latch stage, the incoming NRZ data stream is sampled in each bit at every rising and falling edges of the four half-quadrature clocks. Then, the DCT detector generates the four DCT signals (DCT0–DCT3) and provides the retimed data output (D0-D3) which are the 1:4 demultiplexed data. With the incoming four DCT signals, the DCT generator produces the DT and CT signals to determine the phase error between the data and the clock [31].

Figure 2-18: Linear 1/8 Rate-Phase Detector.

#### 2.3.2.5 Binary 1/8 Rate Phase Detector

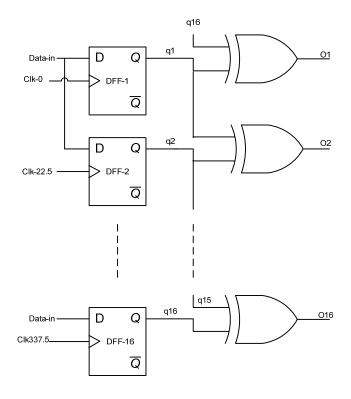

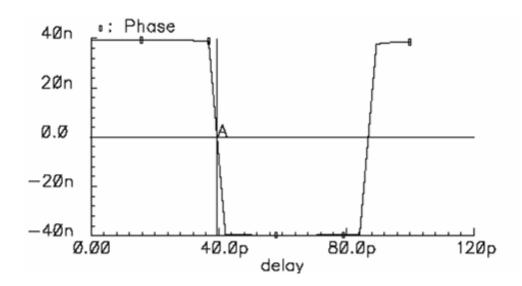

The structure of the proposed 1/8 rate PD is shown in Figure 2-19. The input data signal is applied to 16 master/slave DFFs. Sixteen different clocks are used (together with their complements), where each clock is offset by 22.5 degrees with respect to the adjacent clocks. The phase detector is an improved version of the digital 1/4-rate phase detector published in [25]. Figure 2-20 shows a 10Gbps 1/8-rate binary phase detector characteristic in 0.18µm CMOS process.

Figure 2-19: Proposed binary 1/8-rate-phase detector.

Figure 2-20: 10Gbps phase detector characteristic.

## 2.4 Voltage-Controlled Oscillators

A Voltage-Controlled Oscillator (VCO) generates the clock signal in a CDR circuit. The design of the VCO directly impacts the jitter performance of the CDR system. The two common methods for designing VCOs for CDR applications are the LC topology; and the ring oscillator.

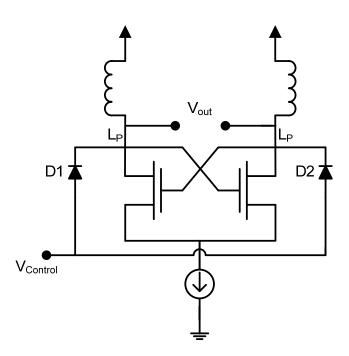

#### 2.4.1 LC Based VCO

The majority of the LC oscillators have a structure similar to the one shown in Figure 2-21 [1], [34], [27]. Due to the narrow bandwidth of the LC-tank, the oscillator inevitably has a frequency that is equal to the tuned frequency of the tank as long as the gain of the circuit is larger than one. To tune the oscillator, a varactor is used in conjunction with LC

structure. Changing the control voltage (V<sub>C</sub>) changes the varactor capacitance and it results in variation of the LC oscillator center frequency.

Figure 2-21: Schematic of an LC-tank oscillator.

With an LC based VCO it is possible to achieve frequencies close to f<sub>MAX</sub> (Transistor cutoff frequency). The disadvantages of using an inductor are the large chip area and the

process dependency. Furthermore, this type of VCOs does not provide a wide frequency

range to compensate for process and temperature variations and usually needs design and

fabrication iteration to achieve the desired frequency range. An LC-based VCO is suitable

for application with strict phase noise or jitter requirements such as SONET regenerators

[34]. This structure is not economical for LAN applications.

### 2.4.2 Ring Oscillator VCO

A ring oscillator is formed by using a cascade of odd number of single-ended gain stage in a loop. At the frequency of oscillation total phase shift is 180° and the loop gain of the system is larger than one. An even number of differential delay cells is commonly used for the ring oscillator VCOs to provide quadrature signals in communications circuits. To make the total phase shift of 180°, in an even number differential delay cells, it is necessary to flip the output of one of the delay cells before closing the loop. The schematic of a fourstage differential ring oscillator is shown in Figure 2-22. Parasitic capacitors are usually used with active resistors to provide the phase shift. Control voltage changes the size of the active resistor to change the phase shift and as a result the frequency variation of the oscillator. A ring oscillator VCO has a lower center frequency and larger phase noise compared to an LC based VCO. However, the ring oscillator consumes less chip area and is more suitable for implementation in a CMOS process. Also, the operating frequency of the ring oscillator VCO can be changed faster than the LC one. This makes the ring oscillator VCOs preferable in a binary CDR, where the small delay of the closed loop results in less jitter generation. A ring oscillator VCO is a better choice for applications that do not have strict phase noise or jitter transfer requirements such as LAN [33].

Figure 2-22: Schematic of a four-stage differential ring oscillator.

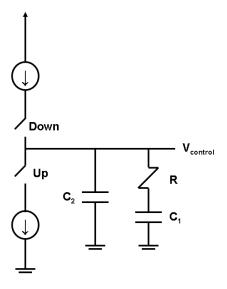

# 2.5 Loop Filter and Charge pump

PLLs based on charge-pumps exhibit a number of desired features. First, they do not exhibit false lock. Second, when the system is in lock, the phase error between the VCO output and the input data becomes almost zero [35]. A simple block diagram of a charge-pump PLL [37] is shown in Figure 2-23. The phase detector produces *up* or *down* signals, and the charge-pump injects or extracts the charge stored across the capacitors in the LPF. If the phase detector can not make correct decision about the phase error, no up or down signals should be generated. In this case, the charge-pump does not change the charge of the LPF capacitors, and, hence, leaves the VCO control voltage unchanged.

Figure 2-23: Simple Charge-Pump and Loop-Filter.

The charge-pump PLL loop dynamics can be simplified as follows. It is necessary to assume that the phase error between the VCO output signal and input signal does not vary rapidly. In other words the frequency error is small. In this case, the average current flowing through LPF will be:

$$I_{Avg} = \frac{\Delta \phi_{in}}{2\pi} I_{Ch} \tag{2-2}$$

where the  $I_{Ch}$  is the charge pump current. Without considering the effect of  $C_2$ , which is usually very small compared to  $C_1$ , the voltage over the LPF will be:

$$V_{LPF}(s) = I_{Avg}(s) \frac{1 + sRC_1}{sC_1}$$

(2-3)

The necessary stabilizing zero is provided by the resistor. Every time the charge-pump switches are turned on, the charge-pump current flows through the resistor, which is in series with the capacitor. This creates a ripple in the VCO control voltage. This voltage ripple will then modulate the VCO and add jitter to the recovered clock. The resistor in the LPF is necessary for the PLL loop stability and can not be deleted. In order to suppress these ripples, a smaller capacitor ( $C_2$ ) is added. The value of  $C_2$  is normally 1/20 of  $C_1$  or even smaller [28]. Introducing this second capacitor decreases the jitter significantly, however, it makes the CDR a third order system. Because  $C_2$  is small, the pole due to this second capacitor is far from the loop resonant frequency, and second order approximation for the loop transfer function is valid [17], [36].

## Reference

- [1] Savoj, J.; Razavi, B., High-Speed CMOS Circuits for Optical Receivers, Kluwer, 2001.

- [2] Walker, R., "Clock and Data Recovery for Serial Digital Communication," short course, Solid-State Circuits, 2006 IEEE International Conference, 2002.

- [3] Gardner, F. M., Phaselock Techniques, Second Edition, NewYork, Wiley and Sons, 1979.

- [4] Best, R. E., Phase-Locked Loops, Second Edition, McGraw-Hill, 1993.

- [5] Pottbacker, A.; Langmann, U.; Schreiber, H.-U., "A Si bipolar phase and frequency detector IC for clock extraction up to 8 Gb/s," Solid-State Circuits, IEEE Journal of, vol.27, no.12, pp.1747-1751, Dec 1992.

- [6] Razavi, B., "Design of Integrated Circuits for Optical Communications," McGraw Hill, 2003.

- [7] Ginzton, E.L.; Hewlett, W.R.; Jasberg, J.H.; Noe, J.D., "Distributed Amplification," Proceedings of the IRE, vol.36, no.8, pp. 956-969, Aug. 1948.

- [8] Beyer, J.B.; Prasad, S.N.; Becker, R.C.; Nordman, J.E.; Hohenwarter, G.K., "MESFET Distributed Amplifier Design Guidelines," Microwave Theory and Techniques, IEEE Transactions on, vol.32, no.3, pp. 268-275, Mar 1984.

- [9] Hajimiri, A., "Distributed integrated circuits: an alternative approach to high-frequency design," Communications Magazine, IEEE, vol.40, no.2, pp.168-173, Feb 2002.

- [10] Wong, T., "Fundamentals of Distributed Amplification. Norwood", Artech House, 1993.

- [11] Strid, E.W.; Gleason, K.R., "A DC-12 GHz Monolithic GaAsFET Distributed Amplifier," Microwave Theory and Techniques, IEEE Transactions on, vol.82, no.7, pp. 969-975, Jul 1982.

- [12] Ayasli, Y.; Mozzi, R.L.; Vorhaus, J.L.; Reynolds, L.D.; Pucel, R.A., "A Monolithic GaAs 1-13-GHz Traveling-Wave Amplifier," Microwave Theory and Techniques, IEEE Transactions on, vol.82, no.7, pp. 976-981, Jul 1982.

- [13] Niclas, K.B.; Wilser, W.T.; Kritzer, T. R.; Pereira, R.R., "On Theory and Performance of Solid-State Microwave Distributed Amplifiers," Microwave Theory and Techniques, IEEE Transactions on, vol.83, no.6, pp. 447-456, Jun 1983.

- [14] Niclas, K.B.; Remba, R.D.; Pereira, R.R.; Cantos, B.D., "The Declining Drain Line Lengths Circuit--A Computer Derived Design Concept Applied to a 2 26.5-GHz Distributed Amplifier," Microwave Theory and Techniques, IEEE Transactions on , vol.34, no.4, pp. 427-435, Apr 1986.

- [15] Alexander, S. B., "Optical Communication Receiver Design," Tutorial Texts in Optical Engineering, vol. TT22, 1997.

- [16] Hogge, C.R., Jr., "A self correcting clock recovery circuit," Electron Devices, IEEE Transactions on , vol.32, no.12, pp. 2704-2706, Dec 1985.

- [17] Lee, T.H.; Bulzacchelli, J.F., "A 155-MHz clock recovery delay- and phase-locked loop," Solid-State Circuits, IEEE Journal of, vol.27, no.12, pp.1736-1746, Dec 1992.

- [18] Alexander, J.D.H., "Clock recovery from random binary signals," Electronics Letters, vol.11, no.22, pp.541-542, October 30 1975.

- [19] Alexander, J. D. H., "Transition Tracking Bit Synchronization System", U.S. Patent 626 298, Dec. 1971.

- [20] Buchwald, A. W., "Design of Integrated Fiber-Optic Receivers Using Hetero-junction Bipolar Transistors," Ph.D. Thesis, Department of Electrical Engineering, University of California, Los Angeles, Jan. 1993.

- [21] Rogers, J.E.; Long, J.R., "A 10-Gb/s CDR/DEMUX with LC delay line VCO in 0.18-/spl mu/m CMOS," Solid-State Circuits, IEEE Journal of, vol.37, no.12, pp. 1781-1789, Dec 2002.

- [22] Walker, R.C.; Stout, C.L.; Wu, J.-T.; Lai, B.; Yen, C.-S.; Hornak, T.; Petruno, P.T., "A two-chip 1.5-GBd serial link interface," Solid-State Circuits, IEEE Journal of, vol.27, no.12, pp.1805-1811, Dec 1992.

- [23] Lai, B.; Walker, R.C., "A Monolithic 622Mb/s Clock Extraction Data Retiming Circuit," Solid-State Circuits Conference, 1991. Digest of Technical Papers. 38th ISSCC., 1991 IEEE International, vol., no., pp.144-306, 13-15 Feb 1991.

- [24] Hauenschild, J.; Dorschky, C.; Von Mohrenfels, T.W.; Seitz, R., "A 10 Gb/s BiCMOS clock and data recovering 1:4-demultiplexer in a standard plastic package with external VCO," Solid-State Circuits Conference, 1996. Digest of Technical Papers. 43rd ISSCC., 1996 IEEE International, vol., no., pp.202-203, 445, Feb 1996.

- [25] Lee, J,.; Razavi, B., "A 40-Gb/s clock and data recovery circuit in 0.18-/spl mu/m CMOS technology," Solid-State Circuits, IEEE Journal of, vol.38, no.12, pp. 2181-2190, Dec. 2003.

- [26] Ramezani, M.; Salama, C.A.T., "An improved bang-bang phase detector for clock and data recovery applications," Circuits and Systems, 2001. ISCAS 2001. The 2001 IEEE International Symposium on , vol.1, no., pp.715-718 vol. 1, 6-9 May 2001.

- [27] Ramezani, M., "Designing an Integrated Fiber Optic Receiver in a Deep Sub-micron CMOS Process," PhD thesis, University of Toronto, 2003.

- [28] Rezayee, A.; Martin, K., "A 10–Gb/s clock recovery circuit with linear phase detector and coupled two–stage ring oscillator," Solid-State Circuits Conference, 2002. ESSCIRC 2002. Proceedings of the 28th European, vol., no., pp. 419-422, 24-26 Sept. 2002.

- [29] Savoj, J.; Razavi, B., "A 10-Gb/s CMOS clock and data recovery circuit with a half-rate linear phase detector," Solid-State Circuits, IEEE Journal of, vol.36, no.5, pp.761-768, May 2001.

- [30] Savoj, J.; Razavi, B., "A 10 Gb/s CMOS clock and data recovery circuit with frequency detection," Solid-State Circuits Conference, 2001. Digest of Technical Papers. ISSCC. 2001 IEEE International, vol., no., pp.78-79, 434, 2001.

- [31] Seong-Jun Song; Sung Min Park; Hoi-Jun Yoo, "A 4-Gb/s CMOS clock and data recovery circuit using 1/8-rate clock technique," Solid-State Circuits, IEEE Journal of, vol.38, no.7, pp. 1213-1219, July 2003.

- [32] Soyuer, M., "A monolithic 2.3-Gb/s 100-mW clock and data recovery circuit in silicon bipolar technology," Solid-State Circuits, IEEE Journal of, vol.28, no.12, pp.1310-1313, Dec 1993.

- [33] Kishine, K.; Ishihara, N.; Takiguchi, K.; Ichino, H., "A 2.5-Gb/s clock and data recovery IC with tunable jitter characteristics for use in LANs and WANs," Solid-State Circuits, IEEE Journal of, vol.34, no.6, pp.805-812, Jun 1999.

- [34] Jun Cao; Momtaz, A.; Vakilian, K.; Green, M.; Chung, D.; Keh-Chee Jen; Caresosa, M.; Tan, B.; Fujimori, I.; Hairapetian, A., "OC-192 receiver in standard 0.18/spl mu/m CMOS," Solid-State Circuits Conference, 2002. Digest of Technical Papers. ISSCC. 2002 IEEE International, vol.2, no., pp.200-471, 2002.

- [35] Johns, D.; Martin, K., Analog Integrated Circuit Design, John Wiley, 1997.

- [36] Mijuskovic, D.; Bayer, M.; Chomicz, T.; Garg, N.; James, F.; McEntarfer, P.; Porter, J., "Cell-based fully integrated CMOS frequency synthesizers," Solid-State Circuits, IEEE Journal of, vol.29, no.3, pp.271-279, Mar 1994.

- [37] Gardner, F., "Charge-Pump Phase-Lock Loops," Communications, IEEE Transactions on, vol.28, no.11, pp. 1849-1858, Nov 1980.

# Chapter 3

# Analysis of CDR Circuit

## 3.1 Introduction

The PLL based CDR is a non-linear system and mathematical analysis is quite difficult. A non-linear theory that could adequately explain the behavior of the loop has not been published yet. The analog CDR analysis can be categorized in two groups:

- 1) Analog CDR: when the phase detector is linear and the loop filter is analog circuit.

- 2) Hybrid CDR: when the phase detector is binary and the loop filter is analog circuit.

## 3.2 Analog CDR

An analog CDR (analog PLL) can be classified based on the number of integrator and the loop filter order. In general, type of PLL is dictated by number of integrators in the loop plus one [1].

## 3.2.1 Analog CDR Type I

The analysis of analog CDR (or analog PLL) can be divided in two conditions, locked condition and un-locked (tracking) condition.

In the locked condition, a CDR can be analyzed by approximating each block with a linear transfer function.

The time domain function of a VCO is given by:

$$f_o(V_C) = f_c + K_{VCO}V_C$$

(3-1)

As the phase detector operates in phase domain, the VCO phase domain equation can be derived as:

$$\omega_o(V_C) = \omega_c + K_V V_C \tag{3-2}$$

The integral of  $\omega_0$  over the time results in the phase of the VCO.

$$\Delta \omega_o = K_V \Delta V_C \tag{3-3}$$

$$\Delta \varphi_o = \int \Delta \omega_o dt = K_V \int \Delta V_C dt \tag{3-4}$$

Using Laplace transform (3-4) can be derived as

$$H_{VCO}(s) = \frac{\varphi_o(s)}{V_C(s)} = \frac{K_V}{s}$$

(3-5)

On the other hand, phase domain function of a linear phase detector can be given by:

$$\varphi_{PD} = K_{\sigma}(\varphi_r - \varphi_o) = K_{\sigma}\varphi_e \tag{3-6}$$

then

$$H_{PD}(s) = K_{\varphi} \varphi_e \tag{3-7}$$

Nevertheless, the low pass filter transfer function is

$$H_{LPF}(s) = \frac{1}{1 + \frac{s}{\omega_{LPF}}}$$

(3-8)

Bringing these equations into play results a linear model for analog PLL in lock condition (shown in Figure 3-1).

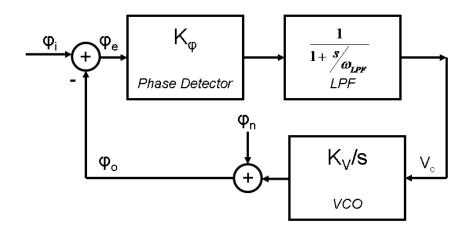

Figure 3-1: Linear model of an analog CDR.

The open loop transfer function, G(s), can be derived as:

$$G(s) = K_{\varphi} \left( \frac{1}{1 + \frac{s}{\omega_{LPF}}} \right) \frac{K_{V}}{s}$$

(3-9)

or

$$G(s) = K \frac{1}{s^2 / \omega_{LPF} + s}$$

(3-10)

where K is the loop gain.

$$K = K_{\phi} K_{V} \tag{3-11}$$

According to the (3-9, 3-10, and 3-11) there is one pole at  $s = -\omega_{LPF}$  and another at s = 0. It can be observed that for low frequency (small s) open loop gain goes to infinity due to existing of a pole at origin. In this case, the feedback circuit passes the small changes in the  $\phi_i$  to the  $\phi_o$ . In other words, if the input excess phase varies very slowly, the output excess phase "track" it. However, if the transients in  $\phi_i$  have decayed, then the change in  $\phi_o$  is precisely equal to the change in  $\phi_i$  [2].

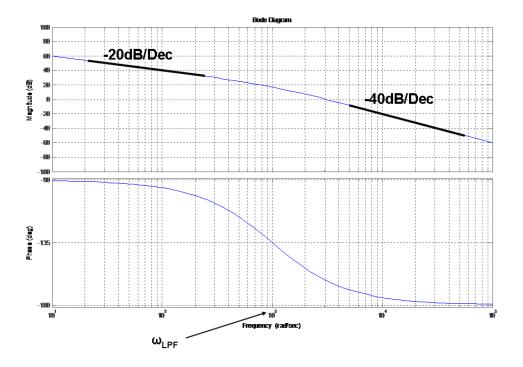

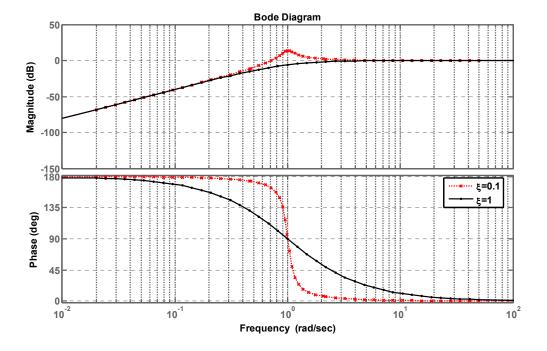

Bode plot of an analog CDR based on (3-10) is shown in Figure 3-2. The closed loop transfer function can be written as:

$$H_{Closed-Loop}(s) = \frac{G(s)}{1 + G(s)}$$

(3-12)

$$H(s) = \frac{\varphi_o}{\varphi_{in}}(s) = \frac{K_{\phi}K_V}{\frac{s^2}{\omega_{LPF}} + s + K_{\phi}K_V}$$

(3-13)

Figure 3-2: Bode plots for analog CDR.

Equation 3-13 can be rewrite in the form of

$$H(s) = \frac{\omega_n}{s^2 + 2\xi \omega_n s + {\omega_n}^2}$$

(3-14)

where

$$\omega_n = \sqrt{\omega_{LPF} K_{\varphi} K_V} \tag{3-15}$$

$$\xi = \frac{1}{2} \sqrt{\frac{\omega_{LPF}}{K_{\varphi} K_{V}}} \tag{3-16}$$

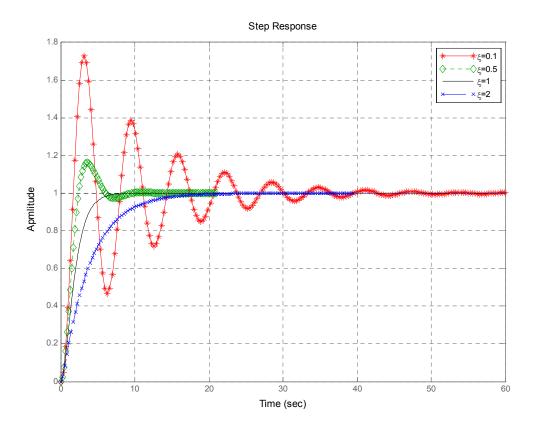

The close loop transfer function has two poles (3-17). If  $\xi > 1$ , both poles are real and system is over-damped. If  $\xi < 1$ , system is under-damped and the poles are complex furthermore the response to an input frequency step  $\omega_{in} = \Delta \omega u(t)$  is equal to

$$\omega_{out}(t) = \left[1 - \frac{1}{\sqrt{1 - \xi^2}} e^{-\xi \omega_n t} \sin(\omega_n \sqrt{1 - \xi^2} t + \theta)\right] \Delta \omega u(t)$$

(3-17)

Figure 3-3: Step response for an analog CDR.

Phase error transfer function can be derived as:

$$H_{e}(s) = \frac{\varphi_{e}}{\varphi_{i}}(s) = \frac{s^{2} + 2\xi\omega_{n}s}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

(3-18)

Above equations show  $K=K\phi.K_V$  and  $\omega_{LPF}$  cannot be chosen independently. As phase error and damping factor are inversely proportional to K; lowering the phase error inevitably makes the system less stable. These constraints translate to significant phase error between the input and the output as well as a narrow capture range [3]. In summary the analog CDR type-I suffers from trade-offs between the settling time, the ripple on the control voltage of the oscillator, the phase error and stability [2].

Figure 3-4: Bode diagrams of the error transfer function.

## 3.2.2 Analog CDR Type-II

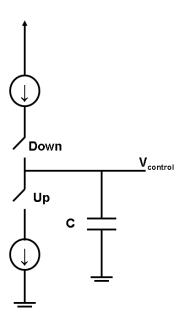

The analysis of Analog CDR Type-I (section 3.2.1) shows some shortcomings such as limited acquisition range, and trade-offs between damping factor and  $\omega_{LPF}$ . Analog CDR type II is used in many modern applications to have more freedom to chose the PLL parameters such as damping factor and  $\omega_{LPF}$  separately. Figure 3-5 shows a charge pump with associated capacitor.

Figure 3-5: Charge pump and capacitor.

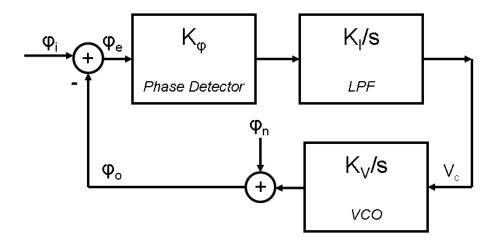

The linear model for analog CDR with phase detector and charge pump loop filter is shown in Figure 3-6.

Figure 3-6: Analog CDR linear model block diagram.

The transfer functions of phase detector, charge-pump and loop filter are given by:

$$H_{LPF}(s) = \frac{K_I}{s} \tag{3-19}$$

where

$$K_I = \frac{1}{C} \tag{3-20}$$

and

$$K_{\phi} = \frac{I_{CP}}{2\pi} \tag{3-21}$$

The open loop transfer function is derived as:

$$G(s) = \frac{K_{VCO}K_{\varphi}K_I}{s^2} \tag{3-22}$$

Therefore, close loop transfer function is equal to

$$H(s) = \frac{K_{VCO} K_{\varphi} K_{I}}{s^{2} + K_{VCO} K_{\varphi} K_{I}}$$

(3-23)

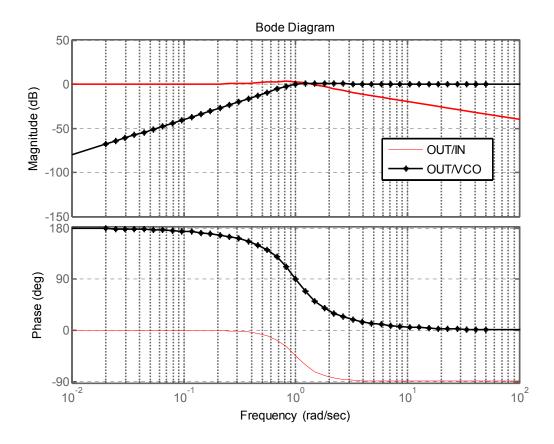

Figure 3-2 shows Bode diagrams for analog CDR with charge pump.

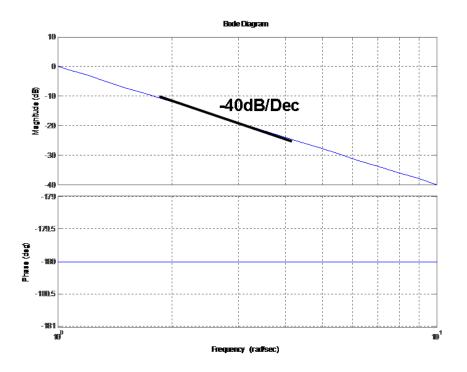

Figure 3-7: Bode diagram for analog CDR with charge pump.

As Bode diagrams show, the two poles results in -180° phase shift allowing the system to oscillate at the gain cross over frequency. To make the system stable we need to decrease the absolute phase shift and one can add a zero to the system.

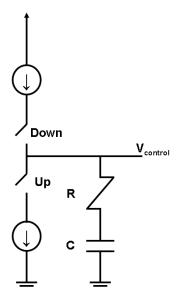

Figure 3-8 shows the block diagram of PLL based CDR with the new loop filter.

Figure 3-8: charge pump with new loop filter.

The modified loop filter has the transfer function of

$$H_{LPF}(s) = K_p + \frac{K_I}{s}$$

(3-24)

then the open loop transfer function is changed to

$$G(s) = \frac{K_{VCO}K_{\varphi}(K_{p} + \frac{K_{I}}{s})}{s} = \frac{K_{VCO}K_{\varphi}(K_{p}s + K_{I})}{s^{2}}$$

(3-25)

Therefore, the close loop transfer function is equal to

$$H(s) = \frac{K(1 + \frac{s}{z})}{s^2 + K\frac{s}{z} + K}$$

(3-26)

where

$$K = K_{VCO} K_{\varphi} K_{I} \tag{3-27}$$

$$z = \frac{K_I}{K_p} \tag{3-28}$$

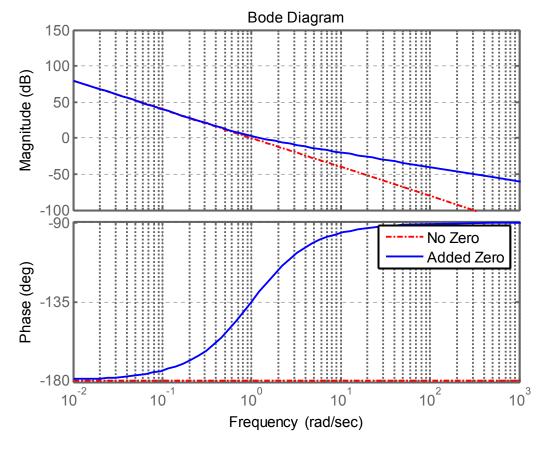

Bode diagrams for two different systems one with zero and one with added zero are shown in Figure 3-9. It shows that added zero is able to compensate the phase shift and makes the system stable.

Figure 3-9: Bode diagrams for system with zero and without zero.

Equations (3-25) and (3-26) can be rewritten in the form of

$$G(s) = \frac{2\xi\omega_n s + \omega_n^2}{s^2}$$

(3-29)

and

$$H(s) = \frac{2\xi\omega_{n}s + \omega_{n}^{2}}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

(3-30)

where

$$\omega_n = \sqrt{K_I K_{\varphi} K_V} = \sqrt{\frac{I_{IP} K_V}{2\pi C}}$$

(3-31)

$$\xi = \frac{\omega_n}{2} \frac{K_P}{K_I} = \frac{R}{2} \sqrt{\frac{I_{IP} K_V C}{2\pi}}$$

(3-32)

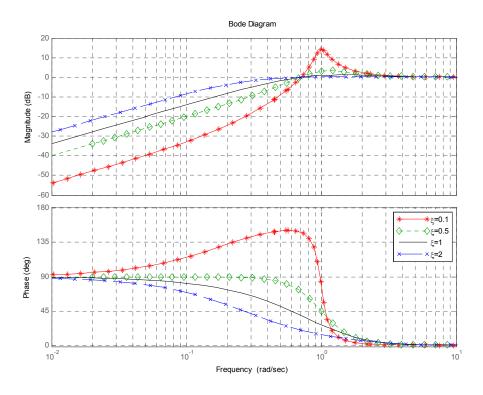

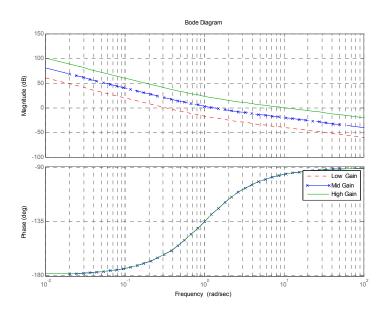

The closed loop transfer function has two poles and stability analysis is quite similar to type-I. However, Figure 3-10 demonstrates that increasing the open loop gain (K) (3-27) increases the phase margin and system moves toward more stability [4].

Figure 3-10: Open loop transfer function with different loop gains.

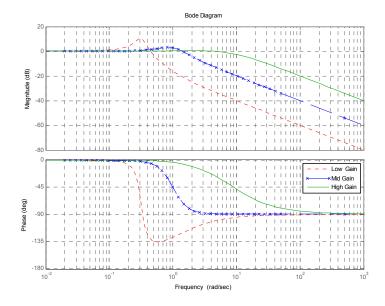

Figure 3-11: Close loop Bode diagram with different loop gains.

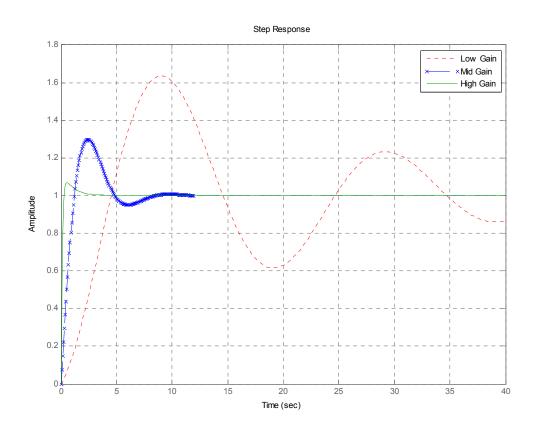

Figure 3-12: Step response to close loop system with different loop gains.

The compensation method (adding a zero) suffers from a critical draw back. Since the charge pump drives the series combination of resistor and capacitor, each time a current is injected into the loop filter; the control voltage experiences a large jump. Even in lock condition there could be an injected current, as a result of mismatch between up and down current sources and clock feed through. A second capacitor (C<sub>E</sub>) in parallel to the RC network should be added to the loop to suppress the initial step. Now the loop filter is 2<sup>nd</sup>

order, yielding a 3<sup>rd</sup> order PLL-based CDR. If C<sub>E</sub> is about one-tenth of C<sub>CP</sub>, the closed-loop time frequency remain relatively unchanged [2].

The error transfer function can be derived as

$$H_{E}(s) = \frac{s^{2}}{s^{2} + 2\xi\omega_{n}s + \omega_{n}^{2}}$$

(3-33)

Figure 3-13: Bode diagrams for error transfer function.

Bode diagram of the error transfer function (Figure 3-13) shows the high frequency noise (jitter) from the VCO can travel to the output. Figure 3-14 conceptually summarizes the response of PLL based CDR to input jitter and VCO jitter. Depending on the application

one or both sources may be significant, requiring an optimum choice of the loop band width.

Figure 3-14: Filtering the input jitter and VCO jitter.

## 3.3 Hybrid CDR

The hybrid CDR employs the binary phase detector and analog loop filter to recover the synchronous clock with input data. The hybrid CDR can be categorized based on the number of the integrator in the loop as follows.

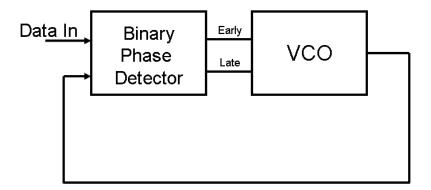

#### 3.3.1 First order hybrid CDR

The 1<sup>st</sup> order hybrid CDR employs the binary (Bang-Bang) phase detector. The binary phase detector is able to provide only early or later phase information. This non-linearity in the loop structure leads to an oscillatory steady-state and rendering the circuit unanalyzable with standard linear PLL theory [5].

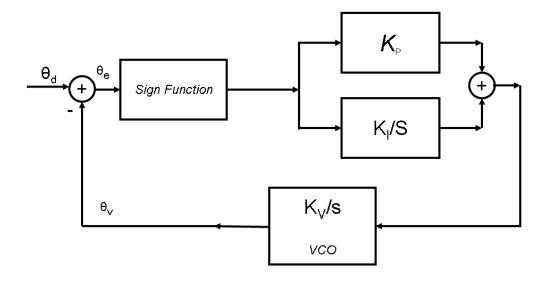

The block diagram and linear model of a 1<sup>st</sup>-order hybrid CDR are shown in Figure 3-15 and Figure 3-16, respectively.

Figure 3-15: The first order hybrid CDR.

Figure 3-16: Phase linear model of the 1st order hybrid CDR.

According to [5] and [6], the  $\theta_n$  is defined as the difference between the data phase  $\theta_d$  and the VCO phase  $\theta_V$ . The frequency of the incoming data differs from the VCO center frequency by  $\delta f$ . The phase detector is binary phase detector therefore

$$\varepsilon_n = sign[\theta_e(t_n)] \tag{3-34}$$

then the VCO frequency is given by

$$f_{VCO} = f_{nom} + \varepsilon_n f_{bb} \tag{3-35}$$

where f<sub>bb</sub> is frequency variation range of the VCO and typically is around 0.1% of f<sub>nom</sub>.

The loop time domain equation can be derived as

$$\theta_V(t_{n+1}) = \theta_V(t_n) + \theta_{bb} \operatorname{sign}[\theta_d(t_n) - \theta_V(t_n)]$$

(3-36)

and the lock range is

$$-f_{bb} \le \delta f \le +f_{bb} \tag{3-37}$$

Meanwhile, the peak-to-peak jitter is given by

$$J_{PP} = 4\pi \frac{f_{bb}}{f_{nom}} \tag{3-38}$$

Equation 3-35 is a starting point for designing the CDR.

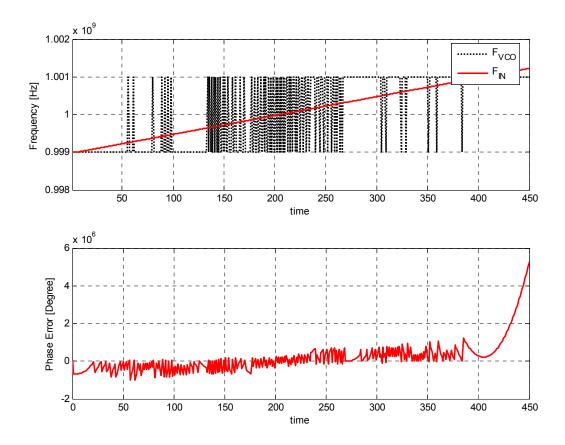

Figure 3-17 depicts simulink simulation results showing the locking range and jitter in lock condition. CDR is in locking range and generates relatively small jitter at the output around time interval of 150 to 250. However, when the input frequency passes the upper limit

(1.0005 GHz) the CDR is not able to lock to the frequency and results in output jitter growth.

Figure 3-17: Simulink simulation of 1st order hybrid CDR.

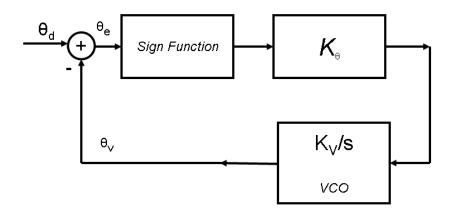

#### 3.3.2 Second-order hybrid CDR

The first-order hybrid CDR has only one degree of freedom. All the parameters are controlled by one parameter,  $f_{bb}$ . To overcome this problem, employing a second control loop to dynamically adjust the nominal VCO frequency is suggested.

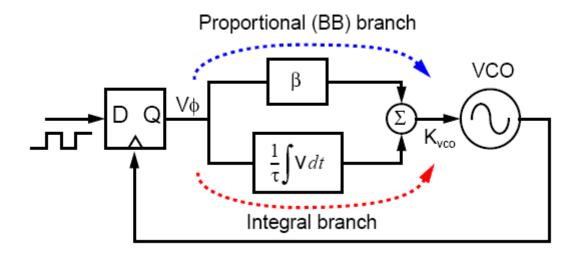

The schematic of a second-order hybrid CDR is shown in Figure 3-18 [5] and corresponding phase model block diagram is shown in Figure 3-19.

Figure 3-18: Block diagram of the 2<sup>nd</sup>-order hybrid CDR [6].

Figure 3-19: phase model for 2<sup>nd</sup>-order hybrid CDR.

The loop equation can be derived as

$$\theta_{V}(t_{n+1}) = \theta_{V}(t_{n}) + \theta_{bb} \left[ \varepsilon_{n} + \frac{\varepsilon_{n}}{\xi} + \frac{2}{\xi} \sum_{n=0}^{n} \varepsilon_{n} \right]$$

(3-39)

$$\varepsilon_n = sign[\theta_d(t_n) - \theta_V(t_n)] \tag{3-40}$$

By adding second path to system, now the VCO frequency is a function of two paths: integral path and bang-bang (proportional) path. The second integral makes the system vulnerable to oscillate. Walker in [5] introduced a stability factor for the system as  $\xi$ .

$$\xi = \frac{\Delta \theta_{Bang-Bang}}{\Delta \theta_{Integral}} = \frac{K_P K_V V_{\phi} t_{update}}{K_I K_V V_{\phi} t_{update}^2} = \frac{2K_P}{K_I t_{update}}$$

(3-41)

If  $\xi$  is greater than 1, the proportional and integral path can be considered non-interacting as long as system is not in slew rate limiting. If  $\xi$  is less than 1, the proportional path does not stabilize the system and large low frequency oscillation may occur [7].

### Reference

- [1] Margaris, N. I., "Theory of the Non-linear Analog Phase Locked Loop," Springer, 2004.

- [2] Razavi, B., "Design of Integrated Circuits for Optical Communications," McGraw Hill, 2003.

- [3] Zhang, R., "Clock and Data Recovery Circuit," PhD Thesis, Washington State University, Aug. 2004.

- [4] Wang, H., "A CMOS Clock and Data Recovery Circuit for Giga-bit/s Serial Data Communication," PhD Thesis, University of Southern California, Aug. 1998.

- [5] Walker, R. C., "Designing bang-bang PLLs for clock and data recovery in serial data transmission systems," in Phase-Locking in High-Performance Systems, B. Razavi, Ed.. New York: IEEE Press, 2003, pp.34–45.

- [6] Walker, R., "Clock and Data Recovery for Serial Digital Communication," short course, Solid-State Circuits, 2006 IEEE International Conference, 2002.

- [7] Rogers J. E., "A 10 Gb/s CDR/DEMUX with LC Dealy Line VCO in 0.18μm CMOS," MASc Thesis, University of Toronto.

# Chapter 4

# **Power Reduction Strategies**

### 4.1 Introduction

Advances in technology and the introduction of high-speed processors have increased the demand for fast, compact and commercial methods for transferring large amounts of data.

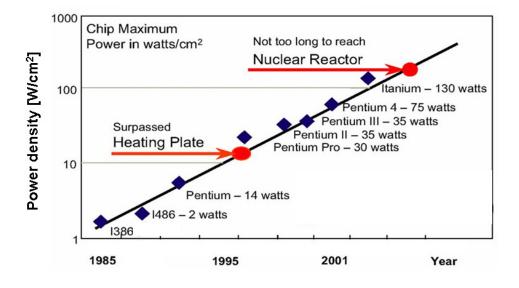

Figure 4-1: power vs. performance over years [1].

Meanwhile, the higher data rate dictates higher power consumption, while thermal and battery-life requirements are demanding lower power consumption.