## Variability-Aware Design of Subthreshold Devices

by

#### Rodrigo Jaramillo Ramirez

A thesis

presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science

in

Electrical and Computer Engineering.

Waterloo, Ontario, Canada, 2007 ©Rodrigo Jaramillo Ramirez, 2007

#### Abstract

Over the last 10 years, digital subthreshold logic circuits have been developed for applications in the ultra-low power design domain, where performance is not the priority. Recently, devices optimized for subthreshold operation have been introduced as potential construction blocks. However, for these devices, a strong sensitivity to process variations is expected due to the exponential relationship of the subthreshold drive current and the threshold voltage. In this thesis, a yield optimization technique is proposed to suppress the variability of a device optimized for subthreshold operation. The goal of this technique is to construct and inscribe a maximum yield cube in the 3-D feasible region composed of oxide thickness, gate length, and channel doping concentration. The center of this cube is chosen as the maximum yield design point with the highest immunity against variations. By using the technique, a transistor is optimized for subthreshold operation in terms of the desired total leakage current and intrinsic delay bounds. To develop the concept of the technique, sample devices are designed for 90nm and 65nm technologies. Monte Carlo simulations verify the accuracy of the technique for meeting power and delay constraints under technology-specific variances of the design parameters of the device.

#### Acknowledgements

First of all, I thank God for giving me his guidance and the great family I have. I express my deepest gratitude to my parents, Margarita and Fernando. They have supported me, as always, with their love, advice, and generosity. To them I owe my values and achievements. Chavitos, gracias totales.

I am grateful to Norma Serna, whose love and support during the last two years have inspired me and lighted up this process. Specially, for her confidence and patient all along the difficult times we have gotten over.

This research project would not have been possible without the support of many people in the University of Waterloo. I am deeply grateful to my advisor, Dr. Mohab Anis, as when I started my M.A.Sc. I was a completely beginner in VLSI research, but he gave me the opportunity and honor to have a position in his group. His guidance and encouragement throughout these two years are of paramount importance in my graduate studies. I would also like to thank Javid Jaffari for being a good friend, a coworker, and specially a second mentor of this project, and to all my colleagues in the VLSI Research Group for their friendship and useful technical support. In addition, thanks to Professors Manoj Sachdev and John Hamel, members of my committee, for their confidence and valuable suggestions.

Also I would like to say a special thanks to Jazmin Romero for her advice and support. Thanks to her friendship my stay in Waterloo has been more pleasant and unforgettable.

An important person in this process has been Gerardo Leyva, he was the mastermind who suggested and encouraged me to study abroad. Thanks for being my teacher and excellent friend.

This research work has been supported by the National Council of Science and Technology (Consejo Nacional de Ciencia y Tecnologia, CONACyT, Mexico). This support is greatly appreciated.

## Contents

| 1 | Intr | roduction                                           | 1  |

|---|------|-----------------------------------------------------|----|

|   | 1.1  | Contribution of this Work                           | 3  |

|   | 1.2  | Organization of the Dissertation                    | 4  |

| 2 | Sub  | threshold Design: Background and Related Work       | 5  |

|   | 2.1  | Power Consumption                                   | 7  |

|   |      | 2.1.1 Static Power: Leakage Mechanisms              | Ć  |

|   |      | 2.1.2 Technology Scaling and Leakage Power          | 14 |

|   | 2.2  | MOS Transistor in the Subthreshold Region           | 19 |

|   | 2.3  | Subthreshold Circuits                               | 23 |

|   |      | 2.3.1 Origin and Evolution of Subthreshold Circuits | 25 |

|   | 2.4  | Process Variations                                  | 26 |

|   |      | 2.4.1 Process Variations in Subthreshold Designs    | 28 |

|   | 2.5  | Devices in Subthreshold Circuits                    | 30 |

|   | 2.6  | Summary                                             | 32 |

| 3 | Pro  | blem Definition and Yield Maximization Technique    | 33 |

|   | 3.1  | Design Parameters and Variations                    | 33 |

|   |      | 3.1.1 Device Structure and Constraints              | 3/ |

|     | 3.1.2                                  | Device Parameters and Variations                                                     | 38                                                                                                                                                                                                                               |

|-----|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2 | Proble                                 | em Statement and Yield Maximization Technique                                        | 43                                                                                                                                                                                                                               |

|     | 3.2.1                                  | General Problem Statement                                                            | 43                                                                                                                                                                                                                               |

|     | 3.2.2                                  | Qualitative Approach                                                                 | 44                                                                                                                                                                                                                               |

|     | 3.2.3                                  | Formal Problem Statement                                                             | 45                                                                                                                                                                                                                               |

| 3.3 | Summ                                   | ary                                                                                  | 50                                                                                                                                                                                                                               |

|     |                                        |                                                                                      |                                                                                                                                                                                                                                  |

| Res | ults ar                                | nd Discussion                                                                        | <b>51</b>                                                                                                                                                                                                                        |

| 4.1 | Imple                                  | nentation                                                                            | 51                                                                                                                                                                                                                               |

| 4.2 | Result                                 | s and Discussion                                                                     | 52                                                                                                                                                                                                                               |

| 4.3 | Optim                                  | izing a Subthreshold Transistor                                                      | 62                                                                                                                                                                                                                               |

| 4.4 | Summ                                   | ary                                                                                  | 62                                                                                                                                                                                                                               |

| Con | . al ai a                              | was di Fratana Wash                                                                  | 64                                                                                                                                                                                                                               |

|     | 3.3<br>Res<br>4.1<br>4.2<br>4.3<br>4.4 | 3.2 Problem 3.2.1 3.2.2 3.2.3 3.3 Summ 4.1 Implem 4.2 Results and 4.1 Optim 4.4 Summ | 3.2.1 General Problem Statement 3.2.2 Qualitative Approach 3.2.3 Formal Problem Statement 3.3 Summary  Results and Discussion 4.1 Implementation 4.2 Results and Discussion 4.3 Optimizing a Subthreshold Transistor 4.4 Summary |

## List of Tables

| 2.1 | CE scaling of MOSFET device and circuit parameters                              | 17 |

|-----|---------------------------------------------------------------------------------|----|

| 4.1 | Desired device constraints and their technology node for optimized transistors. | 53 |

| 4.2 | Design parameters and specifications of optimum devices                         | 54 |

| 4.3 | Various worst case leakage components of optimum devices                        | 56 |

# List of Figures

| 2.1 | Architecture of an n-channel MOSFET                                                   | 6  |

|-----|---------------------------------------------------------------------------------------|----|

| 2.2 | Projected leakage power as a fraction of the total power consumption ac-              |    |

|     | cording to the ITRS                                                                   | 8  |

| 2.3 | Short-channel transistor mechanisms: $(I_1)$ , reverse biased p-n junction; $(I_2)$ , |    |

|     | subthreshold or weak inversion; $(I_3)$ , drain-induced barrier lowering; $(I_4)$ ,   |    |

|     | punch-through; $(I_5)$ , gate-induced drain leakage; $(I_6)$ , gate oxide tunneling;  |    |

|     | and $(I_7)$ , hot-carrier injection                                                   | 9  |

| 2.4 | Band-to-band tunneling in an nMOS: valence band electron tunneling from               |    |

|     | the valence band of the p-side to the conduction band of the n-side; the total        |    |

|     | voltage drop across the junction, the reverse bias voltage and the built-in           |    |

|     | voltage is greater than the energy-band gap, $(V_{app} + \psi_{bi} > E_g)$            | 10 |

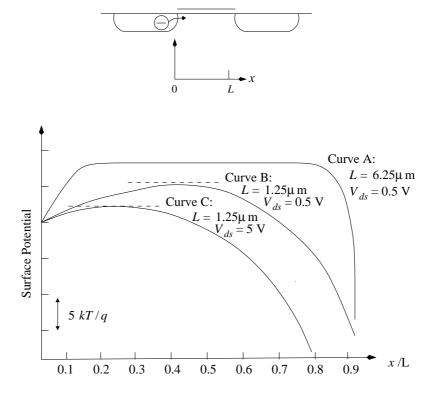

| 2.5 | Normalized channel length from the source to the drain versus the surface             |    |

|     | potential: Curve A: a long-channel MOSFET, Curve B: a short-channel                   |    |

|     | MOSFET at a low drain bias, and $\mathit{Curve}\ C$ : a short-channel MOSFET at a     |    |

|     | high drain bias; the gate voltage is constant for the three cases                     | 11 |

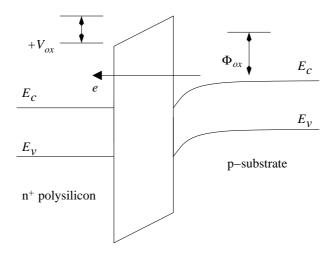

| 2.6 | Tunneling of electrons: direct tunneling occurs when the potential drop               |    |

|     | across the gate oxide is lower than the barrier height of the tunneling electron      |    |

|     | $(V_{ox} < \phi_{ox})$                                                                | 13 |

| 2.7  | Injection of hot electrons from the substrate to the oxide                           | 13 |

|------|--------------------------------------------------------------------------------------|----|

| 2.8  | Leakage components of $0.35 \mu m$ technology for a $20 \mu m$ wide transistor; cur- |    |

|      | rents for various leakage mechanisms are accumulated for a given drain bias.         | 14 |

| 2.9  | Variation of leakage components: (a) oxide thickness and channel length,             |    |

|      | and (b) doping profile in a 50nm device; "Doping-1" has a stronger halo              |    |

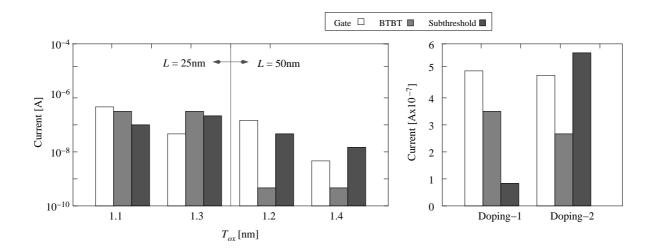

|      | profile than "Doping-2"                                                              | 15 |

| 2.10 | MOS constant electric field scaling by a factor of $S.$                              | 16 |

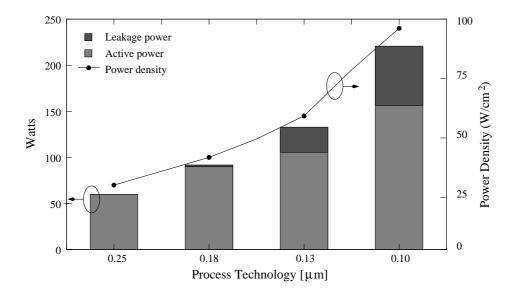

| 2.11 | Power breakdown trend over technology generations                                    | 18 |

| 2.12 | Drift and diffusion components of the total current, represented by the solid        |    |

|      | curve                                                                                | 20 |

| 2.13 | Capacitance in weak inversion                                                        | 21 |

| 2.14 | Percentage of the total variations accounted for intra-die variation for dif-        |    |

|      | ferent technology generations                                                        | 28 |

| 3.1  | Architecture of the subthreshold device                                              | 34 |

| 3.2  | Total leakage $(TL)$ estimation scheme                                               | 37 |

| 3.3  | Charge sharing model                                                                 | 39 |

| 3.4  | Top view of the transistor                                                           | 41 |

| 3.5  | Simplified problem in 2-D                                                            | 45 |

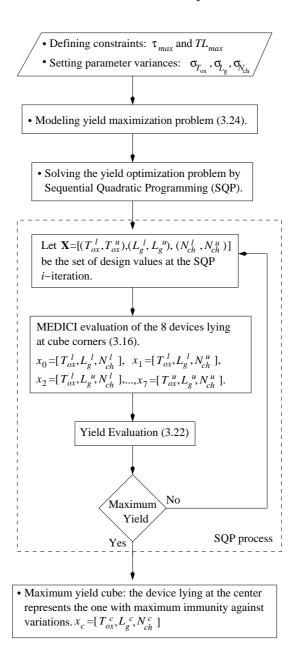

| 3.6  | Flowchart of the yield maximization technique. For each iteration, a set             |    |

|      | of design values are determined by the optimization engine, and directly             |    |

|      | evaluated by MEDICI                                                                  | 49 |

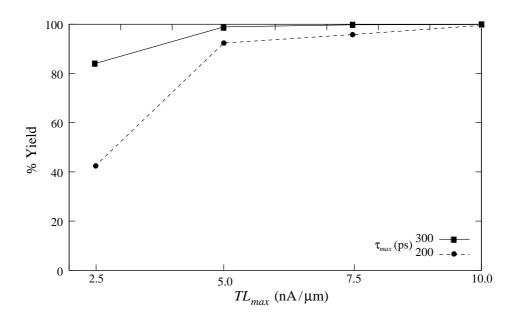

| 4.1  | %Yield obtained from experimental $90nm$ devices                                     | 56 |

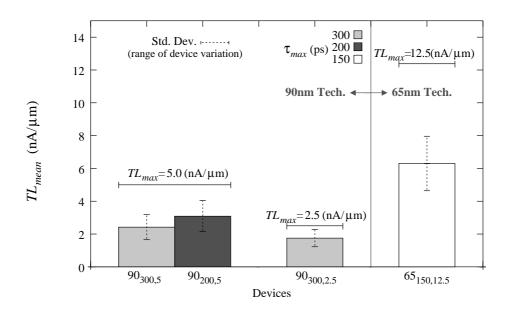

| 4.2  | Mean and standard deviation of total leakage. The bars correspond to mean            |    |

|      | values whereas the dotted vertical lines are the standard deviations (range          |    |

|      | of device variation)                                                                 | 57 |

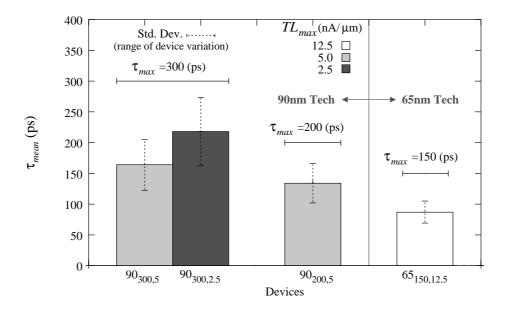

| 4.3 | Mean and standard deviation of intrinsic delay. The bars correspond to                   |    |

|-----|------------------------------------------------------------------------------------------|----|

|     | mean values whereas the dotted vertical lines are the standard deviations                |    |

|     | (range of device variation)                                                              | 58 |

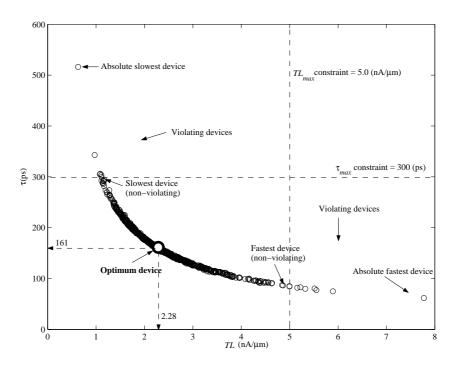

| 4.4 | Monte Carlo simulation of the $90_{300,5.0}$ device, $98.9\%$ of devices satisfy both    |    |

|     | constraints (relaxed $TL$ bound)                                                         | 59 |

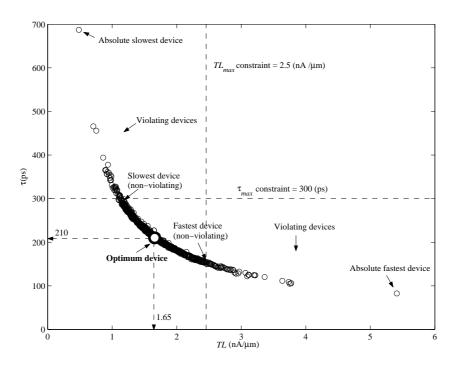

| 4.5 | Monte Carlo simulation of the $90_{300,2.5}$ device, $84.0\%$ of devices satisfy both    |    |

|     | constraints (tight $TL$ bound)                                                           | 60 |

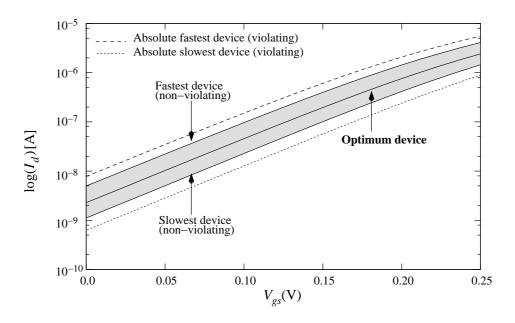

| 4.6 | I-V characteristics of the $90_{300,5.0}$ device (more relaxed constraints, yield =      |    |

|     | 98.9%)                                                                                   | 61 |

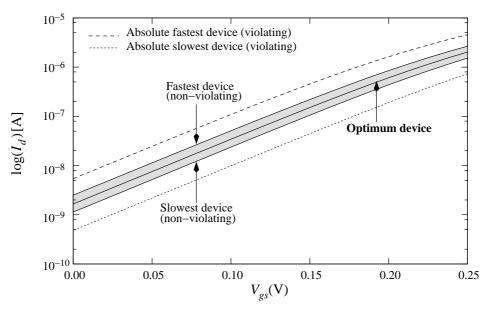

| 47  | I-V characteristics of the $90_{200.05}$ device (tighter constraints, yield = $84.0\%$ ) | 61 |

## Chapter 1

### Introduction

With the growing demand for system portability, power consumption has become an issue in VLSI applications such as biomedical devices, self-powered Radio Frequency IDentification (RFID), and wireless sensor networks. The progress of mobile electronics will depend on the development of inexpensive devices with complex functionality and long battery life [25]. In turn, the continuous increase in system necessities demands higher levels of integration and performance which have been solved by highly scaled CMOS technologies. However, MOS transistor scaling has resulted in unacceptable off-state leakage currents beyond 130nm process technologies [66]. Moreover, since the fabrication process tolerances have not scaled proportionally with the device dimensions, the relative impact of process variations has become more significant with each technology generation (especially beyond the 90nm technology) [67]. These two issues, power and variability, are the most challenging obstacles for modern IC design, according to the International Technology Roadmap for Semiconductors (ITRS) [7]. It is evident that new strategies for designing low-power systems under effects of parameter variations are crucial needed.

In recent years, dramatically scaled CMOS technologies have boosted the mass produc-

tion of portable battery-powered electronic devices, and an immense interest in energy-efficient designs. Nowadays, low-power IC design is an especially vibrant area of research and development, resulting in advances in low-power fabrication processes and energy-sensitive design techniques [24]. It has been proven that, in a CMOS circuit, the minimum energy operation occurs in the subthreshold region (or weak inversion) [12, 73]; thus, sub-threshold logic [58, 59, 60] has emerged as a compelling approach to design energy-efficient systems.

Subthreshold logic operates solely in the weak inversion region of transistors, that is, the power supply voltage is below the threshold voltage ( $V_{dd} < V_{th}$ ) such that load capacitances are charged/discharged by subthreshold leakage current. On the one hand, driving CMOS circuits with the subthreshold leakage current can provide orders of magnitude power reduction over standard strong inversion (superthreshold) CMOS circuits [46]. On the other hand, the minute operating leakage current is orders of magnitude lower than the saturation drain currents in the strong inversion regime, and there are significant limits on the maximum performance of subthreshold circuits [73]. By pursuing subthreshold design, it is expected that an energy efficiency in the range of 1pJ/instruction can be achieved [44], enabling applications which require ultra-low-power dissipation and low-to-moderate circuit performance. Some successful applications include an ultra-low-power adaptive filter for hearing aid devices [31], a 180-mV subthreshold FFT processor [71], a 256k subthreshold SRAM [13], and a 2.60pJ/instruction subthreshold sensor processor [78].

Researchers have demonstrated that it is possible to implement subthreshold logic circuits by using standard CMOS transistors, however; such devices are not optimum in terms of power and performance in the subthreshold regime. Indeed, a device should be specifically optimized for subthreshold operation to improve the device's Power-Delay Product (PDP) as shown by Paul et al. [46]. They have introduced an optimized transistor for sub-

Introduction 3

threshold operation that improves the PDP in comparison to that of a standard transistor in the subthreshold region. However, authors have not accounted for process variations. It is well known that subthreshold current is exponentially dependent on the transistor's threshold voltage, where  $V_{th}$  is strongly related to various device parameters; they in turn vary considerably in the Deep Sub-Micron (DSM) regime [64]. Therefore, subthreshold designs are expected to be prone to process variations [77]. Consequently, this dissertation focuses on a device optimization technique which includes process variations on subthreshold transistor design.

#### 1.1 Contribution of this Work

The objective of this investigation is to provide an automatic optimization technique to design a transistor for subthreshold operation that addresses process variations and device yield, power and performance constraint satisfaction, in a simple framework. To the best of our knowledge, this is the first variability-aware design approach at the device level for subthreshold devices.

By using the technique, a transistor can be optimized for subthreshold operation in terms of the desired total leakage current and intrinsic delay bounds, taking into account device design-parameter variations. In addition, designers can still apply circuit and architecture level techniques to further mitigate the variation effects.

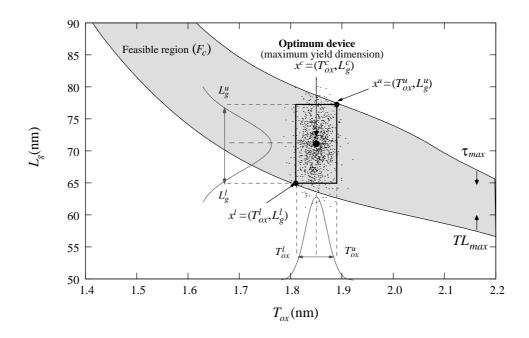

The design technique exploits the 3-D space generated by device's design parameters oxide thickness, gate length, and channel doping concentration, to maximize the device yield in the presence of variations in the three parameters; that is, a feasible region is constructed and bound by the desired total leakage current and intrinsic device delay. As a result, any point in the feasible region represents a satisfactory device under the stated power and delay restrictions. Finally, a cube is formed and inscribed in the region such

that the center of the cube represents the properties of a device that is the most robust to process variations.

#### 1.2 Organization of the Dissertation

The remainder of this thesis is organized as follows.

Chapter 2 provides an overview of the subthreshold regime. After the basic characteristics of MOS transistors in the subthreshold region are summarized, subthreshold circuits, and the state-of-the-art of subthreshold designs are discussed with the emphasis on works, addressing process variations. Finally, the considerations for constructing a subthreshold optimized transistor are outlined.

Chapter 3 defines the problem and develops the yield maximization technique. An analytical discussion of device parameters and variations is presented. Subsequently, the problem is defined in terms of the selected parameters and constraints, and the yield maximization technique is formalized.

Chapter 4 describes the implementation, results, and discussion. Sample devices for two technologies are optimized. The experimental results are assessed by examining several characteristics of the new subthreshold optimized devices. Finally, guideline is introduced to optimize transistors.

Chapter 5 not only concludes this thesis but also outlines future work for subthreshold designs.

## Chapter 2

# Subthreshold Design: Background and Related Work

This chapter introduces the problem of power consumption in modern DSM devices. Subsequently, a description of a transistor's leakage mechanisms is given, and the obstacle to technology scaling, by exponential leakage power increases, is exposed. Later, the paradigms of subthreshold design at several levels of hierarchy are presented. First, the characteristics and behavior of MOS transistors in the subthreshold region are described to comprehend subthreshold logic. In addition, the properties and evolution of subthreshold designs, including the state-of-the-art are presented. Then, the challenges of process variations and its impact on circuit behavior are addressed with an emphasis on research in the subthreshold regime. Lastly, considerations for construct a subthreshold optimized transistor are discussed.

In this thesis, the object of discussion, analysis, and optimization is the Metal-Oxide-Semiconductor Field-Effect (MOSFET, or MOS for simplicity) transistor. Such a transistor is the dominant device in integrated circuits such as processors and memories. The transitor

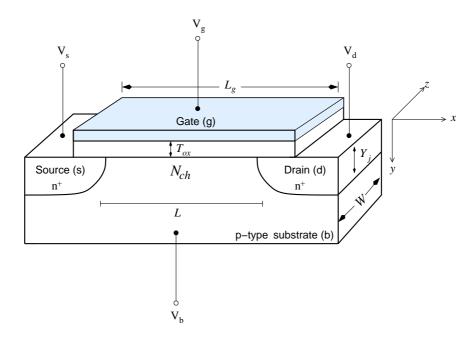

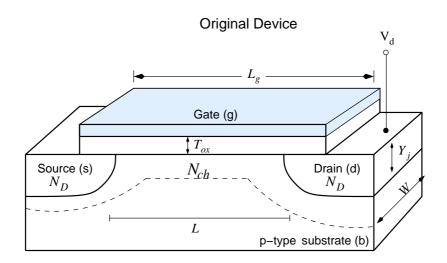

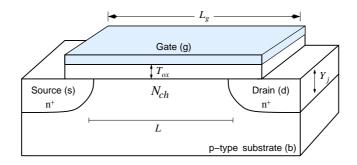

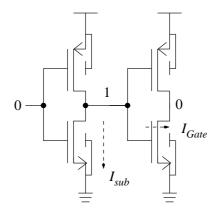

sistor's current is transported by electrons in n-channel devices (nMOS) or by holes in p-channel devices (pMOS). A basic nMOS channel structure is depicted in Figure 2.1, the substrate (bulk or body) is composed of p-type silicon in which two heavily doped n-type silicon regions, the drain and the source, are formed. Typically, the gate consists of heavily doped or salicide polysilicon, and is separated from the substrate by a thin silicon dioxide film, the gate oxide. The main device parameters are gate oxide insulator thickness  $(T_{ox})$ , physical gate length  $(L_g)$ , channel doping concentration  $(N_{ch})$ , source/drain junction depth  $(Y_j)$ , and transistor width (W).

Figure 2.1: Architecture of an n-channel MOSFET

#### 2.1 Power Consumption

The power consumption of a system sets up how much energy is consumed per operation, and how much heat is dissipated. The upper power limits determine the maximum number of transistors that are integrated on a single chip, heat removal system, chip package, and especially, the frequency at which the transistor switches [50]. In digital CMOS circuits, the power consumption is composed of two components: dynamic power due to the active switching activity, and static power due to the leakage current. These two sources of power consumption are represented by

$$P_{total} = P_{dynamic} + P_{static} = \alpha C_L V_{dd}^2 f_{clk} + V_{dd} I_{leak}. \tag{2.1}$$

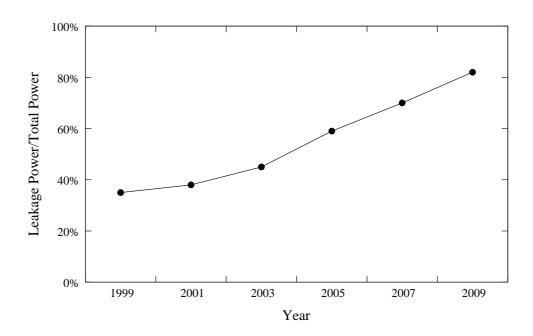

To reduce the dynamic power component, the first target has been aggressive supply voltage  $(V_{dd})$  scaling, since it leads to quadratic power reductions; the switching activity  $(\alpha)$ , operating frequency  $(f_{clk})$ , and load capacitance  $(C_L)$  reductions provide linear decreases in the dynamic power. For the static power component, besides the supply voltage scaling which provides linear power reductions, the objective is to keep the leakage current  $(I_{leak})$  as low as possible. Leakage power exponentially increases for each technology node, and eventually becomes the dominant component of the total power  $(P_{total})$  as the technology scales beyond 65nm [9, 29], as seen Figure 2.2 [7]. This is why low-power strategies, especially those for static power reduction, are necessary at almost any design level in recent digital circuits.

The power dissipation of high performance applications such as microprocessors, digital signal processors, and random access memories has increased along with the progress in CMOS technologies, where the design emphasis has been on maximizing the operational frequency ( $f_{clk}$  in (2.1)). The increased power consumption raises a chip temperature which leads to electromigration reliability problems, and degradation in the device perfor-

Figure 2.2: Projected leakage power as a fraction of the total power consumption according to the ITRS.

mance. Thus, lowering the power dissipation is crucial for high performance VLSI designs [34]. Also, applications are emerging for which the energy consumption is the key metric, and the speed of operation becomes less relevant. Generally, energy-constrained VLSI applications such as micro-sensor networks and nodes, radio frequency identification, and biomedical devices have low activity rates and low speed requirements ( $\alpha$ , and  $f_{clk}$  in (2.1), respectively); but the concern is to lengthen battery life. Ideally, the power consumption of these systems should decrease to the extent that they can harvest energy from environmental resources such as solar power, thermal gradients, radio-frequency, and mechanical vibration [17], and theoretically have unlimited lifetimes. Such ultra-low-power applications have established a significant niche for subthreshold circuits [70].

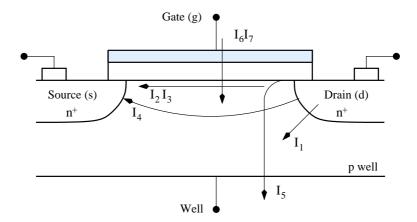

Figure 2.3: Short-channel transistor mechanisms:  $(I_1)$ , reverse biased p-n junction;  $(I_2)$ , subthreshold or weak inversion;  $(I_3)$ , drain-induced barrier lowering;  $(I_4)$ , punch-through;  $(I_5)$ , gate-induced drain leakage;  $(I_6)$ , gate oxide tunneling; and  $(I_7)$ , hot-carrier injection.

#### 2.1.1 Static Power: Leakage Mechanisms

Static power is dissipated during the idle time, that is, when no transition or switching activity occurs. As the transistor threshold voltage, channel length, and gate oxide thickness are reduced in DSM regimes, the static power dissipation becomes a challenging obstacle for the development of modern ICs. Consequently, the identification of the different leakage components is pivotal for the analysis and design of low-power applications. Figure 2.3 [57] denotes the seven transistor intrinsic leakage mechanisms in short channel devices.

•  $I_1$  is the **reverse bias p-n junction leakage**. Drain-to-substrate and source-to-substrate junctions are normally reverse biased, occasioning a p-n junction leakage current. It has two components: i) the minority carrier diffusion/drift near the edge of the depletion region, and ii) the electron-hole pair generation in the depletion region of the reverse biased junction. If both the n- and p-regions are heavily doped, which is the case of an advanced MOS, to mitigate short-channel effects, Band-To-

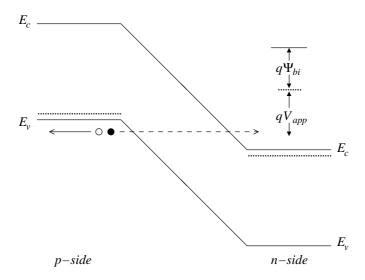

Band Tunneling (BTBT) can also be present. The effect dominates the p-n junction leakage component.  $I_{BTBT}$  occurs when a high electric field (>  $10^6V/cm$ ), across the reverse biased junction, leads to electrons from the valence band of the p-side to migrate to the conduction band of the n-side, as denoted in Figure 2.4 [65].

•  $I_2$  is the weak inversion or subthreshold conduction current between the source and drain. It occurs when the gate voltage is below the threshold voltage  $(V_g < V_{th})$ . Recently, this current dominates device off-state leakage mechanisms due to the low  $V_{th}$  values of transistors [5]. This weak inversion current is the *drive* current in the subthreshold regime. Consequently, this leakage component is looked at the next section.

Figure 2.4: Band-to-band tunneling in an nMOS: valence band electron tunneling from the valence band of the p-side to the conduction band of the n-side; the total voltage drop across the junction, the reverse bias voltage and the built-in voltage is greater than the energy-band gap,  $(V_{app} + \psi_{bi} > E_g)$ .

•  $I_3$  is the **Drain-Induced Barrier Lowering** (DIBL). It occurs when a high drain voltage is applied to a short-channel device, and thus, the potential (voltage) barrier (to the electrons for an nMOS) at the surface between the source and drain is lowered. For example, consider the potential energy barrier at the surface between the drain and source, depicted in Figure 2.5 [65]. At the off-condition, this potential prevents the flow of electrons between the terminals. However, as the drain voltage is increased, the potential barrier is reduced in short-channel devices. In this way,

Figure 2.5: Normalized channel length from the source to the drain versus the surface potential: Curve A: a long-channel MOSFET, Curve B: a short-channel MOSFET at a low drain bias, and Curve C: a short-channel MOSFET at a high drain bias; the gate voltage is constant for the three cases.

the higher the drain voltage applied to a short channel device, the lower the barrier height is, and thus, the source injects carriers into the channel surface without the control-gate voltage playing a role [65].

- $I_4$  is the **channel punch-through**. At even higher drain voltages and channel length reductions, the drain and source depletion regions approach each other and eventually merge in the deep substrate. As a result, the gate totally loses control over the channel, and the flow of the drain current becomes independent of the control voltage [65].

- $I_5$  represents the **Gate-Induced Drain Leakage** (GIDL). It is the result of the influence of high electric fields on the gate-drain overlap region. Consequently, the depletion width of the drain to substrate p-n junction is thinned out [53]. Carriers are generated in the substrate and drain from the direct band-to-band tunneling, trap-assisted tunneling, or a combination of thermal emission and tunneling [5]. Oxide thickness  $(T_{ox})$  reductions and higher supply voltages lead to a higher potential between the gate and the drain, which in turn, enhances the electric field dependent GIDL.

- $I_6$  refers to **oxide leakage tunneling**. The continuous reduction of the oxide thickness leads to an increase in the field across  $T_{ox}$ . The high electric field results in the tunneling of electrons from the inverted substrate-to-gate and also from the gate-to-substrate through  $T_{ox}$ . This current flow is known as oxide leakage tunneling. The direct tunneling of electrons is signified in Figure 2.6 [54, 56].

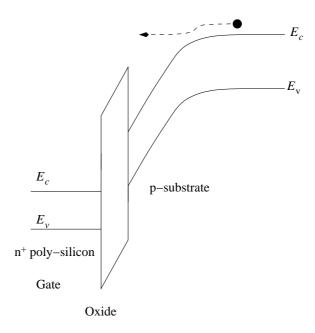

- $I_7$  is the gate current due to **hot carrier injection**. If a region with a high electric field is located near the  $Si\text{-}SiO_2$  interface (as it occurs in the pinch-off condition),

Figure 2.6: Tunneling of electrons: direct tunneling occurs when the potential drop across the gate oxide is lower than the barrier height of the tunneling electron  $(V_{ox} < \phi_{ox})$ .

Figure 2.7: Injection of hot electrons from the substrate to the oxide.

some of the electrons or holes can gain sufficient energy from the field to cross the interface potential barrier and enter the oxide layer. This phenomenon, called a hot-carrier injection, is represented in Figure 2.7 [65].

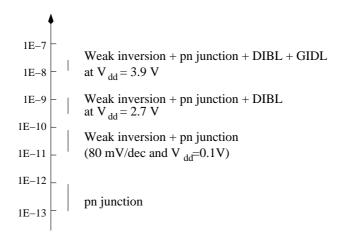

Currents  $I_1$  to  $I_5$  are off-state leakage mechanisms;  $I_6$  is present when the transistor is in the on-state. Finally,  $I_7$  can occur in the off-state, but is more typical during the transitions of the transistor bias states [5]. Figure 2.8 [30] summarizes the relative contributions of the leakage components for  $0.35\mu m$  CMOS technology.

Leakage ( $I_{off}$ ) Current in Amps

Figure 2.8: Leakage components of  $0.35\mu m$  technology for a  $20\mu m$  wide transistor; currents for various leakage mechanisms are accumulated for a given drain bias.

#### 2.1.2 Technology Scaling and Leakage Power

In the last three decades, the CMOS technology evolution has resulted in substantial device scaling for achieving density, speed, and power improvements, as predicted by Moore's Law [40]. The direct result of device scaling is the reduced intrinsic capacitance, enabling a faster

switch. Simultaneously, the power supply voltage scaling has reduced the switching energy. To maintain the speed enhancement for each technology node, threshold voltage  $V_{th}$  must also scale down in order to retain enough gate overdrive  $V_{dd}/V_{th}$ . However, reducing the  $V_{th}$  results in an exponential increase in the subthreshold leakage current, as shown by (2.5) in the next section. The oxide thickness scaling, required to maintain reasonable short channel effects, results in a considerable amount of direct oxide tunneling leakage current. Finally, the higher substrate doping density and the application of the halo profiles to reduce short channel effects in scaled devices, cause substantially large junction band-to-band tunneling leakage. In this way, among the seven leakage mechanisms in scaled devices, the three more contributive components of leakage power are: subthreshold, oxide tunneling, and reverse bias p-n junction BTBT [52]. The magnitudes of each component depend strongly on the device constitution, that is, oxide thickness, channel length, and doping profile in Figure 2.9 [41].

Figure 2.9: Variation of leakage components: (a) oxide thickness and channel length, and (b) doping profile in a 50nm device; "Doping-1" has a stronger halo profile than "Doping-2".

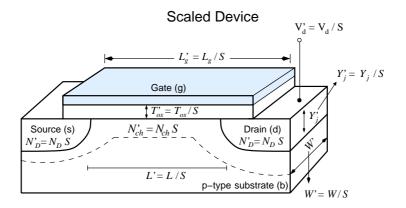

There are two MOS scaling theories: Constant Electric (CE) field scaling [19] and Constant Voltage (CV) scaling [18]. In CE scaling, it has been proposed that for keep the short channel effect under control, the horizontal and vertical dimensions should be scaled down. In addition, the applied voltage should be decreased and the substrate doping concentration should be increased proportionally, as summarized in Figure 2.10.

Figure 2.10: MOS constant electric field scaling by a factor of S.

The CV theory retains the same scaling down theory as the CE, but the power supply voltage remains unchanged. Therefore, to maintain the charge-field, the doping densities are increased by a factor of  $S^2$  [18]. However, the CV scaling inherently leads to a continuous increase of the transistor's internal electric field, which can cause reliability problems such as electron migration, hot carrier degradation, and oxide breakdown in recent CMOS process generations. As a result, since the  $0.5\mu m$  MOS technology, the industry's scaling methodology has been the CE [23].

Table 2.1: CE scaling of MOSFET device and circuit parameters.

| D                                   | 1/S Constant  | 30% Scaling   |

|-------------------------------------|---------------|---------------|

| Parameter                           | Field Scaling | Field Scaling |

| Physical Device Dimension           | 1/S           | 0.7           |

| Supply and threshold voltage        | 1/S           | 0.7           |

| $C_{ox} = (\epsilon Area)/T_{ox}$   | 1/S           | 0.7           |

| Gate Capacitance = $WL/T_{ox}$      | 1/S           | 0.7           |

| $Current = (W/L)(1/T_{ox}V_{dd}^2)$ | 1/S           | 0.7           |

| Propagation Delay = $CV_{dd}/I$     | 1/S           | 0.7           |

| Frequency                           | S             | 1.43          |

| Dynamic Power = $CV_{dd}^2 f_{clk}$ | $1/S^2$       | 0.5           |

| Leakage Power                       | Exponential   | Exponential   |

| Energy                              | $1/S^{3}$     | 0.34          |

The principle of the CE theory is that the physical dimensions (gate length, transistor width, and oxide thickness), and voltages (power supply and threshold) are scaled by a factor of 1/S (S > 1). Consequently, the current, gate capacitance, and propagation delay

also scale by a factor of 1/S. Hence, with a 30% reduction of all the device parameters (1/S = 0.7), improvements, close to 50% in the operation frequency, are achieved for each generation. Table 2.1 lists the CE scaling rules for various device parameters and circuit performance factors. Evidenlty, the resulting switching energy scales by  $1/S^3$ , whereas the dynamic power scales by  $1/S^2$ . However, for a constant die size, the power dissipation due to the dynamic switching currents remains relatively constant with scaling, because the number of switching elements for the same die size increases by a factor of  $S^2$ . The negative effect of the CE is that the subthreshold current increases exponentially, as the threshold voltage scales. For example, consider a device with a  $V_{th}$  of 400mV that is to be scaled by 0.7. For a constant die size, scaling provides around a 43% (S = 1.43) frequency improvement, and doubles the number of devices. The dynamic power dissipation scales by unity, but the leakage current increases by a factor of  $1.43 \times 10^{(V_{th}/S(1-0.7))} = 45$  [28]. Figure 2.11 [55] demonstrates the power breakdown composition for Intel's process technologies. Leakage power in the  $0.25\mu m$  technology corresponds to 0.1% of the active power, but

Figure 2.11: Power breakdown trend over technology generations.

dramatically increases to approximately 25% of the active power in  $0.1\mu m$  technology.

Since the primary reasons for technology scaling are performance and device integration, the CE scaling theory serves as an essential blueprint. However, as the device's dimensions and voltages are shrunk, the leakage power becomes a significant barrier in present and future technologies. Therefore, the scaling of VLSI technology leads to multiple challenges, including power dissipation, leakage management, and short channel effects. This problem worsens for portable energy-constrained VLSI applications, where battery power is drained needlessly during long idle periods [3].

In Subsection 2.1.2, the three contributive leakage components in recent sub-micron technologies are the subthreshold, oxide tunneling, and reverse bias p-n junction BTBT, whereas subthreshold leakage is the *drive current* in the subthreshold regime. Thus, consideration of this component is developed in the next section.

#### 2.2 MOS Transistor in the Subthreshold Region

In this section, the behavior of a MOS transistor in the subthreshold or weak inversion region is examined. As the gate voltage drops below  $V_{th}$ , the strong inversion model erroneously predicts a drain current; thus, a model for the subthreshold region is necessary. The vital parameters for the subthreshold regime include subthreshold swing coefficient and subthreshold slope.

A current flow in silicon is carried out by two mechanisms: the drift of carriers caused by the presence of an electric field, and diffusion of carriers which is caused by a gradient concentration of electrons or holes. In weak inversion, the channel inversion layer charge is much lower than that of the substrate or depletion charge  $(Q_I \ll Q_B)$ . Since the substrate is weakly doped,  $Q_B$  is small, and the electric field along the channel direction is not enough to pull the electrons from the source to the drain; as a result, the drift current is negligible [65]. Thus, unlike the strong inversion region where the drift current dominates, in the subthreshold region, the diffusion current is the major component, as portrayed in Figure 2.12.

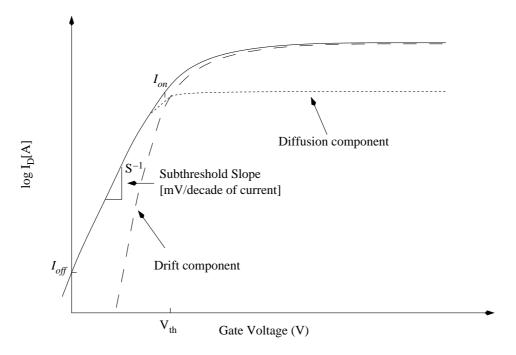

Figure 2.12: Drift and diffusion components of the total current, represented by the solid curve.

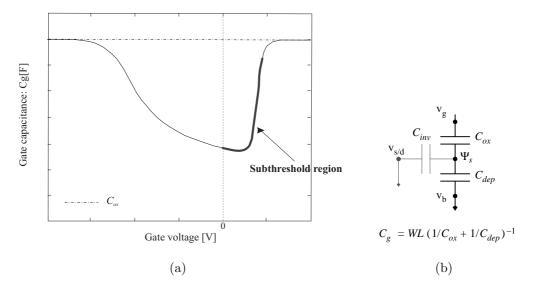

To obtain an expression for the subthreshold diffusion current, the surface channel potential in weak inversion is explored. The inversion charge in weak inversion is negligible, such that the gate-to-bulk capacitance is principally influenced by the oxide capacitance  $(C_{ox})$  and the depletion capacitance  $(C_{dep})$ , as signified in Figure 2.13.

Assuming that  $V_b = 0$ , the relationship between the surface potential  $(\psi_s)$  and the applied gate voltage  $(V_g)$  is the capacitive divider

$$\psi_s = \kappa V_g = \frac{C_{ox}}{C_{ox} + C_{dep}} V_g, \tag{2.2}$$

Figure 2.13: Capacitance in weak inversion.

where  $\kappa$  is the coupling coefficient of the gate voltage to the surface potential. At the surface level, the charge concentration in the source (x = 0) and the drain (x = L) are given by

$$|Q'_{I0}| \propto exp\left(\frac{V_s - \kappa V_g}{V_T}\right),$$

$$|Q'_{IL}| \propto exp\left(\frac{V_d - \kappa V_g}{V_T}\right),$$

(2.3)

$V_T = kT/q$  is the thermal voltage. The concentration gradient of electrons in the channel decreases linearly from x = 0 to x = L (i.e., the concentration gradient is constant). Then, the diffusion current is written as

$$I_d = -W D_n \frac{Q'_{I0} - Q'_{IL}}{L} = -\frac{W}{L} \mu_0 V_T (Q'_{I0} - Q'_{IL}), \tag{2.4}$$

$\frac{W}{L}$  is the width over length ratio of the device, and  $\mu_0$  is the zero bias electron mobility in

the channel. This leads to a compact expression for the subthreshold current,  $I_{sub} = I_{ds}$  as follows:

$$I_{sub} = I_o e^{(V_{gs} - V_{th})/nV_T} \left( 1 - e^{-V_{ds}/V_T} \right), \tag{2.5}$$

where  $I_o = \mu_0 C_{ox} \frac{W}{L} V_T^2$ , and n is the subthreshold swing coefficient, defined as  $n = 1/\kappa = 1 + C_{dep}/C_{ox}$ . In subthreshold logic, the drive current  $(I_{on})$  is precisely the subthreshold current modeled by (2.5) as  $I_{on} = I_{sub}(V_{gs} = V_{ds} = V_{dd} < V_{th})$ . Also, the transistor "off" state current  $(I_{off})$  is the drain current, when the gate voltage is zero; that is  $I_{off} = I_{sub}(V_{gs} = 0, V_{ds} = V_{dd} < V_{th})$ . Throughout this thesis,  $I_{on}$  and  $I_{off}$  refer to the latter definitions, unless otherwise specified. In addition, note that for  $V_{ds} > 4V_T \approx 100 mV$  at room temperature, the term  $(e^{-V_{ds}/V_T} << 1)$  such that  $I_{sub}$  saturates and is independent of the  $V_{ds}$  as follows:

$$I_{sub} = I_o e^{(V_{gs} - V_{th})/nV_T}$$

for  $V_{ds} > 4V_T$ . (2.6)

It is observed that the drain current changes exponentially with the  $V_{gs}$ , whereas in strong inversion,  $I_D$  responds quadratically with  $V_{gs}$ . These relationships are illustrated in the logarithmic plot of  $I_D$  vs.  $V_{gs}$  in Figure 2.12. From this figure, the dependence of the gate voltage swing needed to change the drain current by one order of magnitude is defined as [65]

$$S = \frac{d(\log_{10} I_d)^{-1}}{dV_{qs}} = 2.3 \frac{nkT}{q} = 2.3 \frac{kT}{q} \left( 1 + \frac{C_{dep}}{C_{ox}} \right). \tag{2.7}$$

The subthreshold slope, S, is an important device parameter in the subthreshold region. The smaller the S value is, the higher the drive  $I_{on}$  current is, and thus, the faster the device. This section introduces the characteristics of a MOS transistor in the subthreshold region that differ from those of the strong inversion in the following ways.

- Current Flow Mechanism: In the subthreshold region, the drain current is governed by diffusion, whereas in strong inversion it is mainly by drift phenomenon.

- Intrinsic MOS Capacitances: Like that of the subthreshold region, the inversion charge is negligible, the gate-to-bulk capacitance is given by the serial combination of  $C_{ox}$  and  $C_{dep}$ .

- Drain Current. It is exponentially related to the gate and threshold voltages, as well as temperature.

The characteristics and state-of-the-art of the corresponding subthreshold logic are discussed in the next section.

#### 2.3 Subthreshold Circuits

In this section, the paradigms of subthreshold logic are briefly outlined. Subsequently, the evolution and the state-of-the-art of subthreshold designs are described.

Subthreshold logic operates completely in the subthreshold region; that is, the drain on and off currents are composed entirely of subthreshold leakage. Therefore, the logic assumes a power supply voltage that is less than the threshold voltage,  $V_{dd} < V_{th}$ . Since the leakage current is orders of magnitude lower than the drain strong inversion current and since the power supply is reduced, subthreshold logic dissipates ultra-low-power. Due to the small drive leakage current, the subthreshold logic only fits in designs, where the performance is considerably poor, and not the main concern.

As mentioned in the former of this section, subthreshold logic shares important properties with traditional strong inversion CMOS logic.

- High Noise Margins: The output swing goes from  $V_{dd}$  to ground (GND).

- Low Output Impedance: In the steady state, a low impedance path to either  $V_{dd}$  or GND exists.

In addition, subthreshold logic has a number of advantages over its strong inversion counterpart.

- Lower Power Consumption: At the same frequency, subthreshold circuits consume orders of magnitude less power than strong inversion circuits [59].

- Higher Gain. The exponential relationship between  $I_{sub}$  and  $V_{gs}$  leads to a high transconductance,  $g_m = \frac{\partial I_{sub}}{\partial V_{gs}} = \frac{I_{sub}}{nV_T}$  [68].

- Better Noise Margins. In (2.6),  $I_{sub}$  readily becomes independent of  $V_{ds}$ . This near-ideal current source characteristic improves the noise margin of the logic gates [60].

A notable difference between strong inversion CMOS logic and subthreshold circuits is their robustness. Strong inversion logic will always work, given that the appropriate complementary Pull-Up Network (PUN) and Pull-Down Network (PDN) are implemented, even if the transistors are erroneously sized. In subthreshold circuits, transistor sizing impacts the functionality of CMOS circuits due to low supply voltages [16]. For example, consider a simple inverter, operating in the subthreshold region. Subthreshold  $I_{off}$  leakage always flow through a large pMOS device (which forms the PUN) to a certain extent where, a smaller nMOS (which forms the PDN) cannot pull down the voltage at the output to a full logic 0 level, and viceversa. This problem is augmented by the effect of the process variations.

Besides the Subthreshold static logic (Sub-CMOS), other logic families such as Sub-threshold pseudo-nMOS (Subpseudo nMOS), Variable Threshold voltage Subthreshold

CMOS (VT-Sub-CMOS), Subthreshold Dynamic Threshold voltage MOS (Sub-DTMOS), and subthreshold dynamic logic (Sub-Domino logic) have been proposed [60, 61, 62].

#### 2.3.1 Origin and Evolution of Subthreshold Circuits

In the 1970s, subthreshold circuits were first considered for analog design in the development of micropower circuits [68]. Between the 1980s and the early 1990s, subthreshold circuits were proposed to implement analog VLSI designs that emulated functions of the brain [38, 69]. It was not until the late 1990s that subthreshold circuits were considered in the digital domain [59]. Subsequently, a growing number of successful implementations of subthreshold systems have occurred.

In 2001, Paul et al. [47] designed an 8x8 VT-Sub-CMOS array multiplier in  $0.35\mu m$  technology. They demonstrated that the PDP of this multiplier is around 25 times lower than its strong inversion operation. In 2003, Kim et al. [31] reported an ultra-low-power Delayed Least Mean Square (DLMS) adaptive filter for hearing aid devices, operating in Sub-CMOS and Subpseudo nMOS in  $0.35\mu m$  technology. This parallel DLMS adaptive filter achieves a 91% improvement in power compared with a nonparallel CMOS implementation. One year later, Wang and Chandrakasan [71, 72] fabricated a 180-mV subthreshold Fast Fourier Transform (FFT) processor in  $0.18\mu m$  technology. At the optimum supply voltage, the FFT processor dissipates 155nJ for a 16 bits and 1024 point FFT. Later on, Calhoun and Chandrakasan [13, 14] proposed a 256k Sub-threshold SRAM in 65nm technology. They show that a traditional six transistor (6 T) SRAM cannot function in the subthreshold region, but solved the problem by introducing a 10 T bitcell. Finally, Zhai et al. [78] have fabricated a 2.60pJ/instruction subthreshold sensor processor in  $0.13\mu m$  technology, and showed that the minimum energy consumption of the core is improved 10 times in that of previous sensor processors of the same MIPS.

Obviously, subthreshold circuits have been used in analog designs for a long time. Moreover, the authors have proven that it is possible to implement subthreshold logic circuits by using standard CMOS process technologies. However, it is prudent to analyze the suitability of these standard technologies in terms of power and performance in the subthreshold regime. This topic is addressed later after a look at the process variations in subthreshold circuits, one of the most challenging obstacles in recent DSM technologies and dramatically accentuated in subthreshold designs.

#### 2.4 Process Variations

Besides the power consumption issue, the process variation issue in today's IC design is paramount [7]. This section briefly introduces this topic. Thereafter, a survey of the literature that address variability in subthreshold circuits is conducted. The identification of the dominant components of variations in the subthreshold regime is imperative to explore this issue.

Since fabrication process tolerances have not scaled proportionally with device dimensions, the relative impact of process variations (especially beyond 90nm) on power and timing has become more significant with each technology generation [67]. For example, the magnitude of variations in a transistor's gate length is predicted to increase from 35% in 130nm technology to almost 60% in 70nm technology. Usually, these variations are expressed as a fraction,  $3\sigma/\mu$ ,  $\sigma$  and  $\mu$  are the standard deviation and the mean of a process parameter, respectively, thus,  $3\sigma$  is considered the worst case shift in a parameter. Hence, a 60% variation in 70nm technology relates the  $\sigma$  of the distribution gate length across a large number of samples in 14nm. Consequently, to maintain the benefits of technology scaling, designers should treat these variations with alternative statistical strategies rather than traditional guard-band deterministic approaches [64].

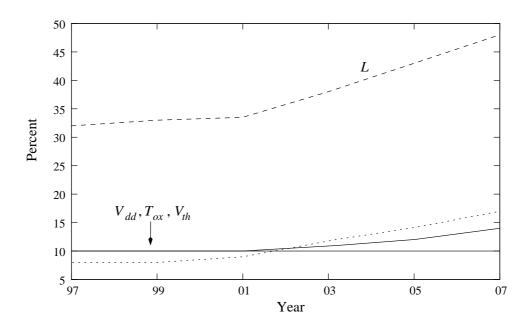

Process variations are fluctuations around the desired value of design parameters introduced during chip device fabrication [4]. The process variations are, inter-die (die-to-die) and intra-die (within-die). Inter-die variations originate from factors such as the processing temperature, and equipment properties [11]; intra-die variations result from factors such as the random placement of dopant atoms in the channel region, and channel length variations across a single die [67]. Traditionally, inter-die variations have become the main concern in CMOS digital circuit design [20]. However, intra-die variations have become just as important, and their impact on frequency and power is becoming more and more pronounced [11]. Figure 2.14 reflects the trend in the ratio between the intra-die and total process variations for some key technology device parameters. The data is reported in [43], and represents projections of the ITRS [7] in conjunction with data from IBM processes. It can be seen that variations in the channel length are expected to increase significantly. In addition, variability in oxide thickness, as well as threshold and supply voltages also increase.

Parameter variability in present designs has intensified the need to consider the impact of statistical leakage current variations. Leakage variability is vital in subthreshold designs, since this current drives the circuits. For example, a 10% variation in the transistor effective channel length can lead to as much as a three-fold difference in the amount of subthreshold leakage current [51]. Gate leakage current exhibits an even greater sensitivity to variations; a 10% variation in the oxide thickness indicates a 15X difference in current (in a 100nm Berkeley Predictive Technology Model) [63]. In addition, random microscopic fluctuations in the number and location of dopant atoms in the channel region, directly produce variations in the threshold voltage, subthreshold swing, drain current, and subthreshold leakage current [74]. For example, consider a uniformly doped nMOS, where  $L_g = 45nm$ ,  $W = 3L_g$ , impurity density  $N_{ch} = 10^{18}cm^{-3}$ , and  $W_{dep} = 35nm$ , the average number of acceptor  $N = N_{ch}L_gWW_{dep}$  is approximately 200. As a result, any random

Figure 2.14: Percentage of the total variations accounted for intra-die variation for different technology generations.

variation in this small number of dopants is translated into a shift in the value of  $V_{th}$ . Some work in the literature [10] shows that for the chips that meet the required operating frequency, a large portion dissipates very large amount of leakage power and thus, are unsuitable for commercial use. In today's designs, the yield is determined according to the operating frequency and the leakage power [4].

Given the categories of variation and the impact of device parameter variability in circuit behavior, the three essential parameters to account for are oxide thickness, gate length, and channel doping concentration.

# 2.4.1 Process Variations in Subthreshold Designs

The exponential dependence of subthreshold leakage current ( $I_{on}$  and  $I_{off}$  in subthreshold circuits) on the threshold voltage, derived from (2.5), results in subthreshold circuits with

a marked sensitivity to  $V_{th}$  variation. The threshold voltage is strongly related to several device parameters, which undergo considerable variations in DSM technologies [64]. Therefore, it is not surprising that subthreshold designs are prone to process variations.

As CMOS devices are further scaled in the nanometer regime, variations in the number and placement of dopant atoms in the channel region, called Random Dopant Fluctuation, (RDF), cause random variations in the threshold voltage, where the  $V_{th}$  standard deviation is roughly  $\sigma_{V_{th}} \propto \sqrt{\frac{N_{ch}}{WL}}$ . This source of variation is the most significant phenomenon in subthreshold operation, as shown by Zhai et al. [77]. They have reduced the impact of RDF through circuit sizing and the choice of circuit logic depth (i.e., averaging this random effect). In addition, the authors have derived statistical models for circuit delay, power, and energy efficiency as a function of the circuit parameters. Also, Kim et al. [32] have reduced the sensitivity to RDF by a device sizing optimization process which uses the Reverse Short Channel Effect (RSCE) present in standard CMOS non-uniform halo doping profile devices.

A major concern, related to process variations, is robustness or the correct functionality of subthreshold circuits. If, for example, the variations strengthen an nMOS, relative to a pMOS device, a PUN cannot drive the logic gate output fully to  $V_{dd}$  because of the increased idle leakage in the PUN, and viceversa. To cope with this robustness issue, Kwong and Chandrakasan [35] have introduced a criterion to determine how sizing affects the variability in the output logic swing and active  $I_{on}$  current in several topologies. With this consideration, they have proposed a design methodology for minimum energy subthreshold circuits by device sizing and optimal supply voltage. They have concluded that upsizing is necessary to achieve robustness at reduced voltages.

With small  $V_{th}$  variations, drive- $I_{on}$  pMOS and nMOS currents can easily differ by an order of magnitude, or even more, in subthreshold circuits. For example, with a reasonable  $6\sigma_{V_{th}} = 100mV$ , the  $V_{th}$  variation disturbs the MOS current ratios by approximately 1.17

times in strong inversion operation, whereas a similar  $V_{th}$  variation upsets current matching by at least 10 times in subthreshold operation [25]. As a consequence, the rise and fall times differ, impacting the switching frequency, and thus, power consumption. So, Melek et al. [39] have equalized mismatched currents by body bias compensation circuits. With a similar body biasing approach, Jayakumar and Khatri [27] have targeted inter- and intra-die Process, supply Voltage, and Temperature (PVT) variations. These techniques inherently lead to area and power overheads due to the extra-circuitiry, but these penalties are not included.

Obviously, process variation plays a key role in energy efficiency and robustness in subthreshold designs. In addition, it should be noted that the previous research involve circuit and architecture level techniques, whereas guidelines for designing a transistor for subthreshold operation is not considered under process variations. The next section conveys some considerations for constructing a subthreshold optimized transistor.

# 2.5 Devices in Subthreshold Circuits

In Subsection 2.3.1 is discussed that subthreshold designs can be constructed with standard CMOS process technologies. In 2005, Bipul Paul, Arijit Raychowdhury, and Kashik Roy [46] have optimized a transistor structure for digital subthreshold operation. They have demonstrated that the optimized device improves the delay and PDP of an inverter chain by 44% and 51%, respectively, of standard Bulk-MOS transistors operated in the subthreshold region. This is a key result for ultra-low-power designs and one of the sources for inspiration of this thesis. This section describes the features and design considerations of the optimized transistor for subthreshold operation.

Throughout this dissertation, the term *subthreshold transistor* refers to the device that is optimized for operating in the subthreshold region, whereas *standard transistor* corre-

sponds to an ordinary transistor oriented to strong inversion operation.

Highly scaled CMOS technologies have satisfied the demand for higher levels of integration and performance in modern VLSI systems. Since subthreshold designs inherently do not operate at high frequencies, it appears that modern highly scaled devices are not necessary in this regime. However, oxide thickness scaling benefits the subthreshold slope, (2.7), and the device length scaling results in a reduction in the total capacitance, as portrayed in Fig. 2.13. Consequently, device intrinsic delay ( $\tau \propto C_g$ ), and dynamic power are reduced such that, subthreshold designs also take advantage of technology scaling.

The behavior of scaled DSM devices differs considerably from that of the well known strong inversion (linear and saturation) region due to undesirable Short-Channel Effects (SCE). In order to mitigate the SCE such as  $V_{th}$  roll-off, drain induced barrier lowering, and body punchthrough, previously explained in Subsection 2.1.1, standard transistors incorporate nonuniform, halo, and retrograde doping profiles [66]. The DIBL is a function of a high drain voltage, applied to a short-channel device, resulting in a decreased  $V_{th}$  which substantially increases the subthreshold current. At even higher drain voltages, the device reaches the punch-through condition, and the gate loses control over the channel, developing high drain currents that are independent of the control gate voltage.

It is noted worthy that the described SCEs occur at high drain voltages. However, in the subthreshold regime, the power supply is small  $(V_{dd} \approx [400, 100]mV)$ , and the DIBL and body punchthrough are very low. As a result, to simplify the fabrication process technology and to significantly lessen the junction capacitances (resulting in a faster device operation and lower power consumption), the subthreshold device is constructed without any halo and retrograde doping profiles [46]. For this reason, the subthreshold transistor is characterized with a simplified uniform high-to-low doping profile in conjunction with the symmetrical Bulk-nMOS structure introduced in Fig. 2.1.

Note that the previous authors have not followed nor proposed an automatic framework

to perform the device optimization process, and have not accounted for process variations. The result is the absence of research on device level techniques to mitigate process variations. This thesis offers an automatic device optimization technique which includes process variations in a subthreshold transistor design.

# 2.6 Summary

This chapter describes some issues in reducing power consumption in scaled devices. A MOS's intrinsic leakage mechanisms are explained. The three more contributive leakage components in DSM technologies are subthreshold, oxide tunneling, and reverse bias p-n junction BTBT. Subthreshold leakage is the drive current in the subthreshold regime. In addition, the characteristics of MOS transistors in the subthreshold region are examined with respect to the strong inversion regime, including current flow mechanism, intrinsic capacitances, and the exponential relation between the gate voltage and drain current. Then, the paradigms of subthreshold logic are outlined. Subthreshold logic and strong inversion CMOS logic share several properties such as high noise margins, and low output impedance with improved features in power consumption and gain. Beginning with the analog field, it was not until the late 1990s that subthreshold circuits attracted attention in the digital domain; since then, several subthreshold systems have been implemented with standard DSM technologies. Later, process variations and their impact on circuit behavior are presented. The three essential parameters to account for variations are: oxide thickness, channel length, and channel doping concentration. Variability is one of the most challenging obstacles in recent technologies, and is accentuated in subthreshold designs. Finally, an optimized transistor structure for subthreshold operation is discussed, as a promising construction block in terms of simplified fabrication processes, faster operation, and lower power consumption.

# Chapter 3

# Problem Definition and Yield Maximization Technique

This chapter extends the qualitative concept of process variations from the last chapter by examining analytically the variations of device parameters, and their impact on performance and power consumption in a subthreshold device. After, the yield maximization problem is defined according to selected device parameters, lastly, the yield maximization technique is developed.

# 3.1 Design Parameters and Variations

This section covers the proposed device structure, the constraints of interest, and device parameters which are the most susceptible to variability. It should be noted that the device parameter models provide an understanding of why certain parameters are or not included in the set of design variables for the device optimization problem. The actual technique is carried out by the MEDICI device simulator [1].

### 3.1.1 Device Structure and Constraints

For convenience, the characteristics of a subthreshold transistor, models and definitions outlined in Section 2, are re-stated.

It is an established fact that for scaled MOS standard transistors, it is essential to incorporate halo and retrograde doping profiles to mitigate SCE [66]. However, in the subthreshold regime, the power supply is small  $(V_{dd} \approx [400, 100] mV < V_{th})$ , and the SCE such as DIBL and body punchthrough are minimal. As a result, for a more simplified fabrication process technology and significantly fewer junction capacitances (resulting in a faster device operation and a lower power consumption), the subthreshold device is characterized without any halo and retrograde doping profiles [46]. For this reason, a simplified uniform doping profile, in conjunction with the symmetrical Bulk-nMOS structure are depicted in Figure 3.1.

Since, in subthreshold logic, circuits are driven entirely by the subthreshold leakage current, it is important to further examine the major transistor leakage components in order to form a realistic estimation scheme.

Figure 3.1: Architecture of the subthreshold device.

### Transistor Leakage Currents and Intrinsic Delay in the Subthreshold Regime

The most contributive leakage components in nanometer technologies that are identified in Chapter 2 are subthreshold leakage,  $I_{sub}$ , gate leakage,  $I_{gate}$ , and reverse biased drain-substrate and source-substrate junction BTBT,  $I_{BTBT}$ .

$I_{sub}$  is the drive current in the subthreshold regime (i.e.,  $I_{on} = I_{sub}(V_{gs} = V_{ds} = V_{dd} < V_{th})$ , where  $V_{dd}$  is the power supply voltage). In the transistor off-state,  $I_{sub}$  is the drain current, when the gate voltage is zero (i.e.,  $I_{off_{sub}} = I_{sub}(V_{gs} = 0, V_{ds} = V_{dd} < V_{th})$ ). This off-state current is the dominant contributor to static power consumption. Therefore, for computing the total leakage current,  $I_{off_{sub}}$  should be taken into account. As derived in the last chapter, the subthreshold current is exponentially dependent on the threshold voltage as follows:

$$I_{sub}(V_{qs}, V_{ds}) = I_o e^{(V_{gs} - V_{th})/nV_T} \left( 1 - e^{-V_{ds}/V_T} \right), \tag{3.1}$$

where  $I_o = \mu_0 C_{ox} \frac{W}{L} V_T^2$ ,  $V_T = kT/q$  is the thermal voltage,  $C_{ox}$  is the oxide capacitance,  $\mu_0$  is the zero bias mobility,  $\frac{W}{L}$  is the width over length ratio of the device, and  $n = 1 + C_{dep}/C_{ox}$  is the subthreshold swing coefficient.

Direct gate leakage is a byproduct of the oxide thickness scaling,  $T_{ox}$ , required to overcome the  $V_{th}$  roll-off in scaled technologies. Such a current is due to the tunneling of an electron (or hole) from the Si-bulk through the gate-oxide potential barrier into the gate, and is an exponential function of  $T_{ox}$  [56], computed by

$$J_{DT} = A\left(\frac{V_{ox}}{T_{ox}}\right) \exp\left\{-\frac{BT_{ox}\left[1 - \left(1 - \frac{V_{ox}}{\phi_{ox}}\right)^{\frac{3}{2}}\right]}{V_{ox}}\right\},\tag{3.2}$$

where  $V_{ox}$  is the drop across the thin oxide, and  $\phi_{ox}$  is the barrier height for the tunneling particle (electron or hole). A and B are physical parameters dependent on the barrier height

and are given in the literature [56]. Because the tunneling current increases exponentially with a decrease in  $T_{ox}$ , the gate tunneling leakage cannot be neglected, when the oxide thickness is less than 3nm [53]. Therefore,  $I_{gate} = J_{DT} \times W \times L$  should be considered in computing the total leakage current, first to have a realistic indication of the leakage mechanisms which contribute to the leakage power consumption, and secondly, to consider the tradeoff between the  $V_{th}$  roll-off improvement by means of  $T_{ox}$  reductions and  $I_{gate}$  exponential increases.

In scaled standard CMOS technology, the higher substrate doping density and the necessary incorporation of halo profiles generate a significantly large junction BTBT current to flow through the reverse biased drain-substrate and source-substrate junctions [52]. The BTBT current,  $I_{BTBT}$  is estimated as [41]

$$I_{BTBT} = \left(\frac{WX_{jSDE}\hat{A}}{E_g^{1/2}}\right)\xi V_{dd} \exp\left(-\frac{\hat{B}E_g^{3/2}}{\xi}\right),\tag{3.3}$$

where

$$\xi = \sqrt{\frac{2qN_{aside}N_{sdside}}{\epsilon_{Si}(N_{aside} + N_{sdside})} \left[ V_{dd} + \frac{kT}{q} \ln \frac{N_{aside}N_{sdside}}{n_i^2} \right]}.$$

(3.4)

$X_{jSDE}$  is the source/drain extension junction depth (for standard CMOS DSM devices),  $N_{aside}$  and  $N_{sdside}$  are the p-side and n-side junction doping.  $E_g$  is the band-gap of the silicon, q is the electronic charge, and lastly,  $\hat{A}$  and  $\hat{B}$  are the physical coefficients given by Taur and Ning [65]. However, the BTBT leakage is mainly present in the halo and retrograde doping profiles, which are not incorporated in the subthreshold structure. Besides, as  $V_{dd}$  is reduced, the BTBT leakage is negligible [15, 46], and is ignored.

Therefore, to gain a realistic indication of the total leakage, TL, the first two leakage components are added for the worst case; that is,

$$TL = I_{sub}(V_{gs} = 0, V_{ds} = V_{dd}) + I_{gate}(V_{gs} = V_{dd}, V_{ds} = 0).$$

(3.5)

$V_{dd} < V_{th}$  to ensure the subthreshold operation. Figure 3.2 portrays a typical scheme, where these two leakage components contribute to the total leakage power consumption. This unwanted leakage power consumption represents a concern in energy-constrained systems for extending battery and system lifetime [73]. Therefore, TL is chosen as the first constraint in the optimization design problem.

Figure 3.2: Total leakage (TL) estimation scheme.

The primary metric for transistor speed is the transistor intrinsic delay [76],  $\tau$ , defined as

$$\tau = C_g \frac{V_{dd}}{I_{cm}},\tag{3.6}$$

where  $C_g$  is the gate capacitance per micron of the transistor width, and  $I_{on}$  is the subthreshold drive current/ $\mu m$ .  $\tau$  is the time required for a MOSFET to charge or discharge the gate of another identical MOSFET with a potential difference of  $V_{dd}$ . In fact,  $\tau$  is the metric for MOSFET performance suggested by the ITRS [7], and constitutes the performance constraint in the optimization design problem. To incorporate the device design parameters in the design problem, it is prudent to look at their variability impact on the defined power and performance constraints.

### 3.1.2 Device Parameters and Variations

To establish a set of device design parameters for the optimization problem, device parameters such as physical gate length  $(L_g)$ , oxide thickness  $(T_{ox})$ , junction depth  $(Y_j)$ , transistor width (W), and channel doping concentration  $(N_{ch})$  are considered in the following. A good starting point for the discussion is the exponential dependence between the subthreshold leakage  $I_{sub}$  and  $V_{th}$  in (3.1). Therefore, the variations in  $V_{th}$  impact both  $I_{off_{sub}}$  and driving current  $I_{on}$ . In turn, any variation in  $I_{on}$  echoes for  $\tau$  as well. Thus, the impact of device parameters on the  $V_{th}$  should be considered.

### Physical Gate Length $(L_g)$

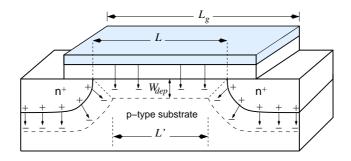

The threshold voltage of a short-channel device decreases as  $L_g$  is reduced. This is due to the closer proximity of the source and drain areas, whose surrounding depletion regions penetrate into a considerable portion of the channel, as signified in Figure 3.3 [75].  $W_{dep}$  is the depletion-layer width, L is the channel length, and L' is the reduced channel region. Consequently, the total charge in the channel,  $Q'_B$ , is reduced to trapezoidal region  $Q'_B \propto W_{dep} \times (L + L')/2$ , in contrast to the long-channel device case, where  $Q_B \propto W_{dep} \times L$  [75]. Therefore, less charge  $(Q'_B)$  must be inverted by the gate voltage to reach the  $V_{th}$  which is defined as follows [65]:

$$V_{th} = V_{fb} + \psi_s + \frac{Q_B'}{C_{ox}}. (3.7)$$

$V_{fb}$  is the flat-band voltage,  $\psi_s$  is the surface potential, and  $Q_B'$  is the total gate depletion (trapezoidal) charge. The shift in the  $V_{th}$ , originated by channel length scaling  $\Delta V_{th}$ , is

Figure 3.3: Charge sharing model.

approximated as [36]

$$\Delta V_{th} = [2(V_{bi} - \psi_s) + V_{ds}](e^{-L/2l} + 2e^{-L/l}), \tag{3.8}$$

where  $V_{bi}$  is the built-in potential, and l is the characteristic length defined as

$$l = \sqrt{\frac{\epsilon_{Si} T_{ox} W_{dep}}{\epsilon_{ox} \eta}}. (3.9)$$

$\epsilon_{Si}$ ,  $\epsilon_{ox}$  are the silicon and oxide permittivity, respectively, and  $W_{dep}/\eta$  is the average depletion layer width along the channel. This analytical approximation defines a short channel effect known as the  $V_{th}$  roll-off. As a result, any reduction in  $L_g$  increases the subthreshold leakage current, and hence, the power consumption [65]. This does lead to a faster device, since the reduction not only boosts the driving current, but also reduces the gate capacitance. Therefore, in finding an appropriate gate length, this tradeoff should be considered in the design problem.

### Oxide Thickness $(T_{ox})$

The oxide thickness has a considerable effect on the  $V_{th}$  since any variation in  $T_{ox}$  impacts the oxide capacitance,  $C_{ox}$  per unit area, given by

$$C_{ox} = \frac{\epsilon_{ox}}{T_{ox}}. (3.10)$$

Any variation in  $C_{ox}$  affects  $V_{th}$  in (3.7) and  $I_{sub}$  in (3.1). Moreover, the SCE is affected by  $T_{ox}$ , as given in (3.9); thus, a thinner oxide is needed to overcome the  $V_{th}$  roll-off in scaled devices. However, this oxide reduction increases the gate leakage current exponentially in (3.2), and hence, the power consumption. Careful engineering of the oxide thickness dimension is crucial to meet the desired device delay and total leakage constraints. As a consequence,  $T_{ox}$  should be considered in the design problem.

### Channel Doping $(N_{ch})$

As CMOS devices are scaled further into the nanometer regime, variations in the number, and the placement of dopant atoms in the channel region cause random variations in  $V_{th}$  (as discussed in Section 2). This effect, called Random Dopant Fluctuation (RDF), is accentuated with technology scaling, since the average number of dopant atoms in the channel is rather reduced [37]. A simple first order model of the  $V_{th}$  standard deviation  $(\sigma_{V_{th}})$ , due to RDF is given by [65]

$$\sigma_{V_{th}} = \frac{q}{\epsilon_{ox}} \sqrt{\frac{N_{ch} W_{dm}}{3L_g W}}.$$

(3.11)

Reinforcing this discussion, Zhai et al. [77] have concluded that RDF is the dominant source of variations in the subthreshold operation. It is observed that by reducing  $N_{ch}$ , the threshold voltage variation is also reduced. However, since in (3.7),  $Q'_B = \sqrt{4\varepsilon_{si}qN_{ch}\psi_B}$ , (where  $\psi_B$  is the difference between the Fermi potential and the intrinsic potential,  $|\psi_f - \psi_i|$ ), the threshold voltage also drops when the channel doping is reduced, increasing the subthreshold off-state leakage current. For these reasons, the channel doping concentration should also be included in the subthreshold device design.

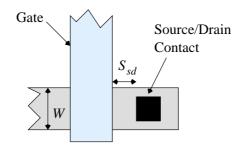

### Junction Depth $(Y_i)$

Aggressive device scaling has necessitated shallow junction depths to reduce the SCE and suppress the depletion layer penetration into the channel. The result is an increase in parasitic device resistance and involves a complex fabrication process [45, 42]. Consequently, any treatment of  $Y_j$  is limited by the sheet resistance,  $R_{sh}$ , of the source/drain region which is defined as [65]

$$R_{sh} = \rho_{sd} \frac{S_{sd}}{W},\tag{3.12}$$

where  $S_{sd}$  is the spacing between the gate edge and the source/drain contact edge in Fig. 3.4, and the sheet resistivity,  $\rho_{sd}$ , is given by

$$\rho_{sd} = \frac{\rho}{Y_i},\tag{3.13}$$

where  $\rho$  is the resistivity of the diffusion region. Therefore, it is desirable to keep the parasitic resistance low to achieve sufficient current-drivability. As a result, the design parameter,  $Y_j$ , should not be included as part of the optimization problem and follows the S/D profile from [6].

Figure 3.4: Top view of the transistor.

### Transistor Width (W)