# On Nonlinear Time-Invariant Behavioural Models of Power Transistors Used in the Computer-Aided Design of Power Amplifiers

$\mathbf{b}\mathbf{y}$

Amir-Reza Amini

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2023

© Amir-Reza Amini 2023

### **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner:        | Johannes Benedikt<br>Deputy Director of School and Professor, School of Engineering,<br>Cardiff University |

|---------------------------|------------------------------------------------------------------------------------------------------------|

| Supervisor(s):            | Slim Boumaiza<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo        |

| Internal Member:          | Lan Wei<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo              |

| Internal Member:          | John Long<br>Professor, Dept. of Electrical and Computer Engineering,<br>University of Waterloo            |

| Internal-External Member: | James Martin<br>Dept. of Diverse and Astronomy                                                             |

Professor, Dept. of Physics and Astronomy, University of Waterloo

### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The Radio Frequency (RF) Power Amplifier (PA) is the main consumer of power in a wireless transmitter. Energy efficient PA design aided with circuit simulation tools requires accurate nonlinear models of the power transistors that lie at the heart of the PAs. This thesis proposes a novel methodology for extracting and implementing power transistor behavioral models from load-pull measurements. These models provide a valuable design aid to power amplifier designers looking to simulate the nonlinear behaviour of their RF circuit designs based on nonlinear characterizations of the power transistors.

Two types of power transistor behavioural models are proposed in this work. The first type is called the time-domain poly-harmonic distortion model (TD-PHD) and it targets the nonlinear multi-harmonic response of power transistors at a fixed fundamental frequency. This type of model allows the PA designer to simulate how the harmonic impedances of their designed RF matching networks effects the large signal behaviour of the PA. The TD-PHD model is shown to be able to replicate the time-domain waveforms of a power transistor under multi-harmonic source and load-pull characterization.

The second model is a generalization of the first model to target a set of non-uniformly spaced fundamental frequencies and is called the time-domain multi-tone distortion model (TD-MTD). Time-domain multi-tone distortion models that are extracted from load-pull measurements spanning multiple carrier frequencies are shown to recreate the load-pull performance contours of interest to PA designers. As a demonstration of TD-MTD models, two distinct behavioural models for the main and peaking transistors of a two-way Doherty PA design are extracted from load-pull measurements and the resulting PA design is then simulated and shown to accurately reflect the measured performance of the fabricated PA as a validation of the usefulness of this modelling methodology for high power amplifier design.

#### Acknowledgements

I am forever grateful for the guidance and kindness of the late Professor Safieddin Safavi-Naeini who was an original member of my PhD examination committee. He will be greatly missed by the many he touched in life.

I would like to thank all the efforts of my PhD research supervisor, Professor Slim Boumaiza, who always supported his students. I would also like to give thanks to the members of my examination committee, Professor Lan Wei and Professor James Martin for their guidance from the beginning stages of this research. In addition, I would like to thank Professor John Long who graciously agreed to join my PhD examination committee.

Throughout my graduate studies at the University of Waterloo, I learned a lot of what is presented in this thesis from fellow graduate students Dylan Bespalko and Hassan Sarbishaei.

Last but not least, I would like to acknowledge all who helped me with proof-reading my conference and journal papers and this PhD thesis, including Saeed Rezaei, Igor Acimovic, Carl Conradi, and Rob Salmond.

### Dedication

To Katie, my unwavering source of love and support,

Your love has propelled me forward, filling each day with motivation and hope. Thank you for standing by my side, even during the most challenging times.

To Daisy and Bear, my loyal companions,

Your wagging tails, playful antics, and unconditional love offered me solace and comfort when the pressures of research weighed heavily on my shoulders.

To Katie, Daisy, and Bear, together you have been the pillars of strength in my life. This thesis stands as a testament to the power of love, support, and unwavering companionship. I am forever grateful for each of you, and I dedicate this work to you with boundless love and appreciation.

# **Table of Contents**

| Li | st of | Figures                                                                  | ix   |

|----|-------|--------------------------------------------------------------------------|------|

| Li | st of | Tables                                                                   | xiii |

| 1  | Intr  | oduction                                                                 | 1    |

| 2  | Stat  | te of the Art of Nonlinear Power Transistor Modeling                     | 6    |

|    | 2.1   | Background                                                               | 6    |

|    | 2.2   | The Nonlinear Behaviour of a Packaged High Power Transistor              | 8    |

|    | 2.3   | Compact Models                                                           | 14   |

|    | 2.4   | Harmonic Balance Simulation of Nonlinear Circuits                        | 19   |

|    | 2.5   | Large Signal Characterization of Power Transistors                       | 20   |

|    |       | 2.5.1 Calibration and Measurement of a Nonlinear Vector Network Analyzer | 20   |

|    |       | 2.5.2 Load-Pull Measurements of Power Transistors                        | 22   |

|    | 2.6   | Poly-Harmonic Distortion Models                                          | 27   |

|    | 2.7   | Discussion on the State of the Art and Motivation for This Thesis        | 36   |

| 3  | Tim   | ne-Domain Poly-Harmonic Distortion Models                                | 39   |

|    | 3.1   | The Intuitive Argument for TD-PHD Models                                 | 39   |

|    | 3.2   | The Nonlinear Impulse Response Formulation of TD-PHD Models              | 45   |

|    | 3.3   | Development of Power Transistor TD-PHD Models                            | 49   |

| R | efere | nces            |                                                                                                               | 105 |

|---|-------|-----------------|---------------------------------------------------------------------------------------------------------------|-----|

|   | 5.3   | Future          | Work                                                                                                          | 104 |

|   | 5.2   |                 | Relevant Publications                                                                                         | 103 |

|   |       | 5.1.2           | A Model for the Nonlinear Behaviour of Power Transistors Across a<br>Range of Fundamental Frequencies         | 102 |

|   |       | 5.1.1           | A Model for the Multi-Harmonic Nonlinear Behaviour of Power Tran-<br>sistors at a Fixed Fundamental Frequency | 102 |

|   | 5.1   | List of         | Contributions                                                                                                 | 102 |

| 5 | Con   | clusior         | 18                                                                                                            | 101 |

|   | 4.3   | Chapte          | er Conclusion                                                                                                 | 100 |

|   |       | 4.2.2           | Doherty High Power Amplifier Simulation of Multi-Tone Distortion         Models                               | 90  |

|   |       | 1.2.1           | surements and its Implementation in a Harmonic Balance Simulator                                              | 81  |

|   |       | mentat<br>4.2.1 | tion in a Harmonic Balance Simulator                                                                          | 80  |

|   | 4.2   |                 | tion and Validation of the Proposed TD-MTD Model and its Imple-                                               |     |

|   |       | 4.1.2           | Formulation of the TD-MTD Model                                                                               | 77  |

|   |       | 4.1.1           | Discrete Projection of a Continuous-Time Volterra Series on a Fixed<br>Frequency Grid                         | 74  |

|   | 4.1   | The Ve          | olterra Series Projection Formulation for TD-MTD Models                                                       | 73  |

| 4 | Tim   | ne-Dom          | nain Multi-Tone Distortion Models                                                                             | 72  |

|   | 3.4   | Chapte          | er Conclusions and Discussion                                                                                 | 70  |

|   |       | 3.3.4           | Comparison of the Simulation of Extracted TD-PHD Models with<br>Multi-Harmonic Loadpull Measurements          | 61  |

|   |       | 3.3.3           | Implementation of a TD-PHD Model in a Harmonic Balance Simulator                                              | 59  |

|   |       | 3.3.2           | TD-PHD Model Extraction From Multi-Harmonic Load-Pull Mea-<br>surements                                       | 56  |

|   |       | 3.3.1           | Multi-harmonic Loadpull Characterization Of Power Transistors                                                 | 51  |

# List of Figures

| 2.1  | Simplified Downlink Path of a Mobile Wireless Communication Network .                                         | 7  |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Single Transistor Power Amplifier                                                                             | 8  |

| 2.3  | Two Transistor Doherty Power Amplifier                                                                        | 9  |

| 2.4  | The DC bias of a packaged power transistor                                                                    | 10 |

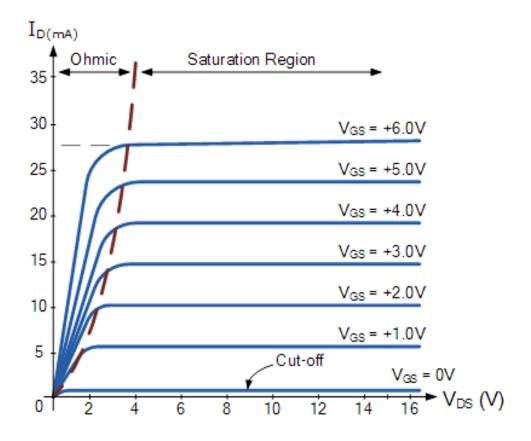

| 2.5  | The DC IV characteristics of a hypothetical field effect transistor with zero threshold voltage               | 11 |

| 2.6  | The DC relationship between the gate DC voltage and the drain current for a fixed DC drain voltage value      | 12 |

| 2.7  | The basic single transistor analog power amplifier classes of operation $\ldots$                              | 13 |

| 2.8  | Typical Compact Model Topology of a Field-Effect Transistor                                                   | 15 |

| 2.9  | Intrinsic Transistor Model                                                                                    | 16 |

| 2.10 | Form of the DynaFET compact model                                                                             | 17 |

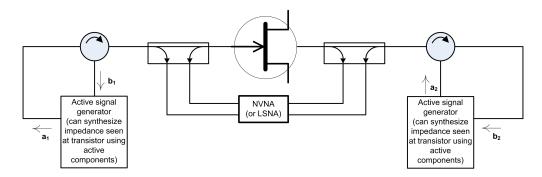

| 2.11 | A Nonlinear Vector Network Analyzer (NVNA) measurement                                                        | 22 |

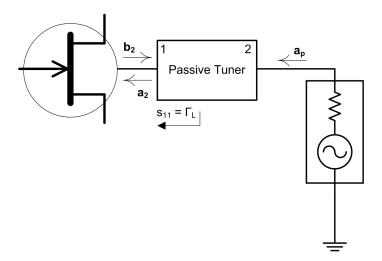

| 2.12 | A Passive Load-pull Measurement                                                                               | 23 |

| 2.13 | An active load-pull measurement                                                                               | 24 |

| 2.14 | A hybrid load-pull measurement                                                                                | 25 |

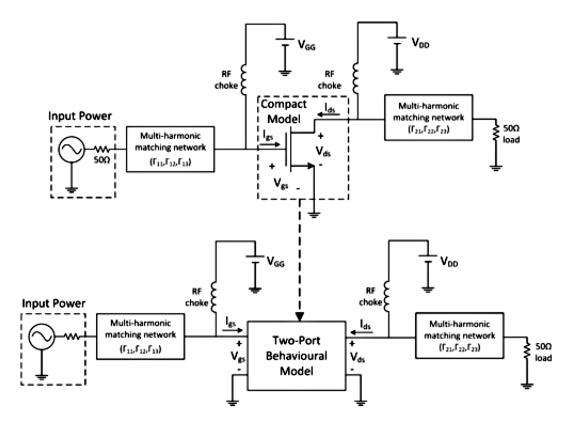

| 2.15 | Using a Compact Model of a Power Transistor as the Device Under Test for<br>a Simulated Load Pull Measurement | 26 |

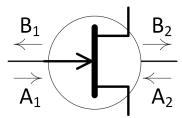

| 2.16 | Incident and reflected powerwaves on a device under test                                                      | 28 |

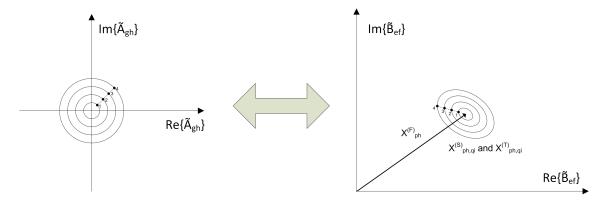

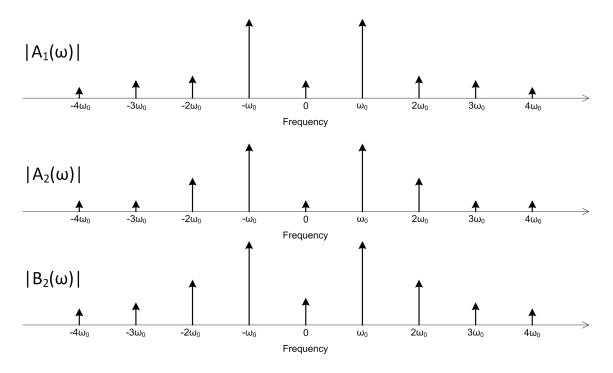

| 2.17 | Visual representation of the $X_{ph}^{(F)}$ , $X_{ph,qi}^{(F)}$ and $X_{ph,qi}^{(T)}$ X-parameters            | 31 |

| 2.18 | Periodic stimulus in the frequency domain                                                                     | 32 |

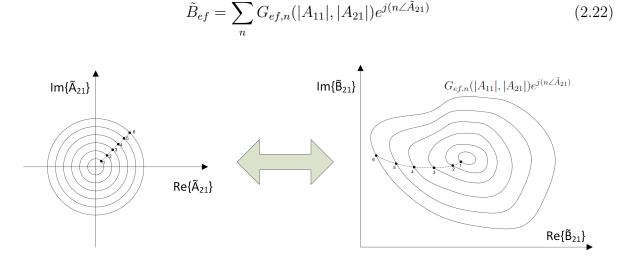

| 2.19 | Change in $\tilde{B}_{21}$ with constant $ A_{11} $ and a polar sweep of $\tilde{A}_{21}$                                                                                                                                                                                                            | 35 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

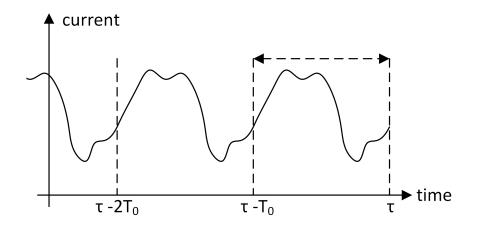

| 3.1  | A single period of a periodic signal fully represents the waveform over all time                                                                                                                                                                                                                     | 40 |

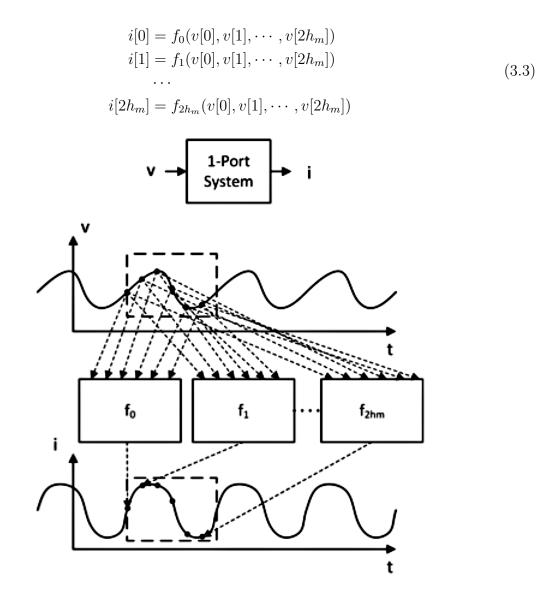

| 3.2  | A basic non-time-invariant but general discrete waveform shape mapping scheme                                                                                                                                                                                                                        | 42 |

| 3.3  | A time-invariant discrete waveform shape mapping scheme                                                                                                                                                                                                                                              | 44 |

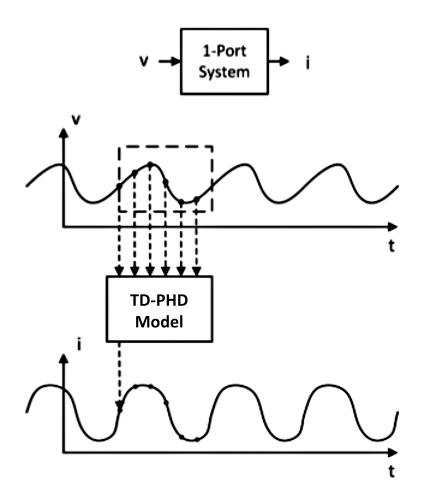

| 3.4  | A periodic signal over its fundamental period (thick line) can be equivalently<br>represented as either a sum of discrete harmonic frequency components (rep-<br>resented by waveforms with dashed lines) or as discrete time representation<br>(represented by the discrete dots on the thick line) | 47 |

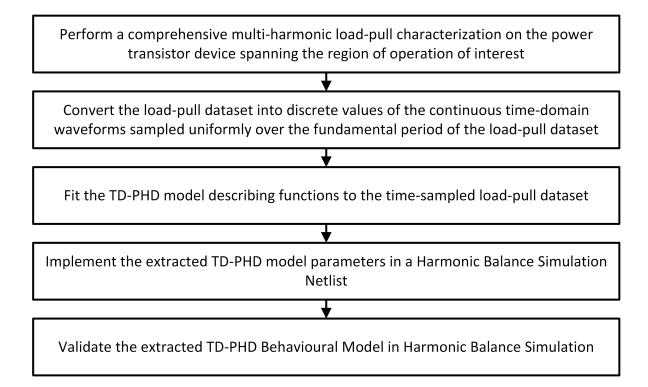

| 3.5  | A flowchart of the steps required to develop a TD-PHD model                                                                                                                                                                                                                                          | 51 |

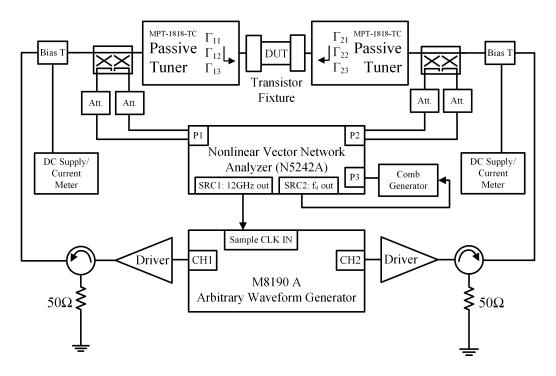

| 3.6  | Hybrid passive/active waveform engineering and large-signal characteriza-<br>tion testbench.                                                                                                                                                                                                         | 52 |

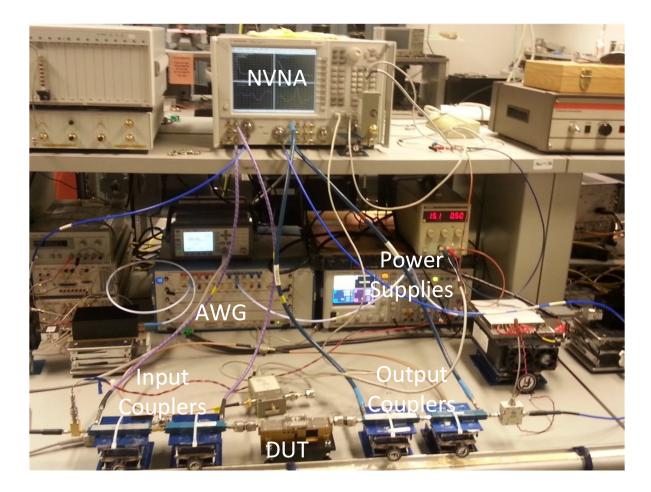

| 3.7  | Active waveform engineering and large-signal characterization testbench dur-<br>ing calibration                                                                                                                                                                                                      | 53 |

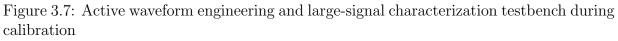

| 3.8  | The variation of the multi-harmonic load-pull characterization dataset in terms of both the harmonic impedances as well as the dynamic load-lines of the device at the power transistor reference plane                                                                                              | 55 |

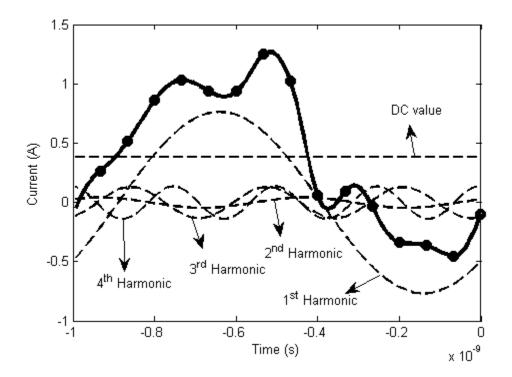

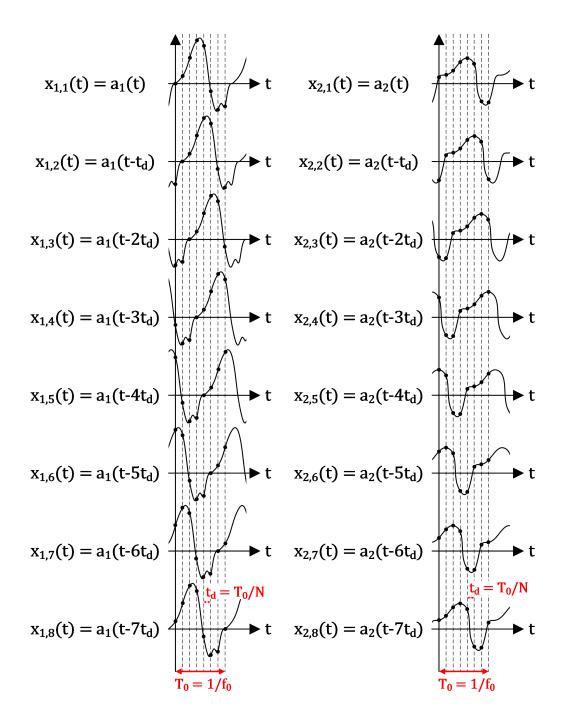

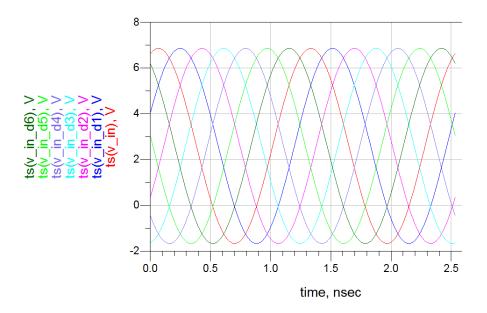

| 3.9  | A graphical example of an N=8 input signal discretization to develop time-<br>domain PHD modeling data                                                                                                                                                                                               | 62 |

| 3.10 | A graphical example of an N=8 output signal discretization to develop time-<br>domain PHD modeling data                                                                                                                                                                                              | 63 |

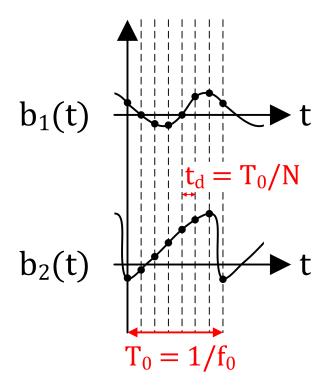

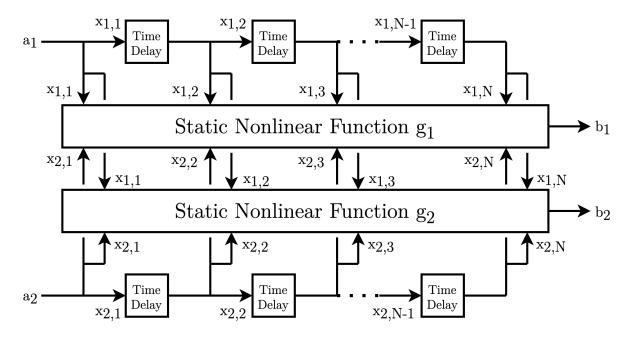

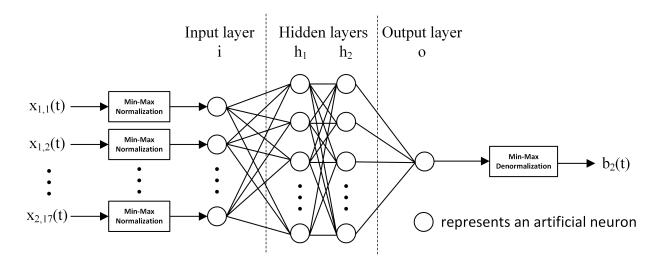

| 3.11 | Diagram of artificial neural network architecture used for the $b_2(t)$ output of<br>the power transistor model based on the 22 auxiliary signals $a_1(t)$ through<br>$a_1(t-10t_d)$ and $a_2(t)$ through $a_2(t-10t_d)$                                                                             | 64 |

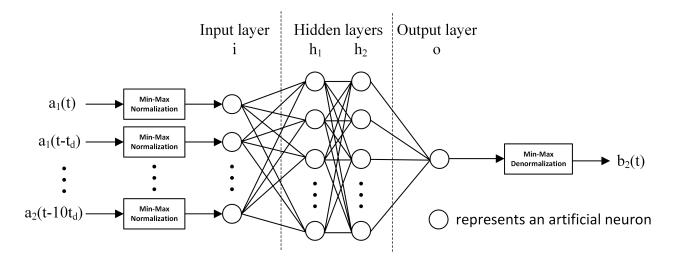

| 3.12 | Harmonic balance implementation circuit of a 2-port TD-PHD model to use<br>as an RF transistor behavioral model                                                                                                                                                                                      | 65 |

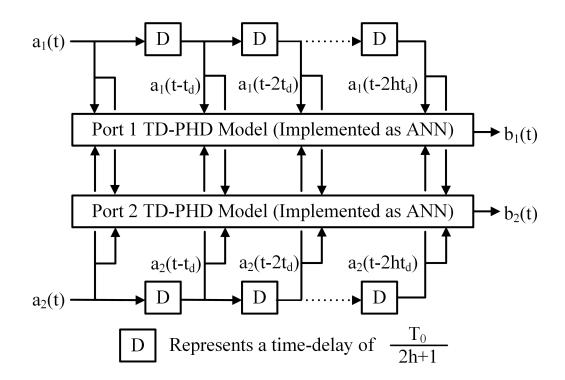

| 3.13 | A multi-harmonic waveform and its delayed version over 7 steps within its fundamental period                                                                                                                                                                                                         | 66 |

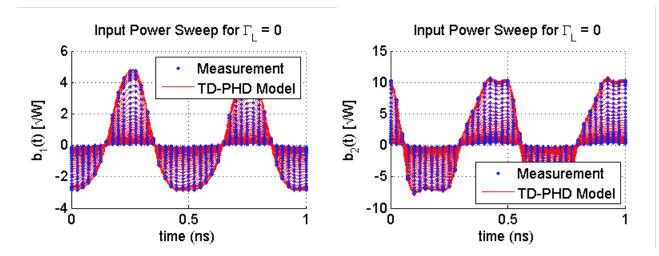

| 3.14 | Measured vs. TD-PHD model power sweep time-domain waveforms for $\Gamma_L = 0$ with a $\text{NMSE}_{b_1(t)} = -42.334dB$ and $\text{NMSE}_{b_2(t)} = -38.637dB$                                                                                                                                      | 66 |

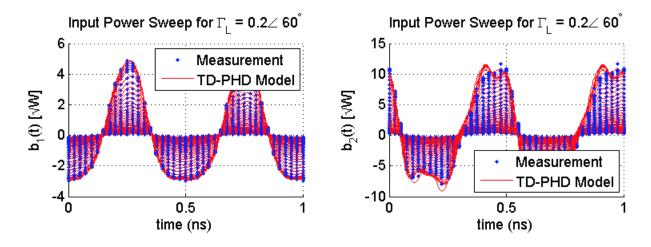

| 3.15 | Measured vs. TD-PHD model power sweep time-domain waveforms for $\Gamma_L = 0.2\angle 60^\circ$ with a NMSE <sub>b1(t)</sub> = -41.286dB and NMSE <sub>b2(t)</sub> = -30.985dB                                                                                                                       | 67 |

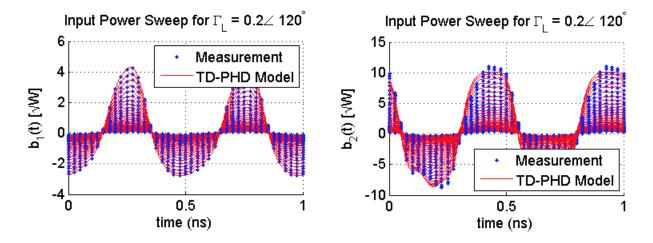

| 3.16 | Measured vs. TD-PHD model power sweep time-domain waveforms for $\Gamma_L = 0.2 \angle 120^\circ$ with a $\text{NMSE}_{b_1(t)} = -41.123 dB$ and $\text{NMSE}_{b_2(t)} = -35.954$                                                                      | 67 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

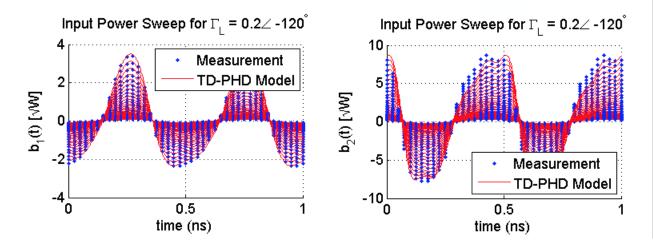

| 3.17 | Measured vs. TD-PHD model power sweep time-domain waveforms for $\Gamma_L = 0.2 \angle -120^\circ$ with a $\text{NMSE}_{b_1(t)} = -40.844 dB$ and $\text{NMSE}_{b_2(t)} = -25.380 dB$ .                                                                | 68 |

| 3.18 | Measured vs. TD-PHD model power sweep time-domain waveforms for $\Gamma_L = 0.2 \angle -60^\circ$ with a NMSE <sub>b1(t)</sub> = -39.989dB and NMSE <sub>b2(t)</sub> = -26.017dB .                                                                     | 68 |

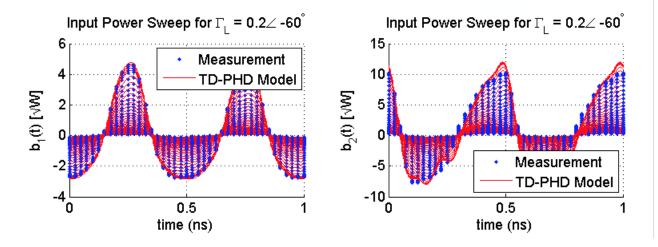

| 3.19 | Measured Gain and Power Added Efficiency Performance of the 10W GaN<br>RF transistor compared to the TD PHD model prediction at the Maximum<br>Efficiency Optimum Impedance multi-hermonic metch with an NMSE                                          |    |

|      | Efficiency Optimum Impedance multi-harmonic match with an $\text{NMSE}_{b_2(t)} = -32.029 dB$                                                                                                                                                          | 69 |

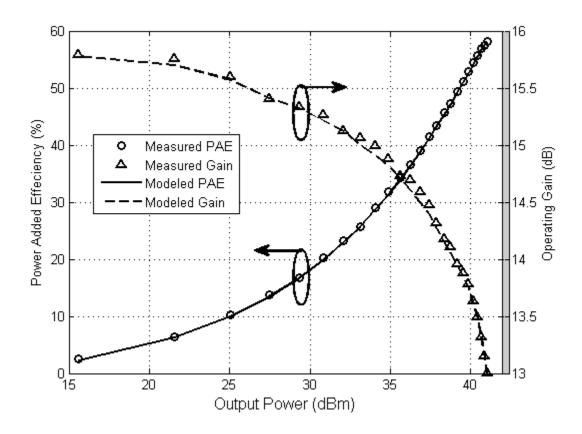

| 4.1  | A flowchart of the steps required to develop a TD-MTD model                                                                                                                                                                                            | 73 |

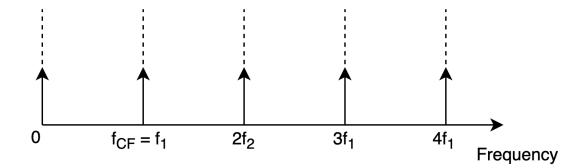

| 4.2  | Frequency grid (dashed lines) and location of frequency content (arrows) for the TD-PHD model                                                                                                                                                          | 74 |

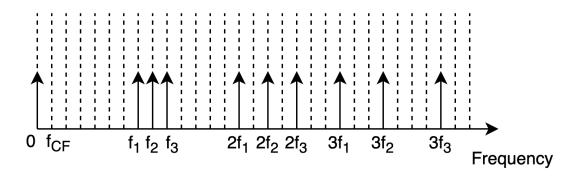

| 4.3  | Frequency grid (dashed lines) and the location of frequency content of multi-<br>harmonic load-pull at three different fundamental frequencies (arrows) for a<br>TD-MTD model                                                                          | 78 |

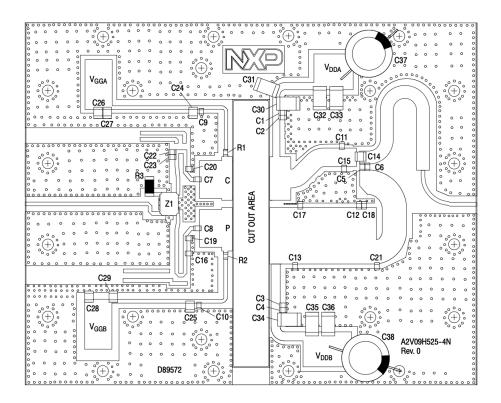

| 4.4  | The dual-device load-pull fixture designed for the NXP A2V09H525 package                                                                                                                                                                               | 81 |

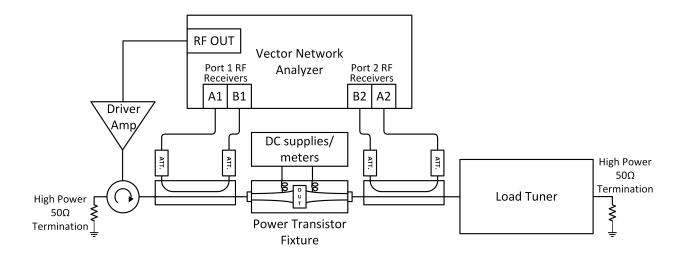

| 4.5  | Block diagram of the load-pull measurement setup used to perform load-pull measurements on the power transistor in an RF fixture                                                                                                                       | 82 |

| 4.6  | Harmonic balance implementation circuit of a 2-port TD-PHD model to use<br>as an RF transistor behavioral model                                                                                                                                        | 83 |

| 4.7  | Diagram of artificial neural network architecture used for the $b_2(t)$ output<br>of the power transistor model based on the 14 auxiliary signals $x_{1,1}$ through                                                                                    |    |

|      | $x_{2,17}$                                                                                                                                                                                                                                             | 85 |

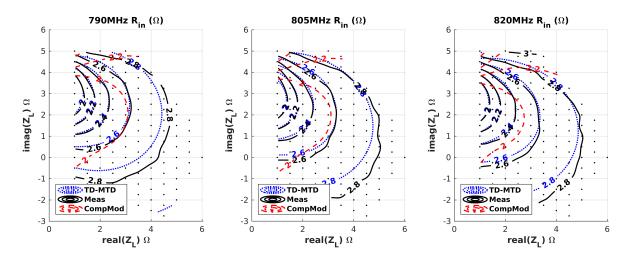

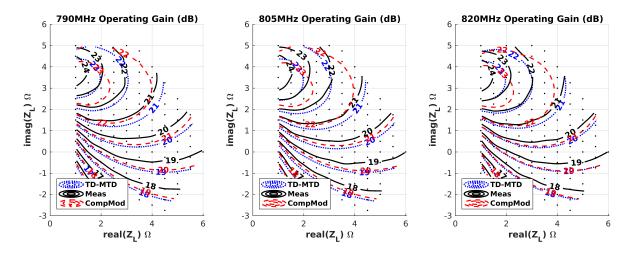

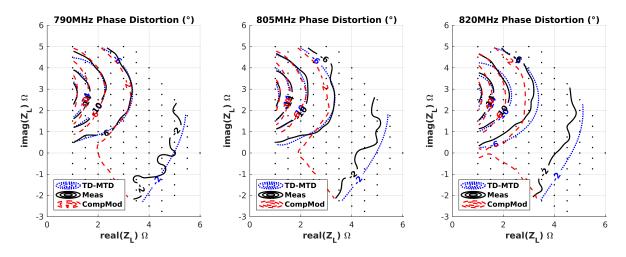

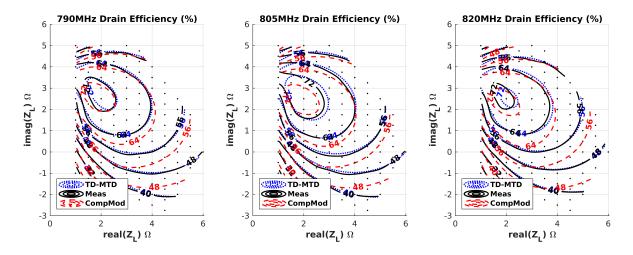

| 4.8  | The real part of the main power transistor input impedance load-pull con-<br>tours of the TD-MTD model and Compact Model at 2dB of gain compression<br>across the three discrete fundamental frequencies compared to the load-pull<br>measurements     | 86 |

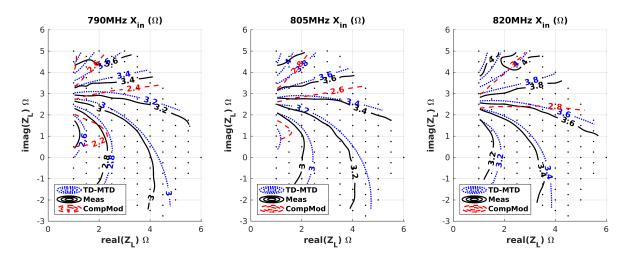

| 4.9  | The imaginary part of the main power transistor input impedance load-<br>pull contours of the TD-MTD model and Compact Model at 2dB of gain<br>compression across the three discrete fundamental frequencies compared to<br>the load-pull measurements | 87 |

|      |                                                                                                                                                                                                                                                        |    |

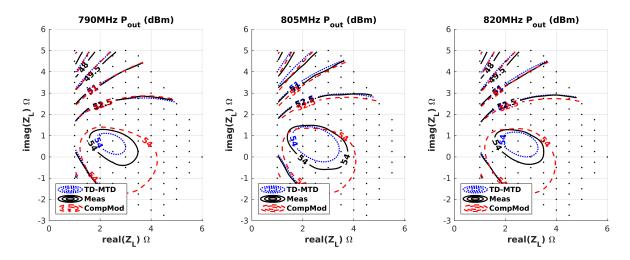

| 4.10 | The main power transistor output power load-pull contours of the TD-MTD model and Compact Model at 2dB of gain compression across the three discrete fundamental frequencies compared to the load-pull measurements .                                     | 88 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.11 | The main power transistor operating gain load-pull contours of the TD-MTD model and Compact Model at 2dB of gain compression across the three discrete fundamental frequencies compared to the load-pull measurements .                                   | 88 |

| 4.12 | The main power transistor AMPM distortion load-pull contours of the TD-<br>MTD model and Compact Model at 2dB of gain compression across the three<br>discrete fundamental frequencies compared to the load-pull measurements .                           | 89 |

| 4.13 | The main power transistor drain efficiency load-pull contours of the TD-<br>MTD model and Compact Model at 2dB of gain compression across the three<br>discrete fundamental frequencies compared to the load-pull measurements .                          | 89 |

| 4.14 | Reference Doherty Printed Circuit Board Layout and Component locations                                                                                                                                                                                    | 92 |

| 4.15 | Reference Doherty Printed Circuit Board Vendor Bill of Materials                                                                                                                                                                                          | 93 |

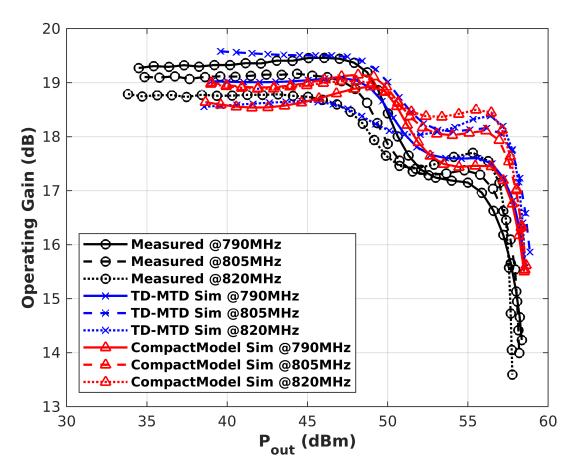

| 4.16 | Comparison of the simulated and measured AMAM frequency variation of the reference Doherty PA                                                                                                                                                             | 94 |

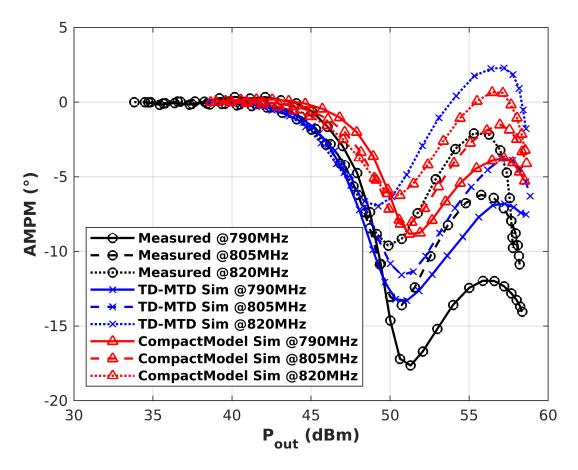

| 4.17 | Comparison of the simulated and measured AMPM distortion frequency variation of the reference Doherty PA                                                                                                                                                  | 95 |

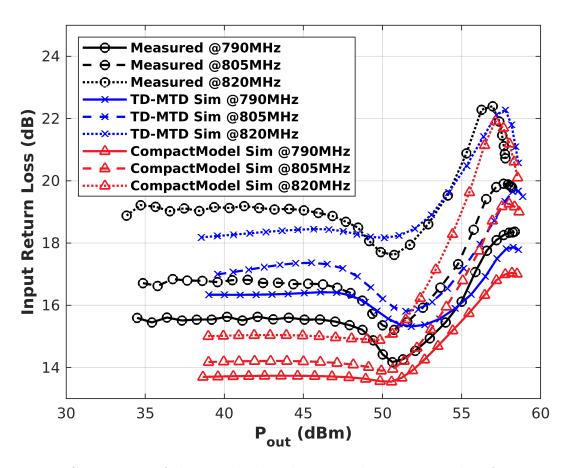

| 4.18 | Comparison of the simulated and measured input return loss frequency vari-<br>ation of the reference Doherty PA                                                                                                                                           | 96 |

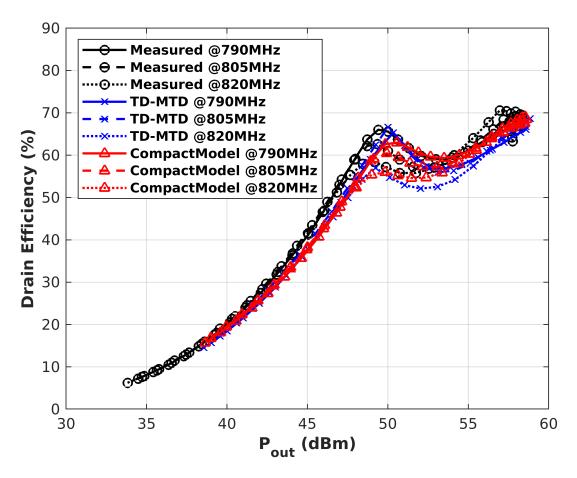

| 4.19 | Comparison of the simulated and measured drain efficiency frequency vari-<br>ation of the reference Doherty PA                                                                                                                                            | 97 |

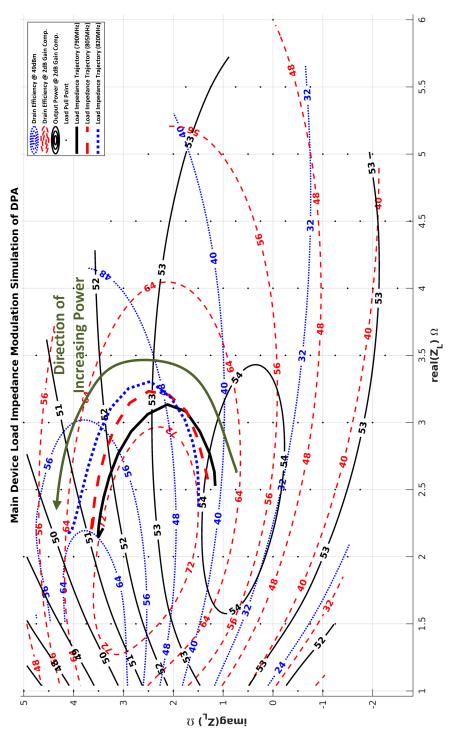

| 4.20 | The load impedance modulation of the main device at the 3 frequencies<br>in the Doherty HPA superimposed on the average power (49dBm) drain<br>efficiency contours and the 2dB gain compression output power contours at<br>the center frequency (805MHz) | 98 |

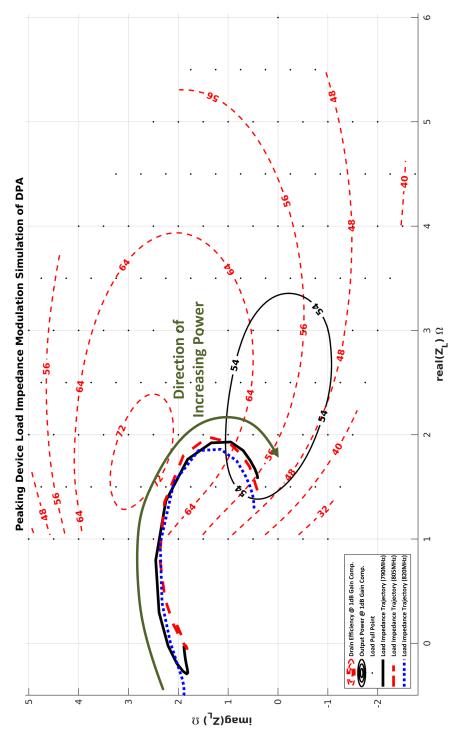

| 4.21 | The load impedance modulation of the peaking device at the 3 frequencies<br>in the Doherty HPA superimposed on the average power efficiency contours<br>and the 1dB gain compression output power contours at the center frequency<br>(805MHz)            | 99 |

# List of Tables

| 4.1 | Table of simulated NMSE of RF and DC parameters of the Compact model<br>and TD-MTD model of the NXP A2V09H525 main device over the entire<br>load-pull measurement dataset | 86 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | Table of simulated NMSE of RF and DC parameters of the Compact modeland TD-MTD model for a power-sweep of the reference NXP A2V09H525two-way Doherty design                | 90 |

| 4.3 | Gain Magnitude and Phase Compression comparison at average and peak power                                                                                                  | 91 |

| 4.4 | Input Return Loss and Drain Efficiency comparison at average and peak<br>power                                                                                             | 91 |

## Chapter 1

## Introduction

This thesis will aim to provide power amplifier designers with a methodology to develop simulation models for the power transistors they use in their designs. These models will be based on Radio Frequency (RF) measurements of the power transistors. These measurements are performed in similar electrical conditions to how the power transistor will operate when it is functioning as part of a power amplifier design. The objective of this research was to propose a methodology to produce nonlinear models of a power transistor from the RF measurements of those devices. These models are called behavioural models, since they only model the RF behaviour of the device as measured, directly.

The large signal characterization of a high power transistor involves the RF measurement of the power transistor over varying loads and bias conditions, requiring calibrated narrow-band pulsed-RF measurements at different power levels and at different frequencies. The datasets produced from power transistor RF characterization can often get very large. One of the main objectives of this research was to find the simplest form a behavioural model should have that can both capture the nonlinear dynamics of the power transistor and uniquely fit the behaviour of the device over the entirety of the measurement dataset. We tried to avoid developing a modeling strategy that relies on using a *guided characterization* on a fixed measurement grid in order to extract the different model parameters, and instead focused on being able to generate models from arbitrary spaced and randomly-generated load-pull data. The incentive here is to develop a methodology to convert already existing load-pull data of RF power transistors into behavioural models that can be used to design RF power amplifiers in the circuit simulator.

While all the nonlinear behavioural models that have been proposed in the literature have been described in the frequency-domain, that is, they describe the behaviour of the signal at the device ports at discrete frequencies, our research found that a simpler model construction can be used to describe the nonlinear behaviour if a time-domain model is used. This time-domain modeling approach lends itself pretty well to future generalization to multi-tone and modulated signal stimulus as the analysis and simulation of the long-term memory-effects rely heavily on time-domain methods. Another aspect of power transistor modeling that this research set out to tackle was the development of models that can track the so-called *hard nonlinearities* of RF power transistors without using look-up tables, while providing a robust converging model in a nonlinear circuit simulation environment.

There are two main contributions in this thesis. The first contribution is the proposal of Time-Domain Poly-Harmonic Distortion (TD-PHD) models. These models were inspired by the state of the art poly-harmonic distortion models that were described in the frequency-domain, but were reformulated to be described in the time-domain. Polyharmonic distortion models target the multi-harmonic behaviour of a power transistor at a fixed fundamental frequency. Part of this contribution is the methodology to post-process the measurement dataset in order to prepare it for the proposed behavioural model extraction. The other part of this contribution is the implementation of the extracted model in a harmonic balance circuit simulation, an important type of nonlinear RF circuit simulation used for power amplifier design. The second contribution of this thesis is the proposal of Time-Domain Multi-Tone Distortion (TD-MTD) models. These models are a generalization of the TD-PHD models to allow for a model extraction from measurement data spanning a non-uniformly spaced frequency grid. This generalization allows the power amplifier designer to take their load-pull data spanning multiple frequencies as is, and fit a single TD-MTD model to the load-pull data such that the simulation model behaves the same way in the harmonic balance simulation of the power amplifier circuit as it does in the measurement of the fabricated power amplifier. With the TD-MTD model (and also similarly for the previous TD-PHD model) this end is achieved without imposing any additional restrictions on the measurement dataset used to extract the model, that is, a model can be extracted from measurements that are irregularly spaced in the measurement space.

In this thesis, a demonstration of the TD-MTD model for the design of a two-way Doherty power amplifier is used as a validation of the large-signal design application of the proposed behavioural model. The comparison of the simulation and the measurement was also done for the same power amplifier design with a compact model available from the power transistor vendor and it is shown that the prediction of the TD-MTD model for the Doherty power amplifier performance is no worse than a compact model. It should be stressed that the purpose of behavioural models is not to replace compact models, but to fill in the modeling gap when compact models are not available. The device used for the demonstration in this thesis was a mature LDMOS RF power transistor device with a mature compact model. Often power amplifier designers are working with power transistors that are recently designed or are from vendors that don't have readily available compact models for their power transistor devices. The availability of load-pull measurement platforms allows power amplifier designers to fully characterize the RF nonlinear performance of their power transistor devices at the frequencies of interest, in addition to the ability to use this captured data to create a simulation model that can be used to design a power amplifier around that power transistor.

In the implementation of both the TD-PHD and TD-MTD models presented in this thesis, artificial neural networks (ANNs) are used to implement the multi-variate nonlinear function at the heart of the model. While non-ANN versions of the TD-PHD and TD-MTD model were theorized and implemented in the work towards this thesis, the ANN implementation that is mainly presented in this thesis allows the tackling of the *hard non-linearities* of the RF power transistor, and the structure of the smooth bounded activation functions of the artificial neurons that make up the artificial neural network allow for the generation of a model that has robustly converges to the solution within the iterations of the nonlinear circuit simulator. The contributions of this thesis include use of ANNs to tackle the hard nonlinearities, but also the structure of the model, the time-delays between the auxiliary signals used in the model, the implementation of the models in the frequency-domain simulator, and how the measurement data has to be post-processed for model fitting.

The models proposed in this thesis are extracted from load-pull measurements of RF power transistors. These load-pull measurements can either be real measurements of physical power transistors, or it can be simulated load-pull measurements. A compact model can be simulated in a harmonic balance simulator and the simulation result can be stored as load-pull data that can be used to extract a behavioural model. Using this method, one can extract a behavioural model to fit the simulated large signal behaviour of a compact model. In this technique the compact model will be the device under test, and the harmonic balance simulator will emulate the load-pull measurement of the power transistor device. One reason to use this method when evaluating behavioural models is because the harmonic balance simulation of a compact model is deterministic and if a behavioural model can reproduce the same load-pull measurement result as the compact model when the behavioural model itself is put as the device under test in a simulated load-pull measurement, then it shows that the behavioural model is at least capable of mimicking a nonlinear device with the complexity of compact models. Of course the next level of validation, after the extraction of simulation models from measurements of power transistors, is the accurate simulation of a power amplifier design that incorporates these power transistors. A good model will be able to provide a good simulated prediction of the RF measurement of the physically built power amplifier design.

In Chapter 2 the state of the art of power transistor modeling and simulation will be presented, starting with a background on the application of computer-aided design of power transistors followed by an explanation of the physics of the power transistors and the different nonlinear and dynamical effects involved in power transistor operation. Then an overview of the compact modeling of power transistors will be provided as it is the main alternative for power transistor models to the behavioural models presented in this thesis. Next, the harmonic balance simulation, the main type of nonlinear frequency-domain circuit simulation that is used by power amplifier designers will be discussed. Parallel to the simulated environment, the large signal characterization techniques used to measure the large signal behaviour of the power transistor, including the type of RF stimulus and various load-pull measurement and calibration techniques will then be discussed. The nature of the frequency-domain simulation in harmonic balance and the frequency-domain measurement capture for load-pull characterization of power transistors allows for the ability to define behavioural models that describe the spectral scattering purely in the frequencydomain. The frequency-domain poly-harmonic distortion models that have been presented in the literature will thus be covered next. Finally a discussion of the limitations of the behavioural models of power transistors presented in the literature will motivate the model proposed in Chapter 3.

In Chapter 3, the time-domain poly-harmonic distortion model, the first contribution of this thesis will be presented. First an intuitive argument for the TD-PHD model will be presented that doesn't require much advanced mathematics but will convince the reader that the structure of the time-domain model makes sense and is indeed the most compact form the model could take to capture the nonlinear poly-harmonic dynamics of interest. Then a more sophisticated argument will be presented that presents the TD-PHD model as a natural extension of finite impulse response models to nonlinear systems, essentially viewing the TD-PHD model as a nonlinear impulse response model. Next the process to extract the TD-PHD model from multi-harmonic load-pull data and also the process of implementing the extracted model in a harmonic balance simulator will be described. Finally a measurement-based validation of the prediction of the multi-harmonic behaviour of a power transistor at a fixed DC bias and fundamental frequency of a 10W GaN power transistor is demonstrated based on a randomly generated set of active load-pull measurements. The prediction of the model for passive load-pull measurements that were not used in the training set were used as a validation for the predictive capability of the TD-PHD model for modeling the multi-harmonic load-pull measurement data.

In Chapter 4, a generalization of the models of Chapter 3 called the time-domain multi-

tone distortion (TD-MTD) models will be proposed. This generalization of the model is to account for the fact that power amplifier designers often have load-pull measurement data at multiple fundamental frequencies while the TD-PHD model as it was proposed was fixed to a single fundamental frequency, requiring the power amplifier designer to extract a distinct TD-PHD model for each fundamental frequency, even though the underlying nonlinear behaviour, as represented by the hypothetical Volterra-series description of the power transistor is constant. Through a Volterra series projection formulation, the TD-PHD model will be seen as a special case of the more general TD-MTD model that can account for a non-uniformly spaced frequency grid as the basis of the time-domain behavioural model. Finally a measurement-based validation of the TD-MTD model will be presented by first showing that a single time-domain power transistor model can fit the load-pull data extracted at multiple fundamental frequencies. Then a TD-MTD model at a class AB bias will be extracted for a Main power transistor device and another TD-MTD model at a class C bias will be extracted for a Peaking power transistor device in a Doherty power amplifier configuration. The resulting power amplifier with the two extracted nonlinear power transistor behavioural models will then be shown to model the large signal behaviour of the power amplifier comparably to how the compact model of the power transistor models the same behaviour, showing that behavioural models, particularly TD-MTD models, can be used to design power amplifiers solely based on large-signal measurements of power transistor devices.

Finally in Chapter 5 the thesis will be concluded with an overview of the main contributions of the thesis and a discussion of future directions that are motivated by the findings of this research.

## Chapter 2

# State of the Art of Nonlinear Power Transistor Modeling

In this chapter, an overview of the application of developing radio frequency (RF) power transistor models and using them to design RF power amplifiers will be presented in Section 2.1. Further, the underlying physical phenomenon that leads to the behaviour exhibited by power transistors will be explored in Section 2.2. Next, the state of the art of the varieties of power transistor models used by power amplifier designers will be discussed, starting with compact models of power transistors in Section 2.3. Another type of transistor model that will be discussed in this chapter are behavioural models of power transistor that model the characterized behaviour of the power transistor directly. The large signal characterization methods used to measure the behaviour of power transistors for the purpose of behavioural model extraction is discussed in Section 2.5. Next the most commonly used nonlinear RF behavioural model called the poly-harmonic distortion (PHD) model will be presented in Section 2.7 to motivate the power transistor behavioural models proposed in this thesis.

### 2.1 Background

Mobile wireless communication requires a wireless network that provides the mobile users of the network a way to send information via an uplink path and a way to receive information via a downlink path. In the downlink path, the base-station radio that is connected to the wider network through high-speed fibre-optical communication, transmits the downlink

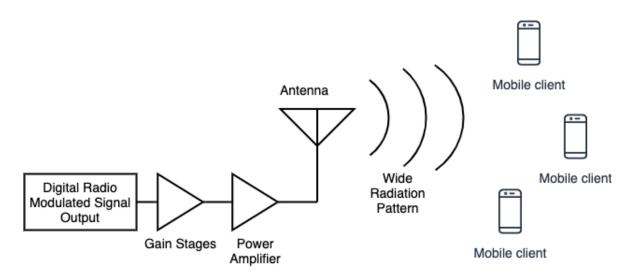

Figure 2.1: Simplified Downlink Path of a Mobile Wireless Communication Network

signal through an antenna with a wide radiation pattern in order to target the mobile users that are scattered across a wireless coverage area. In order to broadcast a downlink signal that has the information of many users over a wide region of space, the downlink broadcast antenna requires a signal of high power. To produce a high power signal from a low power digitally generated modulated signal, many amplification stages are typically required, and the final stage of amplification that boosts the power of the informationcarrying modulated signal enough to be transmitted over the antenna is called the power amplifier. Figure 2.1 shows a typical simplified diagram of the path that the downlink signal takes to get to the mobile users.

Today, existing and emerging radio standards (5G, 6G, and so on) will push the requirements of spectrum efficiency, linearity, quality of service and power efficiency, targets that are often-times in conflict with one another. The radio downlink is the part of the communication system that consumes the most amount of power and at the same time the power amplifier is the most nonlinear component in the downlink communication chain. If the nonlinearity of the power amplifier is not addressed, the spurious emissions that are generated as a result of the nonlinearity will violate the requirements enforced by spectrum regulatory bodies. Through the use of linearization techniques like Digital Pre-Distortion that can correct for the spectral regrowth of power amplifiers in adjacent bands, the design of highly power-efficient power amplifiers that are quite nonlinear in their operation becomes an attractive approach in the design of the downlink power amplifier.

This means that the circuits designed by the power amplifier designer will be designed to

be nonlinear and in fact the nonlinear operation of the circuits is used to make more efficient RF power amplifiers. Providing tools that would allow the power amplifier designer to tune the nonlinear performance of their design over frequency in a simulation environment from models of the nonlinear components of the circuit can be greatly beneficial in the circuit design progress and is indeed the goal of this research.

Since the source of nonlinearity in a power amplifier circuit are the nonlinear power transistors, the next section will discuss this nonlinear behaviour that is exhibited by the power transistor and illuminate the inherent complexity involved with modeling the behaviour of an RF power amplifier.

## 2.2 The Nonlinear Behaviour of a Packaged High Power Transistor

Power amplifier designers can use computer-aided design (CAD) tools to simulate the performance of their designs before they manufacture their circuits. To design power amplifier circuits in a simulation environment, an accurate power transistor model is required.

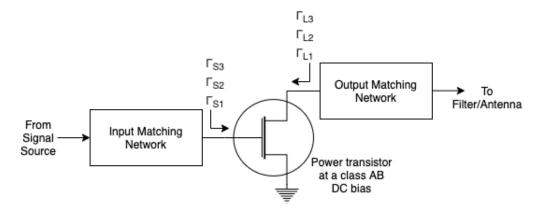

Figure 2.2: Single Transistor Power Amplifier

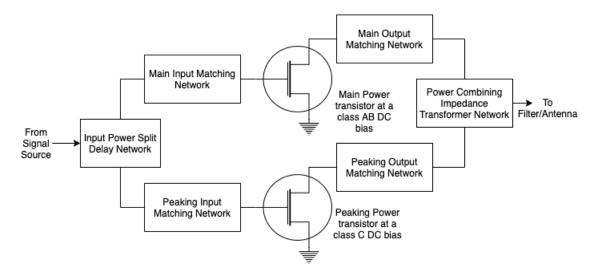

A power amplifier design can include a single power transistor like in Figure 2.2 or could have two power transistors like the two-way Doherty power amplifier structure of Figure 2.3 or have even more transistors in an N-way Doherty or other efficiency enhancement power amplifier topologies with multiple transistors like the Load Modulated Balanced Amplifier.

Figure 2.3: Two Transistor Doherty Power Amplifier

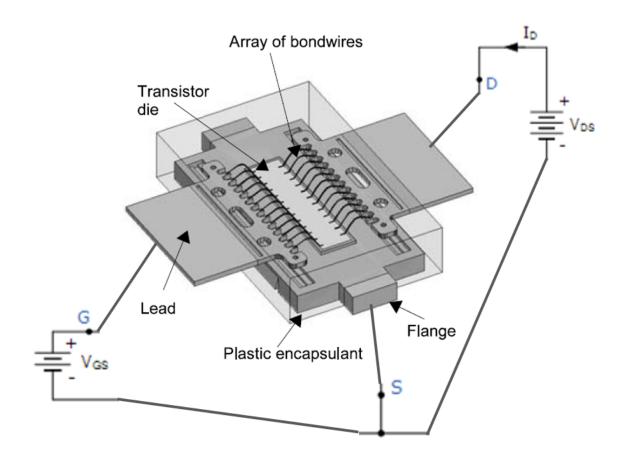

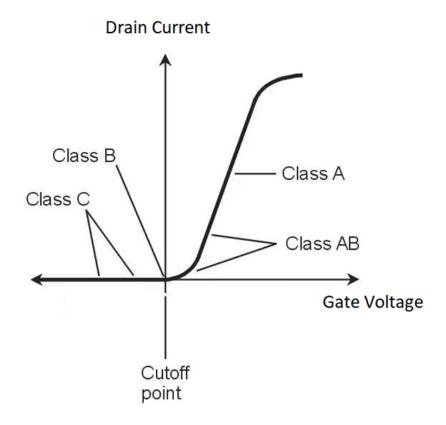

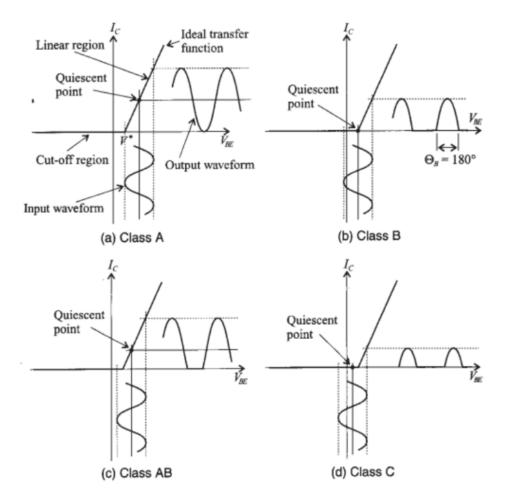

To make an amplifier, an actuated device like a transistor as shown in Figure 2.4 is biased by applying a DC gate electrical potential  $V_{GS}$  between the gate and source leads of the device and then applying the DC drain electrical potential  $V_{DS}$  between the drain and source leads of the device. Figure 2.5 shows the DC relationship between the current that flows between the drain and the source as a function of both the gate to source and the drain to source electrical potential for an ideal zero threshold voltage field effect transistor device. When the power transistor is biased in the saturation region, the output characteristic of the transistor and its drain current in particular, becomes mainly a function of the actuating gate voltage. This allows an application where low power signals incident at the gate can be effectively amplified into high power signals generated at the drain. Figure 2.6 shows the relationship between the gate to source voltage and the drain to source current for a fixed drain to source voltage. The RF signal behaviour of the power transistor is heavily dependent on where the transistor is biased on this curve. Figure 2.7 shows how the RF amplification of a power transistor changes based on its classes of operation with the example of an ideal current conduction transfer function used for a transistor, as the conduction angle of a hypothetical sinusoidal wave input is different for each case [1]. In this ideal case, the conduction angle represents the angular duration between  $0^{\circ}$  and  $360^{\circ}$ that the drain will be conducting current when the input of the transistor is incident with a sinusoidal RF signal. In each case the power transistor is biased at a different offset relative to the threshold gate voltage. While a class A bias provides the most linearity with a conduction angle of 360°, it is also the least efficient bias as it is consuming power

Figure 2.4: The DC bias of a packaged power transistor

in the entirety of the sinusoidal input voltage swing, and also when there is no RF signal being applied. A class B operation is when the transistor is biased right at gate threshold voltage of the device and will have a conduction angle of 180°, resulting in a half-sinusoidal current waveform generated at the drain of the device in the ideal case. A class AB bias is any bias in between class A and class B that may be desired due to a good trade-off between linearity and power efficiency. A class C biased device will be biased below the gate threshold voltage in the "off region" of operation. A class C biased device behaves like a passive device at small signal levels, but as the magnitude of the incident signal increases and the conduction angle of device increases, eventually the device will have more than unity power gain. This power-level dependence of a class C biased device makes it very useful in a Doherty configuration power amplifier. In a Doherty PA, the peaking (auxiliary) amplifiers are biased in class C as these transistors are meant to provide power

Figure 2.5: The DC IV characteristics of a hypothetical field effect transistor with zero threshold voltage

for the peaks of the modulated signal that is being amplified with good power efficiency, while being off and not consuming much power at backed-off power levels. The plots of the classes of operation only provide a simplistic view of how the transistor will behave as the actual shape of the DC current curves are not as ideal as the one shown in Figure 2.5 and the transistor device of Figure 2.4 has a frequency dependent response due to the many electrical parasitic behaviour from both the package and bonding manifold to the capacitance of the transistor die itself. Many power transistors have very nonlinear gate to source capacitance like in the case of Gallium Nitride High Electron Mobility Transistor (GaN HEMT) devices or have a very nonlinear drain to source capacitance like in the case of Laterally Diffused Metal Oxide Semiconductor (LDMOS) devices which further changes the nonlinear behaviour as a function of the output power level.

Figure 2.6: The DC relationship between the gate DC voltage and the drain current for a fixed DC drain voltage value

In addition to the electrical nonlinear behaviour of the power transistor, the power transistor behaviour is highly dependent on temperature. The DC drain to source current is known to drift and increase when biasing power transistors due to self-heating effects. These changes also show themselves in the large signal RF behaviour of power transistor. In addition, some GaN HEMT power transistors display significant "trapping effects" where trap states can form for the electric charge carriers due to the impurities at the semiconductor material interfaces. The time constants associated with the temperature and trapping effects are usually much slower than the electrical behaviour of the power transistor. As a result of these memory effects, more DPD resources would be required to correct for these effects and the amount of achievable correction with for a finite DPD algorithm will be limited.

Figure 2.7: The basic single transistor analog power amplifier classes of operation

One of the main tasks of RF power amplifier design is the design of the input and output matching networks at the gate and the drain of the power transistors. These matching networks present the appropriate input and output impedances to the device at the operating frequencies as well as harmonic frequencies. In the design of linear RF amplifiers, the task of designing these matching networks can be performed by extracting the linear Sparameters of the power transistor and thus using closed form solutions to find the optimal matching input and output impedances of the transistor [2]. However when the power transistor is exhibiting nonlinear behaviour then its RF performance metrics like power gain and input return loss will also need to be measured as the input power level is increased. Due to the nonlinearity of the power transistor, these RF characteristics also change when the RF load impedance changes. This is why for the nonlinear characterization of a power transistor involves large-signal load-pull measurements. In these load-pull measurements, the fundamental load impedance presented to the drain of the power transistor at the operating frequency is varied, and power sweeps of the input power are performed on the device where the DC and RF behaviour of the power transistor is completely measured at both the gate and the drain of the device. The load-pull measurements are frequency dependent, so all these load-pull measurements will need to be performed across the frequency band of interest.

Since the behaviour of the power transistor is nonlinear, due to a stimulus at the operating frequency, there will be power generated at both the gate and drain of the device at the harmonic frequencies. This means that in addition to a fundamental frequency impedance termination, the harmonic impedance terminations at both the gate and the drain of the device can have an effect on the performance. The design of the power amplifier, in the narrow-band sense, involves the design of the input and output matching networks that provide the input and output impedances at the operating frequency and its harmonic frequencies that give the desired performance. This is called the "poly-harmonic design space" at a given fundamental frequency and it is the space where the load-pull measurements will be performed.

The discussion of how the large-signal RF behaviour of a power transistor device can vary with bias, impedance terminations and frequency, brings into focus the importance of having accurate power transistor models for the simulation of power amplifier circuits.

### 2.3 Compact Models

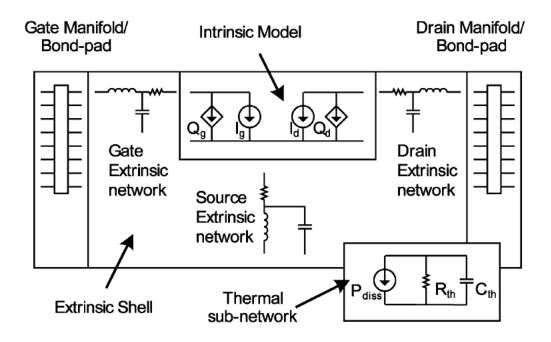

Compact models of power transistors are implicit models of their electrical behaviour. These models are formulated based on a known theory of operation of the device and are expressed as a circuit representation which includes linear and nonlinear elements. This circuit representation of the model consists of nodes that are connected by branches. Each branch of the circuit can be equivalently represented by a differential equation (e.g. the relationship of the current flowing through a capacitor and the electrical potential across the capacitor is a differential equation). Due to this basic fact, compact models are not frequency specific as they're made up of time-domain differential equations that hold for all frequencies of interest. The basic compact model topology used in the literature for packaged power transistors involves the logical separation of the package model from the inner transistor. The inner transistor is then also further sub-divided and modelled as an *active intrinsic transistor* embedded within a *passive extrinsic shell*. The underlying

Figure 2.8: Typical Compact Model Topology of a Field-Effect Transistor [3]

assumption here is that the extrinsic network is linear and non-temperature-dependent while all the nonlinearity of the device as well as thermal effects originate from the intrinsic transistor. Some models even include the trapping effects exhibited by the power transistor as part of the intrinsic transistor description [3] [4].

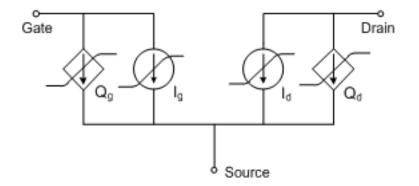

Figure 2.9 shows a simplistic nonlinear model of the intrinsic transistor used by many compact models. Here the total gate-to-source and drain-to-source current of the intrinsic transistor is represented by a current source in parallel with a charge source and described by the state equations 2.1 and 2.2 [5]:

$$I_{drain}(t) = I_d \left( V_{gs}(t), V_{ds}(t) \right) + \frac{d}{dt} Q_d \left( V_{gs}(t), V_{ds}(t) \right)$$

(2.1)

$$I_{gate}(t) = I_g \left( V_{gs}(t), V_{ds}(t) \right) + \frac{d}{dt} Q_g \left( V_{gs}(t), V_{ds}(t) \right)$$

(2.2)

The drain and gate current expressions of equations 2.1 and 2.2 are separated into a conduction current nonlinearity (nonlinear current sources  $I_d$  and  $I_g$ ) and a displacement

Figure 2.9: Intrinsic Transistor Model

current nonlinearity (nonlinear charge sources  $Q_d$  and  $Q_g$ ). Nonlinear capacitive effects that are common in many transistor devices such as LDMOS and GaN HEMTs and are represented by these displacement current nonlinear terms that can account for a general two-dimensional nonlinear capacitance.

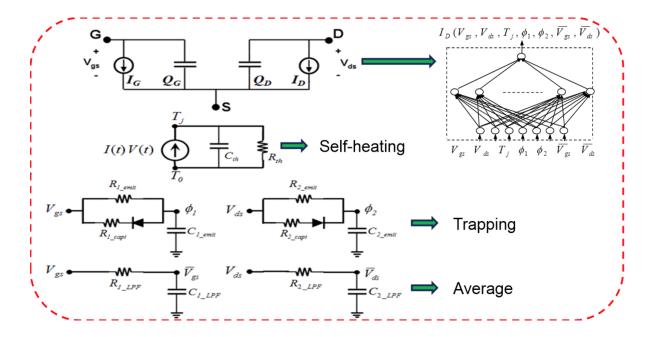

The development of compact models requires a strong insight into the actual sources of linear and nonlinear dynamics of the device. For example, the nonlinearity of a transistor device is not entirely static, meaning that having the DC input/output trans-conductance of the intrinsic transistor does not have all the information to predict the nonlinear dynamics of the transistor. This is in part due to nonlinear capacitances (capacitances that vary with the instantaneous voltage level) of devices which show up as nonlinear charge sources in the intrinsic transistor model. These nonlinear components of the intrinsic transistor can themselves be temperature dependent. A thermal sub-circuit that tracks the temperature of the transistor as a function of power dissipation is usually used in compact models to model the thermal effects of the power transistor. Some very useful compact models in the literature include the Angelov model [6][7], the Root model [8][9], and the DynaFET model [10][11]. The DynaFET model in particular is summarized in Figure 2.10 where an artificial neural network that takes a parameter input from a self-heating circuit meant to simulate the junction temperature and separate trapping circuit meant to simulate the trap states. The field of research of compact model design is active and ongoing work is being done to improve the modeling capability of compact models for the objective of RF power amplifier design [12][13][14][15][16].

A common strategy employed in the development of compact models of a power transistor, after determining a compact model topology that reflects the dynamics of the device of interest, is to experimentally extract the chosen model parameters from measurements

Figure 2.10: Form of the DynaFET compact model

that isolate the parameters of interest. For instance, for packaged transistors, the package model and the bonding manifold to the transistor die can be modelled in 3D electromagnetic simulation software, and measurements can be de-embedded through this simulated package model to get to the transistor die measurement reference plane. For compact models of the general form of Figure 2.8, the extrinsic shell is usually extracted next via a measurement that isolates the effect of the intrinsic transistor from the extrinsic shell. By doing this, the model engineer will then be able to de-embed measurements of the transistor to the intrinsic transistor in order to extract the active parameters. In order to delineate the extrinsic shell from the intrinsic transistor, a technique known as the *cold FET measurement* is often used [5]. In this technique, the active transistor is kept unstimulated by keeping the transistor in the *OFF* state and measuring its small signal response. It is assumed that the dynamics measured when the transistor is off is mainly due to the extrinsic shell. Using a frequency sweep of its two-port parameters, the extrinsic shell parameters can be optimized to match the cold FET measurements.

After determining the extrinsic shell parameters, the focus is on determining the conduction current and displacement current nonlinearities of the intrinsic transistor respectively. If the model is a electro-thermal model, these intrinsic parameters will be measured in a temperature controlled environment and will be made to be a function of temperature. In addition some new compact models also include trap state variables for the intrinsic transistor to account for the non-ideal trapping effects seen in some transistor topologies like GaN HEMT devices. Extracting the parameters for the trapping model also requires its own specialized measurements of the power transistor.

The extraction of the intrinsic parameters has been traditionally performed using pulsed DC and RF measurements. The measurement is pulsed so that the self-heating effects do not have an effect on the measured behaviour of the transistor. The gate and drain DC voltages are swept, and for each DC bias condition, a small-signal S-parameter measurement is performed to extract the bias-dependent local linear dynamics of the transistor. The DC current measurement of the intrinsic transistor at each DC voltage bias point is used to determine the conduction current nonlinearity ( $I_d$  and  $I_g$  functions of equations 2.1 and 2.2 respectively). The S-parameter measurements at each bias point are used with numerical integration (and an assumption of charge conservation of the intrinsic transistor) to find the displacement current nonlinearity terms ( $Q_d$  and  $Q_g$  of equations 2.1 and 2.2 respectively) [5]. Using this method the large signal intrinsic transistor behaviour is extracted only from bias-dependent small-signal measurements.

After numerically extracting the values of the two-dimensional nonlinear functions representing the DC conduction current nonlinearities  $I_d(V_{gs}, V_{ds})$  and  $I_g(V_{gs}, V_{ds})$ , and the displacement current nonlinearities  $Q_d(V_{gs}, V_{ds})$  and  $Q_g(V_{gs}, V_{ds})$  over a range of  $(V_{gs}, V_{ds})$ DC biases, a closed form equation can then be fit to these points or a curve-fitting tools like artificial neural networks (ANNs) is often employed.

An important point to note is that a compact model is fundamentally a time-domain model in the sense that every single component of the model, whether a circuit element or nonlinear equation describing conduction current or displacement current is described by a time-domain differential equation. The frequency behaviour of the compact model is implied by the time-domain description. It is in this sense that a compact model is not an explicit model of the frequency domain behaviour of the device. To see what frequency domain and large-signal behaviour is implied by a certain compact model, it will have to be simulated in a large-signal circuit simulator. Since the measurements that were used to extract the compact model using the common method were all small-signal measurements, resulting in a model that can imply a certain large signal behaviour, a good validation of compact models is their ability to predict the large signal behaviour of a power transistor, especially under load-pull measurements. If there is significant error between the largesignal prediction of the compact model in the large-signal simulator and the large-signal measurement of the power transistor, then the model engineer can go back and re-tune their compact model parameters to result in a simulated large-signal performance that has less error when compared to the load-pull measurements of the power transistor.

It should be noted that the extraction and development of compact models of power transistors is neither an easy task, nor can it be done with simple measurements of the power transistor. Often when power transistors are new and in development, mature compact models that accurately model the large-signal behaviour of the power transistor in a circuit simulator are not available, leaving the power amplifier designer with only load-pull measurements of the power transistor as their only design guide. This is the primary motivation for the development of behavioural models of RF power transistors. Behavioural models will fit the load-pull measurement data directly and behave in the circuit simulator exactly like how they were measured to behave in the load-pull measurement.

## 2.4 Harmonic Balance Simulation of Nonlinear Circuits

The first computer simulation tools that simulated the nonlinear behaviour circuits used time-domain methods. The time-domain simulator steps in time, and solves for the circuit behaviour for each discrete time given the behaviour at the previous time samples. When it comes to the simulation of the response of nonlinear circuits to a periodic stimulus, e.g. a sinusoidal stimulus at a fixed fundamental frequency, then the time-domain simulator would start at an initial seed (instantaneous state of the circuit) and evolve in time until the time-domain response converges to a periodic response with the same fundamental frequency as the stimulus signal. At this periodic steady-state response, the entirety of the voltage at each node of the circuit can be described by its Fourier series coefficients at DC, the fundamental frequency of the periodic response and its harmonic frequencies. Harmonic balance simulation is a frequency-domain simulation that quickly resolves to the periodic response of the circuit at these fixed discrete Fourier series frequencies [17][18].

When a nonlinear circuit Netlist is defined, the harmonic balance simulator would need to track a voltage vector of complex Fourier coefficients and at every node of the circuit and a current vector of complex Fourier coefficients for every branch of the circuit. These Fourier coefficients include the value at DC (frequency of 0) and the complex phasor at each harmonic frequency of the fundamental frequency representing the magnitude and phase of the sinusoidal component at that harmonic frequency.

It's important to note that harmonic balance simulation is a discrete frequency domain simulation, so even though the time-domain waveforms of the voltages and currents can be plotted as though they are continuous waveforms, this continuous representation is just an evaluation of the discrete terms of a Fourier series, and so the voltage and current information extracted from the simulation are fundamentally discrete. When doing a power sweep of a power transistor model in harmonic balance simulation, for each power level a separate harmonic balance simulation is performed until convergence is obtained for each power level state independently.

The poly-harmonic distortion models (that will be discussed in Section 2.6) are defined to fully take advantage of the harmonic balance simulator by having the input and output terms of the frequency domain model match up with the simulation harmonic frequencies.

The harmonic balance simulation of a compact model of a power transistor can be seen as the simulation analog of performing a frequency-domain measurement on the physical power transistor. In the next Section, the techniques used in the large-signal characterization of power transistors will be discussed.

### 2.5 Large Signal Characterization of Power Transistors

To measure the full large signal RF periodic behaviour of a power transistor device in a lab, there are different measurement techniques, based on different types of measurement instruments, namely either a Large Signal Network Analyzer (LSNA), Nonlinear Vector Network Analyzer (NVNA), or a multi-channel high-speed oscilloscope [19]. The most popular method that is used for the full-waveform periodic characterization uses an NVNA, and that's what is discussed in the next subsection.

### 2.5.1 Calibration and Measurement of a Nonlinear Vector Network Analyzer

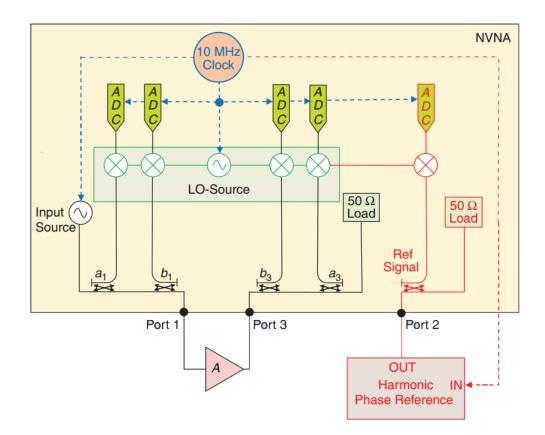

The Vector Network Analyzer (VNA) has been a ubiquitous tool in RF measurement laboratories globally as they provide a comprehensive platform for performing calibrated relative measurements between different RF receivers, allowing for the extraction of Sparameters of different linear networks. Using a common local oscillator at a specific frequency to down-convert the sampled incident and reflected waveforms down to an intermediate frequency (IF) and then sampling those IF signals using time-coherent ADCs, an VNA is able to fully capture the relative relationship between the incident and reflective waveforms at the device ports one RF frequency at a time. And since for linear systems, the characterization of the system is not a function of power, a VNA calibration and measurement does not include or need an absolute RF power calibration as all measurements and calibrations are performed relative to each other and the absolute value of the power is not known. In addition, since a VNA measures each frequency separately, if it were to measure the harmonic response of a nonlinear circuit to a fundamental frequency stimulus, it would not be able to infer the relative phase of the harmonic signal it measures relative to the fundamental frequency as the VNA can only perform cross-port relative measurements but not cross-frequency relative measurements.

The Nonlinear Vector Network Analyzer overcomes the limitations of VNAs for performing large-signal multi-harmonic periodic waveform measurements by augmenting a standard VNA with a power calibration to allow for the measurement of absolute power levels, resulting in an 8-term calibration model that can be used for load-pull measurements [20][21][22][23][24]. In addition to the power calibration, a system phase reference is measured on a separate RF receiver of the NVNA to allow for cross-frequency relative phase measurement of the waveforms. By performing a standard VNA calibration followed by a power calibration and then a phase calibration, a full NVNA calibration can be achieved that allows for the full periodic (multi-harmonic) waveform characterization of both the incident and reflected waves on each port of the device under test (DUT) [19] [25][26]. Figure 2.11 is an illustration of the NVNA system around the DUT device (shown with the letter A).

For power transistor and power amplifier measurements, pulsed-RF measurements are used since using a non-pulsed sinusoidal RF signal at the saturation power levels of a high power transistor device would result in excess heat generated by transistor device and would likely cause heat damage. When the power transistor is used to amplify a modulated signal with a high peak-to-average-power-ratio (PAPR) then instantaneously the amplifier will output RF powers close to the saturation level but since the modulated signal is at those peak powers for a short time, the self-heating at the peak power do not result in heat damage, since on average the RF output power is at a backed-off level compared to the saturation power level of the power transistors. A 10% duty cycle can allow for the characterization of the periodic response of the power transistor at its peak powers without overheating the device. Performing pulsed measurements requires some considerations on triggering of instruments used for the DC measurement during the RF-pulse and can be performed using triggered digital multimeters or current probes attached to a triggered oscilloscope.

Though a NVNA calibration and measurement instrument is a requirement for the type of power transistor characterization that is needed for model extraction, it is not sufficient as a power sweep measurement of a general RF power transistor when it is terminated

Figure 2.11: A Nonlinear Vector Network Analyzer (NVNA) measurement

with  $50\Omega$  ports does not give a full account of the its entire nonlinear behaviour and the load-impedance would need to be varied to explore the nonlinear response of the power transistor in more detail. This is the topic of the next subsection which describes the load-pull measurements of power transistors.

### 2.5.2 Load-Pull Measurements of Power Transistors

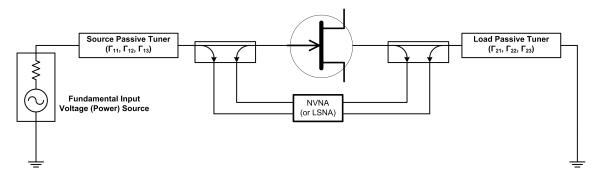

In a load-pull measurement of a power transistor, a power sweep is performed on the power transistor for different values of load impedances (or source impedances for the case of source-pull measurement). In Passive Load-pull [27], passive tuners, which are mechanical devices that can produce desired RF impedances at desired frequencies are employed for the large-signal power sweep measurement like in Figure 2.12.

Figure 2.12: A Passive Load-pull Measurement

In the example of Figure 2.12 a three-harmonic source tuner and a three-harmonic load-tuner is used and is placed outside the dual-directional couplers that are calibrated to measure the input and output waveforms at the DUT measurement reference plane. Placing these tuners outside of the couplers allows for the changing of the impedance termination seen by the power transistor without changing the required RF calibration for the measurement. The harmonic tuners allow the designer to set the input and output impedances (or equivalently the reflection coefficient) presented to the power transistor. These passive tuners require automated mechanical/RF calibrations where the tuner probes move through their positions and the S-parameters of the tuner are measured, allowing the tuner software to be able to predict what the S-parameters of the passive tuner are at every tuner position. In addition the tuner software allows them to be reconfigured mechanically to generate a requested RF impedance at a specific calibrated frequency, and in the case of multi-harmonic tuners, will also present the desired impedances to the DUT at the harmonic frequencies.

Passive tuners have the advantage of being able to operate under very high powers, making them very attractive for the load-pull measurement of high power RF transistors. The tuning capability of the passive tuner is limited to a certain maximum reflection coefficient magnitude (a reflection coefficient typically limited to around 0.9 at RF frequencies). With the imposition of the dual directional couplers in front of the passive tuners, any insertion loss from those couplers, as well as the insertion loss of the transistor fixture will will further limit the achievable RF reflection coefficient magnitude at the power transistor plane. Another drawback of passive load-pull is due to the fact that the passive tuners are mechanical devices, they are slow to re-adjust and so passive load-pull measurements are much slower than active load-pull measurements that are fully electrical and do not have any moving parts for the measurement.

In active load-pull [28][29][30], the impedance, or alternatively, the reflection coefficient

generated at the device plane is not the result of the reflection of a passive system, but the result of an active system that injects power back into the device to emulate a desired reflection coefficient. Figure 2.13 shows the basic idea behind an active load-pull system. The reflection coefficient  $\Gamma$  seen at a device port is the ratio of the incident wave (represented by a complex number a) on the port to the reflected wave from the port (represented by another complex number b). The b wave is generated by the device and can be diverted to a load to be dissipated through an RF circulator. This circulator can also be used to inject any desired a wave incident back onto the device independent of the b wave generated by the device. The active load-pull system will then try to maintain a desired reflection coefficient  $\Gamma = a/b$  by adjusting the injected a wave accordingly.

Figure 2.13: An active load-pull measurement

One of the drawbacks of using active load-pull for high power devices is that since the *a* wave has to be independently produced, to generate a high reflection coefficient  $\Gamma$ at the load of the device, the *a* wave produced must be comparable in magnitude to the high power *b* wave generated by the device, resulting in the requirement of high-power and expensive drivers in the active load-pull measurement setup. The main advantage of using active load-pull is the measurement speed, as these systems do not have any moving parts, they can measure many impedance loads rather quickly while the same number of measurements in a passive load-pull system would take thousands of times longer.

It is possible to take advantage of the benefits of both passive and active load-pull systems by employing what is referred to as a hybrid load-pull system, demonstrated by Figure 2.14.

In a hybrid load-pull measurement system, the a wave required for the generation of the desired reflection coefficient is partially generated by the reflection of a passive tuner but also has a contribution from an active load that generates the rest of the a wave presented to the device load. In this method, a high-power (expensive) driver as an active load can

Figure 2.14: A hybrid load-pull measurement

be avoided, by using a passive tuner to get the load impedance to an impedance close to the desired high reflection coefficient target, and have a local and fast active load-pull around that passive impedance. This allows one to take advantage of the speed of active load-pull while not requiring a very high power active-load driver.

An analogy to the load-pull measurement of a power transistor using RF measurement instruments also exists in the harmonic balance simulation of a power transistor model. Creating the same conditions as a load-pull measurement, that is, changing the load impedances and performing power sweep measurements, can also be performed in a simulation environment in what is known as a simulated load-pull measurement. In fact, as stated before, the only way to find out what the large-signal performance is implied by a compact model at different load impedances is to perform a simulated load-pull measurement on the power transistor model in a harmonic balance circuit simulator.

Power transistor models that are explicitly directly derived from load-pull measurements are behavioural models of power transistors and have been used in the design of RF power amplifiers [31][32][33][34]. A good methodology used in this research to evaluate the efficacy of a behavioural model before getting involved with the complexities of performing large-signal measurements on power transistors, was to use a compact model as a device under test, and to perform simulated load-pull measurements on this compact model. The extracted load-pull measurements would then be used to extract a load-pull measurement as shown in Figure 2.15.

Of course the extracted behavioural models can themselves be used as the device under

Figure 2.15: Using a Compact Model of a Power Transistor as the Device Under Test for a Simulated Load Pull Measurement

test in a load-pull simulation. Once a behavioural model is shown to at least be capable of replicating the simulated behaviour of a compact model of a power transistor, then it can at least have a chance to model the real measured behaviour of a power transistor as the behaviour of the compact model in a harmonic balance simulator can be seen as representative of how a power transistor of a par typically behave in measurements though there are differences that further necessitates the measurement validation of power transistor behavioural models.

In the next Section the poly-harmonic distortion model will be introduced as the dominant nonlinear frequency-domain behavioural modeling strategy used in the industry for RF power amplifier design.

#### 2.6 Poly-Harmonic Distortion Models