## Effect of Layer Transfer and Plasma Etching on The Behavior of Transition-Metal Dichalcogenide Field-Effect Transistor Arrays

by

Mohammad Nouri

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering (Nanotechnology)

Waterloo, Ontario, Canada, 2023

© Mohammad Nouri 2023

## **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner        | Michael Adachi                              |

|--------------------------|---------------------------------------------|

|                          | School of Engineering Science, Simon Fraser |

|                          | University                                  |

| Supervisor               | William S. Wong                             |

|                          | Dept. of Electrical & Computer Engineering  |

| Internal Member          | Chris Backhouse                             |

|                          | Dept. of Electrical & Computer Engineering  |

| Internal Member          | Youngki Yoon                                |

|                          | Dept. of Electrical & Computer Engineering  |

| Internal-external Member | Yuning Li                                   |

|                          | Dept. of Chemical Engineering               |

## Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

The application of two-dimensional (2D) layered transition metal dichalcogenide (TMDC) for highperformance large-area memory applications requires establishing long-term electrical stability through an understanding of the carrier transport and the effect of the materials processing on the device behavior. In this Ph.D. dissertation, a novel two-step approach for creating arrays of thin-film and fewlayer molybdenum disulfide (MoS<sub>2</sub>)-based field-effect transistors is developed through mechanical exfoliation and a dry etching process. Few-layer structures (~ 3 monolayers) were fabricated using a dry etching process to thin multilayer (~ 60-90 nm thick) TMDC structures. Then, the effect of plasma etching of the TFT backchannel surface and bulk defects in the layers on the electrical performance and stability of the n-channel depletion-mode TFTs were investigated. The etching improved the threshold voltage of the TFTs, resulting in a positive threshold voltage shift of +40 Volts after etching the back channel, correlating to a bulk trap density of approximately 1×10<sup>16</sup> cm<sup>-3</sup>eV<sup>-1</sup> per monolayer. Etching the  $MoS_2$  surface resulted in a threshold voltage shift of 0.2 V per nanometer of  $MoS_2$  removed (for  $MoS_2$  thicknesses >15nm). For etched  $MoS_2$  layers reduced to < 15 nm, a threshold voltage change of  $\sim$ 1.8 V per nanometer was measured. The backchannel surface was also found to be doped and roughen due to the dry etching process but did not significantly affect the device performance until the  $MoS_2$ thickness was below 15 nm. An observed degradation of the carrier transport and electrical stability of these samples were found to be due to the proximity of the etched surface approaching the active channel region of the device. The results reveal the performance tradeoffs of fabricating large-area arrays of few-layer TMDC TFTs using a mechanical exfoliation and dry etching approach.

Hydrogen-contained passivation layers were then used to mitigate the impact of the surface defects on the TFT's electrical performance. It is discovered that the diffusion of the hydrogen into the active region of the TMDC devices after the passivation process causes n-type doping, leading to a degradation in the electrical performance and stability of the devices and a negative threshold voltage shift. Furthermore, it is shown that hydrogen diffusion has a higher impact on the electrical performance of TMDC devices with thicknesses less than 15 nm due to the hydrogen diffusion length. Therefore, a hydrogen barrier layer was used to reduce the adverse effect of hydrogen-containing backchannel passivation layers and processes. This approach might be used to make hydrogen-contained passivation layers more compatible with the TMDC semiconductors for developing the next generation of TMDC-based memory devices.

Finally, dual-gate TMDC-based TFT arrays were fabricated using a bilayer dielectric on pristine and backchannel etched TMDC films. The electrical characterization shows that the dual-gate TFTs suffered due to trap states on the backchannel surface of the etched TMDC-based TFTs. The research also revealed that the effectiveness of the top-gate electric field in regulating the electrical performance and stability of dual-gate TFTs is affected by both the presence of backchannel surface traps and the distance between the top gate and the active channel region. The findings of this study demonstrate that using a dual-gate structure is a feasible method for managing and adjusting the electrical performance and stability of TMDC-based TFTs affected by backchannel surface states.

#### Acknowledgments

I am deeply grateful to everyone who has contributed to my journey throughout my Ph.D. dissertation. This accomplishment would not have been possible without their support, encouragement, and guidance.

First and foremost, I extend my heartfelt thanks to my supervisor, Professor William Wong, for his invaluable advice, mentorship, and unwavering support throughout my research. His knowledge, expertise, and dedication have been a constant source of inspiration and motivation.

I would like to express my sincere gratitude to my advisory committee, Professor Christopher James Backhouse, Professor Youngki Yoon, and Professor Yuning Li, for their insightful feedback, constructive criticism, and guidance throughout my research. Their expertise and encouragement helped me navigate through the challenges I encountered. I would also like to thank Professor Michael Adachi for accepting the role of my external Ph.D. examiner.

I also extend my gratitude to the lab managers, Richard Barber and Dr. Czang-Ho Lee, for their technical support and expertise that made my experiments possible.

I am grateful to my colleagues: Dr. Mozhgan Sadeghianlemraski. Dr. Celal Con, Dr. Mohsen Asad, Dr. Won-tae Park, Dr. Ali Tari, Hyunwoo Choi, and Pranav Gavirneni for their support, stimulating discussions, and collaboration. Their encouragement and insights have been a significant source of motivation for me.

I would like to thank my parents for their unwavering support and encouragement throughout my academic journey. Their love and support have been a constant source of strength for me.

Last but not least, I would like to express my deepest appreciation to my wife, Mozhgan. Her unwavering love, emotional, and financial support throughout my academic journey have been immeasurable. Her encouragement, sacrifices, and belief in me have been my constant source of strength, especially during challenging times.

I am deeply thankful to everyone who has played a part in my academic journey, and I am honored to have had their support and guidance along the way.

This work was performed at the Giga-to-Nanoelectronics (G2N) Centre at the University of Waterloo. The author acknowledges support from the Natural Sciences and Engineering Research Council Strategic Partnership Grant.

## Dedication

I dedicated this thesis to my love Mozhgan.

| Table of ( | Contents |

|------------|----------|

|------------|----------|

| Examining Committee Membership ii                                   |

|---------------------------------------------------------------------|

| Author's Declarationiii                                             |

| Abstractiv                                                          |

| Acknowledgments                                                     |

| Dedication                                                          |

| List of Figures                                                     |

| List of Tablesxvi                                                   |

| List of Abbreviationsxvii                                           |

| Chapter 1 Introduction1                                             |

| 1.1 Introduction1                                                   |

| 1.2 Two-dimensional materials2                                      |

| 1.3 Transition metal dichalcogenides                                |

| 1.4 MoS <sub>2</sub> properties                                     |

| 1.5 Thin-film transistors7                                          |

| 1.5.1 Materials for thin-film transistors                           |

| 1.5.2 Trap states in 2D semiconductors                              |

| 1.5.3 The electronic properties of TMDC-based thin film transistors |

| 1.5.4 Current-Voltage Relations of a TFT13                          |

| 1.5.5 Threshold voltage                                             |

| 1.5.6 Subthreshold swing17                                          |

| 1.5.7 Field effect Mobility                                         |

| 1.5.8 State-of-art TMDC Field effect transistors                    |

| Chapter 2 Challenges of developing TMDC-based devices               |

| 2.1 Introduction                                                                                                                           |               |

|--------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 2.2 TMDC synthesis                                                                                                                         | 22            |

| 2.2.1 Bottom-up method                                                                                                                     | 22            |

| 2.2.2 Top-down method                                                                                                                      | 24            |

| 2.3 TMDC thinning process                                                                                                                  | 25            |

| 2.4 TMDC/dielectric interface traps                                                                                                        | 26            |

| 2.5 TMDC bulk traps                                                                                                                        | 27            |

| 2.6 Backchannel surface traps                                                                                                              | 28            |

| 2.6.1 Backchannel surface passivation                                                                                                      | 29            |

| 2.6.2 Dual gate structure                                                                                                                  | 31            |

| 2.7 Organization of dissertation                                                                                                           | 31            |

| Chapter 3 The fabrication process of TMDC-based TFT arrays using the dissolving tag                                                        | pe method and |

| dry etching process                                                                                                                        |               |

| 3.1 Introduction                                                                                                                           | 33            |

| 3.2 Large–area TMDC exfoliation                                                                                                            | 33            |

| 3.3 MoS <sub>2</sub> device array fabrication                                                                                              | 37            |

| 3.4 Dry etching process                                                                                                                    |               |

|                                                                                                                                            | 41            |

| 3.5 Conclusion                                                                                                                             |               |

| 3.5 Conclusion<br>Chapter 4 Effect of large-area exfoliation and etching on the electrical behavior of tran                                | nsition-metal |

|                                                                                                                                            |               |

| Chapter 4 Effect of large-area exfoliation and etching on the electrical behavior of tran                                                  |               |

| Chapter 4 Effect of large-area exfoliation and etching on the electrical behavior of tran<br>dichalcogenide field-effect transistor arrays | 42            |

| Chapter 4 Effect of large-area exfoliation and etching on the electrical behavior of tran<br>dichalcogenide field-effect transistor arrays |               |

| 4.3.2 MoS <sub>2</sub> bulk thickness effect                                                     | 44      |

|--------------------------------------------------------------------------------------------------|---------|

| 4.4 Conclusion                                                                                   | 54      |

| Chapter 5 Effect of hydrogen-containing passivation layers on the electrical performance of      |         |

| transition-metal dichalcogenide field-effect transistors                                         | 55      |

| 5.1 Introduction                                                                                 | 55      |

| 5.2 Experimental                                                                                 | 56      |

| 5.2.1 Backchannel passivation process                                                            | 56      |

| 5.2.2 Chemical Analysis and Electrical Characterization                                          | 57      |

| 5.3 Results and Discussion                                                                       | 57      |

| 5.4 Conclusion                                                                                   | 65      |

| Chapter 6 Effect of backchannel surface traps on dual gating of dry-etched multilayer transition | ı metal |

| dichalcogenides TFTs                                                                             | 66      |

| 6.1 Introduction                                                                                 | 66      |

| 6.2 Experimental                                                                                 | 66      |

| 6.2.1 The top-gate TFT fabrication process                                                       | 66      |

| 6.2.2 Electrical characterization                                                                | 67      |

| 6.3 Results and Discussion                                                                       | 68      |

| 6.4 Conclusion                                                                                   | 77      |

| Chapter 7                                                                                        | 78      |

| 7.1 Conclusions                                                                                  | 78      |

| 7.2 Suggestions for Future Work:                                                                 | 79      |

| 7.3 Publications and conferences                                                                 | 80      |

| References                                                                                       | 82      |

| Appendix A Supplementary Information for Chapter 4                                               | 90      |

| Appendix B Supplementary Information for | Chapter 5 | 94 |

|------------------------------------------|-----------|----|

|                                          | -         |    |

| Appendix C Supplementary Information for | Chapter 6 | 98 |

## List of Figures

| Figure 1.2-1: contemporary 2D monolayers' physical structures. Reproduced with permission from                                      |

|-------------------------------------------------------------------------------------------------------------------------------------|

| [11]. Copyright © 2014, Nature Publishing Group                                                                                     |

| Figure 1.4-1: Schematics of structural polytypes of MoS <sub>2</sub> . Reproduced with permission from [17].                        |

| Copyright © 2012, Nature Publishing Group6                                                                                          |

| Figure 1.4-2: (a) Vibration Modes and (b) Raman Spectra of 2H-MoS <sub>2</sub> with a different number of                           |

| layers. Reproduced with permission from [17]. Copyright © 2012, Nature Publishing Group7                                            |

| Figure 1.5-1: (a) Schematic of a MoS <sub>2</sub> TFT, (b) TFT in OFF state, (c) TFT in ON state                                    |

| Figure 1.5-2: Band diagram of an n-type TFT under different conditions of gate voltage (a) No gate                                  |

| bias, (b) Negative gate bias, (c) Positive gate bias                                                                                |

| Figure 1.5-3: (a) Carrier concentration profile of TFT in the linear regime. (b) Pinch-off (c) saturation                           |

| regime14                                                                                                                            |

| Figure 2.2-1: (a) Optical micrograph of CVD growth $MoS_2$ on $SiO_2$ substrate and (b) single layer                                |

| MoS <sub>2</sub> triangle with a 123 μm grain size. Reproduced with permission from [57]. Copyright © 2013,                         |

| Nature Publishing Group                                                                                                             |

| Figure 2.2-2: (a) parent MoS <sub>2</sub> bulk material. (b) transferred MoS <sub>2</sub> films on SiO <sub>2</sub> substrate using |

| mechanical exfoliation                                                                                                              |

| Figure 3.2-1. Modified mechanical exfoliation procedure                                                                             |

| Figure 3.2-2: Optical micrograph of exfoliated MoS <sub>2</sub> flakes on a SiO <sub>2</sub> substrate, transferred by the          |

| modified method using a dissolvable adhesive. The inset shows the transferred MoS <sub>2</sub> flakes by the                        |

| conventional method                                                                                                                 |

| Figure 3.2-3: The AFM images of transferred MoS <sub>2</sub> flakes on a SiO <sub>2</sub> substrate using (a) conventional          |

| exfoliation and (b) modified exfoliation method                                                                                     |

| Figure 3.2-4: Raman spectroscopy of MoS <sub>2</sub> films with different thicknesses                                               |

| Figure 3.3-1: Optical micrograph of the $MoS_2$ TFT array with a resulting channel width of 40 $\mu$ m and                          |

| a channel length of 20 $\mu$ m for each TFT. (b) Schematic of bottom-gate MoS <sub>2</sub> TFTs38                                   |

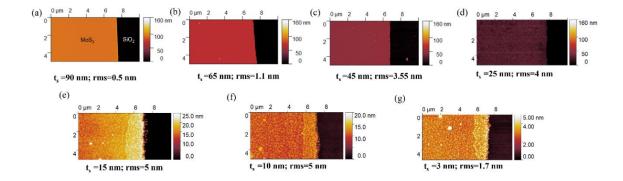

| Figure 3.4-1: Atomic force microscopy images of (a) As-transferred MoS <sub>2</sub> film. (b) to (g) are AFM                        |

| images after dry etching for 8 s, 16 s, 24 s, 26s, 28s, and 32 s, respectively. The thickness and root                              |

| mean square (rms) of the $MoS_2$ film at each step are added under each image                                                       |

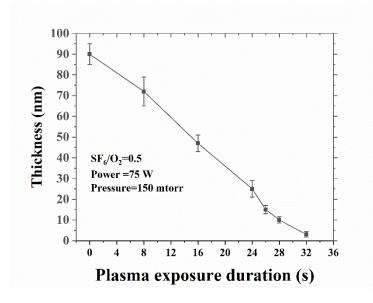

| Figure 3.4-2: Thickness variations of multiple MoS <sub>2</sub> at different plasma exposure duration40                             |

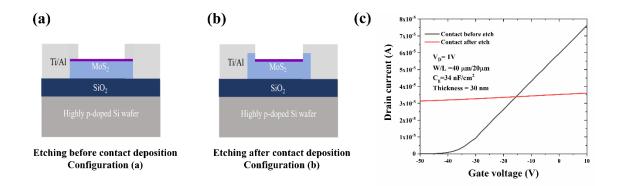

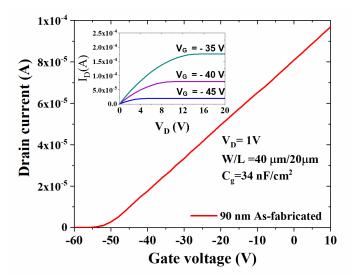

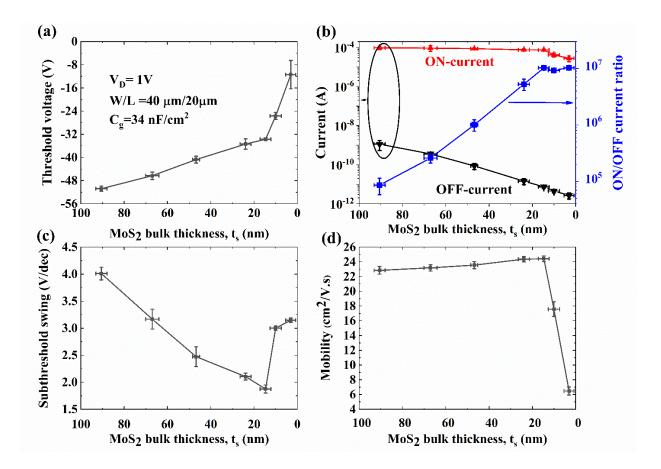

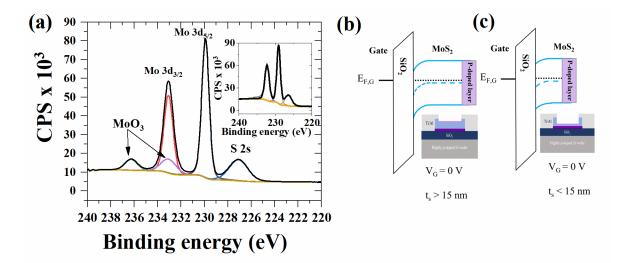

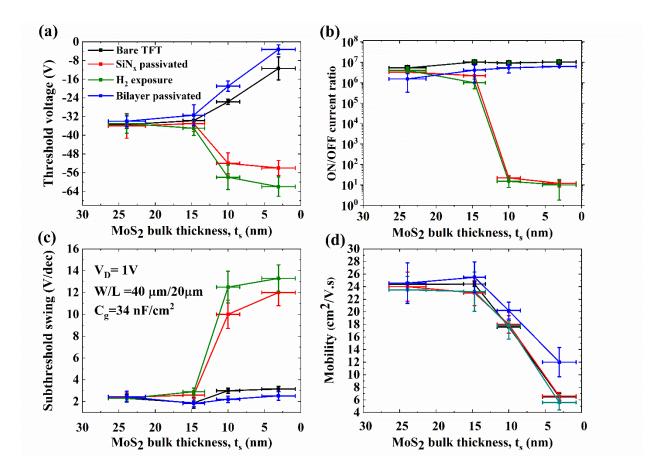

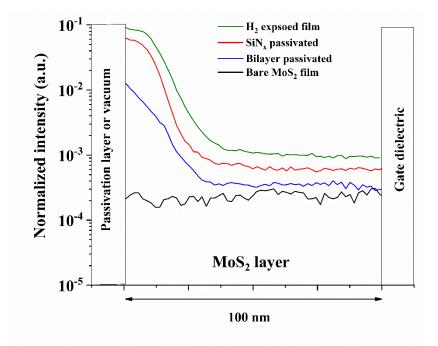

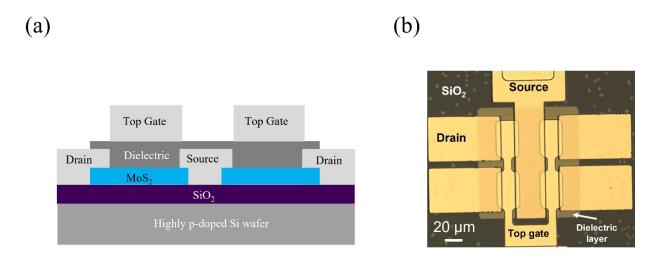

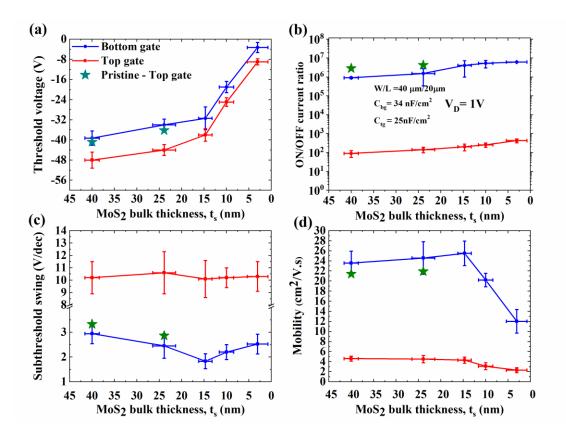

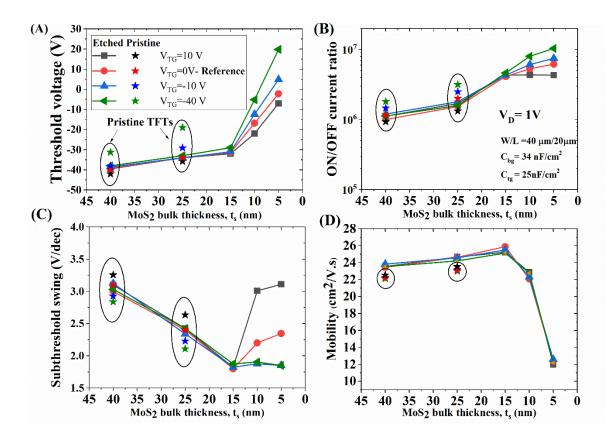

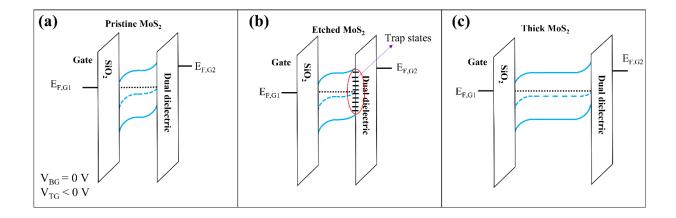

Figure 4.3-1: Cross-sectional schematic of  $MoS_2$  TFT with deposited drain and source (a) after and (b) before the plasma etching process. (c) Drain current vs. gate voltage characteristics for the TFTs. Figure 4.3-2: Drain current vs. gate voltage characteristics for a typical transferred and as-fabricated TFT with a  $MoS_2$  bulk thickness = 90 nm. The inset shows the output characteristics of the  $MoS_2$ TFT......45 Figure 4.3-3: The electrical characteristics of  $MoS_2$  TFTs are plotted for different t<sub>s</sub>. (a) the threshold voltage of MoS<sub>2</sub> TFTs as a function of semiconductor thickness, (b) TFT ON and OFF current variations vs. t<sub>s</sub>, the blue square symbols show the ON/OFF-current ratio variations, (c) the Figure 4.3-4: (a) XPS surface analysis of a dry etched MoS<sub>2</sub> film. The inset shows the XPS results of the layer of the unexposed surface. (b) and (c) show the energy band diagram and cross-section Figure 5.3-1: The electrical characteristics of  $MoS_2$  TFTs in bare condition (black curve), after passivation with 100 nm  $SiN_x$  (red curve), after exposure to H<sub>2</sub> plasma (green curve), and after passivation with SiN<sub>x</sub>/SiO<sub>x</sub> bilayer dielectric (blue curve) are plotted for different t<sub>s</sub>. (a) the threshold voltage of MoS<sub>2</sub> TFTs as a function of semiconductor thickness, (b) TFT ON/OFF-current ratio variations vs. t<sub>s</sub>, (c) the subthreshold swing vs. t<sub>s</sub>, and (d) the field-effect mobility vs. t<sub>s</sub>......59 Figure 5.3-2: Secondary ion mass spectroscopy results of a  $MoS_2$  film, (normalized to the hydrogen signal intensity), after exposing to  $H_2$  plasma (olive curve), after passivating with 100 nm SiN<sub>x</sub> (red curve), after passivating with bilayer  $SiNx/SiO_x$  (blue curve), and at bare condition (black curve). Figure 6.2-1: (a) cross-sectional schematic and (b) optical micrograph of dual-gate MoS<sub>2</sub> TFTs......67 Figure 6.3-1: The electrical characteristics of the bottom gate (blue curves), top gate (red curves), and top gate pristine (green stars)  $MoS_2$  TFTs are plotted for different t<sub>s</sub>. (a) the threshold voltage of  $MoS_2$ TFTs as a function of semiconductor thickness, (b) TFT ON/OFF-current ratio variations vs. t<sub>s</sub>, (c) the Figure 6.3-2: The electrical characteristics of the bottom gate backchannel etched (lines) and pristine (stars) MoS<sub>2</sub> TFTs with different top gate biases are plotted for different t<sub>s</sub>. (a) the threshold voltage

| of MoS <sub>2</sub> TFTs as a function of semiconductor thickness, (b) TFT ON/OFF-current ratio variations | s vs.            |

|------------------------------------------------------------------------------------------------------------|------------------|

| $t_s$ , (c) the subthreshold swing vs. $t_s$ , and (d) the field-effect mobility vs. $t_s$                 | 74               |

| Figure 6.3-3: Energy band diagram of dual gate TFTs with (a) pristine, (b) etched, and (c) thick M         | loS <sub>2</sub> |

| channels                                                                                                   | 76               |

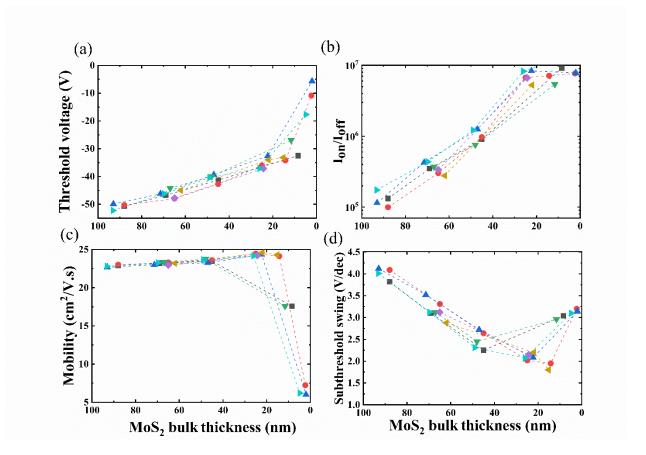

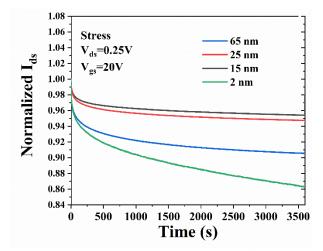

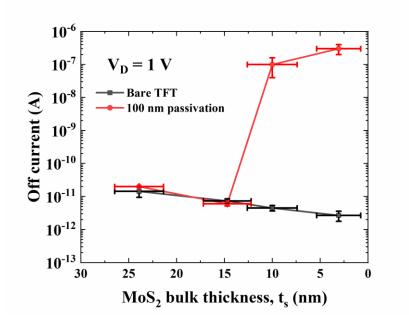

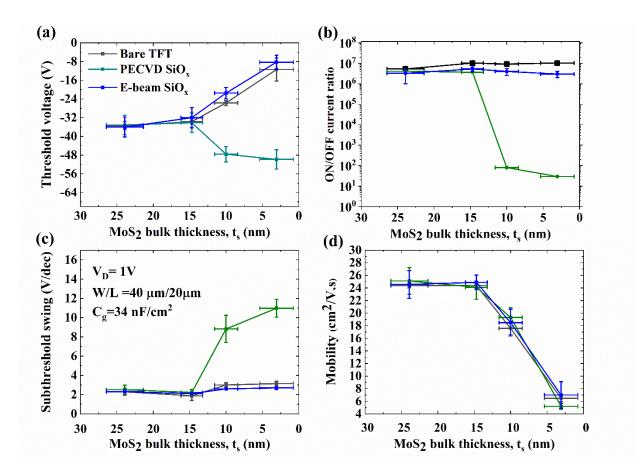

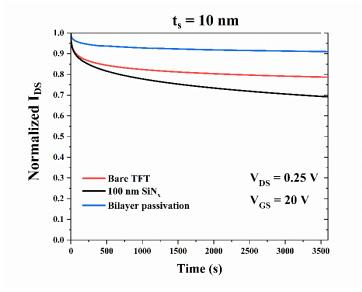

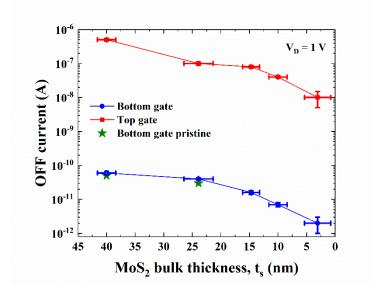

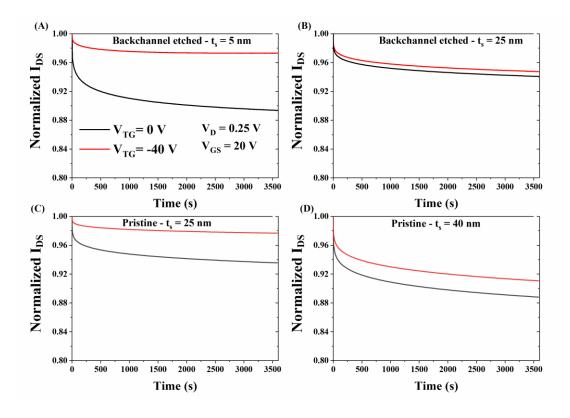

Figure S 1: Absolute parameter values of  $MoS_2$  TFTs at different  $MoS_2$  bulk thicknesses. The threshold voltage, the I<sub>on</sub>/I<sub>off</sub> ratio, the field-effect mobility, and the subthreshold swing as a function of the  $MoS_2$  bulk thickness are plotted in (a) – (d), respectively. Each symbol represented an individual TFT, and dashed lines connect their parameter variations with the  $MoS_2$  bulk thickness. 91 Figure S 4:The electrical characteristics of bare MoS<sub>2</sub> TFT (black curve), after passivation with 50 nm PECVD SiO<sub>x</sub> (green curve), and after passivation with 50 nm E-beam SiO<sub>x</sub> (blue curve) are plotted for different  $t_s$ . (a) the threshold voltage of MoS<sub>2</sub> TFTs as a function of semiconductor thickness, (b) TFT ON/OFF-current ratio variations vs.  $t_s$ , (c) the subthreshold swing vs.  $t_s$ , and (d) the Figure S 5: Electrical stability measurement of TFTs with 10 nm MoS<sub>2</sub> bulk thicknesses in different Figure S 6: OFF current of the bottom gate, top gate, and top gate pristine MoS<sub>2</sub> TFT as a function of Figure S 7: Electrical stability measurement of (A) etched dual-gate  $MoS_2$  TFT with  $t_s = 5$  nm, (B) etched dual-gate MoS<sub>2</sub> TFT with  $t_s = 25$  nm, (C) pristine dual-gate MoS<sub>2</sub> TFT with  $t_s = 25$  nm, and

## List of Tables

| Table 1: Typical features of various multilayer MoS <sub>2</sub> TFTs                             | 21    |

|---------------------------------------------------------------------------------------------------|-------|

| Table 2: Bias-stress measurement parameters at different t <sub>s</sub>                           | 93    |

| Table 3: Bias-stress measurement parameters for $t_s = 10$ nm at different backchannel conditions | 97    |

| Table 4: Bias-stress measurement parameters                                                       | . 102 |

### List of Abbreviations

| TMDC           | Transition Metal Dichalcogenide              |

|----------------|----------------------------------------------|

| 2-D            | Two-Dimensional                              |

| $D_A$          | Acceptor channel doping,                     |

| AFM            | Atomic Force Microscopy                      |

| ALD            | Atomic Layer Deposition                      |

| k <sub>B</sub> | Boltzmann constant                           |

| L              | Channel Length                               |

| W              | Channel Width                                |

| CVD            | Chemical Vapor Deposition                    |

| I-V            | Current-Voltage                              |

| $N_t$          | Density of bulk traps                        |

| $D_t$          | Density of interface traps                   |

| Cs             | Depletion region capacitance                 |

| $D_D$          | Donor channel doping,                        |

| $V_d$          | Drain Voltage                                |

| $Q_f$          | Effective charge in the depletion region     |

| $\mu_{e}$      | Effective mobility                           |

| FETs           | Field-Effect Transistors                     |

| MOSFET         | Metal-Oxide-Semiconductor Field Effect       |

| $\Phi_{ m ms}$ | Metal-semiconductor work function difference |

| ts             | MoS <sub>2</sub> bulk thickness              |

| PECVD          | Plasma-Enhanced Chemical Vapor Deposition    |

| S              | Subthreshold swing                           |

| $V_{th}$       | Threshold Voltage                            |

| Ea             | Trap activation energy                       |

| XPS            | X-ray Photoelectron Spectroscopy             |

## Chapter 1 Introduction

#### **1.1 Introduction**

CMOS technology has become well established in the semiconductor industry over the past 40 years. The industry has used Moore's Law as a reference for technological progress. According to this law, the number of transistors in a dense integrated circuit is doubled almost every two years [1]. The International Technology Roadmap for Semiconductors (ITRS) was developed to outline the next steps to reach this aggressive projection. Until today, the miniaturization of the transistor's physical dimensions to about 5 nm makes Moore's Law projection valid [2]. However, further decreasing the physical dimensions leads to so-called short-channel effects, which lower the electrical performance.

Furthermore, the devices suffer from variations in the device parameters and low reliability over time [3]. Unfortunately, Moore's Law can not be further valid with only the current established technology, design, and materials. Thus, new technologies, such as spintronics [4], single electron devices [5], and molecular computing [6], are being evaluated as solutions for the described problem. However, despite the exciting and promising applications based on these technologies, they are unlikely to provide a platform to replace the CMOS technology in the near future.

Metal-oxide-semiconductor field effect (MOSFET) technology with two-dimensional (2D) channel materials is a promising solution for sustaining the Moore's Law projection. As such, the discovery of the field effect in graphene by Novoselov et al. in 2004 triggered extensive

research in this field [7]. Gradually, different 2D materials, such as transition metal dichalcogenides (TMDCs), are introduced as potential semiconductors for realizing the next generation of field-effect transistors (FETs) [8-10]. This chapter briefly reviews transition metal dichalcogenides' structural and electrical properties. Then the device physics of TMDC-based thin film transistors is reviewed.

#### **1.2 Two-dimensional materials**

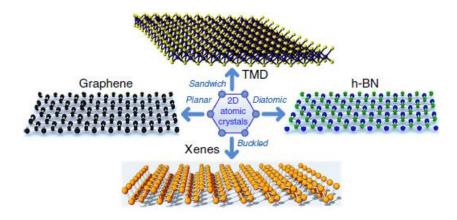

2D layered materials are a group of materials having an atomically thin, layered crystalline phase. The intralayer bonding in these materials is covalent, and the layers are held together with weak van der Waals bonding. Figure 1.2-1 shows different physical structures of 2D layered materials, including archetypical 2D crystalline graphene, transition metal dichalcogenides (TMDs), diatomic hexagonal boron nitride, and monoatomic buckled crystals known as Xenes (e.g., germanene and phosphorene). These materials are considered 2D since the crystalline solid is the thinnest form that can be created. Moreover, they have a fully terminated surface with no dangling bond and more superior intralayer charge transport than interlayer [11].

Research in the field of 2D materials grew significantly after the first demonstration of a fieldeffect graphene transistor by Andre Geim and Konstantin Novoselov in 2004 [7]. Although their pioneering mechanical exfoliation fabrication method was the first approach for processing graphene and other 2D materials, other approaches, such as chemical vapor deposition [12] and epitaxial growth [13], are also used to obtain 2D materials.

# Figure 1.2-1: contemporary 2D monolayers' physical structures. Reproduced with permission from [11]. Copyright © 2014, Nature Publishing Group.

Graphene was the first 2D material obtained by mechanical exfoliation. The lack of a band gap makes it unappealing for switching applications. Therefore, transition metal dichalcogenides attract attention due to having a tunable bandgap.

#### 1.3 Transition metal dichalcogenides

Transition metal dichalcogenides (TMDCs) are another group of 2D materials that can be thinned to a monolayer. The general formula of this group is MX<sub>2</sub>, where M is a transition metal from groups IV, V, or VI, and X is a chalcogen (S, Se, or Te). In a monolayer of TMDC, a metal layer (M) is sandwiched by two chalcogen layers (X), and these sublayers are covalently bonded together. Single layers are bonded with weak Van der Waals forces, enabling bulk exfoliation to a monolayer. Bandgaps around 1-2 eV for several members of the TMDCs group make them suitable for FET switching devices [14]. Furthermore, carrier transport in these materials relies on the number of layers. For instance, while the bandgap of bulk  $MoS_2$  is 1.3 eV and indirect, monolayer  $MoS_2$  is 1.8 eV and direct, making a monolayer  $MoS_2$  appealing for optoelectronic applications [14]. TMDCs can be utilized as electrodes such as tungsten ditelluride (WTe<sub>2</sub>), insulators such as hafnium disulfide (HfS<sub>2</sub>), and semiconductors such as molybdenum disulfide (MoS<sub>2</sub>), tungsten disulfide (WSe<sub>2</sub>) and tungsten diselenide (WSe<sub>2</sub>).

The advantages offered by 2D TMDCs over conventional 3D semiconductors like Si, Ge, and III-Vs include their ultra-thin bodies that enable superior electrostatic gate control and carrier confinement compared to bulk 3D semiconductors. This feature can be beneficial in reducing short-channel effects in ultra-scaled FETs based on 2D TMDCs, as the ultra-thin bodies of these materials can lead to a significant reduction in the characteristic channel length scaling ( $L_{CH}$ ) factor " $\lambda$ " given by:

$$\lambda = \sqrt{\frac{t_{ox}t_{body}\varepsilon_{body}}{\varepsilon_{ox}}}$$

(Equation 1-1)

, where  $t_{ox}$  and  $t_{body}$  are oxide and semiconductor thickness, respectively, and  $\varepsilon_{ox}$  and  $\varepsilon_{body}$  are their correspondence dielectric constants [15]. As channel length decreases, the gate can control a lower fraction of charge in the channel region due to the extended drain space charge region into the channel. This issue leads to short-channel effects. A straightforward formula to determine the scaling limit of FETs, which is the minimum length required to avoid short-channel effects, is that  $L_{CH}$  must be greater than three times the characteristic "channel length ( $L_{CH}$ ) scaling" factor "  $\lambda$ ." Low  $L_{CH}$  can be achieved in the 2D TMDCs due to their ultra-thin body thickness.

Additionally, 2D TMDCs have the advantage of having a broad range of sizable band gaps and various band alignments. They also lack surface "dangling bonds," a feature not found in conventional 3D semiconductors. This characteristic enables the formation of pure, defect-free interfaces compared to conventional Si-based devices. This property though also makes the TMDC materials sensitive to surface contamination and microfabrication processes that may modify the surface properties of the layers and affect the overall device performance

Among the TMDCs,  $MoS_2$  has been one of the most studied TMDCs due the natural availability as molybdenite. It possesses promising semiconducting characteristics and can enable potential applications in nanoelectronics [16]. While these properties provide a strong motivation for selecting  $MoS_2$  as the target semiconductor for this research, there are still many unknowns to how the processing of the materials affect the resulting fabricated device and its performance. In this thesis, the effect of processing of few-layer and multi-layer  $MoS_2$  structures was investigated. The thesis investigates the effect of conventional microfabrication techniques to develop a fundamental understanding of these processes on the device characteristics of TMDC-based field-effect transistors.

#### 1.4 MoS<sub>2</sub> properties

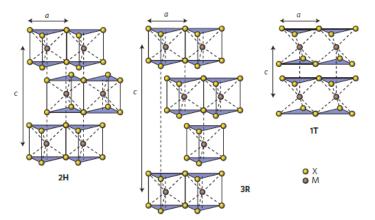

MoS<sub>2</sub> consists of a stack of planes where the hexagonal structure of closely packed molybdenum and sulfur atoms connected by covalent bonds. The MoS<sub>2</sub> planes are stacked with weak Van der Waals interactions in the range of 200 meV per unit cell [14]. Each monolayer thickness is approximately 0.65 nm. MoS<sub>2</sub> has three well-known structural polytypes: 2H (hexagonal symmetry), 1T (tetragonal symmetry), and 3R (rhombohedral symmetry). Among them, 2H-MoS<sub>2</sub> has semiconducting properties (Figure 1.4-1).

Figure 1.4-1: Schematics of structural polytypes of MoS<sub>2</sub>. Reproduced with permission from [17]. Copyright © 2012, Nature Publishing Group.

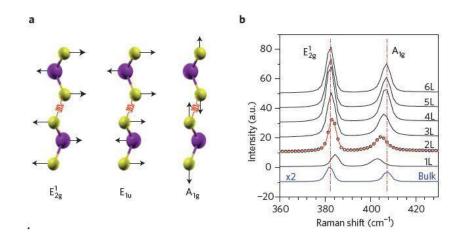

MoS<sub>2</sub> has a tunable bandgap depending on the number of layers. While a MoS<sub>2</sub> monolayer has a direct bandgap of 1.8 eV, the bulk has an indirect bandgap of 1.3 eV [9]. Thus, the number of layers determines the electrical properties of the MoS<sub>2</sub> film. In order to define the number of layers of MoS<sub>2</sub> flakes, Raman spectroscopy is used [17]. The number of layers changes the phonon vibration properties of MoS<sub>2</sub>. In the Raman spectroscopy of MoS<sub>2</sub>, out-of-plane A<sub>1g</sub>, and in-plane  $E_{2g}^{1}$  and  $E_{1u}$  modes are the key active phonon modes near the 406cm<sup>-1</sup> and 382cm<sup>-1</sup> wave numbers (Figure 1.4-2 (a)). By increasing the number of layers from mono to bulk, A<sub>1g</sub> and  $E_{2g}^{1}$  have upshift and downshift, respectively (Figure 1.4-2 (b)). The upshift of the A<sub>1g</sub> with increasing the number of layers is due to the increased effective restoring force acting on the atoms because of higher interlayer interactions. At the same time, the downshift of the  $E_{2g}^{1}$  is due to long-range Columbic interlayer interactions, which decreases the restoring forces on the atoms [18, 19].

Figure 1.4-2: (a) Vibration Modes and (b) Raman Spectra of 2H-MoS<sub>2</sub> with a different number of layers. Reproduced with permission from [17]. Copyright © 2012, Nature Publishing Group.

The monolayer has attracted attention for optoelectronics applications. At the same time, multilayer TFTs show a higher drive current originating from the multiple conduction channels and less stringent device fabrication processes, making multilayer  $MoS_2$  suitable for fabricating thin-film transistors [9]. Thus, multilayer  $MoS_2$  will be used in this research to fabricate thin film transistors (TFTs).

#### 1.5 Thin-film transistors

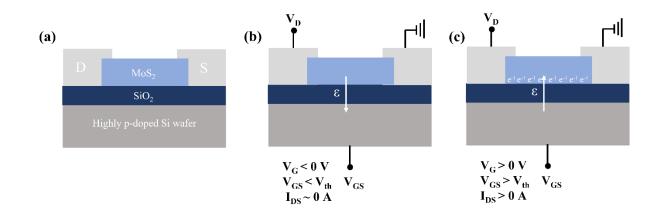

TFTs are field-effect transistors (FETs) comprising three electrodes: a drain (d), source (s), and gate (g) contact. The working principle of TFTs is similar to the MOSFET. In a TFT illustrated in Figure 1.5-1 (a), the gate electrode controls the carrier flow from the source to

the drain. The gate voltage creates a transverse electric field that has either of these effects: 1) depleting the semiconducting channel of carriers that block the current flow from source to drain (off-state), 2) or increasing the channel carrier concentration in the semiconductor to enable the flow of current (on-state) happening at gate voltages higher than the threshold voltage (Figure 1.5-1 (b), (c)). In an ideal transistor, the off-current is very small ( $I_D < 10^{-12}$ A/cm<sup>2</sup>), and the ratio between the on and off current is > 10<sup>4</sup> [20].

Figure 1.5-1: (a) Schematic of a MoS<sub>2</sub> TFT, (b) TFT in OFF state, (c) TFT in ON state.

Different materials are used as a semiconductor for fabricating thin film transistors. The following section discusses the two most prominent material systems for TFT fabrication.

#### 1.5.1 Materials for thin-film transistors

Disordered and 2D materials are two categories of materials investigated for thin-film transistor applications [17, 21]. Although both material systems have distinctive features that make them suitable for electronic applications, they differ in various ways.

Disordered materials lack long-range order in their atomic structure, such as amorphous silicon, organic semiconductors, and some metal oxides [20]. In addition, they often have high defect densities, which can lead to poor charge carrier mobility and electrical stability. In TFT applications, disordered materials are frequently used for the semiconductor because they can be deposited at low temperatures over large area, making them compatible with glass and flexible substrates. However, their low mobility and stability can constrain their performance [21].

On the other hand, 2D materials refer to single-crystal materials that comprise single or multilayers of atoms [17]. The lower defect density in the bulk of the 2D materials than in disorder materials results in a higher field effect mobility and stability. However, other trap sites, backchannel surfaces and semiconductor/dielectric interfaces, can significantly affect their electrical properties. The challenges with 2D materials are their synthesis, processing, and lack of understanding of the processing effect on the electrical properties of the TFTs. These challenges are discussed in detail in Chapter 2.

#### 1.5.2 Trap states in 2D semiconductors

Trap states in 2D semiconductors are present in various locations, including the TMDC bulk, TMDC/dielectric interface, and TMDC backchannel surface [22].

Defects, such as vacancies, dislocations, and grain boundaries, have been detected in TMDCs, regardless of the synthetic approach. The sample preparation approach defines the dominant type of defects, with sulfur vacancies being the primary type of trap in CVD-deposited and mechanically exfoliated samples [23, 24].

Bulk traps in multi-layer TMDC-based TFTs can have multiple negative effects on the electrical performance of the device. Firstly, they can make the threshold voltage ( $V_{th}$ ) a negative value, causing the TFT to operate as a depletion mode device. The threshold voltage is the gate voltage, at which the gate begins to control current flow by effectively modulating the conductivity of the semiconductor. Since bulk traps can capture and hold some charge carriers, they can change the threshold voltage [25] due to the electrostatic shielding from the occupied trap states.

Secondly, bulk trap states have the capability to seize and immobilize charge carriers present in the semiconductor substance. This entrapment diminishes the pool of available carriers for conducting, leading to a decline in the flow of current in the transistor. As time elapses, the captured carriers can be liberated, giving rise to a delayed reaction or hysteresis in the behavior of the transistor [26]. Furthermore, bulk traps can decrease the field-effect mobility ( $\mu_e$ ) of the TFT. Field-effect mobility measures the transport of charge carriers through a solid under the influence of an electric field and scattering mechanisms. When charge carriers come across trap states, they have the potential to deflect from their intended trajectory due to the presence of localized energy levels [26]. This deflection, known as scattering, hampers the mobility of the carriers, degrading the charge transport within the semiconductor. Consequently, charge transport efficiency is reduced, resulting in a decline in carrier mobility. These scattering events have a negative impact on the overall conductivity of the transistor [26]. The effect of bulk trap states on the electrical transport of TMDC-based TFTs is investigated in Chapter 4. Therefore, in TMDC-based TFTs having multiple layers, the bulk material plays an important role in the device behavior. It is important to understand how defects in the bulk affect the TFT performance and how these defect states may be minimized in multi-layer TMDC-based TFTs to enhance their electrical performance. In this research, the bulk traps are minimized by etching the TMDC bulk thickness using a dry plasma etch. This approach may lead to an improvement in the electrical performance and stability of multi-layer TMDC-based TFTs. The approach is systematically discussed in Chapter 4, showing the role of the TMDC bulk in affecting the electrical behavior of the TFT.

Traps at the semiconductor/dielectric interface capture electrons under a large positive gate bias and release them at a large negative gate bias. This trapping behavior changes the threshold voltage [25]. The cause of this effect is due to unscreened Coulomb scattering by the trapped charges at the interface [27]. On the other hand, microfabrication processes on the backchannel surface, such as dry etching, can induce traps on the surface by increasing surface roughness [28], sulfur vacancies [29], or oxidizing the surface [30]. Additionally, oxygen and water molecule adsorbates on the backchannel surface are another source of surface traps that capture electrons from the channel, resulting in an increase in the threshold voltage due to electron depletion under a large positive gate bias [25]. This issue causes a degradation in the electrical properties of TMDC-based TFTs. The following sections will explain the basics of the electronic properties of TMDC-based TFTs.

#### 1.5.3 The electronic properties of TMDC-based thin film transistors

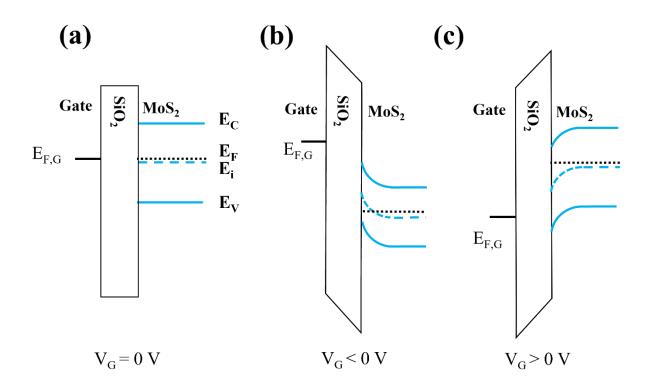

The band diagram of an n-type MoS<sub>2</sub> TFT under different applied gate voltages is depicted in Figure 1.5-2. Ideally, the band diagram is flat when the gate voltage is zero (Figure 1.5-2 (a)). A region depleted of free carriers forms by applying a negative gate bias for an n-type semiconductor. A positively charged region forms when the mobile charges are depleted, causing the conduction and valence bands to bend upward (Figure 1.5-2 (b)). During the accumulation of electrons at the gate dielectric/channel layer interface by an applied (in this case,  $V_G > 0 V$ ) gate bias, a downward (positively sloped) bending of the bands occurs (Figure 1.5-2 (c)). For the investigated MoS<sub>2</sub> TFTs, there can be two classifications for operation based on the gate voltage: a) accumulation mode and b) depletion mode devices. In the depletion mode, the devices are turned off by depleting the channel layer under negative bias. In contrast, the former devices require positive voltage to be turned on [20].

Figure 1.5-2: Band diagram of an n-type TFT under different conditions of gate voltage (a) No gate bias, (b) Negative gate bias, (c) Positive gate bias.

#### 1.5.4 Current-Voltage Relations of a TFT

In the TFTs, parameters such as the threshold voltage ( $V_{th}$ ), field-effect mobility  $\mu_e$ , ratio between ON and OFF currents, and subthreshold swing (*S*) are often extracted with equations governing the relationships between current and voltage characteristics in MOSFETs.

When  $V_d < V_g - V_{th}$ , the TFT works in linear mode, and when  $V_d > V_g - V_{th}$ , the device works in saturation mode, where  $V_d$  is the drain voltage, and  $V_g$  is the gate voltage. The gradualchannel approximation can be used to determine the linear and saturation current of TFTs:

$$I_d = \frac{W\mu_n C_g}{2L} \left[ 2 \left( V_g - V_{th} \right) V_d - V_d^2 \right] \qquad for \ 0 \le V_d \le V_d(sat)$$

(Equation 1-2)

$$I_d(sat) = \frac{W\mu_n C_g}{2L} \left( V_g - V_{th} \right)^2 \qquad for \, V_d > V_d(sat) \qquad (Equation 1-3)$$

Where  $C_g$  is the specific capacitance of the gate dielectric, W and L are the TFT channel width and length, respectively.

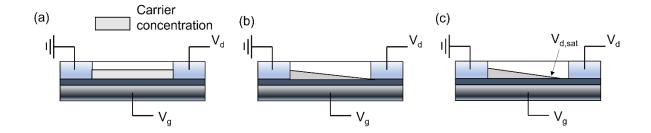

In the first equation, the squared term is negligible when  $V_d$  is low, and the device behaves like a variable resistor with the I<sub>d</sub> proportional to the  $V_d$  (Figure 1.5-3 (a)). At higher  $V_d$  values, the surrounding region of the drain becomes depleted of electrons, making a pinch-off point, and the I<sub>d</sub> does not change by increasing the  $V_d$  (Figure 1.5-3 (b)). When  $V_G-V_{th} < V_d$ , the device is in saturation mode (Figure 1.5-3 (c)). In this mode, the device is like a constant current source where the gate voltage varies with the drive current [31].

Figure 1.5-3: (a) Carrier concentration profile of TFT in the linear regime. (b) Pinch-off (c) saturation regime.

The existence of short-range order in the disorder materials enables us to use the relationships governing the I-V characteristics for single crystal materials [20]. Furthermore, it is possible to use these relationships for 2D materials due to their single crystalline properties.

#### 1.5.5 Threshold voltage

Ideally, the threshold voltage is positive for an n-channel MoS<sub>2</sub> TFT, and the device works in enhancement mode. However, the threshold voltage can be negative, and the TFT operates in the depletion mode. In this research, it is observed that the MoS<sub>2</sub> TFTs on SiO<sub>2</sub> dielectric operate in depletion mode, and the threshold voltage is a high negative value, which is not ideal for low-power applications. The negative threshold voltage might be due to the trapped charges (Q<sub>T</sub>) given by:  $Q_T \approx -qN_T t_s (E_F - E_i)$ , where  $N_t$  is the bulk trap density,  $t_s$  is the MoS<sub>2</sub> thickness, q is the electron charge, and  $E_F$  and  $E_i$  are the Fermi and the midgap energy levels, respectively. Thus, the threshold voltage can be written as:

$$V_{th} \approx \frac{q N_t t_s (E_F - E_i)_{threshold}}{C_g}$$

(Equation 1-4)

In practice, the semiconductor/dielectric interface is not ideal due to the  $MoS_2$  transferring process, which is done in the air. Thereby the threshold voltage equation can be related to the bulk and interface trap densities for thin film transistors [26]:

$$V_{th} \approx \frac{qN_t t_s (E_F - E_i)_{threshold}}{c_g} - \frac{Q_f}{c_g} + \frac{qD_t (E_F - E_i)_{threshold}}{c_g} - \frac{q(D_D - D_A)}{c_g} + \Phi_{ms}$$

(Equation 1-5)

, where  $Q_f$  is the effective charge in the depletion region,  $D_D$  and  $D_A$  are the donor and acceptor channel doping, respectively, and  $\Phi_{ms}$  is the metal-semiconductor work function difference [26]. As a result, traps inside the semiconductor bulk, interfaces, and/or doping concentration variation may lead to a negative threshold voltage, resulting in the TFT operating as a depletion mode device. In the case of multi-layer TMDC TFTs, when the TMDC thickness is higher than the maximum gate electric field screening length ( $\ell$ ), the gate cannot control the trapped charges in bulk. The maximum gate electric field screening length,  $\ell$ , is given by:

$$\ell = (\varepsilon_s / q^2 N_t)^{1/2}$$

(Equation 1-6)

, where  $\varepsilon_s$  is the MoS<sub>2</sub> dielectric constant [26]. Thus, the TFT structures in this thesis is expected to have a screening length of ~ 15 nm. This issue may lead to a high negative threshold voltage. Etching processes may be used to remove these bulk defects and improve the gate control over the trap states by thinning the film. As a result, removing these defects and TMDC bulk thinning can change the threshold voltage of the transistor. This hypothesis is investigated in Chapter 4.

Furthermore, the nature of the metal-semiconductor interface (the work function of the metal electrodes), can also affect the threshold voltage of the TFT. The work function differences between the metal and the semiconductor can induce a Schottky barrier at the interface, shifting the threshold voltage. To achieve high performance in TMDC TFTs, it is necessary to form a metal-TMDC junction with low contact resistance. Titanium is commonly used as a drain and source contact for mechanically exfoliated  $MoS_2$  flakes due to the small Schottky barrier between  $MoS_2$  and Ti (~60 meV) [32]. Thus, the research presented uses Titanium as the drain-source contact.

#### 1.5.6 Subthreshold swing

In equations 1.5-1 and 1.5-2, it is assumed that the transistor does not have a flow of charges at gate voltages lower than  $V_{th}$ . In reality, the channel may not be completely depleted. The drain current near threshold is characterized by an exponential behavior and is characterized by plotting the  $I_d$ - $V_g$  curve in a semi-log form. Extracting the inverse slope of the linear part of the semi-log curve provides the subthreshold swing (*S*). For switching applications of the TFT, having small values of *S* is preferable, meaning that the transistor can rapidly change from an Off- to an On-state by small gate voltage variations. In the case of the Si-MOSFET with an inversion layer, the theoretical subthreshold swing is given by:

$$S \equiv \frac{dV_g}{dlogI_d} \approx \frac{k_B T}{q} \left( 1 + \frac{c_S}{c_g} \right) ln 10$$

(Equation 1-7)

, where  $C_S$  is the depletion region capacitance and  $k_B$  is Boltzmann constant.

In the case of disordered materials, the interface and semiconductor bulk states also have an impact on the sub-threshold swing. Within the sub-threshold regime for a given variation in  $V_G$ , the interface and bulk trap states will capture a portion of the induced surface charge leading to the more trapped charge and reducing the concentration of free charge that results in less band bending under applied gate bias [26]. This effect changes the threshold voltage of the transistor in order to maintain the same drive current resulting in a larger *S* for the device. Accounting for the trap states, the subthreshold current [26] is given by:

$$I_D \propto \frac{k_B T}{q} \mu_e. e^{\frac{C_g V_G}{q N_T t_S k_B T}} / L$$

(Equation 1-8)

For the inverse subthreshold slope, we find:

$$\frac{1}{S} = \left(\frac{d\log_{10}I_D}{dV_G}\right) = \left(\frac{C_g}{q^2 \left(\frac{k_B T}{q}\right)(N_t t_s)}\right) \times \log_{10}e$$

(Equation 1-9)

Considering the effect of interface traps, the inverse subthreshold slope can be written as:

$$\frac{1}{S} = \left(\frac{C_g}{q^2 \left(\frac{k_B T}{q}\right)(N_t t_s + D_t)}\right) \times \log_{10} e$$

(Equation 1-10)

The  $MoS_2$  TFT subthreshold swing value has a theoretical limit of 60 mV/dec [33], but the typical value for our devices on SiO<sub>2</sub> dielectric is around 2 V/dec. This value can vary with changing trap density in the  $MoS_2$  TFT structure.

#### **1.5.7 Field effect Mobility**

Field-effect mobility measures the transport of charge carriers through a solid under the influence of an electric field and scattering mechanisms. In monolayer 2D materials, charge carriers move primarily in a 2D plane, leading to unique electronic and optical properties compared to 3D materials [17]. The field-effect mobility of TFTs can be significantly affected by the number of layers in 2D materials.

The impact of the multilayer 2D structure on field-effect mobility depends on several factors, including the number of layers, stacking order, and properties of individual layers [34]. Generally, multilayer 2D materials exhibit higher field-effect mobility than their single-layer counterparts due to increased carrier density and reduced Coulomb scattering in the multilayer structure [34]. In multilayer MoS<sub>2</sub>, varying the number of layers can tune the bandgap, interlayer interactions, and Coulomb scattering [17].

However, the impact of the multilayer structure on field-effect mobility can also depend on interface quality between layers. Defects or impurities at interfaces can act as scattering centers for charge carriers and reduce mobility [17]. Backchannel surface and semiconductor/dielectric interface traps can also significantly impact field-effect mobility. Investigating the thickness-dependent behavior of each trap site can help reveal their effects on the electrical performance. Further research is needed to fully understand these factors.

The linear or saturation regimes are used to extract the field-effect mobility  $\mu_e$ . I<sub>d</sub> can be fitted to a straight line with respect to V<sub>G</sub> in the linear regime (when V<sub>d</sub> << V<sub>d</sub> (sat)), and mobility is derived in the linear region from the slope of the line as follows:

$$\mu_e = \left[\frac{\partial I_{ds}}{\partial V_{gs}}\right] \times \left[\frac{L}{C_g V_{ds} W}\right],\tag{Equation 1-11}$$

The typical field effect mobility value for non-passivated multilayer  $MoS_2$  TFT on SiO<sub>2</sub> is reported as 22 cm<sup>2</sup>/V.s [35-37].

#### **1.5.8 State-of-art TMDC Field effect transistors**

In 2004, the first TMDC transistor was reported, which utilized WSe<sub>2</sub> as the transistor channel material [38]. This transistor displayed a mobility of up to 500 cm<sup>2</sup>/V.s, ambipolar behavior, and an on/off current ratio of  $10^4$  at a low temperature of 60 K. The first n-type MoS<sub>2</sub> transistor was introduced by Kis, *et al.* in a top-gated structure with a single layer of MoS<sub>2</sub> [8]. This transistor exhibited a significant on/off current ratio of approximately  $10^8$ , a large room-temperature mobility of 200 cm<sup>2</sup>/V.s, and a subthreshold swing of 74 mV/decade. In another study, a p-type FET with WSe<sub>2</sub> was created using a top-gate geometry with high-k dielectric

and chemically doped source/drain contacts [39]. This monolayer transistor had a hole mobility of  $250 \text{ cm}^2/\text{V.s}$ , an on/off current ratio of  $10^6$ , and a subthreshold swing of 60 mV/decade.

Recently, many advanced devices using MoS<sub>2</sub> have been explored. One of these devices used atomic-layer-deposited (ALD) high-k dielectric integration on MoS<sub>2</sub> crystals and dual-gate nchannel with ALD Al<sub>2</sub>O<sub>3</sub> as the gate dielectric [40]. This device showed high field-effect mobility of electrons. However, the commercial fabrication processes of single-layer MoS<sub>2</sub> with high-k dielectric layers are limited by their compatibility with the large-area fabrication methods. As a result, multilayer MoS<sub>2</sub> FETs have been thoroughly investigated. Table 1 shows the reported features of multilayer MoS<sub>2</sub> TFTs with SiO<sub>2</sub> dielectric. These FETs display electrical parameter dependence on the thickness of the MoS<sub>2</sub> bulk, for few layer and monolayer structures. The MoS<sub>2</sub> bulk plays an essential role in the behavior of multilayer TFTs. This topic is further investigated in Chapter 4. Studying the TFTs with different thicknesses fabricated in this thesis, with the state-of-art, shows the value of the typical features are close to the state-of-art (Chapter 4).

| Thickness<br>(nm) | Electrodes | Effective<br>mobility  | Subthreshold<br>swing (V/dec) | Threshold<br>voltage (V) | Reference |

|-------------------|------------|------------------------|-------------------------------|--------------------------|-----------|

|                   |            | (cm <sup>2</sup> /V.s) |                               |                          |           |

| 2.8               | Cr/Au      | 20                     | 1.6                           | -30                      | [37]      |

| 5                 | Ti/Au      | 13                     | 1                             | -10                      | [41]      |

| 10                | Au         | 24                     | 0.24                          | -1.3                     | [36]      |

| 15                | Cr/Au      | 20                     | 2                             | -25                      | [42]      |

| 20                | Ti/Au      | 20-30                  | -                             | -                        | [34]      |

| 32                | Ti/Ni      | 37                     | 3-4                           | -30                      | [43]      |

| 39                | Ti/Ni      | 32                     | 3-4                           | -35                      | [43]      |

| 50                | Au         | 23                     | 4                             | -40                      | [35]      |

Table 1: Typical features of various multilayer MoS<sub>2</sub> TFTs.

#### Chapter 2

#### Challenges of developing TMDC-based devices

#### 2.1 Introduction

High mobility, a low surface dangling bond, and a tunable bandgap make TMDCs interesting materials for TFT operation [8, 44]. However, the advance of the TMDC-based TFTs for different applications, such as memory devices, needs a reliable method for depositing high-quality TMDC layers and controlling their thicknesses. Furthermore, long-term stability is required for developing TMDC-based devices. This requirement is impeded by the existence of traps in the TMDC bulk, the semiconductor/dielectric interfaces, and/or the backchannel surface. A more precise understanding of the factors involved in the bias instability helps improve the two-dimensional semiconductor performance for the next generation of memory devices. This chapter will discuss common TMDC deposition methods, the TMDC thinning process, and prior investigations of the trap sources' impact on TMDC devices.

#### 2.2 TMDC synthesis

Various methods have been successfully used to synthesize TMDC, which are classified into two groups. Bottom-up methods (e.g., chemical vapor deposition (CVD)) and top-down methods (e.g., mechanical exfoliation).

#### 2.2.1 Bottom-up method

For many years, the chemical vapor deposition technique has been utilized for growing TMDC films [45-48]. Various approaches are used to deposit TMDCs from the vapor phase.

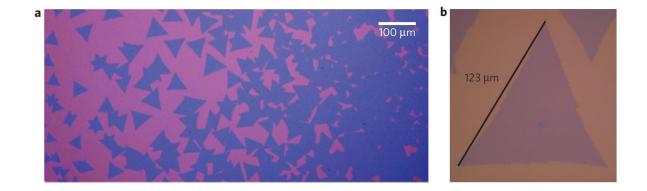

These approaches include MoO<sub>3</sub> or Mo metal sulfurization or selenization using sulfur/ selenium vapor phase [49, 50], MoS<sub>2</sub> powder direct evaporation [51], single precursor thermolysis [52], and utilizing multiple precursors e.g., H<sub>2</sub>S, MCl<sub>5</sub>, or M(CO)<sub>6</sub> [53-55]. CVD technique leads to synthesizing large-area TMDC films; however, the deposited film is polycrystalline with a smaller grain size than those made by mechanical exfoliation [56, 57] (Figure 2.2-1). Furthermore, the technique requires high temperatures (700-1000 °C) that prevent using large-area substrates such as glass [55]. In addition, this method introduces impurities, causing structural defects, wrinkles, and contaminations in the deposited films. This issue can lead to changes in the electrical properties of the TMDC film [58, 59].

Figure 2.2-1: (a) Optical micrograph of CVD growth MoS<sub>2</sub> on SiO<sub>2</sub> substrate and (b) single layer MoS<sub>2</sub> triangle with a 123 μm grain size. Reproduced with permission from [57]. Copyright © 2013, Nature Publishing Group.

#### 2.2.2 Top-down method

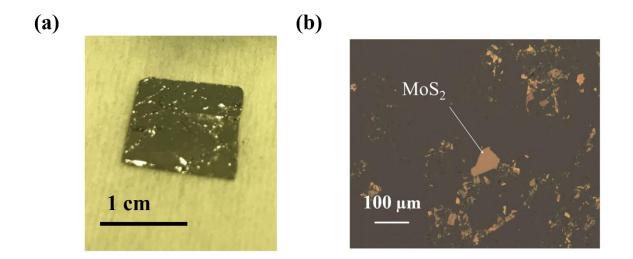

The crystal quality, purity, and grain size of TMDC films are essential for high-performance applications. Mechanical exfoliation using the scotch-tape method is the easiest and the most popular method for obtaining high-quality, thin, microscale sheets on arbitrary substrates, and it is still the best approach for studying the fundamental properties and prototyping of TMDC-based devices [60-62]. This method uses an adhesive tape to liberate a thin layer of TMDC from the parent bulk material (Figure 2.2-2 (a)). The thickness of the thin layer is further reduced by repeating the exfoliation process. Eventually, the tape with the exfoliated materials is placed on the desired substrate and subsequently peeled away (Figure 2.2-2 (b)). TMDC flakes on the target substrate can be detected using optical contrast induced by the thickness/substrate interface effects [63]. Furthermore, atomic force microscopy and Raman spectroscopy are used to characterize the transferred TMDC flakes further.

Figure 2.2-2: (a) parent MoS<sub>2</sub> bulk material. (b) transferred MoS<sub>2</sub> films on SiO<sub>2</sub> substrate using mechanical exfoliation.

Unfortunately, the mechanical exfoliation method causes defects in the TMDC semiconductor [42, 64] at the interface states between the semiconductor and gate dielectric structure [27, 65] and the backchannel surface [66-69]. Furthermore, processing the transferred TMDC flakes with this approach is difficult due to the small and discontinuous shapes, leading to different fabrication yields and unpredictable device characteristics [9, 70, 71]. Recently, some attempts have been made to increase the lateral dimensions of the transferred flakes up to  $500 \times 500 \,\mu\text{m}^2$  using additional annealing steps and intermediate materials in the exfoliation process (e.g., Au) [68, 72]; however, the TMDC flakes transferring yield in these approaches are low. In this thesis, mechanical exfoliation using a soluble tape is developed to address the problems of the conventional mechanical exfoliation method, which will be explained in Chapter 3.

#### 2.3 TMDC thinning process

In the mechanical exfoliation technique, the thickness of the flakes is not well controlled. Moreover, there is a tradeoff between the area and thickness of flakes, where thinner ones result in smaller areas. Therefore, an etching technique that reduces the thickness of the flakes without reducing their area is needed. The dry etching technique provides the ability to etch the TMDC flakes uniformly. Moreover, the etch rate is independent of the initial thickness of the flake [73-76]. Different precursor gases were reported in the literature, such as Ar, SF<sub>6</sub>/N<sub>2</sub>, Cf<sub>4</sub>, etc. [73-76]. This project used an SF<sub>6</sub>/O<sub>2</sub> dry etching process to thin the TMDC layers to achieve few-layer (3 – 4 layers) structures (Chapter 3). Exposure to the plasma may change the physical and electrical properties of the TMDC film. Huang et al. [28] show the surface

morphology of TMDC film significantly varies after the dry etching process. This variation might be due to a nonuniform reaction on the surface because of adsorbates on the surface. Furthermore, different etch rates of Mo and S in the sandwich structure of S-Mo-S might be another root cause of the nonuniform etching process on the TMDC surface [28].

Moreover, plasma exposure may lead to the incorporation of impurities in the TMDC film. Neal et al. [77] studied the effect of oxygen plasma exposure on the electrical properties of MoS<sub>2</sub> TFTs. They show after the plasma exposure, the MoS<sub>2</sub> film is doped with oxygen molecules, which leads to p-type doping and conductivity variations. Furthermore, the oxygen incorporation can create new energy states within the bandgap of MoS<sub>2</sub> and cause significant lattice distortions [78]. These new states can act as trap sites for charge carriers and reduce their mobility, which can be undesirable for some electronic applications.

The TMDC synthesis process may create trap states at the semiconductor/dielectric interface, semiconductor bulk, or at the backchannel surface. Thus, it is necessary to understand the role of each trap location in determining the electrical properties of the TFT. The following sections will review prior investigations on each trap site.

#### 2.4 TMDC/dielectric interface traps

Traps at the semiconductor/dielectric interface capture electrons under large positive gate bias and release them at large negative gate bias, causing a change in the threshold voltage [25], suggesting an unscreened Coulomb scattering by the trapped charges at the interface [27].

Illarionov et al. show the role of dielectric material on the density of TMDC/dielectric interface traps by fabricating TMDC TFTs on SiO<sub>2</sub> and hBN dielectrics. They illustrate a better electrical performance for the TFTs on hBN rises from the lower TMDC/dielectric interface trap density [65]. Furthermore, the dielectric cleaning procedure plays an important role in the TMDC/dielectric interface trap density. Shen et al. use an oxygen plasma cleaning procedure to control the density of the TMDC/dielectric interface trap [79]. The effect of TMDC/dielectric interface traps on the electrical performance is observed in TFTs with small [27, 65, 69] and large [80, 81] TMDC bulk thicknesses. These studies suggest that the TMDC bulk thickness might significantly impact electrical performance. This topic is discussed in the next section.

#### 2.5 TMDC bulk traps

Regardless of the synthesis approaches, bulk defects have been detected in TMDCs. These defects include vacancies, dislocations, and grain boundaries [22]. The sample preparation approach defines the dominant type of defects [23]; for instance, sulfur vacancy is the primary type of trap in the CVD-deposited and mechanically exfoliated samples [23, 24]. Shu et al. have investigated the effect of TMDC bulk traps on the electrical performance of multilayer TMDC-based devices. They have studied the electrical stability of dielectric supported and suspended multilayer MoS<sub>2</sub> TFTs, showing both structures have bias instability, rising from the MoS<sub>2</sub> bulk traps besides some minor impact from the backchannel surface traps [42]. It is shown that the TMDC bulk traps are filled with free carriers at a positive gate bias, causing a

decrease in conduction and a positive threshold voltage shift [25]. In another study, a multilayer  $MoS_2$  TFT was passivated with cyclized transparent optical polymer (CYTOP) to decouple the effect of backchannel surface traps [64]. The authors have shown the  $MoS_2$  bulk traps have a more dominant impact on the bias stability of the devices than the semiconductor/dielectric interface traps.

In these studies, the role of TMDC bulk traps is detected in multilayer TMDC TFTs, suggesting the TMDC thickness may play a role in bulk trap impact on the electrical performance. Kim et al. [82] have studied the effect of TMDC bulk thickness on pristine and backchannel passivated TFTs. They show that the electrical instability decreases by reducing the semiconductor thickness due to reducing the TMDC bulk trap density. In this study, the backchannel trap density was low due to utilizing thin TMDC flakes transferred with an intact and passivated backchannel surface. Therefore, the effect of backchannel surface traps was insignificant. However, different processes on the TMDC films, such as TMDC bulk thickness thinning [28, 29, 74], may introduce traps on the backchannel surface, affecting the electrical performance. The following section reviews the previous investigation on the backchannel surface traps.

#### 2.6 Backchannel surface traps

Microfabrication processes on the backchannel surface, such as dry etching, can induce traps on the backchannel surface by increasing the surface roughness [28], increasing the sulfur vacancies [29], or oxidizing the surface [30]. Furthermore, the oxygen and water molecule adsorbates on the backchannel surface are another source of the surface traps. These traps capture electrons from the channel, causing an increase in the threshold voltage due to electron depletion under a large positive gate bias. This issue causes electrical instability in the current– voltage characteristics [25]. Doherty et al. [83] have studied the electrical stability of uncapped MoS<sub>2</sub> TFTs with thicknesses ranging between 4 nm to 8 nm. After an electrical stress test, they show that the uncapped TFTs in ambient air have a substantial threshold voltage shift, significantly reduced by measuring in a vacuum chamber. These effects correlated to the backchannel surface traps due to the adsorption of oxygen and water molecules on the surface. The review of the prior investigations shows that the effect of TMDC bulk traps is mainly observed for the TMDC devices with large thicknesses. In contrast, most studies on the backchannel surface are done on mono and few-layer TMDCs. This observation suggests that TMDC bulk thickness may define the primary trapping mechanism in the device; however, this topic has not been thoroughly studied yet. Therefore, in this thesis, the effect of TMDC

bulk thickness on the electrical performance of TMDC TFTs is investigated, and the dominant trap source as a function of TMDC bulk thickness is revealed (Chapter 4). Furthermore, backchannel surface passivation can be used to reduce the effect of backchannel surface traps. This topic will be explained in the following section.

#### 2.6.1 Backchannel surface passivation

Different backchannel encapsulation layers, including poly methyl methacrylate (PMMA) [83], SU-8 photo resist [83], hexagonal boron nitride (h-BN) [65], and plasma-enhanced chemical vapor deposition (PECVD) silicon nitride ( $SiN_x$ ) [83], are used to mitigate the impact

of the backchannel surface traps on the TFT's electrical performance. SiN<sub>x</sub> is a standard passivation material for electronic devices due to its large band gap and high thermal stability [84, 85]. However, it is shown that the SiN<sub>x</sub> passivation leads to change and degradation of the electrical performance of the TMDC-based TFTs [83, 86]. A recent study ascribed the electrical performance variation to the TMDC crystal damage during the SiN<sub>x</sub> deposition [83]. At the same time, another report suggests the role of trapped charges inside the  $MoS_2$  film in changing the electrical performance of TMDC-based devices [86]. Furthermore, introducing hydrogen contamination into the active region during the passivation process is another possibility reported for PECVD SiN<sub>x</sub> coated onto the backchannel surface of TFTs with various semiconductors [87, 88]. It was shown that hydrogen atoms could physically or chemically adsorb and replace sulfur vacancy defects [89, 90] in a TMDC film. Koh et al. [91] studied the effect of hydrogen adsorption and diffusion into the TMDC layer using density functional theory. They reported that conductivity enhancement of the TMDC film through forming S-H bonding. In addition, it is shown that hydrogen plasma exposure to a monolayer TMDC film leads to the creation of trap states [89, 92], causing degradation of the electrical performance of TMDC-based devices [93]. A more precise understanding of the root cause of the electrical performance variations of TMDC TFTs after SiN<sub>x</sub> passivation will lead to overcoming the impediments of using this dielectric. Previous investigations are mainly done on mono to fewlayer TMDCs [37, 65, 83, 86, 94-96]. Furthermore, none of these studies have systematically examined more than one TMDC bulk thickness for the comparative effect of passivation on electrical performance. Thereby, the impact of the SiN<sub>x</sub> passivation process on the electrical performance of TMDC TFTs with various thicknesses is investigated in Chapter 5.

#### 2.6.2 Dual gate structure

The effect of backchannel surface traps can be minimized by proper passivation using dielectric material [36, 83, 97, 98], which can be used as a top gate dielectric for fabricating a dual-gate device. A dual gate above and below the TMDC is used to perform electrostatic modulation of contact resistance, threshold voltage, and the TMDC channel [99-102]. This device architecture has applications in logic operations [101], optoelectronic response control [103], and memory devices [101, 104]. However, the investigation of dual gate TMDC TFTs is usually done on pristine backchannel surface semiconductors; thus, the effect of backchannel surface traps on the electrical performance of dual gate TFTs is ambiguous. Furthermore, the previous reports studied the dual gate effect on few-layer TMDCs films (TMDC thickness < 10 nm) [8, 99-106]; nevertheless, the impact of TMDC thickness on dual gating of dry-etched TMDC TFTs is unclear. This topic will be studied in Chapter 6.

#### 2.7 Organization of dissertation

This Ph.D. dissertation studies the effect of the microfabrication process on the electrical performance of TMDC-based TFTs, covering the influence of large-area exfoliation of TMDC flakes, dry etching process impact on the backchannel surface, and the impact of PECVD passivation process. Finally, it describes the effect of the microfabrication process on the electrical performance of a dual gate structure electrical.

To address the introduced problems of the TMDC deposition method, a two-step mechanical exfoliation and etching approach for transferring and controlling the thickness of TMDC will be presented in Chapter 3.

In Chapter 4, the effect of the two-step mechanical exfoliation and etching approach on the electrical performance and stability of multi- and few-layer TMDC-based transistors was investigated. In this chapter, device parameters were extracted using current-voltage (I-V) and gate-bias-stress measurements to determine the effect of the process on the interface, bulk defects, and backchannel surface states on the performance of the device. PECVD SiN<sub>x</sub> was used to passivate the TMDC devices to control the impact of backchannel surface traps. In Chapter 5, the effect of PECVD SiN<sub>x</sub> passivation on TMDC TFTs with varying TMDC thicknesses was studied. This chapter explored the effect of SiN<sub>x</sub> thicknesses, hydrogen plasma exposure, dielectric deposition with an electron beam and PECVD, and incorporation of hydrogen diffusion barriers on TMDC-based transistors. Chapter 6 explores the effect of backchannel surface traps on the electrical performance of dual-gate TMDC-based TFTs using dry-etched and pristine TMDC. Bilayer SiO<sub>x</sub>/SiN<sub>x</sub> dielectric is used to fabricate the dual gate structure. Finally, Chapter 7 summarizes the contribution of this Ph.D. thesis to the 2D semiconductor field and points out suggestions for future work.

#### Chapter 3

## The fabrication process of TMDC-based TFT arrays using the dissolving tape method and dry etching process

#### 3.1 Introduction

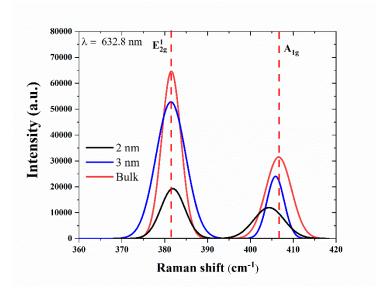

This chapter presents a two-step mechanical exfoliation and etching approach for transferring and controlling the thickness of molybdenum disulfide (MoS<sub>2</sub>) as the active semiconductor. Atomic force microscopy (AFM) was used to characterize the thickness and surface morphology of transferred MoS<sub>2</sub> flakes and extract the etch rate of the dry etching process. Raman spectroscopy was used to verify the thicknesses and quality of processed MoS<sub>2</sub> flakes by referencing the frequency difference between the  $E^{1}_{2g}$  and  $A_{1g}$  peaks to the number of MoS<sub>2</sub> layers.

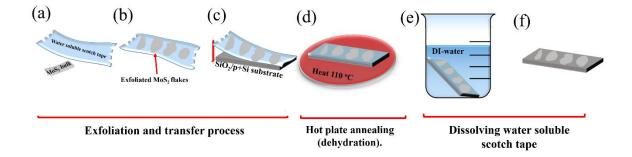

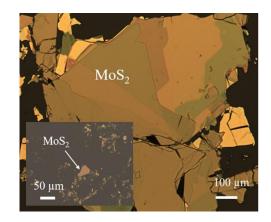

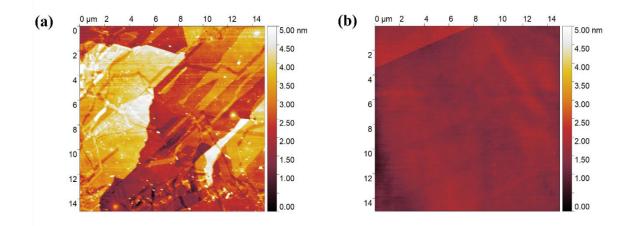

#### 3.2 Large-area TMDC exfoliation