# Real-Time FPGA-Based Testbed for Evaluating Digital Predistortion in Fully Digital MIMO Transmitters

by

Hoda Barkhordar-pour

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2023

© Hoda Barkhordar-pour 2023

### Author's Declaration

This thesis consists of material all of which I authored or co-authored: see Statement of Contributions included in the thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

### Statement of Contributions

This thesis includes material that has appeared in conference proceedings and published in IEEE MTT-S International Microwave Symposium Digest.

### Work presented in Chapter 3:

Hoda Barkhordar-pour selected the digital hardware for the testbed and designed and implemented the digital signal processing section of the testbed, which includes the PCbased server, the datapath of the signal flow on the FPGA and the radio hardware of the FPGA. Jin Gyu Lim designed, fabricated and tested the RF circuits, antenna and mechanical frame of the testbed. Mohammed Almoneer designed and simulated the SISO DPD in hardware descriptive language. Hoda Barkhordar-pour performed the experiment and compiled the results. Mohammed Almoneer drafted the manuscript. Hoda Barkhodarpour reviewed and edited the manuscript. Prof. Slim Boumaiza and Prof. Patrick Mitran reviewed and edited the manuscript and supervised the project.

### Citation:

M. Almoneer, H. Barkhordar-pour, P. Mitran and S. Boumaiza, "Hardware-efficient implementation of piece-wise digital predistorters for wideband 5G transmitters," *IEEE MTTS Int. Microw. Symp. Dig.*, 2022, pp. 514-517, doi: 10.1109/IMS37962.2022.9865388.

### Work presented in Chapter 4:

Mohammed Almoneer designed and simulated the DISO DPD in hardware descriptive language. Hoda Barkhordar-pour integrated the DISO DPD module into the FPGAbased testbed that was developed in Chapter 3. Hoda Barkhordar-pour and Jin Gyu Lim conducted the experiments, compiled the results and drafted the manuscript. Prof. Slim Boumaiza and Prof. Patrick Mitran reviewed and edited the manuscript and supervised the project.

### Citation:

H. Barkhordar-pour, J. G. Lim, M. Almoneer, P. Mitran and S. Boumaiza, "Real-time FPGA-based implementation of digital predistorters for fully digital MIMO transmitters," *IEEE MTTS Int. Microw. Symp. Dig.*, 2023. [Accepted]

#### Abstract

As one of the key enabling technologies of 5G networks, massive multiple-input, multipleoutput (MIMO) transmitters use many transmit chains to ensure a very high data rate and acceptable signal quality. Realizing Massive MIMO not only includes increasing antenna count but also requires proportionally more power amplifiers (PAs). Digital predistortion (DPD) is a well-established signal processing method that mitigates the non-linearities of a PA when operated near saturation. Design tradeoffs must be carefully considered to reduce the system's overall power requirements given the high PA count in MIMO systems. This implies DPD power consumption for each transmission chain must be minimized. Apart from this, larger transmission bandwidths in next-generation networks require high hardware clock rates on the order of a few gigahertz. Current hardware can satisfy clock rates of up to hundreds of megahertz. Thus, there is a need for parallelized signal processing methods to meet bandwidth requirements.

This thesis investigates and addresses some challenges for deploying massive MIMO systems by designing and building a reconfigurable digital signal processing (DSP) testbed that allows for the implementation and validation of real-time DSP algorithms including DPD, for fully digital massive MIMO transceivers. This testbed allows transmission of up to 16 fully digital transmission chains at sub-6 GHz frequencies and supports up to 120 MHz of modulation bandwidths. Finally, a low-complexity and parallelized piecewise-linear (PWL) dual-input dual-output (DISO) DPD solution is proposed for linearizing MIMO transmitters. This DPD solution is realized with a commercially available field-programmable-gate-array (FPGA).

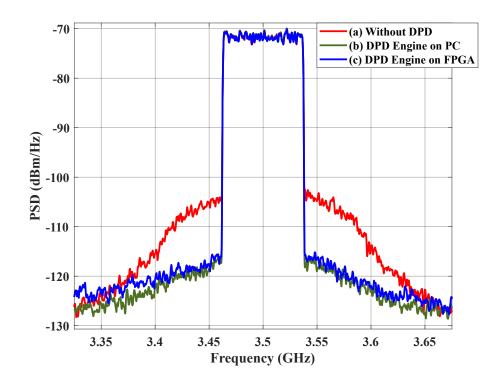

The developed 16-chain FPGA-based MIMO testbed was first evaluated for singlechain transmission and later with 4 transmission chains using a 2x2 antenna sub-array and tested with 4 uncorrelated signals with 75 MHz bandwidth inside an anechoic chamber. The proposed DPD algorithm was evaluated using both the FPGA-implemented engine and a PC-based engine. With a starting adjacent channel power ratio (ACPR) of -33.4 dB and root normalized mean square error (RNMSE) of 7.71%, the FPGA-based engine reached -47.1 dB of ACPR and achieved an RNMSE of 1.59% after linearization. The PC-based engine performed similarly, reaching ACPR of -48.3 dB and RNMSE of 1.42%. Resource utilization was reported for the DPD implementation of 4 and 8 chains. An 8-chain reduced-complexity DPD implementation uses up to 89% of the DSP slices on the FPGA.

### Acknowledgements

I would like to thank Professor Slim Boumaiza and Professor Patrick Mitran for guiding me in my research, teaching me critical thinking and providing a healthy research environment.

I thank my mother and father for bearing hardships all these years just so my sister and I would have the best education growing up. Thanks to Sepehr, for his patience and the survival kits on deadline nights. Thank you, Boshra, for the memes and laughs and for keeping me sane. I couldn't have done it without the unconditional support of my loved ones.

A big thank you to my colleagues in the EmRG group, who listened to me complain about the FPGA and gathered for laughs and discussions, about research and life. I will always cherish the memories of the first conference we attended together and I wish them all the best.

# **Table of Contents**

| Aι            | uthor | r's Declaration                                                  | ii       |

|---------------|-------|------------------------------------------------------------------|----------|

| $\mathbf{St}$ | atem  | ent of Contributions                                             | iii      |

| Al            | ostra | $\mathbf{ct}$                                                    | iv       |

| Ac            | cknov | wledgements                                                      | v        |

| Li            | st of | Figures                                                          | ix       |

| Li            | st of | Tables                                                           | cii      |

| Li            | st of | Abbreviations                                                    | iii      |

| 1             | Intr  | oduction                                                         | 1        |

|               | 1.1   | Motivation                                                       | 1        |

|               | 1.2   | Thesis Objectives                                                | 3        |

|               | 1.3   | Thesis Outline                                                   | 4        |

| <b>2</b>      | Bac   | kground and Literature Review of Hardware Implementation of Dig- |          |

|               |       | Predistortion                                                    | <b>5</b> |

|               | 2.1   | Digital Predistortion of Single Chain Transmitters               | 5        |

|               |       | 2.1.1 Single Chain Transmitter Architecture                      | 5        |

|   |     | 2.1.2                                    | Power Amplifier Non-Linear Behavior                                                       | 7  |  |  |

|---|-----|------------------------------------------|-------------------------------------------------------------------------------------------|----|--|--|

|   |     | 2.1.3                                    | Linearity Figures of Merit                                                                | 8  |  |  |

|   |     | 2.1.4                                    | Digital Predistortion for Linearizing Single Chain Transmitters                           | 11 |  |  |

|   | 2.2 | Digita                                   | al Predistortion of MIMO Transmitters                                                     | 15 |  |  |

|   |     | 2.2.1                                    | MIMO Transmitter Architecture                                                             | 15 |  |  |

|   |     | 2.2.2                                    | Impact of Antenna Crosstalk on Power Amplifier Behavior $\ . \ . \ .$                     | 17 |  |  |

|   |     | 2.2.3                                    | Dual-Input-Single-Output Digital Predistortion for MIMO Trans-<br>mitters                 | 20 |  |  |

|   | 2.3 |                                          | w of Existing DPD Hardware Implementations for Single Chain and D Transmitters            | 22 |  |  |

|   | 2.4 | Revie                                    | w of Real-time MIMO Transmitter Testbeds                                                  | 25 |  |  |

|   | 2.5 | Discus                                   | ssion                                                                                     | 27 |  |  |

| 3 |     | ns in F                                  | Testbed Development and Implementation for DSP Applica-<br>ully Digital MIMO Transmitters | 28 |  |  |

|   | 3.1 | Introd                                   | luction                                                                                   | 28 |  |  |

|   | 3.2 | Real-t                                   | time FPGA-based Testbed Requirements                                                      | 29 |  |  |

|   | 3.3 | .3 Testbed Implementation Considerations |                                                                                           |    |  |  |

|   |     | 3.3.1                                    | Server-based User Interface Design                                                        | 35 |  |  |

|   |     | 3.3.2                                    | Signal Streaming Memory                                                                   | 36 |  |  |

|   |     | 3.3.3                                    | Clock Domain Crossing                                                                     | 36 |  |  |

|   |     | 3.3.4                                    | Data Converter IP Configurations                                                          | 37 |  |  |

|   | 3.4 | SISO                                     | DPD Engine for Single-Chain Transmitters                                                  | 40 |  |  |

|   |     | 3.4.1                                    | Piecewise SISO DPD Formulation                                                            | 41 |  |  |

|   |     | 3.4.2                                    |                                                                                           | 42 |  |  |

|   |     |                                          | Hardware Implementation of SISO DPD                                                       | 14 |  |  |

|   |     | 3.4.3                                    | Hardware Implementation of SISO DPD          Validation Setup and Results                 | 44 |  |  |

| 4        | DPI           | D Imp  | lementation for MIMO Transmitters and Validation Results | <b>49</b> |  |

|----------|---------------|--------|----------------------------------------------------------|-----------|--|

|          | 4.1           | DISO   | DPD Engine for MIMO Transmitters                         | 49        |  |

|          |               | 4.1.1  | Piecewise DISO DPD Formulation                           | 50        |  |

|          |               | 4.1.2  | System Setup                                             | 51        |  |

|          |               | 4.1.3  | Validation Results                                       | 52        |  |

|          | 4.2           | Testbe | ed Comparison and Capacity Analysis                      | 55        |  |

|          |               | 4.2.1  | Testbed Comparison                                       | 55        |  |

|          |               | 4.2.2  | Capacity Analysis                                        | 55        |  |

| <b>5</b> | Con           | clusio | n and Future Work                                        | 61        |  |

|          | 5.1           | Conclu | usion                                                    | 61        |  |

|          | 5.2           | Future | e Work                                                   | 62        |  |

| Re       | References 64 |        |                                                          |           |  |

# List of Figures

| 1.1  | Conceptual wireless communication base station in 4G LTE (left) and 5G networks, which deploy MIMO technology (right).                                                      |    |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.1  | A single transmitter chain base station architecture with an ideal PA                                                                                                       | 6  |  |

| 2.2  | A single transmitter chain base station architecture including the DPD en-<br>gine and the transmitter-observation receiver feedback structure used for<br>training the DPD | 7  |  |

| 2.3  | Linearity-efficiency tradeoff in the PA. [1]                                                                                                                                | 8  |  |

| 2.4  | PA non-idealities including non-linearity and memory effect, without and with DPD                                                                                           | 10 |  |

| 2.5  | Conceptual diagram showing DPD process in complex baseband equivalent domain. The direct learning process (green) and indirect learning process (blue) are pictured         | 13 |  |

| 2.6  | A MIMO transmitter chain architecture.                                                                                                                                      | 16 |  |

| 2.7  | Beamforming structures: (a) Digital beamforming (b) Analog RF beam-<br>forming (c) Hybrid beamforming                                                                       | 18 |  |

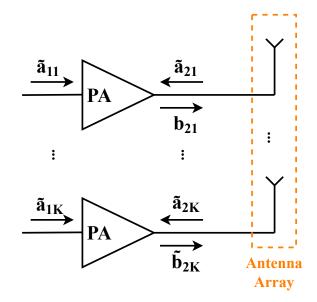

| 2.8  | Incident and reflected waves in $k$ -chain MIMO system                                                                                                                      | 19 |  |

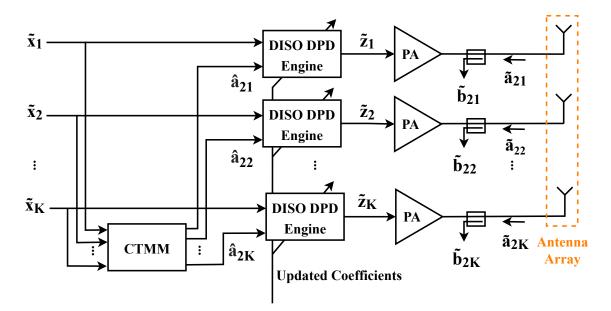

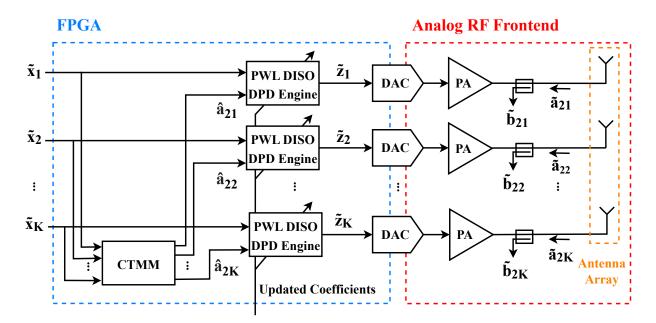

| 2.9  | Structure of the DISO DPD proposed in [2], consisting of a DISO DPD engine in each transmission chain and a shared CTMM module                                              | 21 |  |

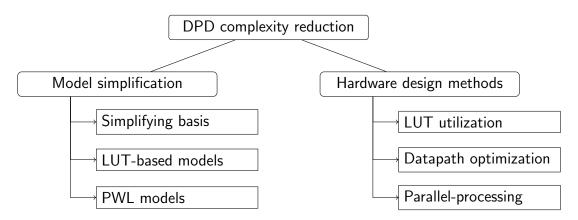

| 2.10 | Categorized prior work on complexity reduction of the predistorter                                                                                                          | 23 |  |

| 2.11 | LuMaMi of Lund University (left) and of KU Leuven (right)                                                                                                                   | 26 |  |

| 2.12 | Argos of Rice University (left) and Southeast University's testbed (right).                                                                                                 | 27 |  |

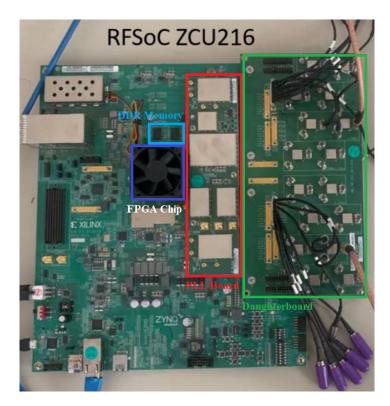

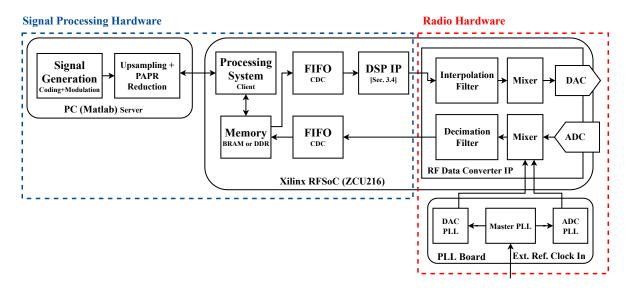

| 3.1  | The chosen hardware for the MIMO testbed, Xilinx RFSoC ZCU216 Eval-<br>uation Board with the daughterboard and PLL board attached                                                                                                                                    |    |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

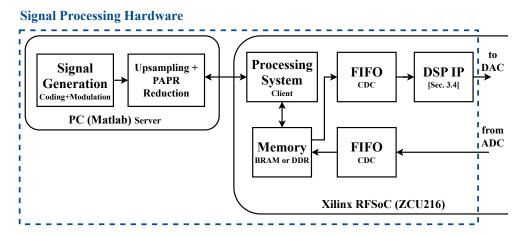

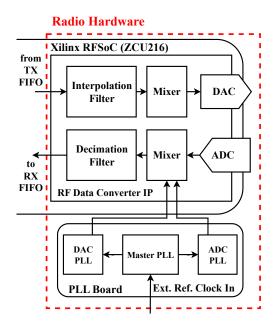

| 3.2  | Simplified diagram showing the components of the processing hardware and radio hardware. For simplicity, it is assumed that only one transceiver path is enabled, however, multiple chains are active in a MIMO system                                               |    |  |

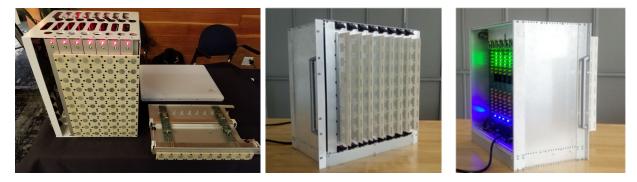

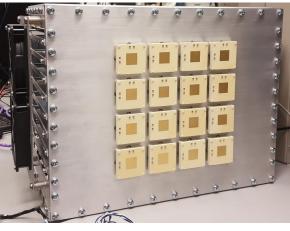

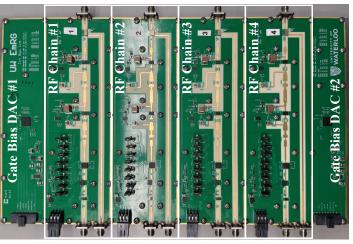

| 3.3  | EmRG 16-chain fully digital MIMO testbed                                                                                                                                                                                                                             |    |  |

| 3.4  | Block diagram showing the components of the signal processing hardware .                                                                                                                                                                                             | 35 |  |

| 3.5  | Block diagram showing the components of the radio hardware                                                                                                                                                                                                           |    |  |

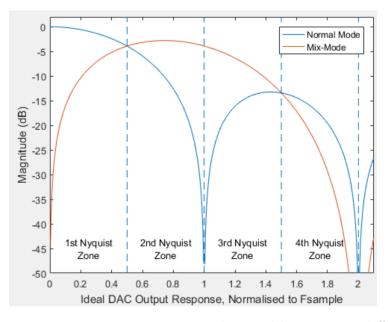

| 3.6  | Different Nyquist zone operations made possible using two different recon-<br>struction waveforms on the Xilinx RFSoC [3].                                                                                                                                           |    |  |

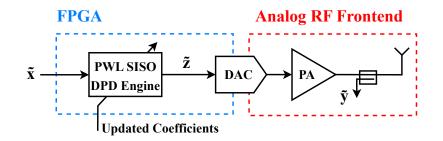

| 3.7  | Proposed real-time PWL SISO DPD, implemented in FPGA hardware                                                                                                                                                                                                        | 40 |  |

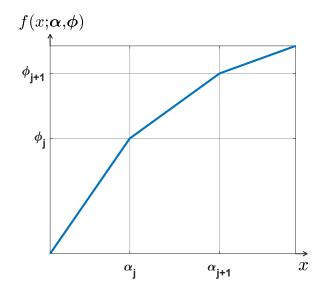

| 3.8  | Piecewise linear function $f(x; \boldsymbol{\alpha}, \boldsymbol{\phi})$                                                                                                                                                                                             | 42 |  |

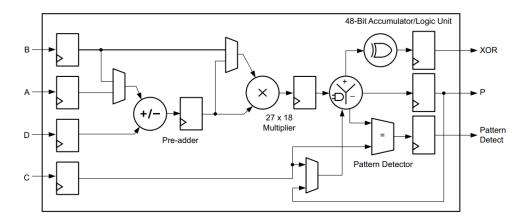

| 3.9  | DSP48E2, the DSP slices available in Ultrascale RFSoC devices [4]                                                                                                                                                                                                    | 43 |  |

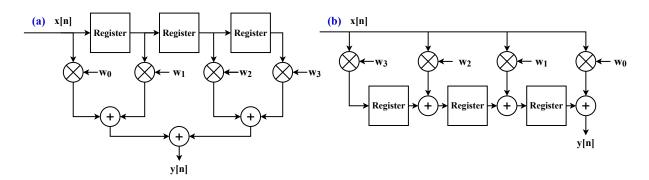

| 3.10 | Multiply-add in a (a) tree structure (b) cascade structure which optimizes<br>DSP slice resource usage                                                                                                                                                               |    |  |

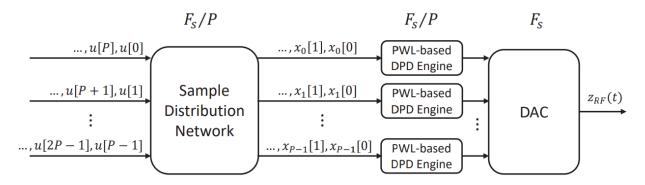

| 3.11 | Distribution and parallelization scheme used in the main DPD module that will allow sample processing at high rates [5].                                                                                                                                             | 44 |  |

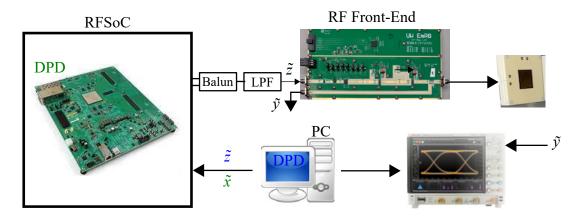

| 3.12 | Block diagram of the setup used to validate the single-chain operation of the testbed. The testbed receives the pre-distorted signal $\tilde{z}$ when PC-based DPD is tested (blue) and receives the ideal signal $\tilde{x}$ when FPGA-based DPD is tested (green). | 45 |  |

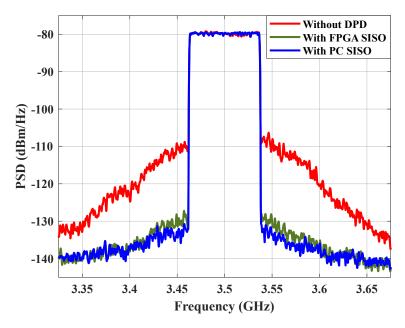

| 3.13 | Power spectral density of the observed signal $(\tilde{y})$ in single-chain operation.                                                                                                                                                                               | 46 |  |

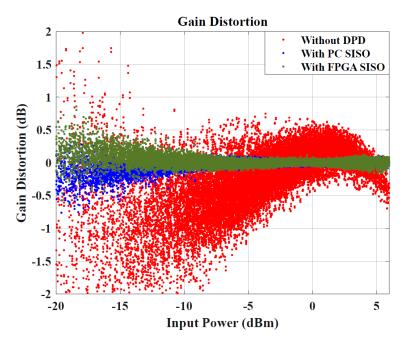

| 3.14 | Logarithmic AM/AM or gain distortion of the observed signal $(\tilde{y})$ in single-<br>chain operation.                                                                                                                                                             | 47 |  |

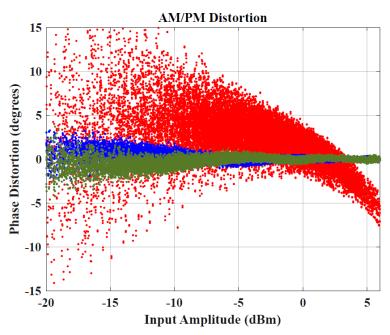

| 3.15 | AM/PM or phase distortion of the observed signal $(\tilde{y})$ in single-chain oper-<br>ation                                                                                                                                                                        | 48 |  |

| 4.1  | Proposed real-time PWL DISO DPD, implemented in FPGA hardware                                                                                                                                                                                                        | 50 |  |

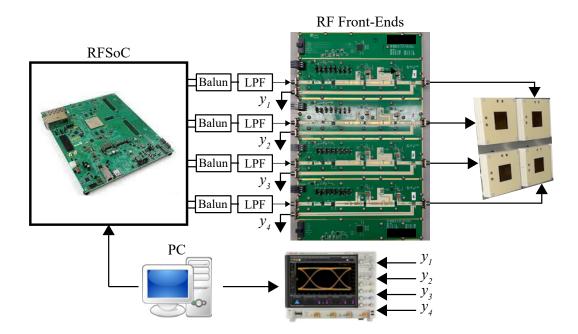

| 4.2  | Block diagram of the measurement setup                                                                                                                                                                                                                               | 52 |  |

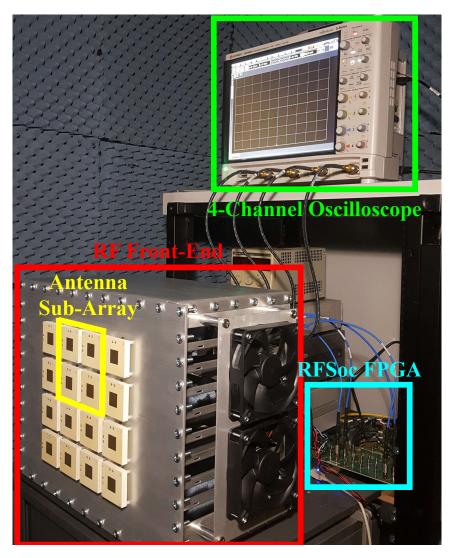

| 4.3  | Experimental fully digital massive MIMO transmitter setup including the 4-element sub-array that was used in the experiments                                                                                                                                         | 53 |  |

| 4.4 | Power spectrum comparison of (a) without DPD, (b) PC-based DPD engine,<br>and (c) FPGA-based DPD engine, at an estimated over-the-air boresight<br>receiver.                                    | 54 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

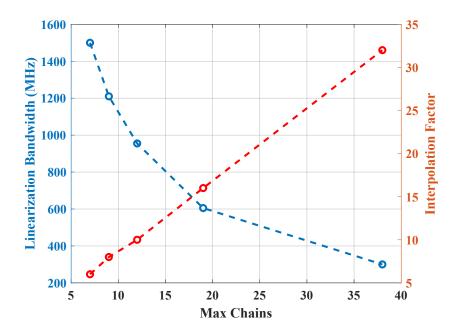

| 4.5 | Relation between the maximum number of implementable chains and maxi-<br>mum possible linearization bandwidth and its consequent interpolation fac-<br>tor for a given DPD                      | 58 |

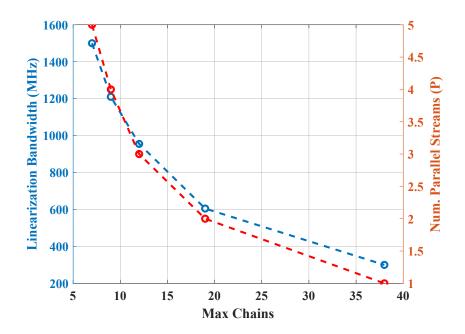

| 4.6 | Relation between the maximum number of implementable chains and max-<br>imum possible linearization bandwidth and its minimum parallel number of<br>streams $(P)$ need to implement a given DPD | 59 |

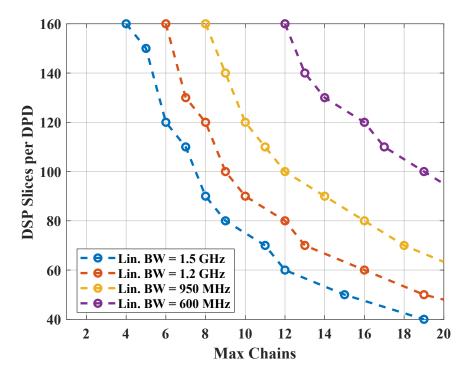

| 4.7 | Trade-off between DPD hardware complexity, linearization bandwidth and the maximum number of implementable chains.                                                                              | 60 |

# List of Tables

| 2.1 | Antenna mutual coupling quantified through ACPR levels                                                                                                            | 17 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Real-time MIMO testbed requirements                                                                                                                               | 30 |

| 3.2 | Commercial products considered to serve as the digital baseband domain of the testbed. Cells populated with 'N/A' were not declared by the manufacturing company. | 31 |

| 3.3 | Performance comparison of PC-based and FPGA-based SISO DPD engine.                                                                                                | 46 |

| 4.1 | Performance comparison of PC-based and FPGA-based DISO DPD engine<br>on the four-chain RF front-end.                                                              | 55 |

| 4.2 | FPGA Resource Utilization of Proposed DPD                                                                                                                         | 56 |

| 4.3 | MIMO testbed comparison of those in literature and the developed testbed in this thesis.                                                                          | 57 |

# List of Abbreviations

5G fifth-generation

ACPR Adjacent channel power ratio

ADC analog-to-digital converter

ASIC application-specific integrated circuit

BRAM block ram

CBBE complex baseband equivalent

CDC clock domain crossing

CRV complexity reduced Volterra

CTMM crosstalk and mismatch model

DAC digital-to-analog converter

DC direct current

DDR dynamic deviation reduction

DISO dual-input single-output

DMA data memory access

DPD digital predistortion

DSP digital signal processing

**DUT** device under test

$\mathbf{DVR}$  decomposed vector rotation

**FLOPS** floating-point operations per sample

FPGA field-programmable gate array

**GMP** general memory polynomial

${\bf GSps}\,$ Giga Samples per second

LTE long-term-evolution

LUT look-up table

MIMO multiple-input-multiple-output

**MP** memory-polynomial

MU-MIMO multi-user MIMO

${\bf NR}\,$  new radio

OOB out-of-band

$\mathbf{OTA}\xspace$  over-the-air

PA power amplifier

**PAPR** peak-to-average power ratio

**PL** programmable logic

**PLL** phase-locked loop

**PS** processing system

**PSD** power spectral density

$\mathbf{PWL}$  piece-wise linear

${\bf RF}\,$  radio frequency

- ${\bf RNMSE}$  root normalized mean square error

- ${\bf SDR}$  software-defined-radios

- ${\bf SISO}\ {\rm single-input}\ {\rm single-output}$

- ${\bf TOR}\,$  transmission-observation-receiver

- **UI** user interface

## Chapter 1

## Introduction

## 1.1 Motivation

The number of connected devices worldwide has been reported to be around 13.1 billion in 2022 and is forecast to reach 29.4 billion by the year 2030 [6]. Given this explosive growth of connected devices and the limited spectrum available, future-generation networks must allow greater network coverage and capacity while being considerate of energy consumption and overall network efficiency. As bandwidth cannot be increased indefinitely, some techniques are introduced in 4G long-term evolution (long-term-evolution (LTE)) networks and fifth-generation (5G) new radio (NR) to provide higher spectral and energy efficiency, including microcells, beamforming, full duplex communication, and multipleinput-multiple-output (MIMO).

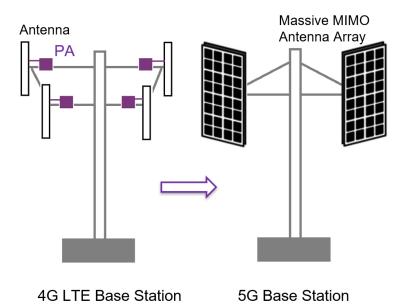

Massive MIMO is one of the key enablers of 5G, which deploys multiple antennas to increase the data throughput and system capacity (Fig. 1.1). Users utilizing MIMO can use the same time or frequency resource simultaneously for transmission. The first wireless standard to specify MIMO use was LTE in 2008 for 2 transmitting and 2 receiving antennas (2x2 MIMO). In 4G LTE networks, 4x4 MIMO became prevalent to allow higher user capacity. 5G NR networks are being deployed in higher frequencies compared to previous generation networks. The shorter wavelengths at these frequencies result in smaller radio frequency component dimensions including smaller antennas. This results in smaller MIMO design form factors and makes a 32 antenna MIMO feasible and realizable [7].

As a result of closely-spaced antennas in MIMO systems, adjacent antenna elements experience inter-antenna cross-coupling. Signals from adjacent chains couple back into

Figure 1.1: Conceptual wireless communication base station in 4G LTE (left) and 5G networks, which deploy MIMO technology (right).

each transmitter chain and affect the operation of the power amplifier (PA), giving rise to additional non-linearity in the PA. Previously, in single-chain transmitters, intrinsic PA non-linearity was able to be addressed using a comparatively simple signal processing method called digital predistortion (DPD). By using a feedback loop, DPD can correct the non-linearity (and consequent spectral regrowth) of power efficient PAs iteratively.

Compared to single-chain transmitters, in MIMO systems, the complexity of the DPD block increases, since DPD will also have to mitigate additional non-linearity due to antenna cross-coupling. Complexity-reduced hardware implementation of single-chain DPD systems has been explored. This includes look-up table (LUT)-based implementations [8, 9, 10, 11, 12, 13, 14] and exploring reduced-complexity DPD basis functions [15, 16, 9, 17, 18]. As complexity scales in MIMO systems, the methods in literature may not be optimal for MIMO DPD methods. To ensure the feasibility of deployment in MIMO systems, MIMO DPD methods must first be implemented in hardware to evaluate their performance.

Realizing massive MIMO not only includes increasing antenna count but also requires a higher number of power amplifiers. Careful consideration must be taken to reduce the power consumption of the whole system to ensure overall system efficiency. This implies signal processing power consumption, including the DPD power consumption, must be reduced for each transmission chain. Apart from this, larger transmission bandwidths in next-generation networks require high hardware processing rates in the order of at least tens of gigahertz. Current hardware can satisfy up to hundreds of megahertz. One solution to process tens of gigahertz of bandwidth using available digital hardware clock rates is to use parallel-processing schemes [19]. Thus, by developing parallel-processing digital signal processing (DSP) methods, it is possible to meet the bandwidth requirements of next-generation networks.

As MIMO technology prevails in 5G telecommunications networks, signal processing methods must be tested for viability and performance before deployment. Developing a MIMO testbed not only enables research in MIMO DSP methods but also allows exploration of the potential of MIMO technology. Some testbeds have already been developed globally [20, 21, 22, 23] but they lack the necessary bandwidth for research in hardware verification of MIMO DPD methods for MIMO base station transmitters.

## 1.2 Thesis Objectives

This thesis investigates and addresses some of the challenges of deploying massive MIMO systems by:

- Designing and building a re-configurable real-time DSP testbed that allows the implementation and validation of DSP algorithms for massive MIMO transceivers. The platform supports up to 16 chains of fully-digital signal transmission at sub-6 GHz frequencies and supports up to a maximum linearization bandwidth of 1.5 GHz.

- Proposing, implementing and testing a low-complexity and parallel-processing singlechain DPD solution and expanding the DPD to a MIMO DPD solution. The solution is verified using the developed testbed and meets signal quality standards for 5G NR transmission bandwidths.

- Providing analysis on the capacity of the developed MIMO testbed. The limited processing resources available on the testbed dictate a tradeoff between the number of transmitting chains and the DPD complexity per chain. The challenges and benefits of a distributed processor for MIMO transmitters are discussed.

## 1.3 Thesis Outline

This thesis is organized as follows. First, in Chapter 2, background theory is discussed regarding DPD techniques for linearizing power amplifiers in single-chain transmitters and MIMO transmitters respectively. In the same chapter, a literature review is presented on DPD hardware implementation methods that reduce implementation complexity and power consumption of the DPD unit. Finally, a review of MIMO systems that were developed for research purposes is presented.

Chapter 3 presents the process of designing and developing the MIMO testbed. Testbed requirements are clarified and design choices that satisfy these requirements are described. Next, some key design challenges and their respective solutions are presented. Finally, to verify the single-chain transmission performance of the testbed, a low complexity, power efficient and parallel processing DPD engine architecture is proposed for single-chain transmitters. This real-time DPD architecture is implemented on the mentioned reconfigurable testbed. The DPD achieves a linearization bandwidth of 1.2 GHz with a digital hardware clock rate of 300 MHz.

In Chapter 4, the single-chain DPD engine is augmented to compensate antenna crosstalk in MIMO transmitters and is presented as the dual-input-single-output DPD. This DPD engine is implemented on the testbed and tested on a 4-chain MIMO system that was designed and built in the lab. Measurement results are presented. To conclude Chapter 4, a brief analysis of the capacity and DPD complexity tradeoff of the MIMO testbed is illustrated. Finally, a summary and conclusion of this thesis are presented in Chapter 5. Potential future works that can result from the work done in this thesis are also discussed in this chapter.

## Chapter 2

# Background and Literature Review of Hardware Implementation of Digital Predistortion

This chapter reviews the relevant background and literature needed to develop a MIMO testbed and implement a low-complexity wideband DPD solution in hardware for MIMO systems. DPD is a signal processing method that compensates for PA non-linearity such that the cascade of the DPD block with the PA results in a linear power amplifying module. In order to understand the scope of the complexity of a MIMO DPD block, this chapter first reviews single-chain DPD in Section 2.1 before addressing MIMO systems in Section 2.2. Previous literature has proposed a variety of techniques to simplify the DPD engine's structure, albeit for a single transmitter chain. These methods are reviewed in Section 2.3. Finally, this chapter reviews all known developed MIMO testbeds as the baseline that will be used to compare the developed testbed in this thesis.

## 2.1 Digital Predistortion of Single Chain Transmitters

### 2.1.1 Single Chain Transmitter Architecture

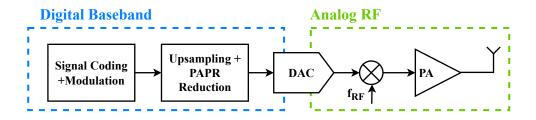

Fig. 2.1 shows the architecture of a single transmitter chain base station with an ideal PA. The modules in this transmitter can be categorized into two sections: the digital baseband

Figure 2.1: A single transmitter chain base station architecture with an ideal PA.

modules that are implemented in digital hardware and the analog radio frequency (RF) modules comprising RF circuits. Data converters, the digital-to-analog converter (DAC) and analog-to-digital converter (ADC), make the transition between these two sections possible. The modules used in the transmitter chain are as follows:

- A signal generator that streams the coded and modulated signal.

- An upsampling and peak-to-average power ratio (PAPR) reduction unit. This unit upsamples the signal to a wider bandwidth in order to accommodate the inevitable spectral regrowth due to non-linearity and memory effects present in the chain, a PAPR reduction module is necessary to avoid PA saturation.

- A DAC that converts the digital signal to a baseband analog signal.

- An upconverter to transfer the baseband analog signal to the desired RF frequency that is within the PA's operational frequency.

- A PA, and if required, a driver amplifier to facilitate the required input power level to the PA.

- A single transmitting antenna.

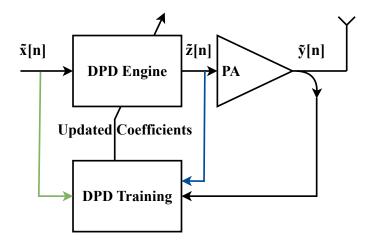

Due to the non-linear nature of the PA and the memory effects that the RF component line-up will exhibit, a transmission-observation-receiver (TOR) along with a signal processing module, the DPD unit, is needed to mitigate non-idealities of the single transmission chain (see Fig. 2.2). The TOR will sample the RF signal and provide a feedback loop to the DPD unit. The TOR consists of the following modules:

• An RF coupler that will sample the RF signal after the power amplifier and before the antenna.

Figure 2.2: A single transmitter chain base station architecture including the DPD engine and the transmitter-observation receiver feedback structure used for training the DPD.

- A downconverter that will bring the PA output signal to the analog baseband and an ADC that will convert the analog baseband signal to the digital baseband.

- A DPD training unit that will use the ideal signal before distortion and the sampled signal after distortion by the PA to generate the parameters (coefficients) needed by the DPD engine. The DPD engine will distort the ideal signal to generate a predistorted signal that will be sent to the PA. Further details about the DPD unit are discussed in Section 2.1.4.

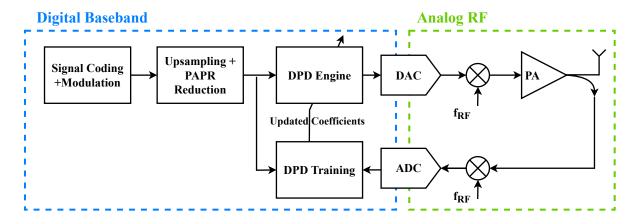

### 2.1.2 Power Amplifier Non-Linear Behavior

In a communications transmitter chain, after the data signal is up-converted to the desired RF frequency, the power amplifier provides the required power level to the signal before being radiated by the antenna. As the most power-consuming component in the transmitter, the PA must have high efficiency. One compromise in designing and utilizing PAs is the linearity and efficiency trade-off. PAs exhibit non-linear behaviour when given a high-power signal at their input and eventually saturate as the input power is further increased. This non-linear behaviour leads to spectral regrowth.

Communication standards specify out-of-band (OOB) emission levels [24]. A simple approach to achieve the required linearity to meet the OOB emission levels is to use the PA in power back-off. As a consequence of the power back-off, the PA will be operating with lower efficiency. This trade-off is visualized in Fig. 2.3. Thus, it is desirable to operate

Figure 2.3: Linearity-efficiency tradeoff in the PA. [1]

the PA at high efficiency and linearize the PA using signal processing methods instead of operating at back-off. The signal processing method that is studied in this work to linearize the PA is digital predistortion or DPD.

### 2.1.3 Linearity Figures of Merit

Below, several metrics that will be used to describe signal characteristics and quantify non-idealities of the PA are reviewed.

### PAPR

Peak-to-Average Power Ratio or PAPR is a measure of the peak power of a signal relative to its average power. In communications systems, the PAPR of a signal is an important factor that affects the performance of the system, i.e., a high PAPR signal can saturate the PA. It is important to back off the input signal of a PA by at least the PAPR of the signal from the saturation power of the PA to avoid significant non-linear distortion. The PAPR of the signal x(t) is defined as follows:

PAPR [dB] =

$$10 \log_{10} \frac{\max(|x(t)|^2)}{\max(|x(t)|^2)}$$

### Linearization Bandwidth

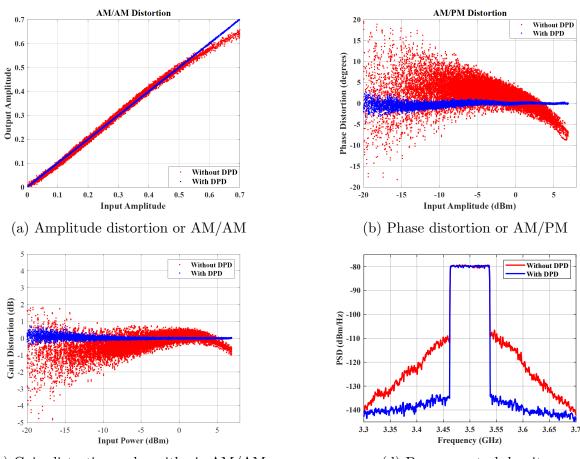

As seen in Fig. 2.4, PA non-linearity gives rise to OOB emissions and spectral regrowth. To linearize this non-linearity with DSP methods, it is necessary to capture and generate a bandwidth wider than that of the modulated signal. This wider bandwidth is called the linearization bandwidth. As a rule of thumb, it is sufficient to capture at least 5 times the bandwidth of the modulated signal. For example, in Fig. 2.4, the modulated signal bandwidth is approximately 80 MHz and the linearization bandwidth is 400 MHz.

### Amplitude and Phase Distortion

AM/AM distortion refers to the distortion of the amplitude of a signal as it is amplified. It is a visual tool that shows the PA's power-dependent behaviour. It is typically plotted as a graph with the input signal level on the x-axis and the output signal level on the y-axis. The AM/AM distortion plot shows how the output signal level changes as the input signal level are varied. Similarly, the AM/PM distortion plot shows how the phase shift of the output signal changes due to distortion, as the input signal level is varied. Fig. 2.4 shows the amplitude and phase distortion of a complex baseband signal at the output of a PA, without and with DPD. This figure also shows how DPD can eradicate spectral regrowth. Note that the complex baseband equivalent (CBBE) signal of the PA output is used to obtain the plots.

### ACPR

Adjacent channel power ratio (ACPR) is a performance metric that quantifies out-of-band emissions. ACPR is typically measured in decibels (dB) and is expressed as the difference between the power of the signal in an adjacent channel and the power of the signal in the desired channel. For example, the ACPR of the signal in Fig. 2.4 without DPD is approximately (-110 dBm)-(-80 dBm) = -30 dB and with DPD, ACPR is improved to (-135 dBm)-(-80 dBm) = -55 dB. The 5G NR standard requires an ACPR of -45 dB or better for a base station [24].

### Root Normalized Mean Square Error (RNMSE)

In this thesis, the root normalized mean square error (RNMSE) is a measure of the difference between the ideal signal x(t) and the amplified PA output y(t), expressed in percentage. The 5G NR standard requires RNMSE of 2.2% or better for a base station [24].

(c) Gain distortion or logarithmic AM/AM

(d) Power spectral density

Figure 2.4: PA non-idealities including non-linearity and memory effect, without and with DPD.

## 2.1.4 Digital Predistortion for Linearizing Single Chain Transmitters

In essence, single-input single-output (SISO) DPD aims to linearize the PA by applying the inverse of the non-linear transfer function of the PA, i.e., by predistorting the signal input to the PA. By doing so, the cascade of the DPD block and the PA will behave linearly. In the next section, the forward model of the PA is reviewed followed by a section on DPD models and learning methods.

### Forward Modelling the PA

The non-linear characteristics of a PA can be modelled using the Volterra/Wiener representation of non-linear systems, first presented in [25]. DPD model derivation starts with modelling the PA non-linearity with the Volterra expansion representing a non-linear system exhibiting memory effects.

$$y(t) = \sum_{l=1}^{\infty} \int_{\mathbb{R}^l} h_l(\tau_1, \cdots, \tau_l) \cdot \prod_{r=1}^l x(t - \tau_r) d\tau_1 \cdots d\tau_l$$

(2.1)

In (2.1),  $h(t_1, \ldots, t_n)$  is the n<sup>th</sup> order Volterra kernel. Together, the kernels of order  $n = 1, 2, \ldots$  describe the non-linear behaviour of the PA. Memory effects are represented by memory values  $\tau_1, \ldots, \tau_n$ . The real bandpass signal x(t), centered at frequency  $\omega_0 = 2\pi f_0 t$  has the following complex baseband representation:

$$x(t) = \frac{1}{2}(\tilde{x}(t)e^{j\omega_0 t} + \tilde{x}^*(t)e^{-j\omega_0 t})$$

(2.2)

where  $\tilde{x}(t)$  is called the complex envelope or complex baseband equivalent (CBBE) of x(t).

Substituting (2.2) in (2.1) and only keeping terms with the center frequency  $\omega_0$ , we have:

$$y(t) = \sum_{n=0}^{\infty} \int_{\mathbb{R}^{2n+1}} \frac{\tilde{h}_n(\tau_1, \cdots, \tau_{2n+1})}{2^n} \cdot \prod_{r=1}^n \tilde{x}^*(t-\tau_r) \cdot \prod_{k=n+1}^{2n+1} \tilde{x}(t-\tau_k) d\tau_1, \cdots, d\tau_{2n+1} \quad (2.3)$$

The main challenge of using the Volterra model in (2.3) is determining the Volterra kernels. Although the Volterra model is the most general and complete formulation of

modelling a non-linear system, it is not practical. Thus, practical models have been developed that provide acceptable modelling accuracy and have reduced complexity. Prevalent models in the literature include general memory polynomial (GMP) [26], dynamic deviation reduction (DDR) [27], decomposed vector rotation (DVR) [28] and complexity reduced Volterra (CRV) [29].

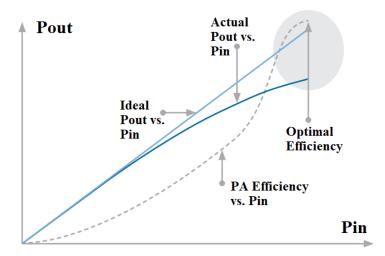

### **Digital Predistortion**

Fig. 2.5 shows a baseband equivalent model of a single transmitter chain DPD consisting of a DPD engine, a DPD training unit and the PA. For simplicity, the TOR is not pictured. If a PA is weakly non-linear, it is commonly assumed that the DPD model structure used to linearize the PA has a model formulation identical to that of the PA's model. Generally, the baseband equivalent model generates the CBBE predistorted signal  $\tilde{z}[n]$  as follows:

$$\tilde{z}[n] = \sum_{p=1}^{P} w_p \tilde{\psi}_p(\tilde{\mathbf{x}}[n]), \qquad (2.4)$$

where the DPD model has P basis functions  $\tilde{\psi}_1(.), \tilde{\psi}_2(.), \ldots, \tilde{\psi}_P(.)$  and  $\tilde{\mathbf{x}}[n] = [\tilde{x}[n], \ldots, \tilde{x}[n-N+1]]$ . In this thesis, the DPD model used is a modified version of the DDR model seen in [27]. Using this model, the predistorted signal  $\tilde{z}[n]$  is:

$$\tilde{z}[n] = \sum_{p=0}^{P_1} \sum_{m=0}^{M} w_{1,p,m} \tilde{x}[n-m] |\tilde{x}[n-m]|^p + \sum_{p=0}^{P_2} \sum_{m=1}^{M} w_{2,p,m} \tilde{x}[n-m] |\tilde{x}[n]|^p + \tilde{x}^2[n] \sum_{p=0}^{P_3} \sum_{m=1}^{M} w_{3,p,m} \tilde{x}^*[n-m] |\tilde{x}[n]|^p + \tilde{x}^*[n] \sum_{p=0}^{P_4} \sum_{m=1}^{M} w_{4,p,m} \tilde{x}^2[n-m] |\tilde{x}[n]|^p$$

(2.5)

where  $P_1$  is the maximum static non-linearity order,  $P_2$ ,  $P_3$  and  $P_4$  are secondary nonlinearity orders and M is the memory depth, all obtained empirically.

Figure 2.5: Conceptual diagram showing DPD process in complex baseband equivalent domain. The direct learning process (green) and indirect learning process (blue) are pictured.

The goal is to determine the  $w_p$  coefficients in (2.4) that minimize the distortion of the output of the PA. This is commonly found using one of two learning methods, called direct and indirect learning. The former method, first introduced along with the Volterra model for modelling non-linear amplifiers in [25], seeks to minimize an objective function J that is the mean-square error between the data signal  $\tilde{x}[n]$  and the PA output  $\tilde{y}[n]$ . Specifically,  $\mathbf{w} = [w_1, \ldots, w_p]$  is sought that minimizes the following objective function over N samples:

$$J = \sum_{n=1}^{N} \|\frac{\tilde{y}[n]}{G} - \tilde{x}[n]\|^2,$$

(2.6)

where G is the PA gain. In order to calculate the complex coefficients  $\mathbf{w}$ , a gradient descent-based approach is adapted [30, 31]. Specifically, to minimize the real cost function J, the following iterations are computed:

$$\mathbf{w}_{k+1} = \mathbf{w}_k - \mu \frac{\partial J}{\partial \mathbf{w}^*},\tag{2.7}$$

where  $\mu$  is the step size or learning rate. In order to compute  $\frac{\partial J}{\partial \mathbf{w}^*}$  in (2.7), the PA output  $\tilde{y}[n]$  is modeled as:

$$\tilde{y}[n] = h_0 \tilde{x}[n] + \tilde{e}[n], \qquad (2.8)$$

where  $\tilde{e}[n]$  is the distortion of the output of the PA and  $h_0$  is the linear gain of the PA. Since the PA is weakly non-linear, by ignoring  $\tilde{e}[n]$  in (2.8),  $\frac{\partial J}{\partial \mathbf{w}^*}$  can be computed from (2.8) and (2.7), resulting in:

$$\mathbf{w}_{k+1} = \mathbf{w}_k + \mu \frac{G}{h_0} (\Psi_{\tilde{x}}^H \Psi_{\tilde{x}})^{-1} \Psi_{\tilde{x}}^H \left(\frac{\tilde{\mathbf{y}}}{G} - \tilde{\mathbf{x}}\right)$$

(2.9)

where  $\tilde{\mathbf{x}} = [\tilde{x}[n], \dots, \tilde{x}[n-N+1]]^T$  and  $\Psi_{\tilde{x}}$  is a  $N \times P$  matrix representing the P basis functions for N samples of  $\tilde{x}[n]$ , i.e.,

$$\Psi_{\tilde{x}} = \begin{pmatrix} \tilde{\psi}_{1}(\tilde{\mathbf{x}}[n]) & \cdots & \tilde{\psi}_{P}(\tilde{\mathbf{x}}[n]) \\ \tilde{\psi}_{1}(\tilde{\mathbf{x}}[n-1]) & \cdots & \tilde{\psi}_{P}(\tilde{\mathbf{x}}[n-1]) \\ \vdots & \vdots & \vdots \\ \tilde{\psi}_{1}(\tilde{\mathbf{x}}[n-N+1]) & \cdots & \tilde{\psi}_{P}(\tilde{\mathbf{x}}[n-N+1]) \end{pmatrix}$$

(2.10)

Alternatively, indirect learning finds  $\mathbf{w}$  by minimizing the error between a post-distorted output signal  $\frac{\tilde{y}[n]}{G}$  and the predistorted signal  $\tilde{z}[n]$  [32]. To do this, a copy of the predistortion engine is used to apply the DPD model to the scaled PA output  $\frac{\tilde{y}[n]}{G}$ . Then the DPD output is compared against the predistorted signal  $\tilde{z}[n]$  and coefficients  $\mathbf{w}$  are updated to minimize the error between the two as follows:

$$\mathbf{w} = \arg\min_{\mathbf{w}} \sum_{n=1}^{N} \|\sum_{p=0}^{P} w_p \tilde{\psi}_p(\frac{\tilde{y}[n]}{G}) - \tilde{z}[n]\|^2$$

(2.11)

The optimal solution for the coefficient matrix  $\mathbf{w}$  in (2.11) is given as:

$$\mathbf{w} = (\Psi_{\tilde{y}}^{H} \Psi_{\tilde{y}})^{-1} \Psi_{\tilde{y}}^{H} \tilde{\mathbf{z}}, \qquad (2.12)$$

where  $\tilde{\mathbf{z}} = [\tilde{z}[n], \dots, \tilde{z}[n-N+1]]^T$  and  $\Psi_{\tilde{y}}$  is defined similar to (2.10):

$$\Psi_{\tilde{y}} = \begin{pmatrix} \tilde{\psi}_1(\tilde{\mathbf{y}}[n]) & \cdots & \tilde{\psi}_P(\tilde{\mathbf{y}}[n]) \\ \tilde{\psi}_1(\tilde{\mathbf{y}}[n-1]) & \cdots & \tilde{\psi}_P(\tilde{\mathbf{y}}[n-1]) \\ \vdots & \vdots & \vdots \\ \tilde{\psi}_1(\tilde{\mathbf{y}}[n-N+1]) & \cdots & \tilde{\psi}_P(\tilde{\mathbf{y}}[n-N+1]) \end{pmatrix}$$

(2.13)

Finally, the coefficients obtained using (2.12) are updated in the original DPD engine. Indeed, the indirect learning method does not use the gradient-descent approach in (2.7) and is quicker in updating DPD coefficients. The caveat to using indirect learning is that after a few update iterations, the signal statistics change and the PA behaviour changes along with it. Thus, in practice, indirect learning is used for the first few iterations and the results are further refined through more direct learning iterations.

## 2.2 Digital Predistortion of MIMO Transmitters

### 2.2.1 MIMO Transmitter Architecture

One of the key enabling technologies of 5G communication networks that will expedite high-speed communications at gigabits-per-second speed is MIMO systems. These systems deploy numerous transmission chains including data converters, PAs and antennas to achieve data rate and signal quality requirements of 5G NR. Increasing the number of antennas at the base station reduces the required overall radiated power due to coherent combining gains, and increases the number of terminals that can be served simultaneously while providing uniformly good service to them. Furthermore, utilizing numerous transmitting antennas results in channel hardening and avoids deep fading and shadow fading due to channel propagation [33]. The challenge in utilizing MIMO systems is to be mindful of size and space, power consumption and antenna loading effects when designing MIMO architectures.

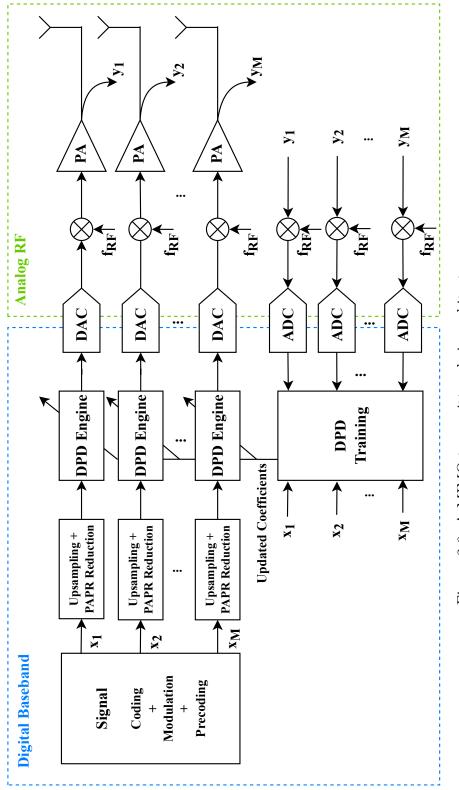

Analogous to a single transmitter architecture, a MIMO transmitter chain is depicted in Fig. 2.6. This architecture consists of duplicates of the single transmitter in Fig. 2.1. In addition to coding and modulation, signals are precoded before being streamed. Precoding is a technology that is used to improve the performance of the system by precoding the transmitted signals to counteract the negative effects of the over-the-air (OTA) channel. It is evident that the complexity of the MIMO transmitter architecture increases significantly when the DPD unit and multiple TORs are added to the architecture in Fig. 2.6.

| Antenna Separation | Mutual Coupling | ACPR                 |

|--------------------|-----------------|----------------------|

| $0.36 \ \lambda$   | -14.0 dB        | -46.4 dB             |

| $0.44 \ \lambda$   | -20.9 dB        | $-52.3 \mathrm{dB}$  |

| $0.59 \ \lambda$   | -28.4 dB        | $-57.4 \mathrm{~dB}$ |

Table 2.1: Antenna mutual coupling quantified through ACPR levels.

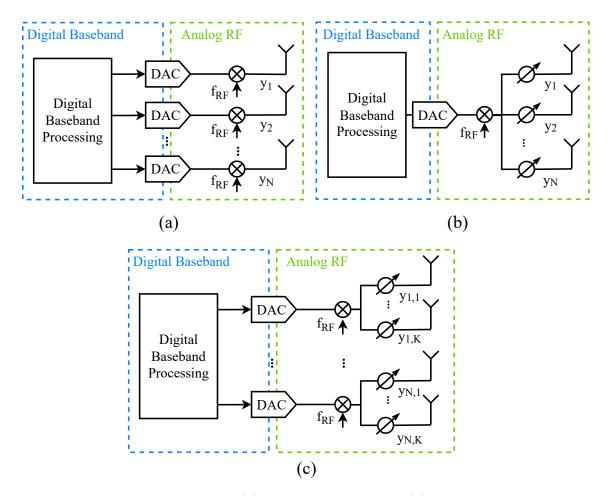

### Beamforming

One method that will unleash the potential of the MIMO structure introduced in this section is beamforming. Essentially, beamforming is the ability to control the direction in which each main antenna beam in the MIMO array is directed towards. There are three types of beamforming, as shown in Fig. 2.7. Digital beamforming controls each and every RF chain with a separate and independent digital chain. On the other hand, analog RF beamforming consists of one digital signal stream that splits into N streams and the phase shifters together control the angle at which the beam is steered by the array. Although digital beamforming consumes more power than its RF counterpart, it provides more flexibility for each transmitter chain. Hybrid beamforming is a mixture of both digital and analog RF beamforming, providing flexibility and lower power consumption. The beamforming structure that is achieved in this thesis is digital beamforming. This structure provides the flexibility to demonstrate analog beamforming and hybrid beamforming.

### 2.2.2 Impact of Antenna Crosstalk on Power Amplifier Behavior

Due to the high level of integration in MIMO chipsets, antenna elements are very close to each other and under the assumption that the antennas of a MIMO transmitter are emitting at the same frequency, mutual coupling between elements is detrimental to signal quality. An increase in mutual coupling between antenna elements results in increased OOB emissions and spectral regrowth [34]. Table 2.1 quantifies this regrowth through ACPR measurements done by varying the separation between two transmitter chain antennas and consequently, the mutual coupling level [35]. As antenna separation distances are decreased from 0.59  $\lambda$  to 0.44  $\lambda$ , the mutual coupling between antennas increases by approximately 8 dB and ACPR degrades by 5 dB. It is noteworthy to mention that in order to exploit their potential, MIMO systems usually consist of more than two antennas. This means each

Figure 2.7: Beamforming structures: (a) Digital beamforming (b) Analog RF beamforming (c) Hybrid beamforming.

Figure 2.8: Incident and reflected waves in k-chain MIMO system.

antenna in a MIMO system is surrounded by more than one neighbouring antenna and thus the numbers depicted in Table 2.1 may be exacerbated as antenna count increases.

One solution utilized to eliminate the inter-antenna crosstalk effect in MIMO systems is to place a circulator or isolator between the power amplifier and antenna. These decoupling isolators take up a large area [36], incur additional costs [37], or have narrow operating bandwidths [38], unsuitable for MIMO systems.

As DPD is a signal processing method that is deployed in single-chain transmitters and avoids problems that arise with isolator uses, it is desirable to modify the DPD presented in Section 2.1.4 to compensate for antenna crosstalk-induced non-linearity in addition to intrinsic PA non-linearity. Thus, one solution that circumvents the mentioned shortcomings is a more complex DPD. To minimize complexity, this DPD should not require complete knowledge of all signals to be transmitted by all other antennas. In the extreme case, only a second signal is input to the DPD that summarizes the crosstalk effect of surrounding antennas. Hence it is referred to as the dual-input single-output (DISO) DPD.

## 2.2.3 Dual-Input-Single-Output Digital Predistortion for MIMO Transmitters

The effect of antenna crosstalk in MIMO transmitters is cancelled by utilizing DISO DPD. Similar to deriving SISO DPD in Section 2.1.4, DISO DPD starts with investigating the forward model to represent a MIMO system exhibiting inter-antenna cross-coupling. Consider the incident and reflected waves in each RF chain of a MIMO transmitter, shown in Fig. 2.8. As explored in [39], the mutual coupling of antennas in MIMO systems that affects the reflected wave  $\tilde{a}_{2i}$  not only exacerbates the non-linear behaviour of the PA but also affects the PA's direct current (DC) behaviour and in return, its efficiency.

Given the K-element antenna array S-parameters around the center frequency as  $\mathbf{S}_{K\times K}$ , the reflected wave  $\tilde{a}_{2i}$  from the antenna at any chain *i* can be written in terms of the incident wave  $\tilde{b}_{2i}$  from K antennas as:

$$\tilde{a}_{2i}[n] = \sum_{k=1}^{K} s_{ik} \tilde{b}_{2k}[n].$$

(2.14)

The output  $\tilde{b}_{2i}$  of the i<sup>th</sup> PA depends on both its input  $\tilde{a}_{1i}$  and the reflected wave  $\tilde{a}_{2i}$  on its output port [40]. Hence, based on (2.14), the output of each PA in a MIMO system also depends on the PA output of each of its K-1 neighbouring chains. Similar to the derivation of Volterra forward models in Section 2.1.4, forward models for PAs in MIMO systems have been proposed in [41]. Given that the Volterra expansion is not of practical value, pruned models are addressed next. Pruning is a technique for reducing the complexity of a trained DPD, with the goal of decreasing the computational requirements without sacrificing its performance. A common pruning method is to remove the least important terms (i.e., those with the smallest absolute value coefficient) from the expansion that describes the predistorted signal  $\tilde{z}[n]$ .

In the literature, different assumptions have been made regarding the coupled signals and their subsequent effect on the linear and non-linear distortion in a specific transmitter chain. The MIMO DPD models in [42, 43] cancel non-linear crosstalk happening before PAs but do not compensate for non-linear crosstalk occurring after the PA. In [44], the authors propose a DPD model based on the assumption that antenna crosstalk only introduces linear distortion.

In [2], the authors assume both linear and nonlinear crosstalk after the PA. Their proposed DPD model comprises two blocks; a linear crosstalk and mismatch (crosstalk and mismatch model (CTMM)) block that models antenna coupling and mismatch and

Figure 2.9: Structure of the DISO DPD proposed in [2], consisting of a DISO DPD engine in each transmission chain and a shared CTMM module.

that is shared between all transmitter chains, and a non-linear dual-input DPD unit in each transmitter chain (see Fig. 2.9). The function of the CTMM block is to compute the estimates  $\hat{a}_{2i}$  of  $\tilde{a}_{2i}$  in (2.14). The k<sup>th</sup> dual-input DPD output  $\tilde{z}_k[n]$  is proposed in the following manner:

$$\tilde{z}_{k}[n] = \sum_{p=0}^{P_{0}-1} \sum_{m_{0}=0}^{M_{0}} \alpha_{p,m_{0}} \tilde{x}[n-m_{0}] |\tilde{x}[n-m_{0}]|^{p} + \sum_{p=0}^{P_{1}-1} \sum_{m_{0}=0}^{M_{1}} \sum_{m_{1}=0}^{M_{2}} \beta_{p,m_{0},m_{1}} \hat{a}_{2k}[n-m_{0}] |\tilde{x}_{k}[n-m_{1}]|^{p} + \sum_{p=0}^{P_{2}-3} \sum_{m_{0}=0}^{M_{3}} \sum_{m_{1}=0}^{M_{4}} \gamma_{p,m_{0},m_{1}} \hat{a}_{2k}^{*}[n-m_{0}] \tilde{x}_{k}^{2}[n-m_{1}] |\tilde{x}_{k}[n-m_{1}]|^{p}.$$

$$(2.15)$$

In summary, numerous works exist in the literature to circumvent the adverse effects of antenna crosstalk by augmenting existing DPD methods. The approach presented in [2] is the most general solution as it makes no narrowing assumptions on the type of crosstalk between adjacent antenna. That being said, research into DSP methods for antenna crosstalk compensation lacks physical model analysis regarding the circuit-level effects of crosstalk in the RF frontend.

## 2.3 Review of Existing DPD Hardware Implementations for Single Chain and MIMO Transmitters

Aside from theoretical work done on digital predistortion systems, the practical implementation of such systems is of high importance. This is specifically true in 5G systems which deploy a high count of base stations compared to previous generations of networks, necessitating power consumption reduction and resource reduction in hardware implementation. As part of the process of deploying signal processing methods in industry, initially, evaluation of DSP methods is done by implementing the methods on an fieldprogrammable gate array (FPGA) and results are assessed in terms of resource utilization, power consumption and performance. Although FPGAs provide a re-programmable platform to verify signal processing algorithms, using them in the field is debatable. Compared to application-specific integrated circuit (ASIC) chips, FPGAs have high unit cost, high power consumption and greater unit size. After evaluating DSP methods' performance, satisfactory methods are hardened on an ASIC and used in deployed systems. Due to the widespread availability of FPGA circuits and simpler design flow compared to ASICs, hardware optimization is explored using FPGA chips in the literature.

Research on reducing complexity and power overhead in predistortion systems can be divided into two categories: DPD model simplification and hardware design methods (see Fig. 2.10). Efforts in DPD model simplification can be divided into three subcategories: (1) basis complexity reduction [15, 16], (2) Lookup table (LUT)-based models [8, 9, 10, 11] and (3) Piecewise-linear models (piece-wise linear (PWL)), also known as magnitude selective affine models [9, 17, 18]. Likewise, hardware design methods can also be divided into three subcategories: (1) realizing any model through LUTs [12, 13, 14], (2) optimizing the datapath [45], and (3) parallel-processing methods [19]. In this section, the work previously done in each category and relevant to this thesis is reviewed.

Many research works in the literature propose a cascade of two DSP units as a DPD solution in order to simplify the complexity of each individual unit. In [15], the authors propose a feedback memory topology that contains linear and non-linear memory effects as the unit cascaded with the memoryless DPD engine. This simplifies the DPD structure, albeit requiring two sets of coefficients and their respective training. In addition, the authors propose a coefficient training algorithm that is O(n) complex, allowing for the coefficient training to be done online on the FPGA. Similar to [15], cascaded DPD is used

Figure 2.10: Categorized prior work on complexity reduction of the predistorter

in [16]. In [16], DPD is proposed for a directional modulation system comprising multiple transmitter chains and should include a predistorter in each chain. A common DPD block is used for all chains, followed by a separate auxiliary DPD block in cascade per chain to fine-tune the remaining non-linearity. It was claimed that this scheme would be suitable for hardware implementation, however, no results were presented regarding resource utilization to verify this claim.

The essence of LUT-based DPD models is to use a predefined table of values that can be used to compensate for the nonlinear distortions introduced by the PA. In a LUT-based DPD, the input signal is first processed to generate a set of input-output characteristics, which are then used to create the lookup table. The LUT is typically implemented as a memory array that can be quickly accessed in real time, and it contains the predistortion values that correspond to different input signal levels. When the input signal is applied to the power amplifier, the LUT is used to apply the appropriate predistortion values to the signal, so that the output of the amplifier is as close as possible to the desired linear response. The main benefits of LUT-based predistortion is that it can correct for a wide range of nonlinear distortions, it can be implemented in real-time, it has low complexity and it requires less computation power compared to other techniques such as polynomial modelling. However, the LUT-based DPD requires a high-resolution memory table and it is not so adaptable to changes in the PA's characteristics like temperature or aging.

The work presented by the authors in [8, 10] is based on the PA behavioural model introduced in [8]. In [8], the authors implement the DPD engine on an FPGA using a LUT-based implementation, and DPD training is done offline on a co-processor. This is followed by [10], in which the training is transferred to the FPGA, allowing for a full online DPD training and application. Resource utilization is reported in [10], showing a reduction in FPGA processing slices at the cost of increased block ram (BRAM) count and low clocking frequency (40 MHz). BRAMs make significant contributions to the overall power consumption of a hardware implementation and it is preferred that they be reduced or altogether avoided.

Another LUT-based DPD is that in [11]. This DPD provides a fair trade-off between BRAM, processing slices and clocking frequency (92.16 MHz) and is based on the well-known memory-polynomial (MP) model. First, the MP model is manipulated to achieve a lower-complexity implementation. Then each section of the model is implemented using independent "adaptive" LUT units whilst allowing flexible memory depth. However, in practice, the LUT units are replaced with BRAMs, whose count is subject to increase with an increase in memory depth. Power consumption is not reported, however, an increased BRAM count leads to an increase in power consumption.

The piecewise linear DPD model (PWL) is another prevalent type of model used to correct for nonlinear distortions of the PA. It is a variation of the LUT-based DPD method where the LUT is divided into several regions, each of which has a different predistortion function. In a PWL DPD system, the input signal is first divided into multiple segments using a set of predefined threshold levels. Each segment is then processed using a separate linear predistortion function. The goal is to find the appropriate predistortion function for each segment, such that the output of the PA is as close as possible to the desired linear response.

The work presented in [9] exhibits a DPD formulation that is both a piece-wise model and implementable through LUTs. By providing a piece-wise model, basis functions are significantly simplified in terms of hardware complexity. What distinguishes [9] from the research in [17, 18] on PWL models is that the authors also ensure continuity between intervals. Although this model was not implemented in hardware, it is evident that it would lead to significant resource optimizations on the FPGA, while being independent of the DPD model chosen. Hence, this work's piece-wise formulations have been adapted in this thesis.

Two other noteworthy works adapting a piecewise DPD model are [17] and [18]. As one of the earliest works in PWL DPD, the authors in [17] determine a partitioning strategy and allow for any Volterra-based DPD model to be implemented in their vector-switched model. Hardware implementation is not available in this work; however, complexity analysis is reported in terms of complex floating-point operations per sample (FLOPS). In [18], the authors implement a magnitude selective affine PWL model to substitute nonlinear crossterms. The proposed model was implemented on an FPGA and complexity was reported in terms of the number of coefficients, registers and processing slices used. Although the model used in [18] is questionable regarding instability on interval limits due to discontinuity, it achieves low complexity and fair FPGA clock frequency (260 MHz).

Several hardware implementation optimization techniques exist that can be used to improve the performance and efficiency of a real-time DPD system. The works in [13], [12], [14], [45] and [19] all use hardware implementation techniques to further optimize resource usage and clocking frequency of the FPGA. The notable work in [14] and [12] both use LUTs in hardware implementation, both works acknowledge using high BRAM and processing resource units and provide no alternative solutions. In [13], a Volterra series-based DPD is implemented in hardware using gain-indexed LUTs with time-shared multiplier usage to decrease resource count. FPGA resource utilization was reported and showed low processing resources but high BRAM count. The authors also mention that while sharing processing resources allows for optimized resource usage, it requires data to be processed in serial, resulting in high processing clock rates.

The authors in [19] provide an elegant solution to meet high bandwidth standards in 5G NR: parallel processing. To further increase the processing speed, this solution uses multiple DPD sub-units in parallel to perform the computations. In other words, this solution takes advantage of the parallel data feeding properties of state-of-the-art data converters by generating the signal that is input to the data converters in parallel streams. Although the resource count for parallel processing increases with parallel stream count, parallel processing is key to meeting high bandwidth requirements within the constraints of the maximum digital clocking rates currently available. In [46, 47], it is demonstrated that SISO DPD can linearize the main beam in analog beamforming MIMO systems. Thus, the parallel-processing method is used to implement SISO DPD in [19] and linearization performance is evaluated using a 64-element analog beamforming array.

At the time of writing this thesis, the author's investigation of the hardware implementation of DPD solutions for fully-digital MIMO systems was inconclusive.

### 2.4 Review of Real-time MIMO Transmitter Testbeds

Noteworthy experimental platforms have been developed in academia developed to demonstrate the potential of MIMO transceivers. These include LuMaMi (Lund University and University of Bristol)[20], ESAT lab's product (KU Leuven University) [21], Argos (Rice University)[22] and State Key Lab of Millimeter Waves' array (Southeast University of China) [23].

The platforms introduced in [20] and [21] are identical and use commercially available software-defined-radios (SDR) as the transceiver unit (Fig. 2.11). These systems can ac-

Figure 2.11: LuMaMi of Lund University (left) and of KU Leuven (right).

commodate up to 128 transmitter chains and operate in sub-6 GHz frequency but only allow for 40 MHz of instantaneous bandwidth. The platforms use up to 50 FPGA processors for coherent signal transmission and synchronization. The commercial SDRs in these testbeds limit the configurability of the RF frontend which in turn limits the applications of this testbed. These platforms have been used in research regarding OTA channel sounding, validating massive MIMO's proof-of-concept, MIMO cloud-RAN and relaying.

On the other hand, the Argos platform from Rice University presented in [22] uses an in-house designed SDR product and is developed for research in multi-user MIMO (MU-MIMO), channel sounding and self-interference reduction. This platform supports up to 64 base station transmitter chains and 15 users and operates at sub-6 GHz frequencies with a maximum bandwidth of 20 MHz. Pairs of SDRs are controlled and synchronized using one FPGA unit. Although the customized SDR provides RF frontend flexibility, the supported bandwidth is insufficient to exploit the full potential of a 5G MIMO system.

Most recently, Southeast University in China presented a 64-chain fully digital testbed targeting 3.4-3.6 GHz [23]. This testbed is claimed to support 200 MHz of signal bandwidth in each chain using one processing FPGA for every few chains. Although this testbed is promising in characteristics, no further measurements or results have been reported other than those in [23].

At the time of writing this thesis, only the aforementioned experimental platforms were known to the author.

Figure 2.12: Argos of Rice University (left) and Southeast University's testbed (right).

## 2.5 Discussion

In this chapter, MIMO systems were introduced as enabling technology in fifth-generation wireless networks. Furthermore, DPD was instigated as a signal processing method that mitigates non-linearities of the RF chain. However, migrating to MIMO systems requires more complex and resource-demanding DPD units due to inter-antenna coupling. An expansive review of DPD hardware implementations was presented. Experimental platforms that are available globally in academia for experimenting on MIMO capabilities were examined. However, there is a noticeable gap between the MIMO technology that is to be deployed in 5G networks and the current MIMO systems, as promised data rates in 5G systems have yet to be exploited. Furthermore, there is no reconfigurable platform that provides flexibility in the RF front-end and allows for exploring linearization of MIMO systems in a real-time system that is similar to what is to be deployed in 5G base stations.

The research that is presented in the following chapters of this thesis aims to provide the central baseband processing unit for a reconfigurable real-time testbed that will rapidly evaluate DPD and signal processing algorithms for the feasibility and efficiency of their design under real conditions of a MIMO system. The testbed that is developed as part of the contribution of this thesis is capable of providing up to 16 chains of RF-modulated signals with up to 1.5 GHz of linearization bandwidth for any custom-designed RF front-end (PA and antenna). Using a combination of hardware implementation techniques that were reviewed in this section, an optimized DPD algorithm is proposed for MIMO systems. The developed testbed provides the experimental platform on which the DPD's performance is evaluated.

## Chapter 3

# Real-time Testbed Development and Implementation for DSP Applications in Fully Digital MIMO Transmitters

## 3.1 Introduction

Fifth-generation telecommunication networks aim to achieve data rates in the order of gigabits-per-second, almost 20 times that of LTE networks. In order to reach these data rates, modulated signals, with hundreds of megahertz of bandwidth are to be used in conjunction with MIMO technology. Massive MIMO is envisaged to deploy hundreds of parallel transmitter chains in the base station that operate simultaneously, facilitating high data rates. MIMO also ensures improved signal quality as it is known to provide transmit diversity to overcome multi-path fading in wireless channels.

Each transmitter chain in the base station is equipped with a PA to provide the necessary output power for the transmitted signal in that chain. As an inseparable part of PA operation, real-time DPD is deployed in the digital domain of every chain to linearize the transmitted signal. In order to capture the OOB emissions of the PAs, a linearization bandwidth of around 5 times that of the modulated signal bandwidth is required. The DPD modules are implemented in hardware to allow real-time operation. However, the maximum fabric clock of a commercially-available FPGA cannot accommodate the required linearization bandwidths of 5G systems. Digital chips are also limited in computational resources. The number of digital transmitter chains implemented on each digital chip is restricted by the total available processing reprocessing resources needed for each DPD module. Therefore it is critical that in the development stage, proposed MIMO DPD methods are evaluated in terms of resource consumption. This calls for a reconfigurable transmitter testbed that allows multi-chain transmission with a flexible digital back-end that can evaluate signal processing methods developed for MIMO systems, including DPD.

It can be argued that multiple digital chips, specifically FPGAs, be used, where each FPGA houses a subset of the total chains, such that the computational burden of MIMO DPD is distributed among them. This poses additional complexities. The multiple FPGAs must be synchronized using a reference clock and common trigger. Furthermore, MIMO DPD may require knowledge of signals of adjacent chains. Thus, a high-speed data transfer protocol must be in place between FPGA chips.

In this chapter, the steps for developing the MIMO testbed are described, discussing requirements along with system design considerations. Next, the challenges of developing the mentioned testbed on an off-the-shelf FPGA platform are presented along with measures taken to overcome these challenges. A complexity-reduced DPD for single-chain transmitters is then presented, along with a parallelization scheme that allows wide linearization bandwidths while meeting hardware timing constraints. To conclude this chapter, the proposed DPD is realized on the MIMO testbed to verify the single-chain operation of the testbed.

### **3.2** Real-time FPGA-based Testbed Requirements

The first step in developing the MIMO testbed is to specify the requirements of the testbed. The requirements, outlined in Table 3.1, are defined such that the transmitted signal meets signal standards of 5G base stations, i.e., as specified in [24], and that the testbed allows for scalability of the number of MIMO chains and supports modular insertion of DSP blocks, which in this work is the DPD engine.

The testbed comprises two main parts: the digital processing hardware and the radio hardware. The digital processing hardware is the digital backbone of the testbed that includes signal generation, streaming memory blocks and DSP modules. The signal is then passed on to the radio hardware, which houses the data converters that convert the digital signal into an analog signal.

The digital processing hardware is more or less independent of the frequency and bandwidth requirements. The processing hardware needs only to be reconfigurable in order

| Number of Chains           | 16                   |

|----------------------------|----------------------|

| Frequency                  | 3.3 - 3.8 GHz        |

| Modulated Signal Bandwidth | $\geq 100~{\rm MHz}$ |

| Processing Hardware        | FPGA                 |

Table 3.1: Real-time MIMO testbed requirements.

to be used as an experimental testbed for different DSP methods, have a fabric clock of hundreds of megahertz and have the capability to potentially connect to a PC through an ethernet port. Establishing a connection to the PC is advantageous since it provides convenient development tools and interfaces. This connection also enables the option of using a PC as an additional processing block in the preliminary development of DSP algorithms with the testbed operated as an arbitrary waveform transmitter. In this case, the PC generates the final signal to be transmitted, uploads the waveform to the testbed and the testbed converts the signal to an analog waveform in the desired RF frequency.

On the other hand, the radio hardware is limited by the number of chains, the frequency band of interest (that is the N78 band from 3.3 to 3.8 GHz), and modulated signal bandwidth requirements. Inter-chains synchronization and coherence are critical when choosing radio hardware as well as verifying that there exists a master synchronization procedure that would allow the expansion of the platform to include a higher number of coherent chains. The chosen radio hardware must contain data converters with sampling rates in the order of a few Giga Samples per second (GSps) to allow for the transmission of a linearization bandwidth approximately 5 times that of the modulated signal bandwidth. Moreover, the data converters should allow internal mixing of the baseband signals to the targeted N78 band frequency range.