Improving the Performance of Nanoscale Field-Effect Transistors Through Electrostatic Engineering

by

Robert Kevin Arran Bennett

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering – Nanotechnology

Waterloo, Ontario, Canada, 2021 © Robert Kevin Arran Bennett 2021

# Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

# ACKNOWLEDGEMENTS

I would like to begin by thanking my supervisor, Professor Yoon, for welcoming me into his research group and for offering me his guidance and patience over the last two years. Thank you for all the help you have given me in both my research and in my academic career.

I would also like to thank all of my fellow group members: AbdulAziz, Andrew, Demin, Hyunjae, Manasa, Mayuri, Richard, and Yiju. I should give special thanks to Demin in particular for teaching me the fundamentals of our NEGF and DFT simulations (and for answering my endless questions) and to AbdulAziz for developing the simulation software that made my research possible. I am also grateful to the Waterloo Institute for Nanotechnology (WIN), the Government of Ontario, and the Natural Sciences and Engineering Research Council of Canada (NSERC) for their financial support.

I've been fortunate enough to have many teachers and mentors who have encouraged me to pursue a career in science and engineering. Thanks go to Sean Ealey, Mitchell Plant, Ross Holt, Dapeng Liu, Collin Tittle, Gordon Hall, William Wang, Yuxing Yao, Professor Wang, and Professor Backhouse for helping me get to where I am today.

I am grateful to my family for always supporting my research career, which may have started I was about four years old and I stuck a twig in a beehive because "I wanted to know what would happen." Thank you for helping me preserve my curiosity while improving my methodology.

And of course, my thanks go out to Sarah for her love and support over the years and for giving me a reason why.

# **ABSTRACT**

The continued scaling of field-effect transistors (FETs) requires that nearly every aspect of these devices be optimized to ensure that they can continue to meet practical performance requirements. However, scaling the channel lengths of FETs naturally enhances electrostatic and quantum mechanical short-channel effects, thereby increasing leakage currents in the OFF-state, reducing driving currents in the ON-state, and making it difficult for FETs attain optimal switching behaviours. To mitigate these detrimental effects, it is imperative to (i) thoroughly understand the electrostatic operation of nanoscale FETs and (ii) establish novel design strategies to mitigate short-channel effects.

In this thesis, I address these two challenges by studying the electrostatic operation of nanoscale FETs using simulation techniques. In particular, I use the non-equilibrium Green's function method, an atomistic quantum transport simulation technique, to study the electrostatic operation of MOSFETs and to assess the utility of novel electrostatic design strategies for nanoscale FETs.

The body of this thesis is divided into three main works. In the first, I study how individual elements of a metal-oxide-semiconductor FET's (MOSFET's) semiconductor's anisotropic permittivity affect device performance, and I establish electrostatic-based guidelines for selecting optimal semiconductors for future MOSFETs. Next, I study how replacing an FET's conventional isotropic insulators (i.e. gate insulator and spacers) with anisotropic insulators can improve the performance of both conventional MOSFETs and tunnel FETs, and I propose novel insulator architectures to further optimize the performance of these devices. Finally, in my third study, I examine how fringe-induced barrier lowering, an electrostatic short-channel effect created by implementing high- $\kappa$  gate insulators, can be exploited to suppress quantum mechanical short-channel effects (source-to-drain tunneling) to improve the overall performance of nanoscale MOSFETs. The operating principles and design rules established in these three works extend the current picture of the electrostatic operation and design rules for nanoscale FETs to help device designers continue to scale FETs while meeting essential performance benchmarks.

# Contents

| Lis | st of Figures                                                                                                                                                                                                                                                     | VI                                           |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Lis | st of Tables                                                                                                                                                                                                                                                      | IX                                           |

| 1   | INTRODUCTION  1.1 Scaling of Field-Effect Transistors                                                                                                                                                                                                             | 1<br>1<br>5<br>5<br>7                        |

| 2   | METHODOLOGY  2.1 Motivation for Simulating Nanoscale Field-Effect Transistors                                                                                                                                                                                     | 11<br>11<br>11<br>12<br>14                   |

| 3   | DIELECTRIC ANISOTROPY IN SEMICONDUCTORS  3.1 Introduction                                                                                                                                                                                                         | 21<br>21<br>22<br>23<br>23<br>26<br>29       |

| 4   | DIELECTRIC ANISOTROPY IN INSULATORS  4.1 Methodology  4.2 Results and Discussion  4.2.1 MOSFETs  4.2.2 Tunnel FETs  4.3 Conclusions                                                                                                                               | 30<br>31<br>32<br>32<br>37<br>41             |

| 5   | EXPLOITING FRINGING FIELDS CREATED BY HIGH-κ GATE INSULATORS  5.1 Introduction  5.2 Methodology  5.3 Results and Discussion  5.3.1 Performance Boost from FIBL  5.3.2 Underlying Physics  5.3.3 Applicability to Other 2D-Material-Based MOSFETs  5.4 Conclusions | 43<br>43<br>44<br>45<br>45<br>47<br>50<br>51 |

| 6   | Conclusions and Future Work                                                                                                                                                                                                                                       | 53                                           |

| Le  | ETTER OF COPYRIGHT PERMISSION                                                                                                                                                                                                                                     | 54                                           |

| RE  | EFERENCES                                                                                                                                                                                                                                                         | 55                                           |

# List of Figures

| 1.1 | (a) A diagram showing how key potentials in an FET are coupled through various capacitors. (b) A top-of-the-barrier model where the conduction band edge is qualitatively plotted as a function of the lateral position in the device. Here, the capacitors from (a) are used to illustrate that the top of the barrier is taken as $\psi_{ch}$ , which is in turn coupled to the source, drain, and gate electrodes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | A schematic illustration showing the difference between thermionic emission (where high-energy electrons contribute to $I_D$ by traveling over the potential barrier) and source-to-drain tunneling (where lower-energy electrons tunnel through the potential barrier).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4   |

| 1.3 | (a) Simulated transfer characteristics for MOSFETs where the semiconductor's dielectric constant was varied between 4 and 4, and whose channel lengths/semiconductor thicknesses are 20/3 nm (group A), 10/3 nm (group B), and 10/4 nm (group C).  (b) Threshold voltage and subthreshold swing as a function of channel length for MOSFETs whose semiconductor's dielectric constant is varied from 4 to 12 and whose semiconductor's thickness is fixed at 3 nm. (c) Various semiconductor dielectric constant profiles used for subsequent simulations. (d) Simulated transfer characteristics for MOSFETs with the profiles shown in (c) (dashed red and black lines) and for MOSFETs with constant semiconductor dielectric constants of 16 (solid red line), 12 (solid black line) and 4 (solid gray line). Linear (e) and logarithmic (f) transfer characteristics for 3-layer MoS <sub>2</sub> -based MOSFETs with a base dielectric constant of 10 and an artificial dielectric constant of 20. In plane (g,h) and out-of-plane (i) permittivities of MoS <sub>2</sub> as a function of strain, where black, blue, red, and green lines correspond to isotropic, shear (xy), uniaxial (x), and uniaxial (y) strains, respectively. |     |

| 1.4 | (a) Transfer characteristics of a MOSFET with various gate insulators, each of whose EOTs are fixed at 0.83 nm. Insulators are listed in the legend in order of decreasing permittivity. (b) MOSFET structure to reduce FIBL while maintaining a large physical thickness to prevent source-to-drain tunneling. (c) Transfer characteristics of an La <sub>2</sub> O <sub>3</sub> -based MOSFET with buffer layers of varying thickness, where the EOT of each gate stack is held constant at 0.86 nm. (d) SS as a function of buffer layer thickness for 3 high- $\kappa$ insulators. (e) Hetero-gate-dielectric MOSFET architecture used to enhance TFETs. (f) $I_{on}$ and SS as functions of geometric parameters as labeled in (e).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ç   |

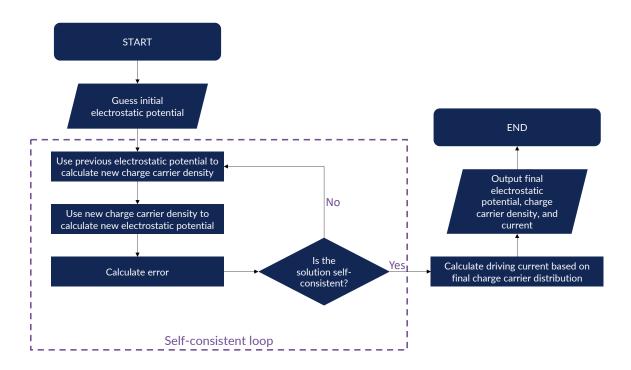

| 2.1 | A flow chart illustrating the NEGF simulation method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12  |

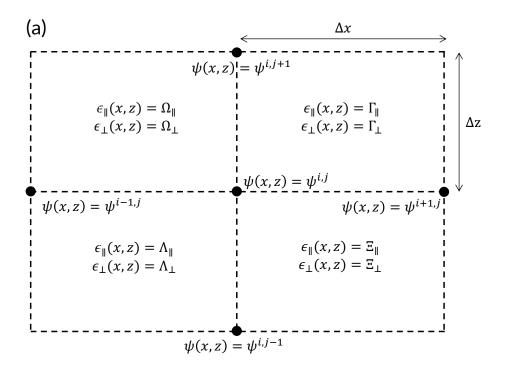

| 2.2 | (a) The five-point star grid used when solving Poisson's equation numerically. Each region in the grid has its own unique permittivities, as labeled. (b) The same, showing the square with differential area $dxdz$ used to set up the integrals shown in Equations (2.20) – (2.23).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16  |

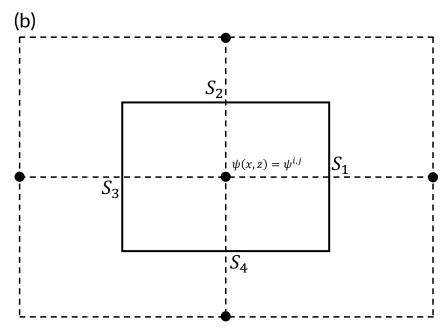

| 3.1 | (a) Various reported values in literature for $\epsilon_{\parallel}^{(SC)}$ and $\epsilon_{\perp}^{(SC)}$ for TMDs. The black dashed line corresponds to $\epsilon_{\parallel}^{(SC)} = \epsilon_{\perp}^{(SC)}$ . (b) the lattice structure of 1T HfS <sub>2</sub> from a top-down view (top) and from a side view (bottom). The red box in the top view shows the rectangular supercell used for DFT calculations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2.2 |

|     | USCO FOR LZE I CALCULATIONS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | //  |

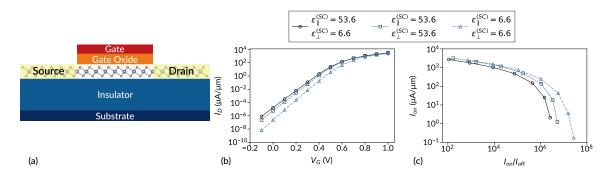

| 3.2 | (a) A diagram of the FET structure used for simulations (not to scale). (b) Transfer characteristics of the nominal device ( $L_{ch}=12$ nm, EOT = 0.5 nm) under three configurations of $\epsilon_{\parallel}^{\rm (SC)}$ and $\epsilon_{\perp}^{\rm (SC)}$ : the full anisotropic case with $\epsilon_{\parallel}^{\rm (SC)}=53.6$ and $\epsilon_{\perp}^{\rm (SC)}=6.6$ (SS = 75 mV/dec, DIBL = 110 mV/V), the isotropic case with $\epsilon_{\parallel}^{\rm (SC)}=\epsilon_{\perp}^{\rm (SC)}=53.6$ (SS = 71 mV/dec, DIBL = 80 mV/V), and the isotropic case with $\epsilon_{\parallel}^{\rm (SC)}=\epsilon_{\perp}^{\rm (SC)}=6.6$ (SS = 66 mV/dec, DIBL = 50 mV/V). (c) $I_{\rm on}/I_{\rm off}$ curves for each configuration of $\epsilon_{\parallel}^{\rm (SC)}$ and $\epsilon_{\perp}^{\rm (SC)}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3 | SS as a function of (a) EOT and (b) $L_{ch}$ . DIBL as a function of (c) EOT and (d) $L_{ch}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25  |

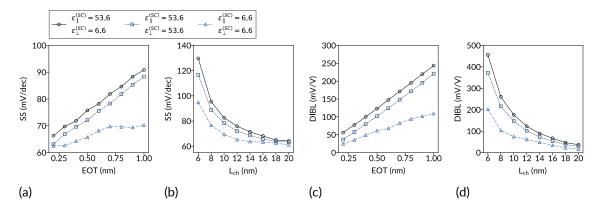

| 3.4 | Heatmaps showing SS as a function of $\epsilon_{\parallel}^{\rm (SC)}$ and $\epsilon_{\perp}^{\rm (SC)}$ for a device with <b>(a)</b> with EOT = 0.5 nm and <b>(b)</b> EOT = 1.0 nm. <b>(c)</b> A schematic of the capacitor model of a MOSFET. <b>(d)</b> $C_G^{(\perp)}/C_D^{(\parallel)}$ plotted as a function of $\epsilon_{\parallel}^{\rm (SC)}$ . <b>(e)</b> $C_G^{(\perp)}/C_D^{(\parallel)}$ plotted as a function of $\epsilon_{\perp}^{\rm (SC)}$ . <b>(f)</b> Electric field lines that begin at the drain and terminate on the gate oxide for a device with $\epsilon_{\parallel}^{\rm (SC)}$ = 5.0 and $\epsilon_{\perp}^{\rm (SC)}$ = 5.0 (top), $\epsilon_{\parallel}^{\rm (SC)}$ = 5.0 and $\epsilon_{\perp}^{\rm (SC)}$ = 10.0 (middle), and $\epsilon_{\parallel}^{\rm (SC)}$ = 10.0 (bottom).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27  |

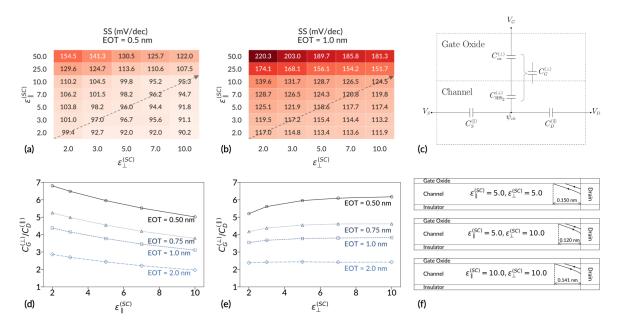

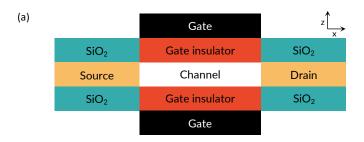

| 4.1 | Device structures for (a) MOSFETs and (b) TFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32  |

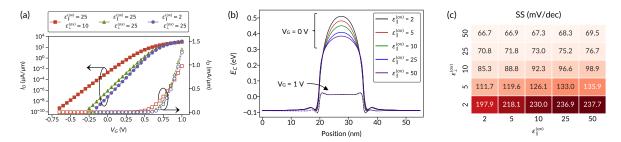

| 4.2 | (a) $I_D$ - $V_G$ characteristics for MOSFETs with varied $\epsilon_{\parallel}^{(ox)}/\epsilon_{\perp}^{(ox)}$ . (b) Conduction band $(E_C)$ profiles of devices at $V_G=0$ and 1 V while varying $\epsilon_{\parallel}^{(ox)}$ ( $\epsilon_{\perp}^{(ox)}=10$ and $V_D=V_S=0$ V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|     | (c) Heatmap of SS as a function of $\epsilon_\perp^{(\mathrm{ox})}$ and $\epsilon_\parallel^{(\mathrm{ox})}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33  |

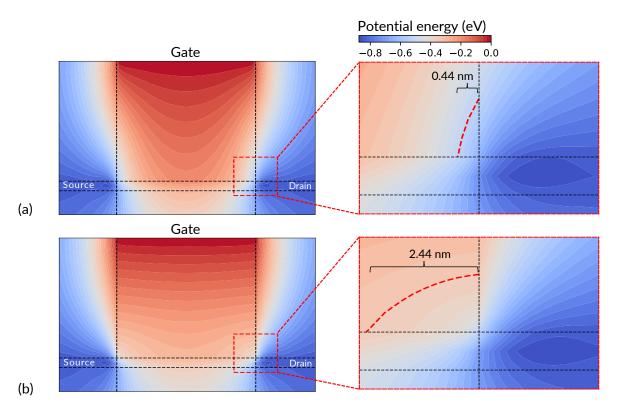

| 4.3 | Contour plots showing the potential energy in devices with anisotropic gate oxides for (a) $\epsilon_{\parallel}^{(ox)} = 2$ and (b) $\epsilon_{\parallel}^{(ox)} = 50$ . The plots on the right show the potential energy contour lines of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|     | the region around the channel/drain interface enclosed in the red dashed box                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 34  |

| 4.4 | (a) Heat map showing SS as a function of the permittivities of the spacer, $\epsilon_{\perp}^{(sp)}$ and $\epsilon_{\parallel}^{(sp)}$ (with $\epsilon_{\parallel}^{(ox)} = \epsilon_{\perp}^{(ox)} = 10$ ). Conduction band profiles of devices at $V_G = -0.5$ and 0.5 V ( $V_D = V_S = 0$ V) (b) for various $\epsilon_{\parallel}^{(sp)}$ (with $\epsilon_{\perp}^{(sp)} = \epsilon_{\parallel}^{(ox)} = \epsilon_{\perp}^{(ox)} = 10$ ) and (c) for various $\epsilon_{\perp}^{(sp)}$ (with $\epsilon_{\parallel}^{(sp)} = \epsilon_{\parallel}^{(ox)} = \epsilon_{\perp}^{(ox)} = 10$ ). The inset shows a close-up of the region towards the top of the barriers enclosed by a red dashed rectangle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35  |

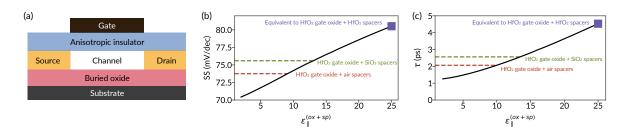

| 4.5 | (a) Revised MOSFET architecture where the gate insulator and spacers are replaced by a single anisotropic insulator. (b) SS and (c) $\tau$ as a function of $\epsilon_{\parallel}^{(\text{ox+sp})}$ (with $\epsilon_{\perp}^{(\text{ox+sp})}$ = 25) for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2 ( |

| , , | device architecture shown in (a).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36  |

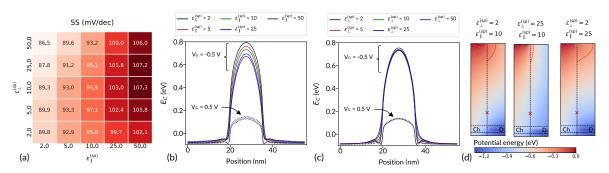

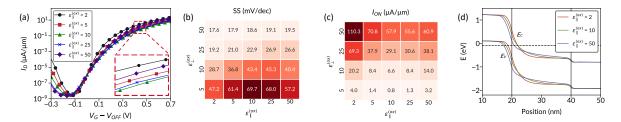

| 4.6 | (a) $I_D$ - $V_G$ characteristics of TFETs while varying $\epsilon_{\parallel}^{(\rm ox)}$ (with $\epsilon_{\perp}^{(\rm ox)}$ = 10). Inset: a close-up of the area enclosed by the red dashed rectangle. Heat maps showing (b) SS and (c) $I_{\rm on}$ as a function of $\epsilon_{\perp}^{(\rm ox)}$ and $\epsilon_{\parallel}^{(\rm ox)}$ for TFETs. (d) Band profiles for TFETs with various $\epsilon_{\parallel}^{(\rm ox)}$ (with $\epsilon_{\perp}^{(\rm ox)}$ = 10) at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|     | $V_G pprox V_{ON}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37  |

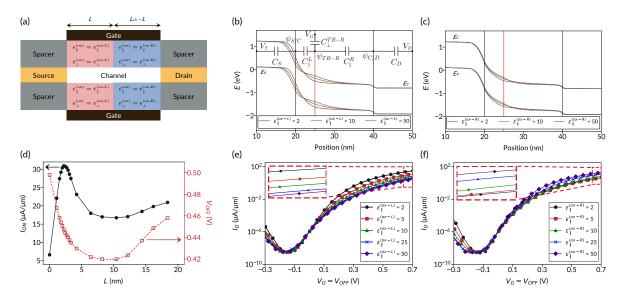

| 4.7 | (a) Hetero-gate dielectric architecture that allows for the permittivities of the left and right portions of the gate insulator to be varied separately. (b) Conduction and valence band profiles for various $\epsilon_{\parallel}^{(\text{ox-L})}$ ( $V_G \approx V_{ON}$ , $\epsilon_{\perp}^{(\text{ox-L})} = \epsilon_{\parallel}^{(\text{ox-R})} = \epsilon_{\perp}^{(\text{ox-R})} = 10$ ). (c) The same, for various $\epsilon_{\parallel}^{(\text{ox-R})}$ (while holding $\epsilon_{\perp}^{(\text{ox-R})} = \epsilon_{\parallel}^{(\text{ox-L})} = \epsilon_{\perp}^{(\text{ox-L})} = 10$ ). (d) $I_{\text{on}}$ and $V_{OFF}$ as functions of $L$ for a device with $\epsilon_{\parallel}^{(\text{ox-L})} = 2$ , $\epsilon_{\parallel}^{(\text{ox-R})} = 10$ , and $\epsilon_{\perp}^{(\text{ox-L})} = \epsilon_{\perp}^{(\text{ox-R})} = 10$ . $I_D$ - $V_G$ characteristics for devices with $L = 2.2$ nm for (e) various $\epsilon_{\parallel}^{(\text{ox-L})}$ (while holding $\epsilon_{\perp}^{(\text{ox-L})} = \epsilon_{\parallel}^{(\text{ox-R})} = \epsilon_{\perp}^{(\text{ox-R})} = 10$ ) and (f) various $\epsilon_{\parallel}^{(\text{ox-R})}$ (while holding $\epsilon_{\perp}^{(\text{ox-R})} = \epsilon_{\parallel}^{(\text{ox-L})} = \epsilon_{\parallel}^{(\text{ox-L})} = 10$ ). | 40  |

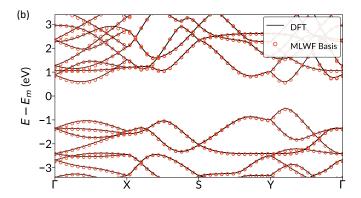

| 5.1 | (a) Structure of MOSFETs. (b) Band structure of the GeSe supercell as computed by DFT and after conversion to an MLWF basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 45  |

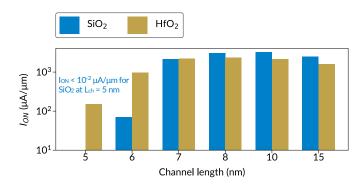

| 5.2 | $I_{\rm on}$ at $I_{\rm off}$ = $10^{-4}$ $\mu$ A/ $\mu$ m for MOSFETs with SiO <sub>2</sub> and HfO <sub>2</sub> gate oxides at various $L_{ch}$ 's, where EOT is varied such that the ratio $L_{ch}$ /EOT is held constant to ensure similar levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|     | of electrostatic control across $L_{ij}$ 's.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46  |

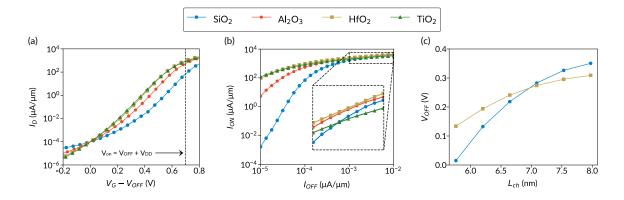

| 5.3 | (a) $I_D$ - $V_G$ curves at $I_{\text{off}} = 10^{-4} \mu\text{A}/\mu\text{m}$ and (b) $I_{\text{on}}$ vs. $I_{\text{off}}$ curves for MOSFETs with |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | $L_{ch}$ = 6 nm and various gate oxides, where oxide thickness is varied to maintain                                                                |    |

|     | EOT = 0.5 nm. (c) $V_{OFF}$ as a function of $L_{ch}$ for SiO <sub>2</sub> -and HfO <sub>2</sub> -based MOSFETs                                     | 47 |

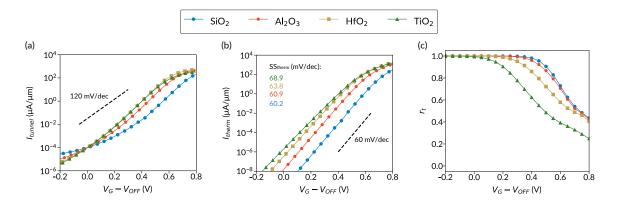

| 5.4 | (a) Tunneling and (b) thermionic components of the $I_D$ - $V_G$ curves plotted in Fig. 5.3(a).                                                     |    |

|     | (c) The ratio of tunneling current to total drain current $r_t$ as a function of $V_G - V_{OFF}$ for                                                |    |

|     | MOSFETs with various gate oxides.                                                                                                                   | 48 |

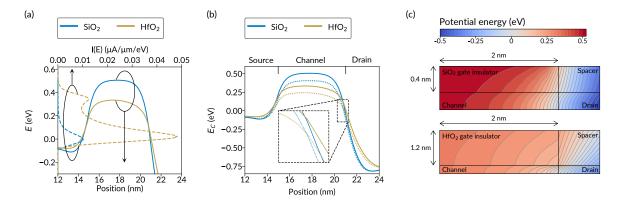

| 5.5 | (a) $E_C$ profiles and current spectra $I(E)$ for MOSFETs with SiO <sub>2</sub> and HfO <sub>2</sub> gate oxides                                    |    |

|     | at $V_G - V_{OFF} = 0.25$ V. <b>(b)</b> $E_C$ for MOSFETs with SiO <sub>2</sub> and HfO <sub>2</sub> gate oxides at                                 |    |

|     | $V_G - V_{OFF}$ = 0.25 V and $V_G - V_{OFF}$ = 0.35 V. (c) Contour plots of the potential energy                                                    |    |

|     | near the channel/drain interface for an SiO <sub>2</sub> -based MOSFET (top) and an HfO <sub>2</sub> -based                                         |    |

|     | MOSFET (bottom), where $L_{ch}$ = 6 nm, EOT = 0.5 nm, and $V_G - V_{OFF}$ = 0.25 V                                                                  | 49 |

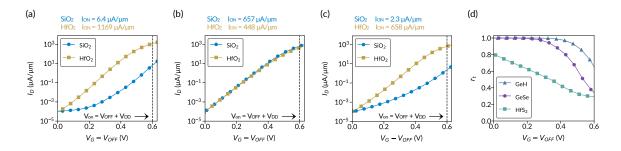

| 5.6 | $I_D$ - $V_G$ curves for MOSFETs that use SiO <sub>2</sub> and HfO <sub>2</sub> gate insulators and (a) GeSe, (b) HfS <sub>2</sub> ,                |    |

|     | and (c) GeH as the semiconductor. $L_{ch}$ = 6 nm for (a) and (b) and 7 nm for (c), and                                                             |    |

|     | EOT = 0.5 nm in (a) and (b) and 0.583 nm in (c). (d) $r_t$ as a function of $V_G - V_{OFF}$                                                         |    |

|     | for MOSFETs where SiO <sub>2</sub> serves as the gate insulator and GeSe, HfS <sub>2</sub> , and GeH serve as                                       |    |

|     | semiconductors.                                                                                                                                     | 51 |

# List of Tables

| 4.1 | Reported permittivities of sample anisotropic insulators | 30 |

|-----|----------------------------------------------------------|----|

| 4.1 | Reported permittivities of sample amsotropic misurators  |    |

S: Look! [Points to the volcano.] Can your fortune telling explain that?

Cuts to shot of the volcano, smoke rising from the top in great plumes.

M: [Amused.] Can your science explain why it rains?

S: [Turns to him; yells angrily.] Yes! Yes, it can!

# 1 Introduction

# 1.1 Scaling of Field-Effect Transistors

The advancement of modern computational technologies has been driven largely by the continued miniaturization, or *scaling*, of the metal-oxide-semiconductor field-effect transistor (MOSFET). The motivation behind miniturization is straightforward: the smaller MOSFETs are, the more we can put on a single computer chip. Over the last 60 years, the lengths of MOSFETs have decreased exponentially, with modern computer processors achieving billions of transistors on a single 1 cm<sup>2</sup> chip. However, MOSFETs that comprise modern computer chips have channel lengths of around 10 nm, and scaling devices beyond these lengths poses immense challenges, both in terms of device design and fabrication. Consequently, the scaling of silicon-based MOSFETs over the last decade has been achieved mostly by decreasing the effective footprint of their interconnects rather than by continuing to decrease their physical channel lengths.

Despite these challenges, the continued scaling of FETs' channels remains a topic of great interest in both academia and industry. FETs need to be extremely well optimized from nearly every perspective to scale them into the sub-10 nm regime, requiring researchers to derive models that capture the unique behaviors of nanoscale FETs (which often different significantly compared to the behaviors of their  $\mu$ m scale counterparts) and to engineer novel design strategies to optimize sub-10 nm FETs. In particular, the electrostatic integrity of devices tends to become compromised as devices are scaled to short channel lengths, making the electrostatic engineering of nanoscale FETs an essential step in realizing the sub-10 nm regime.

Therefore, the goals of the work presented in this thesis are (i) to provide a deeper understanding of the electrostatic operation of nanoscale FETs and (ii) to present novel design strategies for enhancing nanoscale FETs' electrostatic integrity. This thesis is organized as follows: firstly, I discuss why electrostatic integrity is essential for any high-performing FET and explain why scaling devices to extremely short channel lengths compromises their electrostatic integrity. Next, I review previous literature to present the current state-of-the-art in electrostatic engineering to contextualize the work of this thesis. Finally, I describe the methodology I used to explore the electrostatic operation of nanoscale FETs before presenting three new advances in electrostatic engineering in the body of this thesis.

# 1.2 ELECTROSTATIC AND QUANTUM MECHANICAL SHORT-CHANNEL EFFECTS

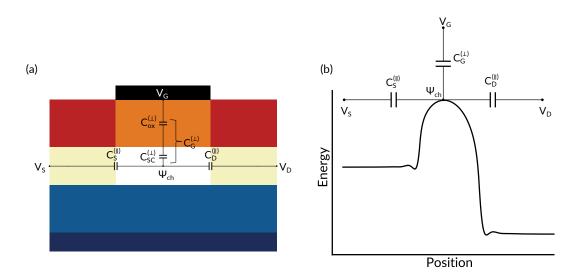

The characteristic behaviours of MOSFETs can be understood using a capacitance network where the source, drain, and gate electrodes are coupled to a point in MOSFET's channel through three capacitors:  $C_S^{(\parallel)}$ ,  $C_D^{(\parallel)}$ ,

and  $C_G^{(\perp)}$ . Here, I use a superscripted parallel (||) or perpendicular ( $\perp$ ) sign to denote that the the capacitor acts in the in-plane or out-of-plane direction, respectively.  $C_S^{(\parallel)}$  and  $C_D^{(\parallel)}$  couple the channel to the source and drain, respectively, and arise due to lateral charge separation within an FET's semiconductor. The gate capacitance,  $C_G^{(\perp)}$ , couples the channel to the gate electrode through the semiconductor and insulator. The capacitances offered by the semiconductor and insulator in the out-of-plane direction are denoted by  $C_{SC}^{(\perp)}$  and  $C_{\infty}^{(\perp)}$ , respectively, and the overall  $C_G^{(\perp)}$  is the series capacitance of  $C_{\infty}^{(\perp)}$  and  $C_{SC}^{(\perp)}$ . The locations of these capacitors in an FET are shown schematically in Fig. 1.1(a), where  $V_S$ ,  $V_D$ ,  $V_G$ , and  $\psi_{ch}$  are the potentials of the source, drain, gate, and a point in the channel, respectively. While we could assign  $\psi_{ch}$  to be the potential at any point in the channel, it is most useful to define  $\psi_{ch}$  at the point in which the potential in the channel is greatest. Consequently, we assign  $\psi_{ch}$  to be located in the center of the channel so that it is identical to the height of the potential barrier, as illustrated schematically in Fig. 1.1(b).

We can already begin to understand the operating principles of a MOSFET using this simplified model. If we increase  $V_G$  by some amount  $\Delta V_G$  then  $\psi_{ch}$  will likewise change by some amount  $\Delta \psi_{ch}$ , thereby inducing a change in the drain current,  $I_D$ . Ideally, a MOSFET's  $I_D$  should be as responsive to changes in  $V_G$  as possible. In other words, we generally wish to maximize  $\partial I_D/\partial V_G$ , as this allows us to maximize the strength of our signal, which is practical for several reasons: it allows us to maximize the frequency at which we can switch MOSFETs off and on [2], it minimizes MOSFETs' power consumptions [3], and it boosts the sensitivity of MOSFET-based sensors [4].

In the most ideal case, the potential of the channel will respond perfectly to a change in the gate electrode, i.e.  $\Delta \psi_{ch} = \Delta V_G$ . However, from the top-of-the-barrier capacitor model shown in Fig. 1.1, we may note that

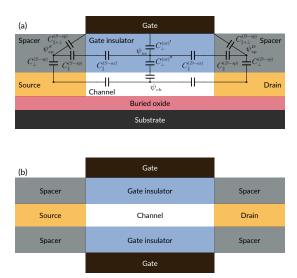

Figure 1.1: (a) A diagram showing how key potentials in an FET are coupled through various capacitors. Adapted from [1], © 2020 IEEE. (b) A top-of-the-barrier model where the conduction band edge is qualitatively plotted as a function of the lateral position in the device. Here, the capacitors from (a) are used to illustrate that the top of the barrier is taken as  $\psi_{ch}$ , which is in turn coupled to the source, drain, and gate electrodes. Adapted from [2].

$V_S$  and  $V_D$  also influence  $\psi_{ch}$ . By applying a capacitive voltage divider, we can estimate the influence of each electrode on  $\psi_{ch}$ :

$$\psi_{ch}(C_S^{(\parallel)} + C_D^{(\parallel)} + C_G^{(\perp)}) = C_S^{(\parallel)} V_S + C_D^{(\parallel)} V_D + V_G C_G^{(\perp)}$$

(1.1)

$$\psi_{ch} = \frac{C_S^{(\parallel)} V_S + C_D^{(\parallel)} V_D + V_G C_G^{(\perp)}}{C_S^{(\parallel)} + C_D^{(\parallel)} + C_G^{(\perp)}}$$

(1.2)

$$\frac{\partial \psi_{ch}}{\partial V_G} = \frac{C_G^{(\perp)}}{C_S^{(\parallel)} + C_D^{(\parallel)} + C_G^{(\perp)}} \tag{1.3}$$

$$\frac{\partial \psi_{ch}}{\partial V_S} = \frac{C_S^{(\parallel)}}{C_S^{(\parallel)} + C_D^{(\parallel)} + C_G^{(\perp)}} \tag{1.4}$$

$$\frac{\partial \psi_{ch}}{\partial V_D} = \frac{C_D^{(\parallel)}}{C_S^{(\parallel)} + C_D^{(\parallel)} + C_G^{(\perp)}} \tag{1.5}$$

From Equation (1.3),  $\partial \psi_{ch}/\partial V_G$  achieves its maximum value of 1 (corresponding to the ideal case of  $\Delta V_G = \Delta \psi_{ch}$ ) when  $C_G^{(\perp)} >> (C_S^{(\parallel)} + C_D^{(\parallel)})$ . In this case,  $\partial \psi_{ch}/\partial V_S \approx 0$  and  $\partial \psi_{ch}/\partial V_D \approx 0$  from Equation (1.4) and Equation (1.5), indicating that a change in the source/drain voltage will have little effect on the channel's potential. In this case, the gate has perfect control over the channel's potential, whereas the channel's potential is entirely unresponsive to changes in the potentials of the source and drain. Such a device is said to have good gate control. However, if  $C_S^{(\parallel)}$  and/or  $C_D^{(\parallel)}$  are on the same order (or greater than)  $C_G^{(\perp)}$ , then  $\partial \psi_{ch}/\partial V_G$  will be considerably less than 1 and  $\partial \psi_{ch}/\partial V_S$  and  $\partial \psi_{ch}/\partial V_D$  will both be non-zero. Such a device is said to have weak gate control and will generally offer poor performance for practical applications. Consequently, device engineers typically seek to maximize  $C_G^{(\perp)}$  while minimizing  $C_S^{(\parallel)}$  and  $C_D^{(\parallel)}$  to maximize an FET's performance. At the same time, however, we also wish to minimize the physical dimensions of MOSFETs to fit as many devices as possible on a single computer chip. These two design considerations conflict: since  $C_S^{(\parallel)}$  and  $C_D^{(\parallel)}$  are geometric capacitances, they are inversely proportional to the channel length  $L_{ch}$  and become larger as the length of MOSFETs are scaled down. In other words, the drain and source electrodes naturally exert greater influence on the channel's potential as the lengths of devices decreases, worsening device performance [2].

The influence of the source and drain's electric fields on the channel's potential gives rise to a number of *short-channel effects* that burden nanoscale FETs. These effects are pervasive among scaled devices and can cause FETs to have reduced ON currents, slower switching speeds, and in extreme cases can lead to leakage currents that prevent FETs from ever entering the OFF state. Therefore, it is extremely important for device engineers to take electrostatic integrity into account when designing nanoscale FETs to ensure that FETs remain able to meet key performance metrics even at the short channel lengths required for practical device applications.

A device's electrostatic integrity is often quantified by the scaling length  $\lambda$ .  $\lambda$  represents the distance that electric field lines penetrate laterally from a device's drain into its channel and is given by Equation (1.6) [5],

$$\lambda = \sqrt{\frac{\epsilon^{(SC)}}{\epsilon_{ox}} t_{ox} t_{ch}},\tag{1.6}$$

where  $\epsilon_{ox}$  is the permittivity of the MOSFET's gate insulator,  $\epsilon^{(SC)}$  is the permittivity of the semiconductor,  $t_{ox}$  is the thickness of the semiconductor. A device with  $C_G^{(\perp)}/C_D^{(\parallel)} \geq 10$  typically exhibits strong electrostatic control, whereas devices tend to suffer from short channel effects when  $C_G^{(\perp)}/C_D^{(\parallel)} < 10$ . It should be noted, however, that Equation (1.6) is only an estimate for  $\lambda$ , and that  $\lambda$  is difficult to quantify precisely, especially for short-channel devices. However, Equation (1.6) still offers a reasonable estimate for  $\lambda$  and is still regularly applied to describe the electrostatic integrity of modern FETs [6].

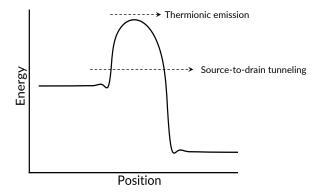

Figure 1.2: A schematic illustration showing the difference between thermionic emission (where high-energy electrons contribute to  $I_D$  by traveling over the potential barrier) and source-to-drain tunneling (where lower-energy electrons tunnel through the potential barrier).

Alongside electrostatic short-channel effects, quantum mechanical short-channel effects can severely degrade the performance of ultra-scaled FETs. In particular, MOSFETs with sub-10 nm channel lengths tend to suffer from source-to-drain tunneling, a quantum mechanical short-channel effect where electrons with energies below the height of the potential barrier tunnel through the barrier to contribute to the total drain current, as illustrated in Fig. 1.2. A MOSFET's source-to-drain tunneling current grows exponentially as the MOSFET's channel length decreases, and in severe cases these tunneling currents can prevent MOSFETs from entering the OFF-state, even at extremely negative gate biases [7].

# 1.3 RECENT ADVANCES IN THE ELECTROSTATIC ENGINEERING OF FIELD-EFFECT TRANSISTORS

## 1.3.1 Electrostatics of Semiconductors

Decreasing the physical thickness of a MOSFET's semiconductor is one of the most common approaches for increasing an FET's electrostatic integrity. Thick semiconductors exhibit relatively poor electrostatic control because the physical thickness of the semiconductor itself acts as a capacitor that weakens the coupling between the bottom of the semiconductor (i.e., the portion of the semiconductor opposite to the gate electrode). This behavior is reflected in Equation (1.3), as  $C_G^{(\perp)}$  is the series capacitance of  $C_{\rm ox}^{(\perp)}$  and  $C_{\rm SC}^{(\perp)}$ , where  $C_{\rm SC}^{(\perp)} \propto \frac{1}{t_{\rm SC}}$ . This behavior is also reflected in Equation (1.6), where  $\lambda$  decreases as  $t_{ch}$  decreases, thereby decreasing  $C_G^{(\perp)}/C_D^{(\parallel)}$  and improving the device's electrostatic integrity. However, mobilities of electrons and holes of common semiconductors (e.g., silicon, gallium arsenide) decrease rapidly as the semiconductor's thickness approaches nanometer length scales, posing a practical limit for further decreasing  $t_{ch}$ . This limitation has one of the main reasons why commercial silicon-based MOSFETs have not been scaled to channel lengths less than 10 nm.

New possibilities in scaled devices emerged in 2010 when two-dimensional (2-D) MoS<sub>2</sub> was found to be a direct band gap semiconductor that exhibits reasonable electron and hole mobilities even at monolayer thicknesses [8]. This generated a surge of research interest within the field of two-dimensional semiconductors and has since lead to the discovery of over 100 2-D semiconductors have been studied for use in FETs in either a theoretical (e.g., using density functional theory coupled with quantum transport simulations) or experimental capacity [9]. While two-dimensional semiconductors still face significant challenges before they can be implemented in practical FETs, such as improving their ambient stability, improving their contact resistances, and doping them without introducing unacceptable levels of strain, they remain the most promising class of materials for enabling scaled FETs with strong electrostatic integrities.

Aside from engineering the thickness of semiconductors, several recent works have focused instead on the semiconductor's permittivity, which is another key parameter for determining the capacitances contained within an FET's semiconductor (labelled in Fig. 1.1). Generally speaking, the electrostatic coupling offered by the semiconductor tends to deteriorate device performance by increasing the drain's influence over the channel. This is also reflected in Equation (1.6), where  $\lambda$  increases as the semiconductor's permittivity increases. Recently, reports have emerged that suggest that due to a phenomenon termed *permittivity reduction*, the permittivity of some semiconductors may not be constant throughout the material. For example, polarized bonds in thin slabs silicon cause the material's local permittivity to decrease, leading to a non-uniform permittivity that is small at the surface and that increases towards the bulk value of silicon (12 $\epsilon_0$ ) in the center of the slab. In 2019, Chen et al. [10] investigated how permittivity reduction could impact the performance of ultra-scaled MOSFETs by using non-equilibrium Green's function simulations to simulate the performance of MOSFETs with differing dielectric profiles. As a test case, they first investigated silicon-based MOSFETs where the dielectric constant of silicon was varied from 4 to 12. As shown in

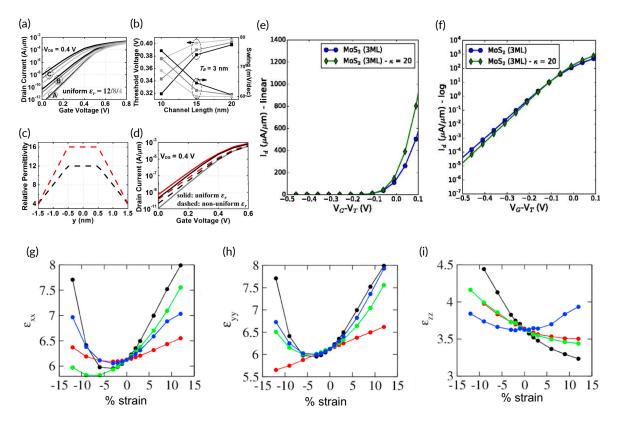

Figure 1.3: **(a)** Simulated transfer characteristics for MOSFETs where the semiconductor's dielectric constant was varied between 4 and 4, and whose channel lengths/semiconductor thicknesses are 20/3 nm (group A), 10/3 nm (group B), and 10/4 nm (group C). **(b)** Threshold voltage and subthreshold swing as a function of channel length for MOSFETs whose semiconductor's dielectric constant is varied from 4 to 12 and whose semiconductor's thickness is fixed at 3 nm. **(c)** Various semiconductor dielectric constant profiles used for subsequent simulations. **(d)** Simulated transfer characteristics for MOSFETs with the profiles shown in (c) (dashed red and black lines) and for MOSFETs with constant semiconductor dielectric constants of 16 (solid red line), 12 (solid black line) and 4 (solid gray line). **(e)** and logarithmic **(f)** transfer characteristics for 3-layer MoS<sub>2</sub>-based MOSFETs with a base dielectric constant of 10 and an artificial dielectric constant of 20. In plane **(g,h)** and out-of-plane **(i)** permittivities of MoS<sub>2</sub> as a function of strain, where black, blue, red, and green lines correspond to isotropic, shear (xy), uniaxial (x), and uniaxial (y) strains, respectively. (a – d) are taken from ref. [10] and are © 2019 IEEE.<sup>a</sup>

(e) and (f) are taken from ref. [11] and are © 2016 Elsevier.<sup>c</sup>

Fig. 1.3(a) and Fig. 1.3(b), the MOSFETs' OFF-currents and subthreshold swings were both minimized when the semicondutor's permittivity was set to small values, whereas the threshold voltage increased as the dielectric constant increased as a result of drain-induced barrier lowering. Next, they simulated the

<sup>&</sup>lt;sup>a</sup> See copyright letter provided at the end of this thesis.

<sup>&</sup>lt;sup>b</sup> Reprinted from Journal of Applied Physics, 121, A. Lu et al., On the electrostatic control achieved in transistors based on multilayered MoS2: A first-principles study, 044505, 2017, with the permission of AIP Publishing.

<sup>&</sup>lt;sup>c</sup> Reprinted from Solid State Communications, 227, A. Maniadaki et al., Strain engineering of electronic properties of transition metal dichalcogenide monolayers, 33 – 39, 2016, Copyright 2016, with permission from Elsevier.

#### 1 Introduction

performance of MOSFETs where the permittivity of silicon followed the functions shown in Fig. 1.3(c), where the *y* direction corresponds to the out-of-plane direction (i.e., perpendicular to the direction in which current is carried). As shown in Fig. 1.3(d), MOSFETs whose semiconductors followed these dielectric profiles had lower subthreshold swings and OFF-currents compared to MOSFETs whose semiconductors' permittivities were set to the peak values in the profiles (i.e. 16 for the solid red line, 12 for the solid black line), but could not outperform a semiconductor whose permittivity was set to the minimum value in the dielectric profile (i.e. 4 for the grey line).

Similarly, two-dimensional layered semiconductors, such as  $MoS_2$  and black phosphorus, exhibit thickness-dependent permittivities where both their in-plane and out-of-plane permittivities decrease from their bulk value as the semiconductor's thickness decreases. This in turn affects source/channel and drain/channel couplings and modifies electrostatic shielding effects between subsequent layers. In 2017, Lu et al. demonstrated that electrostatic shielding between layers of two-dimensional semiconductors could greatly impact the performance of two-dimensional semiconductors by simulating the transfer characteristics of  $MoS_2$ -based MOSFETs with varying numbers of layers. Interestingly, they observed that the ON current increased and subthreshold swing decreased when the semiconductor's permittivity increased from  $\sim$ 10 to 20 [Figs. 1.3(e,f)], which is in disagreement with scaling trends for the semiconductor's permittivity predicted by Equation (1.6). However, the reason for this discrepancy was not commented on in the original publication, but will be investigated in greater detail in Chapter 3 of this thesis.

Although a material's permittivity is typically thought of as a fixed constant, in 2016 Maniadaki et al. [12] demonstrated that a semiconductor's in-plane and out-of-plane permittivities could be tuned by straining the material's atomic lattice. For example, the in-plane permittivity of  $MoS_2$  could be tuned between  $\sim$ 5.5 and 8 by applying compressive/tensile strains [Figs. 1.3(g),(h)], whereas the out-of-plane permittivity of  $MoS_2$  could be tuned between  $\approx$  3.2 and 4.5 [Fig. 1.3(i)]. As strain engineering is regularly employed to tune other essential electronic properties of semiconductors, such as mobility and band gap [13], the ability to simultaneously tune dielectric constants through strain engineering could allow promising semiconductors to be further optimized post-fabrication.

#### 1.3.2 Electrostatics of Insulators

The most straightforward approach to enhance a MOSFET's electrostatic integrity is by increasing the capacitance offered by its gate insulator. As  $C_{\rm ox}^{(\perp)} \propto \epsilon_{ox}/t_{ox}$ , this may be achieved by decreasing the insulator's physical thickness and/or by using insulators with higher permittivities, called *high-\kappa* insulators. To facilitate the comparisons of various gate oxides, device designers often discuss gate insulators in terms of their equivalent oxide thicknesses (EOTs), calculated as:

$$EOT = \frac{\epsilon^{(SiO_2)}}{\epsilon_{ox}} t_{ox} \tag{1.7}$$

where  $\epsilon^{(SiO_2)}$  is the permittivity of silicon dioxide (3.9). The EOT quantifies the capacitance of an insulator by describing how thick a layer of silicon dioxide would have to be to provide an equivalent gate capacitance. For instance, a hypothetical insulator with a permittivity of 39 and a physical thickness of 10 nm has an EOT of 1 nm, which means it offers the same gate capacitance as 1 nm of silicon dioxide. To quantify how EOT affects a MOSFET's electrostatic integrity, we can substitute Equation (1.7) into Equation (1.6) to obtain

$$\lambda = \sqrt{\frac{\epsilon^{(SC)}}{\epsilon^{(SiO_2)}}} t_{ch} EOT. \tag{1.8}$$

Let us consider a hypothetical MOSFET made with a semiconductor with  $\epsilon^{(SC)}=10$  (a typical value for semiconductors),  $t_{ch}=1$  nm, and with a target  $L_{ch}=10$  nm. To achieve strong electrostatic control, we require that  $\lambda\approx 1$  nm, which in turn requires the gate insulator to offer an EOT of 0.39 nm. Although silicon dioxide can indeed be grown at physical thicknesses of <1 nm, such a small EOT cannot practically be obtained using silicon dioxide (or other insulators with low permittivities) because electrons and holes can readily tunnel from the gate electrode to the semiconductor when the insulator is made too thin, which would prevent MOSFETs from ever entering the OFF-state. Consequently, researchers have instead turned towards implementing high- $\kappa$  insulators in MOSFETs to achieve small EOTs while still maintaining large physical thicknesses to suppress gate leakage.

However, implementing high- $\kappa$  insulators into FETs creates several drawbacks. Firstly, the interfaces between semiconductors and high- $\kappa$  insulators tend to contain large numbers of interfacial defects, such as trapped charges and recombination sites, which negatively impact device performance. This is particularly problematic for 2-D semiconductors, as their crystal structures do not align well with those of conventional insulators. Consequently, the search for high- $\kappa$  insulators compatible with 2-D semiconductors has been identified as a key step that must be fulfilled before 2-D semiconductor-based FETs can be realized for most practical applications [14].

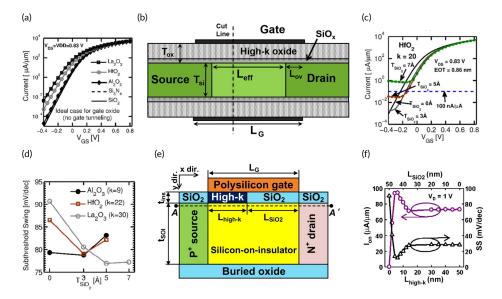

Another notable problem with high- $\kappa$  insulators is that while their high permittivities couple the channel more strongly to the gate, they also tend to enhance lateral fringing fields that run horizontally through FETs. These fringing fields negatively contribute to circuit-level performance metrics of MOSFETs (e.g. by increasing FETs' intrinsic delays) and also deteriorate their ideal source-to-drain transfer characteristics by relinquishing some of the gate's control over the center of the channel. Consequently, while high- $\kappa$  insulators outperform low- $\kappa$  insulators at a given physical thickness, they tend to offer worse performance than low- $\kappa$  insulators at the same EOTs by increasing both SS and OFF-currents, as shown in Fig. 1.4(a). This phenomenon, referred to as *fringe induced barrier lowering* (FIBL), is well known and has been studied since the early 2000s.

To circumvent FIBL while still ensuring that oxides could retain physical thicknesses large enough to prevent gate leakage, Salmani-Jelodar et al. proposed using the MOSFET structure in Fig. 1.4(b), where a thin (< 1 nm) layer of SiO<sub>2</sub> served as a buffering layer and a larger layer composed of a targeted high- $\kappa$  gate

Figure 1.4: (a) Transfer characteristics of a MOSFET with various gate insulators, each of whose EOTs are fixed at 0.83 nm. Insulators are listed in the legend in order of decreasing permittivity. (b) MOSFET structure to reduce FIBL while maintaining a large physical thickness to prevent source-to-drain tunneling. (c) Transfer characteristics of an La<sub>2</sub>O<sub>3</sub>-based MOSFET with buffer layers of varying thickness, where the EOT of each gate stack is held constant at 0.86 nm. (d) SS as a function of buffer layer thickness for 3 high-κ insulators. (e) Hetero-gate-dielectric MOSFET architecture used to enhance TFETs. (f) I<sub>on</sub> and SS as functions of geometric parameters as labeled in (e).

- (a) (d) were taken from ref. [15] and are © 2016 IEEE.

- (e) (f) were taken from ref. [16] and are © 2010 IEEE.

dielectric served as the principal gate insulator. For example, Fig. 1.4 (c) shows the transfer characteristics of the architecture in Fig. 1.4(b) with an La<sub>2</sub>O<sub>3</sub> gate insulator ( $\epsilon_{ox}$  = 30) for buffer layers of varying thickness, where EOT was held constant at 0.86 nm for every configuration. The MOSFET with no buffering layer [i.e. the thickness of SiO<sub>2</sub> ( $t_{\rm SiO_2}$ ) = 0] exhibited an OFF-state current of  $10^{-2}$   $\mu$ A/ $\mu$ m at  $V_G$  = -0.4 V, whereas the OFF current decreased when  $t_{\rm SiO_2}$  was set to 3 or 5 Å. However, at 7 Å, the insulator's physical thickness became too small to prevent gate leakage, leading to an extremely high SS in the OFF-state. Similarly, the authors found that the SS's of MOSFETs using other gate insulators could be improved using this buffering layer strategy [Fig. 1.4(d), also at a fixed EOT of 0.86 nm], thus presenting a unique way to maintain large physical oxide thicknesses while still mitigating FIBL.

Finally, recent works have sought to optimize the electrostatics of tunnel field-effect transistors (TFETs, a type of FET whose current is driven by source-to-drain tunneling rather than thermionic emission) using hetero-gate-dielectrics, which are gate insulators that are composed of two or more distinct lateral regions with differing permittivities. Hetero-gate-dielectrics were first proposed by Choi and Lee in 2010 [16], who demonstrated that the hetero-gate-dielectric architecture in Fig. 1.4(e) could improve both the SS's and ON-currents and TFETs. In this architecture, a low- $\kappa$  insulator, such as SiO<sub>2</sub>, spans most of the device, and a small high- $\kappa$  insulator, such as HfO<sub>2</sub>, is inserted between the source/channel interface and the center of the channel. The abrupt transition in the lateral dielectric constant induces a dip in both the valence band and

conduction band edges near the source side of the channel. Consequently, the tunneling distance is decreased when the device is in the ON-state, whereas the tunneling distance remains relatively unchanged when the device is in the OFF-state, leading to an improved current in the ON-state without compromising the SS, as shown in Fig. 1.4(f). Using this optimized architecture, the authors demonstrated that the TFET's ON-state current improved by 30% while SS decreased by 60%.

# 2 METHODOLOGY

# 2.1 Motivation for Simulating Nanoscale Field-Effect Transistors

In this thesis, I exclusively use computational methods to study the electrostatics of nanoscale FETs and to explore new strategies for engineering FETs' electrostatics. While an FETs' electrostatics can also be studied experimentally, simulation studies carry several distinct advantages that make them especially useful for this task. In particular, much of the work presented in the body of this thesis studies how varying the dielectric constants of various regions in FETs affects devices' transfer characteristics. This type of study is difficult to carry out experimentally because varying a region's dielectric constant by using different materials can result in experimental differences (e.g., processing conditions, interfacial defects), which may introduce confounding factors. Furthermore, intermediate results, such as an FET's electrostatic profile, conduction/valence band edge profiles, current spectra, and charge carrier densities, can be difficult to measure experimentally, though they are readily extracted from device simulations. Consequently, many innovations in electrostatic engineering reported in previous literature were initially studied through simulation methods before their subsequent experimental demonstration.

# 2.2 Non-Equilibrium Green's Function Simulations

The non-equilibrium Green's function (NEGF) method is a simulation method frequently used to model quantum transport in nanoscale materials and devices. The NEGF method is extremely popular because it is quantum mechanical and atomisticly rigorous and hence can accurately model devices with arbitrarily small dimensions. Other popular modeling techniques for semiconductor devices, such as the semi-classical drift diffusion model, fail to capture the quantum mechanical phenomena (e.g., electron wave interference and quantum mechanical tunneling) that influence nanoscale devices.

The NEGF method models quantum transport using Green's functions and the electrostatic potential using Poisson's equation. Green's functions calculate the spatial distribution of charge carriers as a function of the device's electrostatic potential, whereas Poisson's equation calculates the device's electrostatic potential as a function of the spatial distribution of charge carriers. The NEGF method therefore aims to find a self-consistent electrostatic potential and charge carrier distribution which simultaneously satisfy both sets of equations. Finally, once the density of charge carriers is known, the current flowing through the device may be easily calculated, as shown schematically in Fig. 2.1.

Figure 2.1: A flow chart illustrating the NEGF simulation method.

The work presented in this thesis focuses specifically on engineering the electrostatics of devices, which are modeled exclusively through Poisson's equation. Therefore, this chapter will briefly present the transport equations used in the NEGF method before discussing the modeling of Poisson's equation in detail.

# 2.2.1 Transport Equations

The basis for the NEGF formalism lies in the Green's function for Schrodinger's equation, given as:

$$G(E) = [(E + \delta i)I - H - q\psi - \Sigma_S - \Sigma_D]^{-1},$$

(2.1)

where E is energy,  $i=\sqrt{-1}$ ,  $\delta$  is an infinitesimally small positive number, H is a tight-binding (or tight-binding-like) Hamiltonian matrix that describes the electronic properties of the semiconductor, q is the elementary charge,  $\psi$  is the electrostatic potential, and  $\Sigma_B$  and  $\Sigma_D$  are the self-energies of the source and drain, respectively. We use Equation (2.1) to find the quantum mechanical electron and hole densities,  $G^n(E)$  and  $G^p(E)$ , as follows:

$$G^{n}(E) = G(E)\Sigma_{\alpha}^{in}G^{\dagger}(E), \qquad (2.2)$$

$$G^{p}(E) = G(E) \sum_{\alpha}^{out} G^{\dagger}(E), \tag{2.3}$$

where a superscripted dagger denotes the complex conjugate, and where  $\Sigma_{\alpha}^{in}$  and  $\Sigma_{\alpha}^{out}$  are referred to as the in-scattering and out-scattering functions, respectively. These functions are calculated using the self-energies of the source and drain as follows:

$$\Sigma_{\alpha}^{in} = i[\Sigma_S(E) - \Sigma_S^{\dagger}(E)]f(E), \tag{2.4}$$

$$\Sigma_{\alpha}^{out} = i[\Sigma_D(E) - \Sigma_D^{\dagger}(E)][1 - f(E)]. \tag{2.5}$$

Here, f(E) is the Fermi function, which describes the probably of an electron existing at a particular energy level:

$$f(E) = \left[1 + \exp(\frac{E - E_f}{k_B T})\right]^{-1},\tag{2.6}$$

where  $E_f$  is the fermi energy,  $k_B$  is the Boltzmann constant, and T is the temperature. Once the solutions to the above equations are known, we can find the density of electrons and holes ( $\rho_n$  and  $\rho_p$ ) simply by integrating across all available energies:

$$\rho_n(r) = 2 \int_{-\infty}^{\infty} \frac{dE}{2\pi} G^n(E), \qquad (2.7)$$

$$\rho_p(r) = 2 \int_{-\infty}^{\infty} \frac{dE}{2\pi} G^p(E). \tag{2.8}$$

And finally, we calculate the density of current flowing through the device as:

$$J_{\alpha} = \frac{2e}{\hbar} \int \frac{dE}{2\pi} \text{Tr} \Big[ \Sigma_s(E) [G^n(E) + G^p(E)] - \Gamma_{\alpha} G^n(E) \Big], \tag{2.9}$$

where Tr is the trace operator.

Equation (2.9) is the end-result of an NEGF simulation and only needs to be computed once we are certain that the charge carrier densities are properly satisfied. To obtain this self-consistent solution, we feed  $\rho_n(r)$  and  $\rho_p(r)$  into Poisson's equation to calculate the device's electrostatic potential, allowing us to resolve Equation (2.1). When these variables do not change significantly between successive iterations then we consider the equations to be satisfied self-consistently, and only then can we correctly calculate the device's current.

## 2.2.2 Poisson's Equation

Poisson's equation of electrostatics, or simply *Poisson's Equation*, is a cornerstone of electrostatics and is an essential component for our NEGF device simulations. The derivation of Poisson's equation is straightforward. We begin with the divergence form of Gauss's law in two dimensions:

$$\nabla \cdot D(x, z) = \rho(x, z) \tag{2.10}$$

where  $\nabla$  is the gradient operator, D is the displacement field,  $\rho$  is the electric charge density, and x and z are spatial coordinates. The displacement field is given by:

$$D(x, y, z) = \bar{\bar{\epsilon}}(x, z)E(x, z)$$

(2.11)