# TiO<sub>2</sub> and Biomaterials based Memristor Devices and

by

its In-Memory Computing Applications

Shubham Ranjan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2020

© Shubham Ranjan 2020

# Author's declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

As information technology is moving toward a big data era, the conventional Von Neumann architecture has shown limitation in performance. This is constrained by the large volume of data being continuously fetched and stored through input-output (IO) device, which not only adds performance penalty but power penalty as well. Therefore, it is necessary to bring processing unit as close as possible to memory for minimizing data transmission. Memristors provide dual functionalities of data storage and computing at the same location without data transmission, therefore is one of the most promising candidates for energy efficient in-memory computing. However, being stochastic in nature, variations in memristor device is one of the major challenges in its use towards in-memory computing. In this thesis, we demonstrate novel memristor devices with unique characteristics, which could facilitate reprogrammable application and high-density storage. Further, we demonstrate the applications of the fabricated memristor devices for in-memory computing, with a motive for less sensitive circuits towards variations in devices.

In the first device, TiO<sub>2</sub> and maple leaves (ML) are combined to form a functional layer (TiO<sub>2</sub>-ML) inside memristive devices, which demonstrate both the capacitive effect and the non-volatile storage capability. When the voltage increases from zero, the device firstly enters a capacitive-coupled memristive state at low voltage before switch to normal memristive state at a higher voltage. The existence of capacitive coupled and memristive behavior, modulated by programming voltage, forms a unique reprogrammable device. In the second device, formed by Al/TiO<sub>2</sub>-Graphene-DNA/Pt layers, high performance and stable intermediate multistate resistive switching behaviors have been achieved. Further, for in-memory computing, a highdensity memory and multibit parallel logic computations are realized based on the multistate resistive switching behaviors. This improves data storage capacity and performance up to 2× with respect to conventional single bit memristor devices when they are used to store binary data, without any compromise in accuracy. Further, we use Al/TiO<sub>2</sub>/Al memristor device, to demonstrate a variation tolerant analogdigital-hybrid matrix multiplication circuit, for high precision and efficient in-memory computing. It was observed that, in comparison to conventional analog based matrix multiplication scheme using memristor, the proposed scheme improves the average accuracy up to 16.35%, with sacrificing power, performance and area up to 18.5%, 8.2% and 3.2% respectively. This work provides a new horizon on the memristor devices and will improve the understanding of engineering device and circuits for efficient and variation tolerant in-memory computing.

# **Acknowledgements**

This dissertation would have been impossible without the guidance and encouragements of several people. I would like to express my deepest gratitude to my supervisors, Professor Lan Wei and Professor Norman Zhou, for their continuous support and valuable insights throughout my master's at University of Waterloo.

I would like to thank the rest of my thesis committee: Professor Yimin Wu and Professor Guoxing Miao, for their insightful comments and encouragement.

I would also like to thank Professor Yimin Wu for providing valuable suggestions and directions on improvement of device and paper writing.

I would also like to extend my appreciation to my lab colleagues Dr. Bai Sun, Dr. Ming Xiao, Tao Guo and Zongxian Yang, who helped me a lot during my course of research on memristor. Dr. Ming Xiao and Zongxian Yang helped me during the initial phase to understand the working and fabrication of memristor. Dr. Bai Sun helped me endlessly for last two years to develop memristor based on biomaterials and have continuously motivated me to explore more about its applications.

Last but not the least, I would also like to thank my family and friends who had supported me unconditionally throughout my life.

# **Table of Contents**

| AUTHOR'S DECLARATION                                                                          | ii  |

|-----------------------------------------------------------------------------------------------|-----|

| Abstract                                                                                      | iii |

| Acknowledgements                                                                              | iv  |

| List of Figures.                                                                              | vii |

| Chapter 1 Introduction.                                                                       | 1   |

| 1.1 In-Memory Computing                                                                       | 1   |

| 1.1.1 Need for New Computing Paradigm                                                         | 1   |

| 1.1.2 In-Memory Computing                                                                     | 3   |

| 1.2 Memristor                                                                                 | 4   |

| 1.3 Scope of Research                                                                         | 6   |

| 1.4 Organization.                                                                             | 6   |

| Chapter 2 Related work                                                                        | 8   |

| 2.1 Introduction                                                                              | 8   |

| 2.2 Development of Memristor Device                                                           | 8   |

| 2.2.1 Memristor based on Inorganic Materials                                                  | 8   |

| 2.2.2 Memristor based on Organic Materials                                                    | 10  |

| 2.3 Applications of Memristor for In-Memory Computing.                                        | 12  |

| 2.3.1 Development of High-Density Memory                                                      | 13  |

| 2.3.2 In-Memory Logic.                                                                        | 14  |

| 2.3.3 Machine Learning Accelerators.                                                          | 16  |

| 2.3.4 Neuromorphic Computing                                                                  | 18  |

| 2.4 Summary                                                                                   | 20  |

| Chapter 3 Capacitive-Coupled Memristive Behavior based on Organic-Inorganic Heterojunction    | 21  |

| 3.1 Overview.                                                                                 | 21  |

| 3.2 Introduction                                                                              | 21  |

| 3.3 Device Fabrication and its Characterization.                                              | 22  |

| 3.4 Result and Discussions.                                                                   | 23  |

| 3.5 Summary                                                                                   | 29  |

| Chapter 4 High Density Memory and Multibit In-Memory Logic based on Graphene as Interlayer in |     |

| Multi-State Memristor                                                                         | 30  |

| 4.1 Overview                                                                                  | 300 |

| 4.2 Introduction                                                                            | 30       |

|---------------------------------------------------------------------------------------------|----------|

| 4.3 Device Fabrication and its Characterization.                                            | 311      |

| 4.4 Device Characteristics and Study of its Mechanism                                       | 322      |

| 4.5 High-Density Memory using Al/TiO <sub>2</sub> -graphene-DNA/Pt as Memristor             | 37       |

| 4.6 In-Memory Logic                                                                         | 41       |

| 4.7 Summary                                                                                 | 48       |

| Chapter 5 Varition Tolerant Matrix Multiplication Method using Memristor for In-Memory Comp | outing49 |

| 5.1 Overview                                                                                | 49       |

| 5.2 Introduction                                                                            | 49       |

| 5.3 Fabrication and Operation of memristor devices.                                         | 50       |

| 5.3.1 Device Fabrication                                                                    | 50       |

| 5.3.2 Device Operation                                                                      | 50       |

| 5.4 Existing Matrix Multiplication Technique using Memristor                                | 52       |

| 5.5 Design for Matrix multiplication                                                        | 54       |

| 5.6 Using proposed matrix multiplication circuit for neural network application             | 56       |

| 5.7 Result and Discussions.                                                                 | 57       |

| 5.7.1 PPA Analysis                                                                          | 57       |

| 5.7.2 Impact of variations in memristor                                                     | 59       |

| 5.8 Summary                                                                                 | 60       |

| Chapter 6 Conclusions and Future Work                                                       | 62       |

| 6.1 Conclusions                                                                             | 62       |

| 6.2 Future Work                                                                             | 62       |

| Bibliography                                                                                | 64       |

# **List of Figures**

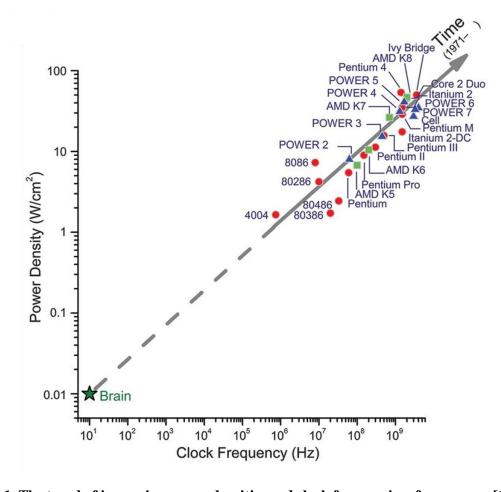

- **Figure 1.1.** The trend of increasing power densities and clock frequencies of processors [13].

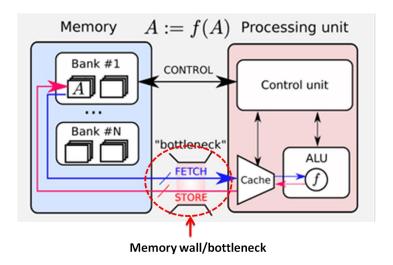

- **Figure 1.2.** Memory wall issue in conventional Von Neumann Architecture [14].

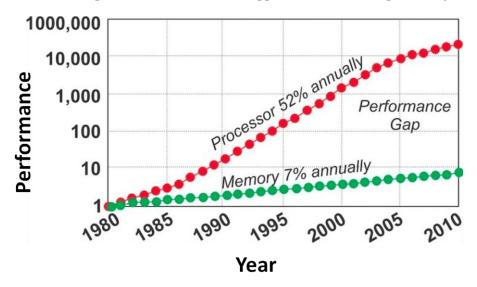

- **Figure 1.3.** Processor Memory performance gap widening trend [15].

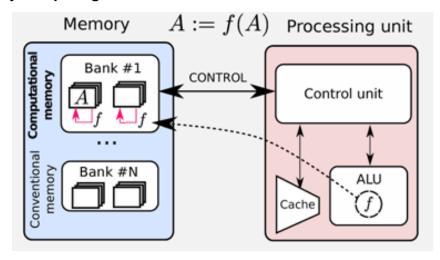

- Figure 1.4. In-memory computing paradigm [14].

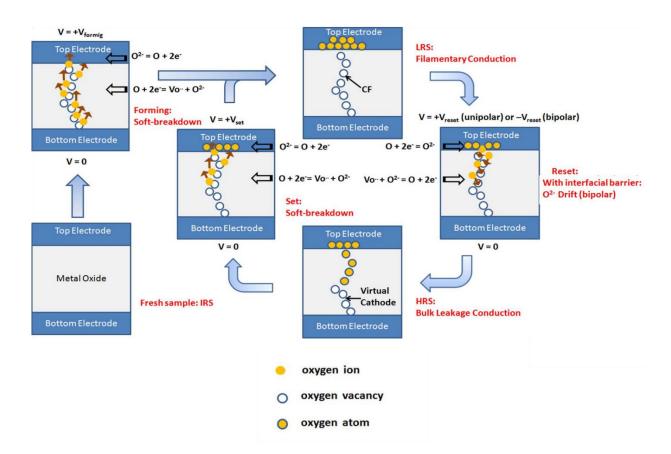

- **Figure 1.5.** Schematic illustration of switching mechanism of memristor [23].

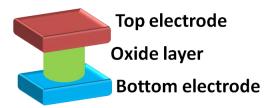

- **Figure 2.1.** Structure of memristor device.

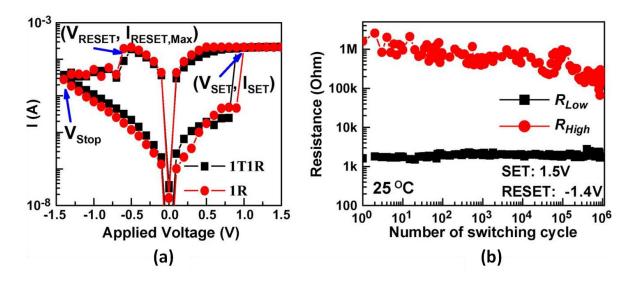

- Figure 2.2. TiN/TiO<sub>2</sub>/HfO<sub>2</sub>/TiN memristor behavior (a) I-V characteristics. (b) switching endurance [28].

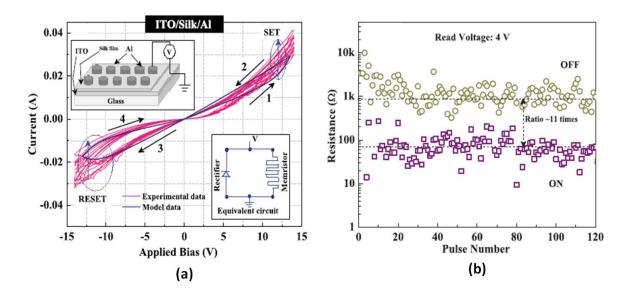

- **Figure 2.3.** Silk based memristor behavior (a) I-V characteristics. (b) Endurance test [32].

- Figure 2.4. Aspects of in-memory computing [16].

- **Figure 2.5.** The color map of the readout conductance with a reading voltage of 3 V using memristor based on hexagonal boron nitride and graphene [44].

- **Figure 2.6.** (a) The schematic of 3D vertical memristor array [49]. (b) The schematic of stacked memristor based memories with peripheral circuit [50].

- **Figure 2.7.** (a) V–R logic gate based on memristor, and (b)corresponding truth table for material implication (IMP) operation [16]; (c) The basic gate/latch circuit based on memristor, and (d) The truth table for the q←pIMPq [52]; (e) 2T2R logic structure with back-to-back RRAM pair, and (f) corresponding truth table for P/Q and P'/Q' when (V<sub>U</sub>, V<sub>L</sub>, G<sub>P</sub>, G<sub>Q</sub>) = (1, 0, 1, 1): P'=Q→P (IMP), Q'=0 (bit set). P'=Q→0 (NOT) operation is highlighted in blue [53].

- Figure 2.8. Matrix vector multiplication using analog crossbar array memristors [16].

- **Figure 2.9.** Digital Matrix Vector Multiplication using memristor crossbar array (a) Parallel digitizing step of RRAM crossbar in matrix multiplication. (b) XOR step of RRAM crossbar in matrix multiplication. (c) Encoding step of RRAM crossbar in matrix multiplication (d) RRAM-based inner-product operation [55,56].

- **Figure 2.10.** (a) memristor-CMOS synapse with 2T1R configuration. (b) voltage waveforms for  $V_{CG}$  and  $V_{TE}$  applied by the pre-synaptic neuron in the spike event (c) and overall circuit including the synapse and

the pre- and post-synaptic neurons. The overlap between  $V_{CG}$  and  $V_{TE}$  pulses causes a negative current proportional to the synaptic weight, which is integrated by the post-synaptic neuron and eventually contributes to fire [60].

**Figure 3.1.** The preparation process of organic-inorganic heterojunction device with Ag/TiO<sub>2</sub>-ML/Al structure. (a) masking for bottom electrode deposition (c) Al sputtering for bottom electrode (d) formation of bottom electrode (e) deposition of bio film using spin coating method (f) TiO<sub>2</sub> film layer formation over bottom electrode (g) Al sputtering for top electrode (h) device formation.

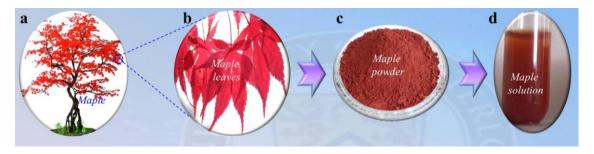

**Figure 3.2.** The preparation process of maple leaf solution for memristor. (a) Maple. (b) Maple leaves. (c) Maple leaf powder. (d) Maple leaf powder solution.

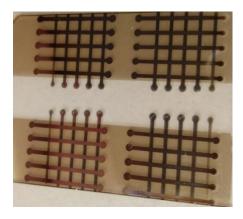

**Figure 3.3.** The optical photograph of the as-prepared device.

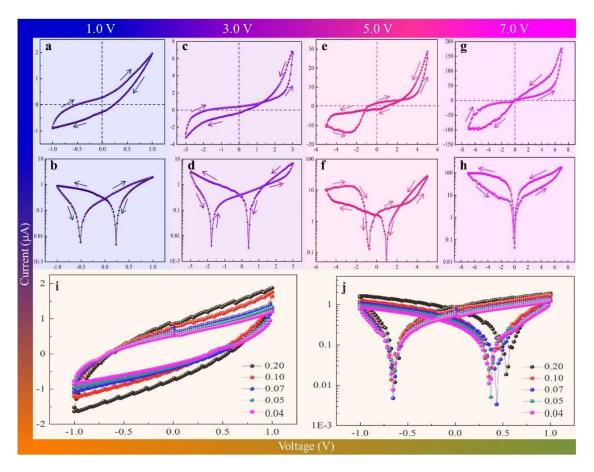

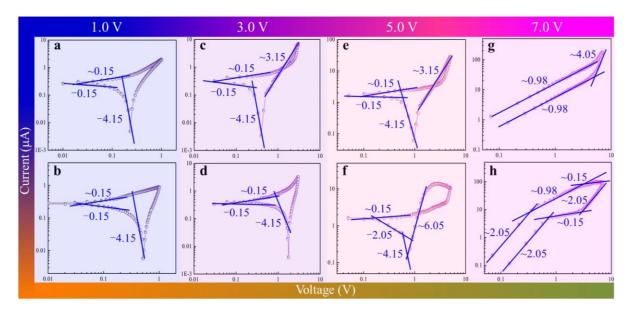

**Figure 3.4.** (a, c, e, g) The I-V curves under different voltage windows. (b, d, f, h) The corresponding logarithmic I-V curves. (i) The I-V curve at 1.0 V under different voltage change rate. (j) The corresponding logarithmic I-V curves.

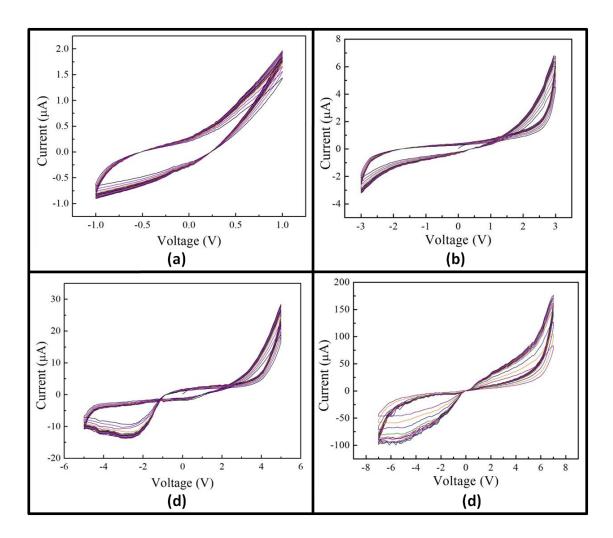

**Figure 3.5.** The I-V curves for multiple cycles (a) 100 cycles under voltage window of 1.0 V. (b) 80 cycles under voltage window of 3.0 V (c) 50 cycles under voltage window of 5.0 V (d) 30 cycles under voltage window of 7.0 V.

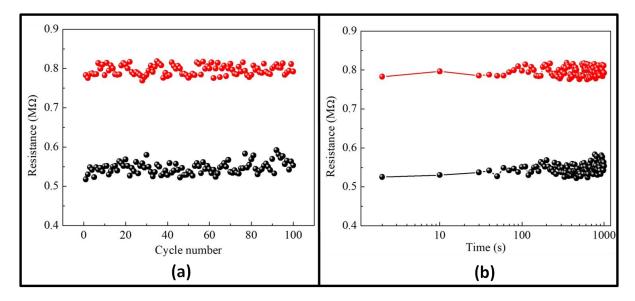

**Figure 3.6.** (a) The endurance test of the device at Vread of 0.25 V. (b) Retention test of the device.

**Figure 3.7.** (a, c, e, g) Experimental data and fitted lines of I-V curves of memory device in positive voltage region. (b, d, f, h) Experimental data and fitted lines of I-V curves of memory device in negative voltage region.

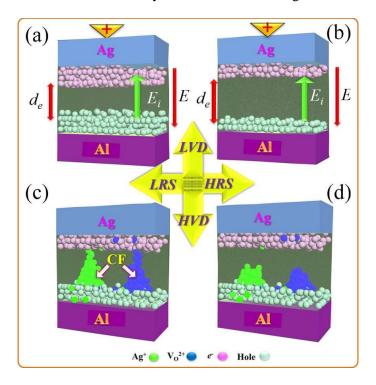

**Figure 3.8.** Schematics showing the electrons and oxygen vacancy diffusion processes. The conductive channel is multilevel formed under high voltage district (HVD).

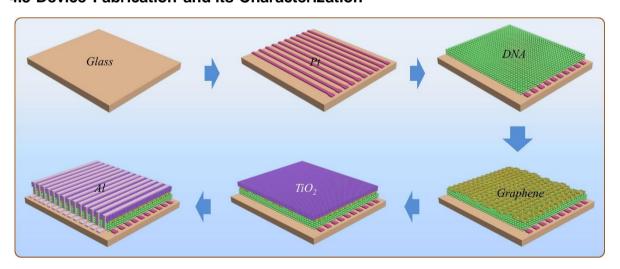

**Figure 4.1.** The preparation process of memristive device with Al/TiO<sub>2</sub>-Graphene-DNA/Pt structure.

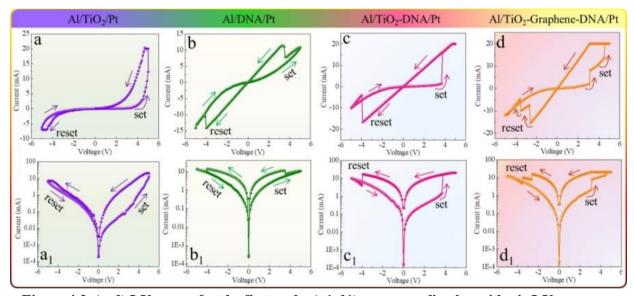

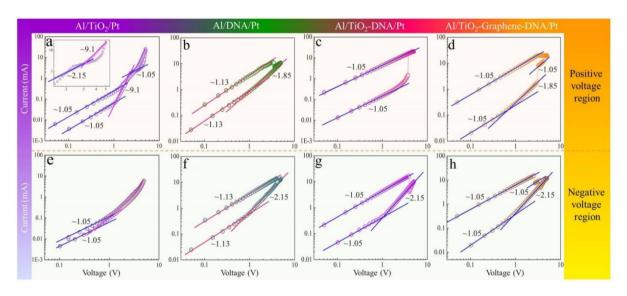

Figure 4.2. (a-d) I-V curves for the first cycle. (a1-d1) corresponding logarithmic I-V curves.

**Figure 4.3.** (a-d) The I-V curves with 100 consecutive cycles. (a1-d1) The corresponding logarithmic I-V curves.

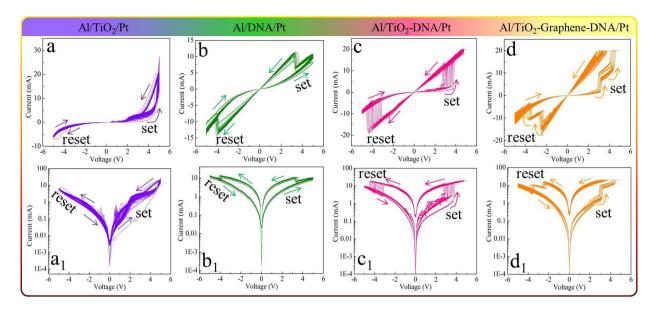

**Figure 4.4.** The range of V<sub>set</sub> and V<sub>reset</sub> voltages, and the fitting curve is satisfied the Gaussian distribution. a Al/TiO<sub>2</sub>/Pt device. b Al/DNA/Pt device. c Al/TiO<sub>2</sub>-DNA/Pt device. d Al/TiO<sub>2</sub>-Graphene-DNA/Pt device.

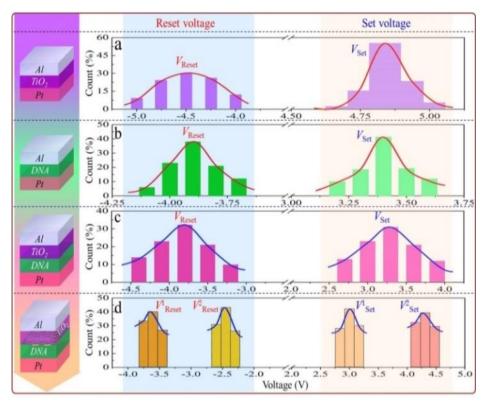

- **Figure 4.5.** The endurance characteristics of Al/TiO<sub>2</sub>-graphene-DNA/Pt device at different conduction states under different bias.

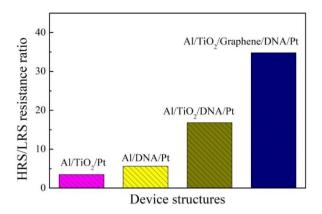

- **Figure 4.6.** The relation between HRS/LRS resistance ratio and device structures.

- **Figure 4.7.** Experimental data and linear fitting of I-V curves of memory device in positive and negative voltage regions, respectively. (a) Al/TiO<sub>2</sub>/Pt device. (b) Al/DNA/Pt device. (c) Al/TiO<sub>2</sub>-DNA/Pt device. (d) Al/TiO<sub>2</sub>-Graphene-DNA/Pt device.

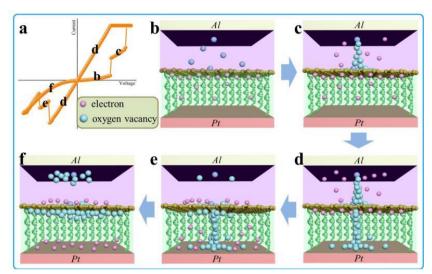

- **Figure 4.8.** (a) Typical I-V curve labelled different states with the models showing in (b-f); (b-f) the schematic diagram of physical dynamic processes for these states for Al/TiO<sub>2</sub>-Graphene-DNA/Pt device.

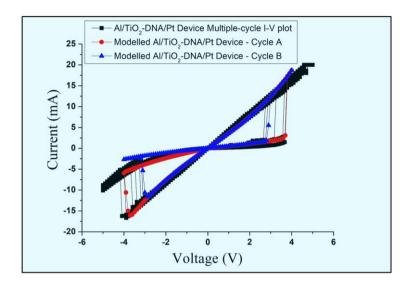

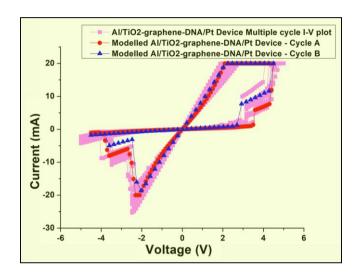

- **Figure 4.9.** Al/TiO<sub>2</sub>-DNA/Pt device modelling with variation. Cycle A represents device characteristics with maximum  $V_{set}$  and  $V_{reset}$ . Cycle B represents device characteristics with minimum  $V_{set}$  and  $V_{reset}$ .

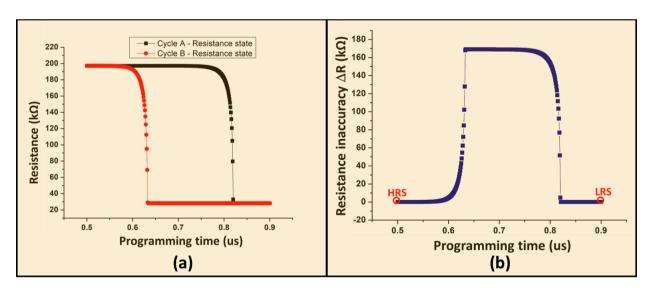

- **Figure 4.10.** (a) Write operation in Al/TiO<sub>2</sub>-DNA/Pt device in Cycle A (with maximum  $V_{set}$  and  $V_{reset}$ ) and Cycle B (with minimum  $V_{set}$  and  $V_{reset}$ ). (b) Variation in resistance state between Cycle A and Cycle B in Al/TiO<sub>2</sub>-DNA/Pt Device.

- **Figure 4.11.** Al/TiO<sub>2</sub>-graphene-DNA/Pt device modelling with variation. Cycle A represents device characteristics with maximum  $V_{set1}$   $V_{set2}$   $V_{reset1}$  and  $V_{reset2}$ . Cycle B represents device characteristics with minimum  $V_{set1}$   $V_{set2}$   $V_{reset2}$  and  $V_{reset2}$ .

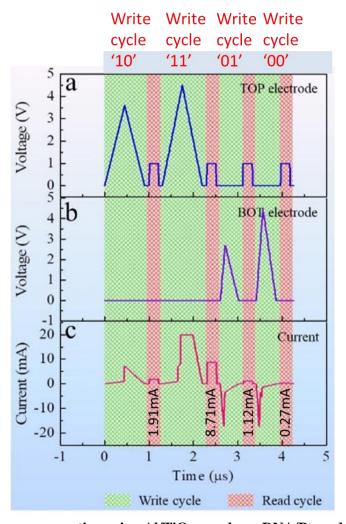

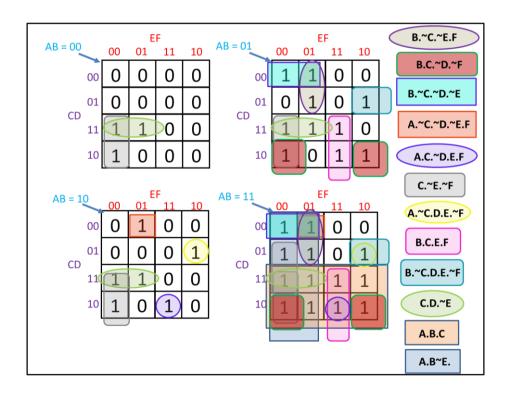

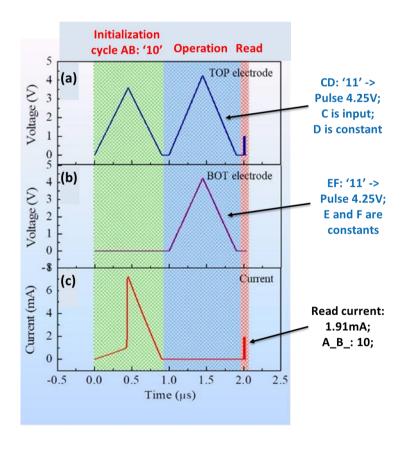

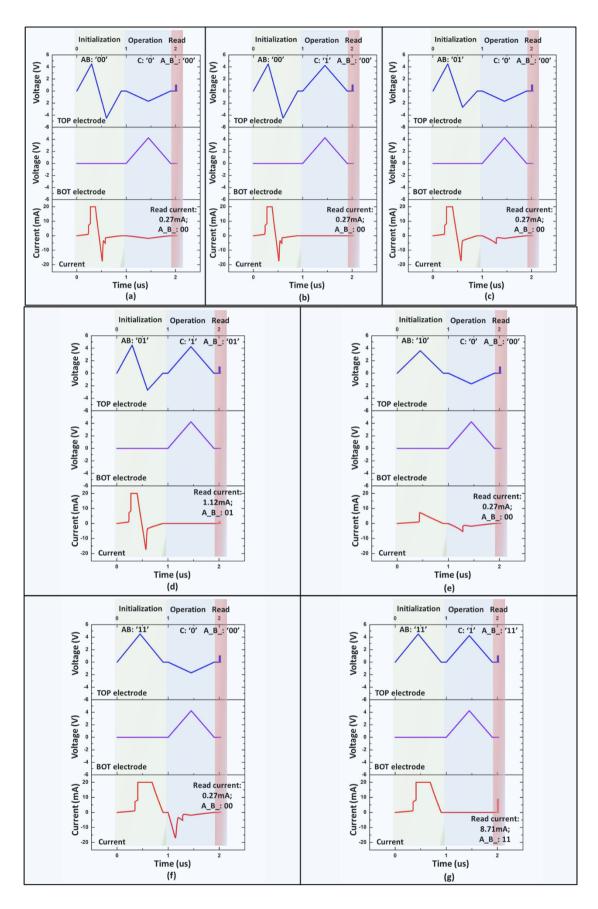

- **Figure 4.12.** 2-bit memory operation using Al/TiO<sub>2</sub>-graphene-DNA/Pt modelled device (a) Word line or the top electrode voltage (b) bit line or the bottom electrode voltage (c) device current. Cycle-1 represents writing and reading data '10', followed by writing and reading data '11','01' and '00' in cycle-2, cycle-3 and cycle-4 respectively. 1.91mA, 8.71mA, 1.12mA and 0.27mA currents were observed flowing through the device during the reading operation of '10','11','01' and '00', respectively.

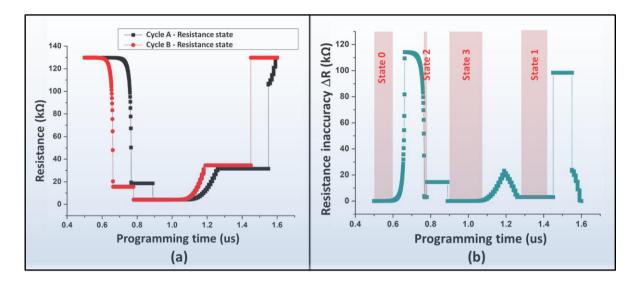

- **Figure 4.13.** (a) Write operation in Al/TiO<sub>2</sub>-grphene-DNA/Pt device in Cycle A (with maximum  $V_{set1}$   $V_{set2}$   $V_{reset1}$  and  $V_{reset2}$ ) and Cycle B (with minimum  $V_{set1}$   $V_{set2}$   $V_{reset1}$  and  $V_{reset2}$ ). (b) Variation in resistance state between Cycle A and Cycle B in Al/TiO<sub>2</sub>-graphene-DNA/Pt Device.

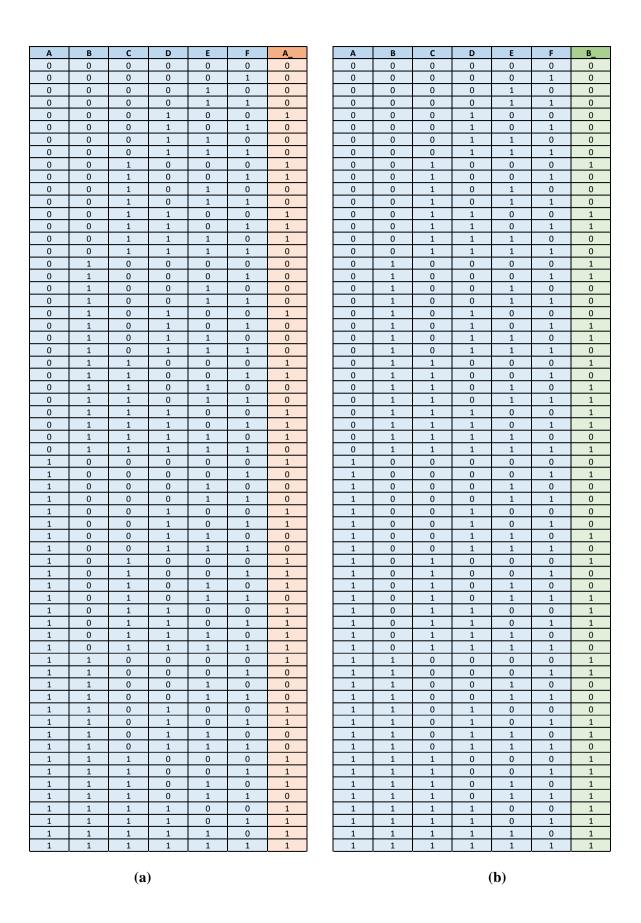

- **Figure 4.14.** (a) Truth table for A\_. (b) Truth table for B\_.

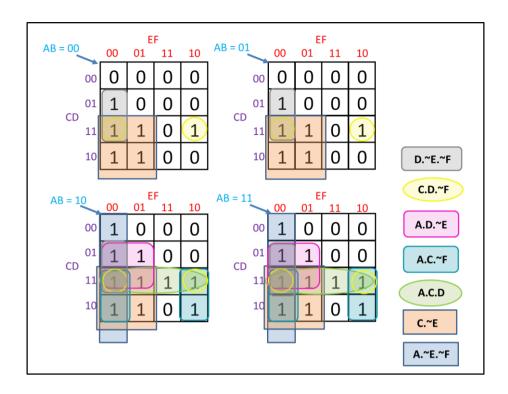

- **Figure 4.15.** Derivation of A\_ in SOP form using Karnaugh map.

- **Figure 4.16.** Derivation of B\_ in SOP form using Karnaugh map.

- **Figure 4.17.** Parallel operations allowed by the proposed Al/TiO<sub>2</sub>-Graphene-DNA/Pt device.

- **Figure 4.18.** Parallel AND operations A<sub>=</sub> = A AND C and B<sub>=</sub> = B AND C for inputs A, B and C as 1, 0, and 1, respectively. (a) Word line or the top electrode voltage (b) bit line or the bottom electrode voltage (c) device current.

- **Figure 4.19.** Parallel AND operations  $A_{-} = A$  AND C and  $B_{-} = B$  AND C for inputs A, B and C as (a) 000; (b) 001; (c) 010; (d) 011; (e) 100; (f) 110; (g) 111, respectively.

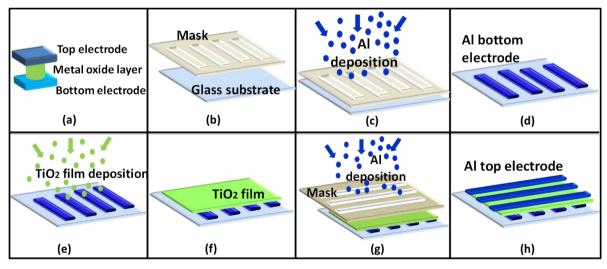

- **Figure 5.1.** Schematics showing the deposition process of layers for memristor device. (a) schematic for memristor structure (b) masking for bottom electrode deposition (c) Al sputtering for bottom electrode (d) formation of bottom electrode (e) deposition of TiO<sub>2</sub> film (f) TiO<sub>2</sub> film layer formation over bottom electrode (g) Al sputtering for top electrode (h) device formation

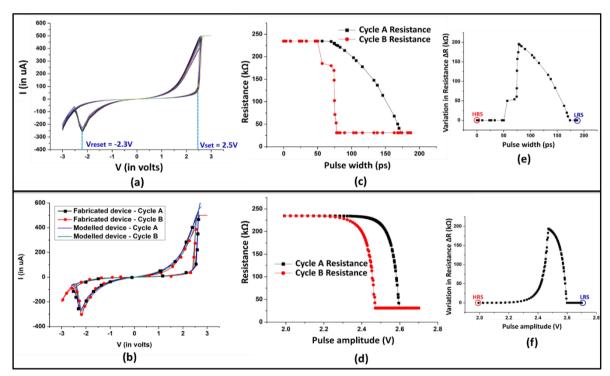

- **Figure 5.2.** (a) Multiple cycle I-V curve of fabricated device. (b) Variation in I-V curve for fabricated and modelled device for maximum  $V_{set}$  (Cycle A) and minimum  $V_{set}$  (Cycle B). (c) Programming by changing pulse width at 2.6V pulse amplitude (d) Programming by changing pulse amplitude at 20ps pulse width (e) Variation in resistance between cycle A and cycle B when programmed by changing pulse width at pulse amplitude of 2.6V (f) Variation in resistance between cycle A and cycle B when programmed by changing pulse amplitude at pulse width of 20ps.

- **Figure 5.3.** Analog matrix multiplication using memristor. The conductance of each memristor cell (e.g. g11, etc.) are sensitive to the device variation and noise.

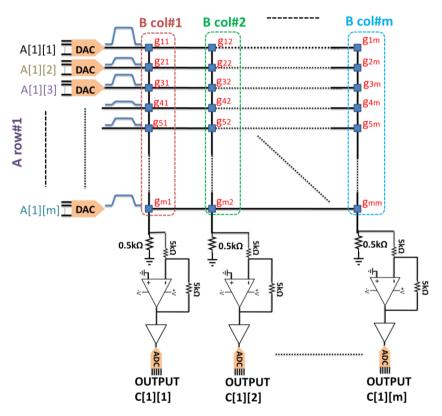

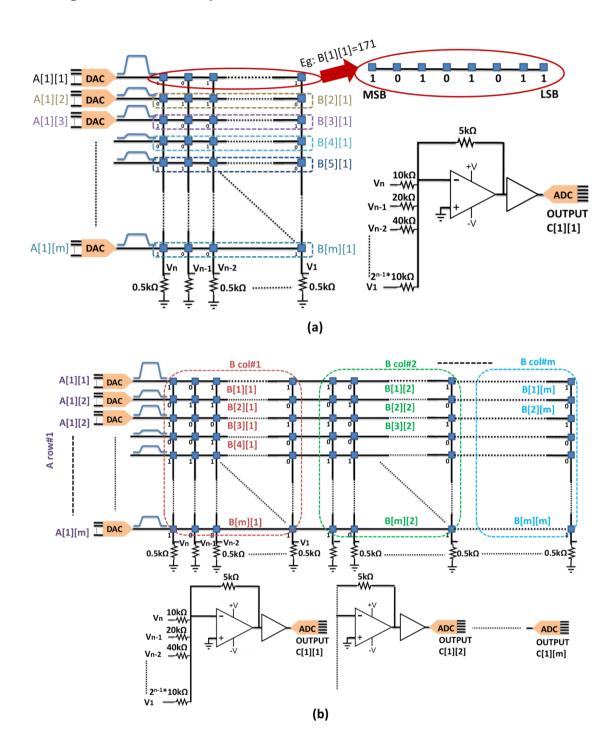

- **Figure 5.4.** (a) Schematic for computation of single output element (C[1][1] = A[1,1..m] x B[1..m, 1]) using the proposed analog-digital-hybrid matrix multiplication. Each element in B is a n-bit binary number. (b) Full schematic for analog digital hybrid matrix multiplication (not necessarily m copies of Figure 5.4a).

- **Figure 5.5.** Edge detection by convolution of matrix. (a) Filter and Input image. (b) Computation of first element of convolution matrix. (c) Conversion of filter and image patch to 1D. (b) Matrix multiplication using analog-digital hybrid matrix multiplication circuit. (e) Computation of second element of convolution matrix.

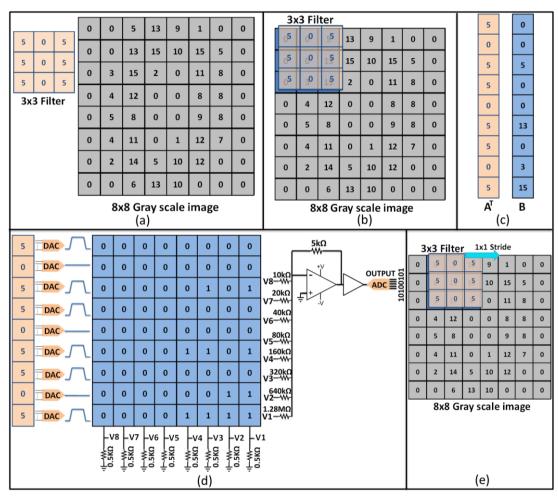

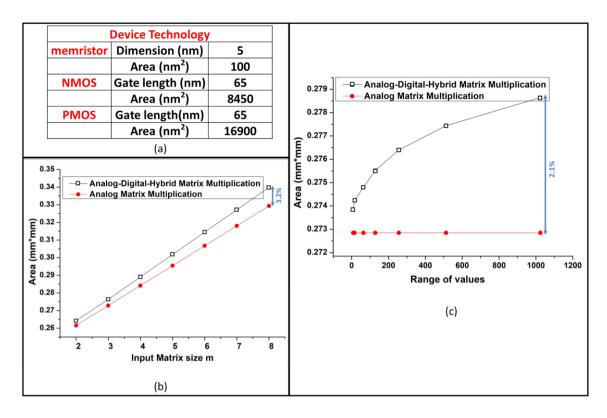

- **Figure 5.6.** (a) Total Power (memristor programming + Matrix multiplication) for analog design technique and analog-digital-hybrid design technique. (b) Power distribution (for Matrix multiplication only) for analog-digital-hybrid matrix multiplication technique.

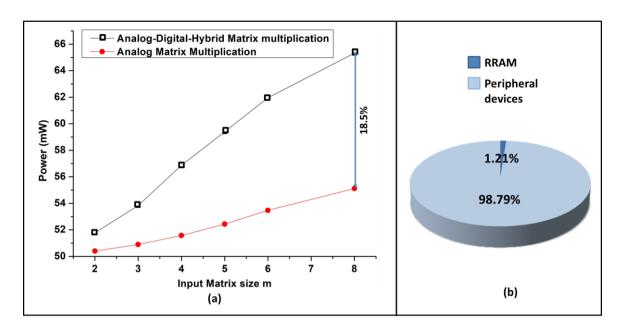

- **Figure 5.7.** (a) Device dimensions used for design evaluation. (b) Circuit Area vs Matrix size for analog matrix multiplication technique and analog-digital-hybrid design technique for range of element values as

256 and input matrix size varying from 2 to 8. (c) Circuit Area vs Matrix size for analog matrix multiplication technique and analog-digital-hybrid design technique for input matrix size 3 and range of element values varying from 16 to 1024 (i.e. n from 4 to 10 and assuming n = p).

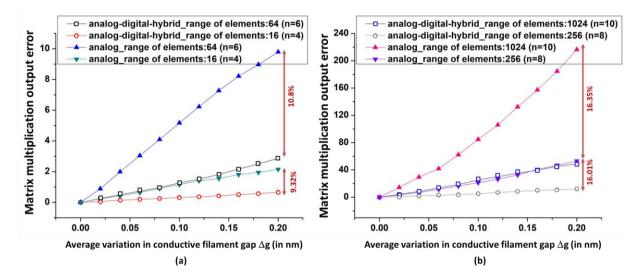

**Figure 5.8.** Matrix multiplication computation output error (w.r.t computation in cycle-A i.e.,  $\gamma$ =17.59) between analog design technique and analog-digital-hybrid design technique with respect to variations in memristor devices. (a) Matrix multiplication output error for range of element values as 64 (n = p = 6) and 16 (n = p = 4). (b) Matrix multiplication output error for range of element values as 1024 (n = p = 10) and 256 (n = p = 8).

# Chapter 1

# Introduction

#### 1.1 In-Memory Computing

#### 1.1.1 Need for New Computing Paradigm

Artificial intelligence and machine learning have proven to provide means for several advanced applications. Recently, various improvements and achievements have been accomplished through deep leaning to implement a wide range of applications such as object detection, face detection, self-driving cars, predictive technology, chat bots, self-learning robots, game playing computers, etc. [1-9]. Although machine learning theories have been developed since 1980s, it was not until the last decade when the field started to boom with an explosive scale of real-world applications. [10-12].

Figure 1.1. The trend of increasing power densities and clock frequencies of processors [13].

One of the key challenges in the early days was inability of hardware machines to support these applications to process large database, often with hundred or more parameters associated with it. Fortunately, continuous CMOS scaling has eventually reached the level to enable the hardware for implementation of deep learning applications.

The CMOS scaling, i.e., the decreasing size of transistor, has been directly associated with the increase in frequency of the processor which in turn can speed up the computation. However, as the frequency of the processor is increased, its power density increases as well. As historical data shown in Figure 1.1 [13], the frequency and power of modern processors have been increasing in a highly correlated manner since 1971. Such trend, however, has started to saturate when Moore's Law eventually comes to an end. Under the current scaling scenarios, with further increase in frequency, the power density would become too large and it is impossible for the chip to cool down by evacuating heat. Therefore, anymore increase in frequency could result in damaging the chip. This is the known as heat wall and is the first limitation in the existing computing paradigm.

Figure 1.2. Memory wall issue in conventional Von Neumann Architecture [14].

The second limitation of the scaling is shown in Figure 1.2, which is known as memory wall [13,14]. The conventional computers are based on Von-Neumann architecture, where the CPU or the basic processing unit and memory unit are separate. However, in case of data intensive computation such as deep learning, a high volume of data movement between processing unit and the memory is involved, which causes high

latency and power consumption. In addition, as the technology is scaled, the gap between performance of processing unit and memory is widening, as shown in Figure 1.3 [15]. Thus, increasing frequency further adds only little to performance in case of data intensive operation, as processing units needs to sit idle for the time the data is being fetched from the memory.

Hence, the traditional Von-Neumann architecture is no longer efficient moving forward. Novel computing architectures are explored for more advanced applications and faster processing.

Figure 1.3. Processor Memory performance gap widening trend [15].

#### 1.1.2 In-Memory Computing

Figure 1.4. In-memory computing paradigm [14].

As illustrated in the Figure 1.1, human brain has much less power density as well as lower frequency of operation comparing with processors based on Von-Neumann architecture, yet it is able to solve very complex problems. One of the key reasons for such efficient operation is that the operation of the brain involves computation and storage of the data in the same region. Therefore, for performing more complex operation more efficiently, it is necessary to shift hardware designs more closer to paradigm of brain. This has inspired researchers to explore in-memory computing architecture, in which computation and memory storage takes within the same unit, as shown in Figure 1.4. These architectures are termed as in-memory computing architectures.

#### 1.2 Memristor

Several emerging nanoscale memory technologies such as memristor, phase change memory, magnetic memory, and ferromagnetic memory have been explored for in-memory computing [16].

The memristor was proposed by L. Chua in 1971 based on missing element in the symmetry of fundamental circuit theory [17]. The classical circuit theory is based on four fundamental quantities (i) current, (ii) voltage, (iii) charge, and (iv) flux-linkage. The resistor, capacitor and inductor relate voltage-current, voltage-charge and current-flux linkage respectively. Therefore, based on symmetry, L. Chua proposed fourth element relating charge and flux, and named it as memristor. Although it was proposed in 1971, the memristor remain unobserved for several decades. It was identified recently in 2008 in HP labs [18]. Memristor devices have many attractive properties such as nanoscale dimensions, low power consumption and non-volatile memory [19-22]. This makes them suitable for many applications such as computer memories, programmable circuits and in-memory computing circuits [16].

Memristor (also known as resistive random-access memory, RRAM or ReRAM), is a combination of two words, memory and resistor. As its name indicates, memristor behaves similar to a non-linear resistor in a sense that it opposes the flow of charge in the same as resistor does. The difference is that the memristor has nonvolatile memory of its states [19]. So, its resistance value changes permanently depending on how much charge has flown through the device. As long as the input signal across the memristor is applied, the device keeps changing its resistance. Once the input signal is removed the memristor will in theory maintain its resistance indefinitely or until input signal is applied again. To change the resistance of the device, appropriate input voltages need to be applied for the appropriate duration of time.

The structure of a memristor device is a simple two-terminal structure where a dielectric layer is sandwiched between two electrodes. The resistance of the sandwiched dielectric layer is controlled by the potential difference applied across it, thus forming a memristor.

Figure 1.5. Schematic illustration of switching mechanism of memristor [23].

The operation of device can be explained by conductive filament growth and rupture in oxide region with application of potential difference at both the electrodes, as shown in Figure 1.5 [23]. During the one-time electroforming process after the device fabrication, a high voltage, known as forming voltage, is applied to generate mobile oxygen ions through dielectric breakdown. As a result, a conductive filament is formed due to oxygen vacancies in the dielectric layer. During normal write operations, a programming voltage, lesser than forming voltage, is applied between top electrode and bottom electrode to control this conductive filament and thus device resistance. When a negative programming voltage  $V_{reset}$  is applied at top electrode with bottom electrode grounded, the oxygen ions migrate back to the oxide layer. Therefore, the conductive filament ruptures and the device behaves as a high resistance device, which is known as high resistance state (HRS) of the device. Similarly, when a positive programming voltage  $V_{set}$  is applied at top electrode

with bottom electrode grounded, the conductive filament grows back again and the device behaves as a low resistance device, which is known as low resistance state (LRS) of the device. To read the resistance state of the device, a read voltage  $V_{\text{read}} < V_{\text{read}} < V_{\text{read}} < V_{\text{reset}}/2$ ) is applied across the device to sense the read current.

An ideal memristor should have large  $I_{LRS}/I_{HRS}$  ratio (>10<sup>2</sup>) i.e.., the ratio of read current when the device is in LRS (low resistance state) to that when the device is in HRS (high resistance state) [16,23-25]. Additionally, an ideal memristor should have high endurance (i.e., device characteristics should not change with several set and reset cycles) and retention (i.e., the device should be able to retain resistance state for a long period of time) ability. It has been shown that very high level of endurance (120 billion cycles) and retention (> 10 years) have recently been achieved in memristor device [16].

#### 1.3 Scope of Research

One of the major hurdles for the use of memristor is its stochastic nature including cycle to cycle variations and device to device variations. This has limited the use of memristor yet to be commercialized even though posing enormous benefits. Moreover, there still remains a lot from a materials point of view to be explored in order to achieve better performance and more stable device, especially using biomaterials, which provides a cleaner source of fabrication for the memristor device.

In this thesis, we will try to address these issues in in-memory computing using memristor devices. The thesis will cover development of memristor device using maple leaves as biomaterials. Further, we will explore the use of DNA along with graphene, for the fabrication of memristor device and its application towards development of high-density memory and parallel logic circuits. Lastly, we will discuss novel circuits for performing matrix multiplication using memristor, with the proposed design being more tolerant towards stochastic nature of the memristor device.

#### 1.4 Organization

The thesis is divided in four main chapters. The Chapter 2 covers brief review about the related work about memristor devices and its applications in in-memory computing. In Chapter 3, memristor device development using maple leaves as a part of functional layer and the behavior of the device under different voltage range will be discussed. In Chapter 4, high density memory and parallel in-memory logic operations using memristor based on DNA as biomaterial functional layer along with graphene and TiO<sub>2</sub> will be presented. In Chapter 5, novel analog-digital-hybrid matrix multiplication scheme to counter stochastic

nature of the device will be discussed based on memristor with  $TiO_2$  as functional layer. The Chapter 6 summarizes the research work and proposes the future work.

# Chapter 2

#### Related work

#### 2.1 Introduction

Since the discovery of memristor device in 2008 by HP, a wide range of materials have been explored to improve the device stability, behavior, endurance, and fabrication methods. Recently, a lot of work has also been particularly devoted towards fabrication of memristor using biomaterials for its easy availability, cheaper fabrication method and environment friendly source. From the circuit and system levels, memristor devices have been widely explored for its applications in in-memory computing. In this chapter, we will discuss briefly about previously explored materials for the memristor in section 2.2, followed by various applications of the memristor in in-memory computing in section 2.3.

#### 2.2 Development of Memristor Device

The structure of a memristor device is a simple two-terminal layered structure, where an oxide layer is sandwiched between two metal electrodes, as shown in Figure 2.1. However, the selection of materials and the fabrication method plays an important role in the device characteristics.

Figure 2.1. Structure of memristor device.

The materials for the oxide layer can be a single uniform oxide layer or a combination of multiple oxide layer. Broadly, the oxide layer can be categorized as inorganic layer, and organic layer, which are discussed in following section 2.1.1 and 2.1.2 respectively.

#### 2.2.1 Memristor based on Inorganic Materials

A number of inorganic metal oxides have been observed to show memristive behavior, with majority of them are transition metal oxides, and few are lanthanide series metal oxides [23]. It has been observed that among different oxides, Cu<sub>2</sub>O and WO<sub>3</sub>, shows most compatibility with the conventional CMOS devices

because a single additional oxidation stage of the Cu or W via/plug is required respectively [23]. The deposition methods of these inorganic metal oxides usually include the ALD (atomic layer deposition), PLD (pulse laser deposition), reactive sputtering, and oxidation of a corresponding metal.

TiO<sub>2</sub> is one of the initial materials to be explored for the memristor application. Yang et al. fabricated 50nm x 50nm Pt/TiO<sub>2</sub>/Pt memristor devices, which exhibited stable switching behavior [26]. Strukov et al. explained that the switching mechanism of the Pt/TiO<sub>2</sub>/Pt device is based on the movement of the positive charged oxygen vacancies [18]. HfO<sub>2</sub> is also an excellent memristor material and its explored widely for its application in memristor technology. In the primary stage of HfO<sub>2</sub> based memristor investigation, the TiN/HfO<sub>2</sub>/Pt structure is typically used to achieve the memristive characteristics [27].

Figure 2.2. TiN/TiO<sub>2</sub>/HfO<sub>2</sub>/TiN memristor behavior (a) I-V characteristics. (b) switching endurance [28].

H. Lee et al. used combination of  $TiO_2$  and  $HfO_2$  as oxide layer for the fabrication of memristor. The typical I–V curve and the variation in resistance with switching cycle for the fabricated memristor, is shown in Figure 2.2 [28]. The resultant  $TiN/TiO_2/HfO_2/TiN$  memristor with high-speed operation showed large  $I_{LRS}/I_{HRS}$  ratio (> 100), reliable switching endurance (> 10<sup>6</sup> cycles), long high-temperature lifetime, and high device yield (~100%).

Among other materials,  $Al_2O_3$  based memristor behaves very similar to that of  $HfO_2$  based memristor in many characteristics. Additionally,  $Al_2O_3$  based memristor also showed unique characteristics

of the low reset current [23]. Using Al/AlO<sub>2</sub>/Pt memristor device, Wu et al. first demonstrated low reset current down to ~1 uA [29]. Further, Kim et al. doped the AlO<sub>2</sub> with nitrogen and achieved even lower reset current (< 100 nA). The low energy/power consumption of AlO<sub>2</sub> based memristor is a striking feature [30].

#### 2.2.2 Memristor based on Organic Materials

In comparison to memristor with inorganic oxide layer, the oxide layer based on biomaterials are relatively less stable, have lower endurance and lower  $I_{LRS}/I_{HRS}$  ratio. However, the major advantage of using biomaterials for the fabrication of memristor is its easy availability, cheaper cost of fabrication and environmentally friendly source [16,31].

Figure 2.3. Silk based memristor behavior (a) I-V characteristics. (b) Endurance test [32].

Hota et al., demonstrated fabrication of memristor based on biomaterials using natural silk cocoon fibroin protein of silkworm, Bombyx mori [32]. Additionally, the film developed was transparent across most of the visible spectrum. ITO and Al were used as top and bottom electrode. The I-V characteristics of the device is shown in Figure 2.3a. The endurance test of the device is shown in Figure 2.3b. It can be clearly observed that in comparison to device based on complete inorganic oxide layer (shown in Figure 2.2), device based on biomaterials shows lesser endurance with cycle, and has lower  $I_{LRS}/I_{HRS}$  ratio.

B. Sun et al., demonstrated fabrication of memristor with natural biomaterials made from spider silk (fibroin) developing Ag/Fibroin/Au structure, where the device showed  $I_{LRS}/I_{HRS}$  of 60 [33]. Chen et al., fabricated memristor with egg albumen film Al/egg white/ITO structure, where the device showed  $I_{LRS}/I_{HRS}$  >  $10^3$  [34].

Mao et al., demonstrated environmentally friendly and sustainable bio-memristor device with Ag/walnut skin (WS)/ITO structure. Interestingly, the fabricated device exhibited an overwhelming capacitance effects in the bio-memristor device [35]. Xingli He et al., demonstrated use of Egg albumen as the dielectric, and dissolvable Mg and W, as the top and bottom electrodes, respectively in order to produce water soluble memristors [36]. The device showed  $I_{LRS}/I_{HRS}$  ratio in the range of  $10^2 \sim 10^4$ . It was further demonstrated that the Mg and W electrodes, and albumen film all can be dissolved in water within 72 hours.

Ham et al., demonstrated tunable memristor using light illumination [37]. The fabricated device consisted of organolead halide perovskite (OHP) as dielectric layer, in which the resistance state is modified by both electrical pulses and light illumination. Owing to the accelerated migration of the iodine vacancy inherently existing in the coated OHP film under light illumination, the OHP based device exhibited light-tunable resistivity functionalities with very low programming inputs ( $\approx 0.1 \text{ V}$ ).

Ku et al., reported the use of organic-inorganic hybrid perovskite materials for the fabrication of Ag/MAPbI<sub>3</sub>/FTO memristor [38]. Further they demonstrated the use of fabricated device for neuromorphic computing. The results showed that the with energy consumption of the MAPbI<sub>3</sub>-based memristor to be estimated as low as 47 fJ/um<sup>2</sup>, which as close as human brain.

The conduction mechanisms observed for the memristor based on organic materials remains same as memristor based on inorganic materials (formation and rupture of conductive filaments), which was confirmed by SEM imaging [16,23,31]. Generally, for the deposition of biofilm, spin coating method was used in above cases, which makes the fabrication step very easy [32-35]. However, the inability to control film thickness and maintaining film uniformity using spin coating deposition, is one of its major drawbacks. Therefore, the device shows lesser endurance and retention ability in comparison to inorganic oxide films. However, other than cheaper fabrication and maintaining cleaner environment, the organic materials based memristor also adds extraordinary features to the device, which makes it noteworthy to be investigated further.

#### 2.3 Applications of Memristor for In-Memory Computing

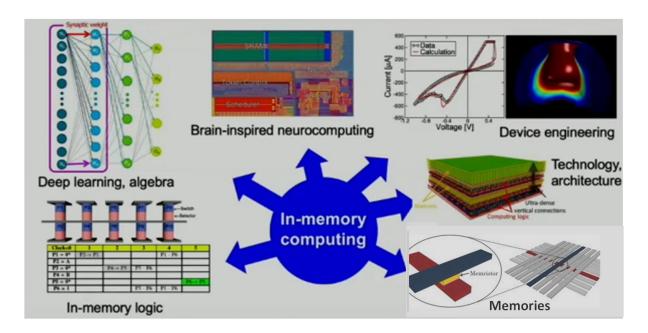

As discussed in chapter 1, in-memory computing is to perform computation within the memory blocks. As shown in Figure 2.4, there are several aspects related to computations within the memory [16]. In this section, we will briefly examine the different digital and analog computing schemes that have been proposed. The most important element of in-memory computing is development of high-density memory architecture. We will discuss various recent advancements in 2D, and 3D memory architectures based on memristor devices in section 2.3.1. For in-memory digital computing, in-memory logics are also being explored for implementation of general logic computation within the memory. Memristor provides various alternative to carry out digital Boolean operations, which will be briefly reviewed in section 2.3.2. One of the other important innovations in in-memory computing is the development of hardware based neural networks and deep learning within the memory, which deals in TBs of data. The hardware implementation of such in-memory computing based machine learning applications, has shown promising results in terms of performance improvement and power reduction in comparison to Von-Neumann architecture [16], which will be discussed in section 2.3.3. In section 2.3.4, brain inspired computing or neuromorphic processors within the memory will be discussed, which relies on fundamental principal of working of brain, and is one the major focus of recent study on in-memory computing.

Figure 2.4. Aspects of in-memory computing [16].

#### 2.3.1 Development of High-Density Memory

The memristor device is widely explored as non-volatile memory in various computing architectures, largely due to its smaller area, high packing density, low power, high switching speed and its compatibility with conventional CMOS device. The data is stored in form of resistance state of the device. Broadly, the use of memristor as non-volatile memory can be categorized as analog memory and digital memory.

Generally, a crossbar structure is utilized for memory using memristor, where top electrode forms the word line and bottom electrode forms the bit line, and the memristor device is formed at junction of each wordline and bitline. For digitally storing data in memristor, 0s and 1s are stored in form of HRS and LRS respectively [39-42]. For writing data, a  $V_{set}$  or  $V_{reset}$  potential difference is applied across the device through word line and bit line. For reading the data, a  $V_{read}$  pulse (generally lower than  $V_{set}/2$  and  $V_{reset}/2$ ) is applied at the word line and current flowing through bit line is sensed to determine the stored resistance state of the device [44].

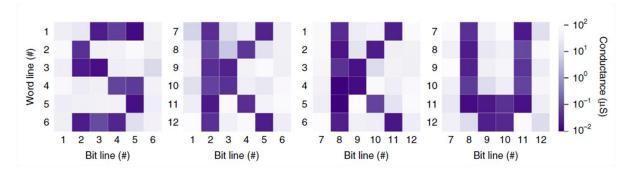

Figure 2.5. The colour map of the readout conductance with a reading voltage of 3 V using memristor based on hexagonal boron nitride and graphene [44].

However, it has been demonstrated that memristor could be used in more efficient manner in an analog way, where more information can be stored in a single memristor. In this, intermediate resistance states are being explored to store data. The use of memristor in analog way helps in reducing the area of the memory significantly [44, 45].

L. Sun et al., demonstrated use of memristor as memory in an analog way as shown in Figure 2.5, where a 12x12 crossbar structure was used to store data in form for conductance. The device used for the demonstration based on hexagonal boron nitride and graphene, with  $I_{LRS}/I_{HRS}$  ratio larger than 10<sup>3</sup> [44]. However, the use of memristor as memory in analog way also creates issue of precision during memory write operations due to stochastic nature of memristor device [46-48].

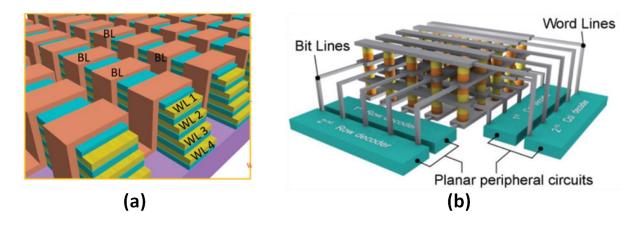

Figure 2.6. (a) The schematic of 3D vertical memristor array [49]. (b) The schematic of stacked memristor based memories with peripheral circuit [50].

Other than planer crossbar structure, a lot of research has also been focused on developing architecture in 3D manner to increase the memory density, as shown in Figure 2.6 [49,50]. The Figure 2.6a shows stacking of memristor positioned vertically over one another [49]. The Figure 2.6b shows stacking of memristor layer over the other [50]. The integration of memristor in 3D architecture manner increases the memory density; however, it makes the fabrication process significantly more complex and potentially more expensive.

#### 2.3.2 In-Memory Logic

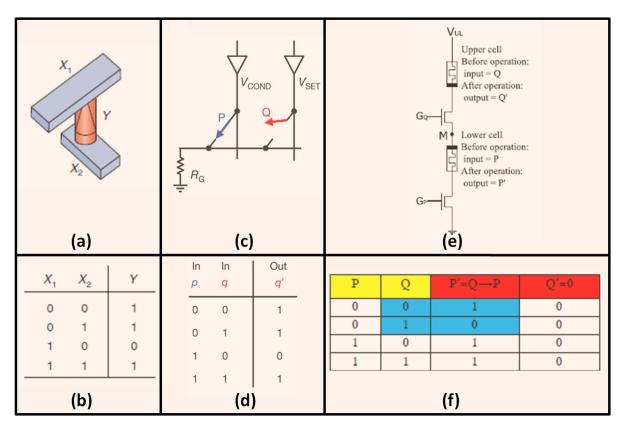

In the past two decades, in-memory digital computing has focused on identifying novel logic gate concepts with lower energy and area consumption [16]. Resistive switching devices, such as memristor, provides a number of advantages in digital computing, including direct access by interconnect lines, the capability to electrically reconfigure the device, and nanoscale miniaturization. Figure 2.7 shows various methods to perform digital Boolean operations using memristor, differing by the input type, the output type, and the physical operation to describe the logic function [51-53].

In the logic gate of Figure 2.7a, the two input states X1 and X2 are represented by the voltage values applied to the top and bottom electrodes, respectively, while the output of the logic operation is stored as the resistance of the memristor device [51]. The output of the computation is the resistive state, namely a logic value 0 for the HRS, and 1 for the LRS, where the memristor device is initialized to state 1. One of the major drawbacks of this method is the requirement of sense amplifier to detect the state of the device, and the conversion of resistive state to voltage state for the operations. Figure 2.7b shows the inputs

and outputs for implementation of IMP logic. The IMP or "imply logic" is a fundamental but powerful Boolean logic operation on two operands (p and q) such that "p IMP q" is equivalent to "(~ p) OR q".

Figure 2.7. (a) V–R logic gate based on memristor, and (b) corresponding truth table for material implication (IMP) operation [16]; (c) The basic gate/latch circuit based on memristor, and (d) The truth table for the q $\leftarrow$ pIMPq [52]; (e) 2T2R logic structure with back-to-back RRAM pair, and (f) corresponding truth table for P/Q and P'/Q' when (V<sub>U</sub>, V<sub>L</sub>, G<sub>P</sub>, G<sub>Q</sub>) = (1, 0, 1, 1): P'=Q $\rightarrow$ P (IMP), Q'=0 (bit set). P'=Q $\rightarrow$ 0 (NOT) operation is highlighted in blue [53].

The logic gate in Figure 2.7c, is fully resistance based logics, where the inputs are stored initially in memristor p and q. Bit '0' is stored in form of HRS, while bit '1' is stored in form of LRS [52]. To execute IMP function a pulse of  $V_{cond}$  and  $V_{set}$  is applied to p and q respectively, and the final result is stored in form of resistance state of q. Figure 2.7d shows the truth table for the operation of IMP function using logic gate shown in Figure 2.7c.

The Figure 2.7e shows another example fully resistance logic, based on memory ratioed logic [53]. In this, two memristor are connected back to back and are initialized to inputs P and Q. After application of

appropriate voltage pulse, memristor P stores the final resistance state as  $P=Q \rightarrow P$  and Q=0 as shown in truth table 2.7f. The basic principal behind is the voltage drop across the memristors based on its initial input resistance values.

#### 2.3.3 Machine Learning Accelerators

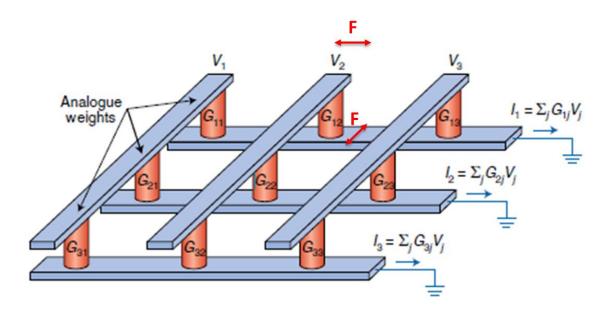

One of the important uses of memristors for in-memory computing is in machine learning accelerators for faster and efficient matrix multiplication using crossbar array. A crossbar array consists of multiple intersections between orthogonal row and column electrodes, each intersection containing a memristor element [16]. The crossbar memories are extremely attractive to reduce the bit cell size, as the individual device area is just  $4F^2$ , where F is the lithographic feature size in the process technology. From the viewpoint of in-memory computing, the crossbar array naturally provides a hardware accelerator for analog matrix-vector multiplication (MVM). Figure 2.8 illustrates the concept of MVM in a crossbar array, where a voltage  $V_j$  is applied to the j<sup>th</sup> column, with j = 1, 2, ..., N, where N is the number of rows and columns. The voltage-induced currents of each resistive element are collected at the grounded rows, yielding a total current.

$$I_i = \sum_i G_{ij} V_i \tag{2.1}$$

at the  $i^{th}$  row, where  $G_{ij}$  is the conductance of the resistive memory at row i and column j. Equation (2.1) is the analog product of the conductance matrix  $G_{ij}$  and the voltage vector  $V_j$ , which implements a hardware-based MVM via Ohm's law and Kirchhoff's law [54].

Crossbar MVM can be adopted for a broad range of problems, including image compression, sparse coding, and implementation of artificial neural networks (ANNs), where  $G_{ij}$  has the meaning of a synaptic weight,  $V_j$  is a pre-synaptic spike amplitude, and  $I_i$  is the input signal to the  $i^{th}$  neuron.

The time consumed in computation of complex algorithms in machine learning and deep learning is dominated by repeated matrix vector multiplication on huge data set. A separate hardware for matrix multiplication inside memory provides huge boost in performance of machine learning algorithms. The analog MVM in the crossbar can be carried out in just one step, as opposed to the digital CMOS based MAC operation, which is a time and energy-consuming step in classical computers. Note that a significant amount of energy for crossbar-based MVM is spent in operating analogue-to-digital converters that transform the digital input vector into analog voltages  $V_j$  in cases where the input of the calculations does not come directly from analog sensors, or where further digital processing of the output is needed [16,55].

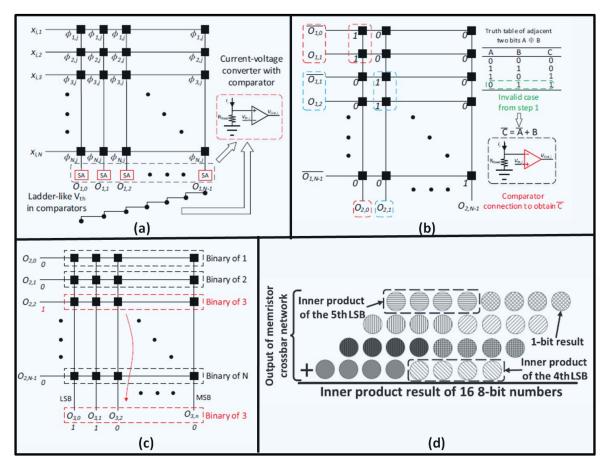

Figure 2.8. Matrix vector multiplication using analog crossbar array memristors [16].

Crossbar MVM has one of the major disadvantages in terms of precision as it relies on memristor devices, which are stochastic in nature [48,55]. The precision is least of intermediate resistance, when performing analog matrix vector matrix multiplication. Another method, proposed by Leibin Ni et al which performs MVM on memristor crossbar array in digital way, where memristor is programmed only to HRS and LRS, thus avoiding the precision issue. As shown in Figure 2.9, the method is based on four major steps [55,56].

The first step is called parallel digitizing, which requires  $N \times N$  memristor crossbars. The idea is to split the matrix vector multiplication to multiple inner-product operations of two vectors. Each inner product is produced by one memristor crossbar. All columns are configured with same elements that correspond to one column, therefore the voltages on bit-lines (BLs) are all identical. The key to obtain the inner product is to set ladder type sensing threshold voltages for each column.

The inner-product output of parallel digitizing step is determined by the position where the result of first step changes from 0 to 1. In the second step, XOR operation is performed for every two adjacent bits on the output of the first step, which gives the result index. The third step takes the output of XOR step and produces in binary format as an encoder. The last step is comprised of addition of all inner products.

In contrast to analog MVM using memristor crossbar array, this method provides better precision and consumes lesser area, with penalty in power by 3.12x [55].

Figure 2.9. Digital Matrix Vector Multiplication using memristor crossbar array (a) Parallel digitizing step of RRAM crossbar in matrix multiplication. (b) XOR step of RRAM crossbar in matrix multiplication. (c) Encoding step of RRAM crossbar in matrix multiplication (d) RRAM-based inner-product operation [55,56].

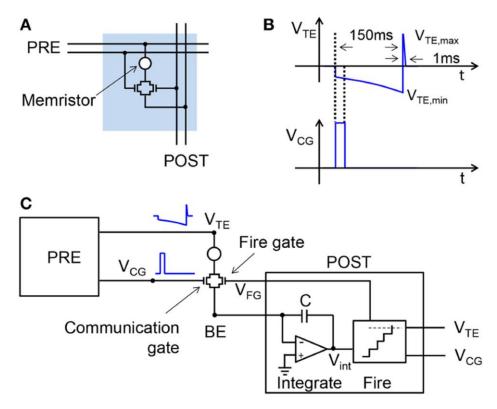

#### 2.3.4 Neuromorphic Computing

Similar to functioning of brain, in addition to performing all the computation within the memory, the neuromorphic computing is based on mimicking the brain synapse on hardware. Various models such as leaky integrate and fire, Hodgkin-Huxlex, integrate and fire models, etc have been proposed to imitate functioning of brain to implement neuromorphic computing. In various research papers, memristor is used as implementation of synapse [57-64]. Inside the human brain, to neurons are connected through synapse. In neuromorphic computing, weight between two neurons (or the connection between two neurons) is stored

in form of memristor's resistance state. The weight of this device is updated depending upon neuron spike. STTP is one example of weight update rule [60].

Figure 2.10. (a) memristor-CMOS synapse with 2T1R configuration. (b) voltage waveforms for  $V_{CG}$  and  $V_{TE}$  applied by the pre-synaptic neuron in the spike event (c) and overall circuit including the synapse and the pre- and post-synaptic neurons. The overlap between  $V_{CG}$  and  $V_{TE}$  pulses causes a negative current proportional to the synaptic weight, which is integrated by the post-synaptic neuron and eventually contributes to fire [60].

Figure 2.10 shows implantation of leaky integrate and fire model using memristor [60]. Figure 2.10b shows the voltage  $V_{CG}$  applied to the gate of the communication gate and  $V_{TE}$  to the top electrode, which are both applied by the pre-synaptic neuron in the spike event. The applied voltage spikes in the figure induce a spiking synaptic current, which is proportional to the conductance of the memristor, thus serving as a storage element of the synaptic weight. The synaptic current flows through the synaptic circuit and is fed into the input terminal of the post-synaptic neuron, where integration and fire take place as shown in the schematic circuit of Figure 2.10c. As the integrated current exceeds a certain threshold, the post-synaptic neuron fires, sending a spike to the following neurons in the network, as well as applying a feedback spike to the fire gate.

Several neurons are connected together, forming virtual brain on hardware, which forms basis of neuromorphic computing, which is a promising candidate for the next generation of computing technologies. [57-60].

#### 2.4 Summary

The memristor provides an efficient hardware technology to perform in-memory computing in terms of power, area, speed and functionality. However, the roads are not straight forward, rather it is full of challenges such as stochastic nature of the device, fabrication of 3D architecture, etc. In this thesis we will discuss the fabrication of memristor using maple leaves along with TiO<sub>2</sub> layer, where the device shows reversible capacitive coupled and pure memristive behavior, modulated by external voltage. Further, we will discuss the fabricated device using graphene as interlayer, where the device shows great potential for multi bit memory, rendering the need for 3D memory architecture moot. Lastly, we will discuss novel design for machine learning accelerator using memristor, with better precision and more tolerance to variation, at the moderate expense of power, performance and area.

## **Chapter 3**

# Capacitive-Coupled Memristive Behavior based on Organic-Inorganic Heterojunction

#### 3.1 Overview

The reprogrammable device is one of the important needs for circuit design. In this Chapter, TiO<sub>2</sub> and maple leaves (ML) are combined to form a functional layer (TiO<sub>2</sub>-ML) inside memristive devices, which demonstrate both the capacitive effect and the non-volatile storage capability. When the voltage increases from zero, the device firstly enters a capacitive-coupled memristive state at low voltage before switch to normal memristive state at a higher voltage. The existence of the capacitive behavior results in a non-zero-crossing I-V characteristic different from the zero-crossing curve observed in normal memristive device.

#### 3.2 Introduction

Both memristor and capacitor share a similar two-terminal structure with a dielectric layer sandwiched between two metal electrodes. While ideal capacitor has a dielectric layer with infinite resistance, resistive paths form and rupture inside the dielectric layers of memristors. Thus, the memristor could demonstrate capacitance characteristic during a unique/extreme phase of operation [65, 66]. That is to say that the capacitive effect and the memristive effect can evolve with each other [67].

In previous reports, the capacitive effect was usually submerged by the high current density caused by the formation of conductive filaments [68]. That is, after the conductive filament was formed between the top electrode and the bottom electrode, it will short-circuit the capacitive effect, thereby exhibiting a pure memristive effect. I. Valov and J. L. M. Rupp's groups emphasized that the redox reaction caused by moisture at the interface/surface plays a leading role for the generation of capacitive state in a memristive device [69-71]. However, moisture does not provide a reliable way to precisely control the electronic behavior. In addition, moisture should generally be avoided in the operation of electronic device because moisture often causes the failure of electronic performance. Besides, the previously observed such behaviors provide very small difference between memristive states of the device to be used in applications.

In this Chapter, we proposed a new device structure which uses voltage to control the device evolving between capacitive behavior and pure memristive behavior. The organic-inorganic heterojunction provides better stability and a greater difference between the resistance states of memristor device. Based on theoretical analysis, a physical model is proposed to understand the evolution process.

In the following section 3.3, we will discuss device fabrication steps and its characterization. In section 3.4, we will discuss the results, followed by conclusion in section 3.5.

#### 3.3 Device Fabrication and its Characterization

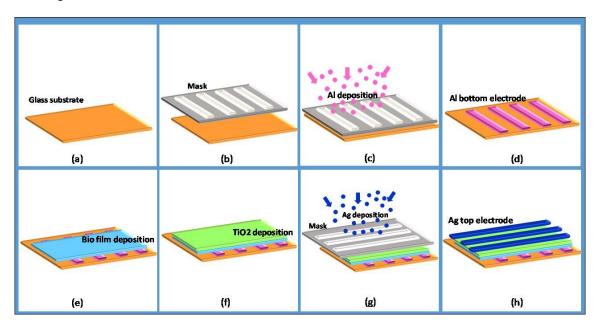

The preparation process of the organic-inorganic heterojunction device with Ag/TiO<sub>2</sub>-ML/Al structure is shown in Figure 3.1.

Figure 3.1. The preparation process of organic-inorganic heterojunction device with Ag/TiO<sub>2</sub>-ML/Al structure. (a) masking for bottom electrode deposition (c) Al sputtering for bottom electrode (d) formation of bottom electrode (e) deposition of bio film using spin coating method (f) TiO<sub>2</sub> film layer formation over bottom electrode (g) Al sputtering for top electrode (h) device formation.

Firstly, glass substrates were cleaned subsequently in acetone, ethanol and isopropyl alcohol, and dried under nitrogen gas flow. We use the shadow mask process to deposit bottom electrodes. The mask is placed on the clean glass substrate, and the Al bottom electrode with a thickness of ~200 nm was deposited using sputtering. Next, the mask was removed, and biofilm made of maple leaves was deposited using a spin-coating technique. To prepare bio-film layer, we extracted the ultrafine ML powder from maple leaves by multiple grinding and suction filtration methods, as shown in Figure 3.2. Then we prepared a ML solution for the deposition of ML film by spin coating on a glass substrate with the Al bottom electrode. The sample was then allowed to dry in the oven for ~24 hours in order to remove any moisture, followed by the deposition of second oxide layer TiO<sub>2</sub> with the thickness of ~20 nm using sputtering. Finally, the top

electrode Ag with a thickness of ~300 nm was deposited using sputtering with the mask rotated by 90° compared to the bottom electrode. An organic-inorganic heterojunction memristive device with Ag/TiO<sub>2</sub>-ML/Al structure was obtained following these steps. An optical photograph of the as-prepared device is shown in Figure 3.3.

Figure 3.2. The preparation process of maple leaf solution for memristor. (a) Maple. (b) Maple leaves. (c) Maple leaf powder. (d) Maple leaf powder solution.

Figure 3.3. The optical photograph of the as-prepared device.

To study the memristive device behavior, we connect the bottom electrode to the ground and then apply voltage sweep at the top electrode in the order of  $0 \text{ V} \rightarrow 1.0 \text{ V} \rightarrow 0 \text{ V} \rightarrow -1.0 \text{ V} \rightarrow 0 \text{ V}$  varying linearly at a constant rate of 0.1 V/s. The experiment is repeated by increasing the voltage ranges from  $\pm 1.0 \text{ V}$  to  $\pm 3.0 \text{ V}$ ,  $\pm 5.0 \text{ V}$ , and  $\pm 7.0 \text{ V}$ , respectively. Finally, the experiment is repeated by changing the voltage sweeping rate.

#### 3.4 Result and Discussions

The I-V curves with  $V_{max} = 1.0 \text{ V}$ , 3.0 V, 5.0 V and 7.0 V are presented in Figure 3.4a, c, e, g (linear scale) and Figure 3.4b, d, f, h (logarithmic scale), respectively. These I-V curves with  $30 \sim 100$  cycles are shown

in Figure 3.5. At  $V_{max} = 1.0$  V, Figure 3.4a shows that the I-V curve is non-zero crossing and does not have point of intersection. It is known that this non-zero-crossing I-V curve indicates that a capacitive effect is present in the memristor [72-74].

Figure 3.4. (a, c, e, g) The I-V curves under different voltage windows. (b, d, f, h) The corresponding logarithmic I-V curves. (i) The I-V curve at 1.0 V under different voltage change rate. (j) The corresponding logarithmic I-V curves.

When  $V_{max}$  is increased to 3.0 V, it can be observed that there is a crossover behavior in the I-V curve, and the intersection is in the first quadrant (Figure 3.4c). However, this I-V curve is still non-zero-crossing. When continuing to increase the test voltage to  $V_{max} = 5.0$  V, the I-V curve shows two cross-over actions, as observed from Figure 3.4e, and the two intersections are in the first and third quadrants, respectively. This is when the device transits from capacitive behavior into capacitive-coupled memristive behavior. In order to further observe the change of the I-V curve at a higher voltage, the  $V_{max}$  was further increased to 7.0 V (Figure 3.4g). The standard memristive behavior is observed with a zero-crossing I-V

hysteresis curve. These I-V characteristics are repeatable, which can be controlled by the selection of  $V_{max}$ . By increasing  $V_{max}$ , the proposed device evolves from a capacitive behavior to capacitive-coupled memristive behavior and eventually to a pure memristive behavior.

Figure 3.5. The I-V curves for multiple cycles (a) 100 cycles under voltage window of 1.0 V. (b) 80 cycles under voltage window of 3.0 V (c) 50 cycles under voltage window of 5.0 V (d) 30 cycles under voltage window of 7.0 V.

Besides, to understand the capacitive effect in the capacitive-coupled memristive device, different voltage sweep rates (dV/dt) of 0.20, 0.10, 0.07, 0.05 and 0.04 V/s are applied with  $V_{max} = 1.0$  V. These results are shown in Figure 3.4i (linear scale) and Figure 3.4j (logarithmic scale). The bottom electrode is grounded, and voltage sweep is applied at the top electrode from 0 V  $\rightarrow$  1.0 V  $\rightarrow$  0 V  $\rightarrow$  -1.0 V. In a

capacitor, I  $\propto$  dV/dt, it is consistent with these results shown in Figure 3.4i. This further proves the occurrence of capacitive effect in the device at low voltage.

The endurance test and the retention test of the device was performed for standard memristor behavior, when the voltage sweeping window is varied as  $0 \text{ V} \rightarrow 7.0 \text{ V} \rightarrow 0 \text{ V} \rightarrow -7.0 \text{ V}$ . The endurance test of the device measured at reading voltage of 0.25V is shown in Figure 3.6a. The test shows that cycle to cycle the device shows small variations in resistance states. The retention test of the device measured for 1000sec for HRS and LRS state of the device is shown in Figure 3.6b. The test shows the device is able to retain the resistance state without much degradation.

Figure 3.6. (a) The endurance test of the device at Vread of 0.25 V. (b) Retention test of the device.

To understand the conduction mechanism in Ag/TiO<sub>2</sub>-ML/Al device, we re-plotted the I-V curves in a log-log scale (with |V| for negative voltages), as shown in Figure 3.7, and perform linear extrapolation to each section of the curves. Based on the fitting results, it is very obvious that there are sections in the log-log I-V curves with negative slopes (e.g. -0.15, -4.15 and -2.05) when the device is tested at  $V_{max} = 1.0 \text{ V}$ , 3.0 V, and 5.0 V. However, no negative slope is observed when the device is tested at 7.0 V. The appearance of these negative slopes is most likely due to the I-V behavior of a capacitive device [72-75]. When the test voltage is low, no conductive filament exists in the dielectric layer. Thus, the capacitive effect dominates in the proposed device. However, when the external voltage is increased to 7.0 V, a conductive filament was formed in the functional layer of the device, which shorts the top and bottom electrodes of the device.

In this case, the current is dominated by conduction current, causing the capacitance effect to disappear, thereby exhibiting a pure memristive effect with positive slopes in log-log I-V curves.

Figure 3.7. (a, c, e, g) Experimental data and fitted lines of I-V curves of memory device in positive voltage region. (b, d, f, h) Experimental data and fitted lines of I-V curves of memory device in negative voltage region.

In addition, we further analyze the case of a positive slope. We can see that the Ohmic conduction behavior (slope of ~1.0) occurs in the positive voltage region when a low voltage is applied to the device (Figure 3.7g). However, the device obeys the space-charge-limited conduction (SCLC) behavior (slope ~ 2.0) in the negative voltage region when a low voltage is applied to the device (Figure 3.7h), indicating that electrons are conducted from the un-filled SCLC of the trap change to the trap filled SCLC[76-79]. It obeys the following equation:

$$J_{trap-filled} = \frac{9}{8} n \varepsilon \mu \left[ \frac{V^2}{d^3} \right]$$

(3.1)

where J is the current density, n is the permittivity of free space,  $\varepsilon$  is the relative dielectric constant,  $\mu$  is the mobility of charge carriers, V is the applied voltage, and d is the thickness of the functional layer. At the same time, we can observe larger slopes ( $\sim 3.15$  and  $\sim 4.05$ ) in the high voltage range. This larger slope reflects the current density and energy distribution of the trap. That is to say, a conductive filament was formed in the functional layer at a high voltage, at this point, the capacitive effect completely disappears. Based on the above analysis, it is thus expected that the main conduction mechanism in our device would

be the trap-controlled SCLC by the defects and formation of conductive filaments induced by oxygen vacancies and Ag ions inside the TiO<sub>2</sub>-ML bilayer film, as shown in Figure 3.8.

Figure 3.8. Schematics showing the electrons and oxygen vacancy diffusion processes. The conductive channel is multilevel formed under high voltage district (HVD).

Figure 3.8 illustrates the carrier transport mechanism in the  $TiO_2$ -ML bilayer film, which display the conversion of the device between high resistance state (HRS) and the low resistance state (LRS) in the low voltage district (LVD) and the high voltage district (HVD), respectively. It can be seen that when a positive voltage is applied to the top electrode of the device, a positive charge, including oxygen vacancies ( $V_0^{2+}$ ) and holes, will move toward the bottom electrode along the direction of the electric field and a negative charge region will be shielded at the bottom interface. At the same time, the anode dissolution reaction equation of Ag atoms in the top electrode occurs according to the reaction [80,81].

$$Ag \rightarrow Ag^+ + e^- \tag{3.2}$$

The positive and negative ions moving in the electric field carry displacement current, which leads to the capacitive effect at the low voltage in the functional layer (Figure 3.8a, b). The displacement current exhibits a non-zero-crossing I-V curve. Moreover, as the voltage increases, the ion concentration correspondingly increases, which further changes the memristive behavior (the circular direction of the I-

V curve) because of the internal electromotive force [82], thus exhibiting a different mode of capacitive-coupled memristive effect in our device.

At high voltages, the device generates Joule heat locally due to high currents, which enhances the mobility of Ag ions and oxygen vacancies, and the high electric field can effectively accelerate the migration of electrons and ions [83-85]. After it reaches a certain threshold, it will eventually form Ag conductive filaments and oxygen vacant conductive filaments inside TiO<sub>2</sub>-ML functional layer (Figure 3.8c). Once the conductive filaments were formed, it provides a path for the conductive current to travel between the two electrodes, overwhelming any displacement current. At this time, the capacitive effect completely is largely suppressed, showing a pure memristive effect. After the voltage polarity is inverted, the Ag<sup>+</sup> ions and oxygen vacancy will be pushed back to the top electrode due to the Coulomb repulsion effect, resulting in the conductive filament to be partially dissolved to form a large gap in the functional layer [86-88]. The carriers of the conduction current are expected to tunnel through this gap. Hence, the device returns to the HRS after such a reset process (Figure 3.8d). This process at high voltage is similar to those reported in the standard memristive device.

# 3.5 Summary

In summary, through the organic-inorganic heterojunction devices fabricated using TiO<sub>2</sub> and natural maple leaves as a functional layer, we proposed a novel memristive device which shows capacitive behavior at low voltages and normal memristive behavior at high voltages. Further, a theoretical analysis is provided to explain the operation and behavior of the device. The existence of capacitive coupled and memristive behavior, modulated by programming voltage, could provide way for new reprogrammable devices for inmemory computing.

# Chapter 4

# High Density Memory and Multibit In-Memory Logic based on Graphene as Interlayer in Multi-State Memristor

#### 4.1 Overview

As information technology moves toward a big data era, the conventional Von Neumann architecture has shown limitation in performance. This is constrained by the continuous large volume of data being fetched and stored through input-output (IO) device [89, 90]. Therefore, it is necessary to bring processing unit as close as possible to memory for minimizing data transmission. Memristors provides dual functionalities of data storage and computing at the same position without data transmission, therefore is one of the most promising candidates for energy efficient in-memory computing. In this chapter, we demonstrate a memristor device, formed by Al/TiO<sub>2</sub>-Graphene-DNA/Pt layers, with high performance and stable intermediate multistate resistive switching behaviors. It was observed that the asynchronous conduction by either oxygen vacancies migration or injected electron transfer is responsible for the multistate resistive switching behaviors. Further, for in-memory computing, a high-density memory and multibit parallel logic computations are realized based on the multistate resistive switching behaviors. This improves data storage capacity and performance up to 2× with respect to conventional memristor devices when they are used to store binary data. This work provides a new horizon on the multistate resistive switching and the complete logic hardware.

#### 4.2 Introduction

Recent research has been devoted to design advanced biomaterial-based resistive switching devices in order to achieve sustainable, environmental-friendly and biodegradable electronics [32-36,77,91-94]. Unfortunately, the performance of pure biomaterial-based resistive switching device is usually inferior compared to inorganic materials-based counterparts. This is because biomaterials are prone to degrade under the electric field or via chemical reactions with water molecules in the air, which ultimately leads to the failure of device [94, 95]. Therefore, inorganic-organic multilayer structures, as functional materials in resistive switching device, have recently attracted great attention. These hybrid structures can achieve better performance in terms of HRS/LRS resistance ratio, retention and cycle stability [96-98].

Since resistive switching behavior firstly reported in TiO<sub>2</sub> a few decades ago, it has been observed in other semiconductor materials systems [18,99,100]. Meanwhile, DNA, an organic compound of deoxyribonucleic acid, is a natural, renewable, and biodegradable biomaterial which shows potential in light emitting diodes and field effect transistors [101, 102]. Recently, DNA has been reported as a functional layer in resistive switching devices which exhibit good memory behaviors [103, 104].

Moreover, graphene has different electron conductivity along horizontal and vertical directions of the basal plane, which can be used in advanced electronic devices [105, 106]. Here, we design a new inorganic-organic TiO<sub>2</sub>-Graphene-DNA hybrid multilayer, as a functional layer to study its memory behaviors in resistive switching devices.

In this chapter, we explore, for the first time, the behavior of inorganic-organic TiO<sub>2</sub>-Graphene-DNA hybrid materials in non-volatile resistive switching devices. It was fabricated with a simple capacitor configuration consisting of Al/TiO<sub>2</sub>-Graphene-DNA/Pt. We demonstrate that this memristor has advantages in in-memory computing by achieving parallel computing, higher storage capacity, and improved area savings. In the previous works, memristors were used as planer digital memory (storing binary data in form of either HRS or LRS) [39-42]. However, the memory density in case of using memristor as planer digital memory remains poor as only single bit can be stored in memristor. Furthermore, it was also demonstrated that memristors could be used in multilevel way, where device is used in analog mode by utilizing intermediate resistance state of the device [44,45]. However, the accuracy and precision of writing data in form of intermate resistance state of the device is very poor [46-48]. In order to achieve higher memory density and higher accuracy, 3D architectures were proposed, which makes the fabrication steps complicated [49,50]. In this chapter, we demonstrate high density memory can be achieved by storing 2-bits using fabricated device Al/TiO<sub>2</sub>-Graphene-DNA/Pt, without any compromise in accuracy and maintaining easier fabrication method. Further, we demonstrate the cell can be used perform two simultaneous operations at a time. Compared with other in-memory computing techniques, this memory system has great advantages in parallel processing, power reduction and area savings. The described resistive switching device has stable multi-resistance states, which can process up to two parallel operations in a single memristor.

#### 4.3 Device Fabrication and its Characterization

Figure 4.1. The preparation process of memristive device with Al/TiO2-Graphene-DNA/Pt structure.

For the device fabrication, firstly, glass substrates were cleaned and dried by nitrogen gas flow. Subsequently, a layer of Pt was deposited on the glass substrate by magnetron sputtering, as shown in Figure 4.1. Then an organic DNA layer was spin-coated onto a bottom electrode Pt. When the spin-coated DNA was completely dried, a layer of graphene was deposited on the DNA by solution method. Then, we deposited a layer of titanium dioxide (TiO<sub>2</sub>) film on graphene by magnetron sputtering. Finally, a mask was used to deposit a top electrode Al with 300 nm thickness and 500 µm in width. As a result, we got a resistive switching device with Al/TiO<sub>2</sub>-Graphene-DNA/Pt structure. The current-voltage (I-V) properties were measured using an electrochemical workstation, where a pulse is applied at the top electrode of the fabricated device, with its bottom electrode grounded. Similarly, devices with structure Al/TiO<sub>2</sub>/Pt, Al/ DNA/Pt, and Al/TiO<sub>2</sub>-DNA/Pt were fabricated and their I-V properties were measured.

# 4.4 Device Characteristics and Study of its Mechanism

Figure 4.2. (a-d) I-V curves for the first cycle. (a1-d1) corresponding logarithmic I-V curves.

The Figure 4.2 presents typical first cycle I-V characteristics of four fabricated devices (Al/TiO<sub>2</sub>/Pt, Al/DNA/Pt, Al/TiO<sub>2</sub>-DNA/Pt and Al/TiO<sub>2</sub>-Graphene-DNA/Pt) under the voltage sweep of  $0 \text{ V} \rightarrow 5.0 \text{ V} \rightarrow 0 \text{ V} \rightarrow -5.0 \text{ V} \rightarrow 0 \text{ V}$ . The I-V curve with more than 100 cycles is shown in Figure 4.3. We can observe that the I-V curve given after many cycles (>100 cycles) is nearly identical to the curve obtained in the initial characterization, indicating excellent endurance of the resistive switching device. The corresponding I-V curves of Figure 4.2a-d in logarithmic form are displayed in Figure 4.2a1-d1.

Figure 4.3. (a-d) The I-V curves with 100 consecutive cycles. (a1-d1) The corresponding logarithmic I-V curves.

The I-V response curves of these devices show obvious changes with different device structures in Figure 4.2. As the number of active layer increases, the loop of the I-V curve becomes larger. In particular, for Al/TiO<sub>2</sub>-Graphene-DNA/Pt device (Figure 4.2d), when an external voltage is scanned from 0 to 5.0 V, the device switches from HRS to LRS after two set processes around voltage of 3.05 V and 4.25 V. After this transition, the LRS would not change until a sufficiently large opposite voltage is applied. The resistance state returns to the HRS after it goes through two reset processes happening around voltages of -2.45 V and -3.75 V. The two set and two reset processes appear in the opposite voltage regions, indicating that the as-prepared device displays bipolar multistate resistive switching memory performance [107].