## Design of 28 GHz 4x4 RF Beamforming Array for 5G Radio Front-Ends

by

Giovanni Scarlato

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Applied Science

in

Electrical Engineering

Waterloo, Ontario, Canada, 2019

© Giovanni Scarlato 2019

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Current state of wireless infrastructure sees mass migration to higher frequencies as much of the already used spectrum is insufficient in supporting the influx of numerous users and various data intensive mobile applications. Data rates are projected to increase by an order of magnitude and harnessing the necessary bandwidth below 6 GHz is not feasible. A move to higher frequencies sees not only increased fractional bandwidth, but also significantly enhanced antenna apertures as a result of beamforming capabilities. Due to device level complications with frequencies nearing the unit gain frequency of transistor technology, high output power is seldom found, and in conjunction with severe path loss, communication links cannot be established without the usage of antenna arrays.

Phased array systems offer significant upside to the traditional array implementation as it permits reconfigurable directive communication. However, Ka-Band phased arrays still struggle to arrive at a reasonable tradeoff between design complexity, cost and performance. With a divide between both organic and printed circuit board (PCB) based approaches to the development of an antenna-in-package (AiP), this thesis sides with the latter. An antenna-on-PCB variant of the AiP is developed, which implements both commercially available RF laminates and RFIC front end modules to produce a 28 GHz 4x4 RF beamforming phased array that is found to exhibit extremely low loss (-0.66 dB), adequate scan volume ( $\theta_o = +/-45^{\circ}$ , in E and H planes) and large bandwidth (3 GHz) for a single layer, non-isolated patch antenna design. Unit cell, infinite array analysis is emphasized and lattice resizing is leveraged to obtain desired scan performance, while significantly reducing design complexity via the absence of intricate isolation enhancement techniques.

In an effort to aid in application based design, the AiP is extended to application of linearization where it is found that the inclusion of dummy elements along the perimeter of the package not only serve as element pattern enhancement, but also provide reliable means of output signal capture. Negating the traditional transmitter observation receiver (TOR) architecture, the AiP design as a TOR for millimeter-wave communication proves optimistic in the quest for maximum system efficiency.

#### Acknowledgements

I would most importantly like to thank my parents, Marcello and Barbara Scarlato, for supporting me throughout all my hardships. They alone have made this thesis possible. My sister Yolanda, for being attentive, understanding and knowing when time is of the essence. To the one I love, Diana Rodriguez, thank you for being by my side throughout this journey. You have been there when I needed you most, and I am forever indebted to you.

I would like to thank Professor Slim Boumaiza for his guidance and support in my transition to Electrical Engineering and for his excellent mentorship over the past two years.

I would like to acknowledge the support given by many individuals at Anokiwave, for their insight and continued attention to my work.

I would like to thank Yushi Cao, for helping me with extensive measurement setup and calibration.

Last and certainly not least, I would like to thank all EmRG colleagues who have participated in conversation with me. In specific, Ahmed Raslan, Mona Razmi, Hejir Rashidzadeh and Ahmed Ben Ayed, for helping me develop new perspective on life. I thank you.

#### Dedication

This is dedicated to my Nonno, Renzo Baggio, for inspiring me as a child, always pushing me to my limits, regardless of age, and instilling in me the need to do more.

## Table of Contents

| Li              | st of | Table  | $\mathbf{s}$                                     | ix |

|-----------------|-------|--------|--------------------------------------------------|----|

| List of Figures |       |        | x                                                |    |

| 1               | Inti  | roduct | ion                                              | 1  |

|                 | 1.1   | Motiv  | ration                                           | 1  |

|                 |       | 1.1.1  | Broadcasting versus Line of Sight                | 2  |

|                 |       | 1.1.2  | Operating Frequency & Integration Complexity     | 4  |

|                 |       | 1.1.3  | Commercial Availability & Scalability            | 4  |

| 2               | Bac   | kgrou  | nd and Literature Review                         | 6  |

|                 | 2.1   | Array  | s: Linear & Planar                               | 6  |

|                 |       | 2.1.1  | Array Factor                                     | 7  |

|                 |       | 2.1.2  | Mutual Coupling Effects                          | 11 |

|                 | 2.2   | Beam   | forming Architectures                            | 13 |

|                 |       | 2.2.1  | Digital Beamforming                              | 13 |

|                 |       | 2.2.2  | Analog (RF) Beamforming                          | 14 |

|                 |       | 2.2.3  | Hybrid Beamforming                               | 15 |

|                 | 2.3   | Revie  | w of mmWave RF-BF Phased Arrays                  | 16 |

|                 |       | 2.3.1  | Initial Developments at V-Band (40 - 75 GHz)     | 20 |

|                 |       | 2.3.2  | Successive Developments at W-Band (75 - 110 GHz) | 23 |

|   |     | 2.3.3  | Current Developments at Ka-Band (27 - 40 GHz)           | 27 |

|---|-----|--------|---------------------------------------------------------|----|

|   |     | 2.3.4  | Implementation Summary                                  | 32 |

| 3 | Ant | enna-i | n-Package Design for RF Beamforming 28 GHz Applications | 33 |

|   | 3.1 | Projec | et Scope                                                | 33 |

|   |     | 3.1.1  | Components                                              | 34 |

|   |     | 3.1.2  | Constraints                                             | 34 |

|   |     | 3.1.3  | Specifications                                          | 35 |

|   | 3.2 | Radia  | tor Selection and Stackup Definition                    | 38 |

|   |     | 3.2.1  | Radiator                                                | 38 |

|   |     | 3.2.2  | RF PCB Stackup                                          | 40 |

|   | 3.3 | Anten  | na Element Analysis and Design                          | 42 |

|   |     | 3.3.1  | Single Element                                          | 42 |

|   |     | 3.3.2  | Feed Line                                               | 45 |

|   | 3.4 | Planai | Array Analysis and Design                               | 47 |

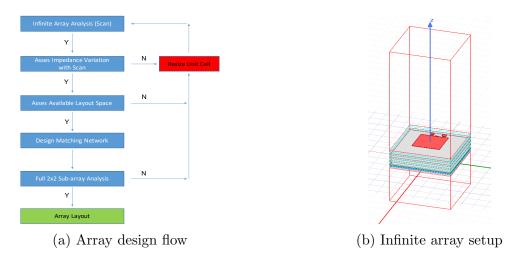

|   |     | 3.4.1  | Infinite Array and The Unit Cell                        | 48 |

|   |     | 3.4.2  | Matching Network                                        | 49 |

|   |     | 3.4.3  | 2x2 Antenna Sub-Array                                   | 50 |

|   |     | 3.4.4  | 4x4 Antenna Array                                       | 53 |

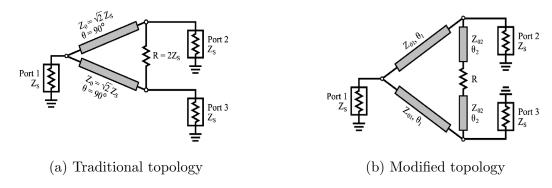

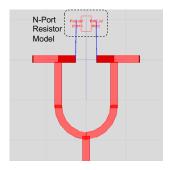

|   | 3.5 | RF Po  | ower Combiner / Splitter                                | 53 |

|   |     | 3.5.1  | SMD Packaging, Placement and Wilkinson Topology         | 54 |

|   |     | 3.5.2  | Design, Layout Verification and Analysis                | 55 |

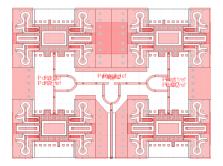

|   | 3.6 | Phase  | d Array PCB Layout                                      | 57 |

|   |     | 3.6.1  | Board Level I/O                                         | 59 |

|   |     | 3.6.2  | SMD Component Placement                                 | 61 |

|   |     | 262    | Solder Meek Definition                                  | 61 |

| 4            | Ant   | enna-in-Package Design as a Transmitter Observation Receiver | 63 |

|--------------|-------|--------------------------------------------------------------|----|

|              | 4.1   | Traditional TOR Architectural Limitations                    | 64 |

|              | 4.2   | Proposed Architecture                                        | 65 |

|              | 4.3   | TOR Integrated Antenna-in-Package                            | 66 |

|              |       | 4.3.1 Coupling Characteristics                               | 68 |

| 5            | Tes   | t Fixture Measurements and Simulation Validation             | 70 |

|              | 5.1   | Single Antenna Element                                       | 71 |

|              | 5.2   | Two Element Array                                            | 72 |

|              | 5.3   | Four Element Array                                           | 74 |

|              | 5.4   | RF 1:2 Power Combiner                                        | 76 |

| 6            | Con   | aclusion                                                     | 78 |

|              | 6.1   | Future Works                                                 | 80 |

| $\mathbf{R}$ | efere | nces                                                         | 83 |

## List of Tables

| 3.1 | IPC Class 2 PCB Fabrication Constraints    | 36 |

|-----|--------------------------------------------|----|

| 3.2 | AiP System Requirements and Specifications | 37 |

| 3.3 | Stackup Material Properties [1, 2]         | 40 |

# List of Figures

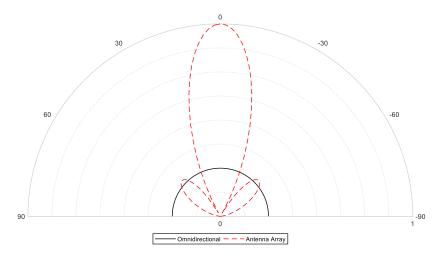

| 1.1  | Radiation patterns of an omnidirectional and antenna array                                                          | 3  |

|------|---------------------------------------------------------------------------------------------------------------------|----|

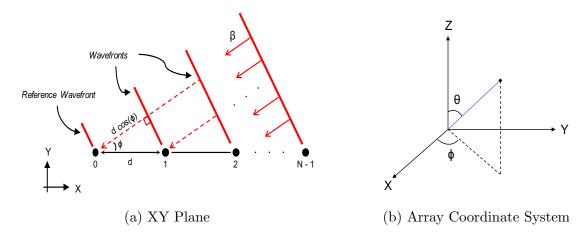

| 2.1  | An N isotropic element linear array operating in RX mode                                                            | 7  |

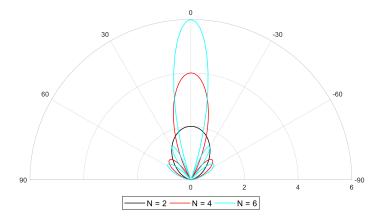

| 2.2  | Array factor for a uniformly excited N element linear array, $(\phi_o = 0)$                                         | 8  |

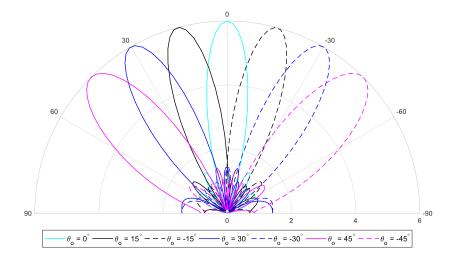

| 2.3  | $AF(\phi,\theta)$ for various scan angles of a six element UE linear array, $(\phi_o=0)$ .                          | 9  |

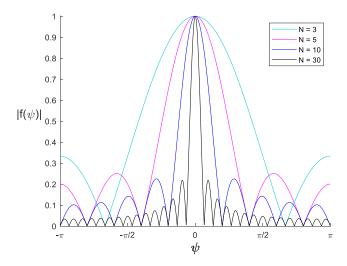

| 2.4  | Normalized array factor for an N element UE linear array                                                            | 10 |

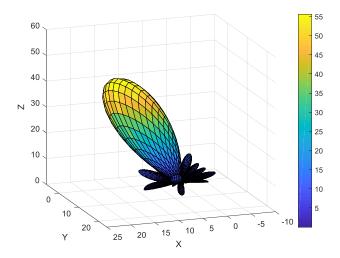

| 2.5  | AF $(\phi, \theta)$ of an 8 x 8 UE planar array, main beam direction $(\phi_o = 45^{\circ}, \theta_o = 30^{\circ})$ | 11 |

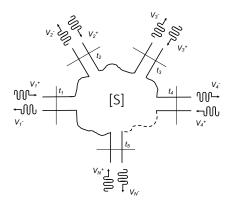

| 2.6  | An arbitrary N-Port microwave network [3]                                                                           | 12 |

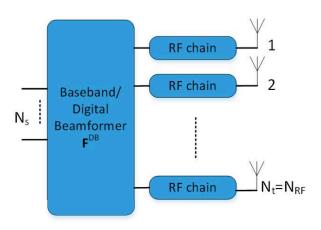

| 2.7  | Digital beamforming [4]                                                                                             | 14 |

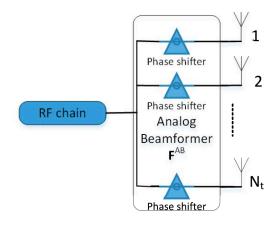

| 2.8  | Analog beamforming [4]                                                                                              | 15 |

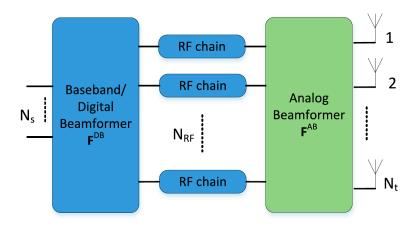

| 2.9  | Hybrid beamforming [4]                                                                                              | 16 |

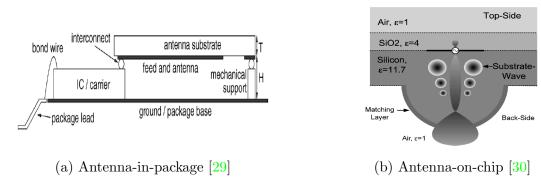

| 2.10 | Initial proposed integration schemes                                                                                | 19 |

| 2.11 | 60 GHz LTCC antenna-in-package [5]                                                                                  | 21 |

| 2.12 | 60 GHz Organic antenna-in-package [6]                                                                               | 22 |

| 2.13 | 60 GHz PCB based antenna-in-package [7]                                                                             | 23 |

| 2.14 | IBM Research W-Band phased array stackup and module integration scheme                                              | 24 |

| 2.15 | IBM Research W-Band phased array implementation                                                                     | 25 |

| 2.16 | IBM Research Enhanced W-Band phased array implementation                                                            | 26 |

| 2.17 | W-Band antenna-on-PCB phased array implementation                                                                   | 27 |

| 2.18 | 28 GHz Organic AiP [8]                                                                                              | 28 |

| 2.19 | 28 GHz antenna-on-PCB phased array implementation                                   | 30 |

|------|-------------------------------------------------------------------------------------|----|

| 2.20 | 28 GHz Fabricated Antenna-on-PCB [9]                                                | 31 |

| 2.21 | $28~\mathrm{GHz}$ antenna-on-PCB phased array implementation with a triangular grid | 31 |

| 3.1  | AWMF 0158 Landing Pad                                                               | 35 |

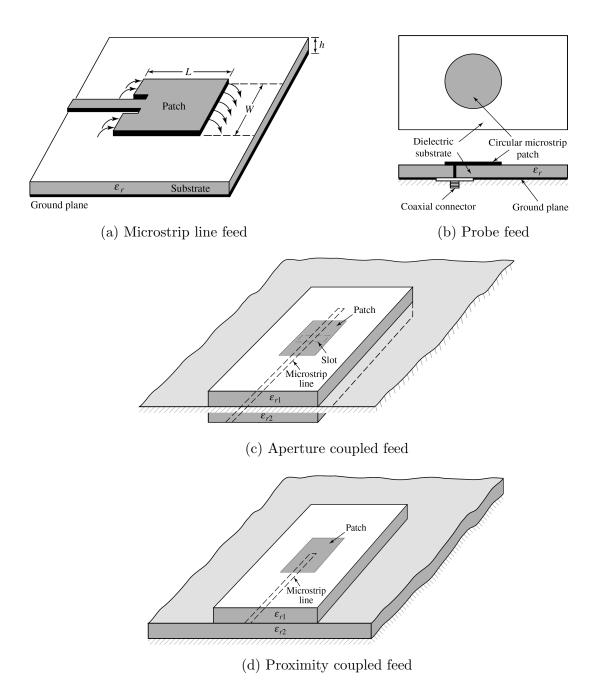

| 3.2  | Feed structures for patch antennas [10]                                             | 39 |

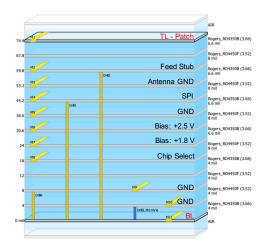

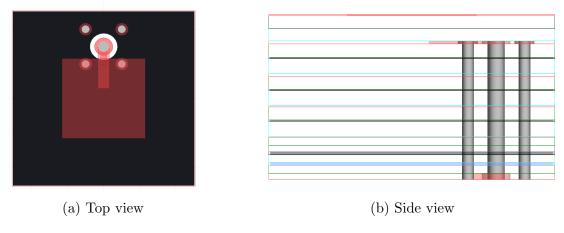

| 3.3  | RF PCB stackup, vertical schematic and via definitions                              | 41 |

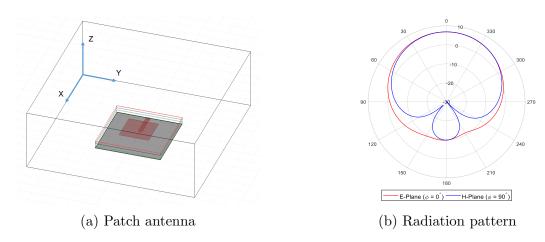

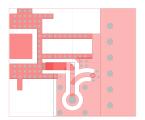

| 3.4  | HFSS 3D Layout model of 28 GHz proximity coupled patch antenna                      | 43 |

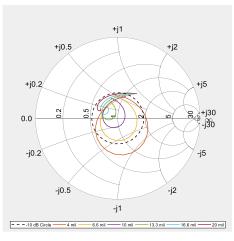

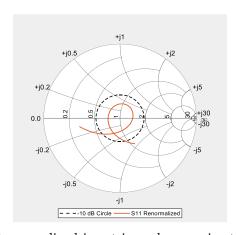

| 3.5  | Impedance contour variation for designed antenna, from 25 GHz - 31 GHz              | 44 |

| 3.6  | Full stack antenna model with vertical transition                                   | 45 |

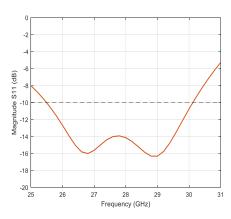

| 3.7  | Antenna input impedance for 25 GHz - 31 GHz and radiation pattern                   | 46 |

| 3.8  | Renormalized antenna input impedance for 25 GHz - 31 GHz                            | 46 |

| 3.9  | Design flow and simulation setup                                                    | 47 |

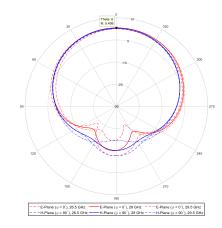

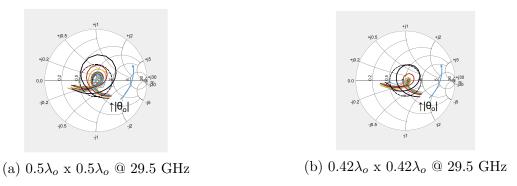

| 3.10 | Infinite array analysis for $\theta_o = +/-45^\circ$ in E,H and D planes            | 48 |

| 3.11 | Designed $0.42\lambda_o \ge 0.5\lambda_o$ unit cell                                 | 49 |

| 3.12 | Designed bottom layer MN and full stack antenna                                     | 49 |

| 3.13 | Designed full stack proximity coupled patch antenna with MN $\dots$                 | 50 |

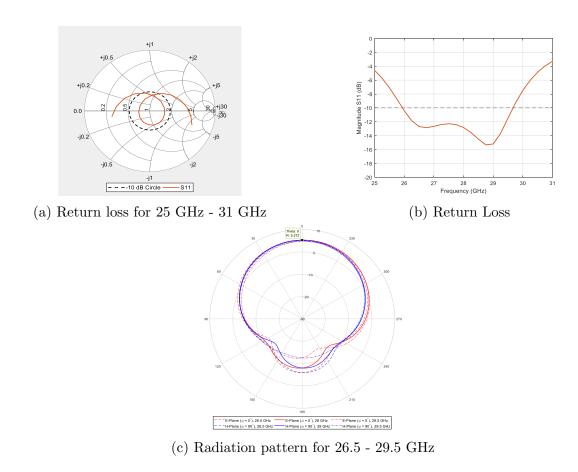

| 3.14 | 2x2 sub-array full stack HFSS 3D layout model and results                           | 51 |

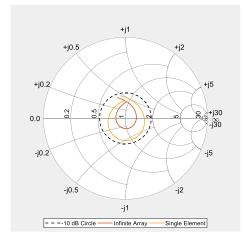

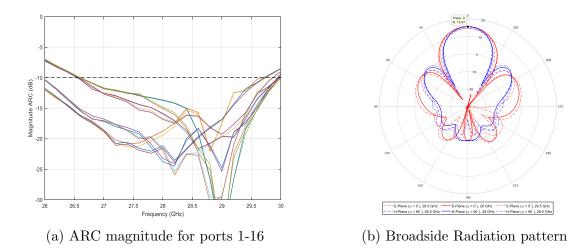

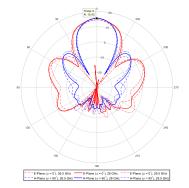

| 3.15 | $2\mathrm{x}2$ sub-array HFSS full wave analysis for 26.5 GHz - 29.5 GHz $\ \ldots$ | 52 |

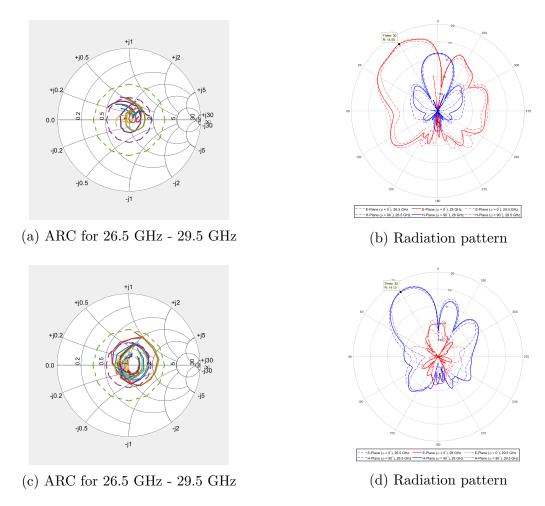

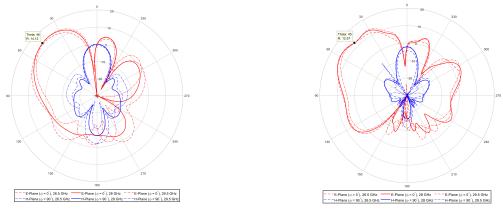

| 3.16 | 4x4 antenna array HFSS full wave simulation results                                 | 53 |

| 3.17 | Wilkinson power combiner [11]                                                       | 54 |

| 3.18 | Designed wilkinson power combiner and array implementation                          | 55 |

| 3.19 | Simulated response of designed wilkinson power combiner                             | 56 |

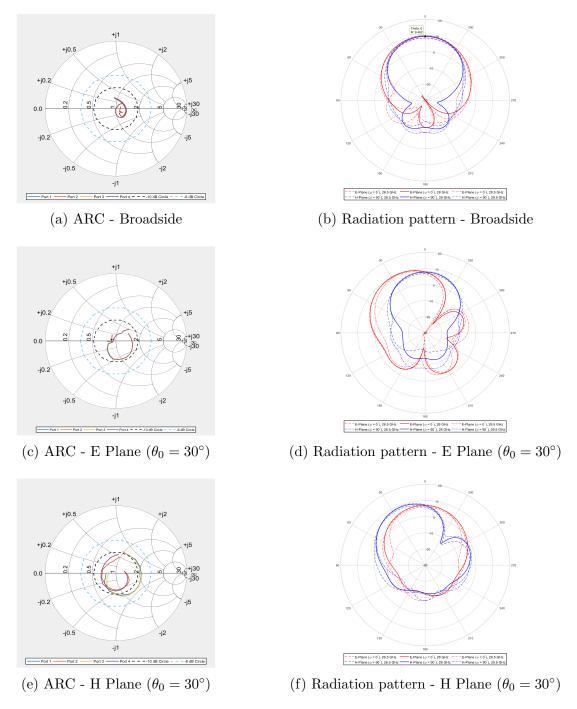

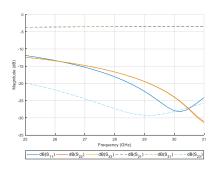

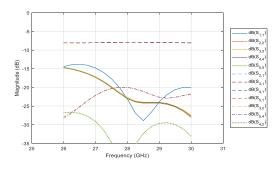

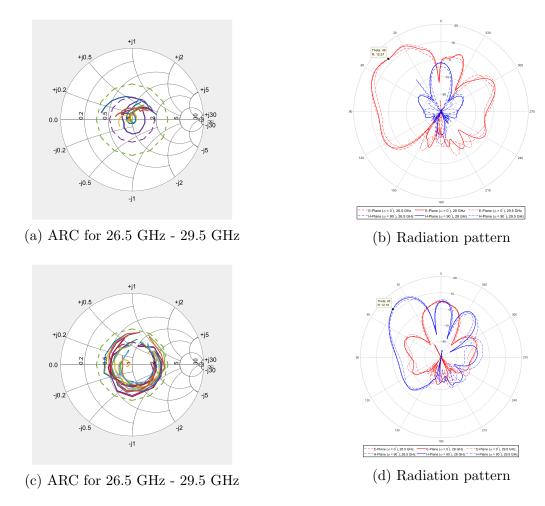

| 3.20 | Isolation, input ARC and synonymous "S21" for scan $\theta_o = +/-45^\circ$ in E, H | 57 |

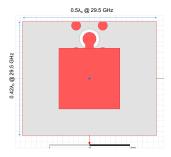

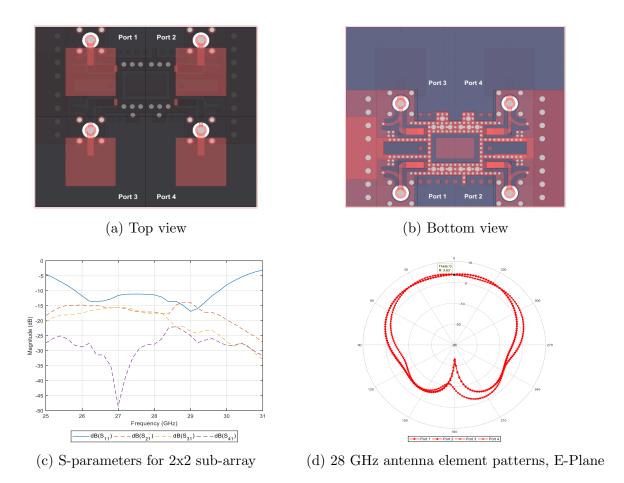

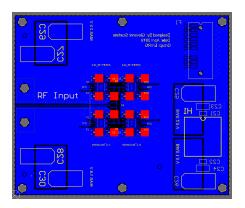

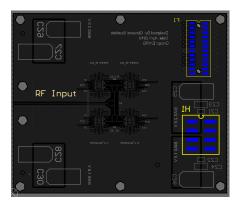

| 3.21 | HFSS full package layout                                                            | 58 |

| 3.22 | Full package layout: Broadside Performance                                          | 58 |

| 3.23 | Full package layout: $\theta_o = +30^{\circ}$ , E and H Performance                 | 59 |

| 3.24 | Full package layout: $\theta_o = +45^{\circ}$ , E and H Performance                 | 60 |

| 3.25                                   | Radiation pattern deformation: Array vs full package                                                     | 61                   |

|----------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------|

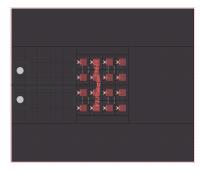

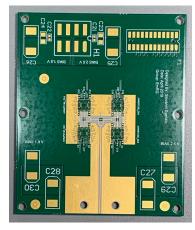

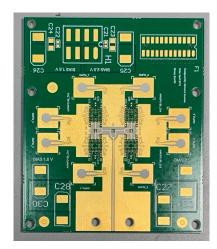

| 3.26                                   | Designed 28 GHz RF beamforming 4x4 AiP                                                                   | 62                   |

| 3.27                                   | Power amplifier decoupling capacitor placement                                                           | 62                   |

| 3.28                                   | AWMF 0158 bottom solder mask definition                                                                  | 62                   |

| 4.1                                    | Spectral regrowth due to power amplifier non-linearity                                                   | 64                   |

| 4.2                                    | Impractical TOR implementation for mmWave massive MIMO systems $$                                        | 65                   |

| 4.3                                    | Proposed TOR implementation for mmWave massive MIMO systems                                              | 66                   |

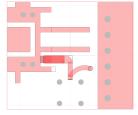

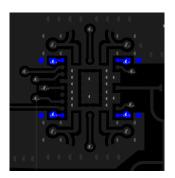

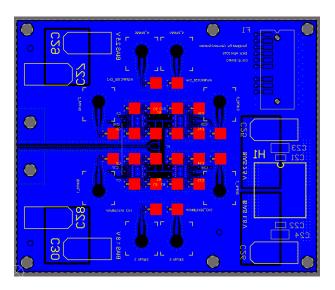

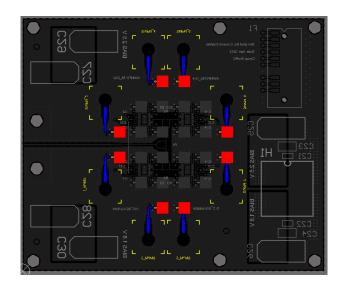

| 4.4                                    | PCB layout view                                                                                          | 67                   |

| 4.5                                    | TOR probing antenna arrangement                                                                          | 67                   |

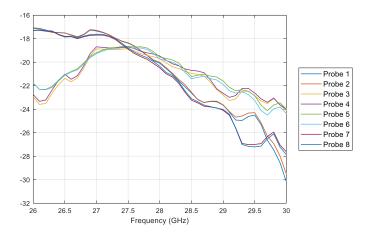

| 4.6                                    | Normalized probe frequency response with array main beam pointed broadside                               | 68                   |

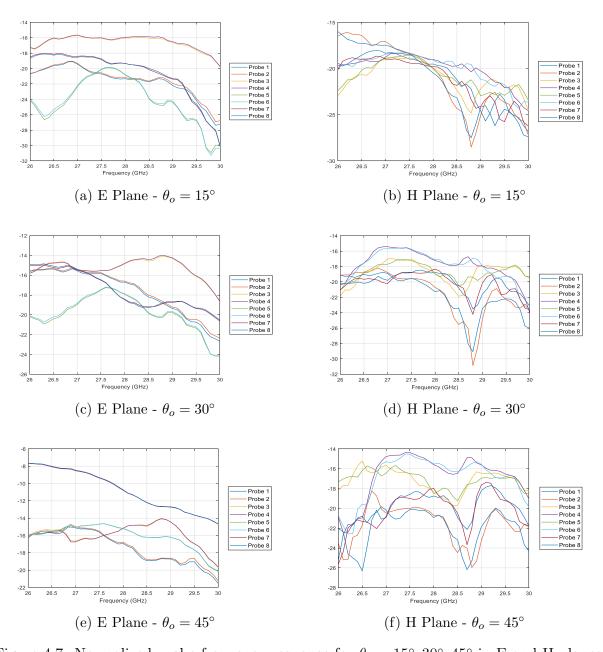

| 4.7                                    | Normalized probe frequency response for $\theta_o=15^\circ, 30^\circ, 45^\circ$ in E and H planes        | 69                   |

| 5.1                                    | Designed TRL calibration kit                                                                             | 71                   |

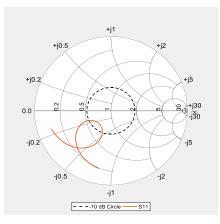

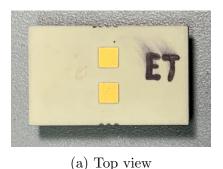

| 5.2                                    | Test fixture: single antenna element                                                                     | 71                   |

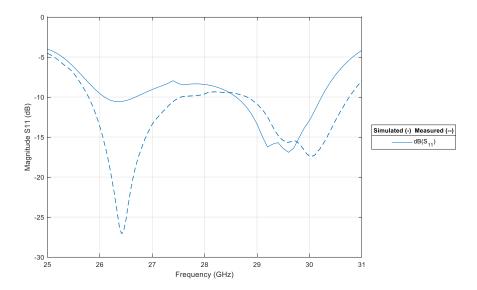

| 5.3                                    | Antenna element simulation comparison to measurement after TRL calibration                               | 72                   |

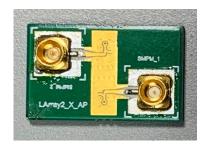

| 5.4                                    | Test fixture: two element array                                                                          | 73                   |

|                                        |                                                                                                          | •                    |

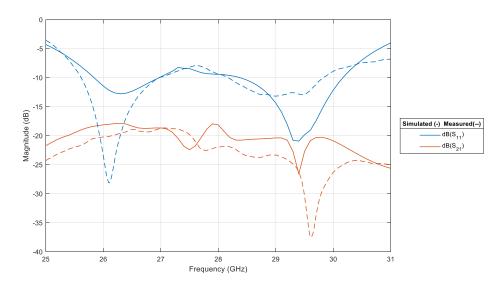

| 5.5                                    | Two element simulation comparison to measurement after TRL calibration                                   | 73                   |

|                                        |                                                                                                          |                      |

| 5.6                                    | Two element simulation comparison to measurement after TRL calibration                                   | 73                   |

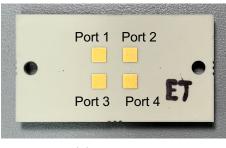

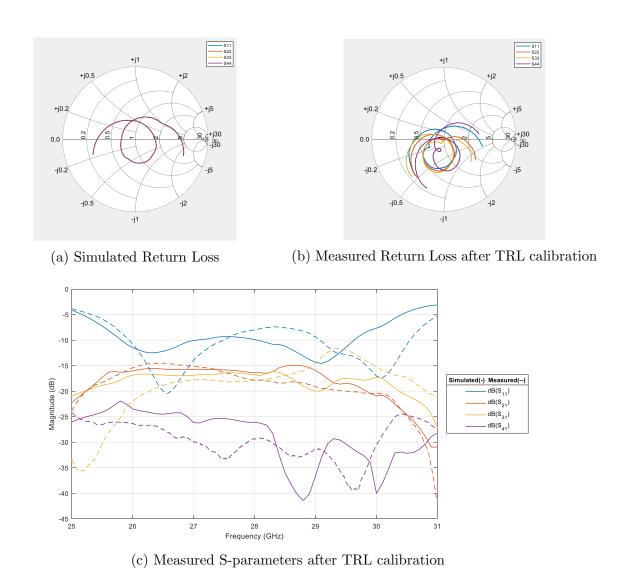

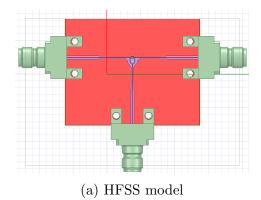

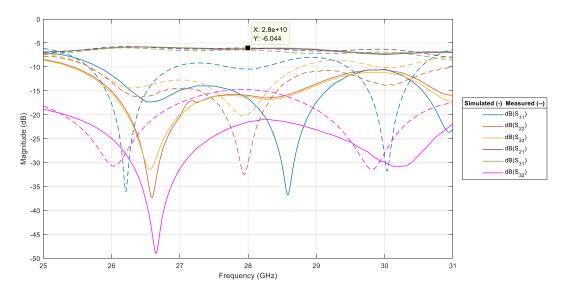

| 5.6<br>5.7                             | Two element simulation comparison to measurement after TRL calibration  Test fixture: four element array | 73<br>74             |

| 5.6<br>5.7<br>5.8                      | Two element simulation comparison to measurement after TRL calibration  Test fixture: four element array | 73<br>74<br>75       |

| 5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>6.1 | Two element simulation comparison to measurement after TRL calibration  Test fixture: four element array | 73<br>74<br>75<br>76 |

## Chapter 1

## Introduction

Current wireless infrastructure and user equipment are mainly operating below 6 GHz. Going forward, to meet the demands for ultra-broadband mobile access and the requirements enforced by the internet of everything, wireless networks will have to extend to the untapped millimeter-wave (mmWave) frequency bands [12]. Yet, this will impose significant challenges to development of the underlying infrastructure given the very high path loss at mmWave. First, wireless communication will need to migrate from a broadcasting based transmission to a directive one. Second, the wireless networks will need to be ultradense with very small cells and consequently interferences will need to be well handled. To tackle these challenges, large scale multiple antenna technology and the associated beamforming and multi-user massive Multiple Input Multiple Output (MIMO) features will be paramount [12]. In fact, the successful deployment of the future wireless infrastructure, commonly called 5G, is predicated to the development of high performance mmWave large scale multi-antenna systems.

## 1.1 Motivation

Over the years, wireless infrastructure has evolved and society has seen first through fourth generation networks. Within the past five years, many services previously bound by wire transmission have made way to being available over wireless and as of 2014, global mobile traffic saw an increase of roughly 70%. Smartphones contributed to a significant portion of this growth, responsible for near 88% of the total traffic [13, 14]. Services like video streaming, with the desire for ultra high definition and reduced latency, constitute up to a 51 percent of this mobile traffic volume [15]. Technology giants like Cisco Systems

projected in 2016, a network involving greater than 50% of its devices being smart devices by 2019. Recent publications by Cisco suggest this to be true at 44% for smartphones alone [16]. Factoring in that the average user is expected to download near 1 terabyte of data annually by 2020 [13], the existing wireless network infrastructure is in question.

Companies are exercising their imagination and developing new use cases for wireless, with applications in augmented reality, online gaming, video conferencing, financial technologies and electronic health care. Furthering this, developments in internet of vehicles (IoV), in addition to internet of things (IoT), device to device (D2D) and machine to machine (M2M) communications, yield extreme stress for the network. With 4G LTE technology, the theoretical limitations on the downlink speed place data rates near 150 Mbps, supporting a maximum of 600 users per cell. Knowing that IoT and M2M look to push cell capacity to tens of thousands of users per individual cell, solutions are under development to tackle mass congestion [13, 17, 18].

Capacity, or the maximum data rate that can be achieved by a communication channel, depends highly on available bandwidth, spectral efficiency and in fact, cell size [13, 19]. In an effort to alleviate the problems foreseen with existing technologies, portions of the frequency spectrum above the traditional "sweet spot" or "beachfront", 0 - 3 GHz, has been opened for commercial use. Given that a minute fraction of the frequency spectrum at mmWave (30 - 300 GHz) results in predominantly large available bandwidths, the data rate possibilities extend by a massive one to two orders of magnitude from the current standing [13, 20].

## 1.1.1 Broadcasting versus Line of Sight

Extending network concepts to mmWave creates both advantages and disadvantages for the development of commercial technologies. Considering that an increase, as mentioned previous, in the number of connected devices is expected, cells can become over cluttered increasing user interference and effectively limiting the potential for efficient usage of the allotted spectrum. Combine the former with poor signal propagation characteristics in the mmWave band [12, 13], which immediately promote smaller cell sizes and shorter communication link distances, and the problem can be perceived as unsolvable.

In Electromagnetic Theory, there exists a relationship of inverse proportionality between the physical size of electronic structures and the representative wavelength corresponding to its operating frequency. Simply put, as operating frequency increases, electronics get smaller. Exploiting this fundamental concept allows one to overcome immediate challenges moving to mmWave, taking advantage of antenna design concepts previously

Figure 1.1: Radiation patterns of an omnidirectional and antenna array

deemed impractical, and ultimately driving the decision to migrate from broadcasting to line of sight communication.

Broadcasting, implemented in previous generation networks, utilizes omnidirectional antennas which transmit signal in all directions. To ensure the communication link can always be closed between the base station and the user in question, the power transmitted must be large enough such that the receiver can distinguish usable signal from noise. Transitioning to mmWave and broadcasting the same output power, the communication link would not work. Atmospheric absorption, rain and material penetration, all together account for much of the signal power reduction, significantly limiting the users ability to recover the information sent. Compensating for this, transmit power can be increased, but this not only decreases the efficiency of the link, but also presents extreme challenges in simply generating such high power at these frequencies. Therefore, broadcasting at mmWave is not very practical.

Line of sight communication employs the concept of antenna arrays, which utilizes multiple antennas in a given grid arrangement, at the expense of physical electronic structure size, to yield the ability to focus transmitted power in a specific direction. Focused energy introduces the potential for significant improvements; it can reduce the necessary transmitted power for a given link distance, or can evidently extend coverage range for the same output power. Further, knowing the aforementioned inverse relationship between size and frequency, mmWave operation can overcome large antenna array footprints, having arrays exhibit similar size to that of single sub 6 GHz omnidirectional antennas. In addition, focused energy introduces spatial diversity. Off axis communication experiences little to no

transmitted power, enabling users in densely populated areas to simultaneously occupy the same communication channel while not interfering with one another, effectively improving spectral efficiency by frequency reuse. Encompassed within all mentioned, is that of the communication link reconfigurability. By manipulation of the signal phase injected into each antenna within the array, power can be refocused in different directions, leaving no user at a disadvantage. This is the fundamental principle behind phased arrays.

#### 1.1.2 Operating Frequency & Integration Complexity

In transitioning to the mmWave bands, practical limitations restrict the potential upside phased arrays have to offer. For instance, considering traditional base station architecture, the antenna is isolated from the RF front end, via an isolator, permitting more appropriate conditions for the amplifying hardware. Scaling in frequency brings reduced component size and inhibits the usage of such dependable components. Further, parasitic effects from component packaging and placement pads weigh in considerably on simulation complexity, introducing new boundaries in the design stage.

In terms of system packaging, component integration presents significant challenges for the mmWave designer. Involved in the operation of phased array transceivers are RF front end modules (RFFEMs), low frequency and microwave signal distribution networks, power distribution and heat management devices. With module package sizes on the order of millimeters and interconnects involving wire bonds and flip chip based ball grid arrays, system packages need to be critically assessed to ensure optimal overall system performance. This deviates from the conventional design philosophy, which emphasizes the performance of individual components and lacks view of top level function.

## 1.1.3 Commercial Availability & Scalability

Phased arrays for mmWave are scarce in the current commercial landscape. Due to specification requirements of developing 5G systems, optimal antenna design requires exotic material selection, directly impacting cost and limiting the potential for small parties to develop phased array systems. Given the importance of mutual coupling and the negative effect beam scanning can have on the circuit level components driving the array, much of the design time is spent achieving a trade-off between usable bandwidth and scan range. Encompassed within all this is the manufacturability of the overall package. Designs are constrained within precision of the fabrication house in addition to that of the thermomechanical overhead imposed by the active circuitry [21].

Additionally, something that is not trivial is the scalability of the system. Much of the desirable attributes associated with phased arrays come from the array factor; enhanced gain, narrow beam width and beam reconfigurability, all stem from the inclusion of many antenna elements. Unfortunately, due to the nature of mutual coupling, system performance at one array size does not accurately predict the performance at another, if not handled. Edge elements exhibit vastly different characteristics and as a result, the designer must utilize a methodology that captures a balance between design time, performance and feasibility.

## Chapter 2

## Background and Literature Review

In recent years, the development of mmWave 5G transceivers has drawn a lot of attention from academia and industry, and significant improvement efforts have been made in semiconductor device technologies, mmWave circuits and transmitter and receiver architectures. Given the importance of directing transmitted signals in a specific direction and the ability to electronically steer according to a users position, much of the development extends itself to innovative architectural implementations and system optimization. At the forefront of the directional transceiver is the antenna array, an integral component that if handled improperly, can act as a bottleneck to the system. Much of the capabilities attainable by antenna arrays originate from thorough understanding of theoretical concepts and knowledge of circuit realizability. Possessing such enables the designer to place emphasis on integration of the antenna array with driving circuitry and peripheral components, increasing the potential for optimal system functionality.

## 2.1 Arrays: Linear & Planar

The antenna array model consists of two parts; the antenna element pattern and the array pattern, where all elements are replaced with isotropic point sources of equivalent amplitude and phase [22]. Due to the pattern multiplication principle, this model can be reinterpreted as a system consisting of a single antenna, referenced to a specific point in space, where its radiated fields are amplified by some multiple, deemed the array factor (AF) [10]. Because the total fields radiated by the array depend significantly on the array factor, an examination of the array factor formulation is paramount in the initial design of a phased array.

Figure 2.1: An N isotropic element linear array operating in RX mode

#### 2.1.1 Array Factor

Given an ideal phased array composed of N isotropic radiating elements, a relationship can be drawn between the angle of arrival (departure) of the incoming (outgoing) plane wave and the respective signal delay each antenna exhibits (introduces) within the array. The array factor devises the relationship between these two quantities and results in an antenna independent model parameter. Figure 2.1 illustrates a one dimensional N element linear array spaced distance d apart in the XY plane, where the spatial delay relationship of the  $n^{th}$  element,  $n\gamma$ , with reference to the edge element (n = 0), is the product of the wave vector magnitude,  $\beta$ , and the perpendicular distance between wave fronts,  $d\cos(\phi)\sin(\theta)$ .

$$\gamma(\phi, \theta) = \beta d \cos(\phi) \sin(\theta) \tag{2.1}$$

Knowing a plane wave yields equal amplitude across a given wavefront, labelled here as unity for simplicity, and isotropic sources are spatially independent, each antenna generates signals of equal amplitude with phase delay corresponding to spatial delay,  $\gamma$ . The array factor therefore, can be written as the summation of these signals, weighted individually by each respective RF chain in amplitude,  $A_n$ , and linear phase,  $\alpha$ ,

$$AF(\phi,\theta,\alpha) = I_0(\alpha) + I_1(\alpha) e^{j\gamma(\phi,\theta)} + \dots + I_{N-1}(\alpha) e^{j(N-1)\gamma(\phi,\theta)} = \sum_{n=0}^{N-1} I_n(\alpha) e^{jn\gamma(\phi,\theta)} \quad (2.2)$$

where  $I_n(\alpha) = A_n e^{jn\alpha}$  and is the weighting factor of the  $n^{th}$  RF path.

Figure 2.2: Array factor for a uniformly excited N element linear array,  $(\phi_o = 0)$

Assuming uniform excitation (UE) such that  $A_0 = A_1 = A_2 = \cdots = A$  and defining  $\psi = \alpha + \gamma(\phi, \theta)$ , the array factor can be rewritten in an easy to interpret form that illustrates the significance of the array principle.

$$AF(\psi) = A \sum_{n=0}^{N-1} e^{jn\psi}$$

(2.3)

By simple examination, one can notice the function evaluates to a maximum of AN for  $\psi=0$ . This dictates that the array factor maximum scales linearly with the number of elements, N, seen in Figure 2.2. Additionally, a closer examination of the factor  $\psi$  suggests that this maxima can be obtained for different angles of arrival, or departure, implying the phased array can refocus its maximum radiation direction by adjusting the phase weighting parameter,  $\alpha$ .

$$\alpha = -\gamma(\phi_0, \theta_0)$$

=  $-\beta d \cos(\phi_0) \sin(\theta_0)$  (2.4)

$(\phi_0, \theta_0)$  = main beam pointing direction

Forcing  $\psi = 0$ , the linear phase relationship given by equation (2.4) is obtained. Utilizing this and compensating for the spatial delay in the RF chain is one of the phased arrays most substantial functions, yielding an extremely versatile device that can maximally combine

Figure 2.3: AF $(\phi, \theta)$  for various scan angles of a six element UE linear array,  $(\phi_o = 0)$

at any angle of arrival  $(\phi_0, \theta_0)$ . This is illustrated in Figure 2.3. Given antennas usually conform to the principle of reciprocity, this is also true when the array is transmitting.

Previously mentioned, one of the advantages to antenna arrays was the ability to focus energy such that users could enforce frequency reuse in a given high density cell. Practically, this can be achieved by extremely precise radiation patterns. When the array factor is rewritten in the normalized form of  $|f(\psi)|$ , the significance of the number of elements is further enforced.

$$|f(\psi)| = \left| \frac{\sin(\frac{N\psi}{2})}{N\sin(\frac{\psi}{2})} \right|$$

(2.5)

$$\psi = \frac{2m\pi}{N} \text{ for existence of a null}$$

(2.6)

By simple examination of the first array factor null,  $|f(\psi)| = 0$ , m = 1, due to the inverse proportionality in relation (2.6), an increase in the number of elements enforces the first null at a reduced value of  $\psi$ . This implies a reduction in the main beam width for an increase in the number of elements, as illustrated in Figure 2.4. Moreover, it can easily be seen that for an increased N the side lobe peaks decrease. This further aids in the concept of frequency reuse in dense coverage areas.

Figure 2.4: Normalized array factor for an N element UE linear array

Exploiting the concepts discussed with respect to linear arrays presents limitations in practice. Versatility is at a minimum when scan functionality is of priority. Linear arrays are subject to severe scan restrictions where beam steering is confined to a single plane. In the ever evolving landscape, many applications call for the ability to scan in both principal planes, ( $\phi = 0^{\circ}, 90^{\circ}$ ), alleviating many of the potential mechanical dependencies in design. Additionally, employing linear arrays that look to harness the advantages of antenna array gain via many antenna elements is considerably problematic. Given the array scales in one dimension, it is most suitable to achieve such characteristics in a smaller form factor. Utilizing a multidimensional array permits the user to attain such functionality in a smaller form factor, albeit without the introduction of new considerable affects.

For planar phased arrays where the z-axis is normal to the plane of the array, the array factor can be written as the product of two linear array factors, assuming the current distribution in all rows is similar, where the same is true for all columns [22, 10]. Under uniform excitation, it can be described using equation (2.7), where  $\alpha_x$ ,  $\alpha_y$  are independent variables.

$$AF(\psi_x, \psi_y) = A^2 \sum_{n=0}^{N-1} e^{jn\psi_x} \sum_{m=0}^{M-1} e^{jm\psi_y}$$

(2.7)

Figure 2.5: AF( $\phi$ ,  $\theta$ ) of an 8 x 8 UE planar array, main beam direction ( $\phi_o = 45^{\circ}, \theta_o = 30^{\circ}$ )

where,

$$\psi_x = \beta d_x \cos(\phi) \sin(\theta) + \alpha_x$$

$$\psi_y = \beta d_y \sin(\phi) \sin(\theta) + \alpha_y$$

To produce a single main beam directed toward angle  $(\phi_o, \theta_o)$ , relations (2.8) and (2.9) should be used, resulting in an array factor resembling that of Figure 2.5.

$$\alpha_x = -\beta d_x \cos(\phi_o) \sin(\theta_o) \tag{2.8}$$

$$\alpha_y = -\beta d_y \sin(\phi_o) \sin(\theta_o) \tag{2.9}$$

### 2.1.2 Mutual Coupling Effects

In section 1.1.2, the array factor was presented where by pattern multiplication, the total field could be computed through multiplication with the pattern of a single antenna element. This assumes that each antenna acts independently within the array and element currents are not affected by surrounding array radiators. This in practice is not the case. Termed mutual coupling, antennas in close proximity exhibit characteristics that are a

Figure 2.6: An arbitrary N-Port microwave network [3]

function of one another, where current in one element can be affected by direct radiation from another element, secondary reflections from surrounding media, or signal feed line leakage. General trends for mutual coupling consist of the following; with distance d, mutual coupling decreases by rate of  $1/d^2$ , element pattern characteristics are proportional to the level of coupling with narrow patterns yielding lower coupling than broad, element polarization perpendicular to element alignment yields increased coupling and most importantly, larger elements are known to exhibit less coupling [22].

The coupling phenomena manifests itself in alterations to the element pattern, changing the radiation characteristics of the array. From a microwave engineering perspective, this behaviour is characterized through off diagonal terms in the network scattering parameters,  $S_{ij}$ . Network scattering parameters relate voltage waves, both incident,  $V^+$ , and reflected,  $V^-$ , at each of the N ports within the microwave network (Figure 2.6), through the following relationship,

$$\begin{bmatrix} V_1^- \\ V_2^- \\ \vdots \\ V_N^- \end{bmatrix} = \begin{bmatrix} S_{11} & S_{12} & \cdots & S_{1N} \\ S_{21} & & \vdots \\ \vdots & & & \vdots \\ S_{N1} & \cdots & \cdots & S_{NN} \end{bmatrix} \begin{bmatrix} V_1^+ \\ V_2^+ \\ \vdots \\ V_N^+ \end{bmatrix} \quad \text{or} \quad [V^-] = [S][V^+]$$

(2.10)

where an entry in the scattering matrix is defined as,

$$S_{ij} = \frac{V_i^-}{V_j^+} \bigg|_{V_k^+ = 0 \text{ for } k \neq j}.$$

(2.11)

Seen from the perspective of one element, any reflected signal is a linear combination of the incident waves at all other ports, weighted by the off diagonal parameters. The result, an active reflection coefficient (ARC),  $\Gamma_i$ , given by (2.12), which governs the  $i^{th}$  antennas bandwidth. Due to its phasor dependence, the reflection coefficient retains the ability to change in both magnitude and phase with array scanning, presenting itself as a potential variable load to driving circuitry. Because of this, the active reflection coefficient extends itself as a key array performance metric and must be minimized for all elements, at a wide range of scan angles.

$$\Gamma_i = \frac{V_i^-}{V_i^+} = \sum_{j=1}^N \frac{S_{ij} V_j^+}{V_i^+}$$

(2.12)

## 2.2 Beamforming Architectures

Incorporating the antenna array into a system that yields both versatility and peak performance is a daunting task. At the forefront of the phased array system is the beamforming architecture, a block level implementation scheme that can severely enhance or hinder system capability dependant on the underlying use case. Many of the applications looking to exploit the massive MIMO concept at mmWave for improved spectral efficiency and path loss compensation present the designer with significant system level tradeoffs between total capacity, user flexibility, design complexity and power consumption. Three architectures are commonly implemented; digital, analog and hybrid.

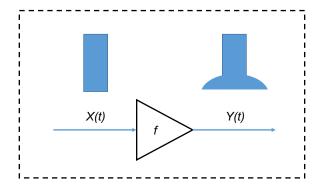

## 2.2.1 Digital Beamforming

Digital beamforming (D-BF), the most resourceful of the three beamforming architectures, is widely implemented in classical low frequency systems, enabling the potential for MIMO functionality [23]. Each antenna is met with its own RF chain ( $N_A = N_{RF}$ ), consisting of mixed signal (analog to digital (ADC) & digital to analog (DAC) converters), frequency translating and RF front end circuitry. Total number of users equals the total number of antennas, permitting the system to operate at highest spectral efficiency via digital precoding, and in a case where spatial multiplexing is not desired, the array can be reconfigured to serve a single user exploiting the array factor to enhance transceiver gain. Due to the large number RF chains however, power consumption exceeds all other beamforming architectures for same data converter resolution, with the move to mmWave exhibiting a

near linear relation between power and system bandwidth [23]. Further, increased system complexity introduces denser circuitry, new signal processing overhead and resulting latency [24]. Because of this, digital beamforming, without the help of lower resolution data converters and reduced system bandwidth [23], is said to be not feasible for mmWave massive MIMO operation [23, 24, 4].

Figure 2.7: Digital beamforming [4]

### 2.2.2 Analog (RF) Beamforming

Analog RF beamforming (RF-BF) combats power consumption at the expense of multiuser support. Largely adopted, RF beamforming depends on line of sight links, where it assigns the necessary magnitude and phase weighting for each antenna in the analog domain via variable attenuators and phase shifters. This results in lack of precoding flexibility and in turn places larger strain on the RF front end, limited by gain behaviour and bit resolution of the phase shifter [24]. The entire antenna array is driven with one RF chain  $(N_{RF} = 1, N_{RF} \neq N_A)$ , reducing system complexity, routing density and signal processing overhead, in addition to introducing considerable power savings. As a result, array size has less impact on power budget, where consumption depends solely on RF FEM efficiency, allowing for significantly larger array size, increased signal-to-noise ratio (SNR) and reduced susceptibility to co-channel interference [24].

Figure 2.8: Analog beamforming [4]

#### 2.2.3 Hybrid Beamforming

Hybrid beamforming (H-BF) looks to combine the benefits of both fundamental architectures; increased spectral efficiency and minimal power consumption. By limiting the number of data streams, using digital precoding for multistream transmission combined with analog beamforming for antenna gain, hybrid beamforming yields massive MIMO functionality with reduced complexity and power overhead. The architecture has two basic forms; sub-array and full array. The sub-array setup consists of multiple analog beamforming sub-arrays ( $N_{RF} \neq N_A$ ), where each sub-array can radiate its own independent beam. For non-line of sight channels, additional precoding can be performed digitally to utilize the entire array for the set of users. Enhancing usable gain at the expense of additional RF paths, the full array setup yields the same number of RF chains, however each chain now connects to all antennas [24, 4]. Determining the optimal number of RF chains, antenna elements and architectural arrangement depends on proper channel estimation and usability case, presenting a unique optimization problem to the designer.

Figure 2.9: Hybrid beamforming [4]

## 2.3 Review of mmWave RF-BF Phased Arrays

A comparison of the known beamforming architectures leads to the obvious conclusion that hybrid beamforming is the solution to mmWave phased array implementation. However, considering the integration complexity previously mentioned, efficiency of circuit level components at mmWave and availability of commercial front end modules that can yield even the most basic analog beamforming functionality, one can quickly conclude that RF beamforming is the necessary first step in the development of 5G phased array systems. RF beamforming has the core capabilities to showcase the potential of initial 5G network implementations and presents the necessary architectural simplicity to develop an appropriate methodology for phased array scaling. Due to this, section 2.3 focuses its review on mmWave RF beamforming phased array systems, with later sections outlining the design and implementation contributions.

Near the beginning of the  $21^{st}$  century, Parker and Zimmerman outlined state of the art phased array implementations and suggested future trends based off the foreseen benefits such systems could bring to radar and communication applications [25]. As of 2002, phased array implementation was passive, predominantly used for radar, where hardware design catered to the type of radar; ground, surface based, airborne or space based. Due to the lack of maturity and high cost associated with active devices, arrays were conveniently designed using corporate or series fed networks where loss minimization was of most importance. With the introduction of gallium arsenide (GaAs) monolithic microwave integrated circuit (MMIC) technology and automated module assembly techniques, cost associated with

active array development experienced an order of magnitude decrease. This meant that active arrays were sufficient for a subset of radar applications, but further cost and weight reductions were necessary to extend to space based radar [25].

Implementing an array involved architectural considerations, appropriate radiator selection and isolation investigations to determine the optimal active array formulation. At the time, many high tech array systems were based off the "brick architecture", where linear multi-module sub-arrays were stacked on top one another to yield one large array. Transmit and receive modules were kept separate, to achieve maximum isolation while lowering manufacturing cost and improving system yield. Front end circuitry and radiating elements were housed in separate modules than that of the beam steering control unit. Radiator selection criteria was based on achievable impedance bandwidth, scan angle, cost and installation environment, and applications requiring low profile designs used patch antennas. Parker and Zimmermann depicted a prime example of this; the L-Band array developed by NASA. This array utilized a multilayer planar structure, integrating both signal and power distribution networks in the system package, mounting MMIC's via flip-chip interconnect, foreshadowing the future of array implementation [25].

Beamforming architecture was under question, as analog beamformers were said to be complex and expensive and digital implementations were focused on available data converter technology, concerned that signal processing cores could not handle the potential system throughput. Nonetheless, Parker and Zimmerman claimed that the ultimate goal in 2002 was an active implementation that utilized a fully digital beamformer, projecting the eventual replacement of many analog implementations [25]. Bosch Satcom, Marconi Communications and the European Space Agency took an alternative approach, where Butz et al. investigated the potential for a hybrid, multi beam modular array implementation for Ka-Band satellite communication. The designed array utilized an analog beamformer MMIC control module and a solid state GaAs MMIC power amplifier (PA), housed on a low temperature co-fired ceramic (LTCC) substrate, and a radiating module consisting of 24 radiating patches. Adopting a sub-array architecture enabled testing feasibility, considering operating the entire array of 520 patches produced an astonishing 60 dBm effective isotropic radiated power (EIRP), with an even more astounding power consumption of 430 watts. This was the first reported multi-beam Ka-Band phased array, built from highly integrated modules, where 500 MHz impedance bandwidth and a scan range of 41.5 degrees off bore sight was attainable [26]. Butz et al. array implementation was state of the art and outlined one of the key problems future integrated array implementations would face; mass heat dissipation from amplifier circuits in a compact volume.

With continued development in process technologies, the scope of phased array integration soon extended its reach beyond GaAs to silicon (Si) based beamforming front ends.

Transistor cut-off frequencies approached 100 GHz, making silicon a prime candidate for mmWave systems. Nonetheless, key weak points in the silicon process, being low breakdown voltage, integrated passive losses, low power budget, cost and area constraints, made architectural decisions challenging [27]. Supporting such a transition however, was the known impact array systems had on communication links. An increase in signal to noise ratio (SNR) from antenna beamforming allowed the system to achieve data rates similar to single path systems, while operating on less total power, making silicon even more of a possibility.

In 2004, Hashemi et al. introduced an 8-Path fully integrated 24 GHz phased array receiver in silicon and outlined key circuit level and architectural trade offs in building silicon based integrated array systems [27, 28]. Hajimiri et al. summarized the advantages and disadvantages in different beamforming architectures, taking into consideration power consumption and array functionality. Within the context of band limited signals, true time delay was emphasized for proper array operation, as approximating a time delay with a phase shift introduced increasing distortion in the constellation for larger bandwidth to carrier ratio. Phase shifting at RF was not implemented due to large phase shifter loss at 24 GHz, and given the need for amplitude and phase decoupling in the beamformer, the phase shift was implemented in the local oscillator (LO) path. The outcome of this work, an 8 element analog beamforming phased array with gain of 61 dB, supported the transition to silicon based phased arrays.

In 2006, low cost packaging solutions for commercial use began to be investigated for the untapped mmWave V-Band (40 - 75 GHz) frequencies, in addition to W-Band (75 - 110 GHz). To develop packaging that was compatible with mmWave integrated circuits allowing for large impedance bandwidth and high system efficiency, researchers Thomas Zwick, Duixian Liu and Brian P. Gaucher proposed the usage of antennas integrated into the package, a possibility given the small wavelengths at 60 GHz. Zwick et al. developed a planar radiating structure printed on low cost substrate using printed circuit board technology (PCB) (Figure 2.10a). Interconnect loss to transceiver front end was minimized via solder ball mount (flip-chip interconnect), resulting in efficiency's of better than 80% [29].

In contrast to antenna in package, Babakhani et al. proposed the integration of radiating structures directly on the silicon chip at 77 GHz, a concept that could potentially improve system reliability and repeatably by ridding the complex arrangement of costly interconnects. Due to the challenges faced with power generation at mmWave, such an implementation was advantageous, however due to silicon exhibiting high dielectric constant and low substrate resistivity, antenna implementation was not quite trivial. Babakhani et al. showed that a simple top side radiating structure is not sufficient due to much of

the radiated power being absorbed into the silicon substrate. In addition, efforts at implementing a ground shield to redirect radiation resulted in reactive effects for low antenna to ground distance, and high power surface waves for large distances. Such a scenario attributed to increased heat dissipation, or edge radiation from surface wave exit. The solution proposed utilized a hemispherical silicon lens, with matching layer, which converted the trapped surface wave energy to radiation (Figure 2.10b). An increase in gain of 10dB was realized, with total antenna gain being 2dBi, a value still quite low [30].

Figure 2.10: Initial proposed integration schemes

As a result of such efforts, Duixian Liu and Brian Gaucher of T. J. Watson Research Center, IBM, outlined design considerations for mmWave antennas within a chip package in their 2007 IEEE conference proceeding. In their article, Liu and Gaucher identified key factors involved in packaged mmWave antenna design that is not traditionally of concern for sub 10 GHz. Characteristics like high bandwidth, efficiency and small form factor all originate from the underlying material selection, feed line connection architecture, manufacturing precision and potential surrounding electromagnetic interference (EMI) [31].

Material selection inherits two separate categories; antenna substrate and packaging material. Antenna substrates tend to have low dielectric constant and exhibit an ideal zero loss. However, at mmWave, many material specifications are measured at very low frequencies with many RF materials around 10 GHz. This introduces significant issues in the accuracy of the model representing the antenna structure. In addition, packaging materials are quite lossy, which can ultimately degrade system efficiency, and should be accounted for in the antenna design stage [31].

Feed line connections present multiple issues that can inherently impact signal quality and reduce assembly flexibility. At mmWave, wire-bonds tend to introduce inductive effects, degrading antenna impedance characteristics. Flip-chip mounting is generally preferred, however to enable such a low loss interconnect, the connecting transmission line

must yield the appropriate metal arrangement (ground-signal-ground) to be compatible with that of the flip-chip. Additional limitations on feed lines stem from the manufacturing precision as not all characteristic impedance's are achievable under a limited line width. This has the potential to lead to significant mismatch issues introducing the need for complex, lossy matching networks [31].

The ultimate challenge Liu and Gaucher stated for printed planar antennas was bandwidth gain product maximization given all the constraints. Of most importance was mentioned the suppression of surface waves, something that is usually strong in planar antennas and significantly deteriorates efficiency, while increasing the antennas dependence on the surrounding environment. Further, with the inclusion of active circuitry, surface waves can introduce new means on EMI. However, as a means to inhibit surface wave excitation, Liu and Gaucher identified a robust mechanism that involved the usage of metal rings surrounding the antenna structure, a common technique employed in designs of today [31].

#### 2.3.1 Initial Developments at V-Band (40 - 75 GHz)

Given the necessary requirement of 24 - 64 antennas for 60 GHz phased array systems to overcome high path loss and PA technology limitations, enabling high speed applications, much attention at first was given to the reduction of chip size. In 2009, as an attempt to rid the system of independent transmit and receive circuitry, Cohen et al. introduced the first bi-directional Tx/Rx four element phased array chipset for 60 GHz applications. This chipset took advantage of common elements like the phase shifter, combining network and frequency translating circuitry to enable a compact form factor comparable to that of a single Tx or Rx chip. Reported with the lowest power consumption and size at the time, and compatible with the time division duplex (TDD) communication standard, this enabled the possibility of significantly reduced antenna package size which would translate to board level scalability [32, 33].

Integrating active circuitry and antenna arrays via a low cost, high performing package was not a trivial task. In 2008 Antti E. I. Lamminen, Jussi Sily, and Antti R. Vimpari began investigating low-temperature cofired ceramic (LTCC) substrates for passive antenna array packaging [34], due to its superior electrical properties; low-loss dielectrics and conductors, good thermal conductivity, high degree of integration capability, low water absorption and good mechanical properties. Extending this to active arrays, Hong et al. developed a 24 element array integrated in an LTCC based package, driven by a single beamforming IC via flip-chip interconnect. Deemed Antenna-in-Package (AiP), the array design focused on differences that can arise between development for proto-type and mass market [5].

Hong et al. outlined that prototype development introduced nonstandard and non-guaranteed techniques that cannot allow realization of a truly low cost and high reliability package. Their attempt at developing an antenna in package for mass market, therefore lead to an eleven layer stackup consisting of  $100\mu$ m thick layers, with permittivity 5.8 and loss tangent 0.004 (Figure 2.11). Utilizing a circular stacked patch radiator with buried ground vias, suppressing surface waves and emulating a cavity, along with ground shielding to create a quasicoaxial feed, the 4x6 layout was capable of 9 GHz BW and 14.5 dBi gain. Full wave analysis allowed for accurate model representation, however due to incorporating a single densely populated beamformer chip, feed lines were uniquely designed and optimized to ensure matched phase response. This tedious task amounted to 0.7 dB amplitude and 8 degree phase deviation across lines, introducing potential impairments in the system. Gain oscillation were found to be present in measurement and later attributed to fabrication process deviations, as well as radiation from edge diffraction and surface waves [5].

Figure 2.11: 60 GHz LTCC antenna-in-package [5]

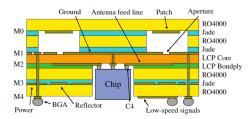

In an effort to allow the 60 GHz market to continue to flourish, Dong Gun Kam and fellow researchers developed an LTCC independent packaging solution that saw improved cost savings. Using standard organic PCB processes to combine newly developed alternative mmWave packaging material, liquid crystal polymer (LCP), with that of RF based glass reinforced PCB laminates, a package structure was developed that was compatible with mainstream manufacturing and assembly, conformed to the structure of the IC and yielded good RF performance and mechanical reliability. The stackup consisted of 5 stacked layers (6 metal); one LCP core, and two top and bottom Rogers 4000 (RO 4000) laminates. Jade adhesives were used to bind the RO laminates, meanwhile a combination of Jade and LCP bondyply was used for the core. An open air cavity at the bottom of the package allowed the beamformer IC to flip chip mount directly onto the inner LCP core layer, avoiding significant high loss via transitions (Figure 2.12). Material properties needed to be extracted before hand for EM simulation integration, due to lack of manufacturer knowledge at 60 GHz. A planar radiator utilizing an aperture coupled feed, with under patch air cavity

was used to improve bandwidth and radiation efficiency, while simultaneously isolating the radiator from the active circuitry. Utilizing quadrant symmetry, the feed line design was simplified with faster simulation times considering the usage of a single chip [6].

Figure 2.12: 60 GHz Organic antenna-in-package [6]

The array of 16 elements assembled in a ring shape, yielded higher side lobe levels than that of a 16 element linear array. Performance was adequate, with single element gain of 5.5 dBi, however significant variation of gain (2-8 dBi) was seen across different elements in the array. This was attributed to finite array behaviour, encompassing coupling to surrounding elements, and a truncated ground plane leading to parallel plate mode and surface wave radiation. The active return loss was assessed, incorporating the effect of coupling (simulations showed -17 dB), and the array exhibited 10 GHz bandwidth. Overall, measurement and simulations exhibited good correlation. A 5.6 Gbps link using a single carrier, 16 quadrature amplitude modulation (QAM) signal was achieved at a link distance of 4 meters. The author made note however, of the fact that assembling such a structure with new materials like LCP was challenging. LCP integrated into the PCB process caused adhesives to introduce voids, which later with gas trapped at high temperature triggered delamination [6].

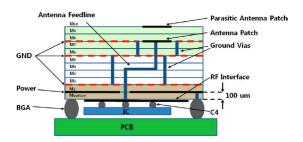

In 2012, knowing that high loss, low gain and low radiation efficiency on chip antennas were not the feasible mass market solution for commercial applications, Hong et al. continued their development in low cost packaging and introduced a third potential variant for the Antenna-in-Package design scheme. Also known as antenna on PCB, the designed package leveraged the existing FR4 PCB production line capabilities to yield an ultra low cost stackup constructed solely from FR4 materials; one 150 $\mu$ m core ( $D_k = 3.54$ ) and four 50 $\mu$ m prepregs ( $D_k = 3.59$ ), bonded via 5 $\mu$ m FR4 adhesives. The package combated potential signal loss from high loss laminates,  $tan(\delta) = 0.012$ , via vertical schematic layout and intelligent feed line design (Figure 2.13). Due to the limited via travel in the FR4 process, the vertical schematic assigned the antenna and feed line to the upper and middle layers respectively, leaving low frequency and power distribution on the bottom of the stack. A circular stacked patch radiator was implemented which utilized a surrounding

ground plane for the probe fed radiator in conjunction with alternating ground vias to minimize parallel plate and surface wave modes. The feed line made use of a coplanar waveguide (CPW) structure, with transitions ground shielded and treated as quasicoaxial. Resulting unit loss exhibited characteristics similar to that of LTCC, however impedance match could not be improved due to FR4 PCB process line width limitations [7].

Figure 2.13: 60 GHz PCB based antenna-in-package [7]

The antenna array was composed of a 4x2 arrangement of radiators, exhibiting a simulated -19 dB mutual coupling. Wafer probe measurements were conducted as IC implementation was to be investigated at a later date, however feed lines were designed with Y-axis symmetry assuming single chip integration. The antenna exhibited 4.1 dBi gain and 76% radiation efficiency and a bandwidth of 9 GHz (57 - 66 GHz). Measurement discrepancies again saw off axis radiation deviation from simulation, attributed to potential scattering and multipath effects along with finite ground edge radiation. Despite the high loss tangent and minor measurement setbacks, the efforts Hong et al. put forth introduced a viable alternative for mmWave phased array package design [7].

### 2.3.2 Successive Developments at W-Band (75 - 110 GHz)

Applications like imaging and radar make use of large available bandwidth and improved atmospheric absorption characteristics at W Band, however systems are still subjected to extreme pathloss given the inverse relationship between frequency and wavelength. W Band communication systems traditionally utilized waveguide interfaces with expensive modules and narrow beam high gain antennas to support high data rate links [35]. Taking advantage of phased array development at 60 GHz and harnessing spectrally efficient techniques, researches extended the capabilities of phased array systems upwards of 75 GHz.

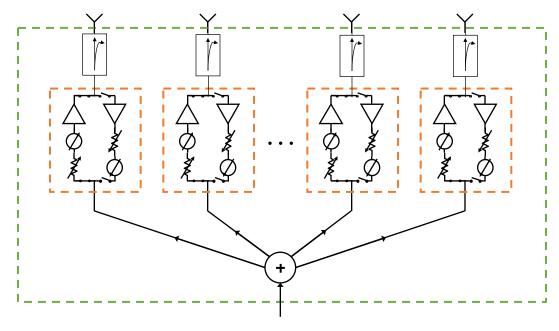

In 2013, great efforts by researchers at IBMs T.J. Watson Research Center were put into the development of a fully integrated dual polarization transceiver. Their 2013 conference proceeding titled "A Fully-Integrated Dual-Polarization 16-Element W-band Phased-Array Transceiver in SiGe BiCMOS" introduced a suitable, compact, low weight and low volume RFIC for W Band, which housed two independent chains per polarization. With the highest level of monolithic integration achieved in silicon at the time, the beamformer IC contained IF and LO distribution on chip, set up for operation in 16Rx-16Rx or 16Tx-16Rx simultaneously. The IC employed compact form factor to conform to half wavelength lattice spacing, enabling phased array solutions to potentially scale at the board level [36].

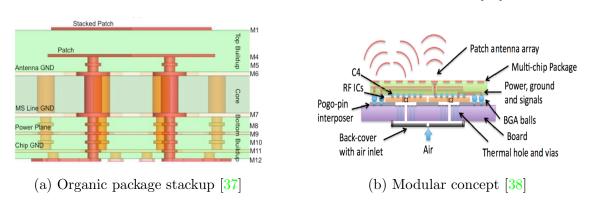

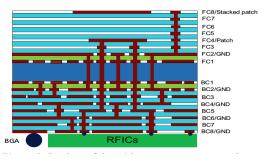

Implementing dual polarization antennas with fine pitch at W Band reserved itself as a challenge to many package manufacturers. In 2014, Liu et al. introduced a planar stacked patch antenna for organic antenna-in-package implementation. The dual polarized probe fed stacked patch harnessed a 12 metal layer stackup with 2 metal core and 5 metal top and bottom build ups exhibiting the same permittivity (Figure 2.14). The feed line consisted of a direct via with vertical ground shielding resembling that of coaxial line, that travelled from the fed patch layer (M4) down to the bottom layer (M12). The antenna exhibited 3 dBi peak gain and 8 GHz bandwidth, centered at 94 GHz with slight deviations from simulation due to metal fill requirements in the organic buildup process [37].

Figure 2.14: IBM Research W-Band phased array stackup and module integration scheme

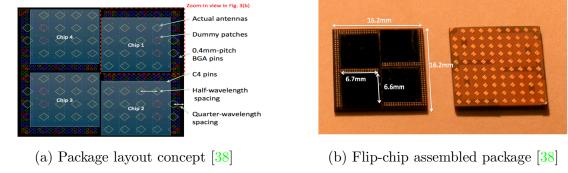

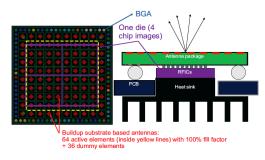

Integrating both the beamforming IC and antenna element, Gu et al. developed a 100 element array with 64 active elements and 36 dummy elements. By sheer integration complexity, a larger package allowed the implementation of 4 beamforming ICs at the expense of antenna fill factor (Figure 2.15). Fill factor for this array of 64% required random placing of dummy elements to minimize the impact on side lobes. Simulation times for the 128 port array took place in ANSYS High Frequency Structure Simulator (HFSS) full wave electromagnetic simulator, which took an elapsed time of 9 hours and

146 GB peak memory for a single frequency. The array was later simulated in 16 element quadrants, enhancing simulation time, where all other elements were assumed to exhibit same behaviour. The bottom buildup in the organic stack contained low frequency signal routing and extensive circuit-package-antenna co-design was performed to yield optimal placement of ICs to enable board level scaling [38].

Figure 2.15: IBM Research W-Band phased array implementation

The array assembly process incorporated underfill after IC attachment to enhance structural reliability and distribute thermal mistmatch stress. An evaluation board with high speed pogo pins test socket was used to monitor synthesizer locking and voltage and current consumption of power supplies, prior to package assembly on PCB. This module level testing further supported the scalable architecture. Final measurements illustrated cross polarization isolation of -25 dB for the full array with single elements exhibiting -15 dB. Similar gain variation to V-Band arrays was seen with -5 to +2 dBi measured. Maximum EIRP was measured at 28 dBm for 64 transmit antennas which indicated the feasibility of board level scalable phased arrays [38]

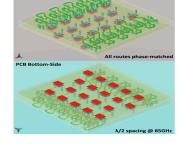

Further efforts at enhancing said design architecture came in 2018, where the organic stackup was extended to 16 metal layers, utilizing a super die composed of 4 SiGe RFICs. This introduced reduced assembly steps and improved overall assembly yield. Additionally, the array architecture was redefined, where 100 elements (64 active, 36 dummy) were still utilized, however fill factor was improved to 100%. By placing the dummys on the perimeter of the array, element pattern uniformity was enhanced without impacting active array performance. This employed an additional level of symmetry in feed line routing, where all lines were identical and phase matched. The array exhibited slightly higher bandwidth, simulated scan range of +/- 30 degrees, peak realized element gain of 2 dBi, -12 dB cross polarization isolation and -20 dB side lobes [39].

(a) 16 layer organic stackup [39] (b) Package top view and module assembly [39]

Figure 2.16: IBM Research Enhanced W-Band phased array implementation

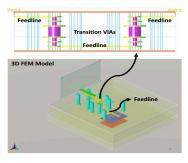

In contrast to the efforts by IBM research, antenna-on-PCB implementations at W Band have also been developed by Bell Laboratories, first in 2015, with a second generation implementation in 2018. Shahramian et al. introduced a 20 element transceiver chipset, where 16 elements were Tx (Rx) and 4 elements were Rx (Tx) [40]. Two chipsets were flip-chip mounted and drove two separate 20 element arrays, housed on the same PCB. One array was designed to operate in vertical polarization, while the other horizontal. This demonstrated dual polarization support for increased throughput. Utilizing an aperture coupled stacked patch radiator to isolate the radiator from the feed along with several coupling apertures to allow for the use of only a single via transition, the antenna design exhibited an astonishing 1 dB feed line loss measured at 100 GHz (Figure 2.17). Several 3D FEM based electromagnetic simulations were performed on the entire stackup with IC and PCB co-design via the inclusion of the flip-chip bump parasitic model, yielding optimal matching conditions. Package stackup was not disclosed.

Array implementation involved half wavelength lattice spacing, arranged in a triangular grid of 4x5 elements. Assembly incorporated underfill after RFIC placement to distribute added stress from thermal expansion mismatch between the RFIC and PCB at the attachment joints. First generation array prototypes exhibited 34 dBm EIRP across a wide bandwidth (80 - 90 GHz), with 14 dBi array gain, -15 dB side lobe level and - 25 dB cross polarization. A 20 meter link was measured achieving 4.8 Gbps under QPSK modulation scheme in each polarization [40]. Second generation designs exceeded the previous, achieving 8 Gbps at 20 meters, with a 1 meter link extending rates all the way to 30 Gbps using 64 QAM. Utilizing both arrays, 60 Gbps is achievable. Scan range included out to +/-30 degrees, and individual antenna radiation efficiency achieved an even more remarkable 92% at 90 GHz [35].

(a) Antenna feed line [35]

(b) Phased array antenna structure [35]

Figure 2.17: W-Band antenna-on-PCB phased array implementation

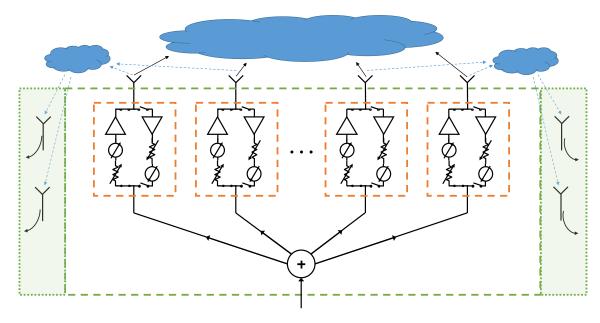

## 2.3.3 Current Developments at Ka-Band (27 - 40 GHz)

Developments at Ka Band have been most rapid due to the anticipation of upcoming 5G networks, with several variations of packaged phased arrays developed within the last two years. Knowledge acquired from extensive research conducted at V and W Band, allowed many of the designed 5G phased arrays to share similar buildup and package methodology. The package variants introduced almost 10 years prior have stood the test of time and with cost driving mainstream phased array implementation, materials like LTCC are seldom found in Ka Band antenna-in-package realization. As mentioned in the published article on W Band scalable phased arrays, fabrication of organic based packages exhibit lower tolerances than that of PCB fabricators [41]. However, due to the inverse relationship between frequency and wavelength, tolerance becomes effectively more tolerable at Ka Band, where wavelengths range from 7.49mm to 11.10mm as opposed to 2.73mm to 4.00mm at W Band.

Carrying over experience gained from W Band implementations, IBM research's first attempt at an organic antenna-in-package solution for 30.5 GHz took place in 2017 with the anticipation of their upcoming 32 element phased array transceiver IC with concurrent dual polarized beams [42]. Introduced in their publication titled "Antenna-in-Package Design Considerations for Ka-Band 5G Communication Applications" and abiding by fabrication constraints and limited material selection, a 14 metal layer stackup was implemented which consisted of a thicker core (4 metal layers), with thinner top and bottom buildups (5 metal layers each), all exhibiting relatively high loss tangent of 0.01. Governed by significant fabrication constraints, antenna design was constricted to limited via density, where three ground vias were used to shield the vertical quasicoaxial transition leading to 0.5 dB loss, with thicker core layer requiring larger via diameter and increased spacing, ultimately

placing limitations on line characteristic impedance. A dual polarized, probe fed stacked patch was utilized where patch corners were cut to modify resonance behaviour. Utilizing grounded metal rings (mentioned previous) to reduce surface wave excitation, the antenna was able to achieve 0.8 GHz bandwidth, 3 dBi gain and less that -20 dB mutual coupling. Impedance bandwidth outlined itself as the main bottleneck and was attributed to limited material selection with appropriate permittivities, low layer count resulting in lack of antenna volume, necessary requirement of half wavelength spacing for beamforming and dual polarization functionality restricting the number of usable bandwidth extension techniques [21].

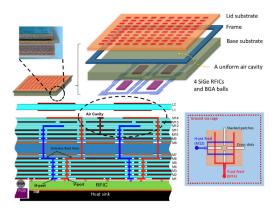

In an attempt to alleviate the impedance bandwidth limitations, IBM research introduced a second generation complex multi tier organic stackup which consisted of a 14 metal layer base, similar to previous, with the introduction of a 2 layer lid substrate and 2 layer frame for the formation of a uniform air cavity (Figure 2.18). Utilizing a dual polarized aperture coupled stacked patch with each polarization fed on separate layers, and harnessing the uniform air cavity for increased bandwidth, gain and reduced surface wave excitation, the antenna element was capable of 3.3 - 3.7 GHz bandwidth for each polarization. A prototype test vehicle was fabricated prior to array implementation which allowed researchers to investigate interconnect performance, package warpage and chip and board level reliability prior to full array implementation [43, 44].

Figure 2.18: 28 GHz Organic AiP [8]

Similar to the implementation at W Band, a 100 element array was implemented with 64 active elements and 36 dummy elements around the edge to improve element pattern uniformity, leading to 100% fill factor. Four 32 element RFICs with internal frequency translation are flip chip mounted with underfill, and the package is further mounted via

BGA to a breakout PCB housing IF, LO, control signals and bias. The array exhibited 54 dBm EIRP at broadside, with +/- 40 degree scan range in both principle E and H planes, for both polarizations. Using no calibration, the array was able to achieve -12 dB side lobe level and 20 dB deep pattern notches. Link measurements using two arrays, each with two single 64 element beams (one per polarization) and a carrier aggregated 8x100 MHz 256 QAM signal, resulted in an astounding 21 Gbps data rate. Extending the range to 50 meter and 19 meter through glass links, 6.7 Gbps raw data rate with 4-5% error vector magnitude (EVM) was achieved [43, 44]. IBM's research efforts resulted in state of the art performance at the expense of complex packaging and assembly.

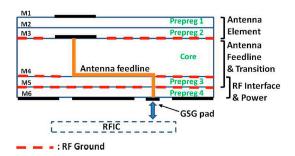

In contrast to organic implementations, in 2017, leveraging the lack of publications in packaged antenna array and transceiver implementations for 28 GHz, researchers Kim et al. of LG Electronics developed a 28 GHz CMOS direct conversion transceiver integrated with a 2x4 element antenna array in an PCB based antenna-in-package design. Design objectives included high EIRP, good beamforming capability and low in band signal distortion (EVM). Kim et al. proposed a stackup consisting of 8 metal layers, one  $400\mu$ m core ( $D_k = 4.4$ ,  $tan(\delta) = 0.006$ ), 3  $30\mu$ m prepreg layers on top and bottom ( $D_k = 3.7$ ,  $tan(\delta) = 0.007$ ), followed by top and bottom  $15\mu$ m solder resist ( $D_k = 3.5$ ,  $tan(\delta) = 0.015$ ). Utilizing a single probe fed patch with ground via fence to improve isolation from adjacent antennas, the antenna exhibited 1.5 GHz bandwidth and worst case -18 dB mutual coupling [45].

Array implementation involved half wavelength spacing to avoid potential grating lobes in the scan range, combined with high routing complexity due to single RFIC driving the array. The resulting feed line loss neared 1 dB with final array measurements indicated 13 dBi realized gain. Achievable scan range was limited to +/- 30 degrees, with broadside EIRP of 23 dBm for 8 elements active. Link measurements indicated that at 25 meters, 2.2 - 7.6% EVM was attainable dependant on array drive, where signal bandwidth was limited to 20 MHz, limiting system throughput [46].

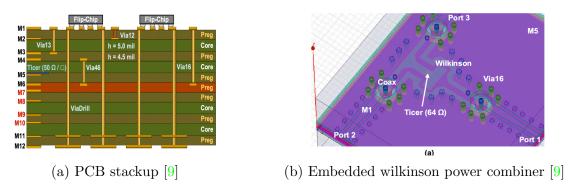

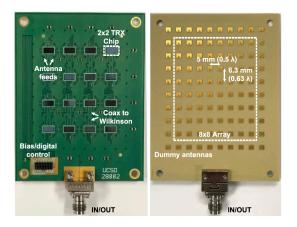

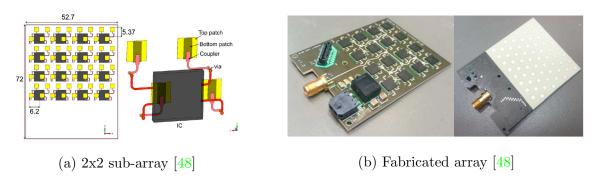

In an effort to demonstrate the sheer capability of a 5G link, researchers at UCSD leveraged the low cost nature of PCB fabrication in conjunction with symmetrical design to develop a scalable phased array capable of double digit gigabit speeds. Presented in their 2018 IMS conference proceeding [47] and later extended in their MTT transaction [9], Kibaroglu et al. introduced an antenna on PCB design that utilized a 12 metal layer symmetric stackup composed of megtron-6 core and prepreg layers ( $D_k = 3.3$ ,  $tan(\delta) = 0.005 @ 29 \text{ GHz}$ ), where design emphasis was placed on a 2x2 unit cell, which could be scaled to any effective size (Figure 2.19a). Master slave boundaries in HFSS were used to analyze single element behaviour in a periodic arrangement and resulting behaviour was combined with circuit simulator to design the antenna matching network and integrate their in house flip-chip bump parasitic model. A probe fed stacked patch was fed with

highly isolated feed lines to not introduce random amplitude and phase errors across lines and the resultant bandwidth was 4 GHz, with feed line loss ranging from 0.8 - 1.3 dB.

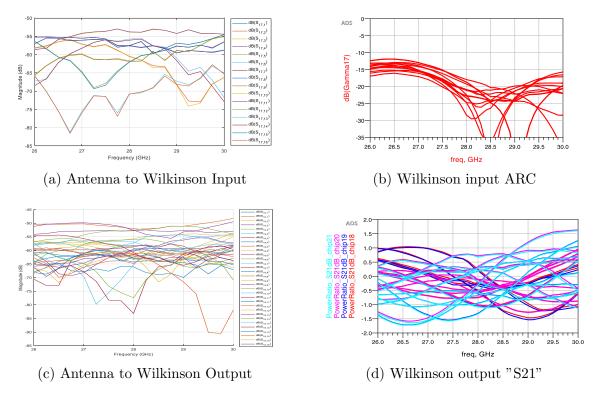

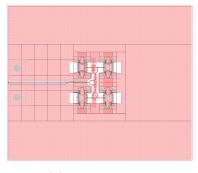

Figure 2.19: 28 GHz antenna-on-PCB phased array implementation