# 22-32 GHz Low-Noise Amplifier Design in 22-nm CMOS-SOI Technology

by

## Bolun Cui

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2019

© Bolun Cui 2019

#### Author's Declaration

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

This thesis explores the use of a 22-nm CMOS-SOI technology in the design of a twostage amplifier which targets wide bandwidth, low noise and modest linearity in the 28 GHz band.

A design methodology with a transformer-coupled, noise-matching interstage is presented for minimizing the noise factor of the two-stage amplifier. Furthermore, benefits of interstage noise matching are discussed. Next, a transistor layout for minimizing noise and maintaining sufficient electromigration reliability is described. It is followed by an analysis of transformer configurations and a transformer layout example is depicted.

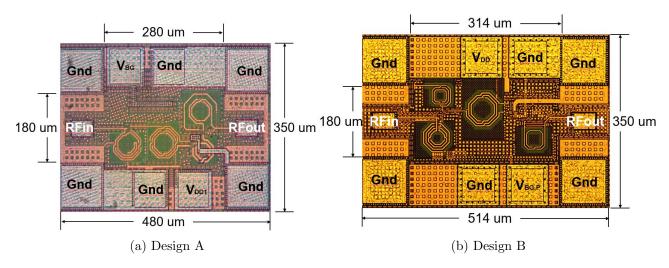

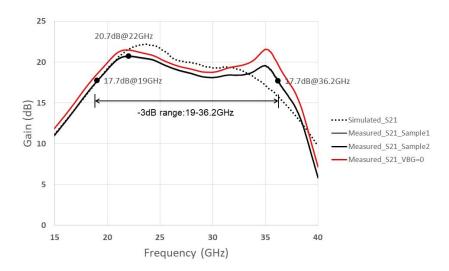

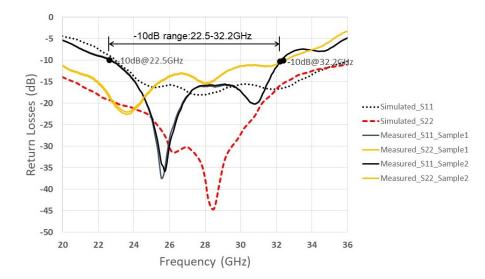

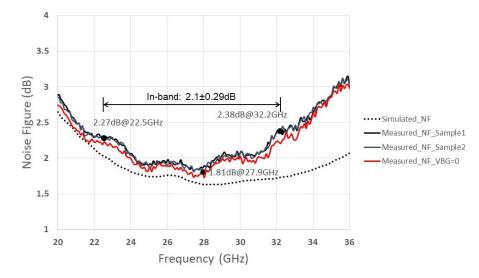

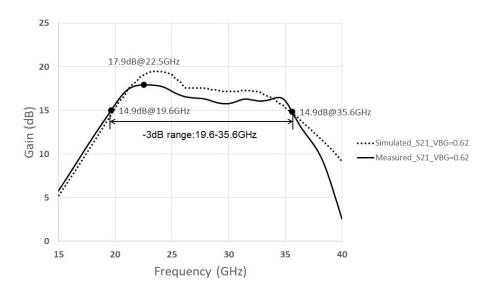

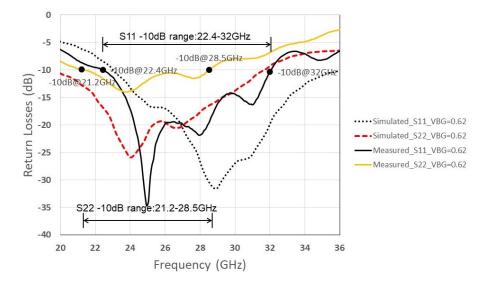

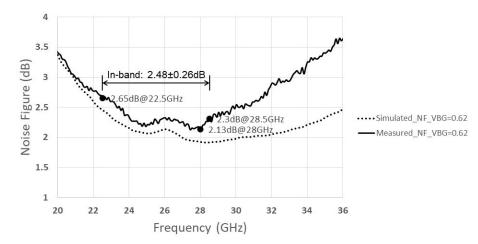

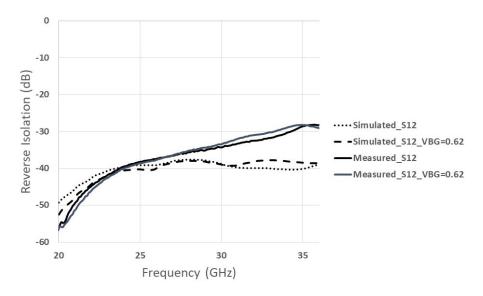

To verify the design methodology, two amplifier prototypes with noise-matching interstage were fabricated. Measurement shows that the first design achieves a peak gain of 20.7 dB and better-than-10-dB input and output return losses within a frequency range of 22.5 to 32.2 GHz. The lowest noise figure of 1.81 dB is achieved within the frequency range. Input IP<sub>3</sub> of -13.4 dBm is achieved with the cost of 17.3 mW DC power consumption. When the bias at the back-gate is lowered from 2 V to 0.62 V, the power consumption is decreased to 5.6 mW and the peak gain drops down to 17.9 dB. Minimum noise figure increases from 1.81 to 2.13 dB and input IP<sub>3</sub> drops to -14.4 dBm.

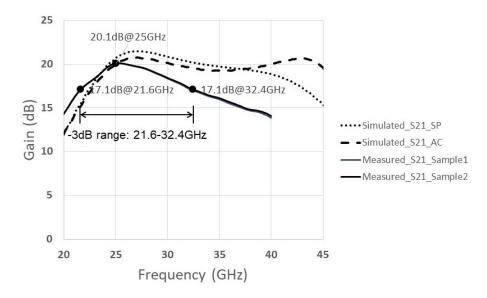

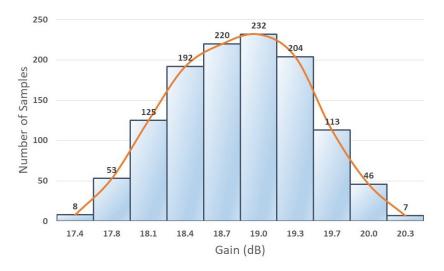

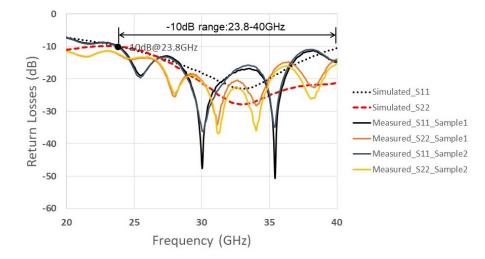

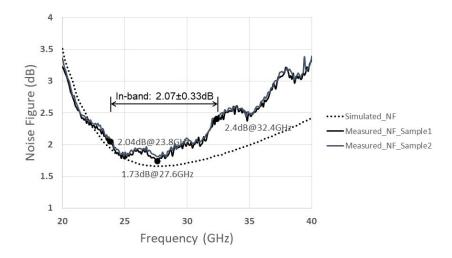

The folded output stage in the second design improves the input IP<sub>3</sub> to -6.7 dBm at the cost of 35 mW total power consumption. The peak gain of the second design is 20.1 dB, and the lowest noise figure of 1.73 dB within a frequency range of 23.8 to 32.4 GHz. Both designs occupy about 0.05 mm<sup>2</sup> active area.

#### Acknowledgements

I would like to express my utmost gratitude to my supervisor Dr. John Long for offering me the opportunity to explore the world of RF IC, as well as his invaluable support, encouragement and guidance throughout my Master's studies. I would also like to thank Dr. Peter Levine and Dr. Slim Boumaiza for reading my thesis and providing valuable feedback.

I would like to thank all my colleagues and friends in the RFIC group for their company and support. I would like to thank especially Hassan and Nansen for their technical knowledge and experience of dealing with the PDK and tool setup, Aman for his technical knowledge and discussion of design documents, Shaeera, Yan, Ayman, Yushi and Stanley for their help and valuable discussion.

Finally, I would like to thank my parents for their deepest love and unconditional support over the years. I also extend my honest appreciation to my grandparents for their selfless support and dedication. Special thanks to my cousin for her support.

I wish this thesis can create some inspiration for other designers.

To the B. C. in 2016, who took the leap To my parents and my grandparents To J. M. and Y. L., the AitD

# **Table of Contents**

| Li | st of | Tables |                                                | ix |

|----|-------|--------|------------------------------------------------|----|

| Li | st of | Figure | S                                              | x  |

| 1  | Intr  | oducti | on                                             | 1  |

|    | 1.1   | Motiva | tion                                           | 1  |

|    | 1.2   | Design | Objectives and Challenges                      | 2  |

|    |       | 1.2.1  | Operating Frequency and Bandwidth              | 2  |

|    |       | 1.2.2  | Noise Figure                                   | 3  |

|    |       | 1.2.3  | Linearity and Power Consumption                | 5  |

|    |       | 1.2.4  | Gain and Tunability                            | 7  |

|    |       | 1.2.5  | Other Objectives                               | 7  |

|    | 1.3   | Thesis | Organization                                   | 8  |

| 2  | Lite  | rature | Summary on Low-Noise Amplifiers                | 9  |

|    | 2.1   | Overvi | ew                                             | 9  |

|    |       | 2.1.1  | Biasing Condition for Low-Noise Designs        | 9  |

|    |       | 2.1.2  | Input-Matching Condition for Low-Noise Designs | 11 |

|    | 2.2   | Previo | us Work on RF Low-Noise Amplifiers             | 12 |

|    |       | 2.2.1  | Cascode LNA                                    | 14 |

|    |       | 2.2.2  | Transformer-Feedback LNA                       | 16 |

|   |     | 2.2.3  | Performance Summary                                                          | 19 |

|---|-----|--------|------------------------------------------------------------------------------|----|

|   | 2.3 | Previo | us Work on Millimetre-Wave Low-Noise Amplifiers                              | 20 |

|   |     | 2.3.1  | Multistage-Cascode LNA                                                       | 20 |

|   |     | 2.3.2  | Inductive Peaking for the Cascode Topology                                   | 23 |

|   |     | 2.3.3  | Performance Summary                                                          | 29 |

| 3 | Des | ign    |                                                                              | 31 |

|   | 3.1 | Design | A: a Two-Stage Amplifier with Noise-Matching Interstage                      | 31 |

|   |     | 3.1.1  | Proposed Circuit Topology                                                    | 32 |

|   |     | 3.1.2  | Body-Bias and the Flip-Well Structure                                        | 33 |

|   |     | 3.1.3  | Characterization of Active Devices in Simulation                             | 34 |

|   |     | 3.1.4  | Noise Analysis of Cascaded Amplifiers with Transformer Coupled<br>Interstage | 44 |

|   |     | 3.1.5  | Drawback of Interstage Noise Matching                                        | 49 |

|   |     | 3.1.6  | Input Stage                                                                  | 50 |

|   |     | 3.1.7  | Output Stage                                                                 | 51 |

|   |     | 3.1.8  | Interstage Transformer                                                       | 52 |

|   |     | 3.1.9  | Summary of Design Methodology                                                | 53 |

|   |     | 3.1.10 | Simulation Results                                                           | 54 |

|   | 3.2 | 0      | B: a Two-Stage, High-Linearity Amplifier with Interstage Noise Match-        | 57 |

|   |     | 3.2.1  | Proposed Circuit Topology                                                    | 58 |

|   |     | 3.2.2  | Input Stage Design                                                           | 59 |

|   |     | 3.2.3  | Output Stage Design                                                          | 60 |

|   |     | 3.2.4  | Simulation Results                                                           | 61 |

| 4 | Lay      | out an                                                                            | d Implementation                                                               | 63 |  |  |  |

|---|----------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----|--|--|--|

|   | 4.1      | Gener                                                                             | al Considerations of FET Layout for Low-Noise Designs                          | 63 |  |  |  |

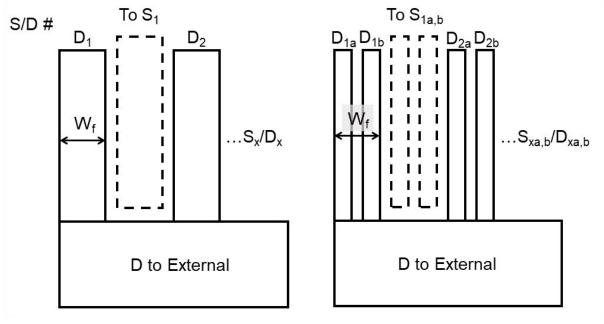

|   |          | 4.1.1                                                                             | Gate, Drain and Source Connections                                             | 64 |  |  |  |

|   |          | 4.1.2                                                                             | Electromigration Considerations                                                | 65 |  |  |  |

|   | 4.2      | Transf                                                                            | former Layout                                                                  | 67 |  |  |  |

|   |          | 4.2.1                                                                             | Interstage Transformer Layout                                                  | 68 |  |  |  |

| 5 | Exp      | oerime                                                                            | ntal Results                                                                   | 72 |  |  |  |

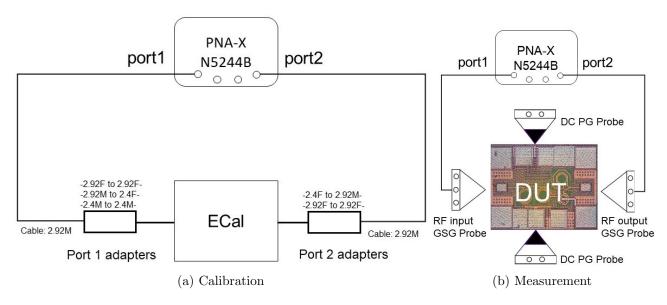

|   | 5.1      | Calibr                                                                            | ation and Measurement Setup                                                    | 73 |  |  |  |

|   | 5.2      | Design                                                                            | A - Two-Stage Amplifier with Interstage Noise-Matching                         | 74 |  |  |  |

|   |          | 5.2.1                                                                             | Low-Noise Mode (Biased at 17.3 mW) $\ldots \ldots \ldots \ldots \ldots \ldots$ | 74 |  |  |  |

|   |          | 5.2.2                                                                             | Low-Power Mode (Biased at 5.6 mW)                                              | 77 |  |  |  |

|   | 5.3      | B Design B - Two-Stage, High-Linearity Amplifier with Interstage Noise-Matching 8 |                                                                                |    |  |  |  |

|   | 5.4      | Comp                                                                              | arison and Summary                                                             | 84 |  |  |  |

| 6 | Cor      | nclusio                                                                           | ns and Future Work                                                             | 86 |  |  |  |

|   | 6.1      | Conclu                                                                            | usions                                                                         | 86 |  |  |  |

|   | 6.2      | Future                                                                            | e Work                                                                         | 87 |  |  |  |

|   |          | 6.2.1                                                                             | Device Modeling                                                                | 87 |  |  |  |

|   |          | 6.2.2                                                                             | Ground Impedance                                                               | 88 |  |  |  |

|   |          | 6.2.3                                                                             | The Omni-Amplifier                                                             | 88 |  |  |  |

| R | efere    | nces                                                                              |                                                                                | 90 |  |  |  |

| A | PPE      | NDIC                                                                              | ES                                                                             | 95 |  |  |  |

| Α | $\mu$ -S | tability                                                                          | / Factor                                                                       | 96 |  |  |  |

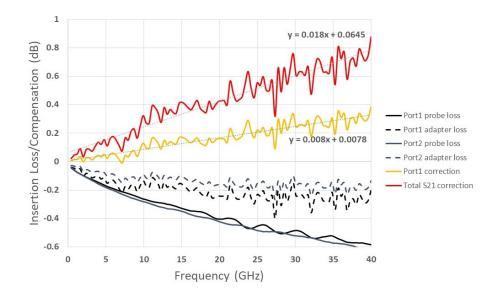

| B | Cor      | rection                                                                           | n of Measurement Results through Calibration                                   | 97 |  |  |  |

# List of Tables

| 2.1 | Typical performance of RF LNAs                                                                                                                        | 19 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Typical performance of mm-wave LNAs                                                                                                                   | 30 |

| 3.1 | Simulation results of the two-stage amplifier (Design A)                                                                                              | 55 |

| 3.2 | Simulation results of the two-stage, high-linearity amplifier (Design B)                                                                              | 61 |

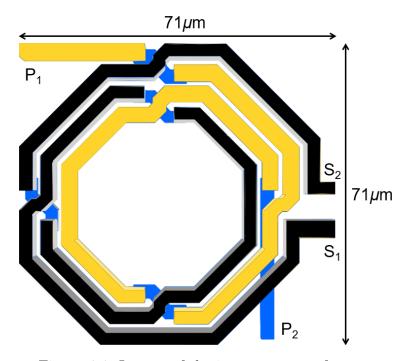

| 4.1 | Simulated parameters for different transformer configurations (with metal width of 5 $\mu$ m and spacing of 2 $\mu$ m, using the 11-layer stack-up)   | 67 |

| 4.2 | Simulated parameters for single and multi-turn interleaved transformers (metal width of 6 $\mu$ m and spacing of 2.6 $\mu$ m for a 10-layer stack-up) | 68 |

| 4.3 | Simulated parameters for the interstage transformer                                                                                                   | 70 |

| 5.1 | Summary and comparison of amplifier performance metrics                                                                                               | 85 |

# List of Figures

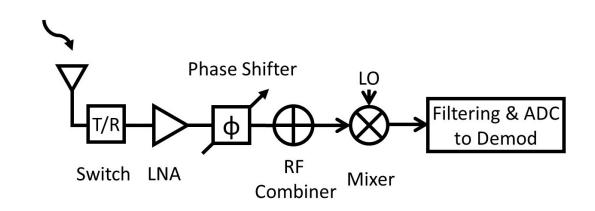

| 1.1  | A slice of a phased-array RF receiver                                                                 | 4  |

|------|-------------------------------------------------------------------------------------------------------|----|

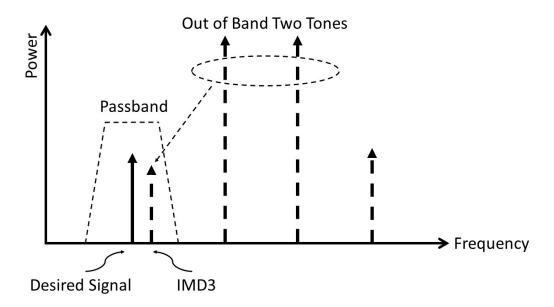

| 1.2  | Interference due to the third-order intermodulation                                                   | 5  |

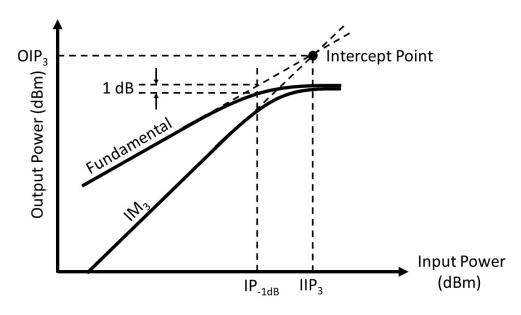

| 1.3  | Third-order intercept point and 1-dB compression point                                                | 6  |

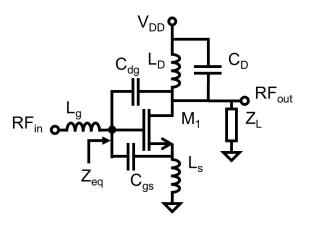

| 2.1  | Common-source amplifier with inductive degeneration                                                   | 12 |

| 2.2  | Noise fed back through $C_{dg}$ in a common-source amplifier (Simplified)                             | 14 |

| 2.3  | Cascode amplifier with inductive degeneration $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 15 |

| 2.4  | Noise of the common-gate stage in a cascode amplifier (Simplified)                                    | 16 |

| 2.5  | Reverse signal flows in drain-source transformer (Ideal) coupled common-<br>source LNA (Simplified)   | 17 |

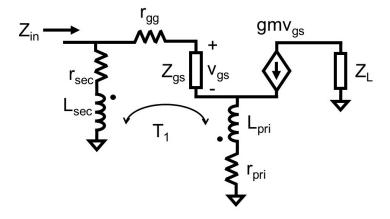

| 2.6  | Small-signal equivalent circuit of gate-source coupled input stage via ideal transformer (Simplified) | 18 |

| 2.7  | Block-level diagram of the multistage-cascode LNA                                                     | 20 |

| 2.8  | Simplified small-signal interstages model                                                             | 21 |

| 2.9  | Two-stage K-band low-noise amplifier                                                                  | 22 |

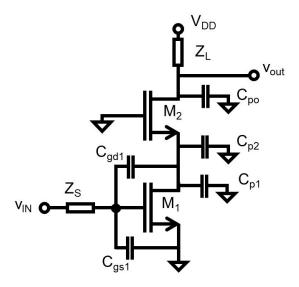

| 2.10 | Cascode amplifier with critical capacitances related to bandwidth (Simplified)                        | 23 |

| 2.11 | Small-signal model of common-source output with series peaking (Simplified)                           | 24 |

| 2.12 | Simplified cascode amplifier with shunt peaking inductor                                              | 26 |

| 2.13 | Inductive peaking at the output of cascode (Simplified)                                               | 27 |

| 2.14 | Inductive peaking at the gate of the common-gate stage                                                | 28 |

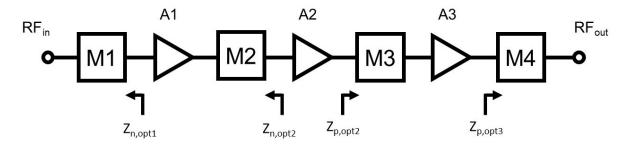

| 3.1  | Topology of a two-stage amplifier with interstage noise matching                                      | 32 |

| 3.2  | Forward body-bias limitations in a bulk CMOS process                                       | 33 |

|------|--------------------------------------------------------------------------------------------|----|

| 3.3  | Body-bias limitations in the 22-nm CMOS-SOI process                                        | 34 |

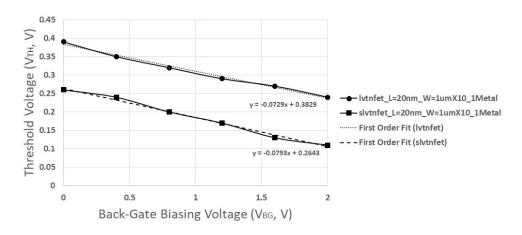

| 3.4  | Threshold voltages for 20-nm LVT and SLVT NFETs $\ldots$                                   | 35 |

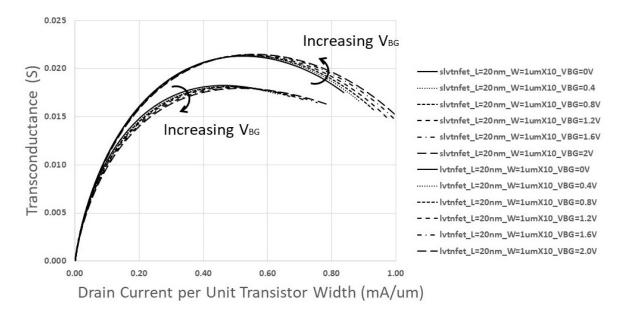

| 3.5  | Transconductance for 20-nm LVT and SLVT NFETs at nominal $V_{DS}$                          | 36 |

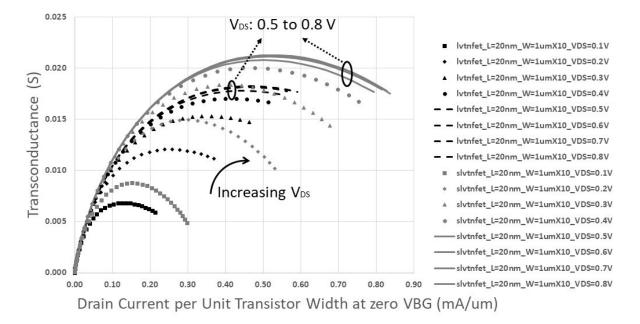

| 3.6  | Transconductance for 20-nm LVT and SLVT NFETs at zero $\rm V_{BG}$                         | 37 |

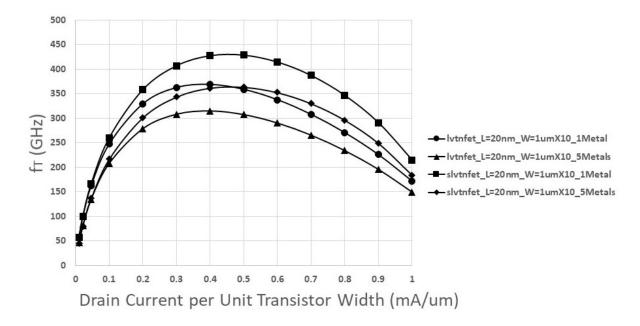

| 3.7  | Transition frequency for 20-nm LVT and SLVT NFETs                                          | 38 |

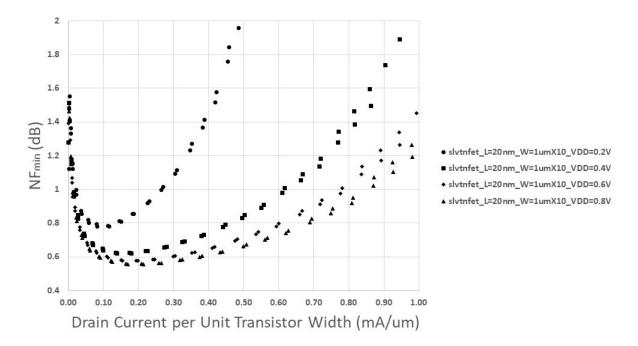

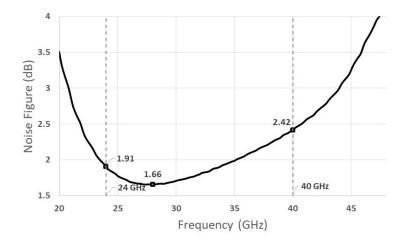

| 3.8  | Minimum noise figure for 20-nm SLVT NFETs                                                  | 39 |

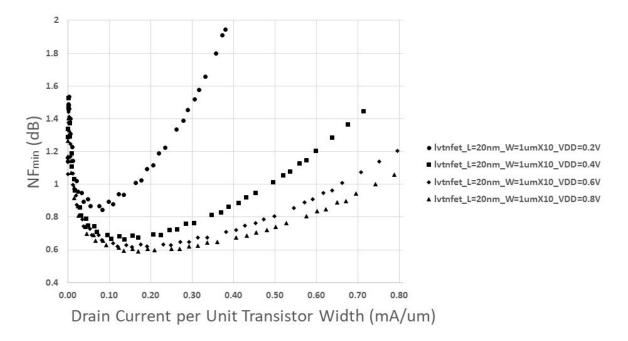

| 3.9  | Minimum noise figure for 20-nm LVT NFETs                                                   | 40 |

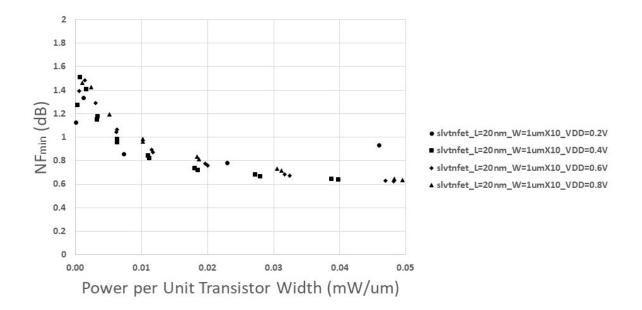

| 3.10 | Minimum noise figure in low-power region for 20-nm SLVT NFETs                              | 41 |

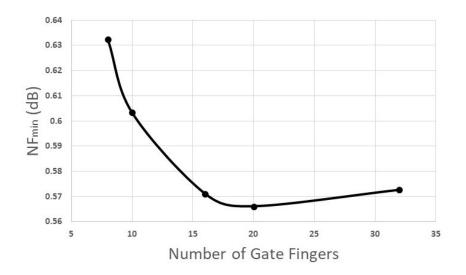

| 3.11 | Minimum noise figure versus number of fingers for a 16- $\mu$ m total-gate-width SLVT NFET | 42 |

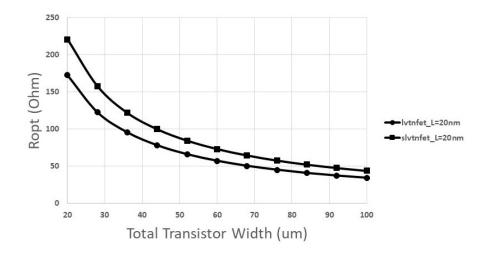

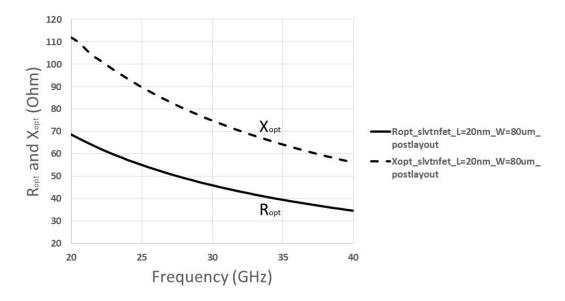

| 3.12 | Optimum noise resistance for 20-nm LVT and SLVT NFETs $\hdots$                             | 43 |

| 3.13 | Simplified two-stage amplifier for noise factor calculation $\ldots \ldots \ldots$         | 44 |

| 3.14 | Transformer-coupled interstage                                                             | 46 |

| 3.15 | Interstage matching setup                                                                  | 47 |

| 3.16 | Source impedance for lowest noise across frequencies                                       | 49 |

| 3.17 | Input stage of the two-stage amplifier                                                     | 50 |

| 3.18 | Output stage of the two-stage amplifier                                                    | 51 |

| 3.19 | Interstage coupling for the two-stage amplifier                                            | 52 |

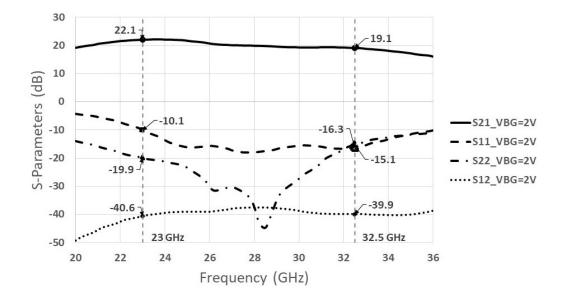

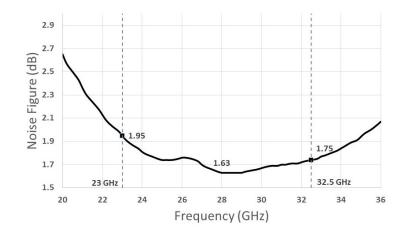

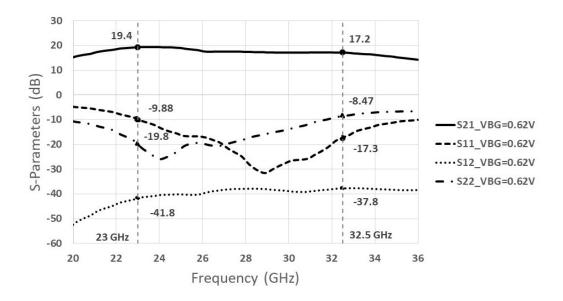

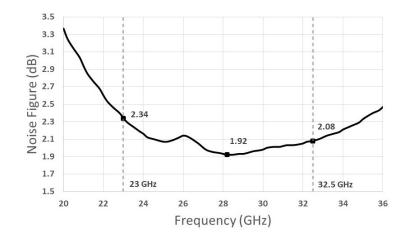

| 3.20 | Simulated S-parameters of the two-stage amplifier in low-noise mode                        | 55 |

| 3.21 | Simulated noise figure of the two-stage amplifier in low-noise mode                        | 56 |

| 3.22 | Simulated S-parameters of the two-stage amplifier in low-power mode                        | 56 |

| 3.23 | Simulated noise figure of the two-stage amplifier in low-power mode                        | 57 |

| 3.24 | Topology of a two-stage, high-linearity amplifier with interstage noise match-<br>ing      | 58 |

| 3.25 | Input stage of the two-stage, high-linearity amplifier                                     | 59 |

| 3.26 | Output stage of the two-stage, high-linearity amplifier                                    | 60 |

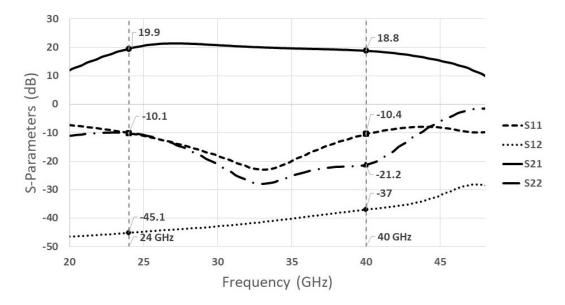

| 3.27 | Simulated S-parameters of the two-stage, high-linearity amplifier                          | 62 |

| 3.28 | 8 Simulated noise figure of the two-stage, high-linearity amplifier                                                    |  |  |  |  |  |

|------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

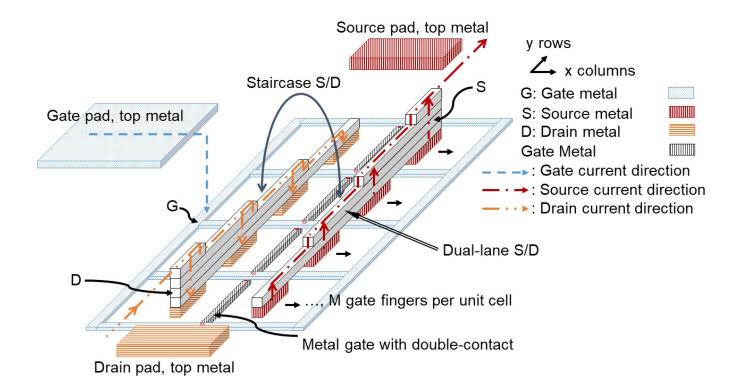

| 4.1  | Simplified grid transistor layout (4-row x 1-column) utilizing 5 x 0.8 $\mu$ m unit cells                              |  |  |  |  |  |

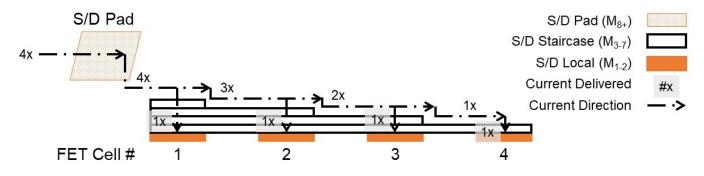

| 4.2  | Simplified side view of the staircase layout of source/drain                                                           |  |  |  |  |  |

| 4.3  | Dual-lane layout for source and drain to improve electromigration reliability                                          |  |  |  |  |  |

| 4.4  | Layout of the interstage transformer                                                                                   |  |  |  |  |  |

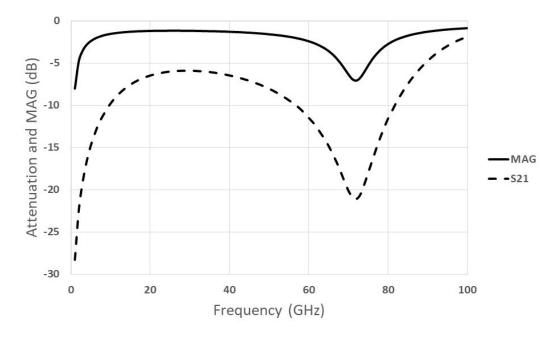

| 4.5  | Interstage transformer insertion loss and maximum available gain $\hdots$                                              |  |  |  |  |  |

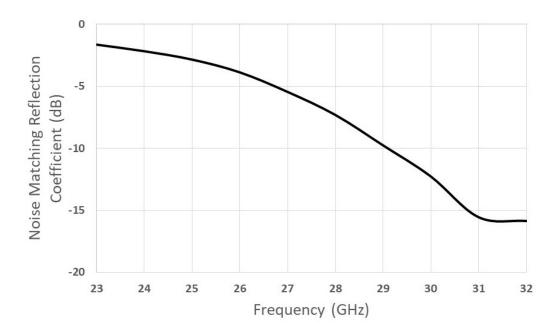

| 4.6  | Noise matching reflection coefficient at the second-stage input (including the interstage transformer) from simulation |  |  |  |  |  |

| 5.1  | Micrographs of two amplifier prototypes                                                                                |  |  |  |  |  |

| 5.2  | Two-port measurement setup $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$              |  |  |  |  |  |

| 5.3  | Measured vs. simulated small-signal gain of Design A biased at 17.3 mW in the low-noise mode                           |  |  |  |  |  |

| 5.4  | Measured vs. simulated input and output return losses of Design A biased at 17.3 mW in the low-noise mode              |  |  |  |  |  |

| 5.5  | Measured vs. simulated noise figure for Design A biased at 17.3 mW in the low-noise mode                               |  |  |  |  |  |

| 5.6  | Measured vs. simulated small-signal gain of Design A biased at 5.6 mW in the low-power mode                            |  |  |  |  |  |

| 5.7  | Measured vs. simulated input and output return losses of Design A biased at 5.6 mW in the low-power mode               |  |  |  |  |  |

| 5.8  | Measured vs. simulated noise figure of the two-stage amplifier biased at 5.6 mW in the low-power mode                  |  |  |  |  |  |

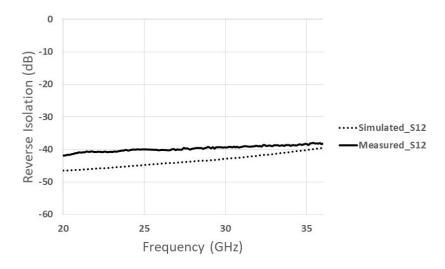

| 5.9  | Measured vs. simulated isolation of Design A in the low-noise and low-power mode                                       |  |  |  |  |  |

| 5.10 | Measured vs. simulated small-signal gain of Design B                                                                   |  |  |  |  |  |

| 5.11 | Gain distribution among various PVT conditions                                                                         |  |  |  |  |  |

| 5.12 | Measured vs. simulated input and output return losses of Design B $\ .\ .\ .$                                          |  |  |  |  |  |

| 5.13 | Measured vs. simulated noise figure of Design B                                                                        |  |  |  |  |  |

| 5.14 | Measured vs. simulated isolation of Design B                     | 83 |

|------|------------------------------------------------------------------|----|

| 6.1  | A three-stage omni-amplifier at block level                      | 88 |

| B.1  | Insertion loss of probes & adapters and the amount of correction | 98 |

## Chapter 1

## Introduction

In this chapter, a brief introduction to the thesis topic is given and the motivations for the research project are outlined. The semiconductor process used in this work is also introduced. Then, the design objectives are defined quantitatively.

### 1.1 Motivation

Demand for services delivered over the internet is driving the development of new communication infrastructure. Among the telecommunication sectors, wireless communication is prominent in mobility and flexibility, and is the largest sector in Canada. As reported in [1], wireless services account for 52% of all retail telecommunications service revenues. New genres such as social networking, live streaming, and electronic commerce are becoming irreplaceable in daily life as technology evolves. These applications require enormous data throughput. In Canada, the average data usage per subscriber has reached around 1.2 GB per month (up from 981 MB in 2015) with a 25% compound annual growth rate [1]. It is reasonable to predict that this growth rate will continue with new market drivers such as the internet of things, automotive, and wearable electronics. Therefore, wireless systems with the capability of handling large data throughputs are currently the subject of intense research & development, and is the application domain for the work in this thesis.

The 22FDX<sup>®</sup> technology developed by GLOBALFOUNDRIES<sup>®</sup> is a 22-nm, fullydepleted silicon-on-insulator (FD-SOI) CMOS process [2]. It features performance and power consumption comparable to FinFET technologies, but at the cost of a 28-nm planar technology while consuming up to 70% lower power (versus 28 nm, in digital applications) [2]. By fully depleting the transistor channel, supply power leakage is reduced, which favours digital applications. Non-idealities such as the kink effect seen in partiallydepleted SOI processes are resolved in FD-SOI [3]. Shrinking the channel length to 22 nm leads to a high transition frequency  $(f_T)$ , which enables high-performance RF and millimetre-wave (mm-wave) circuit designs. The ultra-thin buried oxide (BOX) underneath the channel raises the well breakdown voltage, which permits integration of a power amplifier by cascoding [2]. The capability to bias the transistor back-gate offers a way to trade-off performance and power on the fly, which provides more flexibility in a system [2].

The purpose of this thesis is to design an integrated, single-ended amplifier demonstrator in the 22-nm CMOS-SOI technology for radio front-end, and attempt to attain lowest noise figure and highest bandwidth. The novelty of the amplifier design methodology is that it utilizes noise-matching technique at the interstage, which provides lower noise figure than the traditional high-gain interstage. Priority in the design is given to wide bandwidth and low noise, with sufficient linearity, low power consumption and small chip area. A major motivation of this thesis is to benchmark the 22-nm CMOS-SOI technology performance in an emerging RF application.

### **1.2** Design Objectives and Challenges

Typical specifications for an RF system [4] consist of linearity (i.e., intercept point), noise figure, power consumption, operating frequency, bandwidth, gain and supply voltage.

#### **1.2.1** Operating Frequency and Bandwidth

As mentioned in Section 1.1, the main trend in the development of wireless communication systems is supporting increasing data throughput. The data rate (C) across a communication channel is proportional to the bandwidth (BW), and the logarithm of the signal-to-noise ratio (SNR), as described by Shannon's equation [5],

$$C = BW \times \log_2(1 + SNR). \tag{1.1}$$

Therefore, a wide bandwidth is the main design objective for a high-speed radio link. Fractional bandwidth is also commonly used to compare the performance of such systems. It is defined as the absolute bandwidth divided by centre frequency. For a fixed fractional bandwidth, the absolute bandwidth increases with increasing the centre frequency, thus high data throughput can be achieved. On the other hand, the sub-6 GHz spectrum is crowded with existing communication standards, which prompts industry to move to higher frequency bands. As a result, mm-wave frequency bands are being considered for the deployment of future generations of radio systems.

However, transistor performance metrics such as gain and noise figure deteriorate rapidly as the operating frequency increases. For passive components, leakage through oxide layers, substrate coupling and substrate losses also significantly degrade their RF performance. Moreover, ground and power plane impedances can affect the performance of a single-ended system. All of these factors have to be taken into consideration, which complicates the design and implementation process.

Overall, 28 GHz is selected as the centre frequency of operation because it has some relevance to 5G mm-wave bands. The highest bandwidth and lowest noise figure achievable are targeted around this centre frequency.

#### 1.2.2 Noise Figure

Aside from gain and bandwidth, noise figure (NF) is a design objective with higher priority over other specifications for this design. Noise factor (F) is defined as the SNR at the input divided by the SNR at the output of an amplifier,

$$F = \frac{S_i/N_i}{S_o/N_o} \quad [4].$$

(1.2)

Note that the noise factor is a measure of the noise power added by the system to the input noise power. By convention, 50  $\Omega$  is usually chosen as the input source resistance, which determines the input noise power  $(N_i = kT_0B)$  at a source temperature of  $T_0$  in Kelvin (k is Boltzmann's constant, and B is bandwidth in Hertz). When a bandwidth of 1 Hz is chosen, the NF may be referred to as the spot noise. Noise figure is the decibel representation of the noise factor,

$$NF = 10 \times log_{10}(F).$$

(1.3)

Receiver (RX) sensitivity is determined by the SNR (and thus noise figure), and plays a role in determining the upper limit of the communication channel capacity, as seen from Eq. 1.1. For an RX consisting of cascaded circuit blocks (as shown in Fig. 1.1), the overall noise factor may be expressed by Friis' equation, where  $F_x$  and  $N_x$  denote the noise factor and power gain of each stage, respectively,

$$F = F_{switch} + \frac{F_{LNA} - 1}{G_{switch}} + \frac{F_{PhaseShifter} - 1}{G_{switch}G_{LNA}} + \frac{F_{RFCombiner} - 1}{G_{switch}G_{LNA}G_{RFCombiner}} + \dots \qquad (1.4)$$

Figure 1.1: A slice of a phased-array RF receiver

For a wideband system, achieving low noise figure across the entire band is difficult because the optimum source impedance for minimum noise added by the transistor varies with frequency. In addition, ohmic losses in passive circuit components contribute noise that is determined partly by the losses of the interconnect metal stack in a given technology.

At mm-wave frequencies, cascading multiple stages with conjugate interstage impedance matching is the most common approach for amplifier design. The reason is that a conjugate match provides high gain for the first stage, which suppresses the noise contributed by later stages (as seen in the Friis equation, 1.4). However, gain decreases as operating frequency increases and transistor gate length decreases (i.e., process scaling) [6]. As a result, noise suppression by the gain of the first stage also decreases. Therefore, the interface between the first and second stages is designed for lowest noise (contributed by the second stage) instead of high-gain (from the first stage) in this work, to optimize the low-noise performance of the amplifier. To the best of author's knowledge, multistage noise-matching has not yet been realized in implementing amplifier operating at 28 GHz.

The target noise figure of this work is set to as low as possible. The upper bound of the noise figure is chosen to be 2 dB after a literature survey on recent low-noise amplifiers (LNAs) in a phased-array receiver application [7]-[9].

#### **1.2.3** Linearity and Power Consumption

Non-linearity of an RF amplifier (e.g., due to gain compression) causes harmonic and intermodulation distortions. Among the different distortion types, third-order intermodulation distortion  $(IMD_3)$  is often the most critical in a radio receiver because it lies within the same band as the desired signal. Thus, it cannot be easily filtered out, as shown in Fig. 1.2. As a result, the RX is desensitized to the desired signal, and fidelity suffers (e.g., poor signal quality, higher bit-error-rates, dropped calls, etc.).

Figure 1.2: Interference due to the third-order intermodulation

To specify this non-linear effect, the third-order intercept point (IP<sub>3</sub>) is used. It is defined as the input (or output) power where the extrapolation of the fundamental and the IM<sub>3</sub> powers intercept, as shown in Fig. 1.3. However, mixed products generated by other odd-order distortions may also appear at the same frequency. Thus, this method is only valid assuming that IM<sub>3</sub> is entirely contributed by the third-order component and that the distortion grows exactly three times as fast as the fundamental power. Assuming that  $P_{tone}$  represents the output power at tone frequencies, IP<sub>3</sub> and IM<sub>3</sub> at the output are related by

$$OIP_3 = P_{tone} + \frac{P_{tone} - IM_3}{2}$$

[4]. (1.5)

Higher IP<sub>3</sub> corresponds to lower IM<sub>3</sub> because the system is more linear. Similar to noise figure, IP<sub>3</sub> can be referred to the output (as  $OIP_3$ ) or to the input (as  $IIP_3$ ). The  $OIP_3$  is higher than  $IIP_3$  by the power gain in the system.

Figure 1.3: Third-order intercept point and 1-dB compression point

Another metric to describe linearity is the 1-dB gain compression point ( $P_{-1dB}$ ). Amplifiers suffer from output power saturation as the input power increases. The  $P_{-1dB}$  defines the power level where the gain of the amplifier is 1-dB lower than its small-signal gain, as shown in Fig 1.3. The IP<sub>3</sub> and  $P_{-1dB}$  are often related by

$$OIP_3 = OP_{-1dB} + 9.6 \, dB \quad [4]. \tag{1.6}$$

If the signal applied to the amplifier input from the antenna has little signal power, then the amplifier is working in the small-signal regime (i.e., the amplifier does not suffer from the gain compression). Thus, the requirement for linearity may not be as high, a priority as bandwidth or noise figure.

Linearity can be improved by Class-A biasing of the output stage. This ensures that the MOS transistor always operates in saturation, and increasing the supply voltage will create more output headroom. However, these approaches increase the DC power consumption  $(P_{DC})$ . The 22-nm CMOS-SOI process used in this work features a back-gate bias which

enables dynamic control of the transistor's threshold voltage [10]. This can be used to trade-off noise performance and power.

For low-noise design, transistors are typically biased at the optimum current per transistor width  $(\frac{I_{DS}}{W_{opt}})$ , which has a unit of mA/ $\mu$ m where minimum noise figure (NF<sub>min</sub>) occurs. As process technologies scale down, the transistor width has to be sized larger to realize the total gate area needed for 50- $\Omega$  noise matching. This leads to higher DC current and power consumption, which makes low-power design challenging, but generally favours linearity.

Since the design in this work targets hand-held mobile devices, the overall power consumption is set as low as possible with a limit of 40 mW after surveying recent literature on LNAs for similar applications. The goal for linearity is to achieve the best result given the limited power budget.

#### 1.2.4 Gain and Tunability

One of the main motivations for placing the amplifier at the input to the RX chain is to suppress noise from subsequent stages, as justified by equation 1.4. Therefore, sufficient amplifier gain is also necessary. If the amplifier consists of multiple stages, the overall gain is determined by the gain of each stage and loading on each stage. The tunability of the gain may be achieved by biasing the back-gate as it adjusts the threshold voltage and thus transconductance of the transistor. However, changes in threshold voltage also affect the DC bias current and the transistor may no longer be biased at  $\frac{I_{DS}}{W_{opt}}$ . Noise figure will increase as a consequence.

The minimum gain specification is set to 15 dB from reviewing recent mm-wave LNAs (in a phased-array receiver application [7]-[9], stand-alone: [11]-[15]). The bias voltage at the back-gate can be set to above the nominal  $V_{DD}$  of the system. Thus, explicit voltage generation and regulation circuits are required, which leads to some power and area overhead. To sum up, tunability is therefore optional.

#### 1.2.5 Other Objectives

The amplifier in this thesis work is designed to interface with other blocks in the receiver front end, such as a T/R switch and a mixer. From the measurement point of view, setting input and output impedances to be 50  $\Omega$  makes the device easier to measure, since test instruments are generally designed for 50  $\Omega$  interfaces. Thus, return losses are designed to be better than 10 dB (i.e.,  $S_{11}$ ,  $S_{22} < -10$  dB) across the amplifier's bandwidth. Meeting this specification is challenging for a wideband system.

## **1.3** Thesis Organization

This thesis consists of six chapters. In chapter two, a literature survey of previous work in mm-wave low-noise amplifier (LNA) design will be reviewed. Moving on to chapter three, theoretical derivation and a summarized design methodology are presented for two amplifier prototypes with their simulation results. The fourth chapter illustrates the challenges during the layout and implementation of the two designs. Chapter five outlines the test plan and measurement results followed by an analysis of discrepancies between simulation and measurement results. Finally, the last chapter concludes this thesis with a proposed plan for future work.

## Chapter 2

# Literature Summary on Low-Noise Amplifiers

In this chapter, a literature survey of previous work in RF and mm-wave low-noise amplifier (LNA) design is presented.

### 2.1 Overview

An LNA can be represented as a two-port network driven at the input by a signal source with a complex impedance  $Z_s = R_s + jX_s$ , and loaded at the output with an impedance  $Z_L$ . There is an optimum source impedance  $Z_{opt} = R_{opt} + jX_{opt}$ , where the minimum noise factor  $(F_{min})$  occurs for the transistor. The  $F_{min}$  of the transistor is determined by the semiconductor process, biasing condition and device dimensions. To minimize the noise factor of the amplifier, one approach is to minimize  $F_{min}$  of the transistor through proper biasing and scaling, and to present  $Z_{opt}$  to the input of the amplifier by an input matching network.

#### 2.1.1 Biasing Condition for Low-Noise Designs

For a FET, the minimum noise factor can be expressed as [16]

$$F_{min} = 1 + 2r_{gg}g_m\gamma(\frac{w_o}{w_T})^2 + 2\frac{w_o}{w_T}\sqrt{r_{gg}g_m\gamma(1 + r_{gg}g_m\gamma(\frac{w_o}{w_T})^2)};$$

(2.1)

When  $r_{gg}g_m\gamma(\frac{w_o}{w_T})^2 \ll 1$  in Eq. 2.1,

$$F_{min} \approx 1 + 2r_{gg}g_m\gamma(\frac{w_o}{w_T})^2 + 2\frac{w_o}{w_T}\sqrt{r_{gg}g_m\gamma}; \qquad (2.2)$$

When  $r_{gg}g_m\gamma(\frac{w_o}{w_T})^2 \gg 1$  in Eq. 2.1,

$$F_{min} \approx 1 + 4r_{gg}g_m\gamma(\frac{w_o}{w_T})^2, \qquad (2.3)$$

where  $\omega_o$  and  $\omega_T$  are the operating frequency and transition frequency of the transistor, respectively. The gate resistance is represented as  $r_{gg}$ ,  $g_m$  is the transconductance and  $\gamma$  is the excess (drain) channel noise parameter, which depends upon the semiconductor process. Among these parameters,  $\omega_T$ ,  $g_m$ , and  $r_{gg}$  are circuit design variables. The  $\omega_T$ and  $g_m$  of the transistor can be adjusted via setting the DC bias point and aspect ratio of the transistor. The gate resistance is given by [4]

$$r_{gg} = \frac{\rho_{sh}W}{L},\tag{2.4}$$

where  $\rho_{sh}$  represents the sheet resistance of the gate material (in  $\Omega/\Box$ ), W and L are the width and length of the transistor, respectively. The gate resistance may be reduced by splitting the gate into multiple fingers (M) and applying double-gate contacts. In addition, the distributed R-C effect of the gate resistance and capacitance (which forms a low-pass filter) has to be taken into consideration at radio frequencies. The equation describing  $r_{gg}$  becomes [4]

$$r_{gg} = \frac{1}{12} \frac{\rho_{sh} W}{ML}.$$

(2.5)

In [17], the optimum current per transistor width  $(\frac{I_{DS}}{W_{opt}})$  instead of the drain current  $(I_{DS})$  is used, because the goal here is to find the biasing condition where the minimum  $F_{min}$  occurs. The relation between the biasing voltage  $(V_{eff})$  and the drain current in saturation region can be expressed as [18]

$$I_{DS} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{TN})^2 [1 + \lambda (V_{DS} - V_{GS} + V_{TN})], \qquad (2.6)$$

where  $\mu_n$ ,  $C_{ox}$ ,  $V_{TN}$  and  $\lambda$  represent the carrier mobility, gate oxide capacitance per unit area, threshold voltage, and channel length modulation factor, respectively. Neglecting

channel length modulation and assuming the transistor operates in the saturation region, it can be shown that

$$V_{eff} = V_{GS} - V_{TN} \approx \sqrt{\frac{2L}{\mu_n C_{ox}} \frac{I_{DS}}{W}},\tag{2.7}$$

which indicates that the biasing point is a function of the current per transistor width  $(\frac{I_{DS}}{W_{opt}})$  (assuming that  $\mu_n$  and  $C_{ox}$  are constant). The drain-to-source voltage  $(V_{DS})$  from Eq. 2.6 also affects the drain current, which leads to changes in  $\frac{I_{DS}}{W_{opt}}$ , as confirmed in [17].

To sum up, transistors are typically biased close to  $\frac{I_{DS}}{W_{opt}}$  in low-noise designs. Note that biasing the transistor at  $\frac{I_{DS}}{W_{opt}}$  does not guarantee the overall noise factor of the amplifier to be at its minimum, because losses from the input-matching network are not included in the analysis.

#### 2.1.2 Input-Matching Condition for Low-Noise Designs

The optimum source impedance  $(Z_{opt} = R_{opt} + jX_{opt})$  is given by [16][17]

$$R_{opt} = \frac{\omega_T}{M\omega_o} \sqrt{\frac{r'_{gg}}{g'_m \gamma}} = \frac{1}{\omega_o M(C'_{gs} + C'_{gd})} \sqrt{\frac{r'_{gg}g'_m}{\gamma}},$$

(2.8)

$$X_{opt} = \frac{\omega_T}{M\omega_o g'_m} = \frac{1}{\omega_o M(C'_{gs} + C'_{gd})},\tag{2.9}$$

where  $r'_{gg}$ ,  $C'_{gs}$ ,  $C'_{gd}$ ,  $g'_m$  represents the gate resistance, gate-to-source capacitance, gate-todrain capacitance, and transconductance of a unit-size transistor, respectively. To reduce noise factor,  $Z_{opt}$  should be presented to the input of the amplifier.

Since the source impedance  $(Z_s)$  is typically 50  $\Omega$ , the transistor can be sized properly by adjusting M and  $g'_m$  to match  $R_{opt}$  to 50  $\Omega$ . Note that for a unit-size transistor,  $R_{opt}$  is inversely proportional to the channel length (i.e., as technology scales down,  $R_{opt}$  increases). Assuming that the transistor is biased at  $\frac{I_{DS}}{W_{opt}}$ , it has to be sized very wide in deep submicron technology to match  $R_{opt}$  to 50  $\Omega$ , which increases the drain current. This leads to a trade-off between low-noise and power consumption. Also, a large transistor area may cause problems such as degradation in gain and noise due to the Miller effect at radio frequencies.

The optimum (noise) source reactance is equal to the input reactance of the FET. Thus, an inductor in series with the source resistance is often used as the input matching network. The ohmic loss of the inductor contributes significantly to the noise factor of the amplifier, and is proportional to the size of the coil. Note that, if the transistor size is large, its input reactance  $\left(\frac{1}{sC}\right)$  becomes low. Thus, a low inductance value is needed, which leads to low ohmic loss, and reduces the noise factor of the amplifier (and vice versa). Therefore, this also leads to the same trade-off (between noise and power consumption) as mentioned in the previous paragraph.

## 2.2 Previous Work on RF Low-Noise Amplifiers

The common-source NFET with inductive degeneration is probably the most commonlyused topology for LNA designs. As shown in Fig. 2.1,

Figure 2.1: Common-source amplifier with inductive degeneration

Neglecting channel length modulation, the equivalent impedance looking into the gate of the transistor  $(Z_{eq})$  can be expressed as [4]

$$Z_{eq}(s) = \frac{(Z_L + \frac{1}{sC_{dg}})(s^2 L_s C_{gs} + g_m L_s + 1)}{s^2 L_s C_{dg} + s(Z_L C_{gs} + g_m L_s) + g_m Z_L + \frac{C_{gs}}{C_{dg}} + 1}.$$

(2.10)

Neglecting current fed back through  $C_{dg}$  and assuming  $Z_L \ll \frac{1}{sC_{dg}}$ , the above equation can be approximated to

$$Z_{eq}(s) \approx \frac{g_m L_s}{C_{gs}} + \frac{1}{sC_{gs}} + sL_s, \qquad (2.11)$$

where the real part of  $Z_{eq}$  becomes  $\frac{g_m L_s}{C_{gs}}$ . Since  $L_s$  and  $C_{gs}$  does not generate thermal noise, a noiseless 50  $\Omega$  can be realized and used for conjugate input match. The gate inductor  $L_g$  may be selected to match the source reactance to  $X_{opt}$ , and bring the imaginary part of the input impedance to zero. As a result, the input is simultaneously noise and conjugate matched to 50  $\Omega$ .

There are several drawbacks to this topology. As the operating frequency approaches the transition frequency of the transistor, the gain of the transistor rolls off, which leads to insufficient gain at radio frequencies. One solution to counter this problem is to cascade more stages, which would involve complicated interstage interfacing as well as much greater power consumption. If  $C_{dg}$  is not neglected in Eq. 2.10 and assuming that the denominator is dominated by  $(1 + \frac{C_{gs}}{C_{dg}})$ ,  $Z_{eq}$  drops by a factor of  $(1 - \frac{2C_{dg}}{C_{gs}})$ , which reduces the input return loss. Another problem created by  $C_{dg}$  is the Miller effect, which increases in the equivalent input capacitance due to the voltage gain across the amplifier, thereby limiting the amplifier bandwidth. The equivalent input capacitance due to the (Miller) feedback capacitor ( $C_{dg}$ ) shown in Fig. 2.1 is given by [18]

$$C_{eq} = C_{dg}(1 + |A_v|), (2.12)$$

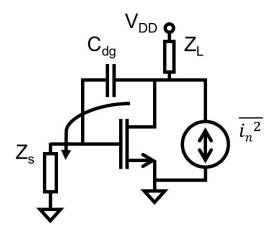

where  $A_v$  is the voltage gain. The presence of  $C_{dg}$  also affects the noise performance. Fig. 2.2 illustrates the common-source amplifier including the drain current noise source for analysis.

Figure 2.2: Noise fed back through  $C_{dg}$  in a common-source amplifier (Simplified)

The presence of  $C_{dg}$  and the finite source impedance  $(Z_s)$  form a feedback path from the output back to the input for the equivalent noise current source of the transistor. The noise power fed back to the input is given by

$$\overline{v_n^2} = 4kT\gamma g_m Z_L^2 \left(\frac{Z_s}{Z_s + \frac{1}{sC_{dg}}}\right)^2.$$

(2.13)

Therefore, a noise voltage is presented at the input which degrades the noise performance of the common-source amplifier at radio frequencies. Moreover, the feedback also reduces the reverse isolation of the amplifier.

#### 2.2.1 Cascode LNA

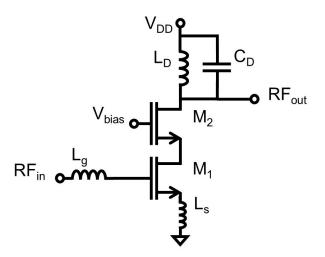

To resolve problems such as insufficient gain, bandwidth limitation due to the Miller effect, and poor reverse isolation with the common-source topology, a common-gate amplifier is connected in series with the common-source transistor to form a cascode topology, as depicted in Fig 2.3.

Figure 2.3: Cascode amplifier with inductive degeneration

Compared to the common-source topology, the cascode amplifier can realize higher gain due to the increase in output impedance (note that, the output impedance will be limited by the quality factor of  $L_D$ ). The low input impedance of the common-gate FET  $(M_2)$  driven by the output of the common-source FET  $(M_1)$  reduces the voltage gain of the common-source stage. Thus, the Miller effect on  $M_1$  is suppressed which improves the bandwidth. Reverse isolation is also improved due to the high isolation across  $M_2$ . However, noise performance is degraded due to noise added by the common-gate stage. Fig. 2.4 shows a simplified small-signal schematic of the common-gate stage with the drain current noise source emphasized.

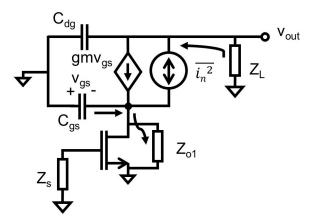

Figure 2.4: Noise of the common-gate stage in a cascode amplifier (Simplified)

Assuming that the output impedance  $(Z_{o1})$  of the common-source stage is finite, there will always be a portion of the noise current flowing through load  $Z_L$  which increases the overall noise factor. The noise contributed by the common-gate stage can become more critical as frequency increases, because  $Z_{o1}$  of the common-source stage decreases as the frequency increases. Note that the impedance of  $C_{gs}$  (i.e.,  $Z_{gs}$ ) of the common-gate stage shown in Fig. 2.4 also affects the noise voltage at the output, as it provides a path to AC ground for the noise current. To optimize the noise performance of the cascode,  $Z_{o1}$  of the common-source and  $Z_{gs}$  of the common-gate stage must be taken into consideration, especially at mm-wave frequencies.

Although the cascode topology resolves many problems occurred in the common-source amplifier, one noticeable drawback is its linearity. For a fixed supply voltage  $V_{DD}$ , adding a transistor  $M_2$  in series with  $M_1$  causes a reduction of the output headroom due to the extra bias voltage required for the common-gate stage. The supply voltage has to be doubled for the same output headroom as a single transistor amplifier, which leads to greater power consumption.

In [19], a cascode LNA is implemented with differential input and output in 180-nm CMOS technology. It achieved a gain of 14.1 dB, the noise figure is 1.8 dB and  $IIP_3$  equals 4.2 dBm for a supply voltage of 1.8 V at 21.6 mW power consumption.

#### 2.2.2 Transformer-Feedback LNA

Another enhancement to the common-source topology to eliminate the unwanted feedback through the Miller capacitor is to apply transformer feedback. In [19], drain and source

terminals of the common-source amplifier are coupled through a transformer.

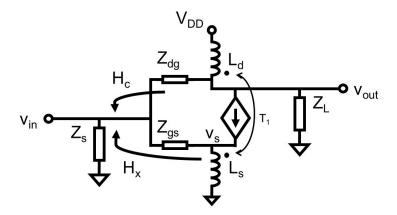

Figure 2.5: Reverse signal flows in drain-source transformer (Ideal) coupled common-source LNA (Simplified)

Neglecting channel length modulation and assuming that the transformer is ideal, the additional output signal fed back to the input  $(H_x)$  counteracts the capacitive feedback via  $C_{dg}$   $(H_c)$ , which are expressed as

$$H_c \approx \frac{v_{in}}{v_{out}}\Big|_{v_s=0} = \frac{Z_s ||Z_{gs}}{Z_s ||Z_{gs} + Z_{dg}},$$

(2.14)

and

$$H_x \approx \frac{v_{in}}{v_{out}}\Big|_{H_c=0} = \frac{-\frac{1}{n}(Z_s||Z_{gd})}{Z_s||Z_{gd} + Z_{sg}}.$$

(2.15)

Assuming that  $C_{gs} = C_{sg}$ ,  $C_{dg} = C_{gd}$  and the transformer is ideal, setting  $H_c = -H_x$  leads to

$$\frac{C_{gs}}{C_{dg}} \approx n. \tag{2.16}$$

As a result, the effect of the Miller capacitor is nulled (i.e.,  $C_{dg}$  is neutralized). Gain and reverse isolation are improved at radio frequencies. Furthermore, noise current through  $C_{dg}$  is suppressed and the output headroom is maintained without the use of the cascode topology. Another advantage of using transformer feedback for  $C_{dg}$  neutralization is its wide bandwidth. From 2.16, the condition for  $C_{dg}$  neutralization only depends on the turns ratio of the transformer. That is, the bandwidth of  $C_{dg}$  neutralization is determined by the bandwidth of the transformer.

In monolithic transformers, the ohmic loss and parasitic capacitances can become critical and limit the bandwidth, which is a potential problem for transformer-coupled amplifiers. The ohmic loss generates thermal noise, which contributes to the amplifier noise factor.

As reported in [19], a differential transformer coupled LNA achieved similar gain as the differential cascode topology (14.2 dB and 14.1 dB, respectively). However, the noise figure has been improved from 1.8 dB to 0.9 dB. With a lower supply voltage of 1 V, a slightly lower IIP<sub>3</sub> of 0.9 dBm is attained with 16 mW power consumption, down from 21.6 mW in the cascode case.

Transformers can also be used to implement wideband matching networks. In [20], a transformer is used at the input of the amplifier to couple gate and source terminals, as shown in Fig. 2.6, where  $C_{dg}$  and channel length modulation are neglected to simplify the analysis. The transformer is assumed to be ideal.

Figure 2.6: Small-signal equivalent circuit of gate-source coupled input stage via ideal transformer (Simplified)

Kirchhoff's current law is applied at the input, the resulted input impedance can be expressed as

$$Z_{in} \approx \frac{v_{in}}{i_{in}} \bigg|_{Z_{gs} \to \infty} = \frac{n^2}{(n+1)g_m},$$

(2.17)

which implies the approximated input impedance is solely dependent on the transformer turns ratio (n) and the transconductance of the transistor  $(g_m)$ . Both variables are independent of frequency. Thus, a wideband input match can be achieved.

Although the topology can achieve wideband matching, there are several potential problems associated with it. The ohmic loss in linear transformer windings is in series with the transistor gate resistance, thus it increases the noise factor of the amplifier. The interwinding capacitance bridges the gate and source terminals of the transistor, which increases the input capacitance and degrades the transition frequency. It also leads to a higher minimum noise factor, as explained in Eq. 2.1.

As reported in [20], an input return loss better than 10 dB is achieved across a frequency range from 3.1 to 10.6 GHz, which indicates a wideband input match. Noise figure is around 2.5 dB within the bandwidth (which is higher than 0.9 dB reported in [19] across a narrower bandwidth of 250 MHz).

#### 2.2.3 Performance Summary

Table 2.1 summarizes the performance data of the topologies covered in previous sections. Lower noise figure is observed from the differential cascode and the differential transformer feedback designs in [19] than others. Wideband circuit (i.e., [20]) shows higher noise figure due to the narrow-band nature of noise matching. Linearity generally degrades with lower supply voltage, as shown in the transformer coupled design in [19] and [20]. Single-ended amplifiers show its advantage on power consumption over differential designs (i.e., 9 mW in [20] vs. 16 and 21.6 mW in [19]).

| Ref. | Technology | Topology                         | $S_{21}$ (dB)  | $f_o$ (GHz)     | NF (dB)      | $S_{11}$ (dB) | $IIP_3$ (dBm)    | $V_{DD}$ | $P_{DC} (\mathrm{mW})$ |

|------|------------|----------------------------------|----------------|-----------------|--------------|---------------|------------------|----------|------------------------|

| [19] | 0.18 CMOS  | Differential<br>Cascode          | 14.1           | 5.75            | 1.8          | N/A           | 4.2              | 1.8 V    | 21.6                   |

| [19] | 0.18 CMOS  | Differential<br>Transformer      | 14.2           | 5.75            | 0.9          | N/A           | 0.9              | 1.0 V    | 16                     |

| [20] | 0.13 CMOS  | Transformer<br>Reactive Feedback | $15.1 \pm 1.4$ | $3.1 \sim 10.6$ | $2.2\pm0.43$ | <-10          | $-8.5 \sim -5.1$ | 1.2 V    | 9                      |

Table 2.1: Typical performance of RF LNAs

## 2.3 Previous Work on Millimetre-Wave Low-Noise Amplifiers

Most mm-wave frequency LNA designs consist of cascaded, cascode amplifiers (e.g., [11]-[15]). Circuit parasitics significantly deteriorate gain, noise figure and bandwidth at these frequencies. Therefore, peaking inductors are commonly utilized to broaden the bandwidth (e.g., as reported in [13]-[15]). Transmission-line-based passive components become attractive for integrated circuits due to the decrease in their electrical length and their simplicity. Also, the area of a spiral coil decreases as the inductance decreases, which may lead to challenges in the layout of inductors (due to coupling from the opposite edge of the coil) and transformers (to realize high magnetic coupling factor). At mm-wave frequencies, coupled transmission lines may be used to implement transformers.

#### 2.3.1 Multistage-Cascode LNA

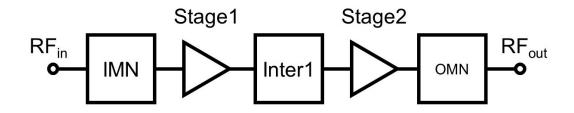

To counter the problem of a decrease in the gain of single-stage amplifiers as the frequency increases, multiple stages in cascade are used to boost the gain. The multistage, cascode LNAs reported in [11] and [12] operate at K, Q, V and W bands. A block-level diagram of the topology is shown in Fig. 2.7 below.

Figure 2.7: Block-level diagram of the multistage-cascode LNA

The input matching network (IMN) matches the first stage  $(Z_{in1})$  to the source impedance, and synthesizes the source impedance for optimum noise factor for the first stage  $(Z_{opt1})$ . The output matching network (OMN) matches the impedance of the second stage output  $(Z_{out2})$  to the amplifier load. In [11], the interstage is designed such that 50  $\Omega$  is presented to both the output of the first stage and the input of the second stage (i.e., the first and second stages are conjugate-matched to 50  $\Omega$ ) to maximize the voltage gain of the first stage [22]. This leads to a general discussion of interfacing stages from microwave and analogue viewpoints. For microwave designs (especially at the print-circuit-board level, where transmission-line effects dominate), the conjugate match is implemented to achieve original integrity. From the analogue point of view, maximizing the load impedance for a transconductor maximizes the gain.

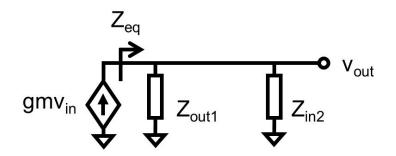

Figure 2.8: Simplified small-signal interstages model

Mathematically, the signal source (with output impedance  $Z_{out1} = R_{out1} + jX_{out1}$ ) delivered to a load  $Z_{in2}$  equal to  $(R_{in2} + jX_{in2})$  for a conjugate match  $(i.e., R_{out1} = R_{in2} \text{ and } X_{out1} = -X_{in2})$  can be expressed as

$$v_{out,conj} = g_m v_{in}(Z_{out1} || Z_{in2}) = \frac{1}{2} g_m v_{in}(R_{in2} + \frac{X_{in2}^2}{R_{in2}})$$

$$= \frac{1}{2} g_m v_{in} R_{in2}(1 + \tan^2 \theta) = \frac{1}{2} g_m v_{in} \frac{Z_{in2}}{\cos \theta},$$

(2.18)

where  $\theta$  is the angle of  $Z_{in2}$  in complex form. For the analogue approach to maximize gain,  $v_{out,analogue} = g_m v_{in} Z_{in2}$  for  $Z_{out1}$  approaching infinity. Therefore, an inequality arises between  $v_{out,conj}$  and  $v_{out,analogue}$ . When  $\theta$  is less than 60°, the analogue approach provides a better output voltage swing. When  $\theta$  is greater than 60°, performing conjugate match results in higher voltage gain. At mm-wave frequencies, realizing a high impedance for  $Z_{out1}$ may be challenging since the drain-to-source capacitance degrades the output impedance of the transistor. Furthermore, the channel conductance  $(g_{ds})$  of the transistor increases as the process scales down, which worsens the problem. The above considerations make conjugate matching attractive at mm-wave frequencies to achieve greater voltage swing at interstages (i.e., high voltage gain), but the load  $(Z_{in2})$  has to be taken into account when designing the interstage. Another advantage of the  $50-\Omega$  interface is that at the system level, stages can be easily swapped by another block with  $50-\Omega$  interface without modifying the matching network. However, the conjugate interstage match may not always be intended. The increase in gain may lead to stability issue, as explained in A (i.e., the interstage mismatch is one way to improve stability). From power viewpoint, conjugate match generates real power at interstage (due to the presence of a real load), which leads to unnecessary heat dissipation (i.e., a high reactance load does not produce any real power).

Figure 2.9: Two-stage K-band low-noise amplifier

The DC bias points of both stages are chosen to be 0.2 mA/ $\mu$ m, where  $F_{min}$  of the transistor is at its minimum [11] (i.e., both stages are biased for minimum noise). To further reduce noise, the input transistor is laid out as 4 discrete instances of 25 fingers, where the width of each finger is 0.8  $\mu$ m [11]. The supply voltage of the second stage is set above nominal to improve the output headroom, which increases DC power consumption. The Q- and V-band designs in [12] use transmission-line-based inductors for interstage and output matching. The common-gate transistor gates are biased at supply voltage through resistors. The use of resistors eliminates the need of the voltage bias for the common-gate stage and adds the flexibility for tuning the output impedance (it can be taken as a part of the output matching network). However, the voltage at the source of the common-gate transistor is not guaranteed to be at the middle of the supply voltage, which leads to uneven distribution of the voltage drop across the common-source and the common-gate stages. As a result, the linearity may be affected.

The gain of 19.5 dB is achieved from 16 to 24 GHz by cascading a common-source

stage with a cascode stage with 45-nm CMOS-SOI technology, as reported in [11]. As the frequency increases, the gain is expected to decrease, which correlates with designs mentioned in [12] on the same process. The amplifier designed for Q-band reports a gain of 15 dB and drops down to 12.5 dB at V-band [12]. At around 80 GHz, a threestage, cascaded common-source amplifier realizes a gain of 14.7 dB in [12]. Noise figure is expected to increase along with the increase in operating frequency ratio, as explained in Eq. 2.1. The noise figure for amplifiers at K, Q, V, W bands are 2 dB, 3.3 dB, 4 dB and 5.7 dB, respectively, which agrees with this expectation. Interestingly, power consumptions reported for these designs have a falling trend (from 32.5 mW to 13.5 mW). This can be explained using Eq. 2.8 and Eq.2.9. Assuming that transistors are biased at the same  $(\frac{I_D}{W})_{opt}$  for the lowest transistor  $F_{min}$ , the multiplicity (M) required to perform noise matching in Eq. 2.8 and Eq. 2.9 decreases as operating frequency increases. As a result, drain current decreases as well as power consumption.

#### 2.3.2 Inductive Peaking for the Cascode Topology

To determine the bandwidth of a regular cascode amplifier (as shown in Fig. 2.10), its effective time constant  $(\tau)$  is given by

Figure 2.10: Cascode amplifier with critical capacitances related to bandwidth (Simplified)

$$\tau = R_s [C_{gs1} + C_{dg1} (1 + g_{m1} R_{d1})] + R_{d1} (C_{p1} + C_{p2}) + R_L C_{po}, \qquad (2.19)$$

assuming  $Z_s$  equals to  $R_s$ ,  $Z_L$  equals to  $R_L$  and neglecting channel length modulation. The impedance looking out from the drain of  $M_1$  is assumed to be purely resistive  $(R_{d1})$ . The drain-to-source and drain-to-bulk capacitances of  $M_1$  are together represented as  $C_{p1}$ , while  $C_{p2}$  contains the source-to-gate and source-to-bulk capacitances of  $M_2$ . The parasitics at the drain of  $M_2$  is shown as  $C_{po}$ . The first term in Eq. 2.19 represents the pole at the input of the amplifier, while the later two terms represent the poles at the internode (between the CS and CG stages) and the output, respectively. As cascode amplifier suppresses the Miller effect by reducing the gain of the CS stage, the dominant pole has moved from the input to the output and the internode. Parasitic capacitances at these nodes become the bottleneck of the bandwidth of the amplifier. Thus, inductive peaking may be used to extend the bandwidth of the amplifier. Note that, the series and shunt peaking inductor in [23] are realized with coplanar waveguides (CPW), which occupies large chip area. To keep the active area small, peaking elements in this thesis are implemented with spiral inductors.

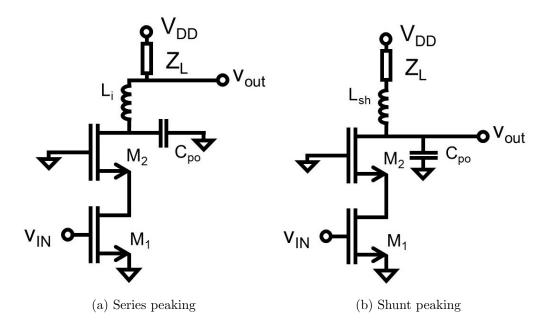

#### 2.3.2.1 Series and Shunt Peaking

A simplified small-signal equivalent circuit is utilized to illustrate series peaking (as depicted in Fig. 2.11).

Figure 2.11: Small-signal model of common-source output with series peaking (Simplified)

Neglecting channel length modulation, without  $L_i$ , the internode pole locates at  $\frac{1}{R_{d1}(C_{p1}+C_{p2})}$  (rad/s). With  $L_i$ , the equivalent output impedance  $Z_{eq}(s)$  can be expressed as [24]

$$Z_{eq}(s) = \frac{R_{d1}}{1 + sR_{d1}(C_{p1} + C_{p2}) + s^2L_iC_{p1} + s^3L_iR_{d1}C_{p1}C_{p2}} = \frac{R_{d1}}{1 + \frac{s}{\omega_u} + (\frac{s}{\omega_u})^2mn + (\frac{s}{\omega_u})^3mn(1-n)},$$

(2.20)

where  $m = \frac{L_i}{R_{d_1}^2(C_{p_1}+C_{p_2})}$  is the level of compensation (unitless),  $n = \frac{C_{p_1}}{C_{p_1}+C_{p_2}}$  is dependent on the process (unitless), and  $\omega_u = \frac{1}{R_{d_1}(C_{p_1}+C_{p_2})}$  is the normalized 3-dB bandwidth for the uncompensated common-source stage with  $L_i = 0$  [24]. By properly choosing m, the bandwidth can be extended beyond  $\omega_u$ .

As described previously in Section 2.2.1, the noise contribution of  $M_2$  is suppressed by increasing the output impedance of  $M_1$  in a cascode amplifier. Placing a series inductor at the drain of  $M_1$  improves the impedance, thus leads to lower noise performance. The disadvantage of adding a series inductor is that the ohmic losses of the inductor degrade the noise performance of the amplifier, which may overcome the benefit depending on the quality factor of the inductor.

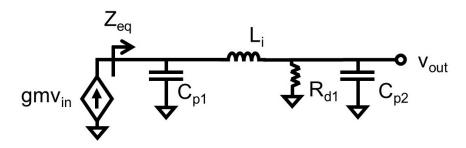

Another approach to push the internode pole to higher frequency is to use a shunt inductor, as depicted in Fig. 2.12,

Figure 2.12: Simplified cascode amplifier with shunt peaking inductor

where  $C_{eq}$  is the shunt equivalent of  $C_{p1}$  and  $C_{p2}$  and  $R_{sh}$  represents the ohmic losses of the shunt peaking inductor. Neglecting channel length modulation, the equivalent output impedance  $Z_{eq}(s)$  can be expressed as

$$Z_{eq}(s) = \frac{R_{sh} + sL_{sh}}{1 + sR_{sh}C_{eq} + s^2L_{sh}C_{eq}},$$

(2.21)

which transforms the one-pole response (without  $L_{sh}$ ) to a transfer function with two poles and a zero. The peaked response is determined by the ratio between the zero (formed by  $L_{sh}$  and  $R_{sh}$ ) and the pole (formed by  $R_{sh}$  and  $C_{eq}$ ). Similar to series peaking, the ohmic losses of the inductor degrades the noise performance of the amplifier.

Similarly, the output pole may also be pushed to a higher frequency by performing series or shunt peaking, as depicted in Fig. 2.13. Eq. 2.20 and Eq. 2.21 may be used to express the bandwidth-enhancement ratio.

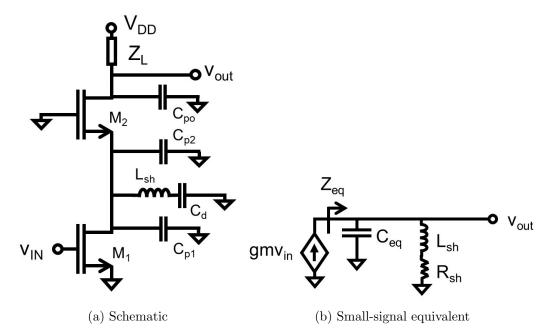

Figure 2.13: Inductive peaking at the output of cascode (Simplified)

With 65-nm CMOS technology, a two-stage cascode with series peaking inductors at internode achieves a peak gain of 16 dB at 58 GHz with 4.5 dB noise figure across a bandwidth of 14 GHz [13]. With single-stage triple-cascode, the gain reaches 14.3 dB at 38 GHz with 3.8 dB noise figure across a bandwidth of 6 GHz in 130-nm CMOS [13]. Although the performance is lower than the ones in [12], it is worthy to mention that the work is done in a much older bulk process rather than the advanced 45-nm CMOS-SOI (used in [12]).

#### 2.3.2.2 Inductive Peaking at the Gate of the Common-Gate Stage

Besides series and shunt peakings, an inductor may be placed at the gate node of the common-gate stage to enhance the bandwidth, as depicted in Fig. 2.14.

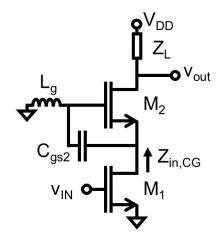

Figure 2.14: Inductive peaking at the gate of the common-gate stage

Neglecting channel length modulation and including the effect of  $C_{gs2}$ , the voltage gain of a cascode amplifier may be expressed as

$$A_{v,woL_g} \approx -g_{m1} Z_L \frac{1}{s \frac{C_{gs2}}{g_{m2}} + 1},$$

(2.22)

where  $L_g$  is excluded. Taking the effect of  $L_g$  and channel length modulation of  $M_1$  into account, the gain expression becomes

$$A_{v,wL_g} \approx -g_{m1} Z_L \frac{1}{s^2 \frac{L_g C_{gs2}}{g_{m2} r o_1} + s \frac{C_{gs2}}{g_{m2}} + 1}.$$

(2.23)

The frequency response has changed from a one-pole response (with a pole at  $s = -\frac{g_{m2}}{C_{gs2}}$ ) to a two-pole response (with the new pole frequency adjusted by  $L_g$ ). Thus, bandwidth peaking may be realized.

A significant impact of adding the gate inductor is stability as it introduces positive feedback. Qualitatively, the impedance of the gate inductor ramps up as frequency increases, which makes the gate of the CG stage floating. The signal fed back through the drain-to-gate capacitance of  $M_2$  is forced to flow through the source and eventually back to the input of the amplifier. Therefore, the isolation is deteriorated (i.e., the amplifier is less stable, as explained in Appendix A). Quantitatively, with channel length modulation neglected, the real part of the input impedance of the CG stage ( $R_{in,CG}$ ) is approximately

$$R_{in,CG}(s) \approx \frac{1 + s^2 L_g C_{gs2}}{g_{m2} + s C_{gs2}}.$$

(2.24)

When  $sC_{gs2} \ll g_{m2}$  in Eq. 2.24,

$$R_{in,CG}(s) \approx \frac{1}{g_{m2}} (1 + s^2 L_g C_{gs2}),$$

(2.25)

which will become negative if the frequency is beyond the resonant frequency of  $L_g$  and  $C_{gs2}$  (i.e.,  $\frac{1}{\sqrt{L_g C_{gs2}}} rad/s$ ). As a result, the amplifier becomes unstable due to this positive feedback. Thus, the value of  $L_g$  has to be chosen properly to ensure the unstable region is far beyond the operating frequency.

The three-stage cascode with inductive peaking (at the gate of CG) utilizing 65-nm CMOS in [14] reports a gain of 20.6 dB at 60 GHz across a -3dB bandwidth of 14.1 GHz. The in-band minimum noise figure is 4.9 dB at 58 GHz. With a supply voltage of 1.2 V, the output -1dB compression point is at -8.4 dBm. The second design in [14] utilizes spiral inductor instead of transmission-line based passives. It achieves a gain of 18 dB across a bandwidth of 12.2 dB. The in-band minimum noise figure improves to 4 dB at 61 GHz. The reduction in bandwidth and improvement in gain could be due to the spiral inductor has a higher quality factor (i.e., with a high quality factor, ohmic losses are improved but bandwidth shrinks). With the same supply voltage, the output -1dB compression point is at -5 dBm. The design in [15] uses inductive peaking at both internode (series peaking) and the gate of CG. It realizes a gain of 20 dB across a bandwidth from 24 to 48 GHz. The in-band minimum noise figure is 3.1 dB. With a supply voltage of 1.2 V, the output -1dB compression point is at -3 dBm.

#### 2.3.3 Performance Summary

Table 2.2 summarizes the specifications of the topologies covered in previous sections. At mm-wave frequencies, cascading multiple stages is a common way to realize high gain, as seen from all the entries. With the same process, lower noise figure is observed from lower operating frequency, which matches with the trend predicted by Eq. 2.1 (2, 3.3, 4.0, and 5.7 dB noise figure at K, Q, V, W bands from [11] and [12], respectively). Compared between [12], [13] and [14], more advanced process technology seems to generally have a lower noise figure, as the transition frequency of transistors becoming higher. Lower supply voltage generally leads to lower  $IIP_3$  (as seen from [12]). Thus, to mitigate this problem, the DC bias of the output stage can be set to above nominal to provide more voltage headroom to improve linearity (as seen from [11]). High input return loss is difficult to be maintained across the -3 dB bandwidth, as seen from the table. Thus, a wideband input matching network may be considered, as  $S_{11}$  is a critical specification of an LNA. Lastly, if the transistor is biased around  $\left(\frac{I_{DS}}{W_{opt}}\right)$  (for lowest device noise), the required bias current is predicted to decrease as operating frequency increases, which leads to low power consumption. This trend is confirmed in [12].

| Ref.          | Technology        | Topology                            | $S_{21}$ (dB) | $f_o$ (GHz)        | NF (dB) | $S_{11}$ (dB)     | $IIP_3$ (dBm) | $V_{DC}$         | $P_{DC}$ (mW) |

|---------------|-------------------|-------------------------------------|---------------|--------------------|---------|-------------------|---------------|------------------|---------------|

| [11]          | 45-nm CMOS<br>SOI | 2-stage<br>cascode                  | 19.5          | $16 \sim 24$       | 2.0     | <-51              | -8            | 1.5 V            | 32.5          |

| [12]<br>Work1 | 45-nm CMOS<br>SOI | 2-stage<br>cascode                  | 15            | $40 \sim 53$       | 3.3     | <-81              | -13.5         | 1.3 V            | 20.8          |

| [12]<br>Work2 | 45-nm CMOS<br>SOI | 2-stage<br>cascode                  | 12.5          | $60 \sim 73$       | 4.0     | <-13 <sup>1</sup> | -14.5         | 1.3 V            | 15            |

| [12]<br>Work3 | 45-nm CMOS<br>SOI | 3-stage<br>common-source            | 14.7          | $76 \sim 88$       | 5.7     | $<-6^{1}$         | -16.2         | 1.0 V            | 13.5          |

| [13]<br>Work1 | 65-nm CMOS        | 2-stage<br>Series Peaking           | 16            | $48 \sim 62^1$     | 4.5     | $<-7^{1}$         | N/A           | N/A              | 10            |

| [13]<br>Work2 | 130-nm CMOS       | Triple cascode<br>Series Peaking    | 14.3          | $36 \sim 42^1$     | 3.8     | $<-7^{1}$         | N/A           | N/A              | 28.8          |

| [14]<br>Work1 | 65-nm CMOS        | 3-stage CG<br>GatePeaking           | 20.6          | $54 \sim 68.1^{1}$ | 4.9     | $<-5^{1}$         | -19.4         | $1.2 \mathrm{V}$ | 33.6          |

| [14]<br>Work2 | 65-nm CMOS        | 3-stage CG<br>GatePeaking           | 18            | $56 \sim 68.2^1$   | 4       | <-61              | -13.4         | 1.2 V            | 28.8          |

| [15]<br>Work1 | 90-nm CMOS        | 3-stage Series & CG<br>Gate Peaking | 20            | $24 \sim 48$       | 3.1     | <-51              | -13.4         | 1.2 V            | 21.1          |

Table 2.2: Typical performance of mm-wave LNAs

<sup>1</sup>Estimated from plots

<sup>2</sup>Estimated from  $P_{-1dB}$

# Chapter 3

# Design

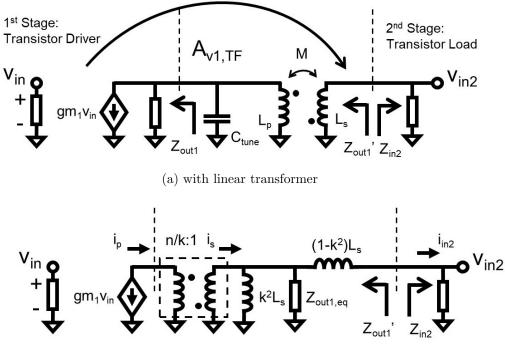

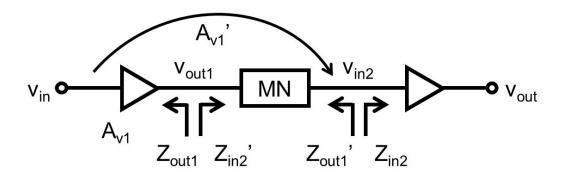

In the previous chapter, it is shown that cascading multiple cascode stages typically achieves a noise figure around 3 dB. Applying noise-matching technique at the interstage is one option to realize sub-2 dB noise figure. In this chapter, greater than 0.13 dB improvement in noise figure is shown after analyzing the cascade noise factor of noise-matching versus conjugate-matching interstages. Design examples of a two-stage amplifier with transformer-coupled, noise-matching interstage are discussed in detail. After considering device selection for the lowest noise factor, the choice of interstage transformer parameters is presented. Lastly, a design methodology for the low-noise amplifier is summarized.

## 3.1 Design A: a Two-Stage Amplifier with Noise-Matching Interstage

The amplifier is single-ended to lower power consumption and to save chip area, at the expense of lower isolation.

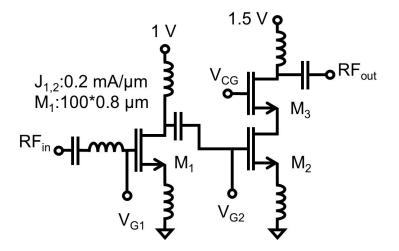

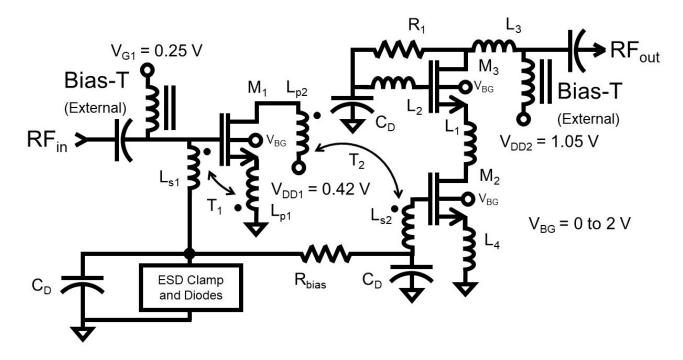

#### 3.1.1 Proposed Circuit Topology

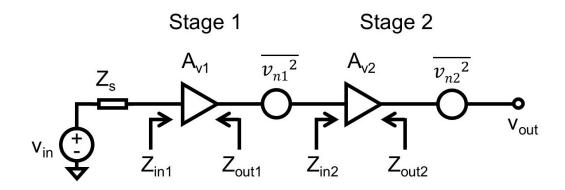

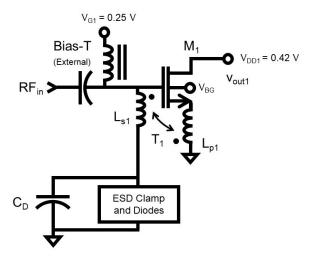

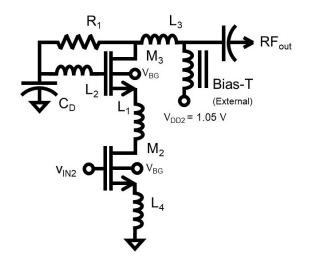

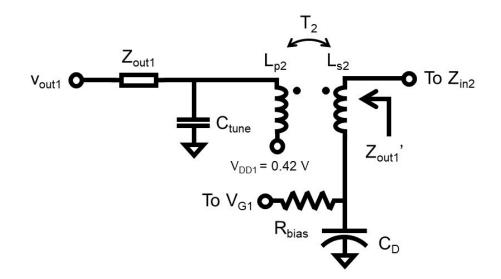

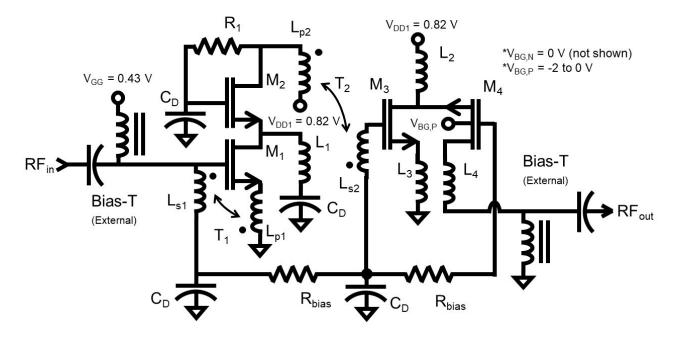

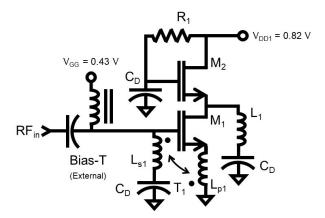

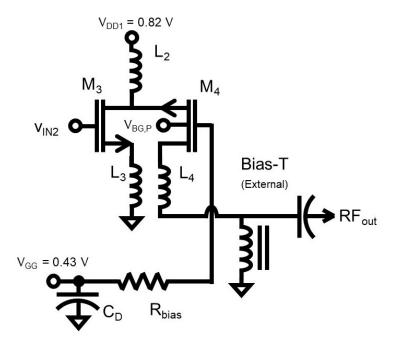

Figure 3.1: Topology of a two-stage amplifier with interstage noise matching

The overall schematic is shown in Fig. 3.1 above. The first stage consists of a commonsource amplifier that is biased at  $\frac{I_{DS}}{W_{opt}}$ . Transistor  $M_1$  is sized such that its  $R_{opt}$  is close to 50  $\Omega$ . Impedance transformation via  $T_1$  is used to realize the input conjugate and noise match simultaneously. The supply voltage of the first stage  $(V_{DD1})$  is set at 0.42 V to reduce DC power consumption (at the cost of some noise and linearity degradation). The second stage consists of a cascode amplifier  $(M_2/M_3)$  with  $M_2$  resistively biased at the same gate voltage as  $M_1$  via  $R_{bias}$ . Thus,  $M_2$  also operates at  $\frac{I_{DS}}{W_{opt}}$  for lowest device noise. The interstage transformer  $T_2$  transforms the output impedance of the first stage to the optimum source impedance for minimum noise  $(Z_{n,opt2})$  from the second stage. As a result, both stages are biased and matched for lowest noise. Inductor  $L_1$  is used to peak the response and thereby suppress the noise contributed by  $M_3$ . Inductor  $L_2$  is used to further extend the bandwidth, but the value is selected carefully so that the amplifier remains stable. Resistor  $R_1$  is used to bias  $M_3$ , as well as to pad the output impedance. The total output reactance of the second stage is nulled by  $L_3$  to give a wideband output return loss. Inductor  $L_4$  provides degeneration, which improves stability. The supply voltage of the second stage  $(V_{DD2})$  is chosen above the nominal voltage to provide more output headroom for better linearity, at the cost of some transistor reliability degradation (during turn-on, the drain-to-source voltage across  $M_3$  may be higher than nominal  $V_{DS}$ ). The design is ESD protected by a network consisting of an RC-clamp and a double-diode connected from the bottom of  $L_{s1}$  to ground.

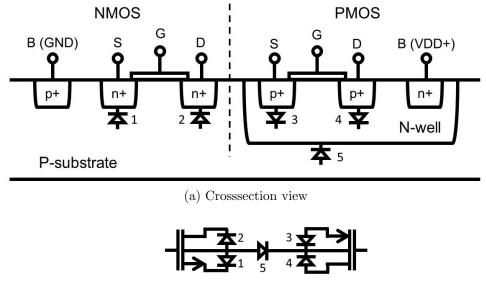

#### 3.1.2 Body-Bias and the Flip-Well Structure

Body-bias trimming of an FD-SOI FET may be used to optimize the threshold-voltage  $(V_{TH})$  of transistors, which may be advantageous as the gate dielectric thickness becomes challenging to be scaled down [25]. Forward body-bias (i.e., applying a positive relative voltage on the body of NFETs or negative relative voltage on the body of PFETs) can lower transistor  $V_{TH}$  to allow higher drive and faster switching capabilities. Reverse body-bias (i.e., applying a negative relative voltage on the body of NFETs) raises  $V_{TH}$  to allow lower leakage. However, in a traditional bulk CMOS process, the range of forward body-bias is limited by the threshold voltage of parasitic diodes between wells, as depicted in Fig. 3.2.

(b) Schematic view

Figure 3.2: Forward body-bias limitations in a bulk CMOS process

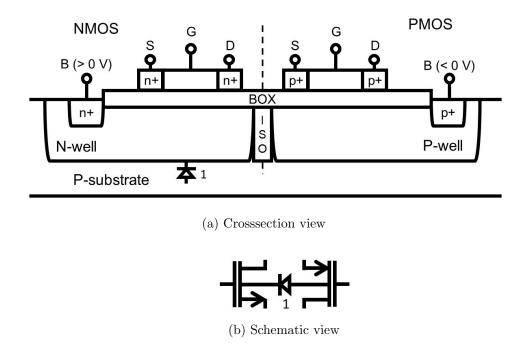

The 22-nm CMOS-SOI process has a buried oxide layer between the source/drain and substrate which enables a flip-well device, where NFETs are fabricated in N-wells instead of P-wells (and PFETs are fabricated in P-wells instead of N-wells). With the flip-well scheme, most of the parasitic diodes shown in Fig. 3.2 no longer exist, which leads to a large voltage range of forward body-bias. The body-bias limit becomes the threshold voltage of the parasitic diode between the P-well and N-well, which will only limit reverse body-bias operations, as shown in Fig. 3.3.

Figure 3.3: Body-bias limitations in the 22-nm CMOS-SOI process

#### 3.1.3 Characterization of Active Devices in Simulation

Transconductance  $(g_m)$ , transition frequency  $(f_T)$ , minimum noise figure  $(NF_{min})$ , transistor unit width and optimum source resistance for minimum noise  $(R_{opt})$  are transistor metrics simulated for designing for lowest noise. By simulating  $f_T$  and  $NF_{min}$  versus current per unit transistor width  $(\frac{I_{DS}}{W})$ , the DC bias point may be selected around where lowest  $NF_{min}$  occurs. Then, the optimum unit transistor width is found by simulating  $NF_{min}$  versus different finger width. Lastly, the total width of the transistor is selected based on the simulation of  $R_{opt}$  to realize noise matching.