# 45-nm SOI CMOS Bluetooth Electrochemical Sensor for Continuous Glucose Monitoring

by

Aman Muthreja

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2018

© Aman Muthreja 2018

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Due to increasing rates of diabetes, non-invasive glucose monitoring systems will become critical to improving health outcomes for an increasing patient population. Bluetooth integration for such a system has been previously unattainable due to the prohibitive energy consumption. However, enabling Bluetooth allows for widespread adoption due to the ubiquity of Bluetooth-enabled mobile devices. The objective of this thesis is to demonstrate the feasibility of a Bluetooth-based energy-harvesting glucose sensor for contact-lens integration using 45 nm silicon-on-insulator (SOI) complementary metal-oxide-semiconductor (CMOS) technology.

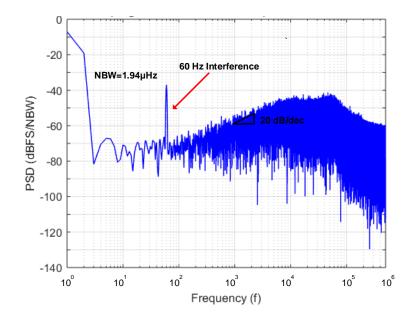

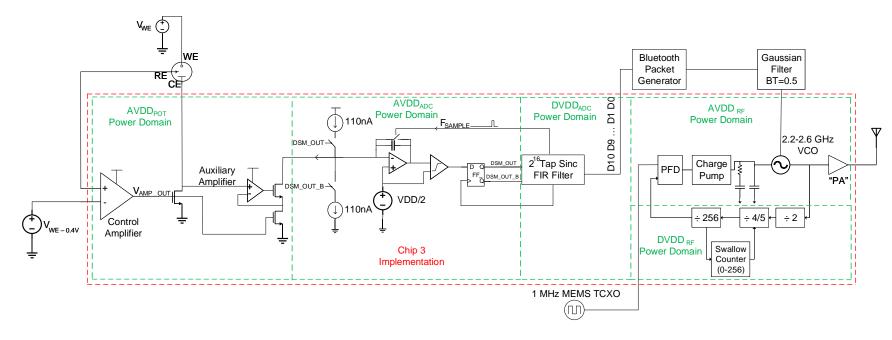

The proposed glucose monitoring system includes a Bluetooth transmitter implemented as a two-point closed loop PLL modulator, a sensor potentiostat, and a 1st-order incremental delta-sigma analog-to-digital converter (IADC). This work details the complete system design including derivation of top-level specifications such as glucose sensing range, Bluetooth protocol timing, energy consumption, and circuit specifications such as carrier frequency range, output power, phase-noise performance, stability, resolution, signal-tonoise ratio, and power consumption. Three test chips were designed to prototype the system, and two of these were experimentally verified. Chip 1 includes a partial implementation of a phase-locked-loop (PLL) which includes a voltage-controlled-oscillator (VCO), frequency divider, and phase-frequency detector (PFD). Chip 2 includes the design of the sensor potentiostat and IADC. Finally, Chip 3 combines the circuitry of Chip 1 and Chip 2, along with a charge-pump, loop-filter and power amplifier to complete the system.

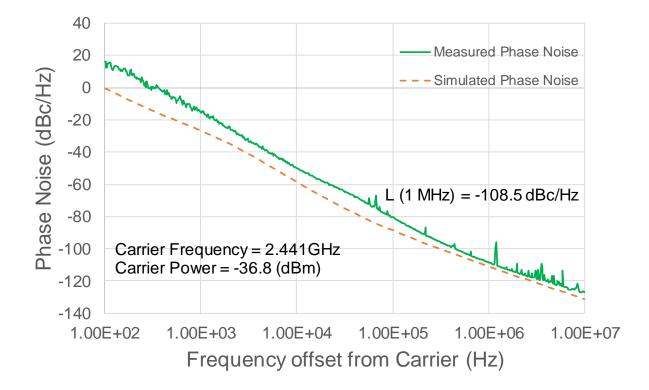

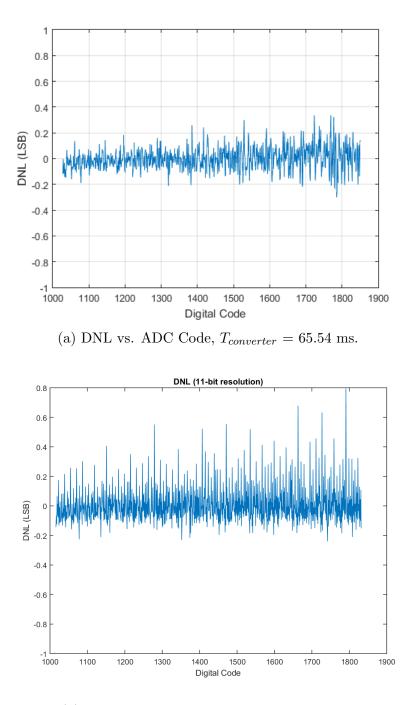

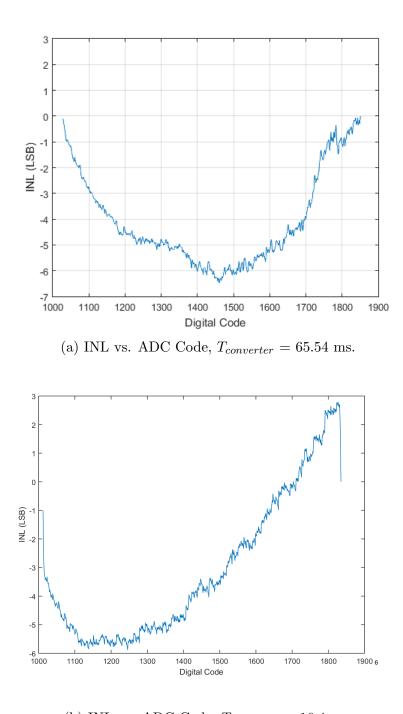

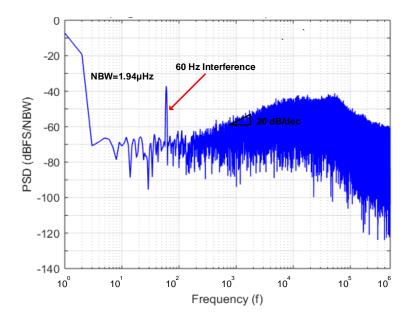

Chip 1 DC power consumption was measured to be 204.8  $\mu$ W, while oscillating at 2.441 GHz with an output power  $P_{out}$  of -35.8 dBm, phase noise at 1 MHz offset L(1 MHz) of -108.5 dBc/Hz, and an oscillator figure of merit (FOM) of 183.44 dB. Chip 2 achieves a total DC power consumption of 5.75  $\mu$ W. The system has a dynamic range of 0.15 nA – 100 nA at 10-bit resolution. The integral non-linearity (INL) and differential non-linearity (DNL) of the IADC were measured to be -6 LSB/±0.3 LSB respectively with a conversion time of 65.56 ms. This work achieves the best duty-cycled DC power consumption compared to similar glucose monitoring systems, while providing sufficient performance and range using Bluetooth.

#### Acknowledgments

I would like to thank my advisors Dr. John Long and Dr. Peter Levine for their continued guidance, advice and feedback.

I would also like to thank my colleagues for putting up with me during these two years.

Finally, I would like to thank my family and my fiance Jessica. Their love and support has been indispensable.

# **Table of Contents**

| Li | List of Tables vi |         |                                        |    |

|----|-------------------|---------|----------------------------------------|----|

| Li | st of             | Figure  | es<br>S                                | x  |

| 1  | Intr              | oducti  | on                                     | 1  |

|    | 1.1               | Motiva  | ation                                  | 1  |

|    | 1.2               | Scope   |                                        | 2  |

|    | 1.3               | Design  | Challenges and Objectives              | 4  |

|    |                   | 1.3.1   | Bluetooth Compliance                   | 4  |

|    |                   | 1.3.2   | System Energy Budget                   | 6  |

|    |                   | 1.3.3   | Glucose Sensor Specifications          | 10 |

|    |                   | 1.3.4   | Low-Voltage, Low-Power Design          | 10 |

|    | 1.4               | Thesis  | Organization                           | 11 |

| 2  | Lite              | erature | Survey and Topology Overview           | 13 |

|    | 2.1               | Review  | v of Wireless Sensor Systems           | 13 |

|    |                   | 2.1.1   | System by Liao et al                   | 16 |

|    |                   | 2.1.2   | System by Zhang et al                  | 17 |

|    |                   | 2.1.3   | System by Xiao et al                   | 18 |

|    | 2.2               | Review  | v of Wireless Sensor System Components | 19 |

|    |                   | 2.2.1   | Review of Bluetooth Transmitters       | 19 |

|   |     | 2.2.2   | Review of Electrochemical Glucose Sensors | 31        |

|---|-----|---------|-------------------------------------------|-----------|

|   |     | 2.2.3   | Review of Sensor Readout                  | 37        |

| 3 | Low | -Powe   | r Bluetooth Transmitter Design            | 41        |

|   | 3.1 |         | Design                                    | 43        |

|   |     | 3.1.1   | Voltage-Controlled Oscillator (VCO)       | 43        |

|   |     | 3.1.2   | Frequency Divider                         | 56        |

|   |     | 3.1.3   | Phase/Frequency Detector and Charge Pump  | 59        |

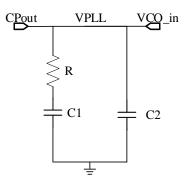

|   |     | 3.1.4   | Loop Filter Parameters                    | 64        |

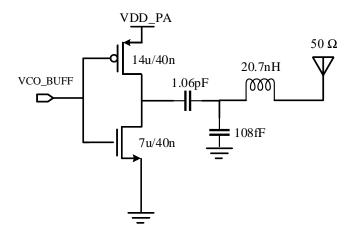

|   | 3.2 | Power   | Amplifier (PA) Design                     | 65        |

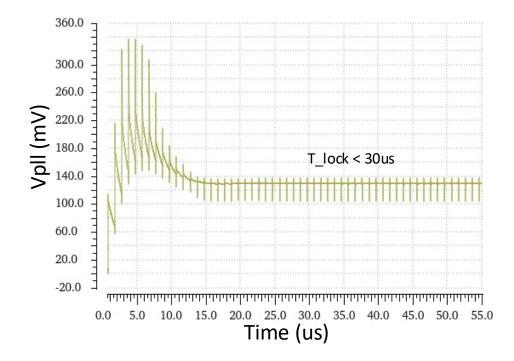

|   | 3.3 |         | mitter Simulation Results                 | 68        |

| 4 | Pot | entiost | at and Sensor Readout Design              | <b>74</b> |

|   | 4.1 |         | tiostat                                   | 74        |

|   |     | 4.1.1   | Voltage Regulation                        | 76        |

|   |     | 4.1.2   | Gain-boosted current mirror               | 82        |

|   | 4.2 | Increm  | nental ADC                                | 84        |

|   |     | 4.2.1   | Integrator                                | 86        |

|   |     | 4.2.2   | Comparator                                | 92        |

|   |     | 4.2.3   | Decimation Filter                         | 94        |

|   |     | 4.2.4   | ADC Simulations                           | 95        |

| 5 | Exp | oerimei | ntal Results                              | 101       |

|   | 5.1 | Partia  | l Bluetooth TX (Chip 1)                   | 101       |

|   |     | 5.1.1   | Chip 1 Layout and Fabricated Device       | 103       |

|   |     | 5.1.2   | Chip 1 Test PCB                           | 105       |

|   |     | 5.1.3   | Measurement Results                       | 106       |

|   | 5.2 | Potent  | tiostat and Readout Circuit (Chip 2)      | 116       |

|              |       | 5.2.1    | Chip 2 Layout and Fabricated Device             | 119 |

|--------------|-------|----------|-------------------------------------------------|-----|

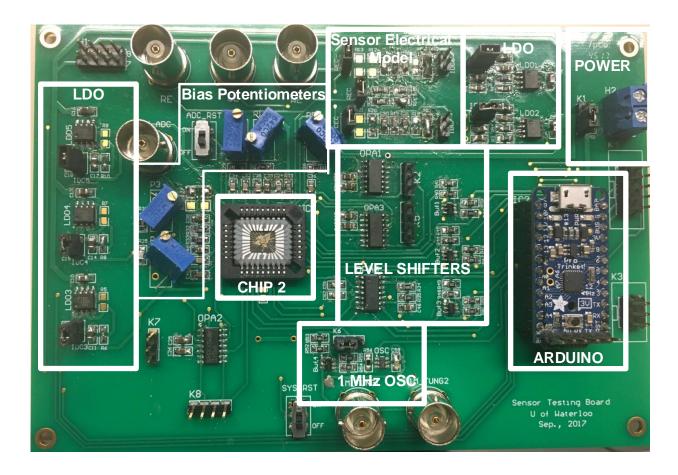

|              |       | 5.2.2    | Chip 2 Test PCB                                 | 121 |

|              |       | 5.2.3    | Measurement Results                             | 123 |

|              | 5.3   | Compl    | lete Bluetooth TX and Sensor Circuitry (Chip 3) | 134 |

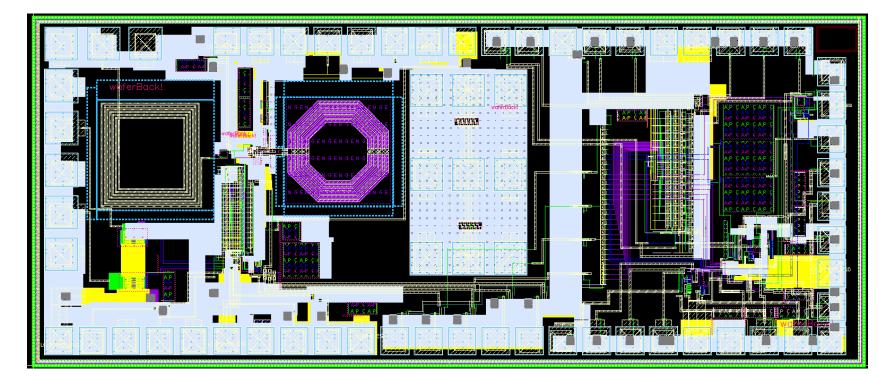

|              |       | 5.3.1    | Chip 3 Layout                                   | 136 |

| 6            | Cor   | clusio   | ns and Future Work                              | 138 |

|              | 6.1   | Future   | e Work                                          | 141 |

| Re           | efere | nces     |                                                 | 142 |

| A            | PPE   | NDICI    | ES                                              | 146 |

| A            | CM    | OS 45    | nm RFSOI Technology                             | 147 |

|              | A.1   | CMOS     | Silicon-on-Insulator Technology                 | 147 |

|              | A.2   | Transi   | stor Performance Simulations at 0.5V            | 150 |

| В            | Reg   | gister N | Map and Pin Descriptions for all tape-outs      | 154 |

|              | B.1   | Chip 1   |                                                 | 154 |

|              | B.2   | Chip 2   | 2                                               | 157 |

|              | B.3   | Chip 3   | 3                                               | 160 |

| С            | Ver   | ilog-A   | model of VCO                                    | 166 |

| D            | Ard   | luino C  | Code for testing                                | 168 |

|              | D.1   | Chip 1   |                                                 | 168 |

|              | D.2   | Chip 2   | 2                                               | 172 |

| $\mathbf{E}$ | Mat   | tlab Co  | ode for Chip 2                                  | 180 |

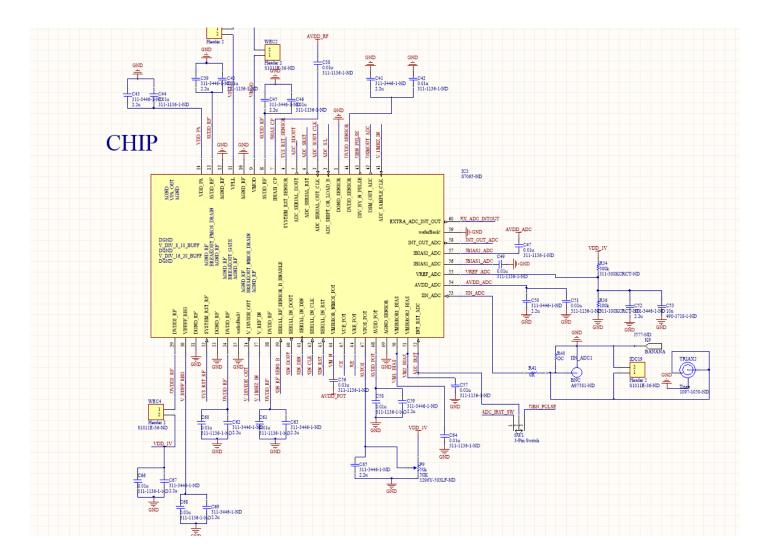

| F            | Tes   | t PCB    | schematic for Chip 3                            | 188 |

# List of Tables

| 1.1 | BLE Transmitter Requirements [1]                                       | 5   |

|-----|------------------------------------------------------------------------|-----|

| 1.2 | System Power and Energy Budget                                         | 8   |

| 2.1 | Performance summary of energy harvesting wireless biosensors           | 14  |

| 2.2 | Performance summary of energy harvesting wireless biosensors continued | 15  |

| 2.3 | Performance summary of BLE transmitters                                | 29  |

| 2.4 | Summary of Electrode Dimensions [2]                                    | 32  |

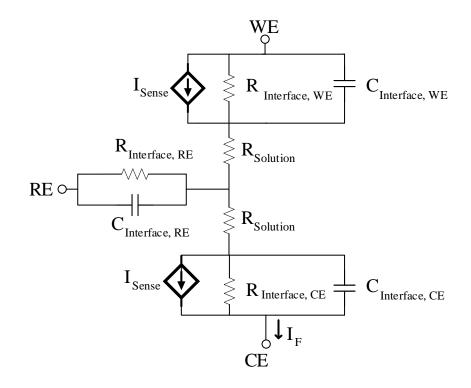

| 2.5 | Parameters used to model the sensor implemented in $[2]$               | 34  |

| 3.1 | BLE Transmitter Requirements [1]                                       | 41  |

| 3.2 | VCO Specifications                                                     | 44  |

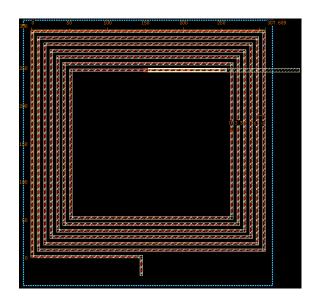

| 3.3 | Inductor Performance Summary                                           | 46  |

| 3.4 | Cross-coupling size and performance summary                            | 46  |

| 3.5 | Divider simulated power consumption.                                   | 59  |

| 3.6 | PA specifications vs. requirements                                     | 68  |

| 3.7 | TX power consumption summary.                                          | 73  |

| 3.8 | TX specifications vs. simulated results                                | 73  |

| 4.1 | Sensor Specifications.                                                 | 75  |

| 4.2 | Potentiostat and Readout Power Consumption Targets                     | 75  |

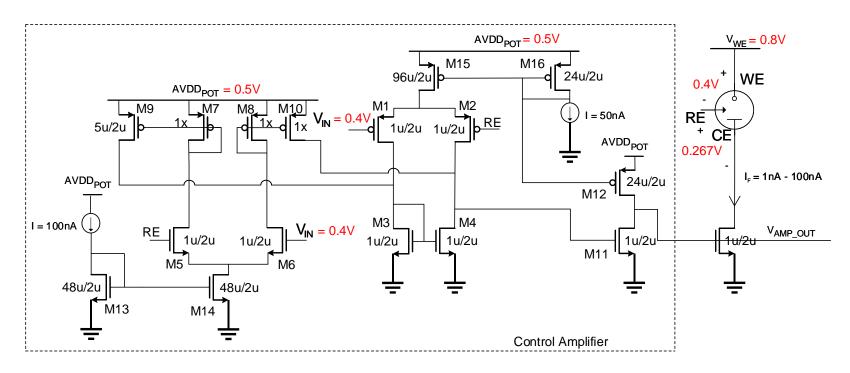

| 4.3 | Control Amplifier Performance Summary                                  | 81  |

| 4.4 | Overall Sensor Power Consumption                                       | 100 |

| 5.1 | Simulation compared with experimental results with $V_{PLL} = 0.5 V, PVT =$ | 440 |

|-----|-----------------------------------------------------------------------------|-----|

|     | 000                                                                         | 116 |

| 5.2 | Measured Sensor Power Consumption Compared to Simulation                    | 127 |

| 5.3 | Measured sensor performance summary                                         | 127 |

| 6.1 | Comparison of results against previous work                                 | 140 |

| A.1 | Summary of relevant transistors                                             | 151 |

| A.2 | Relevant simulation data for NMOS transistors                               | 153 |

| B.1 | Register map for Chip 1                                                     | 156 |

| B.2 | Register map for Chip 1                                                     | 157 |

| B.3 | Register map for Chip 2                                                     | 159 |

| B.4 | Register map for Chip 2                                                     | 160 |

| B.5 | Pin description table for Chip 3                                            | 163 |

| B.6 | Pin description table for Chip 3                                            | 164 |

| B.7 | RF Register map for Chip 3                                                  | 165 |

| B.8 | Sensor Register map for Chip 3                                              | 165 |

# List of Figures

| Smart contact-lens energy harvesting glucose monitoring system [3] | 2                                                   |

|--------------------------------------------------------------------|-----------------------------------------------------|

| Overview of the proposed glucose monitoring system                 | 3                                                   |

| BLE Frequency Spectrum [4]                                         | 5                                                   |

| System timing overview                                             | 9                                                   |

| System architecture of [2]                                         | 16                                                  |

| System architecture of $[5]$                                       | 17                                                  |

| System overview of [6]                                             | 18                                                  |

| Non-connectable non-scannable advertising event structure $[1]$    | 20                                                  |

| Two-point GMSK Transmitter Architecture                            | 22                                                  |

| I/Q based GMSK Transmitter Architecture                            | 22                                                  |

| Conceptual RF Synthesizer [7]                                      | 24                                                  |

| Integer-N PLL [7]                                                  | 25                                                  |

| A block diagram of the PLL in the frequency domain                 | 25                                                  |

| CMOS LC VCO-without tail current source [7]                        | 26                                                  |

| Ideal Class-D PA                                                   | 28                                                  |

| System architecture of [8]                                         | 31                                                  |

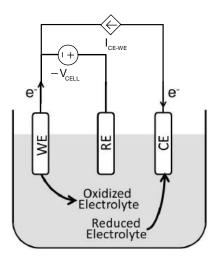

| Standard three electrode system [9]                                | 32                                                  |

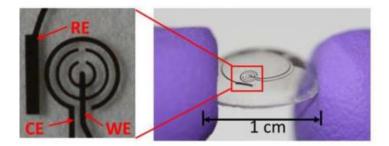

| Contact Lens Glucose Sensor [2]                                    | 33                                                  |

| Model of Electrochemical Glucose Cell                              | 34                                                  |

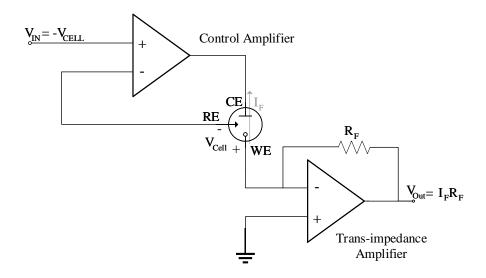

| Example of a grounded WE topology [10]                             | 36                                                  |

|                                                                    | Overview of the proposed glucose monitoring system. |

| 2.17 | Potentiostat used in [6]                                                     | 36 |

|------|------------------------------------------------------------------------------|----|

| 2.18 | 1st order delta-sigma ADC Model [11]                                         | 38 |

| 2.19 | Noise Transfer Function for a 1st-order DS-ADC [11]                          | 39 |

| 2.20 | IADC used in [6]                                                             | 40 |

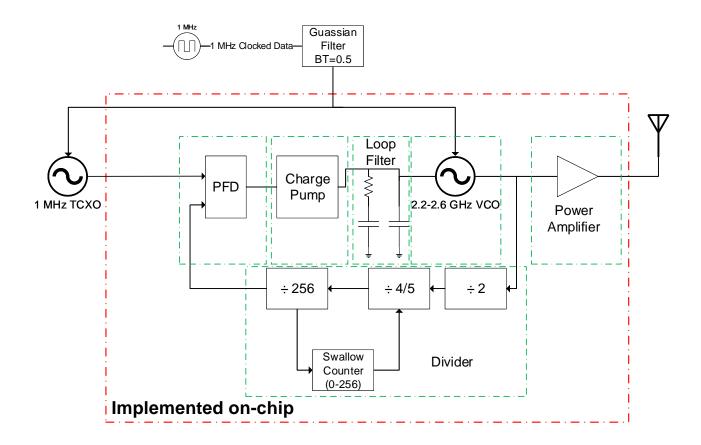

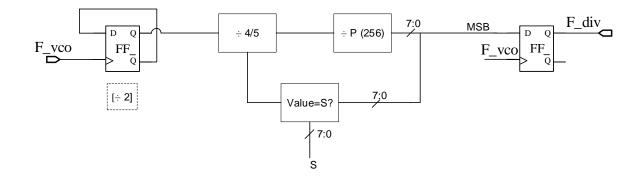

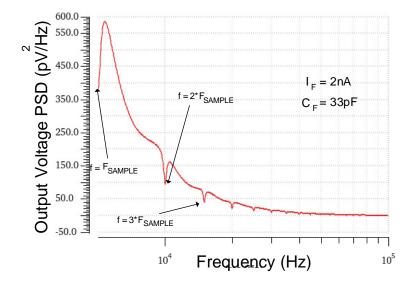

| 3.1  | GMSK modulator system diagram.                                               | 42 |

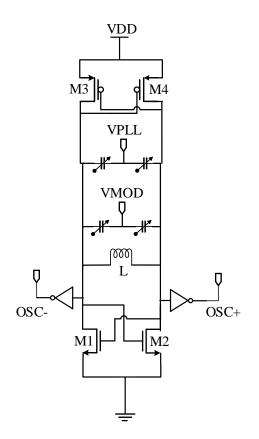

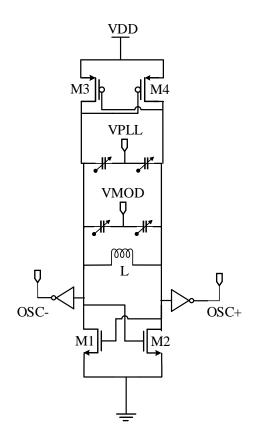

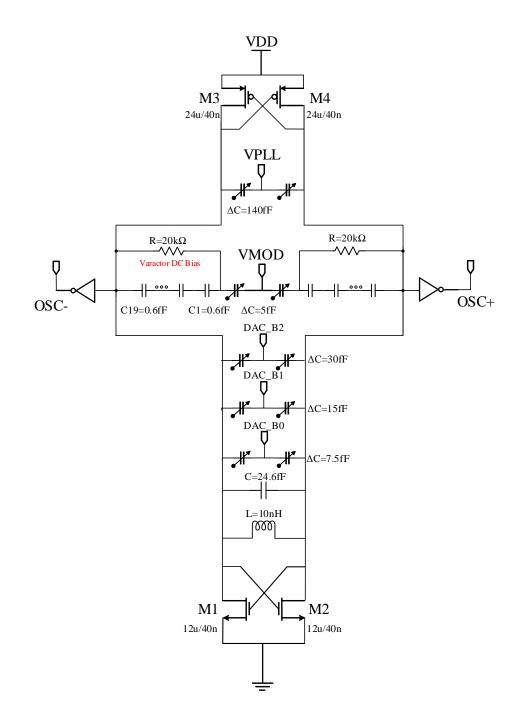

| 3.2  | CMOS LC VCO implemented without PVT capacitor DAC                            | 45 |

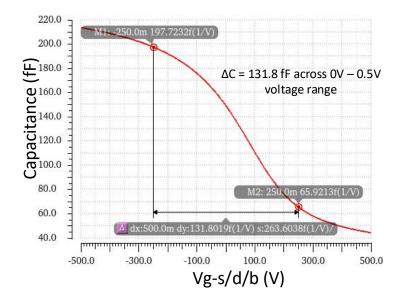

| 3.3  | Accumulation mode varactor CV tuning curve                                   | 47 |

| 3.4  | Annotated VCO schematic.                                                     | 48 |

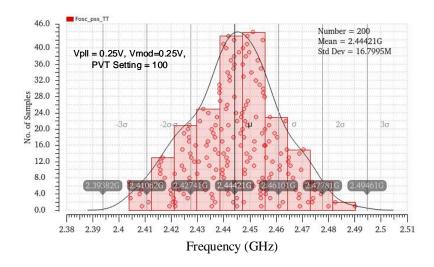

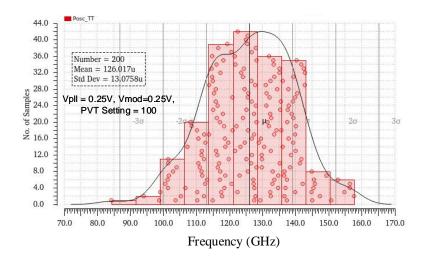

| 3.5  | Monte Carlo simulation of oscillation frequency (200 trials).                | 49 |

| 3.6  | Montecarlo simulation of oscillator power consumption (200 trials). $\ldots$ | 50 |

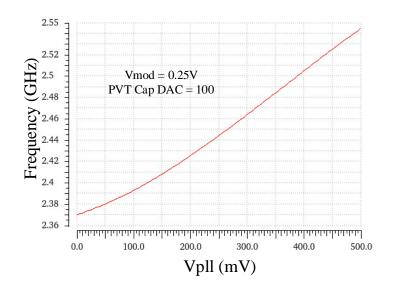

| 3.7  | Oscillation frequency across tuning range                                    | 51 |

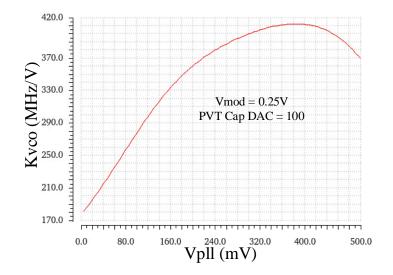

| 3.8  | Oscillation frequency gain (Kvco) across tuning range                        | 52 |

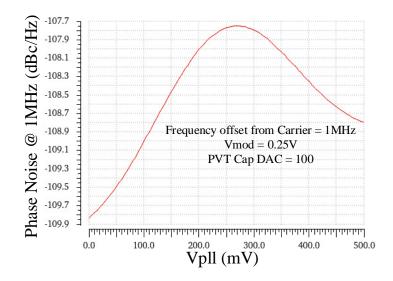

| 3.9  | Phase Noise @ 1MHz across tuning range                                       | 53 |

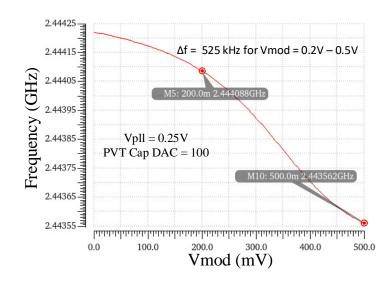

| 3.10 | Oscillation frequency across modulation voltage.                             | 54 |

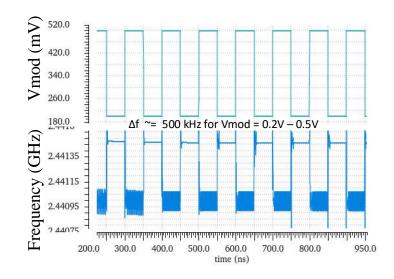

| 3.11 | FSK modulation waveform applied to $V_{mod}$ .                               | 55 |

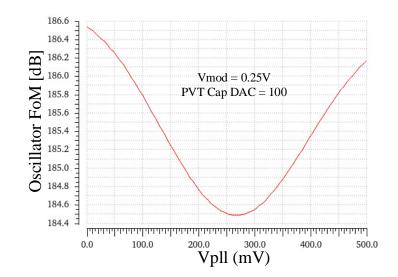

| 3.12 | Oscillator Figure of Merit across tuning range                               | 56 |

| 3.13 | PLL Divider chain                                                            | 57 |

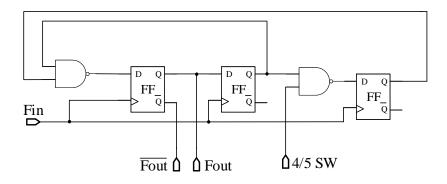

| 3.14 | Dual-modulus divider block diagram.                                          | 58 |

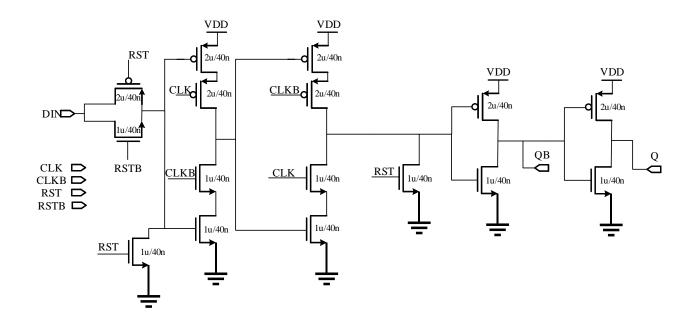

| 3.15 | Dynamic $C^2$ MOS D-flip-flop implementation.                                | 58 |

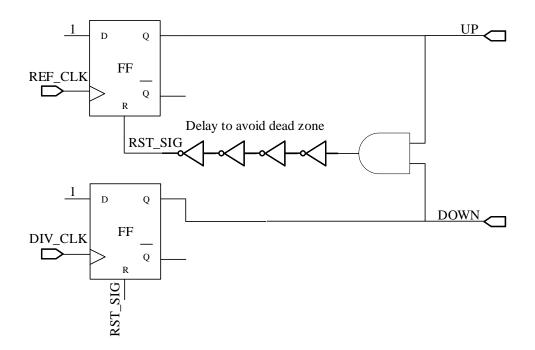

| 3.16 | Phase-frequency detector implementation.                                     | 59 |

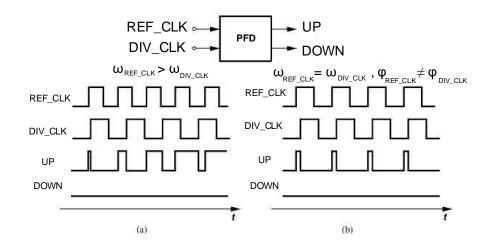

| 3.17 | Response of a PFD to inputs with unequal (a) frequencies, or (b) phases [7]. | 60 |

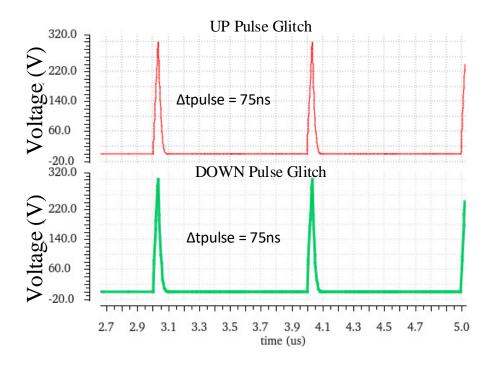

| 3.18 | PFD UP and DOWN pulse glitch when locked.                                    | 62 |

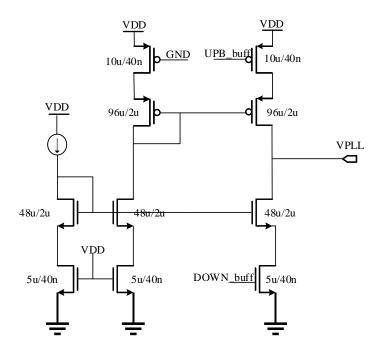

| 3.19 | Charge pump circuit                                                          | 63 |

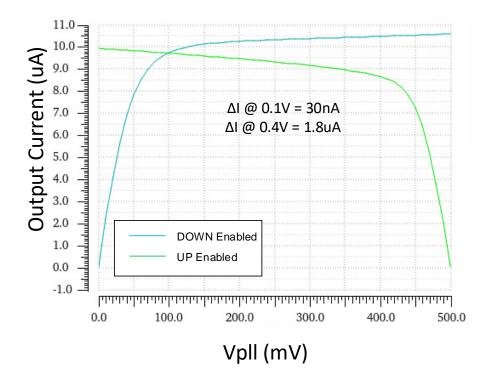

| 3.20 | Charge pump output current vs. tuning voltage                                | 64 |

| 3.21 | Loop Filter                                                                  | 65 |

| 3.22 | PA implemented for the GMSK modulator                                        | 66 |

| 3.23 | Inductor layout used in PA matching network                                  | 68 |

|      |                                                                              |    |

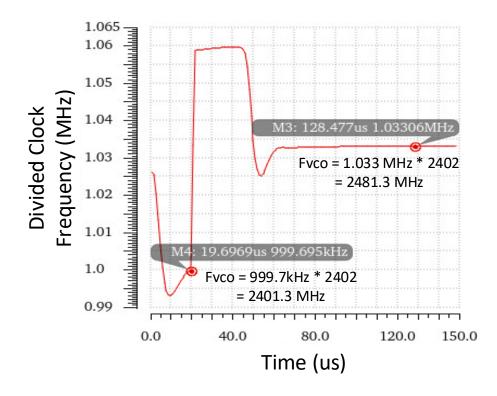

| 3.24 | TX startup locking transient using a Verilog-A VCO model                                               | 69 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 3.25 | PLL locking transient between 2402 MHz and 2480 MHz channel using a Verilog-A VCO model.               | 70 |

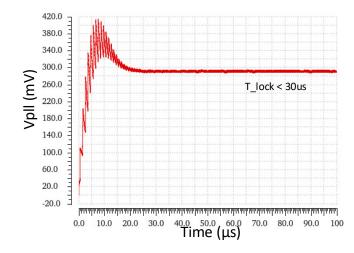

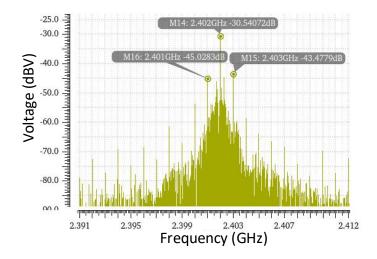

| 3.26 | TX transient simulation showing locking transient from start-up to 2.402 GHz with transistorized VCO   | 71 |

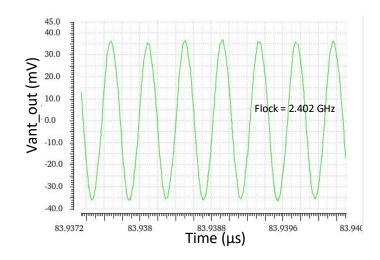

| 3.27 | TX transient simulation showing output waveform at the antenna with par-<br>asitic extracted VCO       | 72 |

| 3.28 | TX transient simulation showing FFT of output waveform with parasitic extracted VCO                    | 72 |

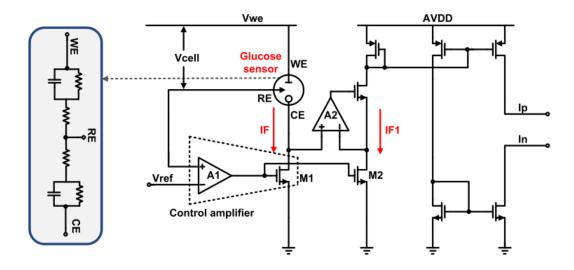

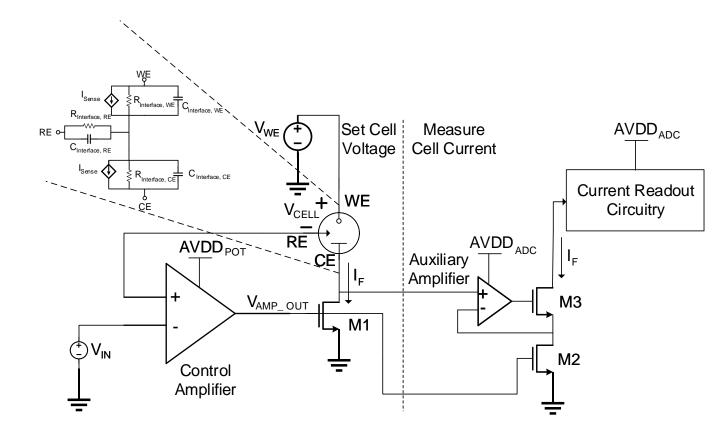

| 4.1  | Potentiostat architecture                                                                              | 76 |

| 4.2  | Control amplifier feedback loop                                                                        | 79 |

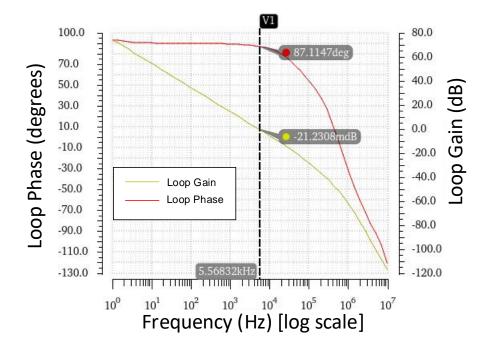

| 4.3  | Simulated loop-gain and phase of control loop with nominal sensor parameters and $I_F$ of 100 nA       | 80 |

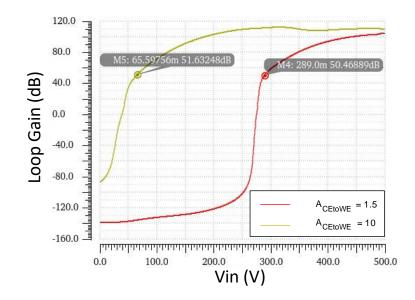

| 4.4  | Simulated DC gain of control loop accross input voltage for two $A_{CEtoWE}$ ratios.                   | 81 |

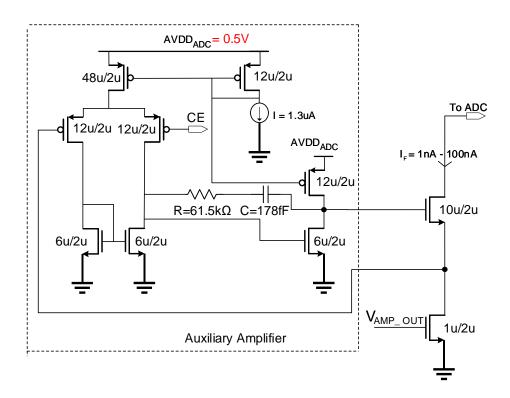

| 4.5  | Schematic of gain-boosted current mirror.                                                              | 82 |

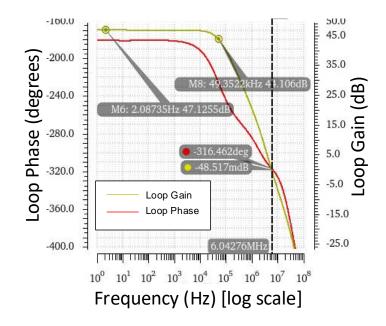

| 4.6  | Loop gain and phase of auxiliary loop with $I_F$ of 100 nA                                             | 83 |

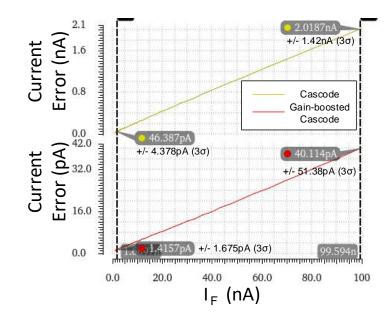

| 4.7  | Absolute current error from sensor to ADC input.                                                       | 84 |

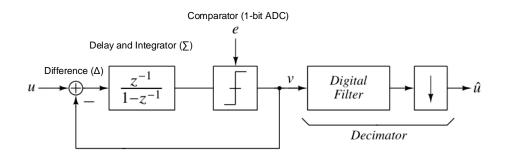

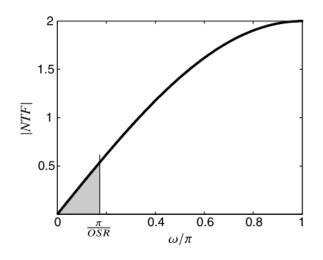

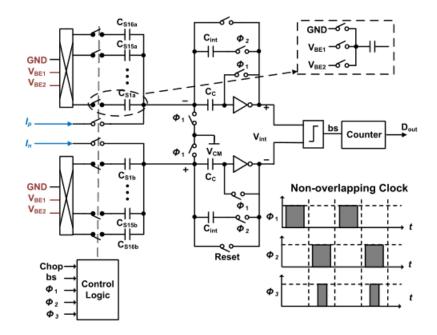

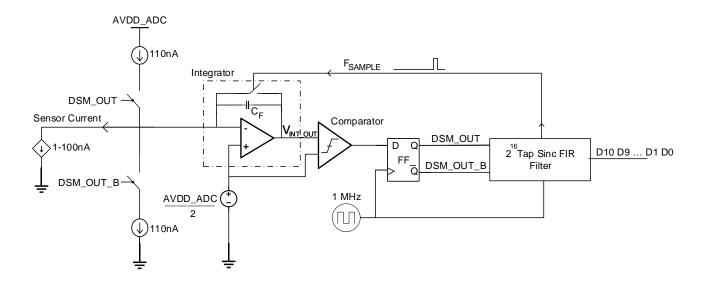

| 4.8  | Incremental ADC architecture                                                                           | 85 |

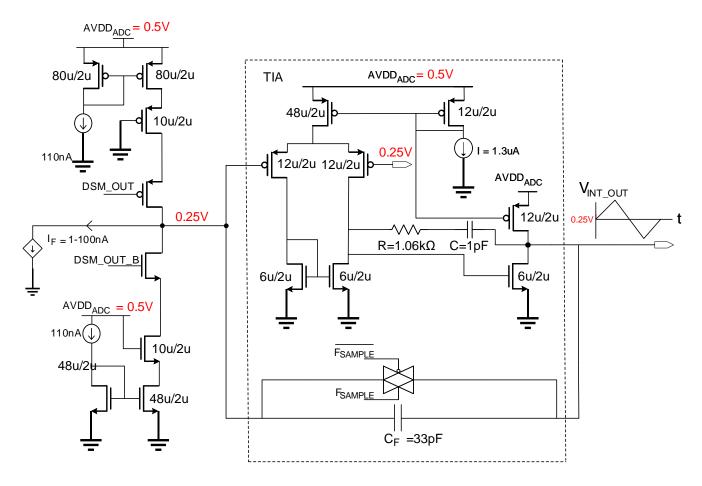

| 4.9  | Schematic of integrator op-amp and current sources in delta-sigma IADC                                 | 87 |

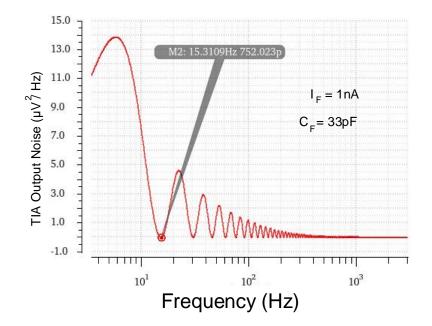

| 4.10 | Simulated output voltage noise PSD of the integrator from current noise generated by the potentiostat. | 90 |

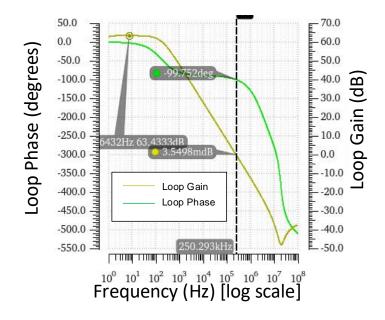

| 4.11 | Open loop gain and phase of the integrator in integrating mode                                         | 91 |

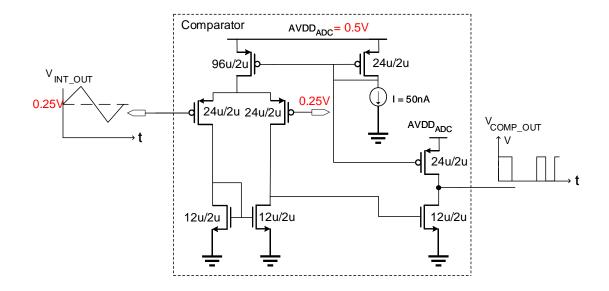

| 4.12 | Implementation of 1-bit ADC                                                                            | 92 |

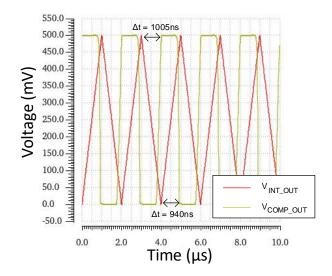

| 4.13 | Transient delay of comparator with 1 MHz large-signal input data                                       | 93 |

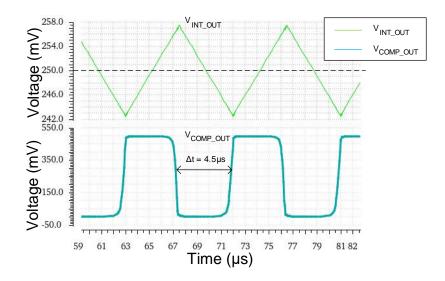

| 4.14 | Transient delay of comparator with small-signal input data                                             | 94 |

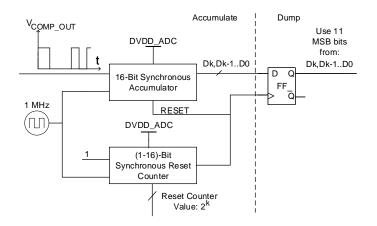

| 4.15 | $2^{1-16}$ Tap Sinc FIR Decimation Filter                                                              | 94 |

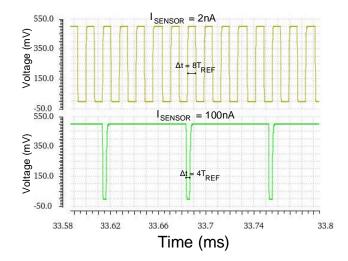

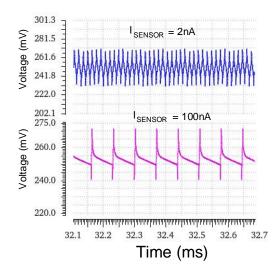

| 4.16 | Modulator output for input glucose current of 2 nA and 100 nA                                          | 96 |

| 4.17 | Integrator output for input glucose current of 2 nA and 100 nA                                         | 97 |

| 4.18 | ADC output spectrum for input glucose current of 2 nA and 100 nA                                                   | 98  |

|------|--------------------------------------------------------------------------------------------------------------------|-----|

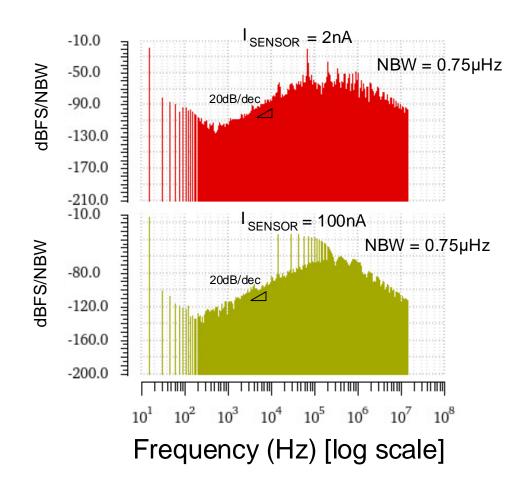

| 4.19 | Simulated ADC noise PSD at the output of the integrator with $F_{SAMPLE} = 5$ kHz, $I_F = 2$ nA, and $C_F = 33$ pF | 99  |

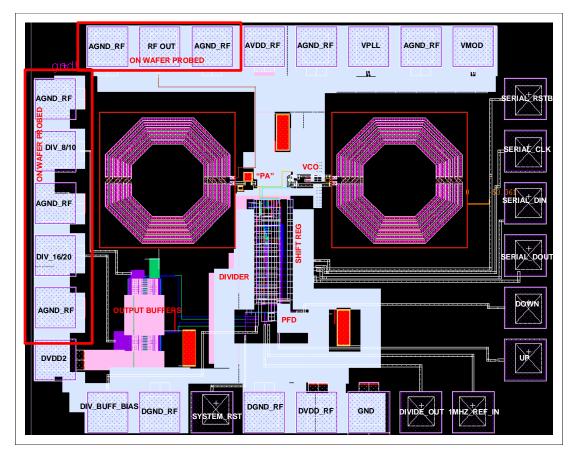

| 5.1  | Architecture of Chip 1                                                                                             | 102 |

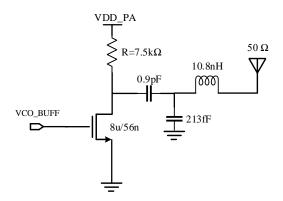

| 5.2  | Initial PA design used in Chip 1                                                                                   | 103 |

| 5.3  | Layout of Chip 1                                                                                                   | 104 |

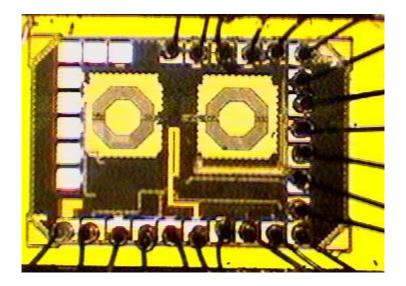

| 5.4  | Die-photo of Chip 1                                                                                                | 105 |

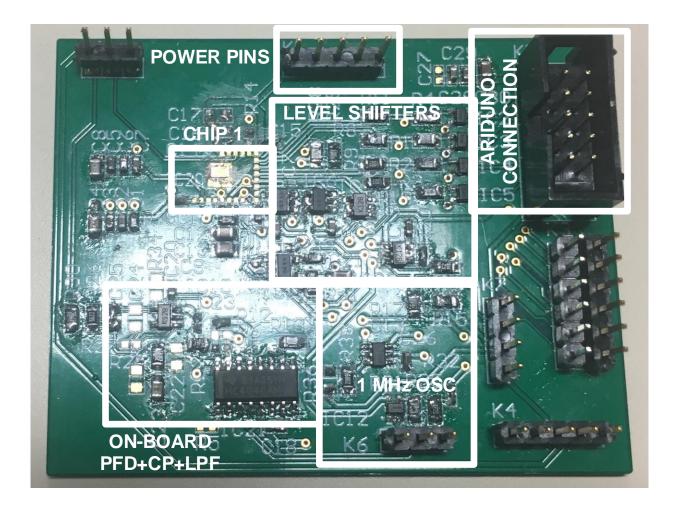

| 5.5  | Test PCB for Chip 1                                                                                                | 106 |

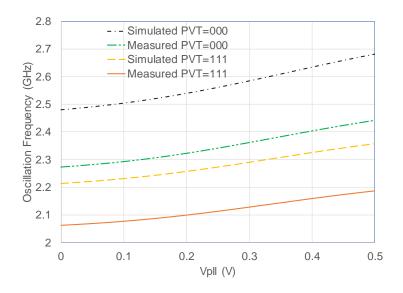

| 5.6  | Oscillation Frequency vs. $V_{PLL}$ at fastest (PVT=000) and slowest (PVT=111) settings.                           | 108 |

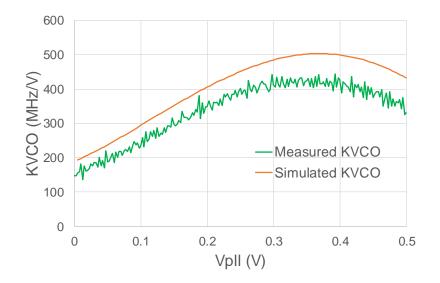

| 5.7  | $K_{VCO}$ vs. $V_{PLL}$ at fastest PVT setting (PVT = 000)                                                         | 108 |

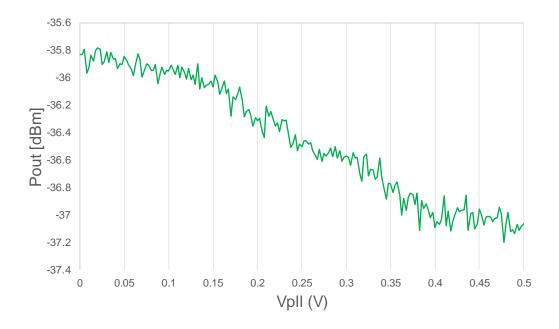

| 5.8  | $P_{OUT}$ vs. $V_{PLL}$ at fastest PVT setting                                                                     | 109 |

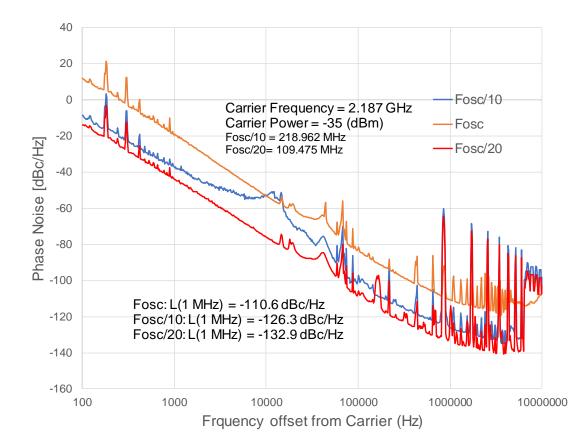

| 5.9  | Phase-noise vs. $F_{OFFSET}$ at 2.45 GHz at PVT=000 and $V_{PLL} = 0.5V.$ .                                        | 110 |

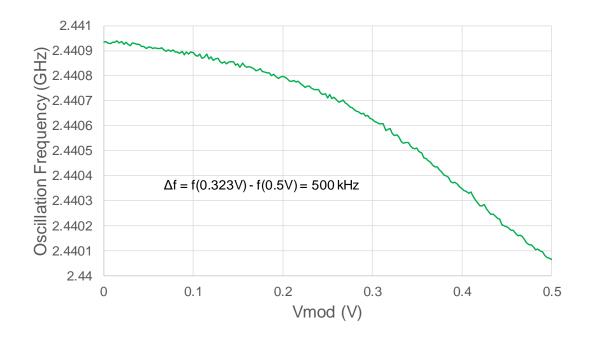

| 5.10 | Oscillation frequency vs. $V_{mod}$ at 2.45 GHz at PVT=000 and $V_{PLL} = 0.5 V$ .                                 | 111 |

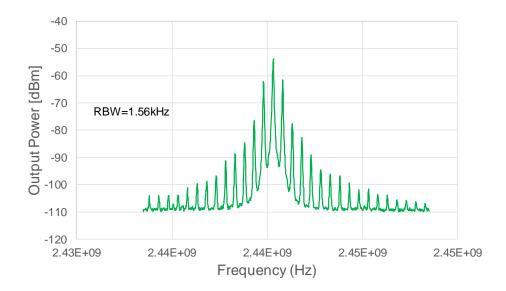

| 5.11 | MSK Output Spectrum with $V_{mod} = 500$ kHz sine wave @ $K_{mod} = 1$ MHz/V.                                      | 112 |

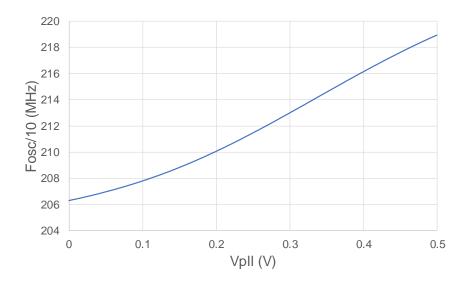

| 5.12 | Divide-by-10 Frequency vs. $V_{PLL}$ at slowest PVT setting [PVT=111]                                              | 113 |

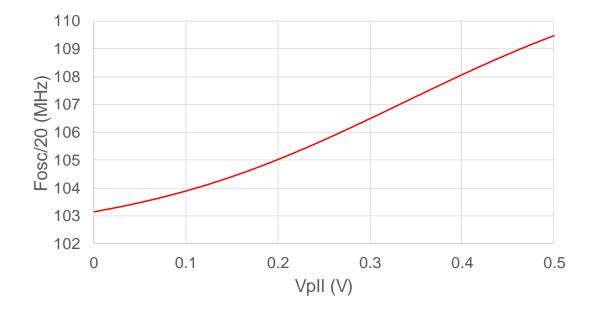

| 5.13 | Divide-by-20 Frequency vs. $V_{PLL}$ at slowest PVT setting [PVT=111]                                              | 114 |

| 5.14 | Phase-noise vs. $F_{OFFSET}$ for carrier and divided outputs where $F_{OSC} = 2.187 \text{ GHz}$ .                 | 115 |

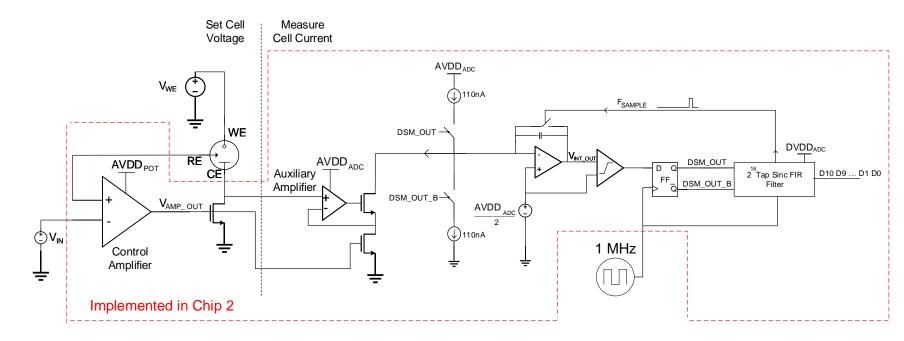

| 5.15 | Architecture of Chip 2                                                                                             | 118 |

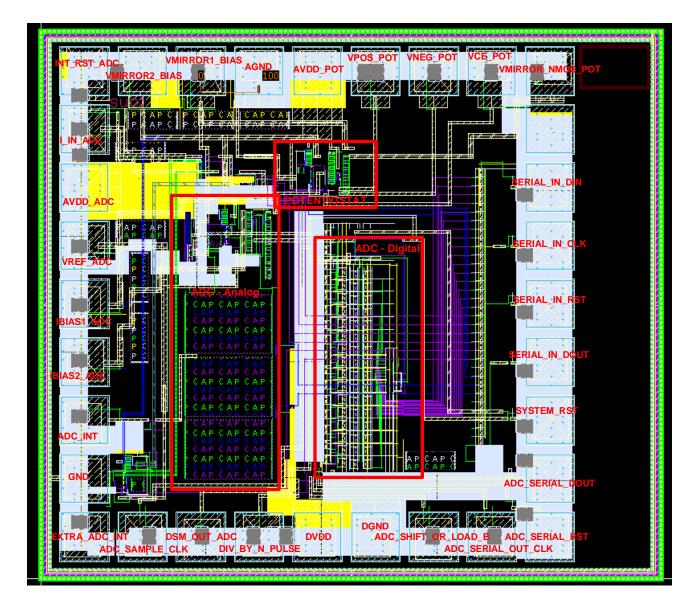

| 5.16 | Layout of Chip 2                                                                                                   | 120 |

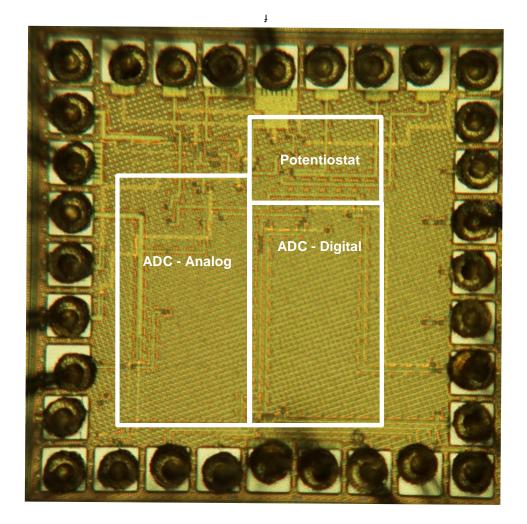

| 5.17 | Die-photo of Chip 2                                                                                                | 121 |

| 5.18 | Test PCB for Chip 2                                                                                                | 122 |

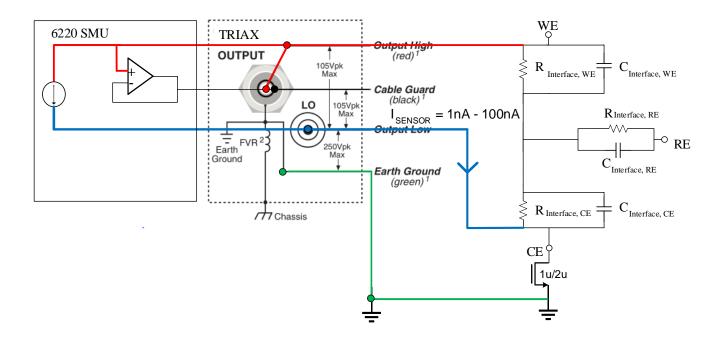

| 5.19 | SMU connection to the sensor interface on the PCB.                                                                 | 123 |

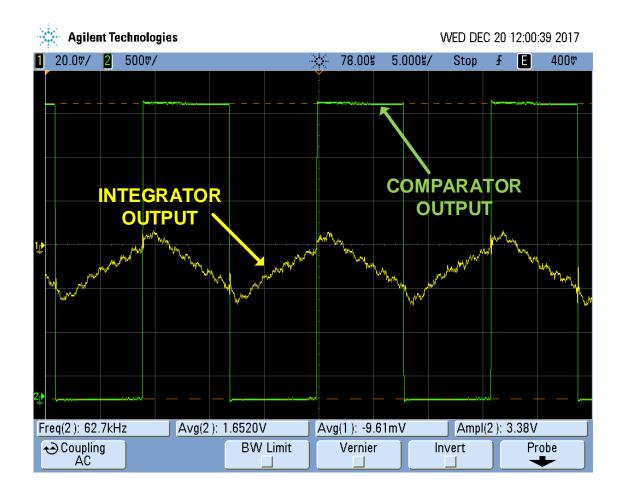

| 5.20 | Measured Integrator and Clocked Comparator Output with $I_{SENSOR} = 1$ nA.                                        | 124 |

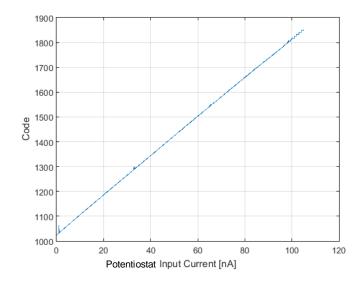

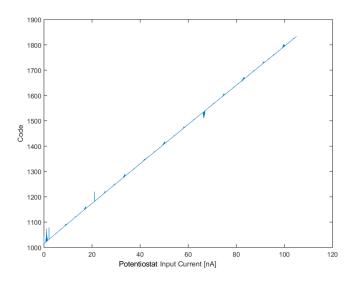

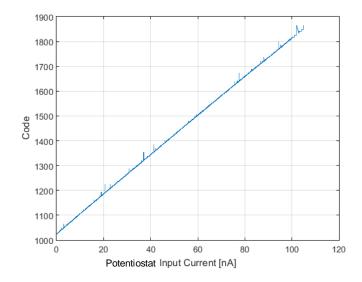

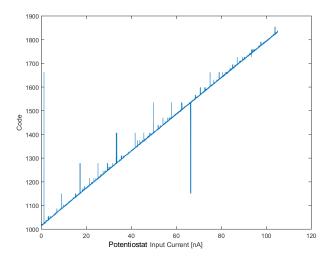

| 5.21 | ADC Code vs. $I_F$ for $T_{converter} = 65.54$ ms and $T_{converter} = 16.4$ ms                                    | 129 |

| 5.22 | ADC Code vs. $I_F$ Transient Output for $T_{converter} = 65.54$ ms and $T_{converter} = 16.4$ ms                   | 130 |

| 5.23 | DNL for $T_{converter} = 65.54$ ms and $T_{converter} = 16.4$ ms                          | 131 |

|------|-------------------------------------------------------------------------------------------|-----|

| 5.24 | INL for $T_{converter} = 65.54$ ms and $T_{converter} = 16.4$ ms                          | 132 |

| 5.25 | Noise Shaping FFT for I=100 nA, $T_{converter} = 65.54$ ms and $T_{converter} = 16.4$ ms. | 133 |

| 5.26 | Architecture of Chip 3                                                                    | 135 |

| 5.27 | Layout of Chip 3                                                                          | 137 |

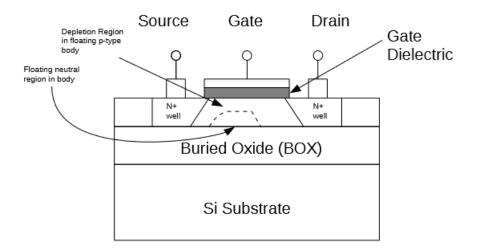

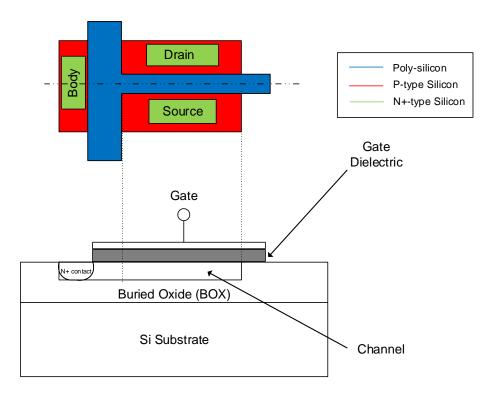

| A.1  | PD-SOI NMOS cross-section.                                                                | 147 |

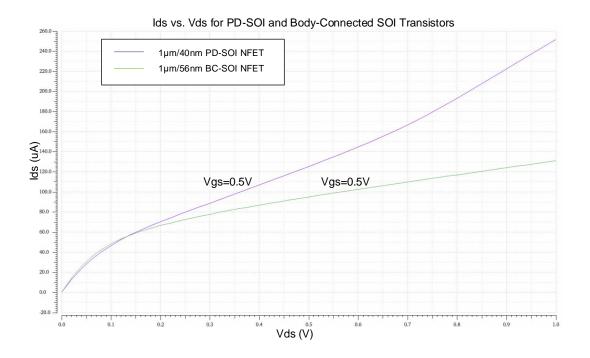

| A.2  | IV-curve showing the kink effect present in PD-SOI                                        | 148 |

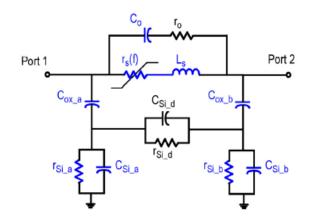

| A.3  | Single-section compact model for a spiral inductor [12]                                   | 149 |

| A.4  | NMOS BC-SOI layout and cross-section illustration                                         | 150 |

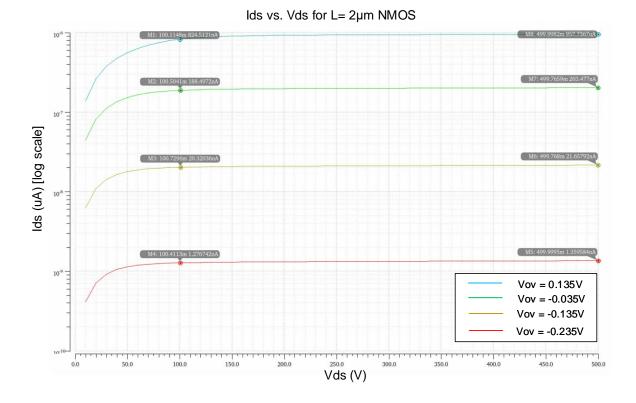

| A.5  | Simulation of minimum $V_{DS}$ for $V_{ov} < 0$                                           | 152 |

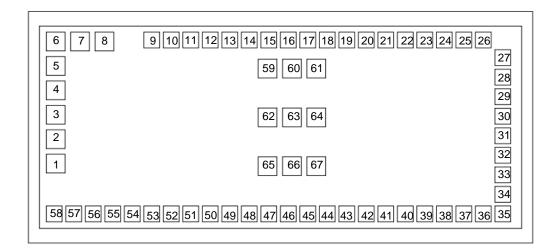

| B.1  | Bonding diagram for Chip 1 annotated with pin numbers.                                    | 155 |

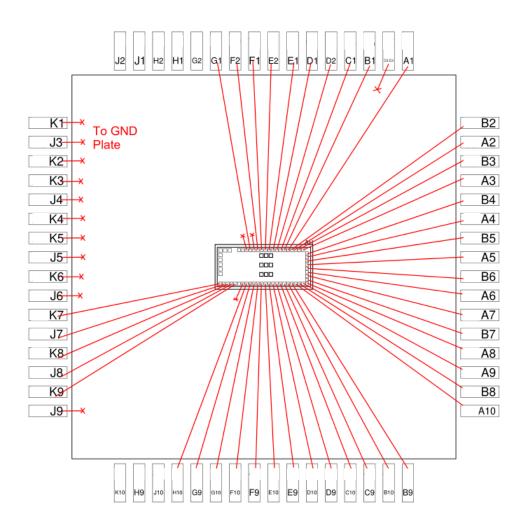

| B.2  | Bonding diagram for Chip 2 annotated with pin numbers.                                    | 158 |

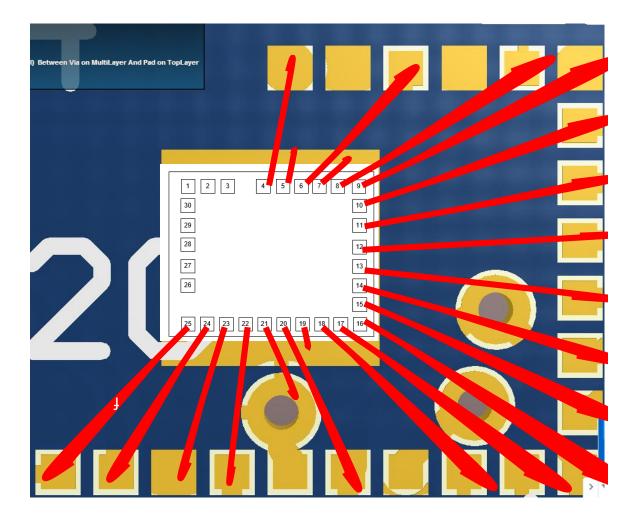

| B.3  | Chip diagram for Chip 3 annotated with pin numbers.                                       | 161 |

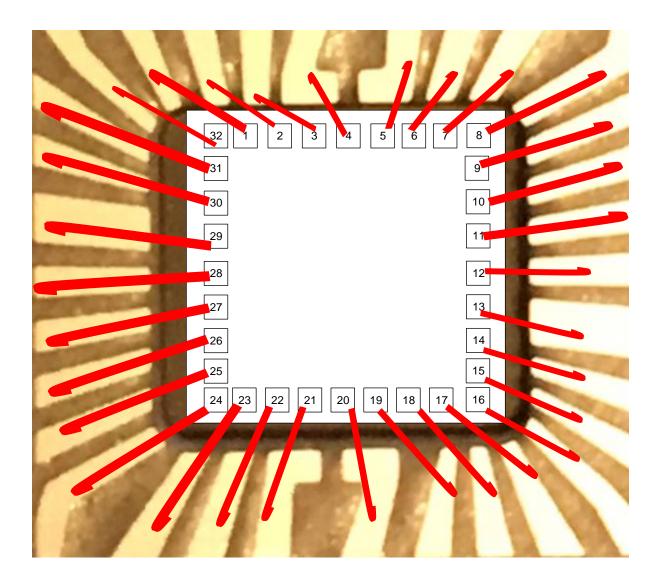

| B.4  | Bonding diagram for Chip 3                                                                | 162 |

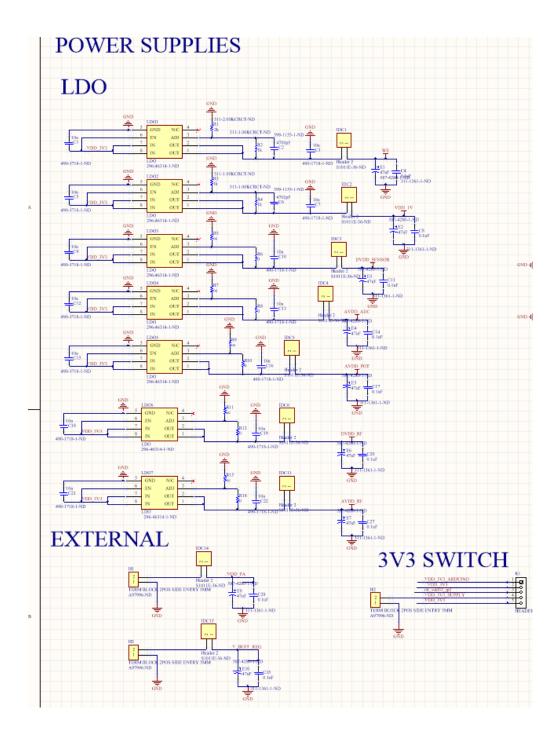

| F.1  | Regulation and Power into Chip 3 Test PCB.                                                | 189 |

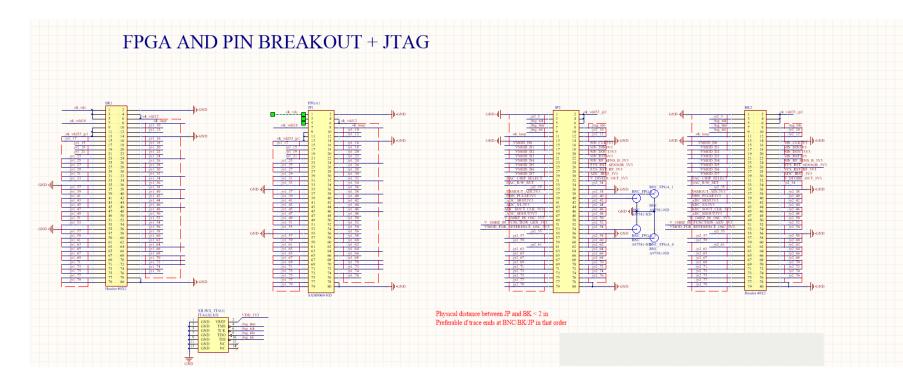

| F.2  | Opal Kelly FPGA input to Chip 3 Test PCB                                                  | 190 |

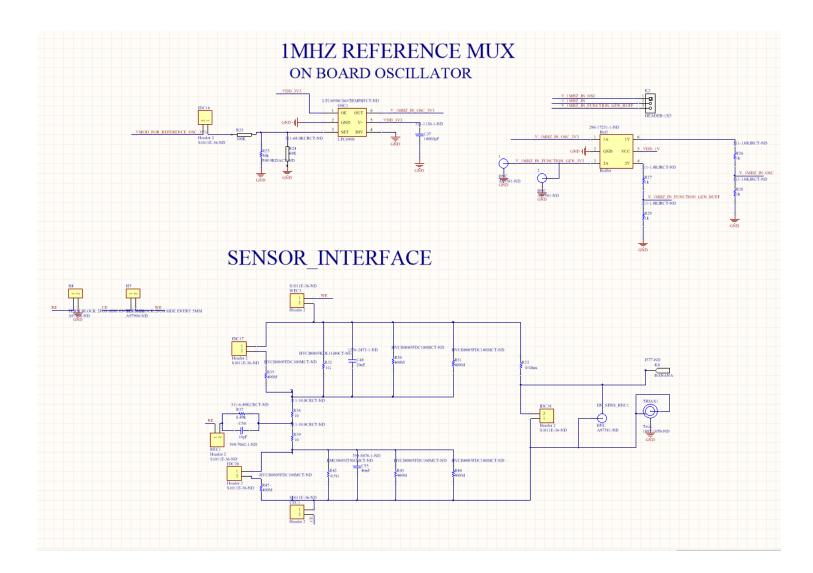

| F.3  | On-board reference oscillator and sensor electrical model used on Chip 3. $\ .$           | 191 |

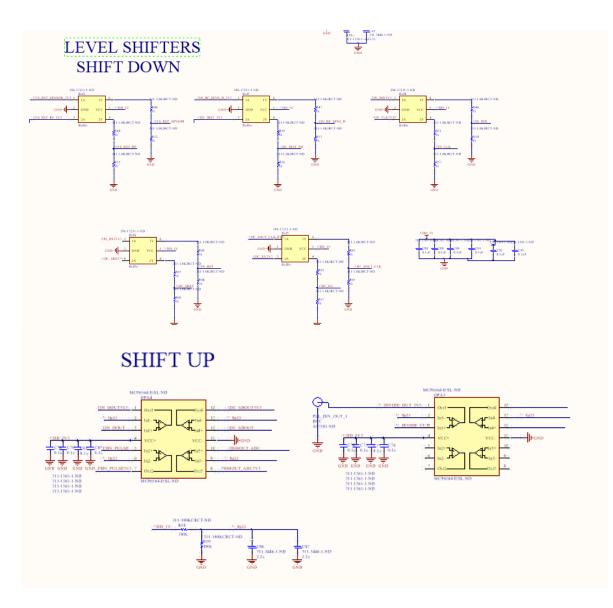

| F.4  | Level Shifters for input/output data to/from Chip 3                                       | 192 |

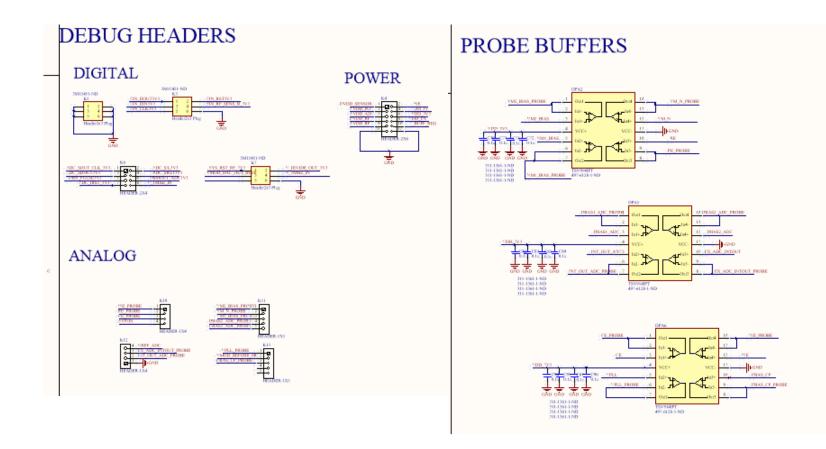

| F.5  | Debug inputs/outputs on Chip 3 Test PCB                                                   | 193 |

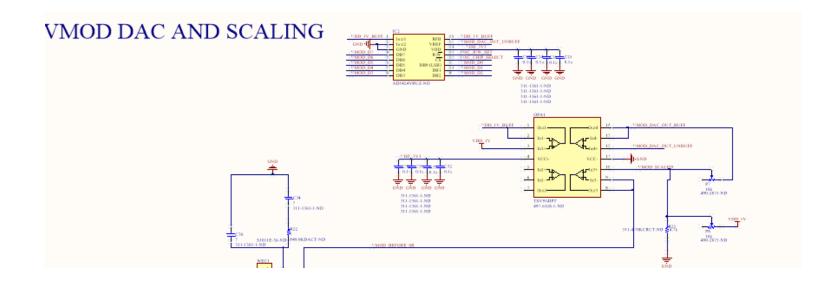

| F.6  | DAC used to drive Bluetooth modulator on Chip 3 from the FPGA                             | 194 |

| F.7  | Chip 3 with associated supply decoupling.                                                 | 195 |

## Chapter 1

## Introduction

## 1.1 Motivation

As obesity rates continue to rise, the risk of on-set diabetes has increased significantly over the last 40 years [13]. Management of the disease requires frequent monitoring of blood sugar levels to ensure that they do not increase to dangerous levels. Currently, the majority of patients manage their blood sugar through the use of blood glucose measurement meters. These systems are often inconvenient and invasive, which has led to interest in less invasive glucose monitoring systems [3].

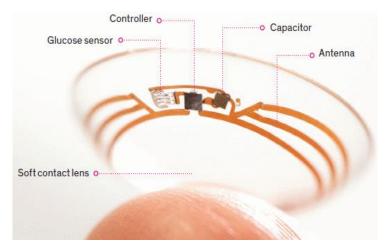

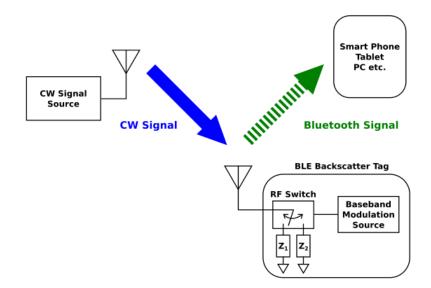

A potential solution is to monitor the glucose levels found in tears using a sensor embedded on a contact-lens. Glucose levels in tear glands are correlated to blood sugar levels, and thus can be used as a proxy when monitoring and controlling human insulin levels [14]. A prototype system has been developed by Verily Life Sciences and Novartis International (Figure 1.1). The system includes a loop antenna surrounding the periphery of the contact lens, a glucose sensor to measure glucose, a capacitor to store harvested energy, and a controller which contains the sensor and communication electronics. This system is an enhanced version of research conducted by Liao, et al., which included a potentiostat, sensor readout, energy harvester and wireless communication circuitry within the controller[2]. The patient uses an external reader in close proximity to power the system with radio-frequency (RF) energy. RF energy is converted into DC power which is then used to measure glucose levels, and transfer this information back to the reader using a radio frequency identification (RFID) device through, for example, backscattering techniques [2][15].

Figure 1.1: Smart contact-lens energy harvesting glucose monitoring system [3].

A major drawback to this scheme is that the reader must be continuously transmitting RF power for the sensor to backscatter data, thus requiring that the glucose monitoring system consume less power than it is able to harvest since these operations occur simultaneously. This scheme requires tight power consumption constraints to meet these requirements. Furthermore, the external reader must transmit +30 dBm of power to harvest an appreciable amount of power at the receiver [2]. This may lead to long-term health risks to the patient as ocular tissue could be damaged over time by the incident RF power required to activate the glucose monitoring system. Finally, the external reader proposed requires patients to carry an extra device as the RFID technology used by the glucose monitoring system is not compatible with mobile phones. Mobile phones typically implement near-field communication (NFC) as their RFID technology, which operates at 13.56 MHz. However, the system in [2] operates at 1.8 GHz, thus requiring a separate reader device.

## 1.2 Scope

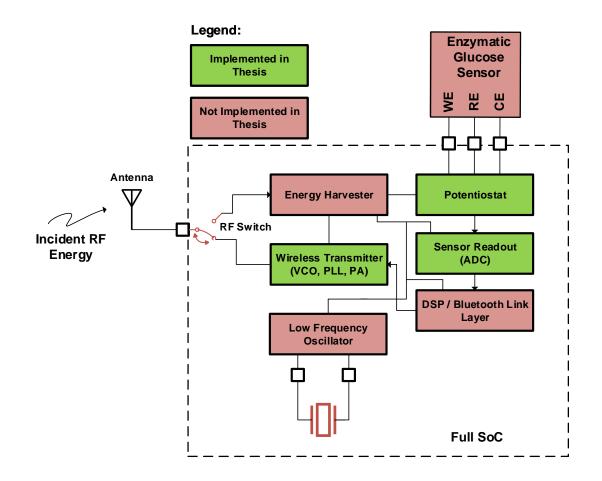

In order to address the above shortcomings, this thesis proposes a new energy harvesting wireless glucose sensor based on the Bluetooth<sup>TM</sup> standard. Bluetooth implementation allows the patient to use their smartphone to power the system, which encourages widespread adoption of the technology. Furthermore, the system can now harvest energy and then transmit data, rather than doing both simultaneously. This allows the smartphone to transmit less energy over a longer period, addressing the potential safety concerns mentioned previously. However, traditional Bluetooth implementations are infeasible for a glucose monitoring system as they consume more than 1 mW [16]. Thus, the goal of this research is to design some of the ultra-low-power blocks required to enable this application, as shown in Figure 1.2. To reduce the scope of this thesis, certain subsystems have not been implemented.

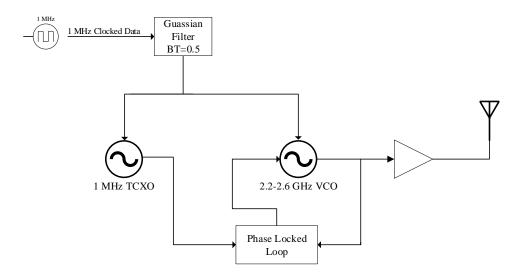

Figure 1.2: Overview of the proposed glucose monitoring system.

The system requires an antenna designed for 2.4-GHz ISM-band operation residing on the outer rim of the contact lens. This would receive incoming RF energy and direct it through an RF switch to the energy harvester subsystem. This system is effectively a rectifier, converting RF energy into DC energy to be used by the remainder of the electronics. Furthermore, an enzymatic glucose sensor, which has been constructed with specific materials and enzymes, is placed on the contact lens to act as a reaction site to sense the glucose levels in the basal tear fluid coating the eye. This sensor is controlled by a potentiostat which acts as voltage source to sustain the glucose reaction, as well as sink the signal current produced by the sensor. The current is then digitized using sensor readout circuitry. The digital subsystem obtains the sensor data and creates a Bluetooth packet in order to transmit the sensor data to the smartphone. This packet is then sent via the wireless transmitter and antenna to the smartphone. The low-frequency oscillator is a stable reference clock for the entire system.

The focus of this thesis is the design and characterization of the wireless transmitter, potentiostat, and sensor readout circuitry. First, a two-point in-loop modulation topology is utilized to reduce the power consumption of the Bluetooth transmitter shown in Figure 1.2. This approach is attractive as it reduces power consumption while reducing channel frequency drift. Second, a low-supply-voltage current-mirror-based potentiostat architecture is employed. Finally, low-supply-voltage sensor readout circuitry is implemented using a first-order, continuous-time incremental analog-to-digital converter (IADC).

## **1.3** Design Challenges and Objectives

In this section, the challenges associated with building a glucose monitoring system are described and design specifications are derived.

### **1.3.1** Bluetooth Compliance

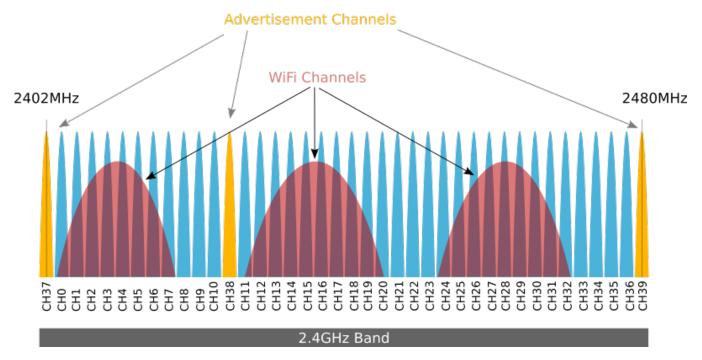

For this application, a subset of the Bluetooth Low Energy (BLE) protocol is implemented to reduce the complexity and power consumption of the transmitter. The BLE protocol operates in the 2.4 GHz ISM band. BLE transmits at 1 Mbit/s using a Gaussian frequency shift keying (GFSK) signal with a modulation index of 0.5. A frequency hopping transceiver is implemented in the standard, which operates in two modes: advertising mode and connected mode [1]. In advertising mode, only three frequency channels are used by the system, as illustrated in Figure 1.3.

For the contact lens system, only glucose concentration must be transmitted. Therefore, an advertising-only transmitter is implemented to reduce power consumption and system complexity. The protocol chosen changes the system requirements, and indirectly the power and energy consumption of the transmitter.

Table 1.1 lists relevant system-level specifications imposed by the BLE standard, which must be satisfied. However, meeting these specifications while significantly reducing the

Figure 1.3: BLE Frequency Spectrum [4]

power consumption is challenging, because power is traded-off to meet various performance parameters.

| Specification               | Minimum       | Maximum                       |  |

|-----------------------------|---------------|-------------------------------|--|

| RF Output Power $P_{out}$   | -20 dBm @ the | +10 dBm @ the                 |  |

|                             | antenna       | antenna                       |  |

| Channel Frequency Range     | 2402 MHz      | 2480 MHz                      |  |

| Modulation Frequency Range  | -250 kHz      | +250  kHz                     |  |

| Adjacent Spur @ 2MHz offset |               | -20 dBm                       |  |

| Adjacent Spur @ 3MHz offset |               | -30 dBm                       |  |

| Frequency drift             |               | $\pm$ 50 kHz                  |  |

| Drift rate                  |               | $400 \text{ Hz}/\mu \text{s}$ |  |

Table 1.1: BLE Transmitter Requirements [1]

### 1.3.2 System Energy Budget

Many of the overall system requirements may be determined from the energy available to the system. The contact lens system requires that energy must be harvested from 2.4 GHz ISM band energy such as Bluethooth and/or WiFi. To calculate the received power many assumptions need to be made. For example, the input power  $P_{TX}$  is assumed to be solely harvested from a smartphone's Bluetooth transmitter. Thus,  $P_{TX}$  is assumed to be 10 dBm. However, the system could instead/in addition harvest energy from WiFi, which emits a much higher output power of 21 dBm. However, this thesis uses a stricter power budget to target more aggressive power savings on the smartphone. The gain of the transmitter antenna  $G_{TX}$  is assumed to be 1.76 dBi, which is standard for omni-directional smartphone antennas. The gain of the loop antenna  $G_{RX}$  was simulated using Ansys High Frequency Structure Simulator (HFSS) with a 5 mm radius, 0.5 mm trace width and 5  $\mu$ m thickness, as was used in [2]. An additional loss of 18.5 dB is added to the receiver gain to account for dielectric losses attributed to the eye. The smartphone is assumed to be transmitting at a distance of 5 cm from the glucose sensor, which implies a path loss PLof 14 dB. Combining these terms using Friis' equation, one can find:

$$P_{RX} [dBm] = P_{TX} [dBm] + G_{TX} [dB] + PL [dB] + G_{RX} [dB]$$

= 10 dBm + 1.76 dB - 14 dB + (-4.3 - 18.5) dB

= -25.04 dBm

= 3.133 \muW. (1.1)

The expected received power is calculated in eq. 1.1 where the maximum transmit power is 10 dBm at 2.4 GHz (as per Bluetooth specification in Table 1.1) at a distance of 5 cm from the contact lens. Assuming an RF to DC conversion efficiency  $\eta_{RFtoDC}$  of 0.5,  $P_{DC}$  is found to be 1.566  $\mu$ W. The energy harvested ( $E_{Harvest}$ ) is dependent on the time given to harvest enough energy for the system ( $T_{Harvest}$ ) as well as the DC power harvested, and is given by

$$E_{Harvest} = P_{DC}T_{Harvest}.$$

(1.2)

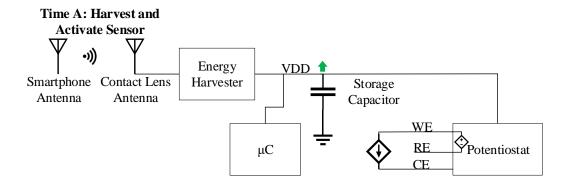

To create a power budget, the activation time for each step of the system is crucial.

•  $T_{MEMSosc}$ . This is the amount of time the MEMS oscillator is enabled. In this case, it must be enabled from the beginning, since it acts as the clock for the rest of the system.

- $T_{Reaction}$ . This is the amount of time necessary for the glucose reaction to occur, which is approximately 20 s.

- $T_{TX}$ . This is the amount of time the TX is enabled. Using an advertising-only based BLE protocol, this time can be reduced to approximately 1ms (19bytes×8bits×3channels / 1 Mbps+500  $\mu$ s for overhead) [1]. This is sufficient due to the fact that the amount of data being sensed is trivial.

- $T_{ADC}$ . This is the amount of time the sensor readout ADC is active, which is estimated to be 200 ms based on 3 samples with an estimated worst case conversion time of 65.5 ms.

- $T_{Digital}$ . This is the amount of time the digital logic is active. This is estimated to be 210 ms, assuming a worst case of 10000 clock cycles at 1 MHz necessary for the system.

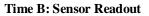

Figure 1.4 details the timing of the system. To make the application viable, the time spent making a measurement needs to be as small as possible. The following equations related Time A (time to harvest energy and activate sensor), B (time to read out the sensor), and C (time to transmit sensor data) to the timing variables above:

$$T_{A} = T_{Harvest} = T_{Reaction} + 5s$$

$$T_{B} = T_{ADC} + T_{DIGITAL}$$

$$T_{C} = T_{TX}$$

$$T_{MEMSosc} = T_{A} + T_{B} + T_{C}$$

(1.3)

Given these activation times, the overall energy consumption can be found as:

$$E_{System} = P_{MEMSosc}T_{MEMSosc} + P_{Potentiostat}T_{Reaction} + P_{ADC}T_{ADC} + P_{TX}T_{TX} + P_{Digital}T_{Digital}.$$

(1.4)

Therefore, reasonable power targets were pursued as detailed in Table 1.2. It is important to note that there are many assumptions implicit in these estimates. For example, it is assumed that Friis' equation holds when calculating input power. However, the system is not completely within the far-field at 5 cm distance. Furthermore, power consumption of the power distribution network is ignored, which would tighten the total power budget further.

| Energy Harvested | Power Generated $[\mu W]$ | Time Active [s]  | Energy $[\mu J]$ |

|------------------|---------------------------|------------------|------------------|

| Total            | 1.566                     | 25               | 39.2             |

| Energy Consumed  | Power Target $[\mu W]$    | Time Active [s]  | Energy $[\mu J]$ |

| MEMS Oscillator  | 1                         | 25.21            | 25.21            |

| Potentiostat     | 0.3                       | 20               | 6                |

| Sensor Readout   | 6                         | $200 \mathrm{m}$ | 1.2              |

| Digital          | 10                        | 211 m            | 2.11             |

| Bluetooth TX     | 250                       | 1 m              | 0.25             |

| Total            | -                         | 25.21            | 34.77            |

Table 1.2: System Power and Energy Budget

(a) Smartphone powering the device with RF energy while potentiostat activates sensor.

(c) RF Modulator transmits sensor data to the smartphone.

Figure 1.4: System timing overview

#### **1.3.3** Glucose Sensor Specifications

The key principle behind an electrochemical glucose sensor is a reduction-oxidation (redox) reaction that releases a number of electrons in proportion to the concentration of the reactants. Glucose sensors function by converting glucose into gluconic acid (gluconolactone). This reaction is catalyzed with immobilized glucose oxidase (GOD). A biproduct of this reaction, hydrogen peroxide  $(H_2O_2)$ , is then oxidized, and the free electrons are sensed in the reaction as shown below:

$$\begin{array}{l} D\text{-}glucose + O_2 \xrightarrow{GOD} H_2O_2 + D\text{-}gluconolactone \\ H_2O_2 \rightarrow 2H^+ + O_2 + 2e^-. \end{array}$$

(1.5)

When  $H_2O_2$  is oxidized, electrons flow in the external circuit. The amount of current flowing is proportional to the glucose concentration [9].

The sensor requirements derive from the physical characteristics of the sensor. Assuming a sensor geometry similar to [2], 2 nA-40 nA of current is to be sensed, which corresponds to a 0.05 mM-1 mM glucose concentration. The system is designed to target 0.1 nA resolution for input currents in the 1 nA-100 nA range, while applying a 0.4 V bias to the sensor to facilitate the reaction. This corresponds to 10-bit ADC resolution. These specifications must be satisfied while also meeting the corresponding block-level power requirements.

### 1.3.4 Low-Voltage, Low-Power Design

To meet the strict power budget detailed in Table 1.2, a reduced supply voltage  $V_{dd}$  is employed. The technology used in this thesis is a 45nm CMOS RF silicon-on-insulator SOI technology (45RFSOI) offered by Global Foundries [17]. The 45RFSOI process is an offshoot of a digital 45nm process (12SOI) with higher resistivity substrates and thicker top metals to improve performance of RF passives. The nominal supply voltage in this technology is  $V_{dd}$  at 1 V, however, the supply voltage used throughout the system is 0.5 V. For digital circuitry, the dynamic power consumption  $P_{dynamic}$  is given by [18]

$$P_{dynamic} = C V_{dd}^2 f_{clk} \alpha, \tag{1.6}$$

where  $\alpha$  is the activity factor, C is the capacitance switched by digital circuitry, and  $f_{clk}$  is the switching frequency of the circuitry. Ideally, the digital circuitry power consumption should be reduced by 75% as a result of the reduction in supply voltage from 1 V to 0.5 V which applies to the digital portion of the wireless transmitter and sensor readout circuitry. For analog circuitry, most circuits are designed with a specific bias current  $I_{dd}$  in mind, thus, the DC power  $P_{dc}$  saved when operated at 0.5 V supply should be ideally be 50% as seen from eq. 1.7:

$$P_{dc} = V_{dd} I_{dd}.$$

(1.7)

However, the reduction in supply voltage affects other parameters such as voltage swing, signal-to-noise ratio, frequency response, offset, etc. which may require a change in bias current. For example, transistors in the CMOS technology employed which have a threshold voltage  $V_{th}$  of 0.3 V to 0.4 V may be forced to operate in the subthreshold region ( $V_{gs} < V_{th}$ ), due to the limited headroom available. In subthreshold, the transistors are inherently slower (reduced bandwidth) due to their reduced transition frequency  $f_T$  as they either have low transconductance  $g_m$  or large width which implies higher parasitic capacitance (i.e., high gate-to-source capacitance  $C_{gs}$  and gate-to-drain capacitance  $C_{gd}$ ), as described in eq. 1.8

$$f_T = \frac{g_m}{2\pi (C_{gs} + C_{gd})}.$$

(1.8)

For example, in an LC-based voltage-controlled oscillator (VCO), high parasitic capacitance affects the frequency tuning range. Moreover, subthreshold operation causes the system to be more sensitive to process, voltage, and temperature variation; as the drainsource current  $(I_{DS})$  is now exponentially related to temperature through thermal voltage  $V_t$ , according to

$$I_{DS} = I_{D0} \frac{W}{L} e^{(V_{GS}/(nV_t))} (1 - e^{-V_{DS}/V_t}), \qquad (1.9)$$

where  $V_t$  is given by  $V_t = \frac{kT}{q}$ ,  $V_{GS}$  is the gate-to-source voltage,  $V_{DS}$  is the drain-to-source voltage,  $I_{D0}$  is a process constant which varies with temperature, n is a process constant greater than 1 and W/L is the width-to-length ratio (aspect ratio) of the transistor.

## **1.4** Thesis Organization

The following chapters are organized to guide the reader through the relevant background and contributions by this thesis. Chapter 2 describes the prior art and delves into topology selection for relevant subsystems including: Bluetooth protocol, integer-N phase-locked loops (PLL), switching power amplifiers, electrochemical sensors, and sensor readout circuitry. Chapter 3 details the design and simulation of the low-power wireless transmitter. Chapter 4 focuses on the design and simulation of the potentiostat and sensor readout circuitry. Chapter 5 presents chip-level implementations of the system, and compares the experimental data with simulation results. Lastly, Chapter 6 provides conclusions on the body of work completed and provides topics for future research.

## Chapter 2

## Literature Survey and Topology Overview

This chapter initially reviews similar low-energy RF sensor systems in the literature. Following this, the chapter moves on to describe the different aspects of the proposed system. Specifically, a brief overview of each subsystem is given to arrive at key topologies and specifications to be discussed in detail in the following chapters.

## 2.1 Review of Wireless Sensor Systems

Much research has been conducted on both system level designs as well as various circuit subsystems for wireless glucose sensors. A summary of the literature published on wireless glucose sensors (but not necessarily for contact lens-based applications) is presented in Table 2.1 and Table 2.2. In addition, previous work in this area by Liao et al. [2], Zhang et al. [5] and Xiao et al. [6] are described in detail.

|                                | JSSC '12 [2]                  | JSCC '13 [5]                             | TBCAS '09 [19]           | TCSII '15 [20]           | ISCAS '15 [21]                |

|--------------------------------|-------------------------------|------------------------------------------|--------------------------|--------------------------|-------------------------------|

|                                |                               | General                                  |                          |                          |                               |

| Application                    | Contact Lens Glucose Sensor   | Batteryless EEG Sensor                   | Blood Glucose Implant    | Low Voltage Potentiostat | Potentiostatic Glucose Sensor |

| V <sub>DD</sub>                | 1.2 V                         | 1.2 V AFE / 1 V LO / 0.5 V PA+DSP        | 1.8 V                    | 1 V                      | 1.8 V                         |

| Power Consumption              | $3 \ \mu W$                   | $19 \ \mu W$                             | $198 \ \mu W$            | $22 \ \mu W$             | $72 \ \mu W$                  |

|                                | Regulator+Bandgap: 1 $\mu$ W  | Supply Regulation: $3 \ \mu A$           | -                        | Potentiostat: 22 $\mu W$ | Potentiostat: 11.5 $\mu W$    |

|                                | Ring Oscillator: 600 nW       | TX: 0.14 $\mu$ A with heavy duty-cycling | -                        | -                        | -                             |

|                                | Potentiostat: 500 nW          | AFE: 4 $\mu$ A                           | -                        | -                        | TIA: 40.3 $\mu$               |

|                                | Digital: 400 nW               | Digital: 4.6 $\mu A$                     | -                        | -                        | -                             |

| Technology                     | 0.13 μm                       | $0.13 \ \mu \mathrm{m}$                  | $0.18 \ \mu m$           | $0.35 \ \mu m$           | 0.18 µm                       |

| Chip size/Core Size            | $0.36 \text{ mm}^2$           | $8.25 \text{ mm}^2$                      | $1.69 \text{ mm}^2$      | $0.13 \text{ mm}^2$      | $0.046 \text{ mm}^2$          |

|                                |                               | Energy Harvesting Perfor                 | mance                    |                          |                               |

| Energy Source                  | RF                            | Thermal+RF                               | Inductive                | -                        | -                             |

| Input Harvesting Power         | 30 dBm                        | $60 \ \mu W + 10 \ dBm \ kick$           | -                        | -                        | -                             |

| Rectifier+Regulator Efficiency | 20%                           | 35%                                      | -                        | -                        | -                             |

| Energy Storage Capacitor       | 500pF on-chip                 | off-chip                                 | 22nF off-chip            | -                        | -                             |

|                                |                               | RF Performance                           |                          |                          |                               |

| Modulation scheme              | FM-LSK                        | BFSK                                     | LSK                      | -                        | -                             |

| Carrier Frequency              | 1.8 GHz                       | 400 MHz                                  | 13.56 MHz                | -                        | -                             |

| Output Power                   | -                             | -18.5 dBm                                | -                        | -                        | -                             |

|                                |                               | Sensor Performance                       |                          |                          |                               |

| WE Material                    | Ti/Pd/Pt + GOD                | -                                        | Ti/Ni/Au                 | Pt/Ag                    | VACNF                         |

| CE Material                    | Ti/Pd/Pt + GOD                | -                                        | Ti/Ni/Au                 | Pt/Ag                    | Ag/AgCl                       |

| RE Material                    | Ti/Pd/Pt + GOD                | -                                        | Ag/AgCl                  | Pt/Ag                    | Ag/AgCl                       |

| WE-RE Cell Voltage             | 0.4 V                         | -                                        | 0.6 V                    | 0.7 V                    | 0.781 V                       |

| Glucose level                  | 0.05 mM - 2 mM                | -                                        | 0-40 mM                  | 2  mM- $22  mM$          | 0.5 mM - 25 mM                |

| Settling Time                  | 15 s                          | -                                        | $2 \min$                 | 100 s                    | -                             |

|                                |                               | Potentiostat Performa                    | nce                      |                          |                               |

| Architecture                   | Current-Mirror                | -                                        | Current-Mirror           | Current-Mirror           | TIA                           |

| Current Range                  | 50 pA - 150 nA                | -                                        | 1 nA - 1 µA              | 70 nA - 2.6 uA           | 100 nA-5 µA                   |

|                                |                               | Sensor Readout Perform                   | ance                     |                          |                               |

| Topology                       | I-to-F Differential Ring Osc. | -                                        | I-to-F Inverter Feedback | I-to-F Converter         | Ring VCO                      |

| Resolution                     | 400 Hz/mM                     | -                                        | -                        | 233 Hz/mM                | 100 kHz/mM                    |

## Table 2.1: Performance summary of energy harvesting wireless biosensors.

|                                | VLSIC '14 [22]                  | JBHI '15[6]                       | JBHI '16 [23]          | BioCAS '11[24]                  |

|--------------------------------|---------------------------------|-----------------------------------|------------------------|---------------------------------|

|                                |                                 | General                           |                        |                                 |

| Application                    | Implantable CGM                 | Implantable RFID CGM              | NFC Glucose Implant    | Wireless Glucose SoC for CGM    |

| V <sub>DD</sub>                | 1.2 V                           | 1.2  V AVDD/1.0  V DVDD           | 2.85 V AVDD/1.5 V DVDD | -                               |

| Power Consumption              | $6 \ \mu W$                     | $50 \ \mu W$                      | 760 $\mu W$            | $50.1 \ \mu W$                  |

|                                | -                               | RFID: 28 $\mu W$                  | ADC: 510 $\mu W$       | Regulator+Bandgap: 10.5 $\mu W$ |

|                                | -                               | ADC: 3 $\mu W$                    | RF: 250 $\mu W$        | Readout: 13.2 $\mu W$           |

|                                | -                               | Potentiostat: 4 $\mu W$           | -                      | Potentiostat: 3.6 $\mu W$       |

|                                | -                               | Digital: 15 $\mu W$               | -                      | ADC: 132 nW                     |

| Technology                     | $0.18 \ \mu \mathrm{m}$         | $0.13 \ \mu \mathrm{m}$           | $0.6 \ \mu \mathrm{m}$ | $0.13 \ \mu \mathrm{m}$         |

| Chip size/Core Size            | $1.96 \text{ mm}^2$             | $2.4 \text{ mm}^2$                | $10 \text{ mm}^2$      | 10                              |

|                                | Ene                             | ergy Harvesting Performance       |                        |                                 |

| Energy Source                  | Inductive                       | Inductive                         | Inductive              | Inductive                       |

| Input Harvesting Power         | 22  dBm@ 5  mm tissue+5  mm air | $20~\mathrm{dBm}~@~3~\mathrm{cm}$ | -                      | -                               |

| Rectifier+Regulator Efficiency | 60%                             | 45%                               | 72%                    | 35%                             |

| Energy Storage Capacitor       | 400 pF on-chip                  | on-chip                           | on-chip                | 1  nF                           |

|                                |                                 | RF Performance                    |                        |                                 |

| Modulation scheme              | LSK                             | LSK                               | LSK                    | LSK                             |

| Carrier Frequency              | 900 MHz                         | $13.56 \mathrm{~MHz}$             | 13.56 MHz              | 13.56 MHz                       |

| Output Power                   | -                               | -                                 | -                      | -                               |

|                                |                                 | Sensor Performance                |                        |                                 |

| WE Material                    | Pt                              | -                                 | -                      | -                               |

| CE Material                    | Pt                              | -                                 | -                      | -                               |

| RE Material                    | Ag/AgCl                         | -                                 | -                      | -                               |

| WE-RE Cell Voltage             | 0.4 V                           | 0.2 V                             | -                      | -                               |

| Glucose level                  | 0 - 20 mM                       | 0 -30 mM                          | -                      | -                               |

| Settling Time                  | -                               | -                                 | _                      | -                               |

|                                |                                 | Potentiostat Performance          |                        |                                 |

| Architecture                   | TIA                             | Current-Mirror                    | -                      | -                               |

| Current Range                  | 20 pA-500 nA                    | 0-20 nA                           | -                      | 10 fA - 100 pA                  |

|                                | Se                              | ensor Readout Performance         |                        |                                 |

| Topology                       | Dual-Slope ADC                  | Delta-Sigma ADC                   | Delta-Sigma ADC        | SAR ADC                         |

| Resolution                     | 7-bit                           | 10-bit                            | 11-bit                 | 8-bit                           |

## Table 2.2: Performance summary of energy harvesting wireless biosensors continued.

### 2.1.1 System by Liao et al.

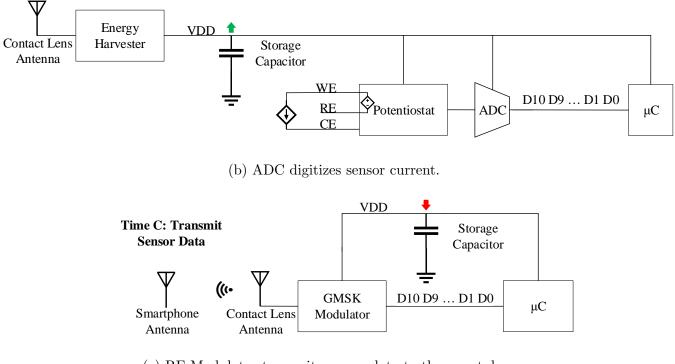

The aforementioned work by Liao, et al [2] is the only complete contact-lens-based wireless glucose sensor this author is aware of to date. The system block diagram is shown in Figure 2.1 and key specifications are summarized in Table 2.1.

Figure 2.1: System architecture of [2]

The 1 cm loop antenna is area limited by the contact lens itself. The system voltage is a rectified continuous-wave (CW) 1.8 GHz signal from an external device. This voltage is then regulated to 1.2 V for the rest of the system. Once the system receives regulated power, it measures current from the glucose sensor via a current-mirror based potentiostat. The sensor implemented includes two CE terminals; one which senses glucose current while the other node only senses background noise current. The sensor and reference currents are converted to frequency directly through a current-starved ring oscillator. This choice was made to save power associated with an explicit ADC. Since the wireless transmitter is based on a backscattering scheme (modulating the reflection coefficient seen by the external device) via pulse width modulation to an NMOS switch, frequency data from the ring oscillator is sufficient to transmit sensor information. The entire system consumes 3  $\mu$ W. As mentioned previously, one key drawback is the use of an arbitrary wireless protocol and frequency, which is not inter-operable with existing mobile phones. This paper provides the basis for many of the assumptions made in later chapters regarding the key specifications and assumptions.

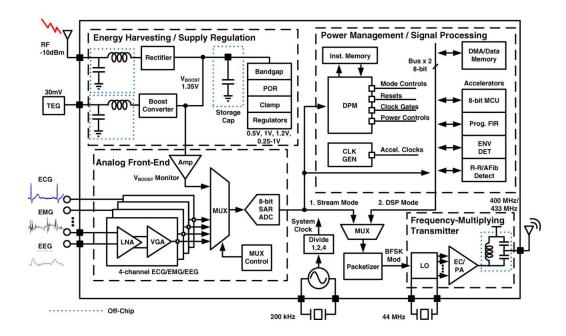

### 2.1.2 System by Zhang et al.

Given the limited literature on contact lens-based wireless glucose sensors, we compare the system with other implemented systems. For example, a 19  $\mu$ W energy harvesting EEG wireless sensor is implemented in [5] (block diagram shown in Figure 2.2).

Figure 2.2: System architecture of [5]

The system primarily harvests thermal energy using an RF pulse as an initial startup kick to the thermal harvesting boost converter. The RF pulse is necessary due to the low voltages the thermal harvester is able to generate given the temperature delta and physical area of the harvester. Thus the RF pulse is used to kick-start the regulator boost circuitry. The RF transmitter is implemented using an injection locked 9-stage ring-oscillator at 1/9th the output frequency of 402/433 MHz. The modulation scheme implemented was BFSK, which is achieved by direct modulation of the reference crystal oscillator. Frequency

multiplication is achieved via a phase interpolated switching PA. this reduces the oscillator power consumption as it oscillates at a lower frequency. The RF subsystem burns 160  $\mu$ W of power when active. The transmitter is heavily duty-cycled in order to drive down the power of the overall system.

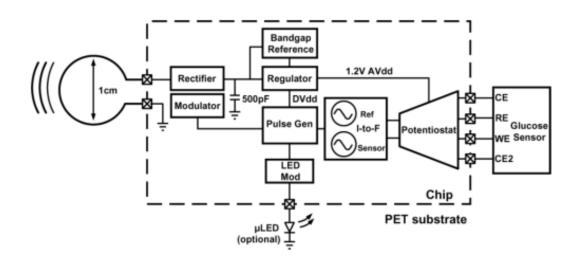

#### 2.1.3 System by Xiao et al.

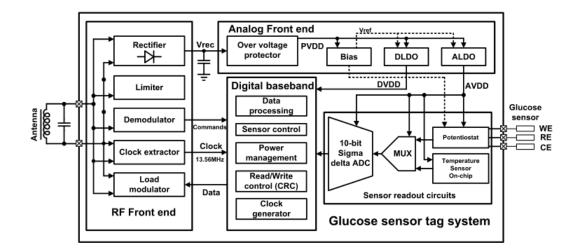

The topology in [6] is particularly interesting, as the sensor subsystem is similar to the circuits implemented in this thesis. The system is a glucose sensor tag to be implanted in the arm of the diabetic patient in order to sense blood glucose directly. Figure 2.3 shows the system overview:

Figure 2.3: System overview of [6]

The system includes an off-chip resonant tank which is used for energy harvesting as well as communication. The system uses near-field inductive charging which couples energy from a -3.5 dBm source at a distance of 5 mm from the implant, through arm tissue. This RF energy is rectified and regulated to 1.2 V/1 V to power the rest of the system. The RF transmission is done through load-shift keying (LSK) whereby the system does not generate RF energy, but transmits data by modulating the antenna impedance in the presence of

an RF signal transmitted by an external device. The sensor subsystem uses a potentiostat to measure glucose current from an external glucose sensor. This current is mirrored and read-out by a 10-bit incremental delta-sigma ADC. The overall DC power consumption of the system is 50  $\mu$ W.

Many other complete systems compared are shown in Table 2.1 and Table 2.2. In summary, they all attempt to harvest energy using back-scattering RFID schemes, mainly at 13.56 MHz. While 13.56 MHz is available on mobile phones as near-field communication (NFC), the required antenna would need to be much larger than the space available on the contact lens.

## 2.2 Review of Wireless Sensor System Components

### 2.2.1 Review of Bluetooth Transmitters

As mentioned earlier, this thesis proposes an energy harvesting system that uses Bluetooth Low Energy (BLE) at 2.4 GHz. Bluetooth is available in all modern mobile phones, and its operating frequency is high enough for an electrically-small antenna to fit on a contact lens.

#### **Bluetooth Protocol**

To use Bluetooth in an energy harvesting system, it is imperative that only the necessary parts of the protocol are implemented. This would to reduce circuit complexity and communication time to ultimately reduce the energy consumption. As mentioned previously, an advertising-mode-only approach was taken. This mode allows the system to only require a transmitter rather than a transceiver, saving power. Furthermore, advertising mode does not require the transmitter to use the 37 data channels, and it also does not require collision avoidance frequency hopping, reducing the digital system complexity.

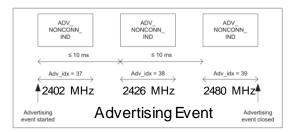

Advertising mode can be used to send many different message types. For example, one message type allows the reciever to respond without switching from advertising mode to connected mode. The non-connectable non-scannable advertising packet is used in this system. This broadcasts data to any device listening to any of the advertiser channels. The packet is sent on all three advertising channels sequentially as shown in Figure 2.4. The packet can be 14-47 bytes long, depending on the data length. Assuming 47 bytes are transferred, the transfer time per advertising channel is 376  $\mu$ s. Accounting for overhead,

this implies a complete advertising event can be completed in approximately 2ms. To read this information, the reader (mobile phone) would be scanning for any packets on one of the advertising channels; the choice of channel is at the reader's discretion as the same information would be transmitted on all three advertising channels.

| LSB<br>Preamble | ADV_NON    | Payload            |                          | MSB<br>CRC |

|-----------------|------------|--------------------|--------------------------|------------|

| (1 or 2 octets) | (4 octets) | AdvA<br>(6 octets) | AdvData<br>(0-31 octets) | (3 octets) |

(a) Non-connectable, non-scannable, undirected advertising packet

(b) Advertising event timing consisting of a packet sent on all three advertising channels

(c) Timing in-between advertising events

Figure 2.4: Non-connectable non-scannable advertising event structure[1]

However, one drawback is that, in order to send subsequent advertising events, the transmitter would be required to wait 20 ms - 30 ms between events. This idle time is quite costly to the energy budget, and although the transmitter could be power-gated within this time frame, the system implemented in this work opts to only send one advertising event to save energy.

#### Low-Power Transmitter Topologies

Bluetooth employs Gaussian minimum shift keying (GMSK), which is equivalent to Gaussian filtered frequency shift-keying (GFSK) with a modulation index m of 0.5. The binary data is filtered by a Gaussian filter, which then modulates the carrier frequency by half the bit-rate. The output signal  $x_{GMSK}(t)$  can be expressed as

$$x_{GMSK}(t) = A\cos(w_c t + K_{VCO} \int x_{BB} * h(t)dt), \qquad (2.1)$$

$$x_{GMSK}(t) = A\cos(w_c t)\cos(\theta) - A\sin(w_c t)\sin(\theta),$$

where :  $\theta = K_{VCO} \int x_{BB} * h(t)dt,$  (2.2)

where  $K_{VCO}$  corresponds to the voltage to frequency gain of the voltage controlled oscillator (VCO), and  $x_{BB}(t) * h(t)$  refers to the gaussian filtered baseband data signal.

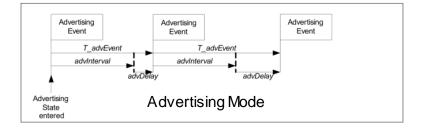

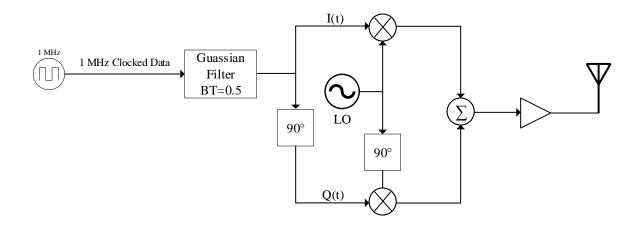

There are two methods used to implement GMSK modulation. The most direct approach is to modulate a VCO directly with Gaussian shaped data. However, given that VCOs are prone to frequency drift over time, two-point modulation (shown in Figure 2.5) is used to implement eq. 2.1. In this scheme, the VCO is part of a frequency synthesizer circuit. The synthesizer uses 1-MHz reference clock to set the carrier to the selected channel (i.e., 2402/2426/2480 MHz). The signal data modulates both the reference and the RF VCO simultaneously to output the GMSK data. Both oscillators are modulated simultaneously such that the loop does not distort the incoming data stream.

The second is shown in Figure 2.6. Here, data is split into in-phase and quadrature (IQ) paths, and recombined after mixing with in-phase and quadrature of the carriers respectively. This scheme implements eq. 2.2.

There are clear tradeoffs between the two methods. The two-point modulation is simpler to implement, as it requires fewer circuit blocks and, consequently, requires less power. However, a disadvantage is that the modulation index depends on the gain of the VCO, which varies with circuit processing and is therefore difficult to control. In addition, the

Figure 2.5: Two-point GMSK Transmitter Architecture

Figure 2.6: I/Q based GMSK Transmitter Architecture

baseband data amplitude must be controlled to ensure that the correct frequency spacing is achieved [25]. On the other hand, the I/Q method allows for precision in setting the modulation index if accurate phase shifts are applied to the LO and input data. This precision comes at the cost of complexity and power, as the LO frequency needs to be controlled precisely and quadrature phases are required (which implies a PLL and LO driver circuitry). The mixer blocks also add power consumption depending on their implementation. Since power consumption is the most important aspect of the glucose monitoring system, the two-point scheme is chosen.

#### **Review of Integer-N Phase-Locked Loops**

Two-point modulation for Bluetooth in advertising mode requires a PLL that is able to select three advertising channels (2402/2426/2480 MHz). A PLL is a feedback control system that reduces the phase error between a reference signal and a fedback signal to a value as close to zero as possible. This is beneficial for frequency synthesis due to:

$$\phi_{error} = \phi_{ref} - \phi_{feed}$$

$$\phi_{error} \rightarrow \epsilon$$

$$f_{error} = \frac{\mathrm{d}\phi_{error}}{\mathrm{d}t}$$

$$f_{error} = 0$$

(2.3)

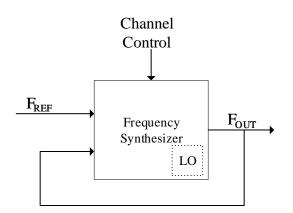

where  $\phi_{error}$  represents the dynamic phase error due to a change in the input phase  $\phi_{ref}$  to the fedback phase  $\phi_{feed}$  and  $f_{error}$  corresponds to frequency error associated with  $\phi_{error}$ . Furthermore, the PLL must be able to switch between various frequency channels accurately. The conceptual system is shown in Figure 2.7.

Generally, the reference oscillator is a low-frequency high spectral purity signal that is fixed at one frequency. Therefore, to accurately generate an RF carrier at a higher frequency than the reference input, the output frequency is divided before being compared at the input. If the divider value is represented by N, this implies that

$$F_{OUT} = NF_{REF},\tag{2.4}$$

where  $F_{OUT}$  represents the output frequency, and  $F_{REF}$  represents the reference frequency. There are two types of PLLs classified by how the divider value is set: integer-N PLLs and fractional-N PLLs. Fractional-N PLLs allow for higher reference frequencies while still being able to synthesize closely-spaced frequency channels by using fractional division ratios. This permits higher system bandwidth and thus faster settling time. However, the cost is added complexity, power consumption and increased spurious output. Integer-N PLLs are simpler and therefore are more power efficient. For this application, the PLL

Figure 2.7: Conceptual RF Synthesizer [7]

only needs to switch between three channels. Moreover, the speed of channel selection is not critical as compared to the overall power consumption. Hence, the integer-N architecture was chosen.

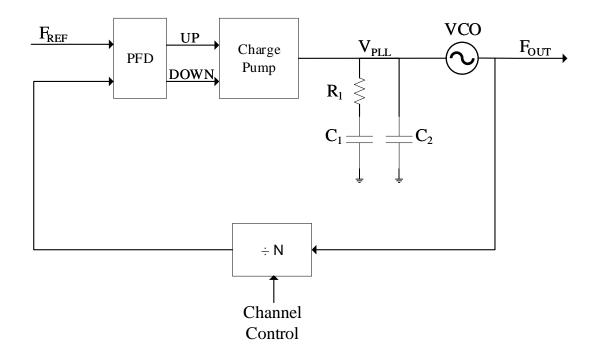

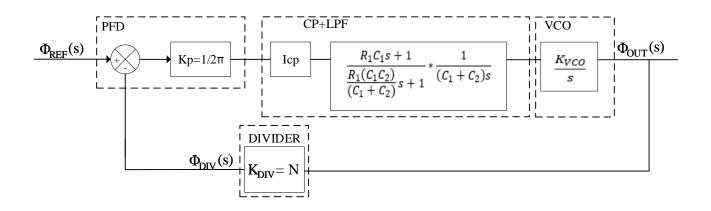

A PLL used to enable integer channel spacing is shown in Figure 2.8. In this architecture, the reference is compared to a divided output frequency with a phase-frequency detector (PFD). The PFD outputs pulses to the charge pump (CP) to either speed up or slow down the PLL. The charge pump will either raise or lower the control voltage based on these pulses, as it drives current to/from the passive network. This voltage change will increase/decrease the output frequency, which will be fed back to the input through the divider, completing the feedback system.

To analyze the feedback system, a continuous-time approximation of the discrete time system in the phase domain can be made that assumes that the loop bandwidth is approximately at most less than one-tenth, the reference frequency. Figure 2.9 shows that the system has two integrator poles, which is defined a type-2 PLL. The system is stable due to the zero in the open loop transfer function.

The major contributor to the power consumption of the PLL is the VCO. The power consumed by the VCO stems from two main metrics: the transconductance needed for the system to oscillate and the phase noise requirements of the oscillator. To meet these requirements, a CMOS cross-coupled LC VCO is chosen to reduce the supply voltage while still providing enough transconductance. This circuit can be seen in Figure 2.10.

Figure 2.8: Integer-N PLL [7]

Figure 2.9: A block diagram of the PLL in the frequency domain.

Figure 2.10: CMOS LC VCO-without tail current source [7].

From Barkhausen's stability criterion:

$$\begin{aligned} |\beta A| &= 1, \\ < \beta A = 2\pi n, n \in \mathbb{W}, \end{aligned}$$

$$(2.5)$$

where  $\beta A = 2g_m R_p$  is the loop gain of the feedback system, and  $R_p$  is the equivalent impedance shown by the LC-tank at resonance, which is generally set by the Q-factor of the inductance and is thus somewhat process specific. Therefore,  $g_m = \frac{1}{2R_p}$  in order to meet the oscillation criteria. This topology provides the lowest  $g_m$  required to oscillate, and thus was chosen so that less bias current is required, thereby reducing the power consumption.

To implement the PFD, a digital state machine was used so that the input reference and feedback signal can be non-linear, reducing the overall system power consumption. For the charge pump, a simple current mirror implementation with digital switches was used due to the reduced headroom available. Charge pumps suffer from mismatch due to channel length modulation. Thus, more advanced charge pumps implement error correction using feedback to match the current sources. These topologies were not implemented to save power. Furthermore, the reference spur specifications are relaxed for this application. Finally, the digital divider is designed using a swallow counter and a dual-modulus prescaler. Sequential logic was designed using dynamic logic circuits in order to reduce power consumption [7].

#### Switching-Mode Power Amplifiers

To transmit the sensor data to the antenna, a power amplifier circuit is required. Power amplifiers are designed to deliver RF power to the load while consuming as little DC power as possible. For this application, the transmitter is required to transmit > -20 dBm of power. Furthermore, the output waveform can be heavily distorted, as information is encoded in the frequency rather than the amplitude. These requirements lend themselves to switching-mode amplifiers.

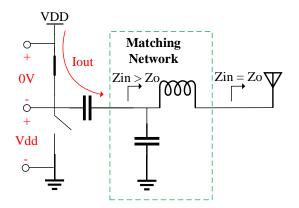

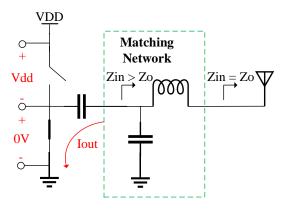

Class-D amplifiers are switching-mode amplifiers that can ideally realize close to 100% efficiency. An example switching amplifier is shown in Figure 2.11. In Class D, the switch either carries current  $I_{SW}(t)$ , or sustains a voltage drop  $V_{SW}(t)$ , but not both simultaneously. This implies that no power is consumed by the switches.

Typical power amplifier designs attempt to deliver the maximum power from the transistor to the load while being as efficient as possible. However, this design requires the transistor to output much less RF power (i.e., -20 dBm, or 10  $\mu$ W) while still being efficient. Since a Class-D amplifier essentially act as a voltage divider between  $R_{sw}$  and  $R_{Load}$ , the output power is set by their combined impedance. Thus, to output less power, either the load or switch impedance must increase. However, increasing the switch impedance will reduce the power efficiency, thus, a matching network is inserted to increase the impedance presented by the antenna. An L-section matching network that uses a shunt capacitor and series inductor was chosen specifically because the inductor can be absorbed by the antenna impedance itself with careful antenna design.

(a) High side switch enabled

(b) Low side switch enabled

Figure 2.11: Ideal Class-D PA

#### **Bluetooth Transmitter Prior Art**

Despite efforts to reduce the power consumption of the Bluetooth physical layer (PHY) with the introduction of BLE, the power consumption is generally far too high for energy harvesting applications. Table 2.3 summarizes recent BLE implementations in the literature.

|                                  | TMTT '13 [26]       | TCAS '18 [27]         | JSSC '16 [28]                        |

|----------------------------------|---------------------|-----------------------|--------------------------------------|

| V <sub>DD</sub>                  | 1 V                 | 1  V/3  V             | 0.5  V/1 V                           |

| Technology                       | $0.13~\mu{ m m}$    | 55  nm                | 28 nm                                |

| Power Consumption                | 5.9  mW             | $3.9 \mathrm{mW}$     | 5.8 mW                               |

| VCO                              | $0.4 \mathrm{mW}$   | $0.7 \mathrm{~mW}$    | $0.4 \mathrm{mW}$                    |

| Dividers                         | -                   | $0.5 \mathrm{~mW}$    | $0.2 \mathrm{~mW}$                   |

| PFD+CP                           | $0.27 \mathrm{~mW}$ | -                     | $0.6 \mathrm{~mW}$                   |

| PA                               | $5.3 \mathrm{mW}$   | $2.5 \mathrm{~mW}$    | 4.4  mW @ Pout=0 dBm                 |

| Chip size/Core Size              | $2.1 \text{ mm}^2$  | $0.53 \mathrm{~mm^2}$ | $0.65 \text{ mm}^2$                  |

| Osc. PN @ 1MHz (dBc/Hz)          | -110                | -119                  | -116                                 |

| Osc. FOM(dB) $^{1}$              | -                   | -                     | 188                                  |

| Osc. tuning range                | -                   | -                     | 2.05-2.55 GHz                        |

| PLL in-band PN (dBc/Hz) $^{2}$   | -80                 | -81                   | -92 @Fref=5 MHz / -101 @Fref=40 MHz  |

| Integrated PN (degree)           | -                   | -                     | 1.08 @Fref=5 MHz / 0.87 @Fref=40 MHz |

| PLL FOM (dB)                     | -                   | -                     | -238                                 |

| PLL settling time $(\mu s)$      | -                   | -                     | 15                                   |