# Hybrid Amorphous Selenium-CMOS Photon-Counting X-ray Imager

by

Abdallah El-Falou

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2018

© Abdallah El-Falou 2018

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Many medical imaging modalities, such as mammography and micro-computed tomography, utilize digital X-ray imagers to observe human anatomy. Direct digital X-ray imagers rely on a sensor layer (typically a photoconductor) to convert X-ray photons to electrical charge, which can then be collected by pixel readout circuits. Whereas traditional integration-mode X-ray imagers typically integrate charge for long durations to acquire image frames, X-ray photon-counting imagers (PCIs) resolve each incident photon as it arrives. This allows for equal energy-weighting of photons and multi-spectral image capture, both of which enhance contrast in images. Furthermore, PCIs also allow for higher dynamic range since count rates are not limited by integration well capacity. Many hybrid X-ray PCIs have been reported in the literature using photoconductors such as CdTe and HgI<sub>2</sub>. However, these photoconductors are expensive to fabricate, suffer from low yield over large areas, and have limited spatial resolution.

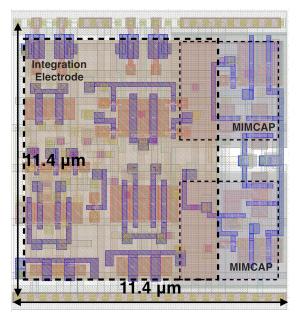

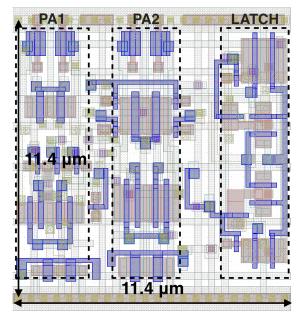

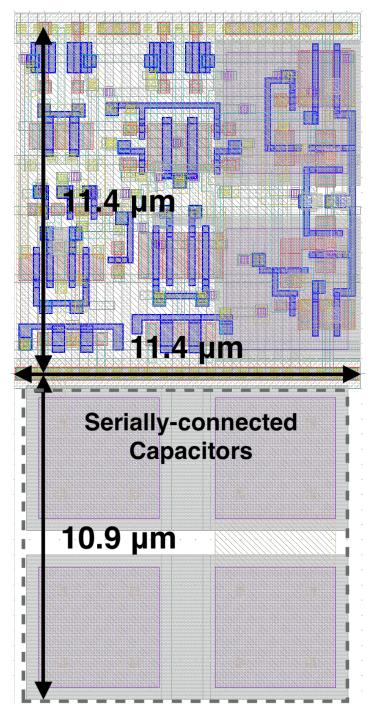

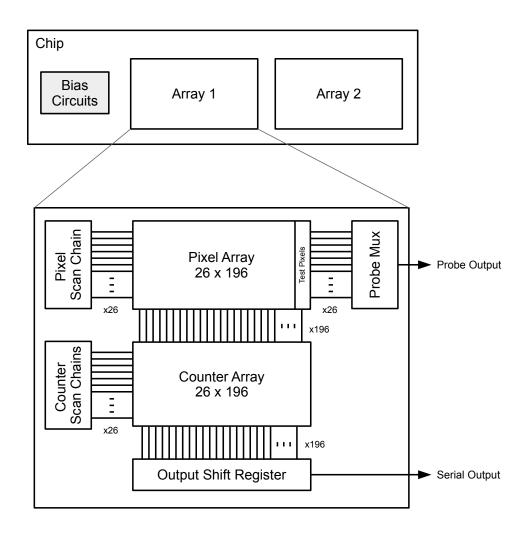

This thesis describes the design and characterization of the first hybrid X-ray amorphous selenium–CMOS PCI for mammography and micro-computed tomography. Amorphous-selenium (a-Se) can be thermally deposited over large areas, allowing for cheaper and scalable fabrication as well as higher spatial resolution. Two arrays of  $26 \times 196$  pixels are implemented in CMOS and interface directly to an a-Se sensor layer. Counter arrays neighbor the pixel arrays and have a one-to-one relationship with pixels, incrementing every time a photon is detected. Novel readout circuits allow for ultra high-resolution pixels, each occupying only  $11.44 \times 11.44 \text{ µm}^2$ . Finally, the design of a custom PCB and FPGA system for characterizing the electronic performance of the PCI is described. The measured input-referred noise and threshold spread of the PCI are  $41 \text{ e}_{rms}^{-}$  and  $107 \text{ e}_{rms}^{-}$ , respectively, when operating the imager as a row scanner. This will enable an energy resolution of 5.7 keV, suitable for the proposed applications. Further analysis was done to identify methods of reducing threshold spread as well. Finally, the concluding chapter summarizes this work, compares its performance to other PCIs in the literature, and identifies future work to improve its performance.

#### Acknowledgements

I would like to thank all the people who made this thesis possible, including but not limited to:

Dr. Karim Karim and Dr. Peter Levine for guiding me throughout my Master's and supporting my research endeavor.

Dr. David Nairn and Dr. Manoj Sachdev for reading my thesis and providing valuable feedback.

Yunzhi (Hummer) Li and Jerry Liang for being excellent company throughout my Master's, in coursework and in research, and for supporting me when times were tightest.

Ahmet Camlica for his insight and help in depositing amorphous selenium and setting up X-ray apparatus.

Alireza Parsafar for allowing me to join his project early on during my Master's as a springboard for further learning.

Reza Mohammedi for supporting the characterization of our imager and keeping our research efforts moving forward.

NSERC, CFI and ORF for funding our research.

The Electrical and Computer Engineering Department for their collective support.

#### Dedication

To my parents, Hassen El-Falou and Soha Abdel-Majid, who have demonstrated the epitome of unconditional love and support towards me. I love you.

To my grandparents, Rasem Abdel-Majid, Yusr Abdel-Majid, Ahmed El-Falou and Fatme El-Falou, who have shown me more kindness than I can fathom.

To my siblings, Ahmad and Mona, for being by my side (both literally and metaphorically).

To my aunts, Sana, Zainab, Sarah, Asmaa and Haneen, who combined the compassion of motherhood and the company of friends.

To Maan and Hasan, for being pillars of support for our family when we needed it most.

To Rudy, for being the voice of reason in the countless times that I've need it, and for our priceless hours of conversations about life.

To Jaber, Fateh, and Osama, for showing me a different perspective on life as best demonstrated by endless nights of steak and Monopoly.

To Sara, for her friendship and company through all the C&D runs.

To my siblings Nada, Adam and Rasim, for being an endless source of inspiration and meaning.

Thank you all, and many many more.

# **Table of Contents**

| Li | st of | Tables                                                 | ix  |

|----|-------|--------------------------------------------------------|-----|

| Li | st of | Figures                                                | xi  |

| A  | bbre  | viations                                               | kiv |

| 1  | Intr  | oduction                                               | 1   |

|    | 1.1   | Digital X-ray Image Sensors                            | 2   |

|    |       | 1.1.1 Background                                       | 2   |

|    |       | 1.1.2 Amorphous Selenium X-ray Sensor                  | 2   |

|    | 1.2   | Photon-Counting X-ray Imagers                          | 3   |

|    |       | 1.2.1 Photon-counting imagers (PCIs) in the Literature | 5   |

|    | 1.3   | Performance of Photon-Counting Pixels                  | 6   |

|    |       | 1.3.1 Comparator Probability of Output                 | 7   |

|    |       | 1.3.2 Photon-Counting Pixel Specifications             | 8   |

|    | 1.4   | Summary of Application Requirements and Specifications | 9   |

|    | 1.5   | Thesis overview                                        | 10  |

| 2  | Pix   | el Design, Modeling and Simulation                     | 11  |

|    | 2.1   | Pixel Architecture                                     | 12  |

|    |       | 2.1.1 Pre-Amplifier Implementation                     | 13  |

|   |     | 2.1.2   | Latch Implementation                         | 16 |

|---|-----|---------|----------------------------------------------|----|

|   | 2.2 | Offset  | Correction                                   | 16 |

|   |     | 2.2.1   | Input-Offset Subtraction Simulations         | 24 |

|   |     | 2.2.2   | Output-Offset Subtraction Simulations        | 25 |

|   | 2.3 | Finaliz | zed Pixel Design                             | 25 |

|   |     | 2.3.1   | Pre-Amplifier Stages Optimization            | 30 |

|   |     | 2.3.2   | Simulations                                  | 31 |

|   |     | 2.3.3   | Pixel Layout                                 | 34 |

|   | 2.4 | Test P  | $rac{1}{2}$                                  | 37 |

|   |     | 2.4.1   | Test Pixel Layout                            | 38 |

| 3 | Ima | ger Ar  | chitecture, Physical Design and Verification | 40 |

|   | 3.1 | Chip A  | Architecture                                 | 40 |

|   |     | 3.1.1   | Power Domains                                | 42 |

|   |     | 3.1.2   | Clock Domains                                | 42 |

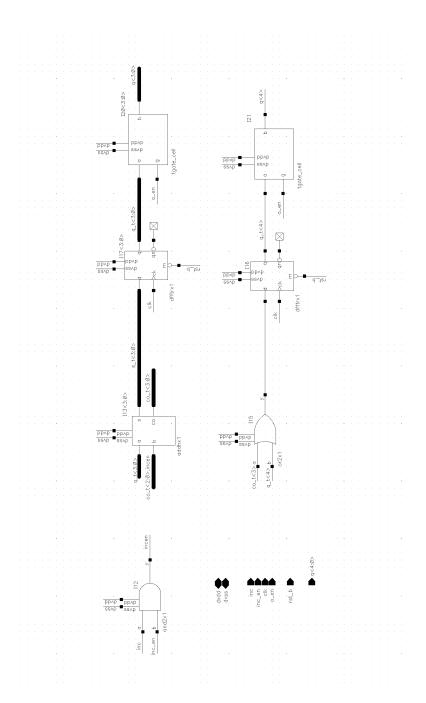

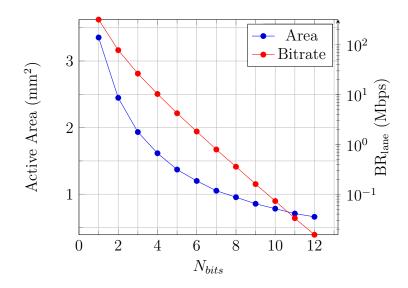

|   |     | 3.1.3   | Counters                                     | 43 |

|   |     | 3.1.4   | Scan Chains                                  | 46 |

|   |     | 3.1.5   | Output Shift Register                        | 49 |

|   |     | 3.1.6   | Bias Circuits                                | 49 |

|   |     | 3.1.7   | Probing circuits                             | 51 |

|   |     | 3.1.8   | I/O Pads                                     | 52 |

|   | 3.2 | Chip V  | Verification                                 | 52 |

|   |     | 3.2.1   | Counters                                     | 53 |

|   |     | 3.2.2   | Scan Chains                                  | 53 |

|   |     | 3.2.3   | Output Shift Register                        | 53 |

|   |     | 3.2.4   | Bias Circuits                                | 53 |

|   |     | 3.2.5   | Sub-Array Functional Verification            | 53 |

| 4                           | Exp           | erimental Results 6                | 60          |  |  |  |

|-----------------------------|---------------|------------------------------------|-------------|--|--|--|

|                             | 4.1           | Printed Circuit Board Design       | 60          |  |  |  |

|                             |               | 4.1.1 Analog and Digital Isolation | 61          |  |  |  |

|                             |               | 4.1.2 Biases                       | 61          |  |  |  |

|                             | 4.2           | FPGA RTL Design 6                  | 66          |  |  |  |

|                             |               | 4.2.1 Scan Chains                  | 66          |  |  |  |

|                             |               | 4.2.2 Data Path                    | 68          |  |  |  |

|                             |               | 4.2.3 Digital to Analog Converters | 58          |  |  |  |

|                             | 4.3           | Imager Characterization            | <u> 5</u> 9 |  |  |  |

|                             |               | 4.3.1 Pixel: Voltage Mode          | <u>5</u> 9  |  |  |  |

|                             |               | 4.3.2 Pixel: Charge Mode           | 74          |  |  |  |

|                             | 4.4           | Performance Summary                | 87          |  |  |  |

| 5                           | Cor           | clusion and Future Work 8          | 88          |  |  |  |

|                             |               | 5.0.1 Future Work                  | 88          |  |  |  |

| $\mathbf{R}$                | efere         | nces 9                             | 90          |  |  |  |

| APPENDICES 94               |               |                                    |             |  |  |  |

| A Simulation Testbenches 95 |               |                                    |             |  |  |  |

| в                           | B Pin List 98 |                                    |             |  |  |  |

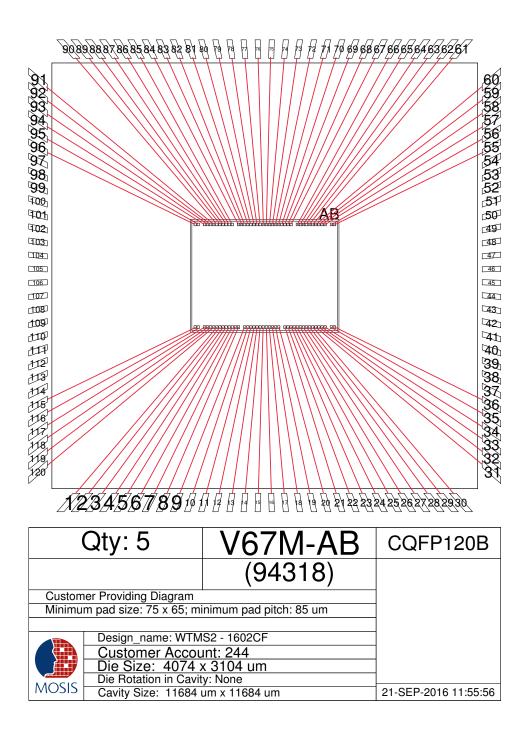

| С                           | Pac           | kage Bonding Diagram 10            | )2          |  |  |  |

# List of Tables

| 1.1 | Comparison of X-ray PCIs in the literature                                                                                                                                                                                         |    |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1.2 | Summary of specifications for PCI in this work.                                                                                                                                                                                    | 10 |  |

| 2.1 | Summary of pixel specifications.                                                                                                                                                                                                   | 12 |  |

| 2.2 | Geometry and bias point of pre-amplifier (PA) devices                                                                                                                                                                              | 15 |  |

| 2.3 | Results of Monte Carlo mismatch simulations. $C_{eff}$ and gains shown are average values. $v_n$ calculated analytically assuming only thermal noise latched onto $C_{eff}$ .                                                      | 34 |  |

|     | Since Ceff.                                                                                                                                                                                                                        | 01 |  |

| 3.1 | Outputs of Pixel Scan Chain.                                                                                                                                                                                                       | 47 |  |

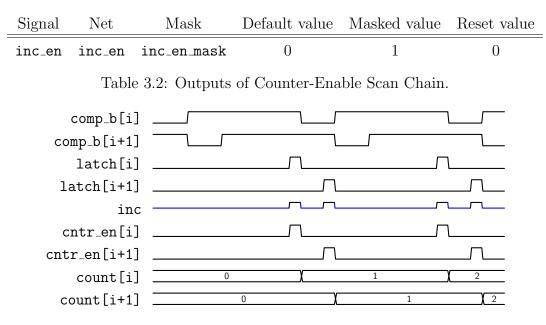

| 3.2 | Outputs of Counter-Enable Scan Chain.                                                                                                                                                                                              | 48 |  |

| 3.3 | Outputs of Counter-Read Scan Chain.                                                                                                                                                                                                | 49 |  |

| 4.1 | Bias values of current mirrors                                                                                                                                                                                                     | 64 |  |

| 4.2 | Noise contributions of voltage reference, digital-to-analog converter (DAC) and buffer. The buffer's figures include both voltage and current noises assuming a DAC output impedance of $8 k\Omega$ (typical). Low-frequency noise |    |  |

|     | is integrated over a bandwidth of 0.1 to $10 \mathrm{Hz}$ .                                                                                                                                                                        | 66 |  |

| 4.3 | Voltage Mode row experiment parameters.                                                                                                                                                                                            | 72 |  |

| 4.4 | Voltage Mode array experiment parameters.                                                                                                                                                                                          | 72 |  |

| 4.5 | Charge Mode row experiment parameters.                                                                                                                                                                                             | 74 |  |

| 4.6 | Charge Mode test pixel experiment parameters.                                                                                                                                                                                      | 79 |  |

| 4.7 | Charge Mode array experiment parameters                                                                                                                                                                                            | 85 |  |

| 4.8 | Summary of the PCI's performance in this work                   |    |  |

|-----|-----------------------------------------------------------------|----|--|

| 5.1 | Comparison of this work and other X-ray PCIs in the literature. | 89 |  |

# List of Figures

| 1.1 | Comparison between direct and indirect X-ray sensors.                                                                                                                                                                                                            |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | quantum efficiency (QE) of amorphous selenium (a-Se) over diagnostic X-<br>ray energy range for various sensor thicknesses. K-edge is observed at 13 keV<br>due to photoelectric absorption when the photon energy exceeds the orbital<br>energy of the K shell. |

| 1.3 | An ideal comparator.                                                                                                                                                                                                                                             |

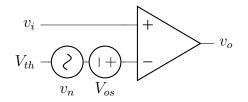

| 1.4 | Comparator with input-referred noise and offset                                                                                                                                                                                                                  |

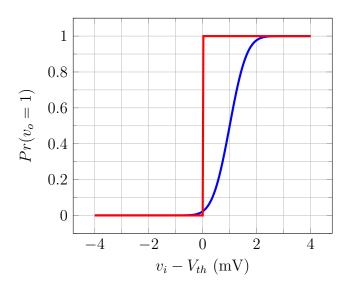

| 1.5 | Probability of output for ideal comparator (red) and non-ideal comparator with $V_{os} = 1 \text{ mV}$ and $v_n = 0.5 \text{ mV}_{\text{rms}}$ (blue).                                                                                                           |

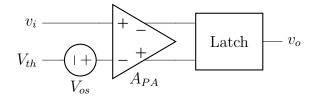

| 2.1 | Comparator with input-referred random offset, composed of a PA followed by a dynamic latch.                                                                                                                                                                      |

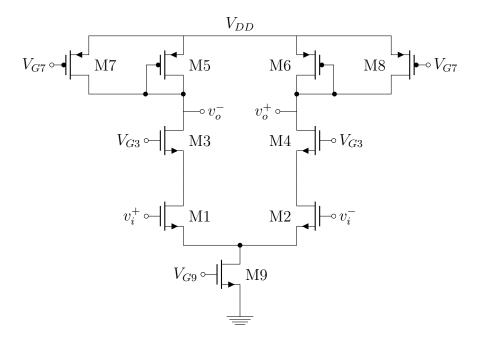

| 2.2 | PA schematic.                                                                                                                                                                                                                                                    |

| 2.3 | Effect of $W_{fac}$ on PA voltage transfer characteristic and dc gain from circuit simulations.                                                                                                                                                                  |

| 2.4 | Input-referred offset voltage of PA due to random mismatch from Monte<br>Carlo simulations                                                                                                                                                                       |

| 2.5 | Dynamic latch schematic.                                                                                                                                                                                                                                         |

| 2.6 | Latch input-referred random offset due to mismatch.                                                                                                                                                                                                              |

| 2.7 | Offset correction schemes.                                                                                                                                                                                                                                       |

| 2.8 | Transient simulations sweep of $W_{fac}$ in input-offset subtraction (IOS) test-<br>bench.                                                                                                                                                                       |

| 2.9 | Transient simulations sweep of $W_{fac}$ in output-offset subtraction (OOS) test-<br>bench.                                                                                                                                                                      |

| 2.10 | Pixel architecture and timing diagram.                                                                                                                                                                                                                                                                                                                                        |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.11 | Pixel simulation input waveforms showing two 10 µs integration cycles, with and without a photon input respectively. Inverted control signals correspond to P-channel metal-oxide-semiconductor (PMOS) switches.                                                                                                                                                              |

| 2.12 | Pixel simulation intermediate and output waveforms for a parasitic extracted netlist showing two 10 µs integration cycles, with and without a photon input. Refer to Figure 2.10a.                                                                                                                                                                                            |

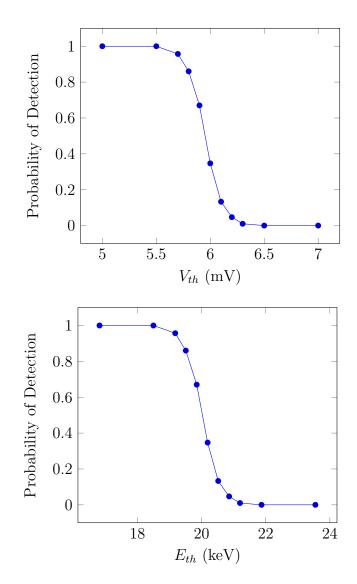

| 2.13 | Probability of output with photon input (probability of detection (PD)) of<br>energy $E_{ph} = 20 \text{ keV}$ as threshold $V_{th}$ (and $E_{th}$ ) increases. error rate (ER)<br>is 0 (not shown) for range of threshold sweep due to small sample size (400<br>Monte Carlo runs per point)                                                                                 |

| 2.14 | Pixel layout.                                                                                                                                                                                                                                                                                                                                                                 |

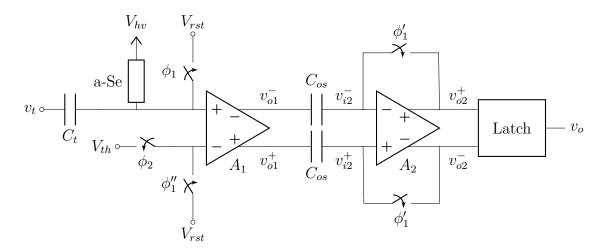

| 2.15 | Test pixel architecture showing input charge-coupling capacitor to $v_t$                                                                                                                                                                                                                                                                                                      |

| 2.16 | Test pixel layout showing test input metal-insulator-metal capacitors (MIM-CAPs)                                                                                                                                                                                                                                                                                              |

| 3.1  | Chip block diagram showing two arrays with a closer look at the blocks and connectivity within an array.                                                                                                                                                                                                                                                                      |

| 3.2  | 5-bit Binary Counter Schematic.                                                                                                                                                                                                                                                                                                                                               |

| 3.3  | Optimization of counter $N_{bits}$ showing area and lane bitrate trade-off                                                                                                                                                                                                                                                                                                    |

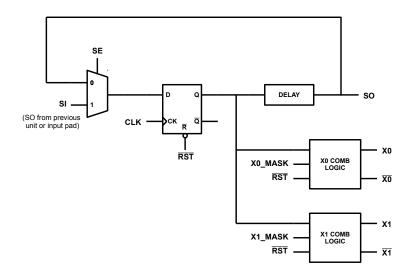

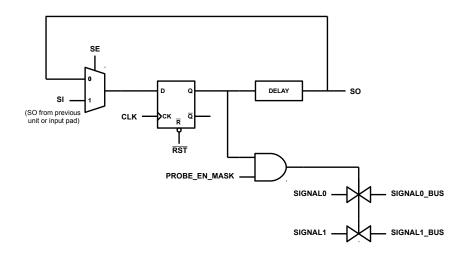

| 3.4  | Generic scan chain unit showing flip-flop (FF) and two signals                                                                                                                                                                                                                                                                                                                |

| 3.5  | Synchronization of Pixel Scan Chain and Counter-Read Scan Chain, showing how pixels from different rows only increment their respective counters                                                                                                                                                                                                                              |

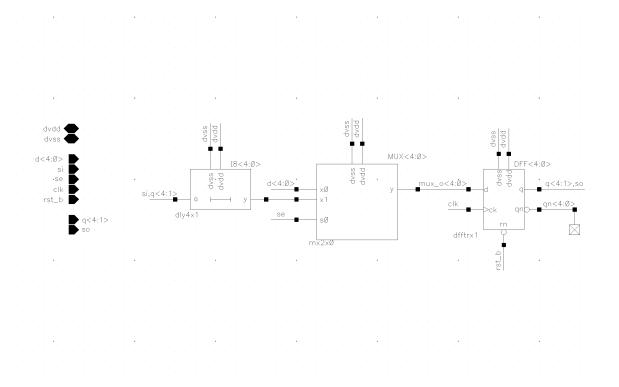

| 3.6  | 5-bit unit element in Output Shift Register.                                                                                                                                                                                                                                                                                                                                  |

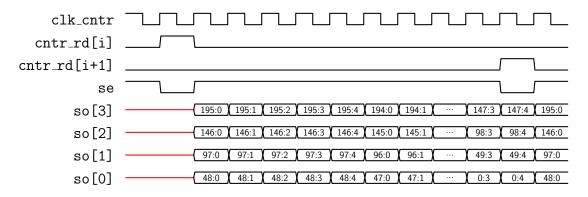

| 3.7  | Output Shift Register sample waveforms                                                                                                                                                                                                                                                                                                                                        |

| 3.8  | Unit of probe multiplexer scan chain showing two multiplexed signals                                                                                                                                                                                                                                                                                                          |

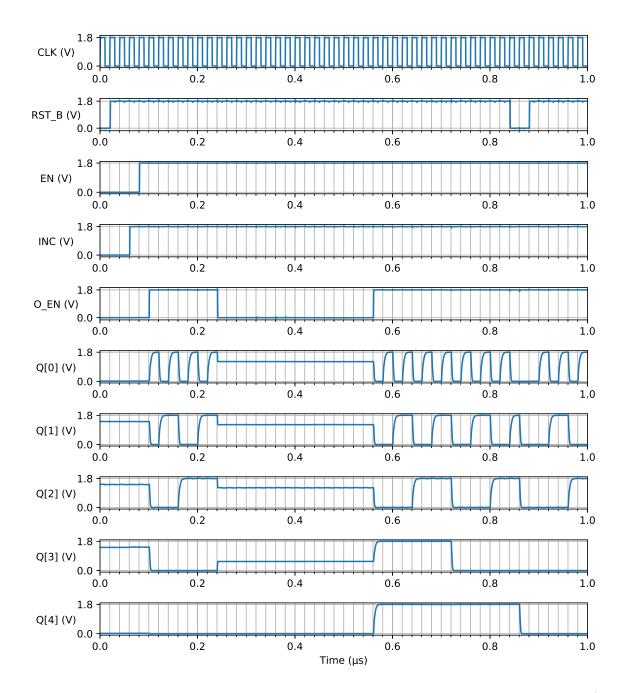

| 3.9  | Counter testbench waveforms. Outputs $Q[4:0]$ are probed on the bus (i.e., after a transmission gate) and only driven when $O\_EN = 1$ . Switching of transmission gates causes glitches on undriven busses (e.g., 0.24 µs to 0.56 µs). Outputs only increment when $EN = 1$ . $Q[4]$ (most-significant bit (MSB)) does not reset to 0 in the event of an overflow at 0.72 µs |

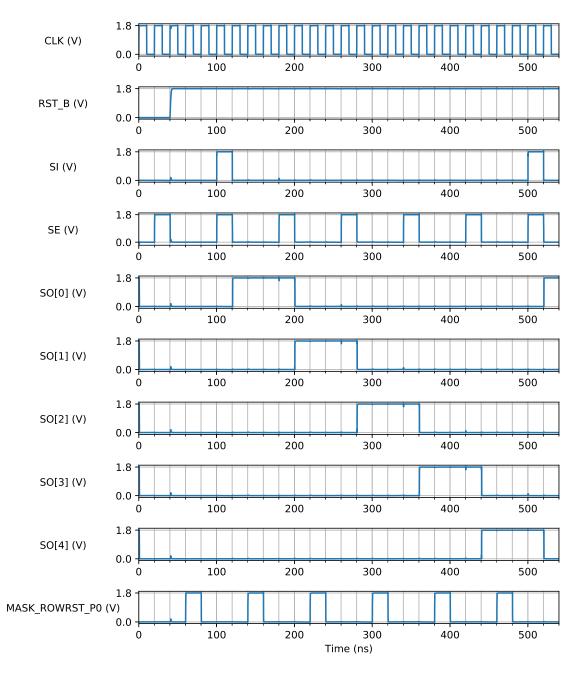

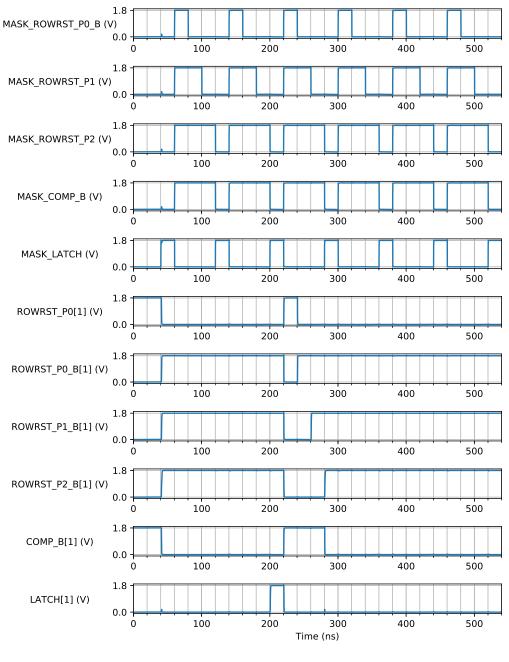

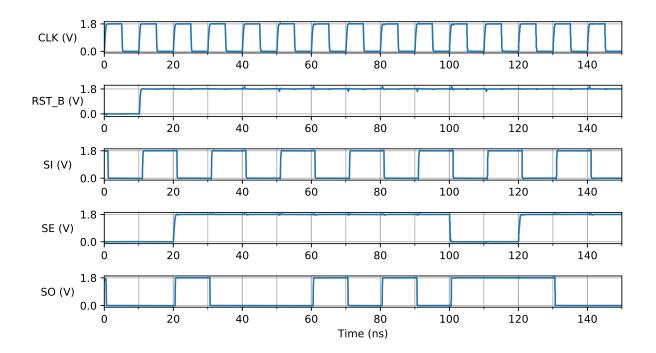

| 3.10 | Pixel Scan Chain testbench waveforms. Bits propagate through the chain<br>as expected and signal masks only affect the enabled row. Signal default,<br>masked, and reset values match those in Table 3.1.       | 56 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.11 | Output Shift Register unit testbench waveforms for an input $D[4:0] = 10001$ . Registers are loaded while $SE = 0$ then shifted through S0 when $SE = 1$ . If $SE = 1$ after all bits are shifted, S0 tracks SI | 57 |

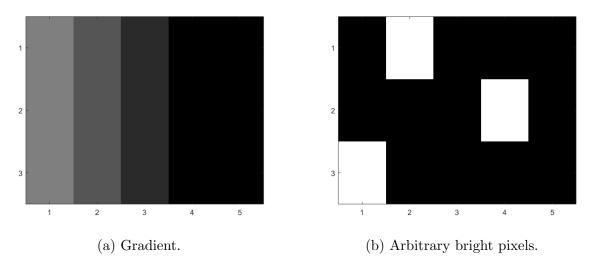

| 3.12 | Output images from 3x5 top level simulation.                                                                                                                                                                    | 58 |

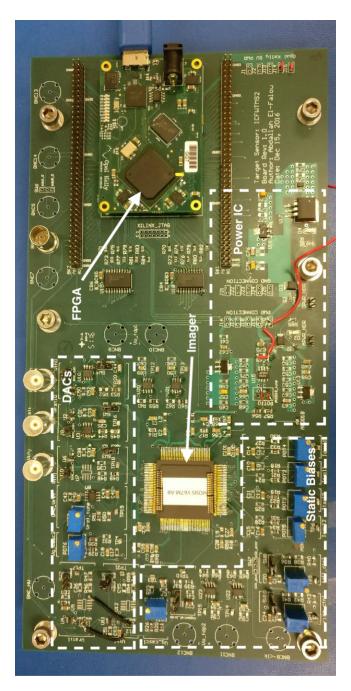

| 4.1  | System printed circuit board (PCB) design showing PCI, field-programmable gate array (FPGA), biasing circuits, and power integrated circuit (IC).                                                               | 62 |

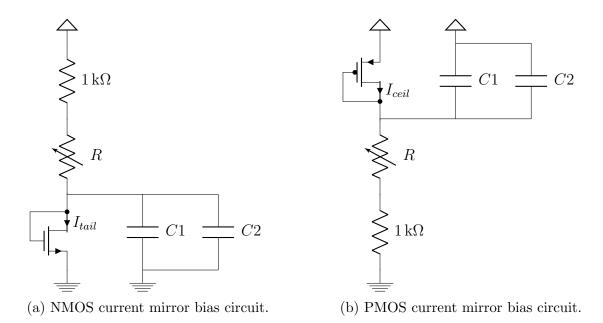

| 4.2  | Current mirror biasing circuits with on-chip devices shown for clarity (they do not exist on PCB).                                                                                                              | 63 |

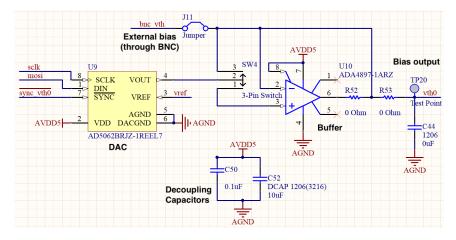

| 4.3  | DAC circuit including unity-gain buffer.                                                                                                                                                                        | 65 |

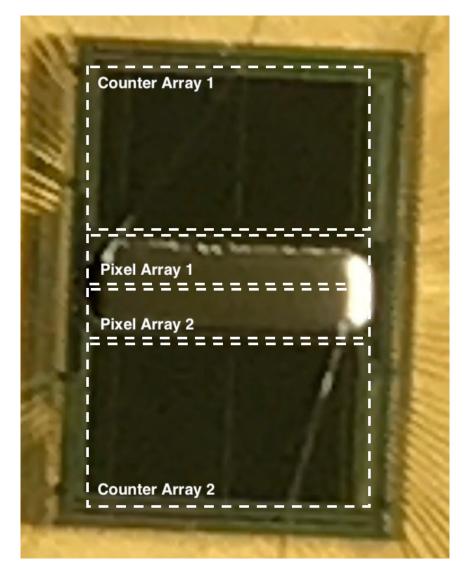

| 4.4  | Fabricated image sensor showing pixel and counter arrays                                                                                                                                                        | 70 |

| 4.5  | Pixel configuration in Voltage Mode.                                                                                                                                                                            | 71 |

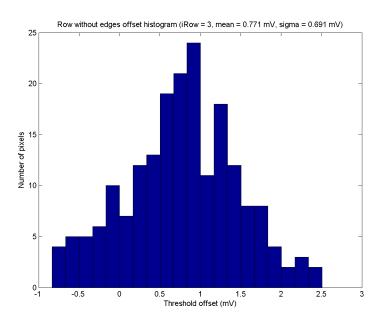

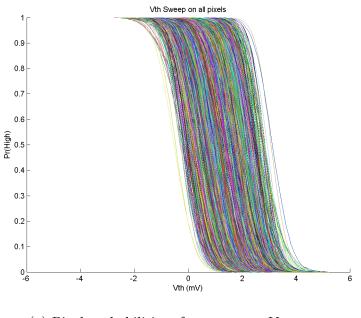

| 4.6  | Results of <i>Voltage Mode</i> row experiment                                                                                                                                                                   | 73 |

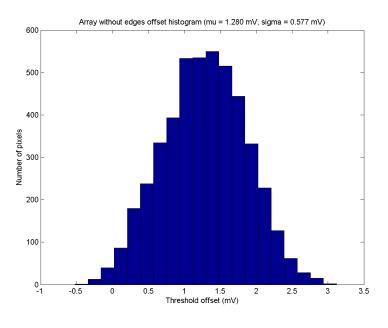

| 4.7  | Results of <i>Voltage Mode</i> array experiment                                                                                                                                                                 | 75 |

| 4.8  | Pixel configuration in <i>Charge Mode</i>                                                                                                                                                                       | 76 |

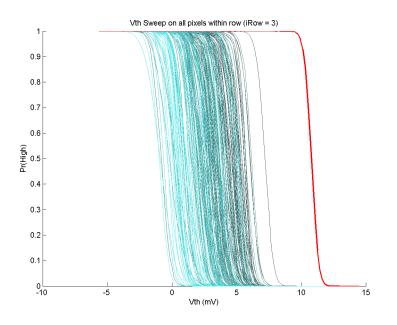

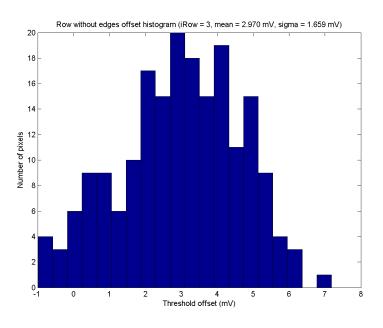

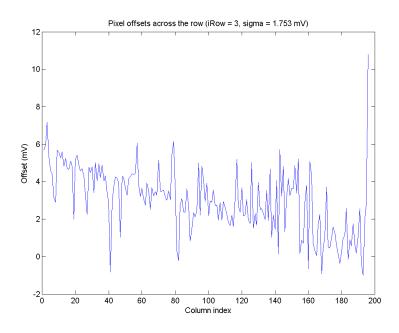

| 4.9  | Results of <i>Charge Mode</i> row experiment                                                                                                                                                                    | 77 |

| 4.10 | Pixel offset vs. column index showing gradient in offsets.                                                                                                                                                      | 78 |

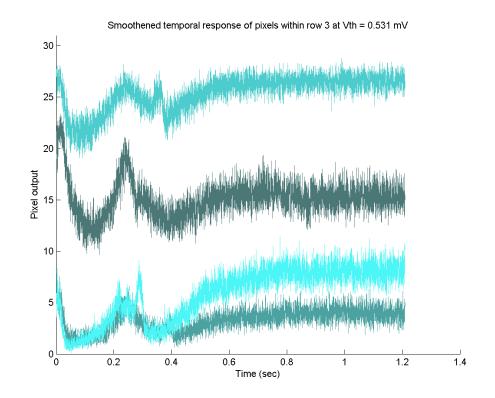

| 4.11 | Temporal response of four arbitrary pixels in a <i>Voltage Mode</i> row experi-<br>ment. A moving mean filter is applied to smoothen the curves                                                                 | 79 |

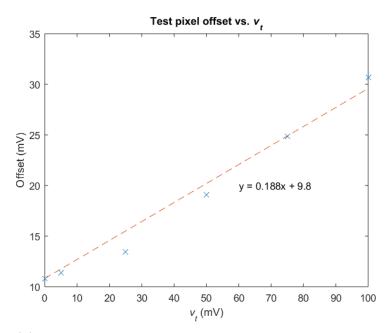

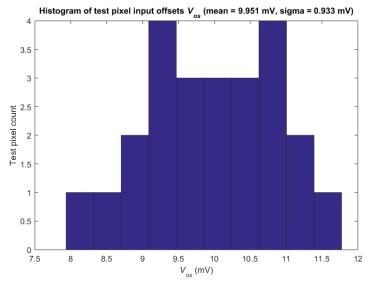

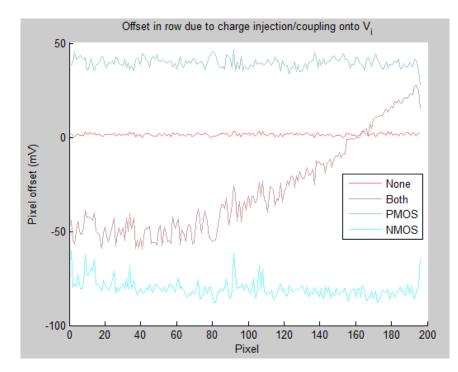

| 4.12 | Results of <i>Charge Mode</i> test pixel experiment                                                                                                                                                             | 81 |

| 4.13 | Results of <i>Charge Mode</i> single row test pixel experiment for all rows                                                                                                                                     | 82 |

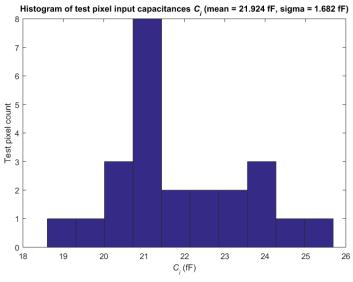

| 4.14 | Offset voltage $V_{os,sw}$ developed on integration node due to switch non-idealities<br>and capacitive coupling from pixel control signals (row 3)                                                             | 83 |

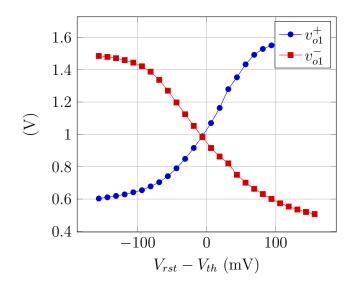

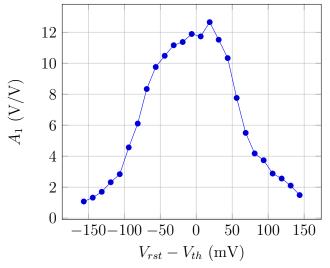

| 4.15 | Characterization of first PA stage. $V_{rst}$ is set to 1.1 V and $V_{th}$ is swept over<br>a range of 300 mV.                                                                                                  | 84 |

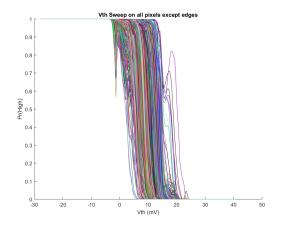

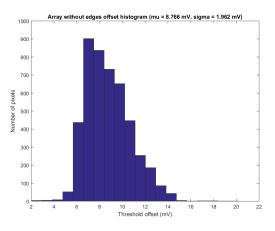

| 4.16 | Results of <i>Charge Mode</i> array experiment excluding edges                                                                                                                                                  | 86 |

| A.1  | Testbench to simulate IOS                                                                                                                                                                                       | 96 |

| A.2  | Testbench to simulate OOS.                                                                                                                                                                                      | 97 |

## Abbreviations

- $\mu$ -CT micro-computed tomography 1, 3, 9, 88

- **a-Se** amorphous selenium xi, 2–5, 9, 10, 29–31, 37, 80, 87, 88

- **AD** Analog Devices 65

- ADC analog-to-digital converter 5, 13

- **CDF** cumulative density function 7, 8, 34, 64, 71, 72, 78, 80, 85

- CMFB common-mode feedback 13

- CMOS complementary metal-oxide-semiconductor 2, 3, 6, 11, 23, 24, 88, 89

- DAC digital-to-analog converter ix, xiii, 6, 61, 64–66, 68

- **DNL** differential nonlinearity 65

- DRAM dynamic random access memory 68

- ehp electron-hole pair 3

- **ER** error rate xii, 7, 8, 10, 31, 34, 35, 85, 87

- ESD electrostatic discharge 52

- FDA fully-differential amplifier 13

- **FET** field-effect transistor 14, 23, 30

- **FF** flip-flop xii, 45, 46, 49, 51

- FIFO first-in, first-out 68

- FPGA field-programmable gate array xiii, 42, 61, 62, 64, 66, 68

- FSM finite-state machine 66

- I/O input/output 42, 43, 52, 53

- IC integrated circuit xiii, 61, 62, 65

- **INL** integral nonlinearity 65

- **IOS** input-offset subtraction xi, xiii, 16, 21, 23, 24, 26, 31, 96

- LDO low-dropout regulator 61

- **LSB** least-significant bit 49, 72, 74, 79, 85

- **MIMCAP** metal-insulator-metal capacitor xii, 14, 23, 25, 29, 30, 34, 36, 37, 39, 51

- MOS metal-oxide-semiconductor 11, 21

- **MSB** most-significant bit xii, 43, 45, 46, 53, 54

- **NMOS** N-channel metal-oxide-semiconductor 24, 42, 47, 63, 80, 83, 85

- **OOS** output-offset subtraction xi, xiii, 14, 16, 21, 23–25, 27, 29, 31, 97

- **PA** pre-amplifier ix, xi, xiii, 5, 12–19, 21, 23–27, 30, 34, 37, 38, 47, 49, 69, 72, 80, 83, 84, 89

- PCB printed circuit board xiii, 60, 62, 63

- **PCI** photon-counting imager iii, vi, ix, x, xiii, 3, 5, 6, 10, 11, 40, 60, 62, 69, 87–89

- **PCP** photon-counting pixel 6-8, 10-12

- **PD** probability of detection xii, 7, 8, 10, 31, 34, 35, 85, 87

- **PMOS** P-channel metal-oxide-semiconductor xii, 24, 32, 42, 47, 63, 74, 78–80, 83

- **PSD** power spectral density 64, 65

${\bf QE}\,$  quantum efficiency xi, 3, 4, 9

${\bf RMS}\,$  root-mean square 7, 64

${\bf SNR}\,$  signal-to-noise ratio 6, 30

${\bf SPI}$  serial peripheral interface  $65,\,68$

USB Universal Serial Bus 61, 68

## Chapter 1

## Introduction

X-ray radiation and sensing are the basis of many medical imaging modalities such as micro-computed tomography ( $\mu$ -CT) and mammography. The general approach in X-ray imaging is to radiate an object and sense the amount of radiation transmitted through the object. Since different substances attenuate X-rays to various extents, a shadow image is formed on the sensor. Mammography is the use of X-ray imaging to detect tumors and cancer precursors (e.g. microcalcifications) in human breast tissue [1]. Mammograms typically utilize low-energy X-rays (up to 30 keV) to image soft tissue, but studies have shown that dual-energy imagers can significantly improve contrast and reduce patient dose [2, 3].  $\mu$ -CT also benefits from dual-energy detectors, enabling better discrimination between tissues and materials in small animals [4]. In  $\mu$ -CT, many X-ray images are taken from various angles and reconstructed algorithmically to produce a cross-sectional image of the object [5]. It is often used in small-animal research studies since it is non-invasive [4, 6].

This thesis describes the design and characterization of a novel photon-counting X-ray imager for mammography and  $\mu$ -CT applications. Photon-counting imagers present many advantages, including energy discrimination for dual-energy imaging. This chapter will present a brief background on X-ray imaging and detection using semiconductor devices. It then proceeds to describe photon-counting imagers, their characterization, and finally outlines the specifications of this work to meet the needs of our applications.

#### **Direct Sensing**

Indirect Sensing

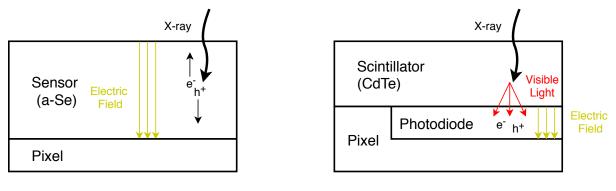

Figure 1.1: Comparison between direct and indirect X-ray sensors.

## 1.1 Digital X-ray Image Sensors

### 1.1.1 Background

X-ray sensing evolved over the last few decades from using traditional photographic films to digital sensors, allowing quicker image acquisition, easier image manipulation, and better dose efficiency [7]. Digital X-ray sensors utilize electronic circuits within pixel arrays on a complementary metal-oxide-semiconductor (CMOS) chip to sense the amount of incident radiation and form an image. A digital X-ray sensor can detect X-rays either indirectly or directly. Indirect sensing utilizes an intermediary scintillator to convert X-rays to visible light, which in turn is typically detected by a photodiode. On the other hand, a single sensing layer is used in direct sensing to convert X-rays to electrical charges, which are then sensed by dedicated pixel read-out circuits. When an X-ray strikes the sensor (typically a photoconductor), it creates a charge cloud within the sensor. Holes and electrons within the cloud are separated and collected by applying a high-voltage across the sensor. Figure 1.1 illustrates the difference between direct and indirect sensing.

### 1.1.2 Amorphous Selenium X-ray Sensor

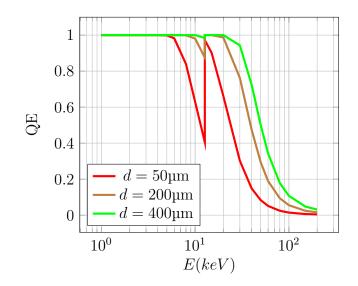

Amorphous selenium (a-Se) is a photoconductor commonly used in X-ray imaging. It was first made popular and technologically matured in Xerox photocopiers, but has since proved suitable for X-ray imaging. Due to its amorphous nature, it is easily deposited over large areas. Crystalline photoconductors (such as cadmium telluride, CdTe), on the other hand, require expensive bonding processes and suffer from low yield over large areas [8]. Another critical benchmark for X-ray sensors is their ability to stop X-rays. This is known as quantum efficiency (QE) and is quantified as

$$QE(E_{ph}) = 1 - e^{-\mu(E_{ph})d} , \qquad (1.1)$$

where d is the sensor's thickness,  $E_{ph}$  is the photon energy, and  $\mu(E_{ph})$  is the sensor's linear attenuation coefficient at a particular photon energy [9]. Figure 1.2 shows the QE of a-Se over the diagnostic X-ray energy range for a few sensor thicknesses of interest [10].

The charge released  $Q_{ph}$  due to a photon interaction with a-Se is given by

$$Q_{ph} = E_{ph}/W_{\pm} , \qquad (1.2)$$

where  $W_{\pm}$  is the conversion gain, typically given in keV/electron-hole pair (ehp).  $W_{\pm}$ depends on many factors including sensor thickness, electric field (i.e., bias voltage), and photon energy. At 10 V/µm and for diagnostic X-ray energies,  $W_{\pm}$  ranges between 30-70 eV/ehp [11]. A major trade-off with conversion gain is dark current, which is the electric current flow through a-Se in the absence of photons (typically given in mA/mm<sup>2</sup>). Dark current can saturate a pixel, preventing it from detecting photons should they arrive. Increasing the bias voltage across a-Se reduces charge carrier travel times, increasing charge collection efficiency and therefor decreasing  $W_{\pm}$  at the cost of higher dark current [12, 11].

The first hybrid a-Se-CMOS image sensor in [13, 14] demonstrated that a thermally deposited layer of a-Se can be coupled to an array of pixels. Most notably, it was (and remains) the highest-resolution direct X-ray image sensor to date.

## 1.2 Photon-Counting X-ray Imagers

Unlike integration-mode imagers, where a pixel integrates photocurrent for a (relatively long) duration during exposure, photon-counting imagers (PCIs) aim to detect and report every photon as it arrives. In the context of X-ray imagers, this effectively translates to very short integration times and highly sensitive pixel circuits. It has been demonstrated that PCIs are useful in diagnostic medical imaging of low-contrast tissue for various applications including  $\mu$ -CT and mammography [15, 16]. PCIs are especially useful for the following reasons:

Figure 1.2: QE of a-Se over diagnostic X-ray energy range for various sensor thicknesses. K-edge is observed at 13 keV due to photoelectric absorption when the photon energy exceeds the orbital energy of the K shell.

- 1. Equal energy-weighting of photons: Each detected photon resolves to a single count regardless of its energy, unlike integration-mode sensors where higher energies are weighted more heavily. This translates to higher contrast for low-density objects [16].

- 2. Multi-spectral image capture: These can be captured by simultaneously setting different detection thresholds within pixels. This way, images of only low-density (e.g. breast tissue) or high-density objects (e.g. microcalcifications) can be reconstructed from a single exposure. Furthermore, contrast agents such as iodine can be used within a single exposure as well, significantly reducing patient dose and motion artifacts [17].

- 3. High dynamic range: The maximum count is limited by a pixel's count rate, which is highly dependent on the sensor's temporal characteristics rather than read-out circuit architecture. On the lower end, pixel dark count can be effectively eliminated by setting the detection threshold high enough to neglect dark current, leakage and noise.

- 4. Linearity: The image sensor's response is linear regardless of exposure since each photon is detected independently [8].

5. In-pixel digitization: Information is digitized as close to the X-ray sensor as possible, circumventing many typical read-out issues such as cross-coupling, noise contributions along the signal path from pixel to analog-to-digital converter (ADC), and buffer settling issues.

However, photon-counting also presents several limitations and challenges, some of which are exacerbated by the use of a-Se as a photodetector:

- 1. Crosstalk: An incident photon's charge cloud may be collected by several pixels, causing erroneous extra counts if its energy is sufficient to excite several pixels, or lost counts if it is not. In a multi-spectral detector, this may also cause a high-energy photon to be mistaken for a few low-energy photons. This is highly dependent on the a-Se's spatial resolution and limits the minimum pixel pitch.

- 2. Dead time: Pixels will typically exhibit a dead-time during reset when they are insensitive to incoming photons.

- 3. Pile-up: Charge "pile-up" may occur if photons arrive shortly after one another, increasing the perceived energy of a photon and potentially causing false counts.

- 4. Slow temporal response: The slow electron response of a-Se causes a long tail to follow the initial spike in pixel response upon the arrival of a photon. This increases risk of charge pile-up (above) and limits the count-rate as well. However, it has been demonstrated that pixels of pitch much less than the sensor depth are less susceptible to this effect [16]. This is known as the small-pixel effect.

### **1.2.1 PCIs** in the Literature

Many X-ray PCIs are reported in the literature with a few common components. Namely, every pixel includes a charge pre-amplifier (PA), a comparator for energy thresholding, and at least one counter. Charge PAs are implemented using explicit capacitors in an amplifier's feedback loop and are often followed by a pulse shaper to remove dc offsets and attenuate charge pile-up issues. Many pixels include several comparators and counters to separate photon energies as well. This review is not meant to be exhaustive but will highlight a few works that are worth noting.

Perhaps the most significant and ongoing project is the Medipix, an on-going effort at CERN for medical imaging, high energy physics and other applications. The Medipix PCI

| Reference                          | [21]             | [20]               | [23]             | [24]             |

|------------------------------------|------------------|--------------------|------------------|------------------|

| CMOS process (nm)                  | 130              | 130                | 130              | 40               |

| Sensor                             | CdTe             | $\mathrm{HgI}_{2}$ | Si               | Si               |

| Active array size                  | $8 \times 4$     | $128 \times 128$   | $128 \times 128$ | $24 \times 18$   |

| Pixel size $(\mu m^2)$             | $756 \times 800$ | $60 \times 60$     | $75 \times 75$   | $100 \times 100$ |

| Number of energy bins              | 256              | 3                  | 1                | 1                |

| Power per pixel (µW)               | 10000            | 4.6                | 26               | 35               |

| Maximum count rate $(cps/\mu m^2)$ | 13               | 103                | 213              | 120              |

| Input-referred noise $(e_{rms}^-)$ | -                | 68                 | 123              | 117              |

Table 1.1: Comparison of X-ray PCIs in the literature.

has gone through three revisions thus far, with Medipix4 announced in 2017 but not yet released as of the time of writing. The Medipix3 stands out for its flexibility in operating modes, allowing trade-offs between pixel size  $(55 \times 55 \,\mu\text{m}^2 \text{ or } 110 \times 110 \,\mu\text{m}^2)$  and the number of photon energy bins. It also provides a mechanism to reduce charge sharing from an incident photon between several pixels [18, 19]. Another  $60 \times 60 \,\mu\text{m}^2$  pixel architecture reported in [20] saves area and power by utilizing a single comparator in conjunction with successive-approximation-like control logic to classify photons into three energy bins. The pixel also operates asynchronously, only resetting after a photon is detected and reducing the amount of dead-time. Reference [21] demonstrates a much larger pixel ( $756 \times 800 \,\mu\text{m}^2$ ) with more elaborate pulse-shaping and pile-up correction circuits. Some pixels opt for analog counters to reduce pixel area as well by accumulating discrete quanta of charge on a capacitor, as in [22]. Pixels in [23, 24] include in-pixel trimming digital-to-analog converters (DACs) to calibrate mismatches and attain tighter energy discrimination at the cost of larger pixels. Table 1.1 compares key metrics across a few PCIs.

## **1.3** Performance of Photon-Counting Pixels

Due to the digital output of photon-counting pixels (PCPs), performance must be characterized differently compared to integration-mode pixel architectures. Whereas the latter architectures are characterized by analog specifications such as signal-to-noise ratio (SNR),

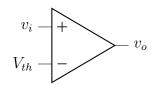

Figure 1.3: An ideal comparator.

well capacity, and noise floor, PCPs are characterized by maximum count rate, error rate (ER), and probability of detection (PD). This section will elaborate further on each of these specifications and more.

### **1.3.1** Comparator Probability of Output

At the heart of a PCP is a comparator as shown in Figure 1.3. An ideal comparator's output  $v_o$  is deterministic: if the input  $v_i$  is lower than the threshold  $V_{th}$ , the output is logic 0. If the threshold is exceeded, the output switches to logic 1. However, several non-idealities arise in practical comparators:

- Temporal noise  $v_n$ : Devices within the comparator exhibit noise (e.g. thermal noise), which can be modeled at the inputs of the comparator. Since it is additive to  $v_i$ , the comparator's output is statistical in nature, rather than deterministic. If the noise profile is Gaussian, the probability of output being 1 ( $Pr(v_o = 1)$ ) is given by a sigmoid centered at  $V_{th}$ .

- Static input offset voltage  $V_{os}$ : Static input offset causes a shift in  $Pr(v_o = 1)$  and can either be systematic or random. Systematic offset can arise due to comparator architecture or systematic device mismatches. On the other hand, random offset is statistical in nature and occurs due to random device mismatch.

These sources of uncertainty can be modeled at the comparator input as shown in Figure 1.4. Figure 1.5 shows an ideal comparator's deterministic output and a non-ideal comparator's statistical output, given as  $Pr(v_o = 1)$ . Note that the effective threshold  $V_{th} + V_{os}$  is now defined as the input voltage at which  $Pr(v_o = 1) = 0.5$ . In other words, it is the input voltage for which  $v_o$  can be either 1 or 0 with equal probability. It can be shown that  $Pr(v_o = 1)$  is a cumulative density function (CDF) of a normal distribution, and hence  $v_n$  (as a root-mean square (RMS)) can be extracted by observing  $Pr(v_o = 1)$  at known confidence intervals [25]. For the example given in Figure 1.5,  $V_{os}$  can be directly

Figure 1.4: Comparator with input-referred noise and offset

observed as 1 mV.  $v_n$  is most conveniently calculated by observing the input at which  $Pr(v_o = 1) = 67\%$  (in relation to  $V_{os}$ ), given here as  $v_n = 1.5 \text{ mV} - 1 \text{ mV} = 0.5 \text{ mV}_{\text{rms}}$ .

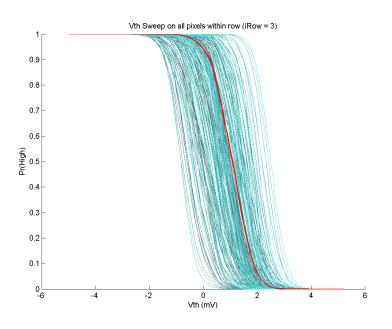

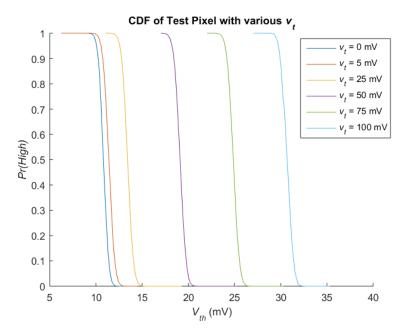

A CDF similar to that in Figure 1.5 can be obtained experimentally by slowly sweeping  $v_i$  while keeping  $V_{th}$  constant and, at each point, observing  $Pr(v_o = 1)$ . Alternatively,  $V_{th}$  can be swept instead, which may be easier to implement for a given comparator as is the case in our work. If  $Pr(v_o = 1)$  is plotted against  $V_{th}$ , the CDF is simply a mirrored version of the original and the analysis above applies directly.

$V_{os}$  was assumed to be static and known so far. However, on the array level, each pixel will demonstrate its own random offset with standard deviation  $\sigma(V_{os})$ . If a global threshold is used (which is usually the case), the total uncertainty in the threshold applied on each pixel is given by

$$\sigma^2(V_{th}) = \sigma^2(v_n) + \sigma^2(V_{os}) , \qquad (1.3)$$

where  $\sigma^2(.)$  denotes the variance of the random variable. An analogous quantity that is more relevant for imaging purposes is the uncertainty in photon energy threshold  $\sigma(E_{th}) = \sigma(V_{th})C_iW_{\pm}/q$ , where  $C_i$  is the capacitance on which charge from an incident photon is collected and q is the unit of elementary charge.

### **1.3.2** Photon-Counting Pixel Specifications

We can now define several metrics for the performance of PCPs:

- PD is given by  $Pr(v_o = 1)$  for a given input voltage  $v_i$  that is developed due to an incident photon of energy  $E_{ph}$ .

- ER is given by  $Pr(v_o = 1)$  in the absence of photons (i.e.,  $v_i = 0$ ). Note that ER can be non-zero due to temporal noise and potential systematic issues.

Figure 1.5: Probability of output for ideal comparator (red) and non-ideal comparator with  $V_{os} = 1 \text{ mV}$  and  $v_n = 0.5 \text{ mV}_{\text{rms}}$  (blue).

• Maximum count rate is the number of photons a pixel can detect within unit time, typically given in counts/second (cps). This is often normalized by area as well and typically reported in cps/mm<sup>2</sup>. Count rate can be limited by the X-ray sensor layer (a-Se), pixel architecture, or system architecture.

## 1.4 Summary of Application Requirements and Specifications

We derive requirements for the imager based on the target applications of mammography and  $\mu$ -CT [15, 16]. Given a photon energy range of 20-50 keV, a-Se must be greater than 200 µm thick to guarantee a QE > 30% for all photon energies of interest. In order to take advantage of the small-pixel effect, the pixel pitch should be 10-20x smaller than that [16]. We aim for at least 15x smaller, yielding a maximum pixel pitch of 13.3 µm.

Photon energy discrimination and the minimum detectable energy are driven by the same specification. That is, to detect a 20 keV photon is equivalent to discriminating between photons with an energy resolution of 20 keV. Assuming  $6\sigma$  separation in  $Pr(v_o = 1)$  between the presence and absence of a photon, and given a minimum photon energy of  $E_{ph} = 20 \text{ keV}$ , the uncertainty of energy threshold  $\sigma(E_{th}) < 3.3 \text{ keV}$ . This translates to

| Parameter                                                     | Specification       |

|---------------------------------------------------------------|---------------------|

| Sensor                                                        | a-Se                |

| Sensor thickness (µm)                                         | 200                 |

| Pixel area $(\mu m^2)$                                        | $\leq 13 \times 13$ |

| Minimum detectable $E_{ph}$ (keV)                             | 20                  |

| Uncertainty of photon energy threshold $\sigma(E_{th})$ (keV) | 3.3                 |

| Probability of detection $(E_{ph} = 20 \mathrm{keV})$         | 99.87%              |

| Error rate $(E_{ph} = 20 \text{ keV})$                        | 0.13%               |

| Maximum count rate $(cps/\mu m^2)$                            | 250                 |

Table 1.2: Summary of specifications for PCI in this work.

a PD and ER of 99.87% and 0.13%, respectively. Lastly, we aim to achieve a maximum count rate greater than the highest we found in literature [23]. Note that a-Se will likely be the limiting factor here rather than the read-out circuit.

A summary of imager specifications is given in Table 1.2.

## 1.5 Thesis overview

This thesis describes the design of a novel PCI. It is organized as follows:

- Chapter 2 begins with a generic model of a PCP then proceeds to describe the analysis, design and optimization of a transistor-level implementation.

- Chapter 3 describes the PCI system architecture including power distribution, control signal and bias generation, pixel counters, and verification.

- Chapter 4 describes the characterization setup and discusses the PCI's bench-top performance.

- Chapter 5 concludes this work with a brief summary.

## Chapter 2

# Pixel Design, Modeling and Simulation

This chapter focuses on the design of our PCP. It begins by introducing a simple architecture and implementation of a PCP in CMOS technology. Since such an architecture does not meet our specifications for input offset uncertainty due to random mismatch, the following sections describe methods to reduce mismatch. We then analyze the finalized pixel architecture and design it to meet the specifications in Table 2.1, including the pixel layout. Each of these subsections are accompanied with simulations to aid the design process. Finally, we describe the design of test pixels that enable easier bench-top characterization of the complete X-ray PCI.

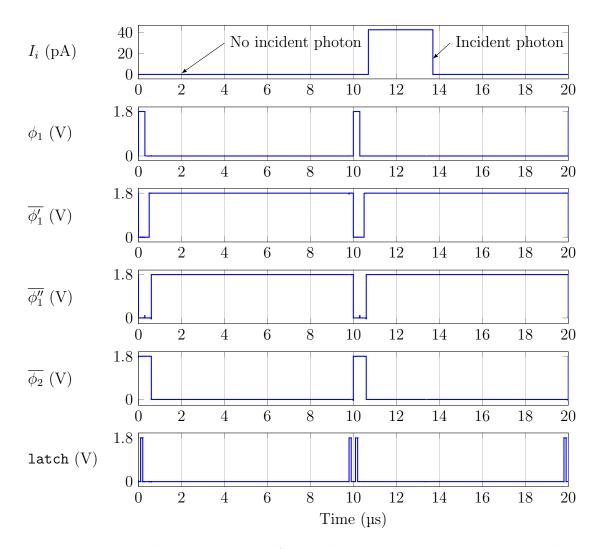

We derive pixel specifications based on the imager specifications in Table 1.2. Assuming the pixel pitch requirement is met, photon count rate translates directly to a minimum pixel count rate of 42 000 cps/pix. It is often more convenient to cite its reciprocal, pixel period  $T_{pix} < 240 \,\mu\text{s}$  during which a complete integration to resolve a photon is completed. Note  $T_{pix}$  is much longer than the expected duration of a photon event, which is on the order of a few microseconds [12]. Therefore, we choose a more strict specification  $T_{pix} < 10 \,\mu\text{s}$ .

The minimum detectable photon energy  $E_{ph}$  (and hence,  $\sigma(E_{th})$ ) drive the specifications for voltage threshold uncertainty  $\sigma(V_{th})$ . Early estimates of integration capacitance  $C_i$  yield 8-12 fF, including a top electrode and a few metal-oxide-semiconductor (MOS) devices. Assuming  $C_i \approx 10$  fF and  $W_{\pm} = 50 \text{ eV/ehp}$ ,  $\sigma(V_{th}) < 1.06 \text{ mV}_{rms}$ . If we assume temporal noise  $v_n$  and random offset  $\sigma(V_{os})$  contribute equally, each must be less than 0.75 mV<sub>rms</sub>. Table 2.1 summarizes pixel specifications which will guide the design process below.

We chose a TSMC 180 nm CMOS process since a hybrid selenium-CMOS image sensor

| Pixel pitch      | 13.3 µm                 |

|------------------|-------------------------|

| $\sigma(V_{th})$ | $1.06\mathrm{mV_{rms}}$ |

|                  | $0.75\mathrm{mV_{rms}}$ |

| $\sigma(V_{os})$ | $0.75\mathrm{mV_{rms}}$ |

| $T_{pix}$        | 10 µs                   |

Table 2.1: Summary of pixel specifications.

Figure 2.1: Comparator with input-referred random offset, composed of a PA followed by a dynamic latch.

was already demonstrated in this technology [13]. Relevant parameters for this process are introduced throughout the text as necessary.

## 2.1 Pixel Architecture

We start with the simplest PCP, composed of a comparator. Within the comparator is a pre-amplifier (PA) followed by a dynamic latch as shown in Figure 2.1. This pixel has two phases: track and latch. During the track phase, the voltage developed on an input capacitance due to an incident photon is compared to a threshold  $V_{th}$ . During the latch phase, the latch is enabled to conclude a comparison and utilizes positive feedback to output digital signal levels. The PA's purpose is two-fold: to amplify input signals to inhibit latch mismatch as well as minimize kickback from the latch onto the input node when the latch is enabled [25]. Note that the input signal here is a voltage and not a current, which should be the case for an incoming photon. We will first develop a model and design suitable for voltage comparison then modify it for a current input integrated onto a capacitor.

Each stage of the comparator exhibits an input-referred offset due to random transistor

mismatch mismatch  $\sigma(V_{os})$  given by

$$\sigma^2(V_{os}) = \sigma^2(V_{os,PA}) + \frac{\sigma^2(V_{os,latch})}{A_{PA}^2} , \qquad (2.1)$$

where  $V_{os,PA}$  and  $A_{PA}$  are the input-referred offset and gain of the PA, respectively, and  $V_{os,latch}$  is the input-referred offset voltage of the latch. All offsets are Gaussian random variables for which  $\sigma^2$  represents the variance. This assumes no systematic input offset as well (i.e., mean is 0 V). Depending on the architecture, a typical PA exhibits an input offset due to random transistor mismatch on the order of  $\sigma(V_{os,PA}) \approx 15 \,\mathrm{mV_{rms}}$ . Similarly, a typical latch exhibits an input offset due to uncertainty on the order of  $\sigma(V_{os,latch}) \approx 17 \,\mathrm{mV_{rms}}$ . Even if the latch's offset is eliminated, we are still limited here by  $V_{os,PA}$ .

#### 2.1.1 Pre-Amplifier Implementation

The purpose of PA is to provide the necessary gain to attenuate the latch's offset and isolate the input node to avoid latch kickback. Therefore, it must exhibit low mismatch as well. It must also have minimal input capacitance, since this will contribute directly to the pixel's input capacitance. Reference [26] suggests a PA architecture for a flash ADC, which has similar requirements to our pixel. This is shown in Figure 2.2. In order to understand this topology, first assume M7 and M8 are removed from the circuit. With M7 and M8 removed, this is a fully-differential amplifier (FDA) with cascodes (M3 and M4) at the input to reduce the Miller effect (and hence, input capacitive loading). Diode-connected devices M5 and M6 are used for loads, and hence the output common-mode level is set by the source-to-gate voltage  $V_{SG}$  of these devices. This eliminates the need for a common-mode feedback (CMFB) circuit, significantly reducing area and simplifying the design. The dc gain of the PA  $A_{PA}$  can be expressed as

$$A_{PA} \approx \frac{g_{m1}}{g_{m5}} = \sqrt{\frac{\mu_n(W_1/L_1)}{\mu_p(W_5/L_5)}}$$

, (2.2)

where  $\mu_n$  and  $\mu_p$  are the transistor electron and hole mobilities, respectively, and  $W_i$  and  $L_i$  are the channel width and length of device *i*, respectively. Since this is independent of bias current, the output common-mode range can be set independently from the gain.

We now consider the effect of M7 and M8. These devices are used to source more current into the input pair, increasing the small-signal transconductance  $g_{m1}$  without affecting the output common-mode level (assuming their output resistance is high). As a result,  $A_{PA}$  becomes:

$$A_{PA} \approx \frac{g_{m1}}{g_{m5}} = \sqrt{\frac{\mu_n (W_1/L_1) I_{D1}}{\mu_p (W_5/L_5) I_{D5}}} , \qquad (2.3)$$

where  $I_{Di}$  is the bias current of device *i*.

Of critical importance, especially for output-offset subtraction (OOS) (explained below), is the output swing of the PA. On the lower end, M3 must remain in saturation in order to limit the voltage swing at the drain of M1. On the upper end, it is limited by M5 remaining on (this will likely occur before M7 enters triode). Similarly, the input common-mode range is bound on the lower end by M1 remaining on and M9 remaining in saturation. On the upper end, it is bound by M1 remaining in saturation. Therefore:

$$V_{G3} - V_{t3} < v_o^- < V_{DD} - |V_{t5}|$$

, and (2.4)

$$V_{t1} + V_{ov1} + V_{ov9} < v_i^+ < V_{G3} - V_{ov3} + V_{t1} - V_{t3} , \qquad (2.5)$$

where  $V_{ti}$  and  $V_{ovi}$  are the threshold and overdrive voltages of device *i*, respectively. These present a trade-off between input and output swing depending on  $V_{G3}$ . A lower  $V_{G3}$  provides wider output swing at the expense of a narrower input swing. This can be optimized since input signal levels are known (and quite low). Input common-mode level in the final pixel design (described in section 2.3) can be set by  $V_{rst}$ .

As will be shown in the final pixel design, the load capacitance seen by a PA during reset is dominated by  $C_{os}$ . This is chosen as the minimum metal-insulator-metal capacitor (MIMCAP) size (20 fF). Assuming a typical system clock period of 20 ns and 7 time constants (7 $\tau$ ) for settling,  $\tau < 2.9$  ns and the maximum output resistance  $R_o$  of the PA is

$$R_o = (1/g_{m5}) /\!\!/ r_{o5} /\!\!/ r_{o7} \approx 1/g_{m5} < \frac{2.9 \,\mathrm{ns}}{20 \,\mathrm{fF}} = 143 \,\mathrm{k\Omega} \;, \tag{2.6}$$

where  $r_o$  is the output resistance of a field-effect transistor (FET) in saturation. Note that the bandwidth requirements are set solely by M5 as a first-order approximation.

During the initial design, the PA was parameterized in order to facilitate the design of multiple stages with various gains, as will be shown in later sections. Current density in all devices is set constant, while  $A_{PA}$  can be tuned easily by adjusting a common transistor

Figure 2.2: PA schematic.

width factor  $W_{fac}$ . The bias points of devices are chosen to reduce mismatch effects; that is, the input device M1 is biased at a low overdrive voltage  $V_{ov}$  while current mirrors M7 and M9 are biased at higher  $V_{ov}$  [27]. The load device M5 size is not dependent on  $W_{fac}$  and is biased to sink a constant current such that the output common-mode level is centered within the output swing. Lastly, M3 is set to match M1 in size and bias conditions for simplicity. Table 2.2 summarizes the geometry and bias points of all devices.

| Device   | W (nm)                                                                       | L (nm) | $ I_D $ (µA)        | $V_{ov} (mV)$ |

|----------|------------------------------------------------------------------------------|--------|---------------------|---------------|

| M1       | $220 \cdot W_{fac}$                                                          | 200    | $3.5 \cdot W_{fac}$ | 110           |

| M3       | $\begin{array}{c} 220 \cdot W_{fac} \\ 220 \cdot W_{fac} \\ 220 \end{array}$ | 200    | $3.5 \cdot W_{fac}$ | 110           |

| M5       | 220                                                                          | 1000   | 3.5                 | -             |

| $M7^{1}$ | $220 \cdot W_{fac}$                                                          | 300    | $3.5 \cdot W_{fac}$ | 250           |

| M9       | $\begin{array}{c} 220 \cdot W_{fac} \\ 220 \cdot W_{fac} \end{array}$        | 400    | $7 \cdot W_{fac}$   | 235           |

Table 2.2: Geometry and bias point of PA devices.

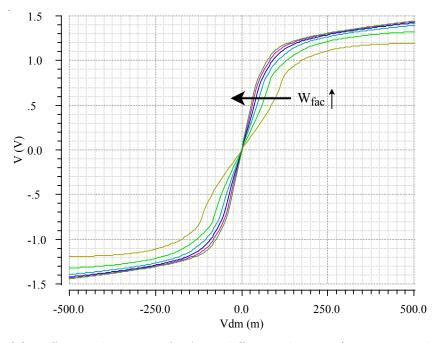

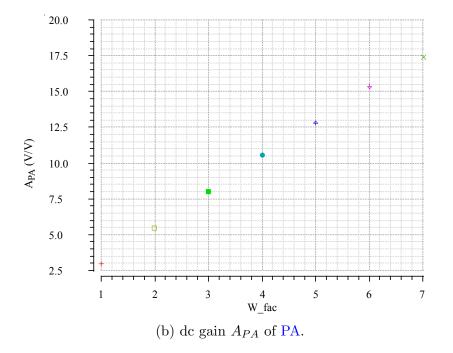

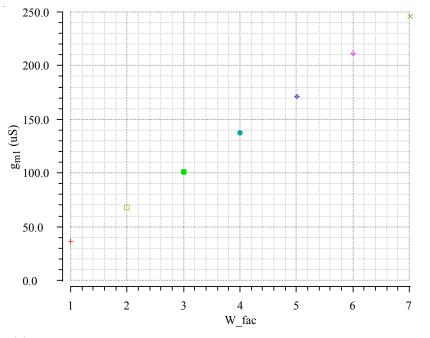

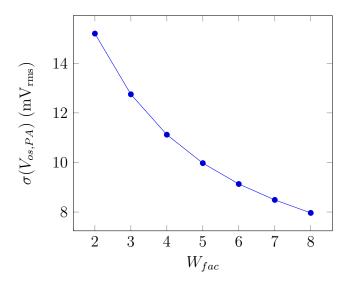

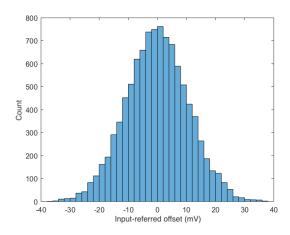

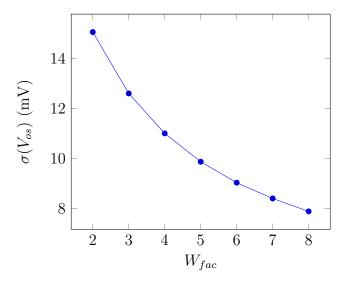

Figure 2.3 shows a few key simulation results while sweeping  $W_{fac}$  that can summarize the PA's performance. Its gain  $A_{PA}$  and the input-pair's transconductance  $g_{m1}$  increase linearly as expected, while bandwidth is relatively constant at 80 MHz (not shown). Figure 2.4 shows the statistical distribution of  $V_{os,PA}$  for  $W_{fac} = 4$ . It is Gaussian as expected, and its spread is inversely proportional to  $W_{fac}^2$  as expected from mismatch models.

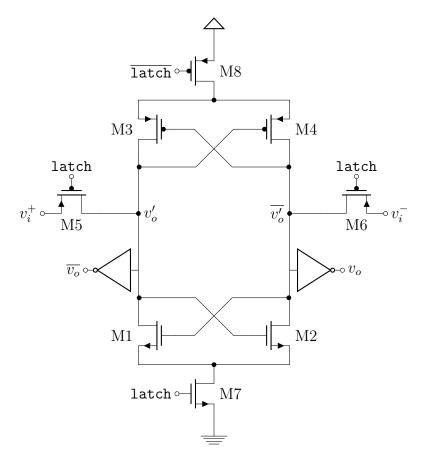

#### 2.1.2 Latch Implementation

A dynamic latch is used to provide the large gain needed at the end of a comparison in order to output digital logic levels. Such a latch is proposed in [25], which consists of two back-to-back inverters and a few switches as seen in Figure 2.5. The latch begins with its input latch signal low, allowing the previous stage to set the initial voltage at nodes  $v'_o$  and  $\overline{v'_o}$ . Note that M7 and M8 are both off, disabling the inverters. When latch switches high, M5 and M6 turn off while M7 and M8 turn on, enabling positive feedback. Digital buffers are added to the outputs in order to drive column buses and match capacitive loads at  $v'_o$  and  $\overline{v'_o}$ .

The latch's mismatch is simulated in a transient analysis. A fast clock signal continuously triggers the latch while its inputs are ramped slowly, and  $V_{os,latch}$  is defined as the input Vip - Vin when  $v_o$  resolves to 1 for the first time. Note that the resolution of this experiment is limited by the ratio of clock speed to input ramp speed, which is made sufficiently high to attain a meaningful result.

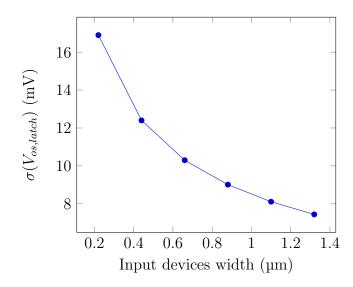

Figure 2.6 shows  $V_{os,latch}$  for increasing device sizes. All input devices M1-4 are sized equally for simplicity. The result is inversely proportional to the input device's area (i.e. square of its width, since its length is constant), which follows mismatch models as expected.

## 2.2 Offset Correction

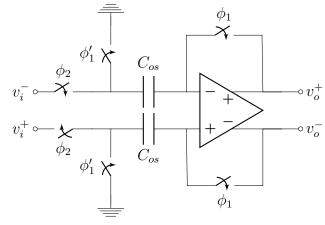

One method to reduce the effective offset of the PA is to store it on a capacitor during a reset phase, then connect the capacitor during comparison such that the offset is removed. There are two methods of storing the offset of a PA: input-offset subtraction (IOS) and output-offset subtraction (OOS) [28]. In IOS, the PA is connected in a unity-gain feedback

<sup>&</sup>lt;sup>1</sup>This is a slight deviation from the correct width of  $220(W_{fac}-1)$  to maintain the same operating point. However, this has a minimal effect on its overdrive  $V_{ov}$  and the drain current is set correctly regardless since its bias  $V_{G7}$  is adjusted accordingly.

(a) Differential output of PA vs differential input (common-mode input 1.1 V). Steeper curves correspond to higher  $W_{fac}$ .

(c) Small-signal transconductance  $g_{m1}$  of input device M1 in PA.

Figure 2.3: Effect of  $W_{fac}$  on PA voltage transfer characteristic and dc gain from circuit simulations.

(a) Input-referred voltage offset of PA due to random mismatch for increasing device sizes.

(b) Statistical distribution of PA input-referred offset  $V_{os,PA}$  for  $W_{fac} = 4$ .  $\sigma(V_{os,PA}) = 10.7 \,\mathrm{mV_{rms}}$  (10,000 points).

Figure 2.4: Input-referred offset voltage of PA due to random mismatch from Monte Carlo simulations.

Figure 2.5: Dynamic latch schematic.

Figure 2.6: Latch input-referred random offset due to mismatch.

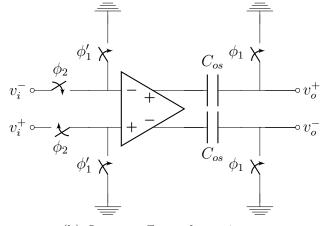

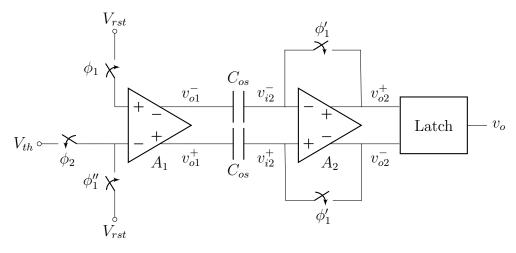

configuration and the offset is stored on input coupling capacitors. In OOS, the PA inputs are shorted and the (amplified) offset is stored on coupling capacitors at the output. These two topologies are shown in Figure 2.7. Note that all switches shown are active-high.

Both circuits operate in two phases: reset and track (note the absence of a latch). The offset is stored on the input/output capacitors  $C_{os}$  during the reset phase, then used to cancel the offset during the track phase. Timing for both of these circuits is as follows:

- 1. Reset:  $\phi_1$  and  $\phi'_1$  are both on and  $\phi_2$  is off. The offset of the PA is stored on the capacitors  $C_{os}$ .  $\phi_1$  shuts off first, releasing charge onto  $C_{os}$  due to MOS switch non-idealities.  $\phi'_1$  then shuts off, also releasing charge onto floating capacitances on its terminals. This concludes the reset phase.

- 2. Track:  $\phi_2$  turns on, connecting the input signals  $v_i^+$  and  $v_i^-$  to the PA. The charge released by  $\phi'_1$  shutting off is discharged through the inputs. Capacitors  $C_{os}$  are connected in series such that offsets are subtracted from the PA's input or output (in IOS and OOS, respectively).

More detail on the operation of these circuits can be found in [28]. A residual offset remains due to clock feedthrough from MOS switches, imperfect offset storage, and capacitor mismatch. The variance of input-referred residual offset voltages  $\sigma^2(V_{ios})$  and  $\sigma^2(V_{oos})$

(a) Input-offset subtraction.

(b) Output-offset subtraction.

Figure 2.7: Offset correction schemes.

can be expressed as

$$\sigma^{2}(V_{ios}) = \frac{\sigma^{2}(V_{os,PA})}{(A_{PA}+1)^{2}} + \frac{\sigma^{2}(\Delta Q_{sw})}{C_{os}^{2}} + \frac{\sigma^{2}(\Delta C_{os})}{C_{os}^{2}}\frac{Q_{sw}^{2}}{C_{os}^{2}}, \text{ and}$$

(2.7)

$$\sigma^{2}(V_{oos}) = \frac{1}{A_{PA}^{2}} \left[ \frac{\sigma^{2}(\Delta Q_{sw})}{C_{os}^{2}} + \frac{\sigma^{2}(\Delta C_{os})}{C_{os}^{2}} \frac{Q_{sw}^{2}}{C_{os}^{2}} \right], \qquad (2.8)$$

where  $C_{os}$  and  $\Delta C_{os}$  are the nominal and mismatch capacitance of the offset storage capacitors, and  $Q_{sw}$  and  $\Delta(Q_{sw})$  are the nominal and mismatch in charge released onto  $C_{os}$ when  $\phi_1$  switches off, respectively. Switch  $\phi'_1$  does not contribute to offset since any charge errors due to switching are drained by switch  $\phi_2$  during comparison.

As shown in Equations 2.7 and 2.8, OOS can result in a lower residual offset since  $V_{os,PA}$  is eliminated completely and the voltage developed on  $C_{os}$  when  $\phi_1$  is attenuated by  $A_{PA}$ . However,  $A_{PA}$  should be limited to ensure the PA is operating within the linear region. Care must also be taken to ensure its inputs are within the common-mode input range since they are dc-coupled. Neither of these is a concern in IOS since it resets in unity-gain feedback and inputs are ac-coupled. The PA must be stable in unity-gain feedback but this is guaranteed since it consists of a single stage only. IOS presents a higher input capacitance than OOS as well, making it unsuitable as a first stage for our pixel.

The term  $\frac{\sigma^2(\Delta C_{os})}{C_{os}^2} \frac{Q^2}{C_{os}^2}$  in Equations 2.7 and 2.8 is the contribution of mismatch between coupling capacitors  $C_{os}$ . Mismatch between two closely-placed MIMCAPs is given by [29]

$$\frac{\sigma(\Delta C_{os})}{C_{os}}(\%) = \frac{2.5563}{\sqrt{(WL)_{os}(\mu m^2)}} , \qquad (2.9)$$

where  $(WL)_{os}$  is the MIMCAP area. In the TSMC 180 nm CMOS process, MIMCAPs have a density of  $1 \text{ fF}/\mu\text{m}^2$ , and the smallest size allowed is a 4 x 4  $\mu\text{m}^2$  with a nominal capacitance of 20 fF (including parasitics).

There are two non-ideal effects when we operate FET switches. Charge injection is a phenomenon whereby charge stored in the FET channel are released to the drain and source terminals when it is shut off. Similarly, clock feedthrough occurs when the gate control signal toggles and couples charge onto the drain and source terminals through the gate-drain and gate-source overlap capacitances. The charge injected onto the drain or source terminal is given by [25]

$$Q_{ch} = W_{ch} L_{ch} C_{ox} (|V_{GS}| - |V_t|)/2 , \qquad (2.10)$$

where  $W_{ch}$  and  $L_{ch}$  are the channel width and length,  $C_{ox}$  is the gate oxide capacitance per unit area, and  $V_{GS}$  and  $V_t$  are the gate-source and threshold voltages, respectively (shown in absolute value for both N-channel metal-oxide-semiconductor (NMOS) and P-channel metal-oxide-semiconductor (PMOS) devices). It has been demonstrated that the charge will split equally between the source and drain if the gate voltage rise/fall time is fast enough, hence the factor of 2 [30]. Since charge injection  $Q_{ch}$  is usually dominant over clock feedthrough, the total charge released into the drain or source is  $Q_{sw} \approx Q_{ch}$ . The last term  $\frac{\sigma^2(\Delta Q_{sw})}{C_{os}^2}$  in Equations 2.7 and 2.8 is due to the mismatch in charge injection and feedthrough  $\Delta Q_{sw}$ , which is typically 1-2 orders lower than  $Q_{sw}$  [25, 28]. In the TSMC 180 nm CMOS process, the minimum  $W_{ch}$  and  $L_{ch}$  are 220 nm and 180 nm respectively.  $C_{ox}$ is nominally 8.85 fF/µm<sup>2</sup>,  $V_{tn}$  is nominally 490 mV, and  $V_{tp}$  is nominally -492 mV. Given these parameters, the standard deviation of total mismatch due to switch and capacitor non-idealities is approximately 0.4 mV<sub>rms</sub>.

If the latch is included, its offset  $V_{os,latch}$  is attenuated by  $A_{PA}$  (refer to Equation 2.1). This is likely to dominate and can be reduced by increasing the gain  $A_{PA}$  or adding more gain stages. In the case of IOS,  $V_{os,PA}$  is the second-largest contributor to offset and can also be reduced by increasing  $A_{PA}$ , but other factors will often limit how high it can go. Since  $A_{PA}$  is also limited in OOS, we will require multiple gain stages as Section 2.3 will describe. Offset due to  $C_{os}$  mismatch is negligible and will be ignored in upcoming sections.

## 2.2.1 Input-Offset Subtraction Simulations

Figure A.1 (see Appendix A) shows the testbench used to verify IOS. A transient simulation is used since a sequence of events is needed. RST and RST\_D are asserted first (RST\_B is simply the inverse of RST for PMOS switches), with the latter remaining high slightly longer to minimize charge injection errors as explained before. COMP is a non-overlapping signal that is asserted afterwards and throughout a comparison to connect the input signals to the PA (COMP\_B is the inverse of COMP). Inputs vip and vin are both ramped in opposite directions to simulate the output of a previous differential stage, and key design parameters are defined as:

1. Gain

$$A_{PA} = \frac{dv_o}{dv_i}$$

when  $v_i = 0$ , where  $v_i = vip - vin$  and  $v_o = vop - von$ .

2. Intrinsic input-referred mismatch  $V_{os} = v_{i3}$  when  $v_o = 0$ , where  $v_{i3} = vip3 - vin3$ .

3. Corrected mismatch  $V_{ios} = v_i$  when  $v_o = 0$ .

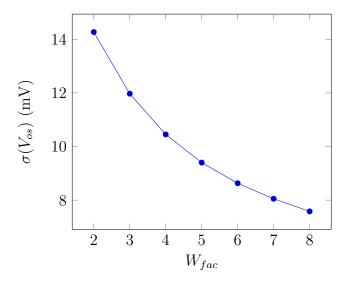

Figure 2.8 shows the standard deviation of intrinsic and corrected offsets  $\sigma(V_{os})$  and  $\sigma(V_{ios})$ , respectively.  $\sigma(V_{os})$  matches the results from dc simulations and  $\sigma(V_{ios})$  shows 7x reduction in mismatch after correction.  $A_{PA}$  also matches results of dc simulations (refer to Figure 2.4).  $\sigma(V_{ios})$  follows the trend as expected, ultimately limited by clock injection. The asymptotic limit is approximately 0.45 mV, which reasonably matches our model.

# 2.2.2 Output-Offset Subtraction Simulations

Figure A.2 (see Appendix A) shows the testbench used to verify OOS. A transient simulation is used since a sequence of events is needed. RST and RST\_D are asserted first, with the latter remaining high slightly longer to minimize charge injection errors as explained before. COMP is a non-overlapping signal that is asserted afterwards and throughout a comparison to connect the input signals to the PA. The negative input signal vin is fixed at a specified "reset level", while the positive input vip is ramped during comparison. Key design parameters are defined as:

- 1. Gain  $A_{PA} = \frac{dv_o}{dv_i}$  when  $v_i = 0$ , where  $v_i = \text{vip} \text{vin}$  and  $v_o = \text{vop}_{-} \text{oos} \text{von}_{-} \text{oos}$ .

- 2. Intrinsic input-referred mismatch  $V_{os} = v_i$  when  $v_{o1} = 0$ , where  $v_{o1} = vop_fdp von_fdp$ .

- 3. Corrected mismatch  $V_{oos} = v_i$  when  $v_o = 0$ .

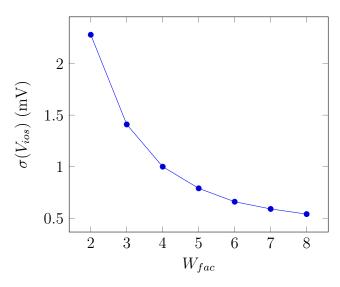

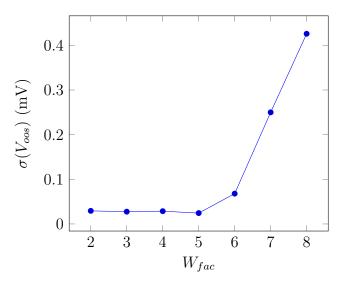

Figure 2.9 shows  $\sigma(V_{os})$  and  $\sigma(V_{oos})$  while sweeping  $W_{fac}$  from a Monte Carlo simulation. Extracting  $V_{os,PA}$  in this testbench is primarily useful to compare with the values obtained from dc simulations and matches them closely. Notice that  $V_{oos}$  is less than 50 µV and decreasing for small geometries but increases drastically when  $W_{fac} \geq 5$ . This is because pixels begin to saturate during reset, causing imperfect offset storage and correction.

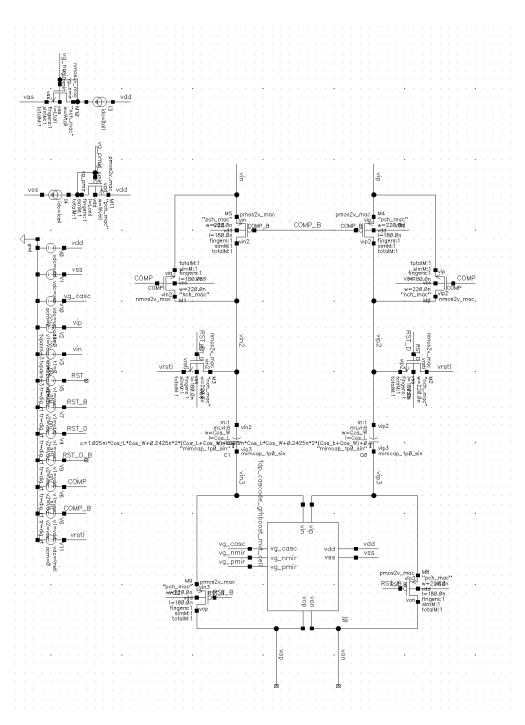

# 2.3 Finalized Pixel Design

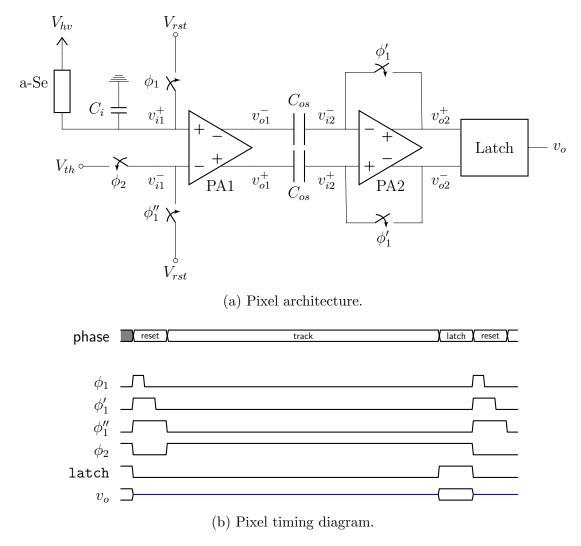

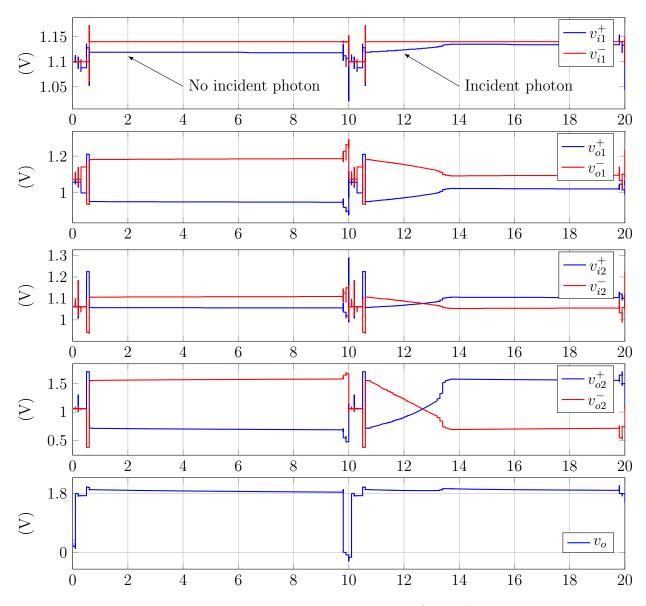

Figure ?? shows the final pixel architecture and timing of digital control signals. A few changes were made here. First, two PA stages are used, with only one set of MIMCAPs used to store the offsets of both stages. This is mainly to minimize the pixel pitch, as

(a) Intrinsic input-referred random offset of PA.

(b) Corrected input-referred random offset of PA.

Figure 2.8: Transient simulations sweep of  $W_{fac}$  in IOS testbench.

(a) Intrinsic input-referred random offset of PA.

(b) Corrected input-referred random offset of PA.

Figure 2.9: Transient simulations sweep of  $W_{fac}$  in OOS testbench.

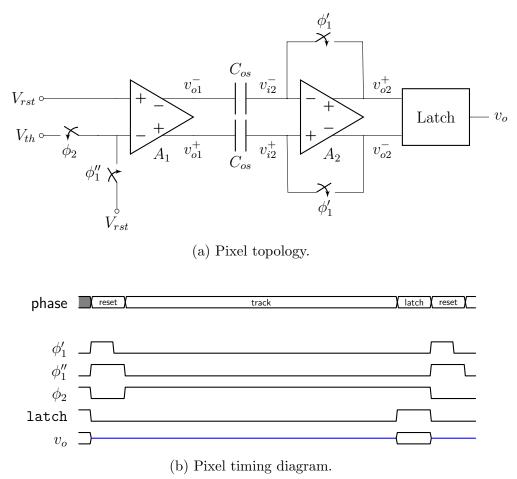

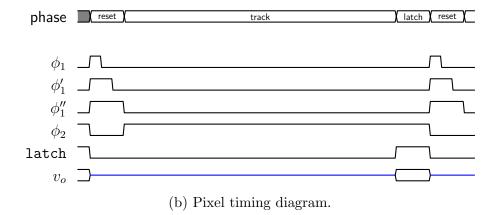

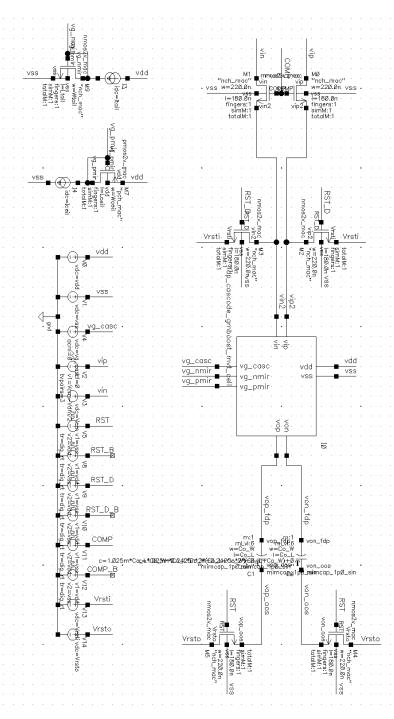

Figure 2.10: Pixel architecture and timing diagram.

MIMCAPs are relatively large. Also, current input from a-Se is integrated onto a parasitic capacitor  $C_i$  at the input node. Subsequent sections will elaborate on these changes.

Similar to previous topologies, reset takes place when  $\phi_1$  (and its delayed versions) switches are on.  $\phi_2$  connects  $V_{th}$  to the pixel and enables comparison, which is concluded after the integration period when the latch is enabled. The following steps illustrate this in detail:

#### 1. Reset:

- (a)  $\phi_1$ ,  $\phi'_1$ , and  $\phi''_1$  are all on. PA1 inputs are shorted to  $V_{rst}$ , PA2 is in unitygain feedback, and both of their offsets are stored on  $C_{os}$ . Any charge from the previous cycle that was integrated onto the integration capacitor is also discharged.

- (b)  $\phi_1$  switches off, injecting charge onto the integration node and adding an offset (both systematic and random). However, since  $\phi'_1$  is still on, this offset is also stored on  $C_{os}$  and corrected for.

- (c)  $\phi'_1$  shuts off, contributing to random offset as seen before in OOS.  $C_{os}$  now store the net offset since its right-hand side is connected to a high-impedance.

- 2. Track:  $\phi_1''$  turns off and  $\phi_2$  turns on, connecting  $V_{th}$  to the pixel and enabling comparison.

- 3. Latch: latch turns on and a digital output is resolved at  $v_o$ .

Finally, the uncertainty in the pixel's input-referred offset voltage due to random mismatch is

$$\sigma^{2}(V_{os,pix}) = \frac{1}{A_{1}^{2}} \frac{\sigma^{2}(\Delta Q_{sw})}{C_{os}} + \frac{1}{A_{1}^{2}(A_{2}+1)^{2}} \sigma^{2}(V_{os,2}) + \frac{1}{A_{1}^{2}A_{2}^{2}} \sigma^{2}(V_{os,latch}) , \qquad (2.11)$$

where  $A_i$  and  $V_{os,i}$  are the gain and input-referred offset of PA*i*, respectively, and  $\Delta Q_{sw}$  is the mismatch in charge released onto  $C_{os}$  when  $\phi'_1$  switches off.

#### Integration Capacitor