# **Data Scratchpad Prefetching for Real-time Systems**

Muhammad R. Soliman and Rodolfo Pellizzoni University of Waterloo, Canada. {mrefaat, rpellizz}@uwaterloo.ca

Abstract—In recent years, the real-time community has produced a variety of approaches targeted at managing onchip memory (scratchpads and caches) in a predictable way. However, to obtain safe Worst-Case Execution Time (WCET) bounds, such techniques generally assume that the processor is stalled while waiting to reload the content of on-chip memory; hence, they are less effective at hiding main memory latency compared to speculation-based techniques, such as hardware prefetching, that are largely used in general-purpose systems. In this work, we introduce a novel compiler-directed prefetching scheme for scratchpad memory that effectively hides the latency of main memory accesses by overlapping data transfers with the program execution. We implement and test an automated program compilation and optimization flow within the LLVM framework, and we show how to obtain improved WCET bounds through static analysis.

#### I. INTRO

The performance of computer programs can be significantly affected by main memory latency, which has largely remained similar in recent years. As a consequence, cache prefetching has been extensively researched in the architecture community [1]. Prefetching techniques incorporate hardware and/or software to hide cache miss latency by attempting to load cache lines from main memory before they are accessed by the program. The essence of these techniques is speculation of the data locality and the cache behavior, which makes them unsuitable to provide Worst-Case Execution Time (WCET) guarantees for real-time programs.

In the context of real-time systems, in recent times there has been significant attention to the management of on-chip memory. In particular, a large number of allocation schemes for scratchpad memories have been proposed in the literature; compared to caches, ScratchPad Memory (SPM) requires an explicit management of transfers from/to main memory. We note that cache memories can also be managed in a predictable manner similar to SPM, for example employing cache locking [2]. These techniques allow the derivation of tighter WCET bounds by statically determining which memory accesses target on-chip and which main memory. However, they do not solve the fundamental memory latency problem, because they generally assume that the core is stalled while the content of on-chip memory is reloaded.

To address such issue, in this paper we present a novel compiler-directed prefetching scheme that optimizes the allocation of program data in on-chip memory with the objective to minimize the WCET. Our method relies on a Direct Memory Access (DMA) controller to move data between on-chip and main memory. Compared to related work, we do not stall the program while transferring data; instead, we rely on static program analysis to determine when data is used in the program, and we prefetch it into on-chip memory ahead of its use so that the time required for the DMA transfer can be *overlapped* with the program execution. As we show in our evaluation, for certain benchmarks our solution allows

to drastically reduce the stall time due to memory latency. More in details, we provide the following contributions:

- We describe an allocation mechanism for SPM that manages DMA transfers with minimum added overhead to the program. To statically determine which accesses target the SPM, we introduce a program representation and allocation constraints based on refined code regions.

- We develop an allocation algorithm for data in scratchpad memory that takes into account the overlap between DMA transfers and program execution.

- We show how to model the proposed mechanism in the context of static WCET analysis using a standard dataflow approach for processor analysis.

- We fully implement all required code analysis, optimization and transformation steps within the LLVM compiler framework [3], and test it on a collection of benchmarks. Outside of loop bound annotations, our prototype is able to automatically compile and optimize the program without any programmer intervention.

The rest of the paper is organized as follows. We recap related work in Section II. We then introduce a motivating example in Section III. We detail the region-based program representation in Section IV, and our proposed allocation mechanism in Section V. Section VI discusses the allocation algorithm, and Section VII introduces the WCET abstraction for our prefetch mechanism. Finally, we present the compiler implementation in Section VIII and experimental results in Section IX, and provide concluding remarks in Section X.

#### II. RELATED WORK

ScratchPad Memory (SPM) management has been widely explored in the literature, both for code and data allocation. We focus on data SPM as it drew more attention in the literature due to the challenges connected to data usage analysis and optimization. Many approaches target improving the average case performance [4], [5], [6], [7], [8], [9]. Other mechanisms optimize the allocation for the WCET in realtime systems [10], [11], [12], [13]. In general, management techniques are divided between static or dynamic. Static methods partition the data memory between the SPM and the main memory and assign fixed allocation of the SPM at compile-time [6], [10]. On the other hand, dynamic methods adapt to the changing working data set of the program by moving objects between the SPM and main memory during run-time [4], [5], [13], [9], [11], [7]. Since our proposed scheme allows us to more efficiently hide the cost of data transfers, we focus on a dynamic approach.

The closest related work in the scope of dynamic methods for data SPM are [7], [8], [14], which utilize prefetching through DMA. In [7], the authors use a SPM data pipelining (SPDP) technique that utilizes Direct Memory Access (DMA) to achieve data parallelization for multiple iterations of a loop based on iteration access patterns of arrays. The work in [8] proposes a general prefetching scheme for onchip memory. It exploits the usage of DMA priorities and pipelining to prefetch arrays with high reuse to minimize

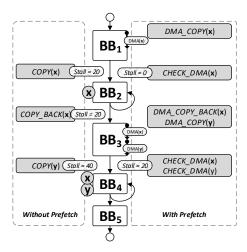

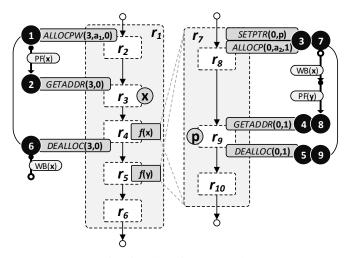

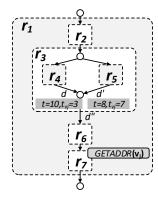

Fig. 1: Motivating Example

the energy and maximize average performance. In [14], the authors add a DMA engine to the processor to control the DMA transfers using a job queue, similarly to the mechanism proposed in our work. They also provide high level functions to manage the DMA. However, no optimized allocation scheme is discussed. Furthermore, all three discussed works target the average case rather than the worst case.

In the context of real-time systems, the closest line of work is the PRedictable Execution Model (PREM) [15], [16], [17]. Under PREM, the data and code of a task is prefetched into on-chip memory before execution, preferably using DMA. A variety of co-scheduling schemes (see for example [18], [19]) have been proposed to avoid stalling the processor by scheduling the DMA operations for one task with the execution of another task on the same core. However, we argue that such approaches suffer from three main limitations, that we seek to lift in this work. 1) Statically loading all data and code before the beginning of the program severely limits the flexibility and precision of the allocation. 2) DMA transfers cannot be overlapped with the execution of the same task, only other tasks. This makes the proposed approaches less suitable for many-core systems, where it might be preferable to execute a single task/thread on each core. 3) With the exception of [20], the proposed approaches assume manual code modification, which we find unrealistic in practice. An automated compiler toolchain is described in [20], but since it relies on profiling, it cannot guarantee WCET bounds.

# III. MOTIVATING EXAMPLE

In this section, we present an example that shows the benefit of data prefetching in scratchpad-based systems. Given a set of data *objects* used by a program, the general scratchpad allocation problem is to determine which subset of objects should be allocated in SPM to minimize the WCET of the program. Since the latency of accessing an object in the SPM is less than in main memory, we can compute the benefit in terms of WCET reduction for each object allocated in the SPM. We model the program's execution with a Control Flow Graph (CFG) where nodes represent basic blocks, i.e., straight-line pieces of code. In particular, Figure 1 shows the CFG of a program where object x is read/written in basic blocks  $BB_2$  and  $BB_4$  and object y is read in  $BB_4$ . Note that  $BB_2$  and  $BB_4$  are loops, since they include back-edges (i.e., the program execution can jump back to the beginning of the block); hence, x and y can be accessed many times. Assume that the SPM can only fit x or y. A static SPM allocation

approach will choose to allocate either x or y for the whole program execution. A dynamic SPM allocation approach will try to maximize the benefit by possibly evicting one of the two objects to fit the other during the program execution.

Let the benefit of accessing x from the SPM instead of the main memory be 100 cycles for  $BB_2$  and 10 cycles for  $BB_4$ . Similarly, the benefit for accessing y from the SPM in  $BB_4$  is 70 cycles. Let the cost to transfer x from main memory to the SPM or vice-versa be 20 cycles, and the cost for y 40 cycles. Then, for static allocation, the total benefit of allocating x is 100+10=110 cycles and the cost is 2\*20 cycles (fetch x from memory to SPM at the beginning of the program and write it back from SPM to main memory at the end). Similarly, the benefit for allocating y is 70 cycles and the cost is 20 cycles (fetch only as y is not modified, so there is not need to write it back to main memory). The optimal allocation would choose x as it has a net benefit of 70 cycles versus 50 cycles for y.

In previous approaches that adopt dynamic allocation, the program execution has to be interrupted to transfer objects either using a software loop or a DMA unit. We represent this case in the *without prefetch* box in Figure 1. In the example, x is fetched before  $BB_2$  and written back after  $BB_2$  to empty the SPM for y. Then, y is fetched before  $BB_4$ . Since x is allocated in the SPM for  $BB_2$  and y is allocated for  $BB_4$ , this results in a total benefit of 100+70=170. The program will stall before  $BB_2$  to fetch x, after  $BB_2$  to write-back x, and before  $BB_4$  to fetch y. The total cost is 20+20+40=80 cycles as the execution has to be stalled for each fetch/write-back transfer. The net benefit is 170-80=90 cycles, which is 20 cycles better than the static allocation.

However, if memory transfers can be parallelized with the execution time of the program, we next show that we can exploit the SPM more efficiently. We illustrate the prefetching sequence in the with prefetch box in Figure 1. Let us assume that the amount of execution time that can be overlapped with DMA transfers is 30 and 40 cycles for BB<sub>1</sub> and  $BB_3$ , respectively. We start prefetching x before  $BB_1$  by configuring the DMA to copy x from main memory to SPM. Then, we poll the DMA before  $BB_2$  where x is first used to ensure that the transfer has finished. Since transferring x requires less cycles than the maximum overlap for  $BB_1$  (20) versus 30), the prefetch operation for x finishes in parallel with the execution of  $BB_1$ ; hence, there is no need to stall the program before x can be accessed from the SPM in  $BB_2$ . Before  $BB_3$ , we first write-back x so that we have enough space in the SPM to then prefetch y. We propose to schedule both transfers back-to-back, e.g. using a scatter-gather DMA, in parallel with the execution of  $BB_3$ . Since the amount of overlap for  $BB_3$  is 40, the write-back for x completes after 20 cycles, leaving 20 additional cycles of overlap for the prefetch of y. Hence, by the time  $BB_4$  is reached, the CPU stalls for 40 - 20 = 20 cycles to complete prefetching y before using it in  $BB_4$ . For the described prefetching approach, the benefit is the same as the dynamic allocation. However, the cost is lower as the CPU only stalls for 20 cycles. The net benefit is 170 - 20 = 150 cycles, compared to 90 cycles without prefetching.

# IV. REGION-BASED PROGRAM REPRESENTATION

The motivating example shows that the cost of copying objects between main memory and SPM can be reduced by overlapping DMA transfers with program execution. However, to achieve a positive benefit, we also need to predict whether any given memory access targets the SPM rather than main memory. In general, programs contain branches

and function calls, making such determination possibly dependent on the execution path. To produce tight WCET bounds, a fundamental goal of our approach is to *statically determine which memory accesses are in the SPM regardless of the flow through the program*. To achieve this objective, in this section we consider a program representation based on code *regions* [21] and we add constraints on how objects can be allocated in the SPM based on regions.

We consider a program composed of multiple functions. Let  $G_f = (N, E)$  be the CFG for function f, where N is the set of nodes representing basic blocks and E is the set of edges. A Single Entry Single Exit (SESE) region is a sub-graph of the CFG that is connected to the remaining nodes of the CFG with only two edges, an entry edge and an exit edge. A region is called canonical if there is no set of regions that can be combined to construct it. Any two canonical regions are either disjoint or completely nested. The canonical regions of a program can be organized in a region tree such that the parent of a region is the closest containing region, and children of a region are all the regions immediately contained within it. Two regions are sequentially composed if the exit of one region is the entry of the following region. Note that a basic block with multiple entry/exit edges does not construct a region by itself.

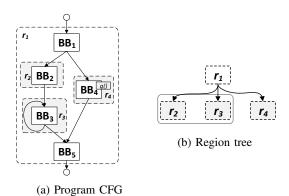

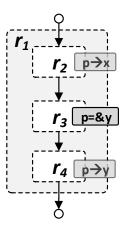

Figure 2a shows an example CFG and its canonical regions. The corresponding region tree is shown in Figure 2b. In this example, region  $r_1$  is the parent of regions  $r_2$ ,  $r_3$  and  $r_4$ . Regions  $r_2$  and  $r_3$  are sequentially composed; this is represented by a solid-line box in the figure.

In the rest of the paper, we use the term *allocation* to refer to the act of reserving a space for an object in the SPM at a given address during the execution of the program code. In our solution, we restrict the allocation of objects on a per-region basis: space for an object is reserved upon entering a region, and the object is then evicted from the SPM upon exiting the same region. This guarantees that the object is available in the SPM independently of which path the program takes through the region; as an example, if we allocate object x in  $r_1$ , then we statically know that any reference to x in  $BB_5$  will access the SPM independently of whether the program flows through  $BB_2 - BB_3$  or  $BB_4$ , or of how many iterations of the loop in  $BB_3$  are taken.

Unfortunately, the proposed region-based allocation has two limitations: 1) we cannot allocate an object in  $BB_1$  only, because  $BB_1$  is not a region; 2) in the example,  $BB_4$  performs a call to another function g(). Since the entirety of  $BB_4$  is a region, we cannot decide to allocate an object only for the call to g(), or only for the rest of the code of  $BB_4$ . To address these limitations, we propose to construct a refined region tree that allows a finer granularity of allocation.

Fig. 2: Program CFG  $G_f$  and region tree

To obtain the refined regions, we first construct a modified graph  $\bar{G}_f = (\bar{N}, \bar{E})$  from  $G_f$ , where  $\bar{N}$  is the set of basic block nodes, call nodes and merge/split nodes and  $\bar{E}$  is the set of edges such that:

- Each call to a function in G<sub>f</sub> is split into a separate call node.

- A merge/split node is inserted before/after a basic block / call node with multiple entry/exit edges.

Note that after the transformation, every node in  $\bar{G}$  that is not a merge/split node has a single entry and a single exit; hence, it is a region. We denote a region that consists of a sequence of sequentially composed regions as a *sequential region*. A sequential region is not canonical as it is constructed by combining other regions. Finally, we construct the refined region tree by considering both canonical regions and maximal sequential regions, i.e., any sequential region that encompasses a maximal sequence of sequentially composed regions. It is proved in [22] that adding maximal sequential regions to the tree still results in a unique region tree.

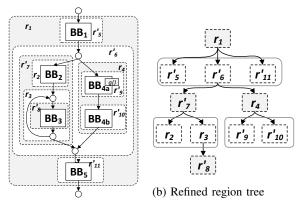

(a) Refined program CFG

Fig. 3: Refined program CFG  $\bar{G}_f$  and region tree

Figure 3 shows the refined CFG and region tree for the example in Figure 2. We added merge points before  $BB_3$ and  $BB_5$ , and split points after  $BB_1$  and  $BB_3$ . Assuming that function g() is called at the beginning of  $BB_4$ , we split  $BB_4$ to a call node  $BB_{4a}$  that contains the function call and a basic block  $BB_{4b}$  for the rest of the instructions in  $BB_4$ . In the refined region tree in Figure 3b, regions  $r_1, r_7$  and  $r_4$  are sequential regions. The regions  $r_1$  to  $r_4$  are the same as in the original region tree, while regions  $r_5'$  to  $r_{11}'$  are added as a result of the refinement process. We refer to  $r'_3$  as a call region as it contains the call node  $BB_{4a}$ . Finally, we use the term trivial region to denote any leaf of the refined region tree  $(r'_5, r'_{11}, r_2, r'_8, r'_9)$  and  $r'_{10}$  in the example); note that by definition, each trivial region must comprise either a single basic block or a single call node, i.e., trivial regions represent code segments in the program. Since allocations are based on regions, for simplicity we will omit individual nodes when representing CFGs and instead draw regions.

#### V. ALLOCATION MECHANISM

We now present our proposed allocation mechanism in details. In the rest of the paper, we assume the following:

- We focus solely on the allocation of data SPM, as it is generally more challenging. We assume a separate instruction SPM that is large enough to fit the code.

- The allocation is object-based, meaning that we do not allow allocation of parts of an object. Transformations

like tiling and pipelining could further improve the allocation, especially for small sizes of SPM. We keep this possible expansion to future work.

- We assume that the target program does not use recursion or function pointers and that local objects have fixed or bounded sizes. We argue that these assumptions conform with standard conventions for real-time applications.

- We assume that all loops in the program are bounded.

The bounds can be derived using compiler analysis, annotations or profiling.

- We use pointer analysis to determine the references of the load/store instructions. A *points-to set* is composed for each pointer reference. The size of the points-to set depends on the precision of the pointer analysis. An allocation-site abstraction is used for dynamically allocated objects to represent objects, *i.e.*, to consider a single abstract object to stand in for each run-time object allocated by the same instruction [23]. To be able to allocate a dynamically allocated object, an upper bound on the allocation size should be provided at compile-time.

- For simplicity, we consider a system comprising a single core running one program. However, the proposed method could be extended to a multicore system supporting a predictable arbitration for main memory as long as each core is provided with private or partitioned SPM.

As discussed in the motivating example, to efficiently manage the dynamic allocation of multiple objects we require a DMA unit capable of queuing multiple operations. In general, many commercial DMA controllers with scatter-gather functionality support such requirement, albeit the complexity of managing the DMA controller in software and checking whether individual operations have been completed could increase with the number of transfers. As a proof of concept, we based our implementation on a dedicated unit, which we call the *SPM controller*; we reserve implementation on a COTS platform as future work <sup>1</sup>.

Our proposed mechanism works by inserting allocation commands in the code of the program, which are then executed by the SPM controller. The process of allocating an object starts with reserving space in the SPM and prefetching the object from main memory if necessary (ALLOC command). Then, once the prefetch operation is complete, the SPM address is read and passed to the memory references that access the object (GETADDR command). Finally, the object is evicted from the SPM and written back to main memory if necessary (DEALLOC command). As discussed in Section IV, we restrict object allocation based on regions; hence, the ALLOC command is always inserted at the beginning of a region, and the corresponding **DEALLOC** command at the end of the same region. In the rest of the section, we first detail the operation of the SPM controller, followed by the semantic of the allocation commands. Finally, we provide a comprehensive allocation example.

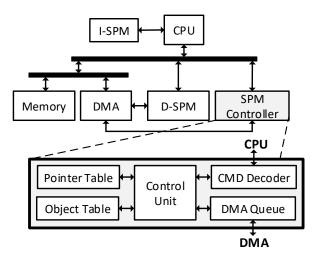

#### A. SPM controller

Figure 4 shows the proposed SPM controller and its connections to an SPM-based system. There is a separate instruction SPM (I-SPM) that is assumed to fit the code of the program. The data SPM (D-SPM) is managed by the SPM

Fig. 4: SPM-based System

controller. Since the processor must be able to access the SPM directly, the SPM is assigned an address range distinct from main memory. The SPM controller is also a memory mapped unit, since the CPU sends allocation commands to the SPM controller by reading/writing to its address range. The system incorporates a DMA unit for memory transfers. The D-SPM is assumed to be dual-ports, which means that access to the SPM by the CPU and transferring data between SPM and main memory using DMA can occur simultaneously. The proposed allocation method and WCET analysis can be applied for single-port SPM, but this will offer less opportunity to overlap the memory transfers. The DMA is connected to a shared bus with the main memory. This bus can be used by either the CPU or the DMA. To efficiently support the parallization of memory transfers with the execution time, the DMA is designed to work in transparent mode: it transfers an object only when the CPU is not using the main memory. Whenever the CPU requests the memory bus, the DMA yields to the request and stalls any ongoing transfer until the memory bus is released.

The SPM controller consists of *command decoder*, *object table*, *pointer table*, *DMA queue* and *control unit* as shown in Figure 4. As discussed, allocation commands are encoded as load/store instructions to the SPM controller. So, the command decoder reads the address and the data of the memory operation and decodes them into one of the allocation commands; the control unit then executes the command using the object table, the pointer table and the DMA queue.

The object table tracks the status of allocated objects in the SPM. The entry of the object table contains the main memory address (MM\_ADDR), the size of the object (SIZE), the SPM address (SPM\_ADDR) and allocation flags. The flags reflects the status of the object:

A (A)llocated in the SPM

PF\_OP (P)re(F)etching (OP)eration has been scheduled WB\_OP (W)rite-(B)ack (OP)eration has been scheduled WB (W)rite-(B)ack when de-allocated if used

U (U)sed in the SPM

USERS number of current users of the object

USERS field records the number of allocations that have issued an ALLOC command for the object and still using it, i.e., the corresponding DEALLOC has not been reached. It is incremented by ALLOC and decremented by DEALLOC. We show an example for the usage of this flag in Section V-C. The DMA is configured with source address, size and

<sup>&</sup>lt;sup>1</sup>For example, the Freescale MPC5777M SoC used in previous work [16] includes both SPM memory and a dedicated I/O processor that could be used to implement the described management functionalities.

a destination address extracted from an entry in the object table. DMA operations are scheduled in the DMA queue that allows scheduling multiple DMA transfers and executing them in FIFO order.

The pointer table is used to disambiguate pointers during run time. An entry in the pointer table consists of the main memory address (MM\_ADDR) of a pointer, flag (ALIASED) and a reference to an entry in the object table (OBJ\_TBL\_IDX). If MM\_ADDR aliases with the main memory address range of an object in the object table, the flag ALIASED is set and the index of the aliased object is stored in OBJ\_TBL\_IDX.

#### B. Allocation Commands

Commands (ALLOC/ DEALLOC/ GETADDR) manage the allocation of objects/pointers in the SPM. Table commands (SETMM/ SETSIZE/ SETPTR) are used to set the object and pointer tables in the SPM controller.

Two commands, **SETMM** and **SETSIZE**, set the main memory address and the size of an object in the entry *OBJ\_TBL\_IDX* in the object table:

# SETMM OBJ\_TBL\_IDX, MEM\_ADDR SETSIZE OBJ\_TBL\_IDX, SIZE

These commands are used to initialize the object table, add the information of dynamically-allocated objects or change the set of objects tracked by the table during run-time.

A pointer resolution command **SETPTR** is required for pointers:

#### SETPTR PTR\_TBL\_IDX, MEM\_ADDR

This command configures the entry PTR\_TBL\_IDX in the pointer table with memory address MEM\_ADDR. This memory address is compared with the valid entries of the object table to find the entry of the pointee object. If the pointee is found, ALIASED flag is set and the table index of the object is stored in OBJ\_TBL\_IDX. All the allocation commands on pointers check the pointer entry for the aliasing object to use in allocation. Alias checking can be implemented in one cycle using a one-shot comparator or over multiple cycles comparing one entry at a time. If the number of entries in the object table is large, an alias set that specifies which objects that can alias with the pointer can be used to reduce the number of comparisons. For the sake of simplicity of analysis, we assume in this paper a one-cycle implementation.

Next, we present the allocation commands. An allocation command can be issued for an object or a pointer. However, an object entry  $OBJ\_TBL\_IDX$  is required for both cases. We use  $TBL\_IDX$  to refer to an entry in the object or pointer table based on a flag PTR. If PTR = 0,  $OBJ\_TBL\_IDX = TBL\_IDX$ . If PTR = 1,  $PTR\_TBL\_IDX = TBL\_IDX$  and  $OBJ\_TBL\_IDX$  is obtained from the pointer entry in the pointer table.

#### ALLOCXX TBL\_IDX, MEM\_ADDR, PTR

# DEALLOC TBL\_IDX, PTR GETADDR TBL\_IDX, PTR

**ALLOC***XX* command reserves the space in the SPM at *MEM\_ADDR* and schedules a DMA transfer if necessary. There are four versions of **ALLOC***XX* command according to the flags (*XX*): **ALLOC**, **ALLOC***P*, **ALLOC***W*, **ALLOC***PW*. The *P* flag directs the controller to prefetch the object from the main memory. The SPM controller will

schedule a prefetch transfer for the object and set *PF\_OP* flag in the object entry. If *P* flag is not used, the object is allocated directly and *A* flag is set. Otherwise, *A* flag is set once the prefetch transfer completes. The *W* flag sets the *WB* flag in the object entry to direct the controller to copy back the object to the main memory when de-allocated. *P* flag is used in two cases: 1) if, during the execution of the region where the object is allocated, the current value of the object is read or 2) the object is partially written, *e.g.* writing some elements of an array. *W* flag is used if the object is modified, so that the main memory is updated with the new values after de-allocating the object. Note that for local objects defined in a function, there is no need to prefetch the object before its first use in the function or write-back the object after its last use in the function.

**DEALLOC** command de-allocates the object/pointer. If the WB and U flags are set in the object entry, the controller will schedule a write-back transfer, set  $WB\_OP$  flag and reset A flag. Otherwise, the object will be de-allocated by simply resetting A flag.

GETADDR command returns the current address of the object/pointer. For a pointer, if ALIASED flag in the pointer entry is not set,  $MM_ADDR$  is returned, otherwise the address is checked for the object in OBJ\_ADDR\_TBL. If PF\_OP or  $WB\_OP$  flag is set for the object, the controller stalls until the DMA completes transferring the object. If no transfer is scheduled or after the transfer finishes, the controller returns SPM\_ADDR if A flag is set and MM\_ADDR otherwise. GETADDR command is only added before the first use of the object after an allocation/de-allocation. The address returned by the command is then applied for all the next uses until another allocation/de-allocation occurs. This process is compiler-automated and does not require per-access address translation from main memory to SPM addresses, as in related work [11]; hence, we do not add extra overhead to the critical path of the processor. For pointers, **SETPTR** and **GETADDR** commands are required if the pointer can alias with the content of the SPM even if the pointer itself is not allocated.

If a prefetch transfer has been scheduled and a **DEALLOC** command is issued for the object to be prefetched, the transfer is canceled as the object is not needed anymore. Also, if a write-back transfer has been scheduled for an object and it was followed by **ALLOCXX** for the same object, the transfer is canceled if the object is allocated to the same SPM address, otherwise the transfer is not canceled. This is particularly important for allocations within loops, when the object can be allocated to the same address over multiple iterations.

#### C. Example

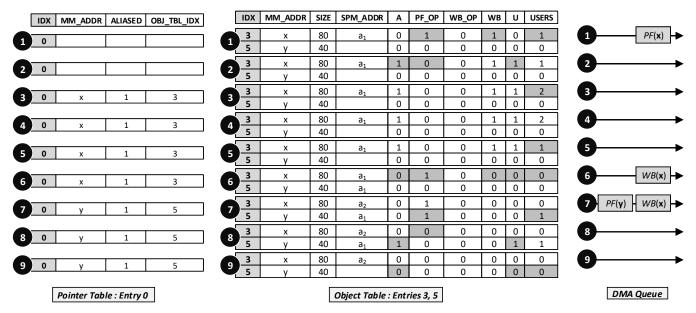

Figures 5, 6 depict an example for the allocation process. There are two objects x and y corresponding to entries 3 and 5 in the object table. Also, a pointer p is an argument to function f and uses entry 0 in the pointer table. Figure 5 shows the CFG of two functions where  $r_1$ - $r_{10}$  represent regions. x is read/written in  $r_3$ , and the pointee of p is read in  $r_9$ . Note that function f, comprising regions  $r_7$  to  $r_{10}$ , is called from two different call regions,  $r_4$  with p = &x and  $r_5$  with p = &y. In the example, we assume that x is allocated at address  $a_1$  in the SPM in sequentially composed regions  $r_2$ ,  $r_3$  and  $r_4$ . The argument of function f is allocated at a different address  $a_2$  inside the function.

We use program points **1** to **2** to follow the allocation process. Entries 3 and 5 of the object table, Entry 0 of the pointer table and the DMA queue are traced in Figure 6 for

Fig. 5: Allocation Example

these program points. At  $\mathbf{0}$ , x is allocated to address  $a_1$  with P and W flags. In the object table,  $PF\_OP$  is set to indicate x is being prefetched, WB is set to indicate a write-back when de-allocated, and *USERS* is incremented. A prefetch transfer PF(x) is scheduled in the DMA queue. At **2**, **GETADDR** checks entry 3 for the address; as PF(x) did not finish at this point, the CPU is stalled. When the prefetch finishes, x is allocated, PF\_OP is reset, A is set; and the CPU continues execution. Also, U is set to mark x as used in the SPM. In  $r_4$ , function f is called. At  $\Theta$ , **SETPTR**(0,p) sets the address for p in entry 0 of the pointer table and apply alias checking with the object table. As p aliases with x at this point, flag ALIASED is set and OBJ\_TBL\_IDX refers to entry 3 in the object table. An allocation of p to  $a_2$  is issued; however, its pointee x is already in the SPM at address  $a_1$ . So, no new allocation at  $a_2$  is performed, and *USERS* is incremented in entry 3 to indicate that two ALLOC commands (users) have been executed for x. **GETADDR** at  $\Phi$  returns  $a_1$ . When p is deallocated at **6**, *USERS* is decremented in entry 3 of the object table. However, x is not evicted as there is another user for it. When x is deallocated at  $\mathbf{G}$ , x is evicted as this is the last user of x in the SPM. As WB and U are set, a write-back is scheduled for x. f is called again in  $r_5$ . The same process to set entry 0 in the pointer table at point ? is done with the address of y and OBJ\_TBL\_IDX refers to entry 5 in the object table. Then, p is also allocated to  $a_2$ with P flag. So, a prefetch is scheduled for y. Before p is used in  $r_9$ , **GETADDR** is executed. At this point the writeback transfer of x is done and the prefetch for y is partially completed. The CPU stalls till y is completely prefetched, then U flag is set in entry 5, address  $a_2$  is returned, and the execution continues at  $\odot$ . Finally, p is deallocated at  $\odot$ which evicts y. No write-back is needed as WB flag is not set.

An essential observation is that the state of the SPM and the sequence of DMA operations in function f depend on which region calls f: if f is called from  $r_4$ , then x is already available in SPM at address  $a_1$ , and the allocation of p to  $a_2$  is not used. If instead f is called from  $r_5$ , p is allocated to  $a_2$  and the object p must be prefetched from main memory. Therefore, let p be the *context* under which a region executes, i.e., the sequence of call regions starting from the main function; note that since the main function of the program is not called by any other function, the only valid context for regions in the main is p = p. We denote the

execution of a region  $r_n$  in a context  $\sigma$  as  $r_n^{\sigma}$ , which we call a region-context pair. Then, allocation decisions, which involve adding allocation commands in the code, must be based on regions, but the state of the SPM and DMA operations, which are needed for WCET estimation, depend on region-context pairs. Intuitively, this is equivalent to considering multiple copies of each region  $r_n$ , one for each context in which  $r_n$  can execute.

#### VI. ALLOCATION PROBLEM

We now discuss how to determine a set of allocations for the entire program with the objective to minimize the program's WCET. For the remaining of the section, we let  $S_{SPM}$  to denote the size of the SPM.  $V = \{v_1, \dots, v_j, \dots\}$  is the set of allocatable objects, where  $S(v_j)$  denotes the size of object  $v_j$ . We let  $R = \{r_1, \dots, r_n, \dots\}$  be the set of program regions across all functions. Without loss of generality, we assume that region indexes are topologically ordered, so that each parent region has smaller index than its children, each call region has smaller index than the regions in the called function, and sequentially composed regions have sequential indexes; this is also the order used in Figure 5. Note that such topological order must exist since the refined region tree for each function is unique, and furthermore the call graph has no loops due to the absence of recursion. To define the relation between region-context pairs we introduce a parent function  $\mathcal{D}(r_n^{\sigma})$  for a region-context  $r_n^{\sigma}$  in function f as follows: if  $r_n$  is the root region of the refined region tree for f, then  $\mathcal{D}(r_n^{\sigma}) = r_m^{\sigma'}$ , where  $r_m^{\sigma'}$  is the region-context that calls f in context  $\sigma$ . Otherwise,  $\mathcal{D}(r_n^{\sigma}) = r_m^{\sigma}$ , where  $r_m$  is the parent region of  $r_n$ . As an example based on Figure 5, assume while for example  $\mathcal{D}(r_8^{\sigma \cup r_4}) = r_7^{\sigma \cup r_4}$ . Finally, to generalize the problem for the usage of pointers, let  $P = \{p_1, \dots, p_k, \dots\}$ be the set of pointers in the program. As the pointee of the pointer can change based on the program flow, we define  $\chi_{r_n^{\sigma}}(p_k)$  as the points-to set for pointer  $p_k$  in region-context  $r_n^{\sigma}$ . For simplicity, we refer to the allocation of the pointee of pointer as the allocation of the pointer. We define  $S_{r_n^{\sigma}}(p_k)$ as the size of  $p_k$  in region-context  $r_n^{\sigma}$  which is computed as:

$$S_{r_n^{\sigma}}(p_k) = \max_{v \in \chi_{r_n^{\sigma}}(p_k)} S(v)$$

Note that the pointee of  $p_k$  can be a global, local objects from the set of objects in V or a dynamically allocated object. In case of dynamic allocation, v refers to a dynamic allocation site in the program.

We begin by formalizing the conditions under which a set of allocations are feasible as a satisfiability problem. This is similar to a multiple knapsack problem where regions are knapsacks (available space in SPM), except that we add additional constraints to model the relation between regions. Remember that to allocate an object  $v_j$  (pointer  $p_k$ ) in a region  $r_n$ , we have to assign an address in the SPM to the object (pointer). Hence, an allocation solution is represented by an assignment to the following decision variables over all regions  $r_n \in R$  and all objects  $v_j \in V$  (pointers  $p_k \in P$ ):

$$alloc_{r_n}^{v_j} = \begin{cases} 1, & \text{if } v_j \text{ is allocated in } r_n \\ 0, & \text{otherwise} \end{cases}$$

$$assign_{r_n}^{v_j} = \text{address assigned to } v_j \text{ in } r_n$$

$$alloc_{r_n}^{p_k} = \begin{cases} 1, & \text{if } p_k \text{ is allocated in } r_n \\ 0, & \text{otherwise} \end{cases}$$

Fig. 6: SPM Controller State for Allocation Example in Figure 5

$assign_{r_n}^{p_k}$  = address assigned to  $p_k$  in  $r_n$

An allocation solution is feasible if the allocated objects fit in the SPM at any possible program point. As discussed in Section V-C, the state of the SPM depends on the context under which a region is executed. Hence, we introduce new helper variables to define the availability of an object  $v_j$  (pointer  $p_k$ ) in a region-context  $r_n^{\sigma}$ :

$$avail_{r_n^{\sigma}}^{v_j} = \begin{cases} 1, & \text{if } v_j \text{ is available in SPM for execution of } r_n^{\sigma} \\ 0, & \text{otherwise} \end{cases}$$

$address_{r_n^{\sigma}}^{v_j}$  = address of  $v_j$  in the SPM during execution of

$$avail_{r_n^{\sigma}}^{p_k} = \begin{cases} 1, & \text{if } p_k \text{ is available in SPM for execution of } r_n^{\sigma} \\ 0, & \text{otherwise} \end{cases}$$

$address_{r_n}^{p_k} = address \text{ of } p_k \text{ in the SPM during execution of } r_n^{\sigma}$

We can determine the value of the helper variables based on the allocation. We first discuss the basic constraints assuming that the points-to information is not available. In this case, allocation of a pointer is handled as an allocation of an object. After that, we discuss how the constraints can be modified to consider aliasing between objects and pointers.

1) Basic Constraints: We present a set of necessary and sufficient constraints for an allocation problem in which points-to information is not available.

$$\forall v_j, r_n^{\sigma} : alloc_{r_n}^{v_j} \vee avail_{\mathscr{O}(r_n^{\sigma})}^{v_j} \Leftrightarrow avail_{r_n^{\sigma}}^{v_j}. \tag{1}$$

$$\forall p_k, r_n^{\sigma}: alloc_{r_n}^{p_k} \lor avail_{\mathscr{D}(r_n^{\sigma})}^{p_k} \Leftrightarrow avail_{r_n^{\sigma}}^{p_k}. \tag{2}$$

Equation 1 (2) simply states that  $v_j$   $(p_k)$  is available in the SPM during the execution of  $r_n^{\sigma}$  if either  $v_j$   $(p_k)$  is allocated in  $r_n$ , or if  $v_j$   $(p_k)$  was already available in the SPM during the execution of the parent region-context pair.

$$\forall v_j, r_n^{\sigma} : avail_{\wp(r_n^{\sigma})}^{v_j} \Rightarrow address_{r_n^{\sigma}}^{v_j} = address_{\wp(r_n^{\sigma})}^{v_j}.$$

(3)

$$\forall p_k, r_n^{\sigma} : avail_{\wp(r_{\sigma}^{\sigma})}^{p_k} \Rightarrow address_{r_{\sigma}^{\sigma}}^{p_k} = address_{\wp(r_{\sigma}^{\sigma})}^{p_k}.$$

(4)

$$\forall v_j, r_n^{\sigma} : \neg avail_{\wp(r_n^{\sigma})}^{v_j} \land alloc_{r_n}^{v_j} \Rightarrow address_{r_n^{\sigma}}^{v_j} = assign_{r_n}^{v_j}.$$

(5)

$$\forall p_k, r_n^{\sigma} : \neg avail_{\wp(r_n^{\sigma})}^{p_k} \land alloc_{r_n}^{p_k} \Rightarrow address_{r_n^{\sigma}}^{p_k} = assign_{r_n}^{p_k}.$$

(6)

Equations 3, 5 (4, 6) specify the address in the SPM for objects (pointers). If the object (pointer) was already available in the parent region-context, then the address is the same. Otherwise, if the object (pointer) is allocated in  $r_n$ , then the address is the one assigned by the allocation.

Finally, given the object (pointer) availability and address for each region-context pair, we can express the feasibility conditions for the allocation problem.

$$\forall v_j, r_n^{\sigma} : avail_{r_n^{\sigma}}^{v_j} \Rightarrow address_{r_n^{\sigma}}^{v_j} + S(v_j) \leq S_{SPM}.$$

(7)

$$\forall p_k, r_n^{\sigma} : avail_{r_n^{\sigma}}^{p_k} \Rightarrow address_{r_n^{\sigma}}^{p_k} + S_{r_n^{\sigma}}(p_k) \leq S_{SPM}.$$

(8)

$$\forall v_{j}, v_{k}, r_{n}^{\sigma}, j \neq k : (avail_{r_{n}^{\sigma}}^{v_{j}} \wedge avail_{r_{n}^{\sigma}}^{v_{k}}) \Rightarrow$$

$$(address_{r_{n}^{\sigma}}^{v_{j}} + S(v_{j}) \leq address_{r_{n}^{\sigma}}^{v_{k}}) \vee$$

$$(address_{r_{n}^{\sigma}}^{v_{k}} + S(v_{k}) \leq address_{r_{n}^{\sigma}}^{v_{j}})$$

$$(9)$$

$$\begin{aligned} \forall p_{j}, p_{k}, r_{n}^{\sigma}, j \neq k : (avail_{r_{n}^{\sigma}}^{p_{j}} \wedge avail_{r_{n}^{\sigma}}^{p_{k}}) \Rightarrow \\ (address_{r_{n}^{\sigma}}^{p_{j}} + S_{r_{n}^{\sigma}}(p_{j}) \leq address_{r_{n}^{\sigma}}^{p_{k}}) \vee \\ (address_{r_{n}^{\sigma}}^{p_{k}} + S_{r_{n}^{\sigma}}(p_{k}) \leq address_{r_{n}^{\sigma}}^{p_{j}}) \end{aligned} \tag{10}$$

$$\forall v_{j}, p_{k}, r_{n}^{\sigma} : (avail_{r_{n}^{\sigma}}^{v_{j}} \wedge avail_{r_{n}^{\sigma}}^{p_{k}}) \Rightarrow$$

$$(address_{r_{n}^{\sigma}}^{v_{j}} + S(v_{j}) \leq address_{r_{n}^{\sigma}}^{p_{k}}) \vee$$

$$(address_{r_{n}^{\sigma}}^{p_{k}} + S_{r_{n}^{\sigma}}(v_{k}) \leq address_{r_{n}^{\sigma}}^{v_{j}})$$

$$(11)$$

Equation 7 (8) states that if  $v_j$  ( $p_k$ ) is in the SPM during the execution of  $r_n^{\sigma}$ , then it must fit within the SPM size. Equations 9 to 11 state that if two objects/pointers are in the SPM during the execution of  $r_n^{\sigma}$ , then their addresses must not overlap. Note that the size for a pointer is dependent on the region-context pair. Giving a points-to set  $\chi_{r_n^{\sigma}}(p_k)$ , the size required for allocating  $p_k$  in  $r_n^{\sigma}$  is the maximum size of all objects in the points-to set.

Fig. 7: Example of Pointer Definition

$$\forall p_k, r_n^{\sigma} : def_{r_n^{\sigma}}^{p_k} \Rightarrow \neg alloc_{r_n}^{p_k} \tag{12}$$

The constraint in Equation 12 states that the allocation of pointer  $p_k$  is not allowed in  $r_n$  ( $alloc_n^{p_k} = 0$ ) if  $p_k$  is defined in  $r_n$ , i.e.,  $p_k$  can change its reference in the region. This constraint is required for correctness of execution and analysis. This case is depicted in Figure 7 where pointer p is defined in region  $r_3$  to point to p rather than p. Hence, p can be allocated in p and p while p allow p and p allocation of p in p or p will result in pointer invalidation as any reference to p after its definition in p should point to p not p.

As long as Equations 7 to 11 are satisfied for a given solution in all region-context pairs, all objects fit in the SPM; hence, the allocation problem can be feasibly implemented. To do so, we next discuss how to determine the list of commands (ALLOC/DEALLOC/GETADDR) that must be added to each region. For a region  $r_n$  that is not sequentially composed, an ALLOC is inserted at the beginning of the region and a DEALLOC at the end of the region.

In the case of sequential regions, to reduce the number of DMA operations, we note the following: if the same object  $v_j$  is allocated in two sequentially composed regions  $r_p$  and  $r_q$  with the same assigned address, then there is no need to **DEALLOC**  $v_j$  at the end of  $r_p$  and **ALLOC** it again at the beginning of  $r_q$ . Hence, we consider the maximal sequence of sequentially composed regions  $r_p, \ldots, r_q$  such that for every region  $r_n$  in the sequence:  $alloc_{r_n}^{v_j} = 1$  and the address  $assign_{r_n}^{v_j}$  assigned to  $v_j$  is the same. We then add the **ALLOC** command at the beginning of  $r_p$  and the **DEALLOC** command are set as discussed in Section V-B based on the usage throughout the whole sequence. The same procedure applies for a pointer  $p_k$  allocated in a sequence of sequentially composed regions.

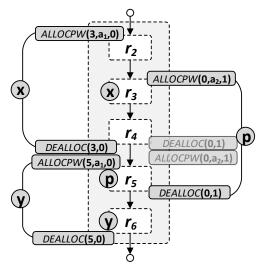

Also, we note the following for object  $v_j$  and pointer  $p_k$  such that  $v_j \in \chi_{r_0^n}$ : if object  $v_j$  and pointer  $p_k$  are allocated in overlapped sequence of sequentially composed regions, DMA operations on the pointer are inserted to re-locate the pointee to avoid pointer invalidation. The example shown in Figure 8 shows the case where object x is allocated to address  $a_1$  in  $r_2, r_3$  and  $r_4$ , pointer p is allocated to address  $a_2$  in  $r_3, r_4$  and  $r_5$ , and object y is allocated to  $a_1$  in  $a_2$  in  $a_3$  and  $a_4$  in the SPM when  $a_4$  is allocated in  $a_4$  in the SPM when  $a_4$  is allocated in  $a_4$  and  $a_5$  in the SPM when  $a_5$  is allocated in  $a_5$  and  $a_5$  will not be copied to address  $a_5$ . However, the copy of  $a_4$  and  $a_5$  should be written-back after  $a_5$

Fig. 8: Allocation Overlap Example

to allocate y to  $a_1$ . Using p in  $r_5$  with the assumption that x is in the SPM will result in a conflict. So, a re-location must be guaranteed after  $r_4$ , so that the copy of x is moved to  $a_2$  before y is fetched to  $a_1$ . Note that the relocation commands will cancel each other if p is not pointing to x.

*Example*: refer to the example in Figure 5, where p is allocated in two regions in sequence  $(r_8 \text{ and } r_9)$ . **ALLOC** is inserted before  $r_8$  and **DEALLOC** is inserted after  $r_9$ . P flag is set in **ALLOC** even though x is not used in  $r_8$ , but it is read in  $r_9$ . Similarly, W is not set as x is not modified in neither  $r_8$  nor  $r_9$ .

Finally, to compute the WCET for the program, we need to determine whether an **ALLOC/DEALLOC** command triggers a DMA operation; this again depends on the context  $\sigma$  in which a given region  $r_n$  is executed, as demonstrated by the example in Section V-C. As in Equation 3, we know that the **ALLOC** will be canceled if  $v_j$  was already available in the parent region-context; hence, for a region  $r_n$  that performs an **ALLOC** on  $v_j$  and a context  $\sigma$ , the **ALLOC** generates a DMA prefetch on  $v_j$  only if both the P flag in the **ALLOC** is set and  $avail_{\wp(r_n^{\sigma})}^{v_j} = 0$  (similarly for DEALLOC, a DMA operation is generated if the W flag is set and  $avail_{\wp(r_n^{\sigma})}^{v_j} = 0$ ).

2) Aliasing Constraints: The feasibility problem can be relaxed using the points-to information of each pointer. Points-to information are derived from a must-may alias analysis. We consider the must-alias points-to sets with object  $v_j$  and pointer  $p_k$  such that  $\chi_{r_n^{\sigma}}(p_k) = \{v_j\}$ ; which is a common case with passing by reference in functions. In this case, the allocation of either  $v_j$  or  $p_k$  in region-context  $r_n^{\sigma}$  means that both  $v_j$  and  $p_k$  are available in the SPM in this region-context. The constraints can be extended if there are multiple pointers that only point to  $v_j$  in a region-context.

$$alloc_{r_n}^{v_j} \lor alloc_{r_n}^{p_k} \lor avail_{\wp(r_n^{\sigma})}^{v_j} \lor avail_{\wp(r_n^{\sigma})}^{v_j} \Leftrightarrow avail_{r_n^{\sigma}}^{v_j}.$$

(13)

$$alloc_{r_n}^{v_j} \lor alloc_{r_n}^{p_k} \lor avail_{\mathscr{D}(r_n^{\sigma})}^{v_j} \lor avail_{\mathscr{D}(r_n^{\sigma})}^{p_k} \Leftrightarrow avail_{r_n^{\sigma}}^{p_k}.$$

(14)

Equations 13, 14 replace Equation 1, 2 and state that  $v_j$  and  $p_k$  are available in the SPM during the execution of  $r_n^{\sigma}$  if  $v_j$  or  $p_k$  is allocated in  $r_n$ , or if  $v_j$  or  $p_k$  was already available in the SPM during the execution of the parent region-context pair. Note that in Equation 14,  $v_j$  can be available in the parent region-context  $\mathcal{D}(r_n^{\sigma})$  while  $p_k$  is not available in it

if  $p_k$  changes its reference in the children of  $\mathcal{D}(r_n^\sigma)$ , *i.e.*,  $\chi_{r_n^\sigma}(p_k) \neq \{v_j\}$ . In that case, Equation 14 is not applicable to  $\mathcal{D}(r_n^\sigma)$  and  $alloc_{\mathcal{D}(r_n^\sigma)}^{p_k} = 0$  according to Equation 12.

$$avail_{\wp(r_n^{\sigma})}^{\nu_j} \Rightarrow address_{r_n^{\sigma}}^{p_k} = address_{\wp(r_n^{\sigma})}^{\nu_j}.$$

(15)

$$\neg avail_{\mathscr{O}(r_n^{\sigma})}^{v_j} \wedge alloc_{r_n}^{v_j} \wedge \neg alloc_{r_n}^{p_k} \Rightarrow \\ address_{r_{\sigma}}^{v_j} = address_{r_{\sigma}}^{p_k} = assign_{r_n}^{v_j}.$$

(16)

$$\neg avail_{\mathscr{O}(r_n^{\sigma})}^{v_j} \wedge alloc_{r_n}^{p_k} \wedge \neg alloc_{r_n}^{v_j} \Rightarrow

address_{r_n^{\sigma}}^{p_k} = address_{r_n^{\sigma}}^{v_j} = assign_{r_n}^{p_k}.$$

(17)

$$\neg avail_{\wp(r_{n}^{\sigma})}^{v_{j}} \wedge alloc_{r_{n}}^{v_{j}} \wedge alloc_{r_{n}}^{p_{k}} \Rightarrow \\ (address_{r_{n}^{\sigma}}^{v_{j}}, address_{r_{n}^{\sigma}}^{v_{j}}) = \gamma(assign_{r_{n}}^{v_{j}}, assign_{r_{n}}^{p_{k}}).$$

$$(18)$$

Equation 3 still applies for  $v_j$  as the availability in the parent dominates any allocation in the region. However, the address  $p_k$  inherits the address of the  $v_j$  if it is available in its parent as in Equation 15. If  $v_j$  is not available in the parent, there are two cases:

Equations 16,17 state that if only  $v_j$  or  $p_k$  is allocated, the address of  $v_j$  and  $p_k$  is the assigned address of the allocated one.

Equation 18 state that if both  $v_j$  and  $p_k$  are allocated, the assigned address for each of them to be determined with an arbitrary function  $\gamma$  that depends on how the allocation is implemented. In this work, we use  $\gamma(assign_{r_n}^{v_j}, assign_{r_n}^{p_k}) = assign_{r_n}^{v_j}$  as we consider relocation of the pointer as we illustrated before in the example shown in Figure 8.

Example: refer to the example in Figure 5, where p is allocated with assigned address  $a_2$  in  $r_8$ . For context  $\sigma \cup r_5$ , we have  $avail_{r_7^{\sigma \cup r_5}}^p = avail_{r_7^{\sigma \cup r_5}}^y = 0$ , since  $\chi_{r_7^{\sigma \cup r_5}}(p) = \{y\}$  and y is not available in  $r_5^{\sigma}$ , the parent of  $r_7^{\sigma \cup r_5}$ . Hence, we also have  $address_{r_8^{\sigma \cup r_5}}^p = address_{r_8^{\sigma \cup r_5}}^y = a_2$ . However, for context  $\sigma \cup r_4$  we obtain  $avail_{r_7^{\sigma \cup r_4}}^p = avail_{r_7^{\sigma \cup r_4}}^x = 1$ , since  $\chi_{r_7^{\sigma \cup r_4}}(p) = \{x\}$  and x is available in  $r_4^{\sigma}$ . So, we get  $address_{r_7^{\sigma \cup r_4}}^p = address_{r_7^{\sigma \cup r_4}}^p = address_{r_7^{\sigma \cup r_4}}^p = a_1$ .

The constraints for SPM size are the same as in Equations 7, 8. Equations 10, 11 for address overlap are not applied for must alias cases. That is, if  $\chi_{r_n^{\sigma}}(p_{k1}) = \chi_{r_n^{\sigma}}(p_{k2}) = \{v_j\}$ , then their address ranges match  $address_{r_n^{\sigma}}^{p_{k1}} = address_{r_n^{\sigma}}^{p_{k2}} = address_{r_n^{\sigma}}^{v_j}$ . So, Equations 11, 10 is not applied between  $p_{k1}, p_{k2}, v_j$  for region-context  $r_n^{\sigma}$ .

We illustrated the possible aliasing constraints for one pointer and one object. Another set of constraints can be derived for aliasing pointers or pointers with multiple pointees in their points-to set. We do not detail these constraints as they exploit a may-alias which means the constraints do not represent necessity.

#### A. WCET Optimization

For a given allocation solution  $\{alloc_{r_n}^{v_j}, assign_{r_n}^{v_j}, alloc_{r_n}^{p_k}, assign_{r_n}^{p_k}|\forall v_j, p_k, r_n\}$ , the described procedure determines the set of objects available in the SPM and the set of DMA operations for each region-context  $r_n^{\sigma}$ . Assuming that bounds on the time required for SPM and main memory accesses are known, this allows us to determine the benefit (WCET reduction) for every

trivial region in context  $\sigma$ , as well as the length of DMA operations. For a dynamic allocation approach without prefetch, the length of DMA operations could simply be summed to the execution time of the corresponding region, since DMA operations stall the core.

However, for our proposed approach with prefetching, the cost of DMA operations depend on the overlap: since DMA works in transparent mode, for a trivial region the maximum amount of overlap is equal to the execution time of its code minus the time that the CPU accesses main memory directly. Furthermore, since the length of DMA operations is generally longer than the execution of a trivial region, the total overlap depends on the program flow. Therefore, we compute the amount of overlap as part of an integrated WCET analysis, which we present in Section VII. We solve the allocation problem by adopting a heuristic approach that first searches for feasible allocation solutions, and then run the WCET analysis on feasible solutions to determine their fitness; we discuss it next in Section VI-B.

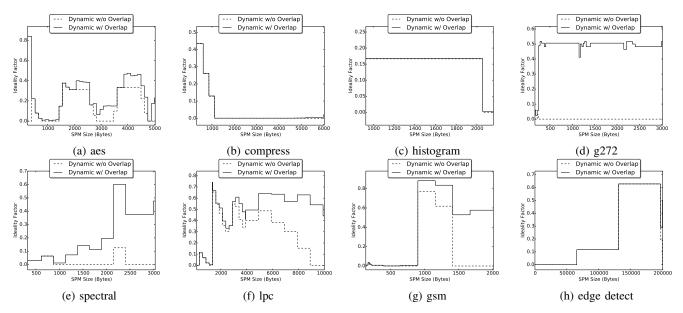

Finally, we note that the proposed region-based allocation scheme is a generalization of the approaches used in related work on dynamic allocation. In [10], the authors applied a structured analysis to choose a set of variables for static allocation. They analyzed innermost loop as Directed Acyclic Graph (DAG) for worst case path and then collapsed the loop into a basic block to analyze the outer loop. The region tree representation captures this structure as loops, conditional statements and functions as regions. The dynamic allocation in [5] is based on program points around loops, if statements and functions which can be matched with an entry/exit of a region. In [13], Deverge et al. proposed a general graph representation that allows different granularities of allocation. The authors formulated the dynamic allocation problem based on the flow constraints which can also be applied to the region representation. All such approaches use heuristics to determine the overall program allocation. Hence, to allow a fair evaluation focused on the benefits of data prefetching, in Section IX we compare our proposed scheme against a standard dynamic allocation approach with no overlap using the same region-based program representation and search heuristic.

#### B. Allocation Heuristic

The allocation heuristic adopts a genetic algorithm to search for near-optimal solutions to the allocation problem.

- Chromosome Model: The chromosome is a binary string where each bit represents one of the  $alloc_{r_n}^{y_j}$  decision variables. Note that we do not represent the  $assign_{r_n}^{y_j}$  decision variables in the chromosome; instead, we use a fast address assignment algorithm as part of the fitness function to find a feasible address assignment for a chromosome.

- Fitness Function: The fitness fit of a chromosome represents the improvement in the WCET of the program with this allocation if it is feasible. The fitness function first applies the address assignment algorithm to the chromosome. If the allocation is not feasible, the chromosome has fit = 0. Otherwise, we execute the WCET analysis after the program is transformed to insert the allocation commands; the fitness of the allocation is then assigned as  $fit = WCET_{MM} WCET_{alloc}$  where  $WCET_{MM}$  is the WCET with all the objects in main memory and  $WCET_{alloc}$  is the WCET for the analyzed solution.

- Initialization: The initial population P(0) is generated randomly with feasible solutions, *i.e.*, fit > 0.

## Algorithm 1 Address Assignment

```

Input: region information, \{alloc_{r_n}^{v_j}, alloc_{r_n}^{p_k} | \forall v_j, p_k, r_n\}

1: for all region r_n by increasing index starting with r_1 do

end\_addr_{r_n} \leftarrow ASSIGN\_ADDRESSES(r_n)

function ASSIGN_ADDRESSES(r_n)

end\_addr_{r_n} = \max_{\sigma} \{end\_addr_{\wp(r_n^{\sigma})}\}

4:

if r_{n-1} is not sequentially composed with r_n then

5:

for all v_j such that alloc_{r_n}^{v_j} do assign_{r_n}^{v_j} \leftarrow end\_addr_{r_n} end\_addr_{r_n} \leftarrow end\_addr_{r_n} + S(v_j)

6:

7:

8:

for all p_k such that alloc_{r_n}^{p_k} do

9:

assign_{r_n}^{p_k} \leftarrow end\_addr_{r_n}

10:

end\_addr_{r_n} \leftarrow end\_addr_{r_n} + \max_{\sigma}(S_{\sigma}(p_k))

11:

12:

else

13:

14:

for all p_k such that alloc_{r_n}^{p_k} \wedge alloc_{r_{n-1}}^{p_k} do assign_{r_n}^{p_k} \leftarrow assign_{r_{n-1}}^{p_k} ...

15:

16:

for all v_j such that alloc_{r_n}^{v_j} \wedge \neg alloc_{r_{n-1}}^{v_j} do

Compute assign_{r_n}^{v_j} using best fit based on

17:

18:

already assigned addresses

for all p_k such that \underset{\cdot}{alloc_{r_n}^{p_k}} \wedge \neg alloc_{r_{n-1}}^{p_k} do

19:

Compute assign_{r_n}^{p_k} using best fit based on

20:

already assigned addresses

\begin{array}{ll} \textit{max}_{r_n}^{\textit{v}} \leftarrow \max_{\textit{v}_j \text{ s.t. } \textit{alloc}_{r_n}^{\textit{v}_j}} \{ \textit{assign}_{r_n}^{\textit{v}_j} + S(\textit{v}_j) \} \\ \textit{max}_{r_n}^{\textit{p}} \quad \leftarrow \quad \max_{\textit{p}_k \text{ s.t. } \textit{alloc}_{r_n}^{\textit{p}_k}} \{ \textit{assign}_{r_n}^{\textit{p}_k} \end{array}

21:

22:

\max_{\sigma}(S_{\sigma}(p_k))

end\_addr_{r_n} \leftarrow \max\{max_{r_n}^{v}, max_{r_n}^{p}\}

23:

```

- Evolution Operations: The evolution process incorporates random random selection, one-point crossover and random bit mutation to generate P'(t+1). The elite chromosomes with highest fitness from P(t) and P'(t+1) are chosen to form the next population P(t+1).

- **Termination:** The algorithm is terminated after k generation or if the best chromosome does not change for n generations.

The address assignment algorithm is depicted in Algorithm 1. Given a chromosome, the region tree is traversed in topological order assigning addresses to the allocated objects and pointers in each region. The topological order visits all the nodes with the same parent before visiting the children. For the root of a function, all the parents (call regions) of the function are visited before the root of the function. Also, for a sequence of sequentially composed regions, the order of the sequence is maintained. After the objects in a region are assigned to SPM addresses, an end address to the last allocated address is maintained. For each region  $r_n$ , the previous end address is the maximum of all parent regions (note that if  $r_n$  is not the root of its function, it has a single parent region). For a region that is not sequentially composed or the first region in a sequence of regions, addresses are iteratively assigned to the allocated objects starting from the previous end address. For a region in a sequence, an allocated object maintains the same address as the previous region if the object is allocated in both. Otherwise, a best fit

Fig. 9: WCET Example: Merging states from different paths

algorithm is used to assign the remaining addresses. The end address for each region is then computed as the maximum end address for any allocated object. Note that the algorithm trivially ensures that objects/pointers allocated in a region cannot overlap with any object or pointer that is available in a parent; hence, Equations 9, 11 are always satisfied. However, the algorithm is not optimal, since it does not consider that an allocation might not be required in any context where the object is already available in the SPM or the aliasing between objects and pointers. Finally, the allocation is considered feasible only if the end address never exceeds the SPM size; this guarantees that Equations 7, 8 are also satisfied.

# VII. WCET ANALYSIS

We discuss how to model the behavior of our prefetch mechanism in the context of static timing analysis so that a safe bound to the WCET of the program running uninterrupted can be computed. We assume a given allocation solution computed based on Section VI. We rely on the standard approach of Data Flow Analysis (DFA) [24], where the detailed state of the hardware is generalized into an *abstract state* based on the theory of abstract interpretation [25], [26]. To avoid maintaining a different state for each path through the program, the analysis relies on computing fixed points by "merging" states when paths joins (i.e., branch join and loops entry/exit). In detail, given two abstract states d and d', we need to compute a *join operator*  $\vee$  such that the resulting state  $d'' = d \vee d'$  is more general than either d or d'. We model time as natural numbers, i.e., processor clock cycles.

We begin by providing an intuitive discussion of the challenges of handling our prefetching mechanism, followed by our intended solutions. In what follows, we use function  $(x)^+$  as a shorthand or  $\max(0,x)$  and  $\mathscr{P}(A)$  to denote the powerset of set A. As discussed in Section IV, let  $\bar{G}_f = (\bar{N},\bar{E})$  to denote the refined CFG for function f. To keep track of the program execution, it is useful to formally define the concept of program state:

Definition 1 (State): The program execution is defined as the transformation of a program state. We let  $\Sigma$  be the set of all possible program states; we use  $\mathbf{s} \in \Sigma$  to denote an individual state and  $S \subseteq \Sigma$  to denote a set of states. The state at any given point in the execution of the program represents the amount of elapsed time  $\mathbf{s}.t$  since the beginning of the program, and the content of all hardware registers and memories.

Definition 2 (Transfer Function): For every edge  $e: BB_i \to BB_j$  in  $\bar{G}_f$  and context  $\sigma$  for f, we define a transfer function  $\mathcal{T}_{e,\sigma}: \Sigma \to \Sigma$  such that: if  $\mathbf{s}$  is the program state at the beginning of the execution of  $BB_i$  and the program execution

flows from  $BB_i$  to  $BB_j$ , then  $s' = \mathcal{T}_{e,\sigma}(\mathbf{s})$  is the program state at the beginning of the execution of  $BB_j$ . Function  $\mathcal{T}'_{e,\sigma}: \mathcal{P}(\Sigma) \to \mathcal{P}(\Sigma)$  denotes the obvious set-extension of function  $\mathcal{T}_{e,\sigma}$ , i.e.  $\mathcal{T}'_{e,\sigma}(S) = \cup_{\mathbf{s} \in S} \mathcal{T}_{e,\sigma}(\mathbf{s})$ .

Note that based on Definition 2  $^2$ , if the execution cannot flow from node  $BB_i$  to  $BB_j$  for any state in S, then  $\mathcal{T}'_{e,\sigma}(S) = \emptyset$ . Given a set of initial program states  $S_{entry}$  with t = 0  $^3$ , a WCET analysis could then simply proceed as follows: enumerate all paths through every function in the program; for each path through the program, iteratively apply function  $\mathcal{T}'_{e,\sigma}$  starting from state set  $S_{entry}$  for all edges comprising the path, obtaining a set of final states  $S_{exit}$ . The WCET can then be obtained as the maximum time elapsed for any state in any final state set  $S_{exit}$ . Since based on our assumptions the number of paths through the whole program is finite, this approach is computable, but it is generally computationally intractable for all but the simplest programs, as the number of paths is exponential in the number of branches/loops in the program.

To obtain a tractable analysis, WCET techniques typically attempt to prune paths that cannot lead to the WCET by making *local* decisions: ideally, we could examine each branch point in the CFG one at a time, determine which branch leads to the WCET, and exclude from the analysis all other branches, thus implicitly identifying the Worst Case Execution Path (WCEP) through the program. In practice, this might not be possible, because the worst case path through a branch might depend on the path taken through another branch preceding or following the one under analysis, either due to the program semantic (i.e., some paths might be invalid) or due to architectural considerations (i.e., an hardware operation started during a basic block might influence the timing of a successive basic block).

Since our objective is to show how to integrate our proposed prefetching scheme in existing WCET frameworks, in the rest of the section we focus on architectural analysis. To explain how we model the behavior of DMA operations, consider as an example the execution of the CFG and associated region tree in Figure 9 in a context  $\sigma$ . Assume that the analysis for the path through  $r_4^{\sigma}$  has computed a program state s with an upper bound to the execution time of the program up to this point equal to t = 10, and an upper bound to the remaining time to complete a DMA fetch operation for an object  $v_j$  equal to  $t_{v_j} = 3$ . For the path through  $r_5^{\sigma}$ , we instead have a state  $\mathbf{s}'$  with  $t = 8, t_{v_j} = 7$ , i.e., the execution takes longer along the path through  $r_4^{\sigma}$  than through  $r_5^{\sigma}$ , but results in a shorter remaining DMA time. Assume now that a **GETADDR** command on object  $v_i$  is executed at the beginning of region/context  $r_7^{\sigma}$ . The amount of time that the command will block is then equal to  $t_{v_i}$  minus the amount of overlap that the DMA operation has with  $r_6^{\sigma}$ , or zero if the operation completes during  $r_6^{\sigma}$ . Assume a simple case where the execution through  $r_6^{\sigma}$  requires  $\Delta$  units of time and performs no access to main memory, so that the DMA operation can overlap up to  $\Delta$ . The program can then resume from **GETADDR** at time  $t + \Delta + \max(t_{v_i} - \Delta, 0)$ . Hence, note that for  $\Delta = 7$ , the worst case path is through  $r_4^{\sigma}$ , resulting in a

time of 17 units against 15 for the path through  $r_5^{\sigma}$ . However, for  $\Delta=3$ , the worst case path is through  $r_5^{\sigma}$ , with a time of 15 time units against 13 for the path through  $r_4^{\sigma}$ . In summary, we cannot determine which path through a branch leads to the worst case unless we analyze the regions following the branch in the CFG ( $r_6^{\sigma}$  and  $r_7^{\sigma}$  in the example). This shows that the WCEP determination is a *global* decision.

A typical solution to the global decision problem is to employ a *Meet Over Path* (MOP) solution: if we do not know which state to use for  $b_4$ , we can *abstract* the execution of the program by considering a new join state  $\mathbf{s}''$  that is worse than either  $\mathbf{s}$  or  $\mathbf{s}'$ . Such state does not need to represent any real execution of the system (i.e., it is *abstract*), as long as we can prove that the WCET obtained based on  $\mathbf{s}''$  is no smaller than the ones determined based on  $\mathbf{s}$  and  $\mathbf{s}'$ . In this case, a trivial solution would be to computing a join state  $\mathbf{s}''$  with  $t = \max(10,8) = 10$  and  $t_{v_j} = \max(3,7) = 7$ . However, this would lead us to over-approximate the time for the **GETADDR**, resulting in 17 time units for  $\Delta = 3$ , rather than the computed bound of 15 time units. Therefore, we seek to derive a tighter abstraction.

Intuitively, this can be achieved by abstracting the states s and s' for the execution through  $r_4^\sigma$  and  $r_5^\sigma$  into abstract states d and d'. An abstract state d is composed of two information: the elapsed program execution time d.t, and a set of *timers*  $\{t_{v_j}\}$ . For an object  $v_j$ ,  $d.t_{v_j}$  represents the worst case time required to complete either a prefetch or write-back operation in the allocation queue; since the allocation queue is served in FIFO order, this represents the time to transfer that specific object, plus the time required for all operations ahead of it in the queue. For the example in Figure 9, let d be the state through  $r_4^\sigma$  and d' be the state through  $r_5^\sigma$ . Since there is only one DMA operation in the queue, we have  $d.t = 10, d.t_{v_j} = 3$  and  $d'.t = 8, d'.t_{v_j} = 7$ , i.e., the abstract states are equivalent to the corresponding program states. The join state  $d'' = d \lor d'$  is then computed as follows:

$$d''.t = t_{\text{max}} = \max(d.t, d'.t), \tag{19}$$

and for every timer  $t_{v_i}$ :

$$d''.t_{v_j} = \max (d.t_{v_j} - (t_{\text{max}} - d.t), d'.t_{v_j} - (t_{\text{max}} - d'.t)).$$

(20)

Based on Equations 19, 20, we compute a join state for the example  $d''.t = \max(10,8) = 10, d''.t_{v_j} = (3 - (10 - 10), 7 -$ (10-8)) = 5. Note that this abstraction is tighter compared to the values  $t = 10, t_{v_i} = 7$  obtained by the trivial overapproximation; in particular, it is easy to see that for the provided example, the time for the GETADDR command computed based on d'' is exactly equal to the worst case between d and d' for any value of  $\Delta$ , albeit for more complex cases involving multiple DMA operations it is still a (tighter) over-approximation. However, the abstraction does not correspond to any "real" program state, since the values of t and  $t_{v_i}$  are different than the program state at  $r_7^{\sigma}$  for either execution paths. The key intuition is that adding  $\Delta$ units of time to the execution time of the program is always worse than adding  $\Delta$  units of time to the length of timers, since a **GETADDR** might block the program for a time at most equal to the length of the corresponding timer. Hence, if the execution time along two paths differs by a value  $\Delta$ , we are guaranteed to obtain an upper bound if we consider the longest execution time but subtract  $\Delta$  units of time from the timers along the shortest path, as performed in Equation 20.

Note that in general, a single DMA operation could overlap with many regions, and the amount of overlap can be further modified by the path through each region and

<sup>&</sup>lt;sup>2</sup>Also note that  $\mathcal{T}_{e,\sigma}$  defines a *deterministic* machine: assuming we know the state **s** at the beginning of the basic block, we can compute the exact state **s'** along *e*. If the machine is non-deterministic, the definition can be modified to return a set of states rather than a single state while maintaining the same theoretical framework, see [26].

<sup>&</sup>lt;sup>3</sup>Note that in general, a set of program states must be considered, rather than a single state, because the initial state of the hardware, including the program inputs, is not known.

allocation commands for both the same and other objects. Due to the presence of the max term in Equation 20, modeling the WCET problem as an ILP (a technique also known as implicit path enumeration [24]) would require adding a large number of auxiliary variables. Therefore, we propose to instead compute the WCET by performing the MOP procedure using a structure-based approach [24] that relies on the region tree, as summarized in Algorithm 2.

### Algorithm 2 WCET Analysis

14:

return d

```

Input: initial program state d with d.t = 0, region informa-

tion, allocation solution

1: d \leftarrow \text{ANALYZE\_REGION}(r_1, \emptyset, d)

2: return d.t + \max_{v_i} \{d.t_{v_i}\}

3: function ANALYZE_REGION(r, \sigma, d)

4:

if r is trivial region then

d \leftarrow \text{STATE\_TRANSFER}(r, \sigma, d)

5:

if r calls a region r_n then

6:

d \leftarrow \text{ANALYZE\_REGION}(r_n, \sigma \cup r, d)

7:

8:

for all paths p_i in r do

9:

d_i \leftarrow d

10:

for all subregions r_n along p_i do

11:

d_i \leftarrow \text{ANALYZE\_REGION}(r_n, \sigma, d_i)

12:

d \leftarrow \text{JOIN}(r, \sigma, \{d_i\})

13:

```

Starting from an initial abstract program state d and region  $r_1$ , the root of the main function, the algorithm recursively calls function  $ANALYZE\_REGION$  to update state d based on the execution of region r in context  $\sigma$ . If r is a trivial region, then function  $STATE\_TRANSFER$  is used to update d based on the region's code, including any allocation command. Note that we need to pass the context  $\sigma$  to the function, since as explained in Section VI, the availability and address of objects in the scratchpad depends on the context for the region. If the region is a call region, we also need to recursively invoke ANALYZE\_REGION on the called region after updating the context. If region r is not trivial, then we need to recursively analyze all sub-regions along every path in r; this results in an updated state  $d_i$  for each path  $p_i$ . The states are then joined by function *JOIN*. If region r has no backedge (i.e., it is not a loop), then the function simply applies the join operator over all states  $d_i$ . If the region is a loop, then function JOIN performs a fixedpoint iteration over the abstract state based on loop iteration bounds (since such fixed point iteration is a well-understood technique in DFA [25], [26], we do not discuss it further). At the end of the analysis, we return the total elapsed time plus the maximum timer length, to indicate the need to complete any remaining write back operation.

In the next section, we first provide required preliminaries on the underlying mathematical principles of DFA using the MOP approach. We then formally introduce our abstraction and prove it correct in Section VII-B. Note that while Algorithm 2 enumerates region, in practice the only regions that contain code and must thus be analyzed are trivial regions, containing one basic block each. Hence, for simplicity and to be consistent with previous analyses, we discuss the MOP procedure over basic blocks using the refined CFG  $\bar{G}_f$ . Finally, note that while we focused on

modeling the behavior of DMA operations, the abstract state can also model both architectural states, such as the state of the processor pipeline [26], as well as the value of program variables, which can be used to exclude invalid paths (flow analysis) and compute loop bounds [27].

#### A. Preliminaries

The theory of abstract interpretation [25] provides a formal way to describe a mathematical model for the state of the program. In this section, we base our discussion on the formulation of DFA with abstract interpretation for WCET analysis proposed in [26].

Definition 3 (Bounds for Partially Ordered Set):

Consider a set A with partial order  $\leq_A$ . We say that an element  $a \in A$  is an upper bound (lower bound) for a subset Y of A iff  $\forall y \in Y : y \leq_A a$  (respectively,  $a \leq_A y$ ). We further say that a is the unique least upper bound (greatest lower bound) for Y, and write  $a = \vee_A Y$  (respectively,  $a = \wedge_A Y$ ) iff for all other upper bounds b of Y it holds  $a \leq_A b$  (respectively,  $b \leq_A a$ ).

For simplicity, for a set  $Y = \{a, b\}$ , we shall write  $a \vee_A b$   $(a \wedge_A b)$  as a shorthand for  $\vee_A Y (\wedge_A Y)$ .

Definition 4 (Complete Lattice): A partially ordered set  $(A, \leq_A)$  is said to be a complete lattice if any subset Y of A admits both a least upper bound and a greatest lower bound.

Observation 5 (Concrete State Set): The set  $\mathscr{P}(\Sigma)$  together with the subset partial relation  $\subseteq$  is a complete lattice, where  $S \vee S' = S \cup S'$  and  $S \wedge S' = S \cap S'$ .

The complete lattice  $(\mathscr{P}(\Sigma), \subseteq)$  is used to model the "real" (concrete) state of the system; in this sense, the partial order  $\subseteq$  represents a relation of generality, in the sense that if  $S \subseteq S'$ , we can say that S' is more general (since it contains more program states), or equivalently less precise, compared to S.

Definition 6 (Monotone Function): Let  $(A, \leq_A)$  and  $(B, \leq_B)$  be partially ordered sets. A function  $f: A \to B$  is said to be monotone iff:  $\forall a, a' \in A: a \leq_A a' \Rightarrow f(a) \leq_B f(b)$ .

Definition 7 (Abstraction): We say that a complete lattice  $(D, \leq_D)$  is an abstraction for the concrete state  $(\mathcal{P}(\Sigma), \subseteq)$  iff there exists a monotone function  $\gamma: D \to \mathcal{P}(\Sigma)$  such that:

$$\forall S \in \mathscr{P}(\Sigma) : \exists d \in D : S \subseteq \gamma(d). \tag{21}$$

$\gamma$  is also called the *concretization* function of the abstraction. Since the concretization function is monotone, for every  $d \leq_D d'$ , it must hold:  $\gamma(d) \subseteq \gamma(d')$ . In other words, the partial order  $\leq_D$  on D must express a relation of generality similar to the one for the concrete state. Furthermore, Equation 21 ensures that for every concrete state S, there exists an abstract state S that "contains" S.