# Automated Analysis of Unified Modeling Language (UML) Specifications

By

Meyer C. Tanuan

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Master of Mathematics

in

**Computer Science**

Waterloo, Ontario, Canada, 2001 © Meyer C. Tanuan 2001

# Author's Declaration for Electronic Submission of a Thesis

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

# Abstract

The Unified Modeling Language (UML) is a standard language adopted by the Object Management Group (OMG) for writing object-oriented (OO) descriptions of software systems. UML allows the analyst to add class-level and system-level constraints. However, UML does not describe how to check the correctness of these constraints.

Recent studies have shown that Symbolic Model Checking can effectively verify large software specifications. In this thesis, we investigate how to use model checking to verify constraints of UML specifications. We describe the process of specifying, translating and verifying UML specifications for an elevator example. We use the Cadence Symbolic Model Verifier (SMV) to verify the system properties. We demonstrate how to write a UML specification that can be easily translated to SMV. We propose a set of rules and guidelines to translate UML specifications to SMV, and then use these to translate a non-trivial UML elevator specification to SMV. We look at errors detected throughout the specification, translation and verification process, to see how well they reveal errors, ambiguities and omissions in the user requirements.

# Acknowledgements

I would like to thank my supervisor, Dr. Joanne M. Atlee, for her valuable comments and insightful suggestions. I am very grateful for her encouragement and guidance throughout this work. To Professor Dan Berry, I thank him for pointing out that some of the errors revealed during model checking were requirements-level errors. I also thank my thesis reader, Dr. Nancy Day, who provided a thorough review of my thesis. I highly appreciate her detailed and helpful comments. Finally, I thank Doug Guderian for acting as our domain expert for the elevator case study.

To my wife,

Marrieta,

and sons,

Mayer and

Marko

# Contents

| 1                           | Int  | roduction                                       | 1 |

|-----------------------------|------|-------------------------------------------------|---|

|                             | 1.1  | Model Checking                                  | 2 |

|                             | 1.2  | Computer-Aided Verification of UML Models       | 3 |

|                             | 1.3  | UML to SMV Model Checking Process               | 6 |

|                             | 1.4  | Main Contribution                               | 9 |

| 2                           | Mo   | odeling Reactive Systems Using UML 1            | 1 |

|                             | 2.1  | Requirements Analysis                           | 2 |

|                             | 2.1. | 1 Three-floor Elevator System Problem Statement | 2 |

|                             | 2.1. | 2 System Properties                             | 4 |

|                             | 2.2  | Defining Object Structure using UML 1           | 5 |

|                             | 2.2. | 1 UML Class Diagram                             | 5 |

|                             | 2.2. | 2 UML Object Model                              | 1 |

|                             | 2.2. | 3 UML Constraints                               | 3 |

|                             | 2.3  | Defining Object Behavior using UML 2            | 5 |

|                             | 2.3. | 1 UML State Machine Semantics                   | 5 |

|                             | 2.3. | 2 Example Scenarios of Elevator State Machine   | 0 |

|                             | 2.3. | .3 Inherited State Diagrams                     | 3 |

|                             | 2.3. | 4 UML Operations                                | 5 |

| <b>3</b> Translating UML to |      | anslating UML to SMV                            | 9 |

|                             | 3.1  | Translation Overview                            | 0 |

|                             | 3.2  | Translating the Elevator Example                | 3 |

|                             | 3.2. | .1 Translating the Button Class                 | 3 |

|                             | 3.2. | 2 Translating the RequestBn Subclass            | 8 |

|                             | 3.2. | .3 Translating the External_Event Class         | 2 |

|                             | 3.2. | .4 Translating Timer Class                      | 5 |

|                             | 3.2. | .5 Translating Door Class                       | 8 |

|                             | 3.2. | .6 Translating the Elevator Class               | 0 |

|                             | 3.2. | 7 Putting it all together: Main SMV Module      | 5 |

|                             | 3.3  | Translation Summary                             | 6 |

| 4                                | Ve         | erifying System Properties Using SMV                  | 68  |  |  |

|----------------------------------|------------|-------------------------------------------------------|-----|--|--|

|                                  | 4.1        | CTL Overview                                          | 68  |  |  |

|                                  | 4.2        | Verifying the Elevator System Properties              |     |  |  |

|                                  | 4.2        | 2.1 Safety Property for Elevator                      | 70  |  |  |

|                                  | 4.2        | 2.2 Liveness Properties for Elevator and Hall Buttons | 70  |  |  |

|                                  | 4.2        | 2.3 Additional System Properties                      | 72  |  |  |

|                                  | 4.3        | Model Checking Partial Specifications                 | 74  |  |  |

| 5                                | Ef         | fectiveness of Model Checking                         |     |  |  |

|                                  | 5.1        | Time Spent per Activity                               |     |  |  |

|                                  | 5.2        | Requirements-level Errors                             | 81  |  |  |

|                                  | 5.3        | UML Model Style Defects                               |     |  |  |

|                                  | 5.4        | Object-oriented Modeling Errors                       |     |  |  |

|                                  | 5.5        | SMV Errors                                            |     |  |  |

|                                  | 5.6        | Summary                                               | 90  |  |  |

| 6                                | Co         | onclusions and Future Work                            | 92  |  |  |

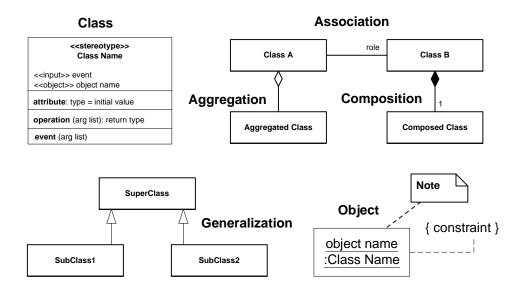

| Appendix A: UML Notation Summary |            |                                                       |     |  |  |

|                                  | A1. I      | UML Class Diagram Notation                            |     |  |  |

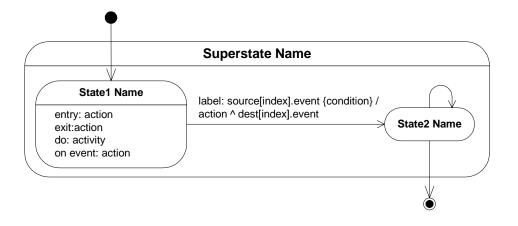

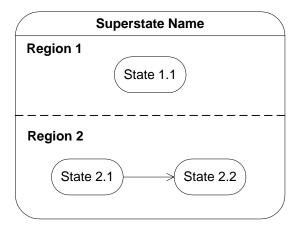

|                                  | A2. U      | UML State Diagram Notation                            |     |  |  |

| A                                | ppen       | ndix B: Elevator UML Specification                    | 99  |  |  |

| A                                | ppen       | ndix C: Elevator SMV Program                          | 107 |  |  |

| A                                | ppen       | ndix D. Additional Elevator Features                  | 121 |  |  |

| R                                | References |                                                       |     |  |  |

# List of Figures

| Figure 1: Finite state model checking                        | 2 |

|--------------------------------------------------------------|---|

| Figure 2: UML to SMV model checking process                  | 7 |

| Figure 3: Two-passenger scenario sequence diagram            |   |

| Figure 4: Three-floor elevator main class diagram in UML     |   |

| Figure 5: Three-floor elevator object model in UML           |   |

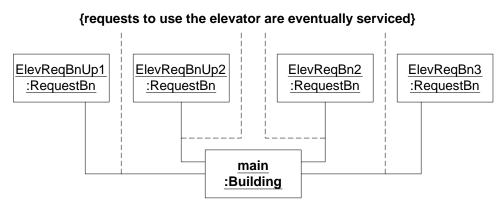

| Figure 6: System properties shown as UML constraints         |   |

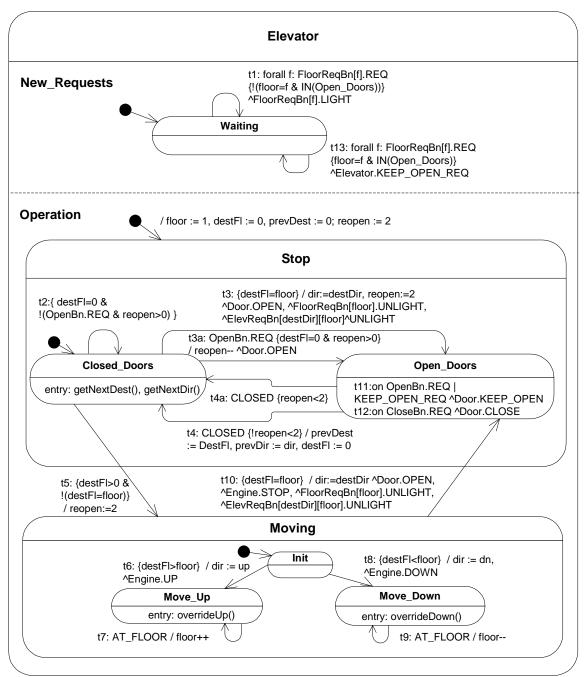

| Figure 7: Elevator state diagram                             |   |

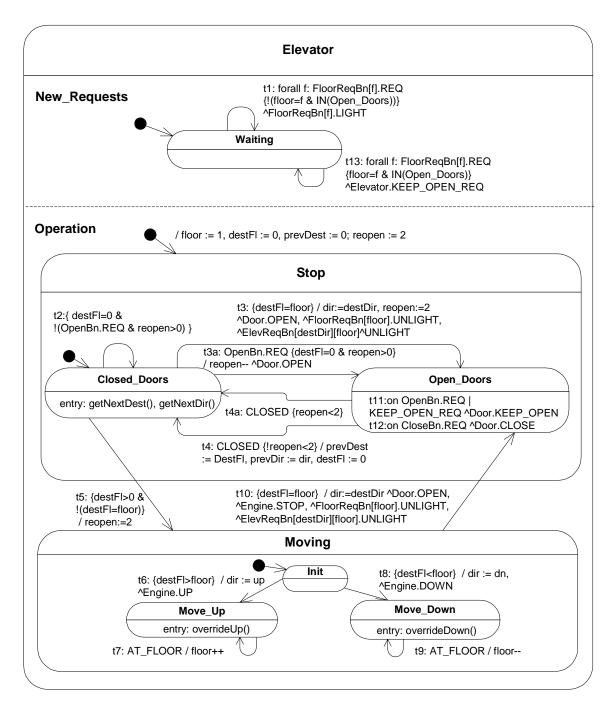

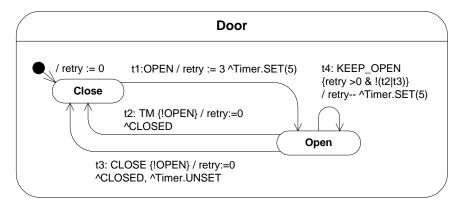

| Figure 8: Door state diagram                                 |   |

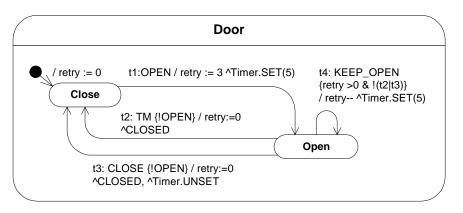

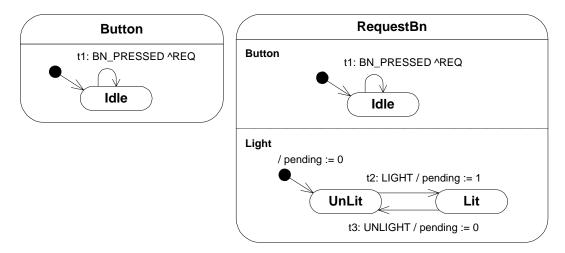

| Figure 9: Button state diagram and RequestBn state diagram   |   |

| Figure 10: SMV module program structure                      |   |

| Figure 11: Button SMV module                                 |   |

| Figure 12 : RequestBn SMV module                             |   |

| Figure 13 : External_Event SMV module                        |   |

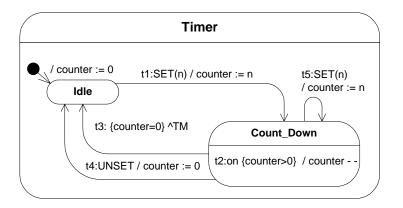

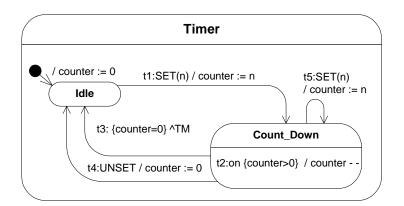

| Figure 14: Timer state diagram                               |   |

| Figure 15: SET Event SMV module                              |   |

| Figure 16: Partial listing of Timer SMV module               |   |

| Figure 17: Partial listing of Door SMV module                |   |

| Figure 18: Partial listing of Elevator SMV module            |   |

| Figure 19: Partial listing of main SMV module                |   |

| Figure 20: Main SMV module for Timer class unit verification |   |

# List of Tables

| Table 1: getNextDest operation modeled as a decision table       | . 36 |

|------------------------------------------------------------------|------|

| Table 2: Macros for going to floor 1 with direction up           | . 37 |

| Table 3: SMV program structure / rules mapping                   | . 66 |

| Table 4: Naming convention for SMV modules, variables and macros | . 67 |

| Table 5: Requirements-level and OO modeling defects summary      | . 80 |

# **1** Introduction

Object oriented (OO) modeling started in the late 1980s, modeling the concepts of object oriented programming at a higher level of abstraction. Several OO methodologists, spearheaded by G. Booch, J. Rumbaugh, and I. Jacobson, joined efforts to combine the best practices of various OO modeling approaches into a single method called the Unified Modeling Language (UML) [UML99]. On November 17, 1997, the Object Management Group (OMG) adopted the UML as a standard for specifying, visualizing, constructing and documenting artifacts of software systems. Since then, UML has gained popularity for providing software practitioners with a set of standard symbols and semantics to effectively communicate and produce predictable, repeatable results. The popularity of UML is evidenced in the number of books, conferences, seminars, reports, papers and software tools available in the commercial market today.

UML has become the most popular method for OO modeling. Most UML specifications are descriptive and easy to understand. However, UML does not provide a standard approach to verify correctness properties of the model. In this thesis, we translate UML object-oriented software models to Symbolic Model Verifier (SMV) [McMi93] models in order to verify the correctness of the UML model.

UML has a very rich set of diagrams, notations and well-formedness rules. However, it does not provide guidelines for writing clear and unambiguous object-oriented specifications that are amenable to model checking. In this thesis, we demonstrate that the use of Class Diagram, Object Model and State Diagrams are sufficient to translate into SMV for model checking. We introduce a set of guidelines in constructing well-formed unambiguous UML specifications that makes translation to SMV easy. We use UML constraints to describe the system properties informally. We provide a set of rules to translate the UML specifications including the UML constraints to SMV. We apply these guidelines to build a UML model for a three-floor elevator and apply these rules to translate the UML model to SMV. To complete the case study, we use SMV to perform model checking automatically.

Our aim is to make systematic model checking available for software developers who use UML to specify reactive systems. The guidelines and examples of translation from UML to SMV described in this thesis are aimed at helping software practitioners translate UML models to SMV easily. This approach has the potential to add model checking capability to commercial UML

tools such as Rational Rose (by Rational) and Rhapsody (by i-Logix). We view model checking as complementary to current simulation and testing capabilities of commercial UML tools.

# **1.1 Model Checking**

Software verification techniques can be classified as *verification-based* or *refutation-based*. Theorem provers use the *verification approach* to find a proof for a given property, while model checkers use a *refutation approach* to refute the correctness property by finding a counter-example. With the aid of deductive verification using axioms and proof rules, theorem proving has the advantage of effectively verifying infinite state models. However, it requires a lot of expertise in Formal Methods. If and when a failed proof occurs, the theorem prover does not present a counter-example.

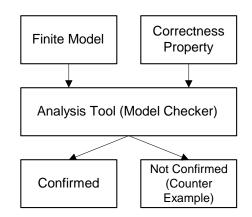

Figure 1: Finite state model checking

Figure 1 shows the process of finite-state model checking where a finite model is checked against a correctness property [CES86]. Both the finite model and the correctness property are expressed in the language of the analysis tool called a model checker. The model checker performs an exhaustive check and responds with confirmed or "not confirmed" with a counter-example. If a counter-example is found, either the finite model was incomplete or wrong, or the expected property was incorrectly specified or the property does not hold in the model specified. In this thesis, we selected model checking for automated analysis because it is more cost-effective to check the software system. Unlike theorem proving, model checking requires less expertise in the use of formal methods. As such, refutation-based tools such as model checkers are more promising for software practitioners.

Recent papers on automated software analysis [GlWe98] [JaRi00] describe how using an essential model (i.e., an abstract model of an important requirement or behavior) helps to make

model checking more practical. Model checking key properties of an essential model is known to incur much lower cost than verifying a complete model [Berr99]. In this thesis, we apply model checking on the essential model of the elevator case study.

## **1.2** Computer-Aided Verification of UML Models

Computer-aided verification of UML Models is currently an active area of research. Some researchers suggested verifying UML specifications using a theorem prover. Kamuller and Helke [KaHe00] translate UML object and state diagrams into Isabelle/HOL, and use the Isabelle interactive theorem prover to detect inconsistencies and check well-formedness. Guaspari and Naydich [GuNa98] describe how to model a UML specification consisting of state diagrams for a restricted class diagram (e.g., no inheritance) in PVS [ORS92], also an interactive theorem prover. Muthiayen [Muth00] proposes real-time extensions to UML and demonstrates how models written in this RTUML notation can be formalized as PVS axioms and theories and how safety and liveness properties can be verified using the PVS theorem prover. Using PVS, one can formally prove that the model is consistent with a property. However, the use of PVS for software verification requires more expertise in Formal Methods because writing theorems and proofs requires mathematical background and reasoning.

There are papers that described how to convert a UML model into a Promela specification [LiPa99][Bose99][McCh01]. Promela is the input language of the SPIN model checker [Holz97]. The SPIN software verification system, developed by AT&T, is based on an interleaving model of concurrency where only one component of the system's state is allowed to change at a time. The interleaving semantics supports a reduction algorithm based upon exploiting symmetries in the order of execution known as *partial order reduction* [Pele94]. This makes SPIN suitable for concurrent processes with uncoupled events such as network protocols. For most reactive systems where events are tightly coupled in distinct processes, SPIN's partial order reduction technique cannot be put to good use.

In contrast, tools that use synchronous models such as COSPAN [Kurs96] (by AT&T) and Symbolic Model Verifier (SMV) allow any number of components to execute at the same time. The SMV tool uses Binary Decision Diagrams (BDDs) to symbolically represent state information rather than explicitly representing each state. Since SMV represents the sets of states and transition relations as boolean formulas, model checking is based on formula manipulation and simplification. In this thesis, we decided to use SMV because it is well suited for reactive

systems and process control systems where components are tightly connected via synchronization messages and internal events.

Studies have shown that symbolic model checking can be successfully applied to large software systems [SrAt96][CAB+98]. Our work builds on previous work that uses SMV to perform automated verification. However, we differ by translating from UML models (instead of CoRE/SCR, RMSL, and Statechart models) to SMV models.

McUmber and Cheng [McCh01] investigated formalization of UML diagrams using formal target languages. Specifically, they demonstrated a framework for translating a subset of UML state diagrams and UML class diagram into Promela/SPIN based on a homomorphic mapping between UML and Promela metamodels. Our work is consistent with their homomorphic mapping approach because we preserve UML's class structure when translating from UML to SMV. Our work differs in that we are translating UML models into SMV and not UML models to Promela. We provide specific rules on how to map UML classes and attributes to SMV's modules and variables.

Our work also differs from the previous translations from UML to PVS and to Promela because the other translations concentrate on the UML state machine only. They use the state diagram for defining internal behavior of objects and translate the state diagram to a formal language, but not in the context of the class diagram. They provide no guidance in how to instantiate the state models associated with the various classes from their class diagram. In contrast, we examine and translate the major model elements of a UML class diagram. We discuss how to model and translate different types of associations including aggregation, composition and generalization (superclass / subclass) relationships. We also investigate how to translate operations and attributes defined in a class. For UML state diagrams, we show how to specify state models that adhere to the object-oriented principles and propose translation rules for events with arguments. Only a subset of UML's notation (i.e., the most common and important modeling elements) is considered in our case study.

In this thesis, we describe how to verify properties of UML specifications using SMV. We expect our guidelines for specifying a well-formed UML specification to be applicable to other non-SMV model checkers. Thus we have separated the UML modeling step from the translation and verification steps, to make it possible to use a different model checker to verify the same UML specification. Using this approach, software practitioners can concentrate on UML modeling and use the SMV tool as a separate component to perform model checking.

# 1.3 UML to SMV Model Checking Process

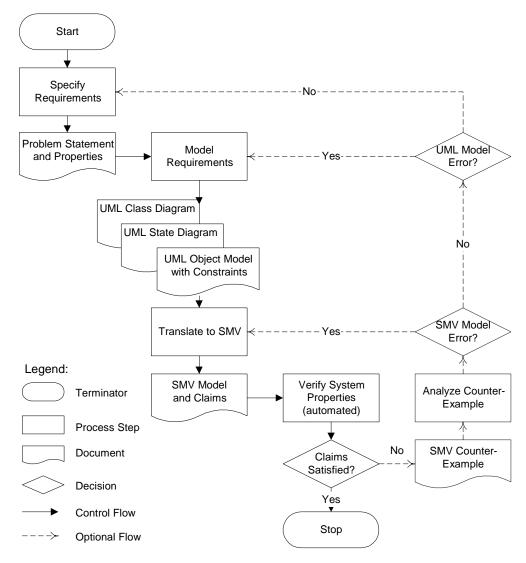

In practice, the translation from UML to SMV is iterative. We specify the user requirements using UML and translate to SMV. Then, we perform model checking using SMV. UML models are updated and retranslated based on the result of the SMV model checking. The iteration is complete when all properties to be checked are satisfied (i.e., no counter-examples or no errors are detected). The complete UML to SMV model checking process is illustrated in Figure 2, where we use basic flowchart notation to describe the process. The UML to SMV model checking process consists of five major steps:

#### Step 1. Attempt to specify the user requirements

This is the requirements elicitation step, in which the stakeholders of the software system discover, reveal, articulate and understand their requirements. For simplicity, we assume that the outcome of this step is the problem statement and system properties that must hold<sup>1</sup>. The following steps help in specifying and refining the problem statement.

### Step 2. Model the requirements in UML

Using all the relevant information provided by the requirements elicitation step, we build a UML class diagram, UML object model and for each class, a UML state diagram. The UML class diagram defines the system's object structure including inter-object associations such as composition, aggregation and generalization. We use the UML object model to represent the maximal instantiation of the class diagram. The object model is annotated with UML constraints that specify desired system properties such as "elevator never moves with its doors open". A UML state diagram defines the behavior of all objects of a specific class. We build the state diagrams that conform to well-formed rules to ensure consistent and intuitive translation to SMV for model checking. Guidelines and detailed examples are discussed in Chapter 2.

#### Step 3. Translate the UML model to SMV

In this step, we translate the classes and their state machines into SMV modules. Then, we translate the objects defined in the object model as instantiations of SMV modules. Details of

<sup>&</sup>lt;sup>1</sup> In practice, the outcome of this step would include objectives, anticipated benefits, strategic and future considerations, constraints and assumptions, security, audit and control aspects of the software system.

translation rules are discussed in Chapter 3. We also translate the UML constraints defined in the UML object model into Computational Tree Logic (CTL) formulas, which is the property language for SMV.

Figure 2: UML to SMV model checking process

Step 4. Verify the system properties using SMV

Verifying the CTL expressions using SMV is an automated step. SMV checks for syntax errors and cyclic dependencies. The SMV software tool builds a representation of the system state space and checks the CTL expressions with respect to the SMV model. There are two possible outcomes:

1. The system property is true.

2. The system property is false. In this case, SMV typically shows a counter-example to substantiate its claim.

For very large SMV models, the SMV tool will run for hours and may run out of memory and abort execution. The Cadence SMV used in this thesis controls the size of the BDDs created and manipulated during state exploration. However, it is still possible that the Cadence SMV tool will exhaust all memory available and abort execution.

In addition to checking the systems properties defined in the user requirements, the developer can check additional CTL expressions, such as test conditions, liveness or progress properties, guarantee conditions and valid value range conditions. Details of these additional system properties will be discussed in Chapter 4.

## Step 5. Analyze the counter-example

If the outcome of the model checking is true, we have increased confidence that the UML model accurately represents the system requirements defined by the system properties. If the outcome of the model checking is false, a counter-example shows a sequence of states that leads to state where the property is violated. If the counter-example reveals an error, then fixing the error *may* mean changing the requirements or changing the UML model. It may also mean that there is an error in the translation process (i.e., UML model to SMV model or system property to CTL formula). Alternatively, we may intentionally construct claims that we expect to be false, in which case a counter-example is a desirable outcome because the counter-example provides a detailed trace of a specific execution path. This trace can be useful for understanding the execution steps of SMV. The types of errors we encountered in the elevator case study and the corrective actions taken are discussed in Chapter 5.

## Step 6. Iterate Steps 1 through 5 until no more problems are found

Using model checking as an automated analysis tool allows us to verify a partial UML model very early in the UML modeling phase. Constraints are specified on an object or a group of objects (on the links) on the UML object model. To verify if a UML constraint is true, one can identify and translate only the objects associated with the constraint and proceed to model check a small portion of the software system.

Thus, new objects and state diagrams can be added in an incremental fashion. This can increase the probability of getting an answer from the SMV tool especially if the final UML model is large. Once a specific object or group of objects has been verified to be correct, we have more confidence and can add more objects for translation and verification. Verifying partial specifications will be discussed in Chapter 4.

## **1.4 Main Contribution**

The main contributions of this thesis are as follows:

- 1. We propose UML extensions and notation conventions that ease the translation from UML model to SMV input. The main extensions to the UML class diagram notation include: adding a special External\_Event class to centralize all the events generated by the environment; adding input events and input objects stereotypes to the class name section of a class; adding a fourth section of a class to define output events; and adding array indices to role names to distinguish multiple instances of the same class. In this thesis, we treat UML operations as mathematical functions. We do not support dynamic use of constructor and destructor operations. We associate a UML state diagram with a single class. We propose changes to the UML state transition by adding an optional source object to distinguish the source of the event trigger; adding an array index to the source or destination objects of the events; and introducing an optional quantification formula over multiple source objects to specify multiple transitions in a more compact manner.

- 2. We develop the SMV program structure (i.e., a template) and rules for translating UML class diagrams and UML state diagrams to SMV. These rules address UML's *composition* and *generalization* constructs and semantics found in UML class diagrams. They also address UML's *timer*, *concurrent states* and *multiple-event processing* semantics found in UML state diagrams.

- 3. We demonstrate how our bottom-up approach in translating and verifying the UML model allowed us to perform unit verification early in the specification process. This approach helps us detect and correct errors for each object before analyzing the entire specification.

- 4. We demonstrate how model checking a UML specification can help to iterate and refine a requirements document. We observe how model checking detected errors that were not detected when writing the user requirement or specifying the UML models.

The primary goal of the proposed translation rules and guidelines is to make both UML and SMV specifications easy for software practitioners to understand. We evaluate our approach in model checking UML models by the ease of translation and the effectiveness of detecting errors in the original UML specification. We also discuss how the proper use of object-oriented specifications can improve the readability of the UML and SMV models. Although it is possible to automate the proposed UML-to-SMV translation rules, this is not part of the thesis.

# 2 Modeling Reactive Systems Using UML

Throughout this chapter, we provide guidelines for writing UML specifications that are amenable to model checking. We provide modeling guidelines for a subset of UML class diagram notation and UML state diagram notation. These guidelines improve readability of the specifications. They also eliminate ambiguity by using clear and precise UML notation. The guidelines were developed based on the elevator example and eliminate many of the common pitfalls in object-oriented specifications.

This chapter provides a case study on how to use the Unified Modeling Language (UML) to model reactive systems<sup>2</sup>. UML provides a set of notations and diagrams to model object-oriented structure and complex behavior of reactive systems. First, we describe the three-floor elevator system and the system properties to be checked. In Section 2.2, we use UML's class diagram to show the object-oriented structure of the software system. In Section 2.3, we use UML's state diagram to describe how each of system's objects reacts to external events. We use the methodology described by Douglass [Doug98] to construct our UML specifications. In Appendix A, we provide a summary of the UML notation used in our case study.

$<sup>^{2}</sup>$  A reactive system is a long running system that interacts continuously with its environment. It is designed not to terminate.

#### 2.1 Requirements Analysis

In this section, we present the problem statement and system properties for a three-floor elevator that we use as a case study. The problem statement is an informal description of the system to-be-developed and its basic requirements.

#### 2.1.1 Three-floor Elevator System Problem Statement

A software system controls an **elevator** for a building with **three floors**. The first and third floors each have *one* **elevator request button**, located outside the elevator, used to request that the elevator to come to that floor. The second floor has *two* **elevator request buttons**, one for requesting service to a higher floor and one for requesting service to a lower floor. This means that when both the up and down second floor hall buttons are pressed and the elevator arrives to pick up a passenger in one direction, the backlight of the hall button for the other direction will remain lit. Elevator request buttons are also known as **hall buttons**. Pressing a **hall button** will keep the elevator door open, if the elevator is on the same floor as the pressed button and the door is currently open.

Inside the elevator, there are *three* floor request buttons used to request to go to a specific floor. The elevator also has an open door button and a close door button. The open door button opens the doors when the elevator is not moving. Each time the open door button is pressed, the time period that the door will remain open shall be reset to five seconds. The close door button closes the doors immediately even if the timeout period of five seconds is not yet reached. To ensure fairness to all service requests, a maximum of three (3) consecutive open door button are called elevator buttons.

The elevator has a sliding door called the **inner door** of the elevator. Each floor has a sliding door called the **outer door** of the elevator. When the elevator arrives at the floor, the **inner door** and the **outer door** of the elevator simultaneously open using a mechanical device. The **doors** close within five seconds after the doors open.

Each time an **elevator request button** or **floor request button** is pressed, the request is placed in a **pending queue**. Once pressed, a request button is lit to indicate that a request is in the **pending queue**. Pressing a request button that is already in the pending queue has no additional effect. The

elevator has a **floor sensor** that determines when the elevator is at a floor. When the elevator arrives to handle an elevator- or floor-request, the light on the request button is no longer lit.

The elevator system shall respond to an elevator request whenever it is idle or already going in the requested direction. This means that if a passenger from the first floor requests to go to the third floor, a passenger with an **elevator** *up* **request** from the second floor will be picked up along the way. An **elevator** *down* **request** on the second floor will not be picked up until the elevator changes direction from up to down.

#### Two-Passenger Scenario

In order to understand the requirement that the elevator responds to new requests for travel in the same direction as its current destination, we present a two-passenger scenario using a UML sequence diagram.

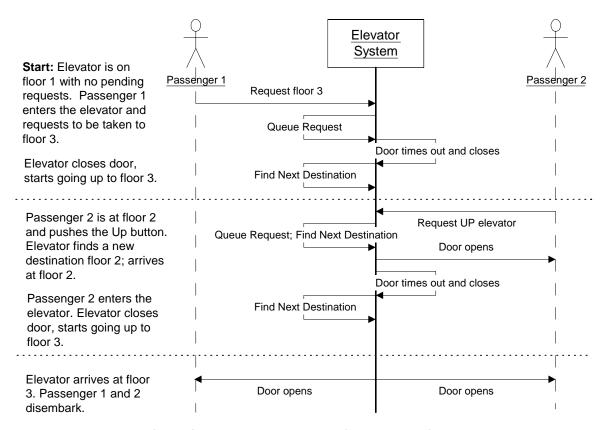

Figure 3: Two-passenger scenario sequence diagram

Figure 3 shows how the requests are sent to the elevator system asynchronously. Each request is stored in the pending queue. This allows the elevator to find the next destination (floor) each time the door closes or when new requests are received by the elevator while it is moving.

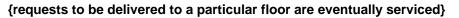

# 2.1.2 System Properties

The elevator should have the following system properties:

- Requests to use the elevator are eventually serviced; requests to be delivered to a particular floor are eventually serviced.

- The elevator never moves with its doors open.

- The elevator doors are not held open indefinitely.

## 2.2 Defining Object Structure using UML

In this section, we describe the object structure of our elevator case study. We will introduce the guidelines in writing UML class diagrams, object models and UML constraints as we construct the UML model for the elevator example. We used Visio's UML template for creating and maintaining our UML diagrams. To implement some of our proposed changes, we added extensions to the original UML template.

#### 2.2.1 UML Class Diagram

The main class diagram shows an object-oriented decomposition of the problem description. When we specify the UML class diagram, we only show objects that form part of the software system. To avoid clutter, classes that represent environmental devices are kept to a minimum. Our primary goal is to produce successful software requirement specifications. As such, we build object models that have sufficient details to verify all the system properties defined by the domain expert, and no more.

# Identifying Classes

A *class* captures the common structure and common behavior of a set of objects. An *object* is an *instance* of a class. It can contain both *data* and *functionality*. Data are represented as *attributes* in a class. Functionality is represented as *operations* that describe computational behavior.

When modeling and analyzing reactive systems, we are interested in the control flow of the software system. Therefore, we are most interested in identifying the *active objects* of the system. *Active objects* can autonomously perform actions, coordinate the activities of *component* objects, and generate events to other objects. In our elevator example, the active objects are the building, elevator, the door and the buttons.

Environmental devices such as sensors and actuators that are not controlled by the software system are shown in our main class diagram with the <<environment>> stereotype<sup>3</sup>. We introduce the *environment* stereotype to define a new form of class that defines classes that are

$<sup>^{3}</sup>$  A *stereotype* is an extension mechanism to UML, allowing analysts to add new semantics to the UML notation.

external to the software system. In our elevator case study, the **External\_Event** and **Engine** classes are environment classes.

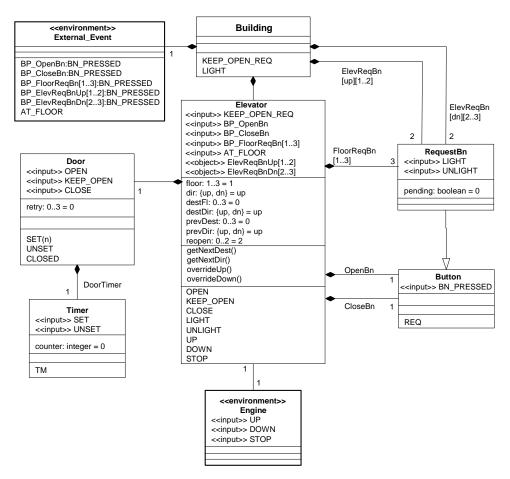

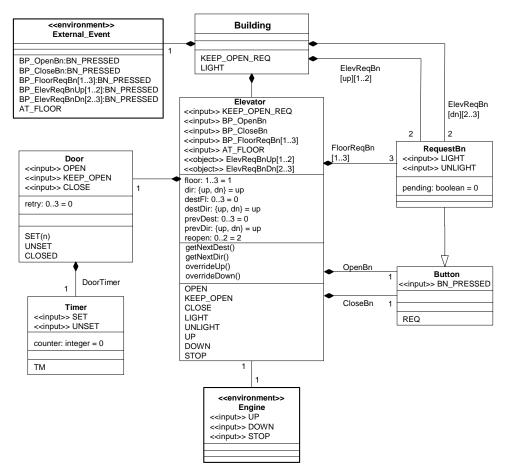

Figure 4: Three-floor elevator main class diagram in UML

Figure 4 shows how the active classes, **Building**, **Elevator**, **Door** and **Button**, are structured as a general solution to the elevator problem. We add an active class **Timer** that generates the timeout event needed by the **Door** class. The **RequestBn** class is a specialization of the **Button** class.

*Class attributes* refer to the data encapsulated within an object. Attribute definitions must include the data type because SMV will need to know the set of possible values for each attribute. Default values are optional because they can be defined in the state diagram. If both a default value for an attribute is specified and an initial value set in the *state diagram*, then they must agree. Alternatively, default values may be left unspecified (non-deterministic). For example, the **Elevator** class has a *floor* attribute whose value ranges from 1 to 3. The *floor* attribute records which floor the elevator is at. Initially, the elevator is on the first floor. Elevator's attributes also keep track of the elevator's current destination (*destFl*) and previous destination (*prevDest*). The

**Elevator** class has attributes *dir*, *destDir* and *prevDir* to keep track of the current direction, the destination's direction and the previous destination's direction respectively. The *reopen* attribute of **Elevator** class counts the consecutive requests to reopen the door while the elevator is on the same floor with doors closed. The **Door** class has a *retry* attribute that counts the number of consecutive requests to keep the door open. The **Timer** class has a *counter* attribute, which simulates the count down of the timer.

UML *operations* are the services provided by the class. For example, the **Elevator** class has a *getNextDest* operation that describes the complex rules used to decide the elevator's destination. To avoid clutter, we do not describe the operations of environment classes. Details of UML operations will be discussed in the next section.

#### Modeling Internal and External Events

Events are the messaging mechanisms that allow a system object to interact with the environment. They also enable the objects within a system to communicate and synchronize. UML does not say anything about how events are modeled in the main class diagram. Since events are critical to reactive systems, we treat events as first class modeling elements in the main class diagram. Modeling events explicitly helps to make the main class diagram more readable and eases its translation to SMV.

The UML notation does not provide a notation to explicitly model the events in the main class diagram. To resolve this problem, we propose several extensions to the UML class diagram notation. We introduce as part of the class name the set of *input events*, which instances of that class can receive and react to. By explicitly defining the input events in the class diagram, we are defining the input interface of the class<sup>4</sup>. The input interface is useful for inspecting the class's state diagram because the state diagram should not generate these input events. An input event serves as an event trigger to enable a transition. Input events are prefixed with <<input>> stereotype. We only declare input events that do not come from an object's class or its component classes. For example, **Door** class can access events generated by its own component class **Timer**, so we do not declare the TM (timeout) input event in the **Door** class. In addition to input events, a class

<sup>&</sup>lt;sup>4</sup> These input events must be consistent with the input events used in the class's UML state diagram.

that needs to access attribute values from other objects that are external to the class are defined as *input objects*. Input objects are prefixed with <<object>> stereotype.

We also introduce in a fourth section of a class declaration the set of *output events*, which instances of that class can generate. By explicitly defining the output events in the class diagram, we are defining the output interface of the class. The output interface is useful for inspecting the class's state diagram because the state diagram should generate these output events. This new *event section* is placed below the name, attribute and operation sections. Although it is possible to use the state diagram to identify the events that the environment and system generate, it is convenient to see them in the main class diagram. Adding a separate event section allows us to check the consistency of event names and prevent conflict. Adding the *<*(input>) stereotype to the class name and adding a separate event section helps the reader to understand how events are passed among objects without having to simultaneously examine several state models. This improves the readability of the main class diagram.

Input events are classified into internal or external events. *Internal events* are events generated by the classes that belong to the software system. Internal events must correspond to the events raised in the class's state diagram. *External events* are events that are generated by the system's environment. Classifying an event as *internal* or *external* is important during the translation to SMV because the translation will rely on this information to decide how and where to define the variables. We introduce the concept of a special **External\_Event** class, which lists all of the external events. These events are distinct from events generated by system classes because we may make assumptions during model checking about when and in what order these events can occur. This allows us to model check the behavior of the system when it is running under certain environmental conditions. In contrast, it would be invalid for us to constrain when system events occur, beyond those constraints defined by the specification. Other than the special **External\_Event** class, environment classes such as **Engine** class, are not translated to SMV for model checking.

We can define the events that come from the environment in either a centralized or decentralized manner. We proposed to centralize all environment events in a special **External\_Event** class because it makes the design focused on the software system where the software system does not need to know where and how the external events are generated. It makes changes to environment events easier to track because there is only one environment class as opposed to many environment classes. This, in turn, eases the translation to SMV.

The UML state diagram notation does not distinguish between events that are shared or not shared. In our elevator case study, each of the push-button devices that are external to the elevator software system generates a BN\_PRESSED event when the button is pressed. Each BN\_PRESSED event leads to possibly generating an REQ event of a specific button. As such, we cannot model the push button events from the nine push button devices using the same external event name. We distinguish each of the nine BN\_PRESSED external events by declaring nine output events in the event section of the **External\_Event** class. These nine output events of **External\_Event** class correspond to the multiple instances of **Button** and **RequestBn** classes. We distinguish each of these BN\_PRESSED events by explicitly referencing the role names of associations from the **Elevator** class to the **RequestBn** and **Button** classes found in the UML class diagram.

When defining output events, we need to distinguish events that are shared by all of the object instances of the same class. In our elevator case study, the elevator object consumes REQ events, generated by both the OpenBn and CloseBn objects. OpenBn and CloseBn objects instantiates the same Button state diagram where an REQ event is generated whenever a button is pressed. Since the OpenBn and CloseBn state machine do not share the same REQ event, we define the REQ event in the event section of the **Button** class as not shared (i.e., not underlined). Consistent with UML's notation for class-scoped attributes, we would define a class-scoped event where the objects of the same class share the same event name and event value by underlining the event name.

#### Modeling Generalization Relationships

The **RequestBn** class is modeled as a *specialization or subclass* of a more generic **Button** class: a relationship denoted by a link with triangle arrowhead. This means that the **RequestBn** class inherits all the data and behavior of the **Button** class. All **Button** objects react to a BN\_PRESSED event from the environment by generating a corresponding REQ event for the system to process. A **RequestBn** object has the added feature of lighting up when it has issued a REQ event that the system has decided to process, but which the system has not yet serviced. We extend the **RequestBn** class by adding a *pending* attribute to keep track of pending requests.

#### Identifying Class Associations

An *association* represents a semantic connection between two classes. Associations allow objects to communicate through messages and events. The **Elevator** class has an association to **Engine**

class. This association is required in order for the elevator to send requests to the engine to move the elevator up and down. Next, we discuss two types of associations, namely, composition and aggregation.

We use *composition* relationship when one object physically or conceptually contains another object. The larger class is called the *whole* and the smaller class is the *part* or *component class*. We refer to the *part* class of a composition relationship as the *component object*. In a composition relationship, the *part* class cannot be shared by other *whole* classes. For example, we model the Timer object as a *component object* of the Door object: relationship denoted by a line with a solid diamond arrowhead. This means that the Door object solely owns the attribute values and state values of the Timer object. This is important because other objects cannot share the five-second countdown of Timer object.

An *aggregation* relationship is a weaker form of composition. In an aggregation relationship, the *part* class can be shared by other *whole* classes. We refer to the *part* class as the *aggregated object*. We can convert aggregation relationships by creating a whole class and making aggregated objects as component objects of the newly created whole class. For example, we added the **Building** class and converted the aggregated hall buttons (not shown) of the **Elevator** class into component objects of the **Building** class. The result is shown in Figure 4.

We add *adornments* to the associations to provide more details to our specification. At each end of the association, we define the *multiplicity* or the *number of objects* that the class refers to. For example, one of the associations from Elevator to **RequestBn** class shows that there are three **FloorReqBn** objects associated to one Elevator object. A *role name* represents the purpose or capacity an object plays in an association. In our elevator example, we add role names on each of the component class-end of the composite associations (i.e., the end without the solid diamond arrowhead).

We borrow from Statecharts [Hare87] and RSML [LHHR94] the concept of *parameterization* and apply it to generate distinguishable object instances. Multiple instances of the same class are declared in the class diagram to be an array of instances. To achieve this, we annotate associations with role names plus array indices. For example, the Elevator main UML class diagram (Figure 4) declares the three FloorReqBn objects inside of the elevator, distinguished by index values 1..3 representing the three different floors. The class diagram also declares four ElevReqBn objects outside of the elevator, distinguished by one index value representing the

desired direction of travel and a second index value representing the floor. Array indices are used to distinguish between individual objects, for the purpose of identifying objects, events, and the source of an event or specifying the destination of an event. To ensure that the system can handle simultaneous events, transitions that are triggered by indexed events are quantified, to process all applicable events. We describe how to use array indices when constructing UML state diagrams in the next section.

#### Naming Conventions

We use naming conventions when defining our class diagrams in order to improve readability and for ease of translation to SMV.

- We specify class names in mixed cases starting with upper case (e.g., Elevator).

- We specify role names in mixed cases starting with upper case (e.g., FloorReqBn).

- We write attribute names in mixed cases starting with lower case (e.g., prevDest).

- We write operation names in mixed cases starting with a lower case. (e.g., getNextDest).

- We write event names all in upper case (e.g., REQ, BN\_PRESSED); this will easily distinguish event names from operation names.

#### Limitations

The SMV model checker requires the state space to be finite. Therefore, we have to explicitly define the number of objects for each class. We assume that there is only one object if the cardinality is not defined. For class attributes with infinite data types (e.g., unbounded integer), we would also need to abstract the set of attribute values. We also expect our object model to be static over the course of execution. We do not support the dynamic use of constructor and destructor operations in our elevator case study.

### 2.2.2 UML Object Model

Object models are derived from the class diagram. They show *instances* of classes called *objects*. It shows *instances* of associations called *links*. An *object model* emphasizes the specification's object structure where all of the relevant run-time objects are shown. At run-time, each object's state machine runs concurrently with other object's state machine, similar to concurrent regions of a state machine running concurrently.

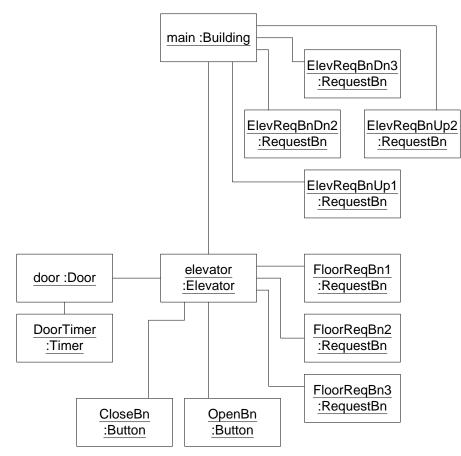

We construct the object model as a requirement before translation to SMV. In this step, we identify the system boundary in order to translate only those classes that are part of the software system. Only the concrete classes (i.e., classes that are instantiated) and the system-controlled classes (i.e., classes without the <<environment >> stereotype) are included in the object model. In UML, we represent an object with a rectangular box where the distinct object name followed by a colon and the object's class name are underlined. Figure 5 illustrates the run-time configuration of the elevator example that will be used for translation to SMV.

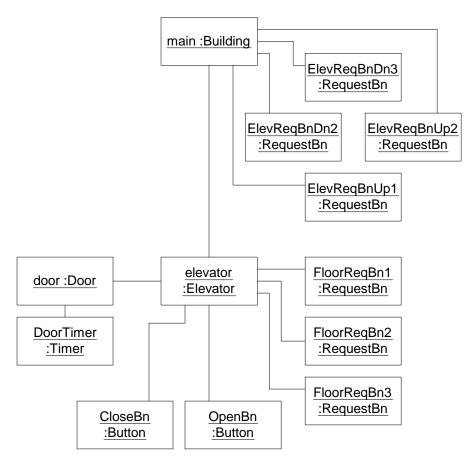

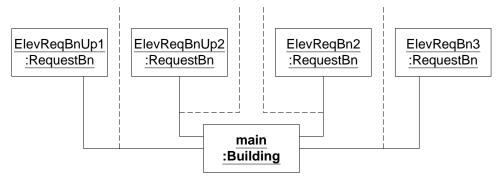

Figure 5: Three-floor elevator object model in UML

We use the following naming conventions to ease translation into SMV. Object names are specified in mixed cases starting with either lower case or upper case. For classes that represent a single object, the object name is the same as the class name starting with lower case. For classes that represent many objects<sup>5</sup>, the object name is the role name. For example, ElevReqBnUp1, ElevReqBnUp2, ElevReqBnDn2, and ElevReqBnDn3 are RequestBn objects representing the

<sup>&</sup>lt;sup>5</sup> Based on the multiplicity of the associations in the class diagram

four hall buttons on the three floors. The object that contains all the other class instances is named **main**.

# 2.2.3 UML Constraints

In UML, a *constraint* is an expression of some semantic condition that must hold whenever the system is in a steady state. It can be added to classes, class attributes, roles and associations.

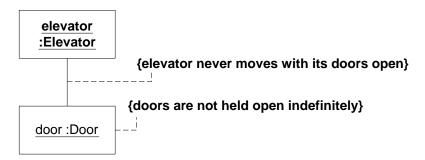

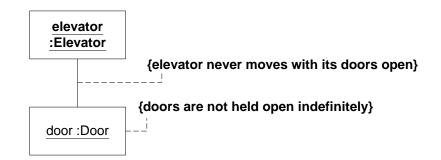

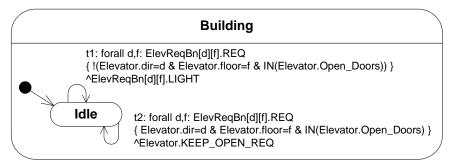

Figure 6: System properties shown as UML constraints

Before the state diagrams and the class attributes are finalized, it is difficult to specify the system properties in terms of object states and object values. Therefore, we write the UML constraints

using the vocabulary found in the problem statement (i.e., without using object states and object values). To avoid clutter, UML constraints are shown separately from the object model, though they are written with respect to the objects and links found in the object model.

Figure 6 shows UML constraints attached to objects and links. The constraint "{doors are not held open indefinitely}" is attached to the door object because only the Door object can achieve this property. The liveness properties "requests are eventually serviced" are related to the links between the request buttons and the elevator that services the requests. The safety constraint "{elevator never moves with its doors open}" is attached to the link between the elevator and the door because it affects both object's behavior. During the translation from UML to SMV, we will rewrite each of these UML constraints in a formal, model-checker-specific language. Details on this translation will be discussed in Chapter 4.

Other UML constraints such as the fairness constraint for environmental variables are defined in the external\_Event object (not shown). Environmental constraints are translated as part of the SMV model. Details of translating environmental events are discussed in Chapter 3.

## 2.3 Defining Object Behavior using UML

In this section, we describe the object behavior of our elevator case study. As we model the elevator example, we will introduce the guidelines in writing UML state diagrams and UML operations.

#### 2.3.1 UML State Machine Semantics

A UML state diagram defines the behavior of UML objects in terms of a state machine. UML semantics allows multiple interpretations of UML state machines. In this thesis, we associate a UML state diagram with a single class. For a class that has many objects, each object is associated with one state machine, which is an instantiation of the state diagram associated with the object's class.

The elevator state machine responds to user requests, input as buttons being pressed. It controls many other classes such as the **Engine** (when and in which direction to move) and the **Door** (when to open or close). The Elevator state diagram shown in Figure 7 is the result of decomposing the state diagram into two orthogonal regions. The first region, New\_Requests, decides whether pressing a floor-request button initiates a pending request (it doesn't if the elevator is already at the requested floor and the doors are open). The second region, Operation, services the pending requests and has two substates (i.e., Stop and Moving) to represent whether the elevator is either stopped or moving. When in the state Stop, the elevator controls the opening or closing of the elevator door. When in the state Moving, the elevator controls whether the engine is moving up or moving down. Within each region, there is a *start-state* icon (drawn as a small filled circle) with a transition<sup>6</sup> pointing to the initial state. The initial state configuration for the Elevator state diagram is state Waiting of the New\_Requests region and state Closed\_Doors within the Stop superstate of the Operation region. The start-state transition of Operation region sets the default values of the elevator attributes floor, destFl, and prevDest to 1, 0, and 0 respectively.

UML state diagrams can be hierarchical. A *superstate* is a state that contains one or more substates. A state without a substate is an *atomic* state. A superstate is either an *and-state*, meaning all its substates are active, or an *or-state*, meaning exactly one of its substate is active

<sup>&</sup>lt;sup>6</sup> We do not assign names to start-state transitions because they are not needed for translation to SMV.

and there are transitions among its substates. The *root-state* is the top-level state that represents the entire state machine. A state is *active* if the state machine is in that state.

## Figure 7: Elevator state diagram

A UML state machine receives *input events* from the system's environment (called *external events*), from other objects within the software system (called *inter-object events*), and from its

own object (called *intra-object events*). Inter-object events and intra-object events are collectively called *internal events* and are defined in event sections of the system-controlled classes. In our Elevator state diagram illustrated in Figure 7, AT\_FLOOR is an *external event* that comes from the environment (i.e., **External\_Event** class). KEEP\_OPEN\_REQ is an *inter-object event* that comes from the Building object that resides within the software system. An event is *set* when the event is raised or generated by the state machine.

The state machine reacts to an input event by (possibly) performing an action and by moving to the same state or to another state. This is called a *state transition*. Our syntax for transition events is derived from the syntax used in Statecharts [Hare87], OMT [RBP+91] and UML [UML99]:

#### label: src[index].event {condition} /action ^ dest[index].event

A state transition is depicted as an arrow originating from a source state to a destination state. It is caused by an *event* and/or a *condition*. An *event-triggered transition* is a transition that is triggered by the occurrence of an event. A *condition-triggered transition* is a transition that is triggered when its guard condition is satisfied. A *conditional event-triggered transition* is a transition is a transition that is transition that is triggered by an event if its guard condition is satisfied. Finally, an *automatic transition* is a transition that has no event-trigger or guard condition. For example, transition t4a of the Elevator state diagram is a conditional event-triggered transition because it is triggered by CLOSED event and has "reopen < 2" as a guard condition.

We introduce the concept of a transition *label* that serves as a macro for the transition's triggering event. Transition labels provide a compact means for prioritizing one transition over another by specifying that a lower priority transition can only occur if the higher priority transition is not enabled (represented as the negation of the latter transition's label). In our Door state diagram (Figure 8), we use transition priorities to specify that transition t4 (KEEP\_OPEN event) has priority over transition t2 (a timeout event) and t3 (CLOSE event) if all these three events happen at the same time<sup>7</sup>.

We also introduce designating the source (*src*) of an input event, because the event's source may affect the state machine's reaction to the event. For example, when the elevator receives a FloorReqBn request, it needs to know which floor the button is associated with, in order to decide

<sup>&</sup>lt;sup>7</sup> Note that while transitions t2, t3, t4 without their priorities may look deterministic since they are triggered by different events, they need not be because multiple events may occur simultaneously. To ensure that the transitions are deterministic, one has to specify transition priorities in the transition events.

whether the request should be serviced. Since this information is encoded in the name of the button sending the event, the source of the event is needed to make this decision<sup>8</sup>. We may also designate the destination (*dest*) of an output event.

**Figure 8: Door state diagram**

Sometimes we may refer to a set of objects with object names that differ only in their indexed value. A benefit of introducing indexed objects is that simple tests and/or actions that need to be performed on a set of indexed objects can be expressed as a formula quantified over the objects' indices. They are represented as *src[index]* and *dest[index]* in our transition syntax presented. Note that we use square braces, which are the traditional condition delimiter, to designate an *index* value that distinguishes an object instance from other instances of the same class. As such, we cannot use square brackets to delimit conditions. Instead, we use curly braces to delimit conditions. For example, the transition t1 uses a quantified formula where state Waiting can receive and simultaneously make decisions about any number of FloorReqBn requests. Without using the quantified formula, we would have to declare three transitions (one for each floor).

In UML, event-processing proceeds as a series of execution steps, initiated by an external event. A transition executes in one *execution step*. A transition executes if at the beginning of a step the system's source state is *active*, its (optional) triggering event is set, and its (optional) condition evaluates to true. The effect of the transition execution is visible at the beginning of the next step, at which point all of the transition's variable assignments have completed, its generated events are set, and its destination state is active. If a transition generates events, these events may trigger

<sup>&</sup>lt;sup>8</sup> Note that storing the floor as an attribute of the **RequestBn** class and sending it as a parameter of the REQ event is not an ideal modeling decision, since the floor never changes as the program executes, so it is not really a variable of the class.

other transitions in the next execution step. An event that is set at the beginning of a step expires at the end of that step (whether or not any transition reacts to it). It is only set in the *next step* if some executing transition generates its reoccurrence. For example, transition t10 executes if the elevator is in state Moving and the guard condition {destFl = floor} is satisfied. When enabled, transition t10 sends an OPEN event to Door, sends a STOP event to Engine and sends an UNLIGHT event to the appropriate RequestBn objects.

UML semantics allows actions to be associated with states. *Entry actions* are executed when the state is entered or reentered. Entry actions are prefixed with "entry:" and we do not add a transition label to entry actions because they do not react to events. In our Elevator state diagram (Figure 7), we associated entry actions to state Closed\_Doors. Upon entry to state Closed\_Doors, the state machine executes getNextDest and getNextDir operations even if the state is entered via a self-transition (e.g., transition t2). "On event" actions are executed within an active state and the state machine stays in the same state after executing an "on event" action. This means that the entry actions are not performed when "on event" actions are executed. The syntax of "on event" actions is similar to the transition syntax discussed earlier. For example, Figure 7 shows transition t11 and t12 as "on event" actions of state Open\_Doors and reacts to an event trigger without reentering the state Open\_Doors.

The UML state machine semantics makes no assumptions about the time intervals between event reception, event dispatching and processing. Analysts will sometimes make assumptions about when input events can occur. One such assumption is the *synchrony hypothesis* [BeGo92], in which the system is assumed to be fast enough to respond to one input event from the environment before receiving a subsequent event. Another assumption is the *single-event hypothesis*, in which the system is assumed to be able to distinguish the arrival order of near-simultaneous events and is thus defined to handle one input event at a time. These assumptions reduce the number of cases in which transitions can execute simultaneously. Such assumptions do not appear explicitly in a UML specification. But for model checking, whether or not such assumptions apply must be known, as they affect constraints on when environmental input events can occur. In our elevator example, we assume that these events occur simultaneously. At the beginning of any execution step, there may be many set external and/or internal events. Multiple transitions may execute simultaneously if they are activated by the same event, if they are activated by different but simultaneous events, or if they are enabled by true conditions.

## 2.3.2 Example Scenarios of Elevator State Machine

In this section, we demonstrate the execution semantics of our UML state machine.

### Two-passenger Scenario

To help understand the elevator state diagram shown in Figure 7, we will trace the steps that make up a sequence of transitions in the two-passenger scenario presented in the problem statement (see Figure 3 of Section 2.1.1). This example exhibits many of the subtleties of UML's concurrent state, nested state and state transitions. We describe this scenario in terms of execution steps as described in our UML state machine definition discussed in the previous section.

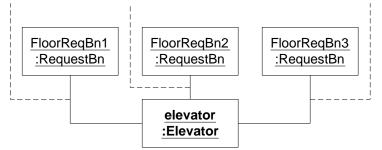

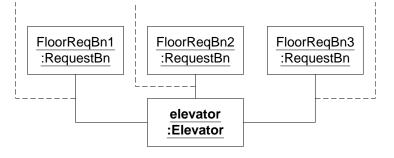

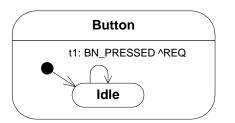

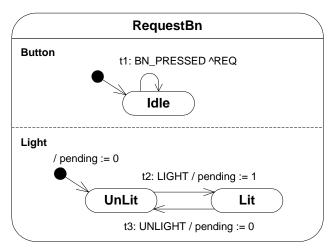

Figure 9: Button state diagram and RequestBn state diagram

**Start of Scenario:** Passenger 1 is inside the elevator, which is on the first floor with its doors open. This is represented as state Waiting in the New\_Requests region and state Open\_Doors in the Operation region. This scenario assumes that the elevator is waiting on the first floor in response to a previous floor 1 request. Thus, prevDest has value 1. There are no pending requests. In Figure 9 (on the right), the scenario starts in state Unlit of the Light region of all RequestBn objects (i.e., the three elevator buttons and the four hall buttons). Thus, attribute destFl has value 0. When the door opened, the DoorTimer object started a timer. The timer has counted down to three right before step 1 starts.

**Step 1.** Environmental Event: Passenger 1 presses the Floor 3 elevator button (i.e., presses a physical push button device for FloorReqBn3 object).

Step 2. External\_Event object generates output event BP\_FloorReqBn3.

Step 3. In this execution step, both REQ and TM events are broadcast.

- a. The state machine for the floor request button FloorReqBn3 (an instance of the RequestBn state diagram shown in Figure 9) responds to the BP\_FloorReqBn3 event (of type BN\_PRESSED) with a self-transition t1, thereby broadcasting event REQ.

- b. Since the door's timer counted down to zero, an internal timeout (TM) event is broadcast by the DoorTimer object.

Step 4. In this execution step, both REQ and TM events are processed.

- a. Transition t1 of the Elevator state machine (Figure 7) reacts to the FloorReqBn3.REQ event by sending a LIGHT event to the FloorReqBn3 object.

- b. The door object reacts to the TM event by moving from state Open to state Close (transition t2 of Door state diagram shown in Figure 8). The door object broadcasts a CLOSED event.

Step 5. In this execution step, both LIGHT and CLOSED event are processed.

- a. FloorReqBn3 responds to the LIGHT event by moving (via transition t2) from state UnLit to state Lit. During this transition, the *pending* attribute of FloorReqBn3 is set to 1 (true).

- b. In Figure 7, the elevator's transition t4 responds to the CLOSED event by moving from state Open\_Doors to state Closed\_Doors.

**Step 6.** On entry to state Closed\_Doors, the elevator calls the *getNextDest* operation. *GetNextDest* is a system-controlled operation that computes the next destination. It finds that FloorReqBn3 has a pending request (i.e., *pending* attribute has value of 1). The *destFl* attribute is updated to 3.

**Step 7.** After the *getNextDest* operation is performed in Step 6, the elevator's transition t5 executes because the guard condition {destFl > 0 and !(destFl = floor)} becomes true. This transition causes a state transition from Stop superstate to Moving superstate of the Operation region.

**Step 8.** Of the two transitions leaving state Init in Moving superstate, the guard condition {destFl > floor} of transition t6 is satisfied, so the elevator now transitions to state Move\_Up and sends

an UP event to the Engine object. The elevator will stay in state Move\_Up until an AT\_FLOOR event<sup>9</sup> occurs.

Steps 1 to 8 show that a transition executes in one step and external events are processed in the next step. A step can process an external event, an internal event (i.e., inter-object event or intra-object event), or a combination of multiple external events and internal events. We assume equal priority of external and internal events. Thus, the analyst has to assign the transition priorities explicitly. Moreover, Steps 3 to 5 show that multiple events can be processed in the same step.

### Modeling a Single Event Generated by Multiple Objects

Multiple objects may generate the same event. We call such an event a *multiple-source event*. UML does not provide guidance in declaring the source of the event that triggers a transition. Whenever it matters, we add the object name of the source as the prefix of the event separated by a dot ("."). For example, REQ event from the OpenBn object will be declared as "OpenBn.REQ". There are two possible ways to refer to a multiple-source event as a *trigger* in a state transition:

- *Unspecified Source*: When the source object of the event is unspecified, we translate this event to mean, "If the state machine receives the event from *any* one of the objects".

- *Fully Specified Source*: When the source of the object is crucial in determining whether the state transition should be enabled, we explicitly write the condition showing the source of the event. For example, transition t1 of Elevator state diagram (Figure 7) has different enabling conditions, depending on the source of the REQ event:

The floor is crucial to setting the light of a specific floor request button because we want to set the light only on the floor request button that has been pressed.

$<sup>^{9}</sup>$  Generating the *AT\_FLOOR* external event is dependent on the environment. In our model, we do not constrain the external events. UML state diagram makes no assumption about the time that it takes for the engine to reach the destination floor.

### Modeling Events with Parameters

In UML, events may pass data as parameters. In the Door state diagram (Figure 8), transition t1 and t4 generate event SET with a parameter 5. Parameters may refer to local attributes or the current state of an object. Parameters of the latter type avoid declaring attributes that store active states. This departs from the UML standard that does not say anything about passing an active state as an event parameter.

# 2.3.3 Inherited State Diagrams

UML does not explicitly require that the state diagram of a subclass adhere to a specific inheritance relationship with its parent class. But the Liskov Substitutability Principle (LSP) [Lisk88] states that a subclass may extend the state-model behavior of its parent class, but must still be substitutable for its parent class. Following the LSP, we aim to reuse the state diagram of base classes when constructing state diagram of subclasses. In this thesis, we restrict the inheritance relationship between a subclass and its parent class using the *strict inheritance model* [McGr93]. Following the strict inheritance model allows reuse of the base class's state diagram when constructing the subclass's state diagram. The strict inheritance model follows two requirements: (1) a method invariant, where (a) pre-conditions of a subclass's method may only be weakened relative to the base class's method, and (b) post-conditions of a subclass's method may only be strengthened relative to the base class's method; and (2) a class invariant, where the base class's specification is a subset of the subclass's specification. This approach allows complex state diagrams to be built with less effort. It also eases translation to SMV by including the SMV specification of the base class as a subset of the SMV specification of the new subclass.

• New attributes can be added and new values can be added to existing attributes. Existing actions found in transitions or state activity section can be modified to set newly added attributes provided the base class's observable behavior does not change with respect to the inherited input events. For example, we add a new pending attribute to the **RequestBn** subclass.

<sup>&</sup>lt;sup>10</sup> The implications of following the strict inheritance model (e.g., a child class cannot delete a state of its parent class) can be found in [McGr93]. For simplicity, we do not include multiple inheritance in our UML models.

- A new concurrent region can be added to an existing state diagram. The region introduces new sub-states and transitions between these sub-states. The transitions can be triggered by new or existing input events, can modify new or existing attributes, and can generate new or existing output events. For example, we add a new Light region to the RequestBn state diagram.

- New states and transitions can be added to an existing state machine if the new transitions from existing states to new states are triggered by only new events [Muth00]. Adding new states while retaining all the existing states means that the post-conditions of the base class's methods are not violated. Adding new transitions to and from the new states must be triggered by new events because the existing behavior of the base class relative to an existing event must be preserved.

- An atomic state can be refined to be a superstate containing two or more substates. The refined state can take advantage of additional information represented by the new substates. This means that we have a more detailed specification and we can construct new system properties (for verification or model checking) that refers to the new substates. For example, we could create a new subclass (not shown) that inherits RequestBn's state diagram where the state Lit is refined to contain substates Low\_Level and High\_Level to indicate the light level when the button light is on.

- Input events can be generalized and output events can be specialized. Existing transitions can be triggered by more general input events and can generate more specific output events. By generalizing input events, a subclass can be substituted for its parent and be sure to accept all of the input its parent would have accepted (it can accept more, but if it is being treated as its parent, it won't be sent more). By specializing output events, the subclass continues to generate output events that its environment will accept (since the environment would accept anything that the parent outputs, and the subclass's output is just a specialization of this).

- *Existing transitions can be modified provided the existing observable behavior is strengthened.* This is achieved by decomposing the existing transition into multiple transitions by modifying the guard conditions.

To ensure substitutability, inherited transitions must have priority over subclass transitions so that the class behaves like the parent class if both inherited and new transitions are simultaneously enabled (e.g., by simultaneous input events). Figure 9 shows the difference between the state diagram of **RequestBn** class (on the right) and that of its **Button** superclass (on the left). All Button objects react to a BN\_PRESSED event from the environment by generating a corresponding REQ event for the system to process. **RequestBn** inherits this behavior shown as Button region. A RequestBn object has the added feature of lighting up when it has issued an REQ event that the system has decided to process. To achieve this, we add a concurrent region (i.e., Light region) that reacts to a LIGHT event generated by Building and Elevator objects. We added substates UnLit and Lit, transitions t2 and t3, and actions to set the *pending* attribute when the button is lit. All the changes and additions to RequestBn state diagram adhere to the strict inheritance model, which means we can substitute RequestBn's state diagram for Button's state diagram, and the original behavior of **Button** class is preserved. If and when the inherited state diagram does not adhere to the strict inheritance model, the translation to SMV is not straightforward.

### 2.3.4 UML Operations

UML Operations<sup>11</sup> are the services provided by the class. To avoid synchronization issues while the UML operation is not completed, we assume that an operation executes in one step. Thus, we model our UML operations as functions. In this thesis, we are interested in using operations to define complex rules that change values within an object. Complex rules are those that cannot be expressed by the use of simple assignment instructions. UML operations may be specified using signatures, pre-conditions, post-conditions and invariants. In the elevator example, the *getNextDest* operation uses the values of the current floor (floor attribute), current direction (dir attribute), previous destination (prevDest attribute), previous direction (prevDir attribute) and pending requests (pending attribute) to calculate the next destination (destFl attribute). Because the *getNextDest* operation has many cases, we use decision tables to graphically separate the different cases and show relationship between input values and post-condition results. For simple functions, we use assignment statements instead of decision tables. We use the SMV logical operators syntax for writing expressions.

Table 1 shows the decision table for finding the next destination. The decision table is divided into two parts by a double solid line. The upper part describes the cases in terms of states and

<sup>&</sup>lt;sup>11</sup> Operation is a conceptual construct, while *method* is an implementation construct. In this thesis, we consistently use *operation* as an action (service) that can be performed by the object.

condition values, while the last row shows the corresponding assignment to the class attribute listed in the leftmost cell (i.e., *destFl*).

The first column in the upper part shows the states of the state machine using the IN operator. The IN operator evaluates to true if the state specified in the argument list is active. The rest of the columns in the upper part show the conditions that must be satisfied in order to set the class attribute to the value shown in the bottom cell of each column respectively. Each cell on the upper part may contain predicates (e.g. value comparison on attributes), functions (e.g., use of IN operator) or macros (e.g., up\_f1\_t1\_1 of Table 2). We use "!" to stand for the logical operator NOT, "&" for logical AND, "]" for logical OR. These logical operators are used in the SMV language and makes translation to SMV straightforward.

| States          | Condition 0   | Condition 1  | Condition 2   | Condition 3 |