# A Framework for Machine-Assisted Software Architecture Validation

by

Kurt Lichtner

A thesis

presented to the University of Waterloo

in fulfilment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Computer Science

Waterloo, Ontario, Canada, 2000

©Kurt Lichtner 2000

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

#### **Abstract**

In this thesis we propose a formal framework for specifying and validating properties of software system architectures. The framework is founded on a model of software architecture description languages (ADLs) and uses a theorem-proving based approach to formally and mechanically establish properties of architectures. Our approach allows models defined using existing ADLs to be validated against properties that may not be expressible using the original notation and tool-set.

The central component of the framework is a conceptual model of architecture description languages. The model formalizes a salient, shared set of design categories, relationships and constraints that are fundamental to these notations. An advantage of an approach based on a conceptual model is that it provides a uniform view of design information across a selection of languages. This allows us to construct alternate formal representations of design information specified using existing ADLs. These representations can then be mechanically validated to ensure they meet their specific formal requirements.

After defining the model we embed it in the logic of the PVS theorem-proving environment and illustrate its utility with a case study. We first demonstrate how the elements of a design are specified using the model, and then show how this representation is validated using machine-assisted proof. Our approach allows the correctness of a design to be established against a wide range of properties. We illustrate with structural properties, behavioural properties, relationships between the structural and behavioural specification, and dynamic, or evolving aspects of a system's topology.

#### Acknowledgements

There are several individuals who deserve recognition for making contributions to this work. I would like to express my sincere thanks to the following people: My supervisor, Don Cowan, for his guidance and encouragment throughout the course of my graduate studies; Paulo Alencar for the endless hours of consultation and time spent proofreading preliminary drafts of this and other works; John Mylopoulos of the University of Toronto, Kostas Kontogiannis and Grant Weddell for agreeing to serve as members of my thesis committee and for their valuable comments and suggestions.

I would also like to thank all my friends at UW and especially the Computer Systems Group for the years of discussion, debate and encouragment - you have helped make my time as a student enjoyable and most of all memorable.

I gratefully acknowlege the financial support of the Natural Science and Engineering Research Council of Canada, the IBM Canada Center for Advanced Studies, the Ontario Graduate Scholarship program and the University of Waterloo's Intstitute for Computer Research.

Last but not least, I would like to express my gratitude to my family, especially my wife Janet for her love and support, and for always understanding what the phrase "just one more year" really meant. Finally, to my daughter Maya for reminding me of the importance of being "all done".

# **Contents**

| 1 | Intr | oductio | n                                              | 1  |

|---|------|---------|------------------------------------------------|----|

|   | 1.1  | Motiva  | ation                                          | 1  |

|   |      | 1.1.1   | Software Architecture Description              | 2  |

|   |      | 1.1.2   | Formal Architecture Validation                 | 3  |

|   |      | 1.1.3   | Applying Formal Methods                        | 4  |

|   | 1.2  | Proble  | m Statement                                    | 5  |

|   |      | 1.2.1   | Expressiveness of Modeling Notations           | 6  |

|   |      | 1.2.2   | Support for Formal Validation                  | 7  |

|   | 1.3  | Propos  | sed Solution                                   | 8  |

|   |      | 1.3.1   | A Specification Framework                      | 9  |

|   |      | 1.3.2   | A Machine-Assisted Validation Framework        | 10 |

|   | 1.4  | Contri  | butions                                        | 11 |

|   | 1.5  | Outlin  | e                                              | 12 |

| 2 | Prel | iminari | es                                             | 14 |

|   | 2.1  | A Mod   | del-based Approach to Architecture Description | 14 |

|   | 2.2  | Introdu | uction to the Model                            | 16 |

|   |      | 2.2.1   | Specification Structure                        | 16 |

|   |     | 2.2.2   | Example Architecture Description           | 17 |

|---|-----|---------|--------------------------------------------|----|

|   |     | 2.2.3   | Modeling Structure                         | 17 |

|   |     | 2.2.4   | Modeling Behaviour                         | 24 |

| 3 | A M | odel of | <b>Architecture Description</b>            | 27 |

|   | 3.1 | Model   | ing Architectural Design Categories with Z | 28 |

|   |     | 3.1.1   | Structure of the Formal Text               | 29 |

|   | 3.2 | Design  | n-time Categories                          | 31 |

|   |     | 3.2.1   | Element                                    | 32 |

|   |     | 3.2.2   | Port                                       | 33 |

|   |     | 3.2.3   | Architectural Types                        | 33 |

|   |     | 3.2.4   | Interface                                  | 35 |

|   |     | 3.2.5   | Library                                    | 38 |

|   | 3.3 | Run-ti  | me Categories                              | 40 |

|   |     | 3.3.1   | Instance and Instance Ports                | 40 |

|   |     | 3.3.2   | Configurations                             | 41 |

|   |     | 3.3.3   | Architecture                               | 43 |

|   | 3.4 | Archit  | ecture Construction Operations             | 45 |

|   |     | 3.4.1   | Add_Library                                | 46 |

|   |     | 3.4.2   | Instantiate                                | 47 |

|   |     | 3.4.3   | Connect                                    | 48 |

|   |     | 3.4.4   | Add_Configuration                          | 50 |

|   |     | 3.4.5   | Implement_Composite and Bind               | 50 |

|   | 3.5 | Initial | State Schemas                              | 53 |

|   | 3.6 | Model   | ing Behaviour                              | 54 |

|   |     | 3.6.1   | Events and Operations                      | 54 |

|   |      | 3.6.2    | Extensions to Interface                         | 55  |

|---|------|----------|-------------------------------------------------|-----|

|   |      | 3.6.3    | Extensions to Library                           | 57  |

|   | 3.7  | Other 1  | Extensions to the Core Categories               | 58  |

|   |      | 3.7.1    | Language Specific Extensions                    | 58  |

|   |      | 3.7.2    | Application Specific Extensions                 | 63  |

| 4 | Arcl | hitectur | ral Specification                               | 66  |

|   | 4.1  | The Pr   | rototype Verification System                    | 67  |

|   |      | 4.1.1    | The PVS Specification Language                  | 67  |

|   |      | 4.1.2    | The PVS Proof Checking Environment              | 68  |

|   | 4.2  | Mecha    | anization of the Model                          | 72  |

|   |      | 4.2.1    | Translation of Schemas                          | 72  |

|   |      | 4.2.2    | Initial Model State                             | 77  |

|   |      | 4.2.3    | Translation of Operations                       | 78  |

|   |      | 4.2.4    | Typechecking the Model                          | 80  |

|   | 4.3  | Case S   | Study: The RPC-Memory Specification Problem     | 87  |

|   |      | 4.3.1    | Problem Statement                               | 88  |

|   |      | 4.3.2    | Problem Specification                           | 90  |

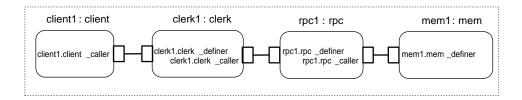

|   |      | 4.3.3    | Specification of Structural Entities            | 92  |

|   |      | 4.3.4    | Specification of Behaviour                      | 98  |

|   |      | 4.3.5    | Behavioural Mappings                            | 106 |

| 5 | Mac  | hine-As  | ssisted Validation                              | 114 |

|   | 5.1  | Verifyi  | ing Properties of the Structural Specification  | 115 |

|   |      | 5.1.1    | Structural Constraints                          | 115 |

|   |      | 5.1.2    | Style Constraints                               | 120 |

|   | 5.2  | Vorify   | ing Properties of the Rehavioural Specification | 123 |

| A<br>B |              | PVS E               | nvironment  VS Language               | 176<br>177         |

|--------|--------------|---------------------|---------------------------------------|--------------------|

|        | The<br>B.1   | PVS EI The PV PVS P | nvironment  VS Language               | <b>173</b> 173 176 |

|        | The<br>B.1   | PVS E               | nvironment VS Language                | <b>173</b> 173     |

|        | The          | PVS E1              | nvironment                            | 173                |

|        |              | -                   |                                       |                    |

| A      | Suii         | indig 0             | 1 Z Symux                             | 109                |

|        | Sum          | mary o              | f Z Syntax                            | 170                |

|        | 7.3          | Future              | Work                                  | 167                |

|        | 7.2          | Evalua              | ation and Discussion                  | 164                |

|        | 7.1          | Summ                | ary                                   | 163                |

| 7      | Con          | clusions            | s and Future Work                     | 163                |

|        | 6.4          | Dynan               | nic Architectures                     | 159                |

|        | 6.3          | Other               | Static Analysis Techniques            | 158                |

|        | 6.2          | Forma               | l Models of Architecture              | 156                |

|        | 6.1          | Archite             | ecture Description                    | 154                |

| 6      | Related Work |                     | 154                                   |                    |

|        |              | 5.4.3               | Validation                            | 149                |

|        |              | 5.4.2               | Configuration Construction            | 147                |

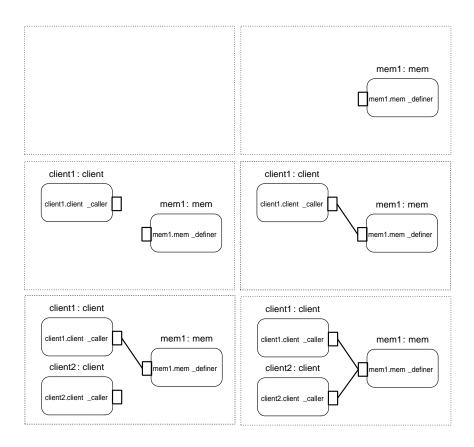

|        |              | 5.4.1               | Architecture Construction Events      | 145                |

|        | 5.4          | Dynan               | nic Architectures                     | 142                |

|        | 5.3          | Verifyi             | ing Structure/Behaviour Relationships | 141                |

|        |              | 5.2.2               | Configuration Behaviour               | 131                |

|        |              |                     |                                       |                    |

# **List of Tables**

| 4.1 | Summary of CSP Expression Syntax. | <br>)( |

|-----|-----------------------------------|--------|

|     |                                   |        |

# **List of Figures**

| 1.1  | An overview of the framework                                    | 9   |

|------|-----------------------------------------------------------------|-----|

| 2.1  | Relationship between the model, ADLs, and architectural designs | 15  |

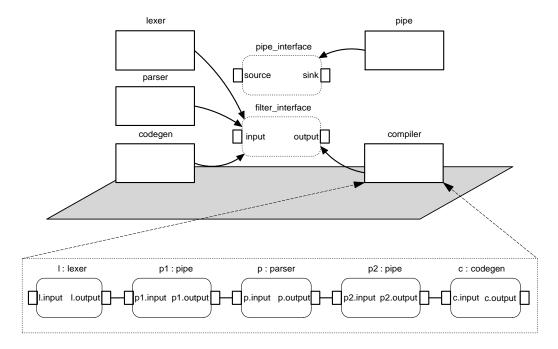

| 2.2  | ADL-based compiler specification                                | 17  |

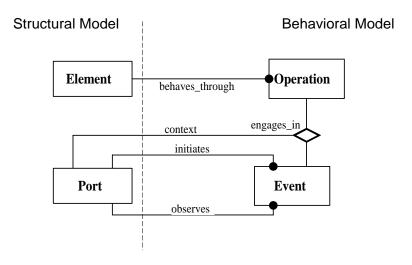

| 2.3  | Model of Structure                                              | 18  |

| 2.4  | Graphical depiction of an architectural element                 | 19  |

| 2.5  | Graphical depiction of an Interface and Ports                   | 20  |

| 2.6  | Graphical depiction of a Library.                               | 21  |

| 2.7  | Graphical depiction of an Instance and Instance Ports           | 22  |

| 2.8  | Graphical depiction of a Configuration                          | 22  |

| 2.9  | Graphical depiction of an Architecture                          | 23  |

| 2.10 | Model of Behaviour.                                             | 26  |

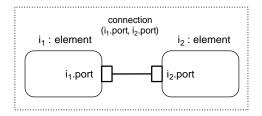

| 3.1  | A connection between two instance ports                         | 49  |

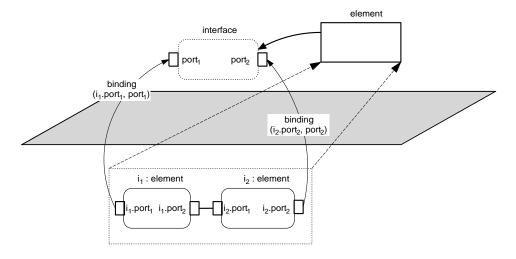

| 3.2  | Bindings between instance ports and ports of elements           | 52  |

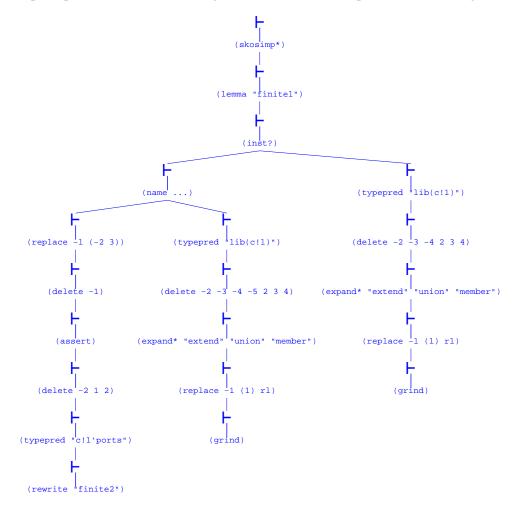

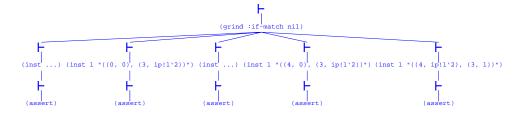

| 4.1  | Proof of the TCC                                                | 85  |

| 4.2  | Specification of the RPC problem                                | 91  |

| 4.3  | Graphical depiction of the system shown in Figure 4.2           | 91  |

| 5.1  | Proof of Property EventsMatch1                                  | 118 |

| 5.2  | Proof of Property <i>Style1</i>                                |

|------|----------------------------------------------------------------|

| 5.3  | Proof of Property ClerkBehaviour                               |

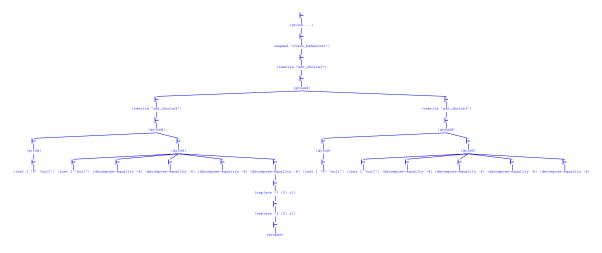

| 5.4  | Portion of Proof for Conjecture <i>ProcCall1</i>               |

| 5.5  | Portion of Proof for Conjecture FirstEvent1                    |

| 5.6  | Proof of Property StructBehaviour                              |

| 5.7  | A system described using architectural construction events     |

| 5.8  | The traces resulting from the system of Figure 5.7             |

| 5.9  | The configurations that correspond to the traces of Figure 5.8 |

| 5 10 | Proof of Property Dynamic.                                     |

## Chapter 1

## Introduction

#### 1.1 Motivation

As the size, complexity and demands placed on software systems have grown, there has been increased effort aimed at developing techniques and notations to support the high-level specification of these systems. The field of *software architecture* has emerged in response to both the recognition of and the need for methods that support a software engineering process at this level of abstraction.

A notable benefit of formally specifying the architecture of a software system is that of early analysis or validation [GP95, PW92]. Analysis at this stage can reveal limitations, oversights, or errors in a system's high-level design specification. Undetected errors or inconsistencies in a system's design are more costly to correct when discovered at a later point in the development cycle [Boe84]. Research activity in architecture specification and analysis has led to a number of formal design notations. Despite making significant inroads for the representation of software architecture, many of these *architecture description languages* (ADLs) and their accompanying tool-sets<sup>1</sup> have either not targeted analysis as a primary goal, or offer varying degrees of sup-

<sup>&</sup>lt;sup>1</sup>We use the term "architecture description language" and "ADL" to refer to both the design language and its

port for mechanized analysis. Supported types of analysis range from parser-driven syntax and type-checking to high-level forms of completeness and consistency analysis. Approaches that do provide more extensive forms of analysis typically allow reasoning over a subset of the total information available within the design.

This work proposes a formal framework that supports an alternate approach to the specification and mechanized validation of architectural designs. Our approach is based on a formal model of architecture description that encompasses a range of existing design notations. Using this formalization we represent an ADL-based design in an alternate mathematical form, one that is directly amenable to formal verification techniques. Specifically, application of this approach introduces new opportunities for detecting errors in high-level system models. Our interest lies in the validation of a design against formally stated properties. We begin by introducing software architecture description and its role in supporting design analysis. We then discuss formal methods and outline their applicability to software architecture.

#### 1.1.1 Software Architecture Description

In recent years modeling notations known as architecture description languages have emerged as the enabling technology for software architecture. These design languages allow architects to construct models of their systems at a high level of abstraction. UniCon [SDK<sup>+</sup>95], Wright [AG94, AG96], Rapide [LV95, LKA<sup>+</sup>95] and Darwin [MDEK95, MK96] are well-known examples of this class of design languages.

Although each of these focuses on a particular set of activities [SG95], these design languages have a significant common core in that they are primarily concerned with capturing the decomposition of a system into its essential high-level computational abstractions and their interconnections [SG94, KC94, Cle96, MT97]. It is generally accepted that the mainstay of architectural

supporting tool-set.

description is a hierarchically defined configuration of architectural *elements* [GP95]. ADLs often further classify these high-level elements as either *components*, which are the basic units of computation, or *connectors*<sup>2</sup>, which mediate the interactions of the components.

This relative importance of system *structure* is reflected in current ADLs, most of which provide similarly extensive support for modeling this aspect of the architecture. By codifying design information that until recently was represented informally through "box-and-line" diagrams [SG96], these notations introduce the possibility of, among other things, applying formal validation techniques to the resulting design.

#### 1.1.2 Formal Architecture Validation

Validation is the process of challenging a formal specification by constructing and attempting to prove theorems that should logically follow from the specification<sup>3</sup> [Rus95a]. The role of a software architecture validation framework is to assist the architect in answering questions regarding the system before it is constructed. For example, does the architectural specification possess certain critical properties or conform to stated constraints? Architectural validation may also serve other purposes, such as comprehension, reuse, re-engineering, or impact and change analysis. A system architect might need to know if the collection of architectural components and connectors remains well-formed after a new component is connected, or if a property still holds when one component is substituted for another.

Architecture validation is performed in the context of a formal system and is therefore dependent upon the use of formal methods. A formalism that supports validation consists of the following components:

• a framework for specifying a mathematical representation of the system;

<sup>&</sup>lt;sup>2</sup>Not all ADLs support the distinction between components and connectors.

<sup>&</sup>lt;sup>3</sup>We also use the term *verification*, although it usually refers to the process of demonstrating that a system satisfies its formal specification [Win90]. We *validate* the system, or *verify* that it possess a property.

- a formal specification language for describing desired properties or correctness criteria;

- a verification procedure to ensure that the criteria are met fully by the modeled system.

In the following section we discuss the role of formal methods applied to the task of specifying and validating architectural designs.

#### **1.1.3** Applying Formal Methods

Formal methods can be used for a precise and unambiguous specification of a system, as well as for providing a rigorous mathematical foundation upon which a variety of formal reasoning techniques can be based. Currently, most applications of formal methods are in the domain of safety- and security-critical systems where the mathematical rigor they impart is recognized as an effective means of establishing the level of required assurance [Rus95a]. The lack of widespread adoption of formal methods across all domains is due to the perceived investment required to produce economically viable returns [Hal90, HPPR95, DR96, HB96, Hal96]. However, continued experience with formal methods is expected to result in the advance of tools and techniques where, through mechanization, the potential costs can be reduced to the point where formalization can be integrated into more mainstream methodologies.

It has been noted that formal methods can offer the largest return for investment when applied early in the design cycle [Rus95b] where discovered errors or omissions are least expensive to correct. Architecture, as the highest level of system design, is an ideal candidate for realizing a return on investment from formalization efforts. Software architecture description has already derived considerable benefit from the application of formal techniques. First, the supporting notations have a well-defined syntax through formal grammar specifications. Given a parser for the grammar, the information contained within a design can be made readily available for further automated interpretation. Second, some have adopted more descriptive formalisms as the underlying semantics for specifying certain aspects of the design. This in turn opens up the

possibility of more specific and useful forms of analysis on the resulting model.

These current approaches to describing architectures can serve as a foundation for more expressive or mechanized representations of architectures. A formal model of the information captured by existing notations can act as a substrate upon which alternate representations can be based, allowing design information to be both specified and formally challenged.

#### 1.2 Problem Statement

Despite widespread recognition that formally verifying properties of an architectural model is useful for uncovering errors or inconsistencies early in a system's development cycle, not all approaches to architectural specification fully support reasoning about the model as a primary goal. Specifically, an architect's initial choice of a modeling notation and its support environment effectively imposes limits upon the nature and scope of follow-on validation efforts. This situation can result in missed opportunities for validating the model and increased likelihood of errors surfacing in subsequent design or implementation activities.

The problem has two important facets. First, existing architecture description languages define a concrete set of syntactic constructs for expressing design information - an ADL simply may not offer the necessary facilities for describing certain required elements of the system. Additional design information, perhaps expressed using an alternate language, generally cannot be incorporated in a meaningful way into an existing description. Second, having defined a model of the system, the support environment might not offer powerful enough reasoning capabilities. Even if the language supports the specification of all required aspects of the system, the analysis environment may be unable to check properties relating to a specific portion of the design.

#### 1.2.1 Expressiveness of Modeling Notations

While current architectural design notations tend to have equivalent support for describing the large-scale structure of a software system, this is where most of the similarities end. As a consequence of focusing on different high-level design activities each notation is founded upon different formal semantics, and in turn formalizes a concrete syntax that directly supports its main activity.

The lack of a common theoretical or syntactic foundation renders each notation descriptively distinct. System models described by one language only have meaningful interpretations within the support environment and tool-sets that are designed explicitly for that notation. Unlike programming languages which are operationally equivalent to Turing machines, architecture design notations share no such common underlying theoretical foundation. Certain categories of information and analyses available within some ADLs are simply not available in the context of others and cannot easily be added to an existing notation by the architect. For example, languages aimed at generating final implementations of the modeled system are typically structure-based and do not address the issue of incorporating a high-level behavioural specification [SDK+95]. This makes them unsuitable for describing high-level patterns of behaviour among system components.

One approach that can be used to overcome these limitations is to specify additional information using external (unsupported) notations and tool-sets. The approach, while a partial solution, is unsatisfactory in that it offers no ability to relate information from within the design to descriptions expressed using external notations. In other words, it precludes the opportunity to specify relationships (perhaps critical) between the supported and unsupported design information.

These issues have more to do with the encompassing scope of software architecture than the shortcomings of any particular design notation. First, no single language could, nor should,

<sup>&</sup>lt;sup>4</sup>Indeed, the focus is usually on associating low-level source-code modules as *implementations* of the architectural-level computational elements.

support the breadth of information and activities that could potentially be handled at the level of architecture. Second, the information needed in the design often varies depending on the application. For example, a description of an architecture with a non-static or evolving structure requires a notation that permits the specification of its allowed structural changes. For an ADL to support a wider variety of purposes it would have to allow extensions to its core syntax. However, a concrete syntax does not readily offer the opportunity to incorporate unsupported design information.

#### 1.2.2 Support for Formal Validation

While the end product of the architectural design phase is a high-level model of the system, there is considerable variability in the intended application of this model. As previously noted, most current design notations share similar descriptive support for a core set of conceptual design categories. However, since each notation and environment targets a particular range of architectural activities, emphasis may or may not include extensive mechanized reasoning. Indeed, the focus on formal validation varies substantially between existing approaches. The choice of a notation for its supported end goal may reduce or even eliminate the possibility of validation.

At the very least, most languages support parser-driven semantic checks of the specification. While this form of analysis is suitable for ensuring that the specification is syntactically correct, as well as for enforcing constraints relating to the legal combinations of typed architectural entities, it is generally unsuitable for reasoning about more complex system properties and relationships.

Languages accompanied by more powerful facilities for formally analyzing designs may not support validation across all of the design information included in the specification. For instance, more expressive notations support both a structural and behavioural characterization of the system. However, existing approaches do not address the issue of verifying properties across the full range of design information in that it is usually only possible to validate the model against properties from a single aspect of the architecture - usually behaviour. Structural information can be

specified but not mechanically checked. This limitation extends to aspects of the architecture that are expressed as combinations of both structure and behaviour related (i.e., hybrid) properties.

Finally, most notations support only a static view of a system. In other words, a system is modeled as a fixed set of architectural elements with a static interconnection topology. However, many real-world software systems exhibit high-level structures that can change over the course of a single execution. These *dynamic architectures* are systems that are best described as a family of related configurations. While some design notations support the specification of dynamic architectures, most either have a static view of system structure or offer no analysis capabilities on the resulting system.

#### 1.3 Proposed Solution

To address these issues, we propose a framework that incorporates the specification and formal validation of architectural designs. The goal of our approach is to provide a systematic means to construct (either manually or in an automated fashion) formal representations of architectural descriptions directly from ADL-based specifications in a form suitable for mechanical reasoning [LAC98]. Our approach centers on a formal *abstract model* of architecture description languages [LAC00a]. This model formalizes a salient, core set of design concepts, relationships and constraints that are invariant across a large class of architectural design notations, including but not limited to UniCon, Wright, Rapide and Darwin. By focusing on shared features, the model provides a uniform representation of design information across these languages.

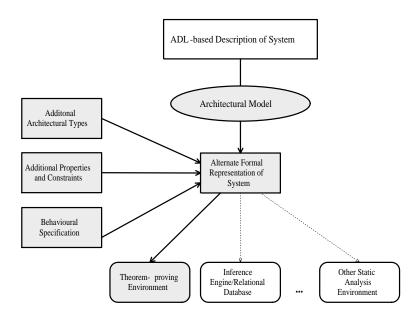

Figure 1.1 presents a high-level overview of our framework. We restrict our attention to the areas shaded with grey. The arrows within the diagram represent the flow of architectural design information (shown in the boxes) through the framework. The shaded oval in the figure represents the model of architecture description that forms the central component of the framework. The model is used as a guide to express the information from existing ADL-based design specifi-

Figure 1.1: An overview of the framework.

cations (shown in the unshaded box at the top of the figure) in an alternate formal representation. This alternate representation can then be augmented with additional design information (depicted in the boxes on the left-hand side of the diagram). The final specification is then subject to formal validation (shown in the round-corner boxes at the bottom of the figure). In this thesis we use a theorem-proving environment that supports validation through deductive proof.

#### 1.3.1 A Specification Framework

An important aspect of the framework is its overall flexibility. The model defines an architectural specification framework with two dimensions of possible extension. First, once a specification is converted into an alternate representation, it can be augmented with any additional design information that is expressible within the context of the chosen formal system. This affords the architect the opportunity to add or substitute design information that may not have been directly supported using the original tool-set. Examples include the definition of new basic architectural types, additional formal constraints or properties, or even behavioural descriptions for the

design's component and connector elements. While the model itself does not provide a formalization of a semantics for expressing system behaviour, it is parameterized with a set of design categories that are intended to act as placeholders for such a definition. These hooks provide a mechanism for mapping elements of a specification to descriptions of their behaviour, allowing previously structure-only specifications to be augmented with behavioural semantics.

Second, the model itself can be extended to incorporate other architectural design categories, including those from other architectural *views* [CN96]. This can be done on a per-application basis to describe information crucial to the application or the follow-on analysis, or on a per-ADL basis to more closely characterize a specific notation. This capability allows the individual users of the framework, i.e., the *architects*, to tailor the amount of detail modeled to that required by their specific design validation needs. This type of extensibility is also important for realizing immediate benefits from continued research in architectural description. Approaches to architectural design should not be considered static. As the field of software engineering matures, new notations or extensions to existing notations are expected to be introduced. A framework that supports extension can potentially take advantage of new advances as they appear.

#### 1.3.2 A Machine-Assisted Validation Framework

The model is an abstract description of a system, and as such there are no *a priori* restrictions on our choice of formal specification language to describe the model. Depending on the desired form of analysis, a representation can be chosen that supports it. For example, formalizing the model using Horn clauses [Pad85] would allow reasoning within an inference engine such as PROLOG [War77]. Alternatively, an Entity-Relationship [Che75] representation would allow analysis based on structured queries on a relational database.

However, by formalizing it within the logic supported by a theorem-proving system we can provide an approach for reasoning about architectural designs based on mechanized formal proof [LAC00b]. The goal of mechanization is important; an automated environment handles te-

dious details allowing the prover to focus on essential issues [VH96] which leads to more reliable proofs than those done by hand [Avr89, GGH90]. The overall (amortized) cost of the verification can be reduced as portions of proofs, or high-level proof strategies can be reused as the system evolves.

The formal system we employ for our machine-assisted verification is higher-order logic ic<sup>5</sup> [And86], as mechanized by the Prototype Verification System [ORS92] (PVS) theorem-proving environment. The main advantage of using higher-order logic is its expressiveness. The basic constructs of the logic are sufficient to represent structural design information directly. Elements of a design are encoded as typed logical expressions and constants. These expressions may be formed or arbitrarily manipulated through higher-order functions. The expressiveness of higher-order logic also allows us to make use of a number of existing alternatives for expressing behaviour; mechanizations of CSP [Hoa85], execution sequence semantics [Tre92] and I/O Automata [LT88], to name a few, are readily available.

This flexibility comes at the cost of fully automated reasoning. The proofs performed will always require some level of guidance from the user. However, the PVS system has many high-level proof commands that can automate significant portions of the proof or capture repeating patterns of proof steps, which help to make the overall effort more economical.

#### 1.4 Contributions

This work develops an extensible model encompassing shared features of existing architecture description languages that provides a foundation for a formal framework supporting the specification and mechanical validation of architectural designs.

The primary contribution of this thesis is the development of a new approach to design-based software architecture specification and validation. The work involved in attaining this goal has

<sup>&</sup>lt;sup>5</sup>Essentially first order predicate logic augmented with typed  $\lambda$ -calculus.

produced the following visible contributions:

- development of a formal model of software architecture description languages;

- development of a mechanization of the model in the context of a formal verification environment;

- application of the formal model for the specification of architectural designs in a logicbased representation;

- use of the framework to validate a system specification formally across application-specific properties relating to structure, behaviour and combinations of both;

- development and demonstration of a technique for specifying and validating models of systems with evolving structure.

#### 1.5 Outline

In this thesis we develop a framework for specifying and reasoning about architectural designs. The central component of the framework is a formal model of architecture description languages. In the following chapter we give a high-level overview of our model-based approach to architecture specification and validation and provide an introduction to the basic concepts of architectural design and of the model. The complete formalization of the model is presented in Chapter 3. In Chapter 4 we discuss the mechanization of the model and describe its use for specifying architectural design information from an illustrative case study within the formal context of a theorem-proving system. We also discuss and give an example of integrating a mechanization of behavioural semantics into the model. In Chapter 5 we discuss how we reason about such specifications, and give examples based on the previously introduced case study. A comparison

of our work with related research is presented in Chapter 6. Finally, in Chapter 7 we summarize our work and outline possible directions for future research.

### Chapter 2

### **Preliminaries**

In this chapter we introduce our model-based approach by describing in more detail how our model relates to both architecture description languages and the designs they produce. We also provide a preliminary introduction to the main design categories formalized in the model. In conjunction with an example specification of a small system, we introduce the terminology and model design categories using both semi-formal and informal descriptions. This is intended to help both illustrate our approach and aid in understanding the model's formal text which is presented in the next chapter.

#### 2.1 A Model-based Approach to Architecture Description

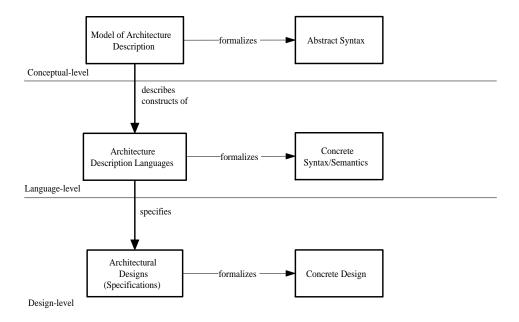

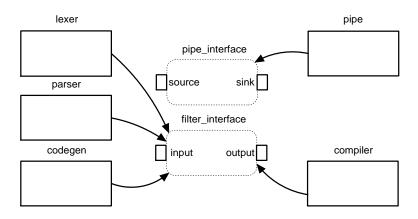

The framework presented here encompasses concepts of three distinct levels of specification related to software architecture: the model, architecture description languages and designs. Throughout this thesis we use the term *model* to refer to our conceptual model, *language* or *notation* to refer to an ADL and *specification* or *design* to refer to a system described using a design notation. The relationship between these specification levels is shown in Figure 2.1.

The central, unifying theme of this work is a conceptual model of architectural description,

Figure 2.1: Relationship between the model, ADLs, and architectural designs.

or an architectural *meta-model*. A conceptual model of a design language is a formalization of an abstract syntax; that is, it defines the information content of a set of syntactic categories and the static semantics of the relationships between them. By modeling this information at an abstract level, a formalization such as this allows a uniform representation of design information from a selection of concrete design notations.

The model supports the activities of architectural specification and analysis. Specification of an architecture is most often facilitated through design languages, which provide a concrete syntax through which design information is encoded. Although the model in and of itself does not constitute a concrete syntax, it describes the constituent components of one and can therefore be used for the purpose of specifying architectural design information. Each category modeled is a formalization of a *class* of design information. *Instances* of the formalized design constructs may be used for encoding the specific information taken from the corresponding constructs of an architectural specification. In this way the basic categories are used to represent elements of

a high-level, concrete syntax. We use this approach in Chapter 4 to encode design information from an architectural description. While currently performed in a manual fashion, the process of converting information from a design into instances of the model can be partially automated by providing a parser for the language that the design is specified with.

#### 2.2 Introduction to the Model

In this section we introduce the main elements of the formalization through semi-formal and informal descriptions of the model's key categories.

#### 2.2.1 Specification Structure

The goal of a formal specification is the precise and readable communication of ideas. With this in mind, particular attention must be paid not only to *what* information is presented, but *how* it is presented. As noted by a number of authors [Hal90, Wor92, BH95, LMZ96] the formal text of a specification can not stand on its own; rather, it must be accompanied by informal but precise supporting text. The primary role of the informal text is to bridge the gap between the initial description of the system and the final formal specification. This includes providing a brief overview of the scope of the formalization, introducing the technical vocabulary and describing data types and constants. Combined, the informal and formal texts constitute a complete specification.

The model is introduced in a series of stages starting with an abstract description and followed by progressively more concrete (and formal) detail. To help develop an intuition of the formalization, we begin by presenting an overview of the main entities in the OMT [RBP<sup>+</sup>91] graphical design notation. This preliminary formalization is intended primarily as a rhetorical aid to introduce the fundamental design categories and relationships, and assist in the comprehension of the model as a whole. We then informally describe and give a graphical depiction of each of the main categories.

#### 2.2.2 Example Architecture Description

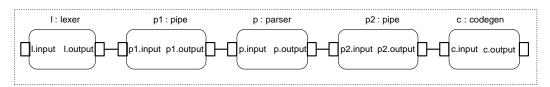

To illustrate the design concepts formalized by the model, we provide a small example system presented in an idealized<sup>1</sup> architecture description language (shown in Figure 2.2). The example describes a simple architecture for a compiler specified in a *pipe-and-filter* [GS92] architectural style.

```

architecture compiler {

element compiler is Component

library {

specified_by filter_interface;

interface pipe_interface {

type Pipe;

element pipe is Connector {

port input : sink

port output : source

specified_by pipe_interface;

interface filter_interface {

configuration compiler_config

type Filter;

implements compiler {

r : l;

port input : dataIn

port output : dataOut

parser : p; codegen : c;

: p1, p2;

element lexer is Component

pipe

specified_by filter_interface;

connect l.output to pl.input;

connect p1.output to p.input;

connect p.output to p2.input;

element parser is Component {

specified_by filter_interface;

connect p2.output to c.input;

bind l.input to input;

element codegen is Component {

bind c.output to output;

specified_by filter_interface;

```

Figure 2.2: ADL-based compiler specification.

#### 2.2.3 Modeling Structure

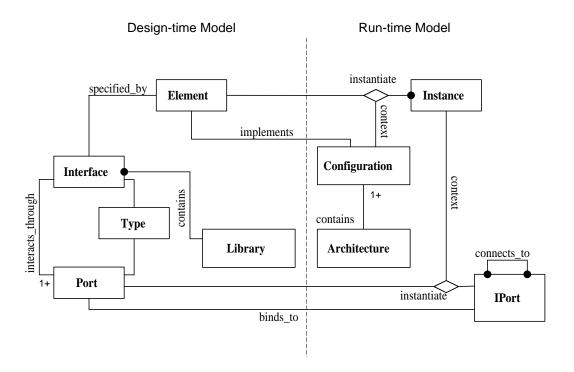

Figure 2.3 illustrates the main elements of the structural model. For clarity we have further subdivided the structural model into two sub-models, a *design*- and *run*-time formalization. The design-time model captures the primitive categories (both finite and infinite) that support the construction of configurations. That is, they represent the building-blocks that are "instantiated"

<sup>&</sup>lt;sup>1</sup>Where, for both clarity and to provide a consistent terminology, the language's syntactic elements have a direct correspondence to similarly named categories defined within the model.

Figure 2.3: Model of Structure.

to form an architecture. The run-time formalization captures the arrangement and connection of instantiated elements within a specification. As it defines the specific topology of components and connectors, elements of the run-time model capture the key configuration information of an architectural specification. We begin by summarizing the basic structural design categories.

#### **Structural Design Categories**

The basic structural model is composed of eight main design categories, their interrelationships and the operations that act upon them. The design categories are defined as follows:

**Definition 2.2.1 (Element)** An architectural element is a basic template corresponding to a component *or* connector *abstraction*.

Components are the architecture's computational elements, while connectors are the glue elements that bind them together, i.e., connectors model the protocols that mediate the interactions of the components. Note that most but not all architecture description languages make an explicit distinction between components and connectors. In this overview we introduce only the category *Element*; however, we do support both components and connectors in the full formalization of Chapter 3. We graphically depict<sup>2</sup> architectural elements as labeled rectangles, as shown in Figure 2.4.

Figure 2.4: Graphical depiction of an architectural element.

**Definition 2.2.2 (Interface)** An Interface defines a collection of "connection point" templates

<sup>&</sup>lt;sup>2</sup>The graphical notation we use is based on one introduced by [Bum96] for describing user interface components. We have extended it to incorporate aspects of architectural specifications.

through which the element interacts with its environment. It also records basic element-type information.

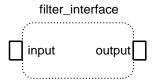

An interface is a specification of how an element "appears" to the rest of the system. Its primary constituent is a set of *Ports* which model the points through which an element connects to other elements. An interface is also responsible for maintaining architectural type information, both for ports and elements. An interface is graphically shown as a dashed box with rounded corners (Figure 2.5).

Figure 2.5: Graphical depiction of an Interface and Ports.

**Definition 2.2.3 (Port)** A Port represents a template for an architectural connection point.

Ports are important abstractions in that they represent a key portion of the endpoints of architectural connections. Languages that distinguish between components and connectors usually distinguish between ports of components and ports of connectors. For example, UniCon labels ports of components as *Players* and those of connectors as *Roles* [SDK<sup>+</sup>95]. Wright uses *Ports* and *Roles* to indicate those of components and connectors respectively [AG94]. We do not make this distinction as it is both redundant (i.e., from a linguistic point of view, a port declared within the context of a component is already a port of a component and need not be redeclared as such), and can be readily specified using the notion of port *type*. The graphical depiction of ports is shown in Figure 2.5 as labeled rectangles.

**Definition 2.2.4 (Library)** A Library models the collection of elements and interfaces defined within an architectural design. It also maintains the relationship between an element and the interface through which it interacts.

While most description languages do not have an explicit construct representing a library, they all allow for a section of the specification to be used as a declarative region for both elements and interfaces. The Library category explicitly models this region by acting as a repository for a design's element and interface definitions. Additionally, a library records the *specified by* association between elements and interfaces. A graphical representation of a library is shown in Figure 2.6. The arrows in this figure depict the relationship between an element and its interface.

Figure 2.6: Graphical depiction of a Library.

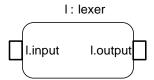

#### **Definition 2.2.5 (Instance)** An Instance is an element that has been instantiated within a design.

The notion of an *Instance* in an architectural design is very similar to that of an instance in an object-oriented language; it represents an element that has been instantiated from its basic component or connector template definition. A graphical depiction of an instance is shown in Figure 2.7. It is represented as a solid box with rounded corners, showing both the instance name and its element type.

#### **Definition 2.2.6 (IPort)** An IPort (Instance Port) models the Port of an Instance.

Instantiating an element has the additional effect of instantiating its port templates. Primarily this is so that each instance will have its own "copy" of the ports declared within its interface. This

Figure 2.7: Graphical depiction of an Instance and Instance Ports.

is necessary for distinguishing between the ports of multiple instances of the same basic element. An IPort is graphically depicted in much the same way as a port. The only difference is that an IPort is labeled with both the instance name and the basic port definition name (as shown in Figure 2.7).

**Definition 2.2.7 (Configuration)** A Configuration is an interconnected set of component and connector instances.

A system modeled at the architectural level of design is represented as a configuration of instantiated elements. The topology of the system is defined by a set of connections between instance ports. A configuration is depicted graphically, as shown in Figure 2.8, as a set of instances within a dashed box outline. The lines between the IPorts represent architectural connections.

Figure 2.8: Graphical depiction of a Configuration.

**Definition 2.2.8 (Architecture)** An Architecture models the full set of design information defined within an architectural specification.

The Architecture design category models a complete specification. Each design has at least one configuration corresponding to the top-level system model. However, our model also supports *hierarchical* system descriptions; that is, an element may be further specified as being *implemented*

by a configuration. An architecture maintains the set of all of the configurations that have been defined, along with the implementation relationship between a configuration and an element. Figure 2.9 shows an architecture. The portion above the shaded dividing area is a representation of

Figure 2.9: Graphical depiction of an Architecture.

the design-time model entities (i.e., those that are contained within the library). The portion below are the entities of the run-time formalization. The dashed arrows represent the *implements* relationship. Note that this relationship must also be accompanied with a description of how the ports of the configuration are associated with the ports of the element. For clarity, the figure omits the specific details of this association. These *binding* mappings are illustrated in Figure 3.2.

#### **Architectural Constraints**

Note that our formalization does not include a design category for the notion of architectural constraints. Although some architecture description languages allow constraint specification on

elements of an architectural design<sup>3</sup>, we have explicitly not captured it with a model design category for two reasons. First, not all languages support the idea of constraints as first-class design categories. Indeed, not all languages even support the notion of explicitly expressed constraints and instead rely on parser-based semantic analysis to enforce implicit constraints.

Additionally, even though the notion of high-level constraints expressed over the elements of a system is a very important one, especially in terms of model validation, the definition of a conceptual model category representing constraints offers little direct benefit. To be useful during an automated analysis phase, we would require additional formal machinery for mapping instances of these categories to sentences of the logic used for representing the design information. Instead, as we illustrate in Chapter 5, it is more useful to specify architectural constraints directly in the same logic that the design is encoded in. In this way these constraints can be incorporated into the analysis phase; the system can be mechanically checked to ensure that it meets these formal requirements.

#### 2.2.4 Modeling Behaviour

Support for the specification of behaviour is not as prevalent within architecture description languages as it is for the description of structure. Rapide and Wright are two examples of ADLs that do support a behaviour specification. Although they are based on different semantic foundation<sup>4</sup>, they share abstract similarities in the way behaviour is specified and component communication is modeled. The main commonalities are that behaviour specification is provided at the level of individual elements, and that the notion of an *event* is used to denote element communication. An event initiated at the port of one element and observed at the port of another is viewed as the discrete communication of information from initiator to observer. This communication can

<sup>&</sup>lt;sup>3</sup>Usually by providing a specification sublanguage based on first-order predicate calculus.

<sup>&</sup>lt;sup>4</sup>Wright uses the CSP process algebra while Rapide uses an execution model based on partially ordered sets of events.

only occur if the ports are connected through an architectural connection. The behavioural design categories we introduce formalize this static, or *syntactic* aspect of event-based component communication: elements are mapped to a behavioural specification, and events are both initiated and observed at ports.

This formalization is not intended to serve as a semantics for describing element behaviour; we have intentionally not attempted to define a more complicated behavioural semantic model as doing so is equivalent to the task of defining a "universal" model of architectural behaviour. Rather, our goal is to provide a generic framework through which a choice of behavioural formalism can be integrated into the model. This type of framework allows flexibility in that a behavioural formalism can be chosen based on its suitability for describing specific requirements of a system, or for permitting a particular type of analysis. We demonstrate how a behavioural formalism is incorporated into the framework in Chapter 4.

#### **Behavioural Design Categories**

Figure 2.10 presents the two main categories of this model, *Events* and *Operations*, and their relationship to categories of the structural model. Within the formalization, the design categories *Event* and *Operation* are uninterpreted; they are provided as placeholders though which a specific behavioural formalism can be incorporated into the model.

#### **Definition 2.2.9 (Event)** The basic unit of element communication.

As mentioned above, components interact by initiating and observing events. This basic communication represents a discrete transfer of information from one point in the architecture to another through a connection. Ports, as the templates for connection endpoints, are the entities from which events are either initiated or observed.

**Definition 2.2.10 (Operation)** An Operation represents an "executable" command of a behavioural specification.

Figure 2.10: Model of Behaviour.

The behaviour of an architectural element is specified as a set of *Operations* that engage in a set of events in the context of a port. Different languages with behavioural support will provide a different interpretations for this category. For example, in the context of the Wright language, an operation is a CSP process. In Rapide it can be interpreted as a transition rule. The *behaves\_through* relationship associates an element with a sequence of values of this type.

## **Chapter 3**

# **A Model of Architecture Description**

In this chapter we present a formalization of the model of software architecture description introduced in the previous chapter. Architecture description languages are predominately defined as text-based notations, although some have an equivalent graphical form (where the syntactic categories are represented by symbols). The process of formalization involves finding suitable formal semantic representations for each category of information expressible by the syntax.

For this work we use the Z specification language [Spi92]. Our choice of Z for the initial definition of the model is a reflection of its effectiveness for communicating information. Z is both well-known and widely accepted within the software engineering community. It has been shown to be clear, concise and relatively easy to learn compared with other formal specification languages [KDGN97].

The model is fully defined in the remainder of this chapter. We begin by first providing an introduction to the Z specification language. Appendix A presents a complete summary of the Z syntax used in this thesis. We then briefly introduce the structure of the model, followed by the formal text itself.

28

**Modeling Architectural Design Categories with Z** 3.1

The Z specification language is a strongly typed formalism based on first-order predicate logic

and set theory. The basic means of formalizing information in Z is by introducing new types. We

use types within our specification to model both the abstract state of the system and the abstract

operations that define the relationships between states.

The complete formal text of the model is composed of Z type definitions, axiomatic defini-

tions and generic constant definitions. We model each of the top-level design categories with one

or more of these constructs. Types are introduced into a Z specification in one of two ways, either

by declaring a given set<sup>2</sup> or a schema.

A given set denotes an infinite but enumerable set of items. For example, the declaration

[NAME]

introduces the set of all names; no other assumptions are made about the type. A given set is

useful for defining types where a more elaborate internal representation is either not required, or

would add no further descriptive power to the specification.

More complicated or structured types are defined with schemas. Besides declaring a new type,

a schema is the basic unit of specification modularity, grouping a collection of related declarations

and predicates into a separate namespace or scope. For example, the schema

$SimplePhoneBook\ [NUM]$  \_\_\_\_\_\_

$entry: \mathbb{P} NAME$

$number: NAME \rightarrow NUM$

$entry = dom \ number$

<sup>1</sup>Recall that the system we model is an architectural design.

<sup>2</sup>Also known as a given *type*.

defines a simple abstraction representing a phone book. Most schemas consist of two sections partitioned by a horizontal line: a *declaration* section above the line and a *predicate* section below the line. As the name suggests, the declaration section introduces a set of named, typed *variable* declarations. The schema given above declares two variables, *entry* and *number*, where *entry* is defined as a set of names, and *number* as a function mapping names to values of type *NUM*. The lower region of the schema contains the predicates that constrain the values of its variables. The predicate in the *SimplePhoneBook* schema states that *number* maps only names of the set *entry* to phone numbers. All constraints appearing in this section are satisfied in every system state; each operation that modifies the state must also maintain these invariants. In formal terms, a schema defines a subset of the cross product of its variables.

The *SimplePhoneBook* schema is *generic* in that it is parameterized by the (undefined) type *NUM*. Before it can be used the schema must be instantiated by providing an actual type parameter in place of this formal generic parameter. This facility allows definitional flexibility: the schema can be used with any type, basic or complex, that models phone numbers. Our formalization makes significant use of parameterized schemas primarily for incorporating ADL-specific architectural type information into a design (discussed further in Section 3.2.3).

#### 3.1.1 Structure of the Formal Text

A fundamental requirement of a formal specification is that it be simple, modular and extensible [LMZ96, vdPHdJ98]. There are a number of reasons why this flexibility is desirable in a specification. First, specifications are rarely written in one pass, but rather are developed iteratively. Modularizing the formal text so that each iteration need not modify the entire specification is crucial. Second, the goal of the specification is the *readable* presentation of information. The individual pieces of formal text must be simple enough that there is no doubt as to *exactly* what is being discussed and that it is indeed correct.

The overall extensibility of the specification is an especially significant requirement of our

30

model. A fundamental tension in any specification is capturing the information at the "right" level of abstraction. Our goal adds another level to this tension - the model must be abstract enough to describe a wide selection of ADLs, while detailed enough to capture their fundamental design constructs. There may be design information not formalized by the model that is necessary for specifying and reasoning about certain aspects of a particular system model. From a practical point of view, partitioning the formal text into a structure that allows architects to readily extend the main (core) categories with additional design information would significantly improve the utility of the model. Conversely, a "good" structure would also allow an architect to remove design information which may not be a critical component of the specification for some applications of the model. A final readability consideration is that it should be obvious to a reader of the specification which information is "core" and which is an "extension".

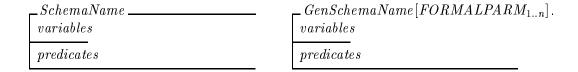

The specification structure we have adopted strives to meet these requirements. We divide the main design categories of the model into a *core* constituent and (possibly) several *extensions*. A design category core is defined as a composite of two schemas: the basic entity sets defined by the category and the relationships and constraints on the entities:

$\_$  Category Core  $\_$  Category Entity Category Relationship

Extensions are useful for capturing design information that is either ADL-specific, application specific, or more naturally (and readably) introduced into the specification at a later point. An extension to a design category is defined by augmenting either or both of the entity and relationship schemas. For example, a new relationship between existing entities could be specified as:

The core and extension schemas are then combined using the schema *conjunction* operator ( $\wedge$ ). The resulting schema represents the complete definition of the design category:

```

Category \ \widehat{=} \ Category Core \land \\ Category ExtExtension_1 \land ... \land Category ExtExtension_n

```

This operation merges the signatures of the schemas and conjoins their predicates. Section 3.7 demonstrates how both ADL- and application-specific information can be added to the model using this mechanism.

Up to this point we have relied on the reader's intuition and good faith in our use of the term "design category" as a collection of entity sets and relationships between them. We now define the notion of a design category core and an extension:

**Definition 3.1.1 (Design Category Core)** A Design Category Core  $C = \langle V, R, \Phi \rangle$  consists of a set V of typed variables, a set R of relations and a set  $\Phi$  of predicates s.t.  $\forall r \in R \bullet dom r \in V \land ran \ r \in V \ and \ \forall \ \phi \in \Phi \bullet dom \ \phi \subset V \cup R$

**Definition 3.1.2 (Extension)** An Extension  $E = \langle V_e, R_e, \Phi_e \rangle$  is an extension of a Design Category Core  $C = \langle V, R, \Phi \rangle$  if  $V \subseteq V_e$ ,  $R \subseteq R_e$  and  $\Phi \subseteq \Phi_e$ .

## 3.2 Design-time Categories

We begin the formal text by introducing the categories of the design-time sub-model.

32

**3.2.1** Element

Architectural elements are the fundamental building-blocks or templates of an architectural spec-

ification. We introduce the element type as a given set:

[ELEMENT]

An element may be either a *component* or a *connector*. Components act as the computational

and data-store elements, while connectors represent the architectural "glue" that mediates the

interactions between components. Although it has been argued that this distinction is required at

the architectural level [Sha96], not all ADLs provide connector abstractions. Our formalization

supports both forms of element, but can be easily extended to more closely characterize languages

that have no support for explicit first-class connectors.

These two basic kinds of elements are distinct yet share many similar characteristics; it can

be useful (when appropriate) to consider them as specializations of the same type. In Z, this can

be accomplished by defining them as disjoint subsets of the ELEMENT type. We introduce the

(infinite) sets of all possible components and connectors as an axiomatic definition:

$COMPONENT : \mathbb{P} \ ELEMENT$

$CONNECTOR: \mathbb{P}\ ELEMENT$

$\overline{\langle COMPONENT, CONNECTOR \rangle}$  partitions ELEMENT

The predicate indicates that the sets of components and connectors are disjoint. Note that Z

considers different subsets of the same given set to have identical type.

Architecture description languages that support the distinction usually make a stronger sep-

aration between the two forms, i.e., they provide two symmetric constructs of different types.

While our definition is non-standard, it has the novel advantage that the representations of both

concepts are identical. This allows us to use the same specification techniques and reasoning

machinery for either category of element, which in turn can shorten both the specification and proofs. Even though their basic structure and type is the same, instances of either element type can still be distinguished if need be as they are partitioned into different sets within the model.

#### 3.2.2 Port

A port is an individual connection point that defines a service an element either offers to, or expects from, its environment. We introduce ports into the model as a given set:

[PORT]

#### 3.2.3 Architectural Types

Architectural types play a role similar to that of types in programming languages in that they provide a means of associating additional semantics to a set of language entities. For example, it is typically more meaningful for readers of a specification to classify elements as either *pipes* or *filters* when dealing with systems defined to be in the "pipe-and-filter" style<sup>3</sup> [AG92].

The precise technical vocabulary introduced by types fulfills a number of roles, both within and outside the context of a specification. First, they establish a meaningful, common vocabulary that permits easier communication between the system's various stake-holders. Second, as alluded to above, they are useful in defining and demonstrating adherence to a particular architectural style. They also provide a basis for a number of parser-driven semantic checks. For example, port typing information is used for ensuring the legality of architectural connections, i.e., the pairs of ports involved in connections must be compatible. Using type information, a parser can also ensure that element interfaces contain only ports that are meaningful within that particular context.

<sup>&</sup>lt;sup>3</sup>Indeed, the notion of *style* is often viewed as being based on a foundation of types. See [SG96] for a thorough introduction to architectural style.

34

Our model supports the inclusion of a predefined set of ADL-specific types for both elements

and ports. We use the generic facility of Z schemas as the basic mechanism for incorporating

this additional type information. Most of our schemas are declared with two formal generic

parameters, one corresponding to a set of supported port types and one to a set of element types.

Additionally, we use a generic constant definition to declare two relations that are used to specify

the legal combinations of these types:

=[PORTTYPE, ELEMENTTYPE]

$export\_map : ELEMENTTYPE \leftrightarrow PORTTYPE$

$port\_map : PORTTYPE \leftrightarrow PORTTYPE$

$\forall \, e : \textit{ELEMENTTYPE}, \exists \, p : \textit{PORTTYPE} \, \bullet \, (e, p) \in \textit{export\_map}$

$\forall p_1 : PORTTYPE, \exists p_2 : PORTTYPE \bullet p_1 \neq p_2 \land (p_1, p_2) \in port\_map$

The parameters PORTTYPE and ELEMENTTYPE serve as a means of integrating ADL-

specific type information into the model. When used to characterize a particular ADL the generic

schemas are instantiated by providing values for these formal parameters.

In addition to the generic parameters, this definition declares two relations, export map and

port\_map, which together model the key semantics of ADL typechecking systems. The ex-

port\_map relation is used to define the legal port types for a particular element type. The

port\_map relation is used for typechecking connections; it encodes the legal combinations of

port types that may interact through an architectural connection. As specified in the predicate

section, these two relations must be defined at each point in their domain.

Some languages, such as UniCon, provide a rich vocabulary of predefined architectural types,

both for elements and their ports. We demonstrate the use of these definitions with an example of

a portion of the UniCon type system. We first define an enumeration of both the supported port

and element types:

```

ELEMENTTYPE\_UniCon == \{Module, Computation, Filter, Pipe, ...\}

PORTTYPE\_UniCon == \{StreamIn, StreamOut, Source, Sink, ...\}

```

The predicate portion of the generic definition is augmented with the specific values of the typemapping relations:

```

export\_map = \{(Pipe, Source), (Pipe, Sink), (Filter, StreamIn), ...\}

port\_map = \{(Sink, StreamIn), (StreamIn, Sink), (Source, StreamOut), ...\}

```

The first two tuple values in *export\_map* state that elements of type *Pipe* can expose ports of type *Source* and *Sink*. Similarly, the first two tuple values of *port\_map* define that ports of type *Sink* and *StreamIn* may be involved in the same connection.

The relations are used by explicitly supplying the actual generic parameters:

```

export_map[PORTTYPE_UniCon, ELEMENTTYPE_UniCon]

port_map[PORTTYPE_UniCon, ELEMENTTYPE_UniCon]

```

Sections 3.2.4 and 3.4.3 demonstrate the use of these relations in the context of the model.

#### 3.2.4 Interface

An architectural element presents an interface to the rest of the system. The primary constituent of an interface is a non-empty, finite set of ports that represents the complete set of interaction points through which an element communicates. This set is defined within the *Interface Entity* schema:

**Definition 3.2.1 (InterfaceEntity)** *InterfaceEntity is defined as*  $\langle interacts\_through \rangle$ , where interacts\\_through is a finite set of ports.

```

Interface Entity \_

interacts\_through : \mathbb{F}\ PORT

interacts\_through \neq \varnothing

```

The predicate portion of the schema restricts the set of ports defined by an interface to be nonempty.

An interface specifies other information regarding its ports, in particular, their type. Additionally, *element* type information is maintained through the interface construct; an interface implicitly defines the type of each element that is specified by it. This additional information is defined within the *InterfaceRelationship* schema:

**Definition 3.2.2 (InterfaceRelationship)** *InterfaceRelationship is defined as the tuple*  $\langle port\_type$ ,  $type\_of \rangle$ , where port\\_type is a mapping from ports to their types and where type\\_of is the element type defined by this interface.

```

Interface Relationship [PORTTYPE, ELEMENTTYPE]

Interface Entity

port_type : PORT \rightarrow PORTTYPE

type_of : ELEMENTTYPE

port_type \in interacts_through \rightarrow PORTTYPE

\forall t : port_type ( interacts_through ) \bullet

(type\_of, t) \in export\_map[PORTTYPE, ELEMENTTYPE]

```

This schema is primarily responsible for maintaining type information, both element and port. It is parameterized by the two types, *PORTTYPE* and *ELEMENTTYPE* (defined in Section 3.2.3). The two predicates of this schema have the following meanings:

• All ports defined by the interface have a type; in other words, the function *port\_type* is total on the set *interacts\_through*.

• For an interface to be well-formed, the type of each port must be compatible with the type of element to which it belongs (as defined by the relation *export\_map*). In other words, for each port, the *export\_map* relation must include a tuple with the appropriate element and port type values.

Having provided definitions of the basic entity sets, relationships and constraints constituting the notion of an architectural interface, we construct a core schema by explicitly including both definitions (note that for readability we omit the generic arguments to the included schemas):

```

\_Interface\,Core\,\,[PORTTYPE,\,ELEMENTTYPE] \_

Interface\,Entity

Interface\,Relationship

```

or, given that the *InterfaceRelationship* schema already includes *InterfaceEntity*, more succinctly as<sup>4</sup>:

```

\underline{\hspace{0.5cm}} Interface\ Core\ [PORTTYPE, ELEMENTTYPE] \underline{\hspace{0.5cm}} Interface\ Relationship

```

An Interface schema is composed from its primary constituents, which, having not yet defined any extensions, consists of just the *Interface Core* schema:

$$Interface [PORTTYPE, ELEMENTTYPE] \triangleq \\Interface Core [PORTTYPE, ELEMENTTYPE]$$

The *Interface* schema formalizes a basic notion that is common to architectural design notations; however, the term, *interface*, is not consistently applied across languages. For example, the properties we formalize closely corresponds to those of the UniCon INTERFACE language

<sup>&</sup>lt;sup>4</sup>While both forms are equivalent, our preference is for the first as the intent of the schema is more clearly illustrated.

construct in that its primary role is to introduce a set of logical, typed architectural connection

38

points. While both Wright and Rapide also have an explicit interface construct, theirs are

used to model different aspects of the architecture. Wright's interfaces capture behavioural prop-

erties that may be shared among a (related) set of ports, while a Rapide interface is a superset

of our definition in that it not only defines a set of ports, but also serves the role of a complete

architectural component.

**3.2.5 Library**

A library represents the sets of elements and interfaces that have been declared in an architectural

specification. Since a given design is, by definition, a finite construction, these sets are finite

as well. We begin the definition of a library by introducing a schema that formalizes the repre-

sentation of the sets of elements (both components and connectors) and interfaces present in an

architectural design:

**Definition 3.2.3 (LibraryEntity)** *LibraryEntity is defined as the tuple (elements, components,*

connectors, contains), where elements, components and connectors are (respectively) the sets of

element, component and connector templates that have been introduced into the specification and

where contains is the set of declared element interfaces.

LibraryEntity \_

$elements: \mathbb{F}\ ELEMENT$

$components: \mathbb{F}\ COMPONENT$

$connectors: \mathbb{F}\ CONNECTOR$

$contains: \mathbb{F} \ Interface$

$\langle components, connectors \rangle$  partitions elements

$\forall i, j : contains \mid i \neq j \bullet$

$i.interacts\_through \cap j.interacts\_through = \emptyset$

Commentary:

- The set of elements declared within the design is composed of the union of two disjoint subsets, the set of components and the set of connectors.

- No interface shares a port with any other interface. That is, the sets of ports through which any two interfaces interact are disjoint.

A library also maintains the relationship between an element and its interface. This mapping is formalized in the *LibraryRelationship* schema:

**Definition 3.2.4 (LibraryRelationship)** *LibraryRelationship is defined as*  $\langle specified\_by \rangle$ , *where* specified\_by *is a mapping from an element to its interface.*

#### Commentary:

• Each element is specified by an interface and each interface defines *at least* one element; that is, the *specified\_by* mapping is a total *surjective*, or "many-to-one" relation.