## Efficient Simulation of Message-Passing in Distributed-Memory Architectures

by

Erik Demaine

A thesis

presented to the University of Waterloo in fulfilment of the thesis requirement for the degree of

Master of Mathematics

$_{

m in}$

Computer Science

Waterloo, Ontario, Canada, 1996

©Erik Demaine 1996

I hereby declare that I am the sole author of this thesis.

I authorize the University of Waterloo to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize the University of Waterloo to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research. The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### Abstract

In this thesis we propose a distributed-memory parallel-computer simulation system called *PUPPET* (Performance Under a Pseudo-Parallel EnvironmenT). It allows the evaluation of parallel programs run in a pseudo-parallel system, where a single processor is used to multitask the program's processes, as if they were run on the simulated system. This allows development of applications and teaching of parallel programming without the use of valuable supercomputing resources. We use a standard message-passing language, MPI, so that when desired (e.g., development is complete) the program can be run on a truly parallel system without any changes.

There are several features in PUPPET that do not exist in any other simulation system. Support for all deterministic MPI features is available, including collective and non-blocking communication. Multitasking (more processes than processors) can be simulated, allowing the evaluation of load-balancing schemes. PUPPET is very loosely coupled with the program, so that a program can be run once and then evaluated on many simulated systems with multiple process-to-processor mappings. Finally, we propose a new model of direct networks that ignores network traffic, greatly improving simulation speed and often not significantly affecting accuracy.

### Acknowledgements

First and foremost I would like to thank my advisor, David Taylor. He provided great support throughout my programme. I am overly impressed by how fast he reads my papers while catching the mistakes. I would like to thank the two readers, Thomas Kunz and Ken Salem, for their comments on this work. Thomas has also read some of my papers, to which he provided crucial comments, even on short notice. Ken Salem amazingly took on the role of a reader only one week before this thesis went on display.

A large part of this thesis was the experiments, which required parallel systems. The Shoshin group provided the network of IBM RS/6000 workstations. Thanks to the Dept. of Oceanography of Dalhousie University for access to Dalhousie's IBM SP2. Joe Potworka of IBM made several tools and contacts available, including the SP2 at Queen's University. Christian Foisy provided test programs and access to the SP2 at Université de Sherbrooke. The interest expressed by the above people made this work more enjoyable.

Without my friends here at the University of Waterloo, my programme would have been tremendously boring. I would like to thank in particular Research Associate Mike Nidd for his help in getting this acknowledgement section to work, among other things.

Most of all I would like to thank my father, Marty Demaine, for his continual love and support, particularly when I was frustrated gathering results. He also gave impressive comments for someone who knew little about the subject. My dog, The Missing Link, was particularly good at guarding my house while I worked. Although he didn't make any comments, I think he understands the world more than anyone.

Thanks go to the many bands and musicians for making great music that helped a lot during the writing phase, and in fact all my writing. Contemporary artists include REM, U2, The Cranberries, Timbuk 3, and The Tragically Hip; classical artists include Amadeus Mozart, Ludwig van Beethoven, Johann Sebastian Bach, and George Gershwin.

Finally, thanks to the Natural Sciences and Engineering Research Council (NSERC) and the Information Technology Research Centre (ITRC) for their financial support.

## Contents

| 1        | Intr    | oducti  | on                          | 1  |

|----------|---------|---------|-----------------------------|----|

|          | 1.1     | MPI     |                             | 3  |

|          | 1.2     | PUPP    | ЕТ                          | 4  |

|          |         | 1.2.1   | Features                    | 5  |

|          | 1.3     | Outlin  | e                           | 7  |

| •        | <b></b> |         | C                           |    |

| <b>2</b> | Lite    | erature | Survey                      | 8  |

|          | 2.1     | Paralle | el-Computer Simulators      | 8  |

|          |         | 2.1.1   | Overall Organization        | 9  |

|          |         | 2.1.2   | Simulation-Program Coupling | 10 |

|          |         | 2.1.3   | Method of Timing            | 12 |

|          |         | 2.1.4   | Network-Simulation Accuracy | 14 |

|          |         | 2.1.5   | Language                    | 15 |

|          |         | 2.1.6   | Parallelism and Concurrency | 16 |

|          |         | 2.1.7   | Survey                      | 18 |

|          | 2.2     | Simula  | ating Components            | 21 |

|          |         | 2.2.1   | Processor Simulators        | 21 |

|   |     | 2.2.2                   | Network Simulators           | . 23 |

|---|-----|-------------------------|------------------------------|------|

| 3 | Pro | posed                   | Evaluation Technique         | 26   |

|   | 3.1 | Timin                   | ag a Pseudo-Parallel Program | . 27 |

|   | 3.2 | Netwo                   | ork Simulation               | . 29 |

|   |     | 3.2.1                   | Overall Model                | . 30 |

|   |     | 3.2.2                   | Network-Link Model           | . 31 |

|   | 3.3 | Point-                  | to-Point Communication       | . 32 |

|   |     | 3.3.1                   | Routing                      | . 32 |

|   |     | 3.3.2                   | Switching                    | . 33 |

|   | 3.4 | $\operatorname{Collec}$ | etive Communication          | . 36 |

|   |     | 3.4.1                   | Multicasting                 | . 37 |

|   |     | 3.4.2                   | Other Collective Operations  | . 40 |

|   | 3.5 | Discre                  | ete-Event Simulation         | . 41 |

|   |     | 3.5.1                   | Overall Architecture         | . 41 |

|   |     | 3.5.2                   | Algorithm                    | . 44 |

|   |     | 3.5.3                   | Multitasking                 | . 47 |

| 4 | Imp | olemen                  | atation                      | 51   |

|   | 4.1 | MPI                     |                              | . 51 |

|   |     | 4.1.1                   | Point-to-Point Communication | . 52 |

|   |     | 4.1.2                   | Collective Communication     | . 53 |

|   |     | 4.1.3                   | Unsupported Features         | . 54 |

|   | 4.2 | Loggin                  | ng Library                   | . 55 |

|   |     | 4.2.1                   | Other Logging Libraries      | . 56 |

|              | 4.3 | User Interface               | 57 |

|--------------|-----|------------------------------|----|

|              | 4.4 | ParaGraph                    | 61 |

|              | 4.5 | Network Evaluator            | 61 |

| 5            | Exp | periments and Results        | 63 |

|              | 5.1 | Test Programs                | 64 |

|              |     | 5.1.1 Merge-Sort             | 64 |

|              |     | 5.1.2 Cholesky Factorization | 65 |

|              |     | 5.1.3 Scalable BLAS          | 68 |

|              | 5.2 | Simulation Accuracy          | 68 |

|              |     | 5.2.1 Ethernet               | 69 |

|              |     | 5.2.2 SP2                    | 73 |

|              | 5.3 | Speed of Simulation          | 78 |

|              | 5.4 | Scaled Speedup               | 80 |

|              | 5.5 | Load Balancing               | 81 |

|              | 5.6 | Different Topologies         | 83 |

|              | 5.7 | ParaGraph                    | 87 |

|              |     | 5.7.1 Merge-Sort             | 87 |

|              |     | 5.7.2 Cholesky Factorization | 88 |

| 6            | Con | clusion                      | 93 |

|              | 6.1 | New Features                 | 94 |

|              | 6.2 | Future Work                  | 95 |

| $\mathbf{A}$ | Rav | v Data                       | 96 |

Bibliography

101

## List of Tables

| 2.1         | A summary of various distributed-memory parallel machine simula-     |     |

|-------------|----------------------------------------------------------------------|-----|

|             | tors, including PUPPET                                               | 19  |

| 3.1         | The latency of various switching techniques.                         | 36  |

| 4.1         | Overview of the MPI standard by chapter                              | 52  |

| A.1         | Accuracy results for the Ethernet                                    | 97  |

| A.2         | Accuracy results for Cholesky factorization on the SP2               | 97  |

| A.3         | Accuracy results for the scalable BLAS library on the SP2            | 98  |

| A.4         | Various speedup metrics for the merge-sort program, as evaluated     |     |

|             | by the simulator.                                                    | 99  |

| A.5         | Convergence of the simple load-balancing scheme.                     | 99  |

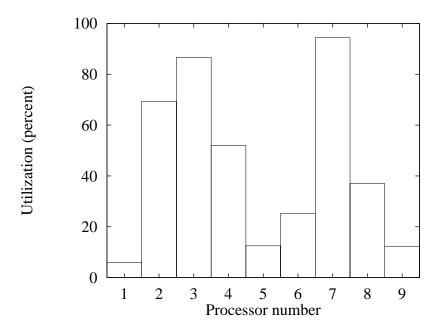

| <b>A</b> .6 | Utilization (in percent) of the nine processors used to solve a 32-  |     |

|             | process merge-sort problem for two process-to-processor mappings     | 100 |

| A.7         | Scaled speedup for the merge-sort program with two different topolo- |     |

|             | gies                                                                 | 100 |

# List of Figures

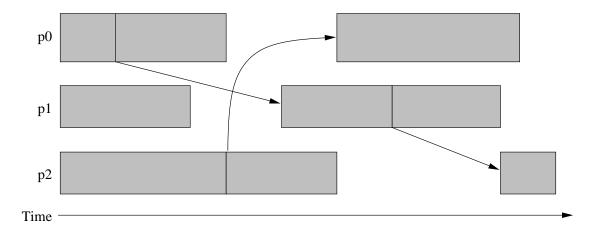

| 3.1  | A sample parallel-program execution, illustrating the notion of com-   |    |

|------|------------------------------------------------------------------------|----|

|      | putation blocks                                                        | 29 |

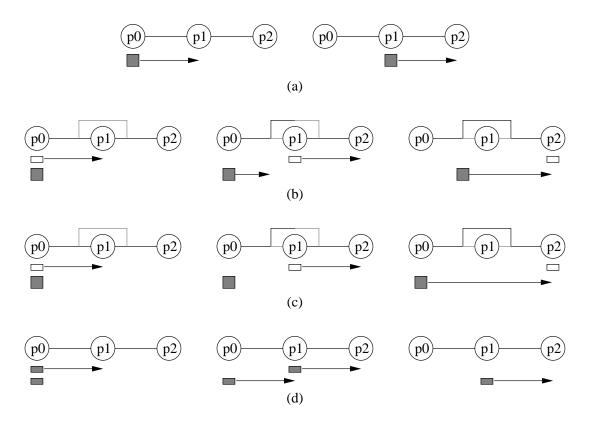

| 3.2  | Illustration of the various switching techniques on a 3-processor lin- |    |

|      | ear array.                                                             | 34 |

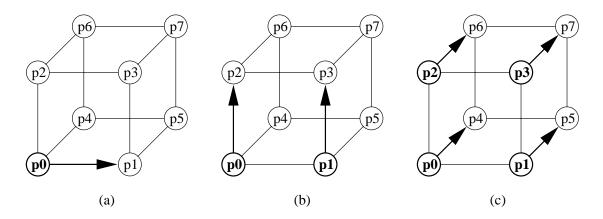

| 3.3  | An example of the smart multicasting approach: the hypercube           |    |

|      | broadcast algorithm.                                                   | 38 |

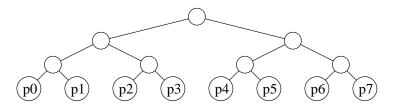

| 3.4  | A complete binary tree multicast-network                               | 39 |

| 3.5  | Architecture of the discrete-event simulation, illustrated by a small  |    |

|      | example                                                                | 42 |

| 3.6  | Pseudo-code for the discrete-event simulation.                         | 45 |

| 3.7  | Pseudo-code to process an event (non-multitasking version). $\ldots$   | 46 |

| 3.8  | Pseudo-code to schedule operation-issue events (non-multitasking       |    |

|      | version).                                                              | 46 |

| 3.9  | Pseudo-code to schedule operation-issue events (multitasking version). | 48 |

| 3.10 | Pseudo-code for advancing a process's computation to a specified time. | 49 |

| 3.11 | Modification of completion case for Procedure Process_event to allow   |    |

|      | multitasking.                                                          | 49 |

| 4.1  | BNF-like grammar for a model file, an input to the simulator                                            | 58 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 5.1  | The two column-oriented serial Cholesky-factorization algorithms. $% \mathcal{L}^{(n)}_{\mathcal{L}}$ . | 65 |

| 5.2  | The fan-in parallel Cholesky-factorization algorithm.                                                   | 66 |

| 5.3  | The fan-out parallel Cholesky-factorization algorithm                                                   | 67 |

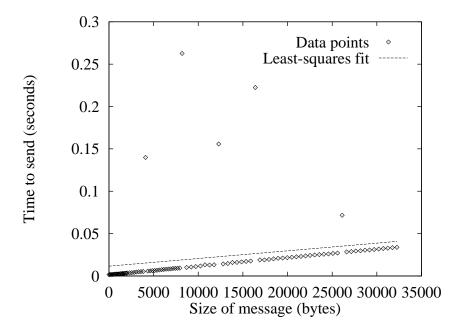

| 5.4  | Raw data from the network evaluator applied to the Ethernet net-                                        |    |

|      | work, with a least-squares fit.                                                                         | 70 |

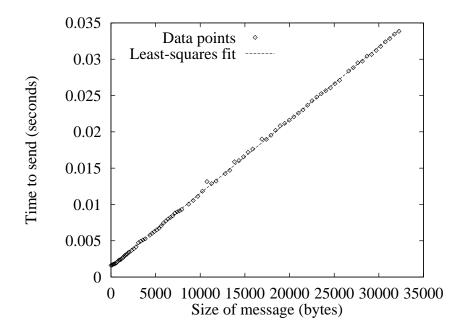

| 5.5  | Data from Figure 5.4 with outliers removed.                                                             | 71 |

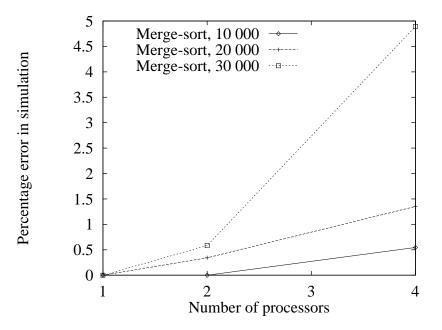

| 5.6  | Simulation accuracy for the merge-sort program on the Ethernet. $% \mathcal{A}^{(n)}$ .                 | 71 |

| 5.7  | Simulation accuracy for the Cholesky-factorization programs (fan-in                                     |    |

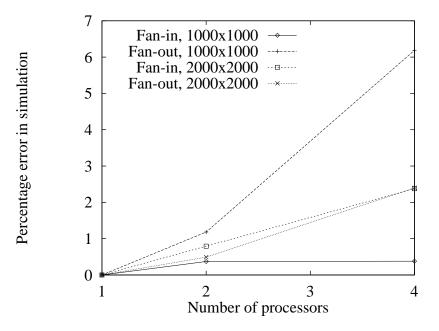

|      | and fan-out) on the Ethernet                                                                            | 72 |

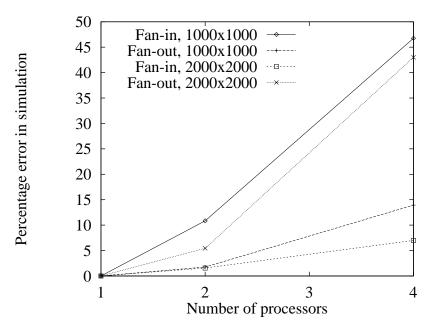

| 5.8  | Simulation accuracy for the Cholesky-factorization programs (fan-in                                     |    |

|      | and fan-out) on the SP2                                                                                 | 74 |

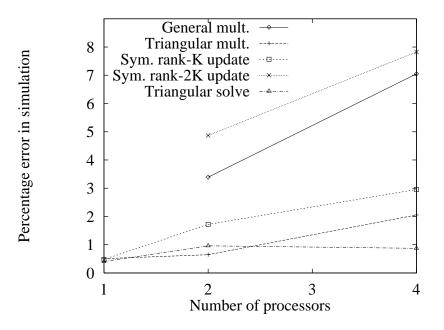

| 5.9  | Simulation accuracy for the Scalable BLAS with a $800\times800$ matrix                                  |    |

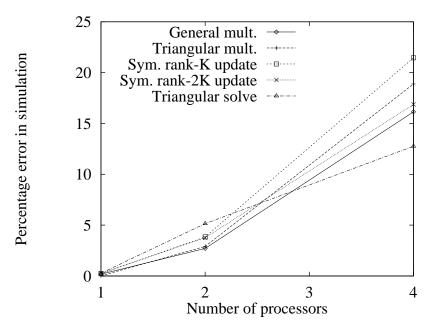

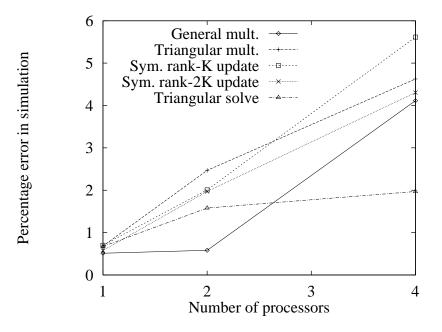

|      | on the SP2.                                                                                             | 75 |

| 5.10 | Simulation accuracy for the Scalable BLAS with a $1600 \times 1600 \ {\rm matrix}$                      |    |

|      | on the SP2.                                                                                             | 76 |

| 5.11 | Simulation accuracy for the Scalable BLAS with a $2400 \times 2400 \ \mathrm{matrix}$                   |    |

|      | on the SP2.                                                                                             | 77 |

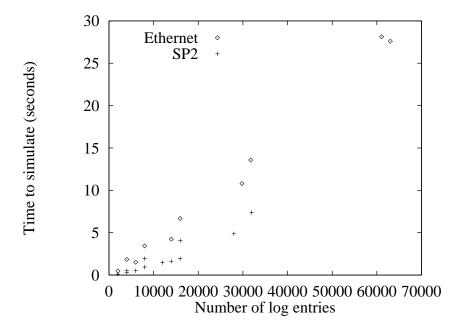

| 5.12 | Time for a node of the SP2 and a RISC/6000 to simulate Cholesky-                                        |    |

|      | factorization executions on the SP2 and the Ethernet, respectively                                      | 79 |

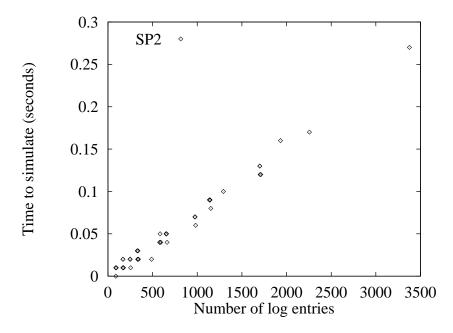

| 5.13 | Time for a node of the SP2 to simulate various Scalable BLAS pro-                                       |    |

|      | grams                                                                                                   | 79 |

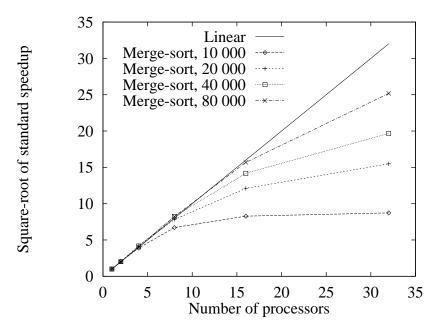

| 5.14 | The typical notion of speedup (time for serial algorithm over time     |    |

|------|------------------------------------------------------------------------|----|

|      | for parallel algorithm) for the bubble-based merge-sort algorithm on   |    |

|      | the simulated Ethernet                                                 | 81 |

| 5.15 | The square-root of typical speedup for the bubble-based merge-sort     |    |

|      | algorithm on the simulated Ethernet.                                   | 82 |

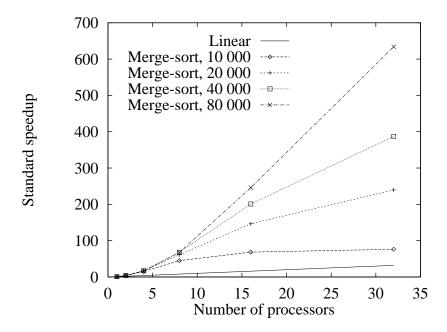

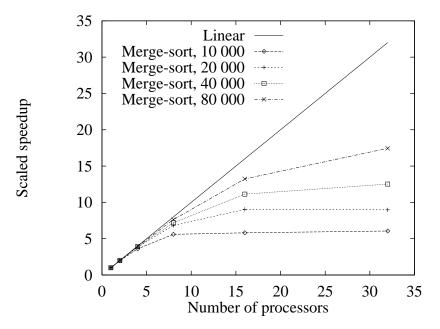

| 5.16 | Scaled speedup for the bubble-based merge-sort algorithm on the        |    |

|      | simulated Ethernet.                                                    | 82 |

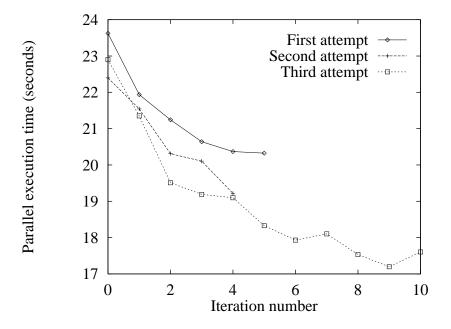

| 5.17 | Iteration-by-iteration view of the simple load-balancing scheme for    |    |

|      | fan-in for three attempts                                              | 84 |

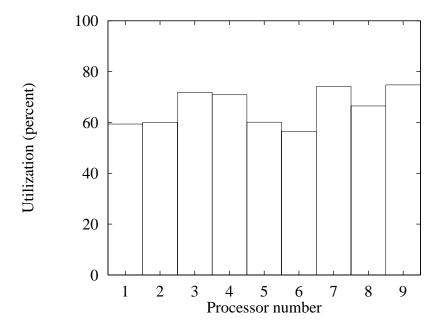

| 5.18 | Utilization of processors for initial random mapping of attempt three. | 84 |

| 5.19 | Utilization of processors for best mapping found in attempt three      | 85 |

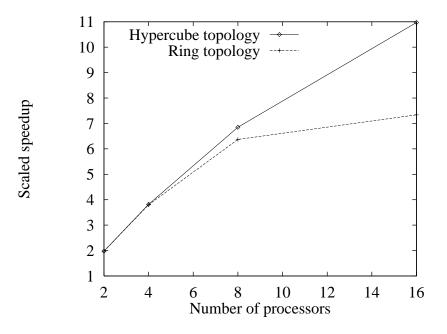

| 5.20 | Scaled speedup for merge-sort program for two different topologies.    | 86 |

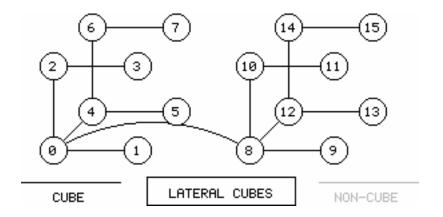

| 5.21 | The hypercube display after animation for the merge-sort program.      | 87 |

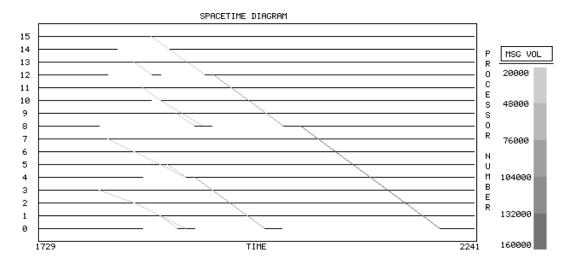

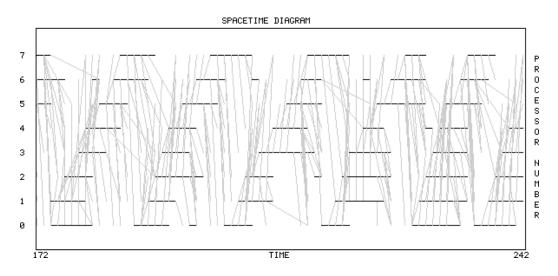

| 5.22 | The tail-end of the space-time diagram for the merge-sort program.     | 88 |

| 5.23 | A window of the space-time diagram for the fan-in program              | 89 |

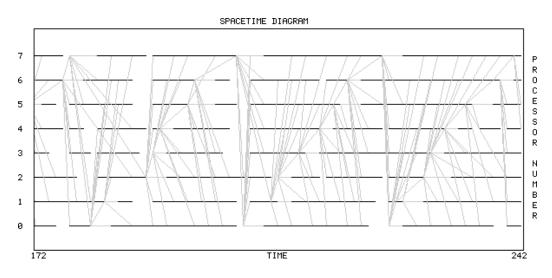

| 5.24 | A window of the space-time diagram for the fan-out program. $\ldots$   | 90 |

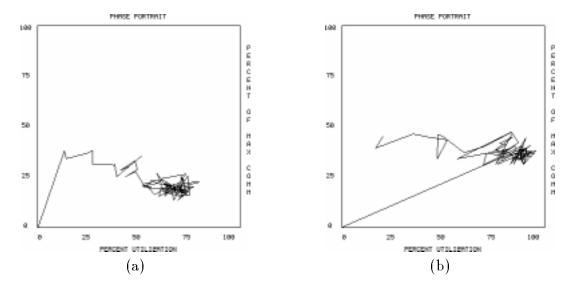

| 5.25 | Phase portraits for fan-in and fan-out.                                | 90 |

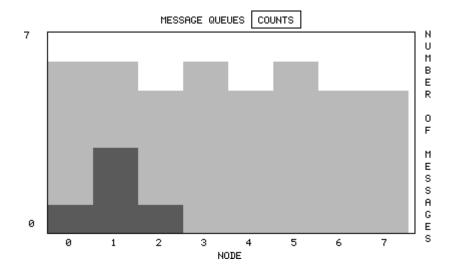

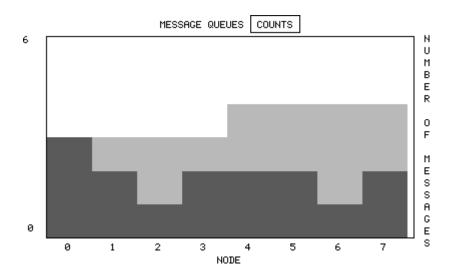

| 5.26 | A snapshot of the queue lengths at each processor for fan-in, includ-  |    |

|      | ing the maximum sizes reached so far                                   | 91 |

| 5.27 | A snapshot of the queue lengths at each processor for fan-out, in-     |    |

|      | cluding the maximum sizes reached so far.                              | 92 |

## Chapter 1

## Introduction

A popular method for testing parallel programs, which we call *pseudo-parallelism*, is to use a single workstation and emulate a parallel computer via multitasking or multithreading. One can develop, debug, and test the correctness of a parallel application, without using valuable supercomputing resources. To use such resources at the development phase of a program is most often a waste. For example, it may not yet be clear that an iterative algorithm ever satisfies a convergence condition, causing an infinite loop; this may in turn cause problems with the supercomputer's scheduler. It is also useful to run a program in interactive mode for debugging purposes, which is not possible in several supercomputing setups. Once the program is ready to go, one can port the program to a desired parallel computer; this is usually a simple task provided a portable language is used.

Another important application of pseudo-parallelism is education. Educational institutes do not need to obtain expensive supercomputing resources to teach parallel programming. Students obviously do not require high performance to obtain experience in parallel programming, provided there exists a parallel environment on the pseudo-parallel system that has similarities to a "real" parallel computer.

A problem does arise, however. How do students know how efficient their programs are? For example, how much speedup would be achieved if the programs were run on a particular truly parallel system? This question does not only apply to students; researchers would greatly appreciate insight into the performance of their parallel algorithms without the use of supercomputing resources. In particular, this applies to performance debugging; since supercomputing power would not (yet) be fully exploited, and so should not likely be used.

The solution is to simulate the supercomputer, subject to the parallel program as the "workload." At least conceptually, the processes are delayed at certain points of execution so that the processes think that they are running on a supercomputer, and that they are running in parallel. One can then measure a value such as the total parallel execution time, and hence derive speedup.

The area of parallel-computer simulation is new and a great amount of interest has been paid in recent years; previous work is detailed in Chapter 2. However, there is still a significant amount of work to be done. We shall focus on distributedmemory parallel computers, since they offer higher scalability and performance than shared-memory multiprocessors; in addition, less interest has been given to the simulation of distributed-memory systems. Some of the topics which we address in this thesis are ease-of-use, trading accuracy for efficiency, and the simulation of multitasking. We also see how simulation can be used in combination with performance-visualization tools (such as ParaGraph) and with the message-passing standard MPI.

### 1.1 MPI

*MPI* (Message-Passing Interface) [40] is becoming an industry-wide standard for message-passing. The MPI Forum consists of universities, research centers, national laboratories, and multi-national high-performance-computing vendors. MPI was designed by over forty organizations and sixty people. The initial version, MPI1 [29], was published in June, 1993. The latest MPI (1.1) [55] was published in late 1994. MPI-2 will be published this year at Supercomputing'96. The goal is to create a universal communication language implemented on all parallel systems. The MPI Forum studied the existing message-passing systems, and instead of taking one as the "standard," they took the most attractive features out of these systems. MPI is based on CHIMP, PICL, EUI (for IBM SPx), Zipcode, p4, CMMD (for CM5), TCGMSG, PVM, NX (for Intel NX/2), PARMACS, Express, and Chameleon [55]. The main advantage of MPI is portability; it has been implemented (both in public domain and commercially) on a variety of parallel systems and networks of workstations. Many free MPI implementations, such as LAM [13] and MPICH [10], support pseudo-parallelism.

Several libraries for profiling MPI programs have been developed [10]. Unfortunately, all of them rely heavily on a shared real-time clock and record events of a program execution with this value. When the MPI program is run in a pseudoparallel manner, this does not provide data useful for predicting behavior in a truly parallel environment. First, since multiple processes must share the machine, each pseudo-processor effectively sees the machine at 1/nth of its speed, where n is the number of pseudo-processors (we do not take into account the operatingsystem overhead of context switches, making real-time values even worse). Thus, if the program is completely parallel, no speedup would be reported by a typical MPI profiling library. Second, communication is measured incorrectly: on a single uniprocessor workstation, no network is involved and the operating system converts "message passing" to shared-memory references, which are often much faster operations. Even on a parallel computer, using real-time often yields incorrect results: the latest supercomputers, as they rarely cost under US\$10,000,000 [37], are often shared, and so both the CPU and network speed viewed by the profiling library are inaccurate.

### 1.2 PUPPET

As we have seen, on both pseudo-parallel and truly parallel computers, the existing MPI profiling libraries are insufficient when full parallelism is not available. The proposed system, called PUPPET, attempts to remedy this problem with a set of tools including an MPI profiling library that is based primarily on (user) CPU time and ignores communication time (since this is inaccurate without full parallelism). The profiling library (or *logging library*) is based on the assumption that a program consists of computation and communication, and ignores other factors such as I/O. The *simulator* (another tool provided) takes a program execution log along with information about a network, and estimates true parallel execution time and speedup based on this network. Finally, the *network evaluator* is a program that estimates the network speed assuming that the computer is dedicated to running the evaluator.

PUPPET is useful in several ways. It allows effective evaluation of parallel programs without the use of a parallel computer (that is, on a pseudo-parallel machine). Researchers can implement various parallel algorithms and compare their running times and speedups. When one technique is chosen, it can be run on a supercomputer without any change to the program's code. Students can implement and test parallel programs and can also compare them; no supercomputing resource at their university is required. In fact, a student can estimate program run-time on any distributed-memory supercomputer, testing different topologies and speeds of the network. Assuming sufficient memory is available on the workstation, as many (pseudo) processors as desired may be used, thereby testing scalability of algorithms without a massively parallel computer.

### 1.2.1 Features

A key difference between PUPPET and existing parallel-computer simulations is that PUPPET is designed for MPI. To use PUPPET does not involve learning a new (simulation) language, and possibly recoding existing algorithms in that language. In fact, one need only link in the logging library, run the program as usual, and then run the simulator to collect results. The simulator can be run many times on the same log with various simulation parameters. This allows several questions such as "what if I used the following hypercube multicomputer instead?" to be answered rapidly. The main theoretical contribution of PUPPET is its approximate network model, which is what makes the simulation phase so fast. The idea is to ignore network traffic and congestion, and simply approximate the time to send a message by assuming an otherwise isolated system. For most applications, this does not significantly affect accuracy, but it has a much better performance than, say, a detailed network simulation.

PUPPET uses CPU time and a non-traffic network model. Sometimes it may be useful to obtain higher accuracy than what these features offer. Fortunately, PUPPET is a fairly flexible system. It is possible to use other computation-time measures, such as augmentation or instruction-level simulation, as well as a network simulator or a different analytical model. There is no point in developing such components in this project, since they have received significant attention before.

PUPPET supports all deterministic features of MPI. In addition to typical send/receive operations, non-blocking operations (including a wait operation to delay until an operation completes) are available. One can also use synchronization, multicasting, reduction, and other collective operations of MPI. As far as we know, these features are unique to PUPPET.

Several modern-day programs exploit concurrency in addition to parallelism. That is, they use more processes than available processors. PUPPET has the ability to simulate multitasking, and so it allows such programs. This allows one to evaluate various load-balancing schemes.

### 1.3 Outline

The rest of the thesis is organized as follows. Chapter 2 surveys existing work done on parallel-computer simulation, as well as various processor and network simulators. In Chapter 3 we present the methods of PUPPET in a theoretical manner. We describe the implementation of PUPPET in Chapter 4. Chapter 5 gives results validating PUPPET and shows its usefulness in combination with performance-visualization tools. Finally, we conclude in Chapter 6 and overview possibilities for future work.

## Chapter 2

## Literature Survey

In this chapter we look at related work that has been described in the literature. Section 2.1 describes competing parallel-computer simulators and compares them to PUPPET. In Section 2.2, we examine simulators for components of parallel computers that have the potential of being used in conjunction with PUPPET. We discuss processor and network simulators in Sections 2.2.1 and 2.2.2, respectively.

### 2.1 Parallel-Computer Simulators

Many vendors have examined the use of simulation to evaluate the performance of parallel computers prior to building them. Researchers have also used simulation to evaluate new techniques for solving problems, in particular, cache coherency. Much of the development in parallel-computer simulation has targeted shared-memory systems, which are not of interest to us. Such simulators include Chief [12], MINT [77], SPASM [68], PSIMUL [70], Talisman [3], Tango [24], and Threads [53].

Unfortunately, far less attention has been given to simulation of distributedmemory (message-passing) systems. The known projects that have addressed this problem are the topic of this section. They have a variety of common properties, and hence we cover common features instead of going into detail for each simulator. Similarly, we compare the individual features (instead of entire systems) to PUPPET.

### 2.1.1 Overall Organization

Most modern-day simulators involve discrete-event simulation (that is, are eventdriven) [32]. This means that (a finite number of) events control the simulation; for example, their occurrence causes the advance through time. The simulator essentially "waits" for an event to occur, does some processing, and then continues. The times at which events occur are the only points when anything is done; these computations usually depend on the nature of the event. Most events are not known ahead of time: processing an event usually involves creating new events. The main advantage of discrete-event simulations is that events can be scheduled at any time.

An alternative to the event-driven approach is *discrete-time* (time-driven) [32] simulation. In this method, there is a global clock that all resources (e.g., processors) are consistent with. During each iteration, some operations are done, and the clock is incremented by a constant amount. One way to use this is to mark events with a *time-left* attribute which says how many clock ticks are left until the event occurs; when the clock is incremented, this value is decreased, and when it

reaches zero the event is executed. This makes the simulation inflexible in terms of granularity of timings. In order to achieve complete generality, the clock unit would have to be extremely small, for example, a microsecond; this however would cause a large overhead if no events occurred during entire seconds.

If time cannot easily be discretized into multiples of a single value, then timedriven simulations are ineffective. For this reason, all simulators that we know of are based on the discrete-event technique.

### 2.1.2 Simulation-Program Coupling

Some simulations are designed to measure the performance of a parallel computer, and assume an artificial workload such as "delays between message-sends follow a negative-exponential distribution" (for example, a similar assumption is made in Calahan and Bailey [14]). On the other hand, we are interested in the case where the workload is generated by the user's parallel program. There are two ways that the program can describe the workload to the simulator, which involve different levels of coupling between the simulator and the program.

The first option, which is used in PUPPET, is to have a *loose coupling* (sometimes called a *trace-driven* simulation [31]). The program executes on an arbitrary *host*, such as a pseudo-parallel system, and records a log of its communication and (amount of) computation. Then as a post-processing phase, the execution is simulated with a particular parallel computer in mind. Note that none of the simulation parameters come into play when the log is generated. Therefore, various options can be tweaked and the program can be re-simulated, without needing to re-run it. Assuming that the simulation is fast (as it is with PUPPET), a complex program can be evaluated for many platforms in little more time than required for a single platform.

An alternative is to make a *tight coupling* and in fact combine the simulator and the program. The program is instrumented either by the user or an automated tool so that relevant events are handled by the simulation portion. Various delays are made so that the program thinks that its environment is the simulated system. This has the obvious disadvantage that the simulation is not a post-processing phase and model changes require a complete re-execution. It does, however, have two main advantages that are worth noting.

First, no log files are created. For extremely long-running programs, loose coupling causes particularly large logs to be created. In such cases, however, it is likely well worth using loose coupling if even two sets of model parameters are to be tested.

Second, processes are allowed to be non-deterministic in the way that they communicate with others. For example, suppose that a process attempts to receive a message, but it may timeout. With a loose coupling, the process might timeout in the pseudo-parallel environment although it would not have in the parallel computer being simulated. On the other hand, a tightly coupled simulation would correctly detect whether a timeout occurred.

Fortunately, there are a wide variety of applications (e.g., most scientific codes) that are *network-deterministic*<sup>1</sup>, that is, the timing of the various communication

<sup>&</sup>lt;sup>1</sup>We add the "network" qualifier to avoid confusion with the non-determinism involved with random numbers.

events affects little in the program other than speed. In these cases, loose coupling applies well.

In the future, it would be worth considering the extension of PUPPET to have the option of being tightly coupled to the program. This would broaden the set of potential uses of PUPPET.

### 2.1.3 Method of Timing

The program's computation is timed by either a log-generator (for loose coupling) or by the simulator itself (for tight coupling). In either case, the way in which we measure the computation cost of a particular block of code is important. There are three basic techniques that are commonly used in simulators, each with its own advantages and disadvantages.

Instruction-level simulations are the most accurate possible. They use processor simulators (see Section 2.2.1) to simulate each instruction of the program, thereby determining the time to execute a particular group of instructions. This allows complicated factors such as caches and the speedup of vector operations to be accurately measured. Unfortunately, instruction-level simulations cause programs to speed-down by around 300 times [71]. It also takes significant effort to build a simulator for a particular processor, and building a portable instruction-level simulation is almost impossible. Since the overhead of instruction-level simulations is so high, it does not make sense in combination with loose program-simulation coupling.

Another possibility is to time computation using CPU time, such as the facil-

ity provided by UNIX (sometimes called an *execution-driven* simulation<sup>2</sup>). The advantage of this method is that it is extremely portable and easy to implement. However, most UNIX systems limit their accuracy to multiples of ten milliseconds. This can be insufficient for very fine-grain programs. The method also requires that the program run on a processor identical to one of the simulated parallel computer.

Much of the recent simulation development has been towards program augmentation, which is a compromise between the previous two methods. Augmentation was first used by Threads [53], later refined in RPPT [19], and perfected in Tango [24] and Proteus [8]. The idea is to count (at compile-time) the number of processor clock cycles required for each basic block (a block of code without any control flow or communication instructions) by examining the involved instructions. The code is then instrumented so that the simulator is notified of any computation done in terms of clock cycles. This fails to take into account caches and vector operations (as the instruction-level approach did), although it is more accurate than CPU time. Augmentation is faster and more portable than instruction-level simulations, although it still takes a fair amount of effort to support a wide variety of processor architectures.

Other advantages of augmentation include non-intrusive debugging and profiling. The simulator will not notice any differences if the program is a little less efficient because of adding profiling or other data-collection code used for debugging, provided that the basic blocks of the added code are ignored by the augmenter. This is in contrast to a parallel computer (or any live system) where the *probe ef-*

<sup>&</sup>lt;sup> $^{2}$ </sup>Unfortunately, the augmentation method is also sometimes called execution-driven [20].

fect [35] may cause a phenomenom to disappear when one attempts to measure it. In addition, augmentation allows unfortunate errors such as stack overflow to be detected and reported in an efficient way [7].

The above three advantages are also possible with instruction-level simulations. In fact, the most common use of processor simulators is to exactly evaluate performance of the processor, avoiding the probe effect. Stack overflow is also easy to detect and report, although it cannot be done as efficiently as augmentation; the stack pointer must be checked after each instruction instead of each basic block<sup>3</sup>.

Currently, PUPPET uses the CPU-time approach. Given time to do so, augmentation could also be implemented. Augmentation essentially provides the same information as CPU time, but with higher accuracy.

#### 2.1.4 Network-Simulation Accuracy

In addition to processor-timing accuracy, we can also examine the amount of accuracy obtained in simulating the network. The most common method is to employ a network simulator (see Section 2.2.2). This allows the measurement of all network latencies, including routing, traffic, and congestion (i.e., hot spots). Unfortunately, network simulations often take a significant amount of time. Thus, the major advantage is accuracy and the major disadvantage is speed.

The obvious simplification is to use an analytical model to approximate the latencies and improve performance. Agarwal [1] proposed a model for a wormhole-

<sup>&</sup>lt;sup>3</sup>It is possible to improve on this. For example, provided that the stack-pointer is at least 100 units from overflowing, the processor simulation could continue for 100 units before checking (or some fraction thereof, depending on what kinds of instructions are available).

routed k-ary n-cube interconnection network (an n-dimensional  $k \times k$  torus) embedded into two-dimensional space. The model attempts to take into account congestion based on the frequency of past requests, providing speedups of between two and four over a detailed network simulation [9]. Unfortunately, such models do not yet exist for all networks, and it may be difficult or even impossible to create models with reasonable accuracy for some networks.

Another approach, proposed in Sections 3.2 and 3.3, is to ignore congestion caused by multiple messages. In other words, the arrival time of a message is calculated as if the network were otherwise empty. This method yields immense performance benefits and (as we shall see in Section 5.2) often maintains considerable accuracy. Currently, it is the method used by PUPPET, but it is certainly possible to extend PUPPET to allow the other methods to be used.

Such an ability to vary accuracy would be extremely useful. It would allow one to get a rough idea of performance during debugging and testing, and also get high accuracy with the flick of a switch. If a loosely coupled simulation is used, this can even be done without re-running the program.

#### 2.1.5 Language

An important human factor of parallel-computer simulation is its ease-of-use. A significant part of this is the programming paradigms (i.e., *languages*) that the simulator supports. The best scenario is that the program is written in a supported language; for example, an MPI program to be used with PUPPET. Usually, little user effort is required to simulate fully supported programs. Popular message-

passing environments include MPI and PVM (Parallel Virtual Machine) [37]. In addition, programs written in parallel languages (which eventually translate into message-passing programs) may be used; a small sample of them consists of HPC (High Performance C) [30], HPF (High Performance Fortran) [51], and pC++ [4].

Unfortunately, simulators do not always directly support a popular parallelprogramming language. This implies that the user must first spend a certain amount of time learning the language. If the parallel program is already written, it must be converted to that language. These steps can be very tedious and should be avoided whenever possible.

### 2.1.6 Parallelism and Concurrency

Our final consideration is parallelism present within the simulator. In simulating a parallel program, some authors claim that there is inherent parallelism available, which can be exploited to yield good speedup [26, 71]. The idea is that the simulator needs to use communication only when the program's processes communicate. Essentially, the parallelism from the program is carried over to the simulator.

For tightly coupled simulation systems, this makes sense: part of the overall system is the parallel program. Parallelization is effective since typically the overhead is in the computation-measurement process described in Section 2.1.3.

It is questionable how useful a parallel simulator is, since parallel resources are rare. However, networks of workstations (NOWs) and workstation clusters are becoming increasingly popular; even having two processors to simulate many would be beneficial. Unfortunately, because of several complications (e.g., a mix of both operating-system multitasking and hand-written multithreading), few tightly coupled simulators allow parallelism, and those that do usually sacrifice some efficiency in the process.

On the other hand, loosely coupled systems can automatically exploit parallelism. This is because the simulation is broken up into two phases: the parallel program execution (which is parallel) and the post-processing simulation (which is serial). The execution includes the major source of overhead mentioned in Section 2.1.3, namely computation measurement, and there is no reason that the execution cannot use a parallel system. Hence, for these systems (such as PUPPET), parallelism can already be easily achieved.

An issue related to parallelism, briefly mentioned above, is how concurrency is provided. The simplest option is to allow the operating system to see the processes, and allow it to multitask them. This often yields a very high overhead, although it allows parallelism to be accomplished (for example, UNIX processes can execute on multiple processors). An alternative is to provide custom multithreading code, greatly improving task-switching latency and message-passing efficiency. However, this method requires that the entire program be run in pseudo-parallel and so performance enhancement via parallelism is not possible.

PUPPET does not necessarily take either option; rather, it depends on the underlying MPI implementation. To date, all UNIX-based MPI implementations use UNIX processes; however, it is quite possible that a multithreaded implementation could be developed. Such an effort has been made by Villanueva [75] for PVM. The results are very impressive: 50,000 processes can be used efficiently on a personal computer.

#### 2.1.7 Survey

We shall now briefly describe various distributed-memory parallel-computer simulators, relative to the above considerations. Their characteristics are summarized in Table 2.1.

The Rice Parallel Processing Testbed (RPPT) [19] was developed at Rice University. It is based on top of the parallel language Concurrent C [52], also from Rice, which provides multithreading support. The Parallel Tracer/Debugger (TRAPP) [20] allows graphical debugging of the program.

Proteus [8] is the most advanced parallel-architecture simulator, developed by Brewer and Dellarocas at M.I.T. for their Master's theses [7]. The authors claim it to be "fast, accurate, and flexible" [9]. It achieves its speed partly from augmentation and its built-in threads, and partly from its module system (which also provides flexibility). The idea is that there are several implementations for each task (such as network simulation), each with its own level of accuracy and efficiency. Proteus also provides some useful graphical utilities for generating plots of performance data.

The EPPP simulator [63] is an extension of Proteus for High Performance C (HPC) [30] programs. Even though it is augmentation-based, the simulator attempts to evaluate pipelining and vector operations. The EPPP (Environment for Portable Parallel Programming) project [47] provides other tools for HPC, including a performance visualizer and debugger. It is based at the Centre de Recherche

| he | ПРРЕД. Т                   | cludina Pl     | chine simulators in | whe 2.1: A summary of narious distributed-memory narallel machine simulators including PUPPET. The | narious distributed                | mmary of 1             | able 2.1: $A_{SH}$          |

|----|----------------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------|------------------------------------|------------------------|-----------------------------|

|    | Varies                     | $N_{O}$        | MPI & NX            | No traffic                                                                                         | CPU time                           |                        | PUPPET                      |

|    | Varies                     | $N_{O}$        | PVM                 | No traffic                                                                                         | Augmentation                       | Either                 | APNM [67]                   |

|    | $\mathbf{Y}_{\mathbf{es}}$ | $N_{O}$        | pC++[4]             | Accurate                                                                                           | CPU time                           |                        | ExtraP [57]                 |

|    |                            | $N_{O}$        | LOOP [6]            | Accurate                                                                                           | Analytic                           | $\operatorname{Loose}$ | $\operatorname{PerPreT}[5]$ |

|    |                            | $N_{O}$        | Task graph          | Accurate                                                                                           | None                               | $\operatorname{Loose}$ | PAPS [78]                   |

|    | $N_{\rm O}$                | $\mathbf{Yes}$ | NX                  | Accurate                                                                                           | Augmentation                       | $\operatorname{Tight}$ | LAPSE $[26]$                |

|    | $\mathbf{Y}_{\mathbf{es}}$ | $N_{O}$        | HPC $[30]$          | Accurate; Agarwal                                                                                  | Tight Augmentation Accurate; Agarw | Tight                  | EPPP $[63]$                 |

|    | $\mathbf{Y}_{\mathbf{es}}$ | $N_{O}$        | Custom              | Accurate; Agarwal                                                                                  | Augmentation                       | $\operatorname{Tight}$ | Proteus [8]                 |

|    | $Y_{es}$                   | $N_{O}$        | Concurrent C [52]   | Accurate                                                                                           | Augmentation                       | ${ m Tight}$           | RPPT [19]                   |

|    | Parallel Threads           | Parallel       | Language            |                                                                                                    | Timing method                      | Coupling               | Simulator                   |

| The                                                                                | -uoi                                                                |                              |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------------------|

| $^{oET.}$                                                                          | ns, "                                                               |                              |

| PUPI                                                                               | ulatio                                                              |                              |

| ding                                                                               | d sim                                                               |                              |

| inclu                                                                              | couple                                                              |                              |

| ttors,                                                                             | sely c                                                              |                              |

| imulo                                                                              | or loo                                                              |                              |

| vine s                                                                             | ed. F                                                               |                              |

| maci                                                                               | omitt                                                               |                              |

| ) of various distributed-memory parallel machine simulators, including PUPPET. The | discrete-event, and hence omitted. For loosely coupled simulations, | ial.                         |

| ory po                                                                             | and $l$                                                             | is seria                     |

| mem                                                                                | vent,                                                               | (uoi)                        |

| buted-                                                                             | $rete$ - $\epsilon$                                                 | second phase (simulation) is |

| distri                                                                             | y disc                                                              | se (si                       |

| ious                                                                               | nsistently da                                                       | d pha                        |

| of var                                                                             | CO                                                                  | <b>U</b> D                   |

| nary .                                                                             | nn" is                                                              | tt the                       |

| sum n                                                                              | iizatic                                                             | rs tha                       |

| Table 2.1: A summary                                                               | "overall organization" is                                           | parallel" means that the     |

| ble $2$ .                                                                          | verall                                                              | rallel"                      |

| Ta                                                                                 | 0, 0, 0                                                             | $ba_i$                       |

Informatique de Montréal (CRIM), McGill University, and Concordia University.

LAPSE (Large Application Parallel Simulation Environment) [26], developed by Dickens, Heidelberger, and Nicol, focuses on parallel simulation. In general, they find reasonably good speedup, although it greatly depends on the amount of parallelism in the simulated program. LAPSE is currently based on the Intel Paragon multicomputer, which uses the NX message-passing library.

PAPS [78, 79] is a simulator developed by Wabnig and Haring at the University of Vienna. It uses Petri nets, a model of parallel processes, to model the network. To do this, it enforces that the "programs" are specified as task graphs, an abstract view of the components involved in the computation and their ordering. This essentially corresponds to a log of a program execution, thereby making it loosely coupled. Task graphs make PAPS restrictive in the types of communications allowed. The generation of the task graphs is not a part of PAPS.

PerPreT [5], created by Brehm, is also based on a task-graph model of programs, but does not limit the communication forms as much as PAPS. Programs may be coded in a language called LOOP [6], also written by Brehm. The computation portions are then analyzed statically, and hence the program must have a static pattern. Conditionals do not exist, although loops are allowed. Some parallel algorithms, such as conjugant-gradient, are programmable in this way, provided the number of iterations is constant.

ExtraP [57] is a pC++ [4] tool for extrapolating pseudo-parallel performance to parallel performance from the University of Oregon. It is a part of the  $\tau$  (TAU, Tuning and Analysis Utilities) tool-set [11], which includes several performancevisualization and analysis programs for pC++. A graphical interface to ExtraP is provided by *speedy* (Speedup and Parallel Execution Extrapolation DisplaY).

After the implementation of PUPPET was completed, we became aware of *APNM* (Abstract Parallel Numerical Machine) [67] which was developed at TUM (Technische Universität München) simultaneously with and independently from PUPPET. It uses a network model along the same lines as ours, but they ignore network topology, hence also ignoring switching methods. Furthermore, they do not support collective operations. Both PVM and NX (the language of the Intel NX multicomputer) programs are supported. A feature unique to APNM is that either loose or tight coupling can be used.

### 2.2 Simulating Components

Significant work has been done on simulating the two main components (processors and networks) of parallel computers independent of the rest of the system. The following two sections overview proposed systems.

#### 2.2.1 Processor Simulators

We are interested in processor simulators because they offer insight into the computation portion of a parallel program. Traditionally, they have been used for simulating workstations, which allows exact benchmark measurement. Six major systems have been proposed, allowing simulation of certain processors designed by HP, SUN, and DEC.

DEC's SPIM (MIPS spelled backwards) [61, p. A-36] supports MIPS

R2000/R3000 processors. It includes an X-windows debugger, since powerful debugging is the main focus of SPIM. Programs typically run 100 times slower than using real MIPS processors.

MINT (MIPS Interpreter) [77] simulates MIPS R3000 and some MIPS R4000 instructions, although it has a flexible design so that it can be extended for other architectures. Several host platforms are supported, including SGI, DEC, and SUN SPARC workstations. It uses a mix between executing instructions on the host system and simulating the instructions to achieve efficiency. MINT also includes support for shared-memory multiprocessors that use a MIPS instruction-set.

Paint (PA Interpreter) [73] is an instruction-set simulator for the PA-RISC architecture [18]. It is based on MINT, illustrating MINT's flexibility; this has the effect that shared-memory multiprocessors are also supported in Paint. Although it is under a different name, Paint is essentially an extension of MINT.

SimICS [65] is a system-level interpreter for the SPARC V8 [72] instruction-set and architecture. It typically achieves a slowdown factor of 15 when running on other Sun architectures. SimICS's goal is to run an operating system; currently, it only supports a UNIX-compatible mode.

Shade [16, 17] simulates SPARC V8 and V9 architectures, as well as the MIPS I instruction set. The host machine is forced to be a SPARC, as with SimICS — this is rather unexpected for the MIPS simulator. Shade introduces dynamic compilation and caching techniques for fast cross-architecture simulation. Slowdowns range from 6.1 to 31.2, depending on the level of output.

Mable [23] is a general framework for instruction-level machine simulation. Typ-

ical slowdown factors range from 20 to 200, depending on the detail of simulation. It has been used to develop three processor simulators: Multiprocessor (MP) Mable, designed for shared-memory multiprocessors using the MIPS-III instruction set; Tsim, a simulation of the TORCH processor [69] which supports speculative execution; and PPsim, a simulator for the FLASH shared-memory multiprocessor.

In general, processor simulators provide high accuracy but have significant overhead. They are particularly useful when effects such as vectorization and caching play crucial roles in the performance of parallel programs. PUPPET currently does not support any processor simulators, although it could be extended to do so.

#### 2.2.2 Network Simulators

Independent interest has also been spawned in the area of networks. Network simulators are typically designed to evaluate the performance of a network subject to some randomly generated message patterns. This is particularly useful for design of new networks; simulators can be used to evaluate metrics such as average latency under a particular load. Similarly, simulations can be used to evaluate new routing algorithms. Network simulators can also be used for overall parallel-computer simulation (our interest), since they evaluate delays involved in sending messages.

NETSIM [49] is designed for all three uses. It forms a part of RPPT (see Section 2.1.7), as well as serving as an independent network simulator. NET-SIM supports direct and indirect (multistage) interconnection networks. A routing algorithm can be specified by the user, using one of packet switching, virtual cutthrough, or wormhole routing techniques. NetSim [42], although it has a name clash with NETSIM, is entirely different. It is designed for simulating circuit-switched networks (both direct and indirect), which is the one switching mechanism that NETSIM does not support. NetSim has also been used to simulate a reconfigurable multicomputer network called the Interconnection Cached Network (ICN). The load of a simulation is measured by a single parameter, m, the probability of sending a message in each time-step.

*PP-MESS-SIM* [64] is the most recent network simulator. A key feature is that it is object-oriented (via C++), making it very flexible. It supports the same switching techniques as NETSIM, namely packet switching, virtual cut-through, and wormhole routing, and allows the k-ary n-cube direct interconnection network [21]. Network workload is only slightly more complex than NetSim; for example, a negative-exponential distribution of send operations can be used.

*PARSE* (Parallel ARchitecture Simulator Environment) [60] is meant to help design networking hardware in distributed-memory supercomputers, although it allows simulation of a general (SPMD) program. It uses a very detailed model, going down to the data-link layer, including the flow-control protocol, and also examines factors such as copying buffers in routing. As Olk [60] says, it "properly model[s] all performance aspects."

$XPOS\acute{E}$  [81] is designed for local-area networks. It would be useful for simulating a network of workstations when many networks are involved. These networks must be primarily buses, connected by various links. It was developed to facilitate the development of hardware as well as software.

It seems that much of the research in network simulation has been repetitive.

Although the above five systems each have distinct features, there is a large amount of intersection. In the future, we hope that PUPPET can bring together the available features, offering (as an option) a detailed simulation of the network.

# Chapter 3

# **Proposed Evaluation Technique**

This chapter describes the models and theory that PUPPET is based on. Section 3.1 examines the portions of a parallel program running in a pseudo-parallel environment that should be timed, defining an execution log. In Section 3.2 we describe an overall model for the underlying network and the performance of the network links. Sections 3.3 and 3.4 detail this model, showing how to estimate the latency involved in point-to-point and collective communications, respectively. Finally, in Section 3.5 we see how the entire model can be simulated using discreteevent techniques, including details on supporting multitasking.

Before we begin, we make note of implicit assumptions in our reasoning. These essentially specify the target applications of PUPPET. Obviously, we are only interested in distributed-memory parallel programs, in particular, those that use a message-passing paradigm. Second, we assume that processes consist of a series of computation and communication instructions; we ignore any overhead such as that associated with I/O. Finally, it is assumed that the parallel applications are network-deterministic (see Section 2.1.2 for a definition).

## 3.1 Timing a Pseudo-Parallel Program

When dealing with programs running in a dedicated parallel environment, the basic metric used for further analysis is the total execution time. In other words, this is the maximum amount of time that a processor takes to complete, including both the communication and computation time. From this we normally calculate other metrics such as speedup. Parallel-execution time must be measured using the wall (real-time) clock, or else synchronization and communication factors will not be properly taken into account.

Such a simple evaluation method cannot be used when the program is run in a pseudo-parallel environment. First, the computation portion stays similar to the serial case because each pseudo-processor obtains one-nth of the CPU power, where n is the number of pseudo-processors, assuming that a fair time-sharing algorithm is employed. Second, the communication portion is not accurate, since a network is not used to transfer messages. Instead, the operating system replaces communication primitives with shared-memory references. Finally, any contextswitching overhead is included in the measure. Similarly, with parallel systems shared by multiple users, the processors and network appear weaker and hence the timing is inaccurate.

This problem is not unique. When time-sharing uniprocessors became common and multiple programs were run simultaneously, it was difficult to determine the amount of time that any one program actually took, in other words, the amount of time that the program was computing and not waiting for its time-slice. For this reason, the concept of CPU time was introduced, measuring the amount of time that a program occupies the CPU, that is, computes.

We wish to create the analog of CPU time for pseudo-parallel programs. A first attempt would be to measure the CPU time spent by each pseudo-processor. Unfortunately, this has the effect of incorrectly measuring communication time. We would hope that this measure included only computation, so that in a second phase we could incorporate communication time. However, communication is achieved using shared-memory references (possibly through a TCP/IP stack), which can take a significant amount of CPU time.

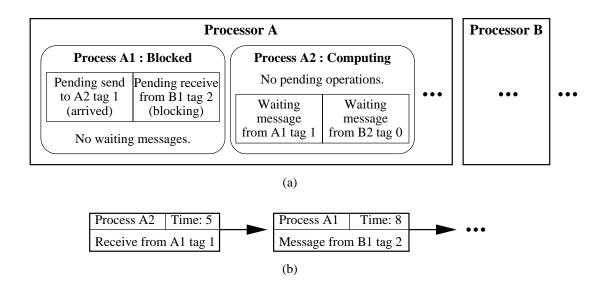

Instead, we must be careful not to incorporate the time taken by the underlying message-passing layer. To do this, we can instrument the program so that we stop (start) timing immediately before (after) each call to a communication routine. Hence, we have timed the *computation blocks*, each corresponding to a communication call (Figure 3.1). By convention, we associate the computation block immediately preceding a communication with that communication.

In the remainder of this chapter we will see how the computation blocks, along with details of the communication calls (together called an *execution log*), can be used to simulate the parallel program. In this way, we can estimate parallel execution of the program as if it were run on a specified parallel computer. First we will look at how the parallel computer's network can be specified (that is, modeled), and later at how it can be simulated.

Figure 3.1: A sample parallel-program execution. The shaded rectangles represent computation blocks. Blank spaces represent blocking (waiting for a receive to complete). Arrows denote messages.

## 3.2 Network Simulation

A fundamental part of a parallel computer is the network, which is used to transmit data between processors. Network simulation is a large area of research (see Section 2.2.2). The standard approach is to monitor the (simulated) travel of each message, including what processors and other hardware (such as switches) it encounters. Each encounter creates a certain amount of delay, and after a certain amount of time the message arrives at its destination.

Such a simulation also takes note of any conflicts when multiple messages require the same piece of hardware. In other words, the message delay caused by *network congestion* is taken into account. Although this delay affects parallel execution, much congestion is usually required before the program is slowed down significantly. In addition, reaching this (maximum) amount of accuracy greatly increases simulation time. We take the view that simulation should be a post-processing phase. Hence, one could vary model parameters (that is, the specification of the simulated parallel computer) several times but only run the program once. This allows one to ask several questions such as "what if the network was twice as fast?" or "what if I added a bus for broadcasting data?" If we achieve efficient simulation, such questions can be answered almost instantaneously.

We thus set out to create an efficient simulation of the network that does not take into account network traffic or congestion. In many cases (as we shall see in Sections 5.2 and 5.3), this does not significantly affect accuracy and leads to an immense performance benefit.

#### 3.2.1 Overall Model

We assume that the network is *direct* (or *static*) so that each *network link* allows exactly two processors to communicate. Hence, we can represent the network as a connected directed graph G = (V, E), called the *network graph*, where the vertices (edges) correspond to processors (links). Typical topologies (i.e., graphs) include meshes, hypercubes, tori, and rings [62]. Since we model the network as a *directed* graph, the links need not be bi-directional.

Next we shall examine how we can model the performance of individual links. For simplicity we assume that each link is identical with respect to speed. (This is almost always the case except in heterogeneous systems, which are not considered in this thesis because of their many complications.)

#### 3.2.2 Network-Link Model

The goal of network links is to achieve transmission times proportional to the message size. Unfortunately, current technology limits us to achieving this only when messages are sufficiently large. When small messages are sent, the dominating factor is the *initialization time* that it takes to prepare the link for transmission.

Another complication of link performance is *packets*. In many networks, messages are split up into fixed-size packets each of which is transmitted separately. For example, Ethernet-based networks employ a packet size of 1500 bytes [58, p. 101]. Since each packet is transmitted separately, an initialization cost must be paid for each packet.

Therefore, we adopt the following model to estimate typical network-link performance. The parameters are i (the initialization time per packet), p (the size of a packet), and  $t_1$  (the time to send one unit of information across the link). Given the size k of the message, the total time to transmit the message across a single link is

$$t(k) = i \cdot \left\lceil \frac{k}{p} \right\rceil + k \cdot t_1.$$

In the case where packets are not employed, i.e.,  $p = \infty$ , we must modify the formula to

$$t(k) = i + k \cdot t_1$$

so that initialization time is paid.

When extremely large messages (large than a megabyte) are involved, performance drops [66]. Since little is known about the exact behavior in this case, we suggest a simple generalization of the above model: let t be a piecewise-linear function. This incorporates the idea of packets, as well as allowing non-monotonicity. Since large messages are somewhat uncommon, we have not yet implemented this extension in PUPPET.

## 3.3 Point-to-Point Communication

It is rare that the graph defining the network topology is completely connected, because of inherent cost restrictions. In this section we examine how to simulate the travel of a message through several links. For the moment, we assume that only one source node and one destination node are involved; in Section 3.4 this restriction will be removed.

#### 3.3.1 Routing

The problem of routing a message through a network to avoid congestion, deadlock, livelock, and starvation has long been studied [25]. Many routing algorithms have been proposed for various networks [33, 36, 59]. Each can be defined as a possibly non-deterministic function yielding a path between two given nodes. Fortunately, in our less detailed simulation we do not need a routing algorithm. Instead, we assume that optimal routes are always taken; which route is chosen does not matter, since we are not considering congestion. In our case, the only identifying feature of a route is its *length*, that is, the number of links that must be traversed to send the message. The length of a shortest route between two nodes is called the *distance* and will be denoted by d.

Determining for each pair of processors (src, dest) the value d is equivalent to the *all-pairs shortest path* graph problem. It can be easily solved in  $O(n^3)$ time using the classical algorithms of Dijkstra [27] and Floyd [34], where n is the number of processors. Using more complicated techniques, one can achieve  $O(n^3 (\log \log n / \log n)^{1/2})$  time [74] or  $O(n^2 \log n)$  expected time [56].

#### 3.3.2 Switching

Routing consists of more than determining a path from the source to the destination processor. The *switching technique* determines the way that messages travel along a chosen path. There are four common methods: packet switching, virtual cutthrough, circuit switching, and wormhole routing, illustrated in Figure 3.2.

Packet switching (or store-and-forward routing) [33] is the most intuitive switching method. A message being transmitted simply travels over all the links on the path, reaching intermediate processors as it goes. The processors are interrupted and determine which way the message should go next, and then transmit it to the next processor, until the destination is reached. At any point in time, only one link in the path is reserved for a single message. Packet switching offers good solutions to deadlock and other problems. It has the severe disadvantage that latency (the time to reach the destination) is proportional to d.

To improve packet switching, virtual cut-through [50] was proposed. In this method, special switching hardware is employed so that a message will only inter-

Figure 3.2: Illustration of the various switching techniques on a 3-processor linear array. (a) Packet switching. (b) Virtual cut-through. (c) Circuit switching. (d) Wormhole routing. Filled squares represent the entire message. Filled and empty rectangles represent flits and headers, respectively. Gray lines denote inactive links.

rupt a processor when the next required link is busy (or the destination has been reached), sending a header of size h to set up the hardware. The message trails behind the header. Virtual cut-through improves the performance so that for messages much longer than the header, d does not affect latency. In particular, in the latency formula, the distance d and t(s) (the actual communication time) are not in the same term.

Two other methods have been proposed to achieve this. In *circuit switching* [41], a control packet of size c is sent through the network to reserve all of the links on the path. As soon as they have all been reserved, special hardware allows the links to combine and become a single "circuit" that the message can be sent through at a speed similar to that of a single link. Circuit switching is similar to virtual cut-through except that the message waits for the header to finish reserving instead of trailing behind it. If we ignore congestion, circuit switching ends up using the same amount of time as virtual cut-through by letting c = h [59].

The final method, wormhole routing [22], is often accepted as the best. Each message is split into a sequence of fixed-size *flits* (flow control units); flits are typically only a byte or two long. The flits are then sent in a pipeline manner along the path. An important point is that each flit must follow the same path; this way, less initialization cost is likely needed for all flits but the first. As with typical pipelining, if the number of inputs (flits) is sufficiently larger than the number of operations (links), then the number of operations (links) does not affect the total time. Thus with extremely small flit sizes, a great performance benefit is obtained.

We summarize the time taken by the switching techniques in Table 3.1.

| Switching technique | Latency when there is no congestion |

|---------------------|-------------------------------------|

| Packet Switching    | $d \cdot t(s)$                      |

| Virtual Cut-Through | $d\cdot t_0(h)+t(s)$                |

| Circuit Switching   | $d\cdot t_0(c)+t(s)$                |

| Wormhole Routing    | $(d-1+\lceil s/f ceil)\cdot t(f)$   |

Table 3.1: The latency of the various switching techniques. d is the distance between the source and destination. c, h, and f are the sizes of the control packet, header, and flit, respectively. t(k) is the time to send a message of size k across a link (see Section 3.2.2);  $t_0$  is the same but may have different parameters than t. s is the size of the message.

Systems that apply packet switching include the Cosmic Cube, iPSC-1, Ncube-1, Ametek 14, and FPS T-series [59]. The University of Michigan's HARTS (Hexagonal Architecture for Real-Time Systems) multicomputer [28] uses virtual cutthrough as its switching method. Circuit switching is used by the Intel iPSC-2 and iPSC/860 multicomputers. Multicomputers that use wormhole routing include the Ametek 2010, Symult 2010, Ncube-2, Intel/DARPA's Touchstone Delta, Intel Paragon, MIT's J-machine, Intel/CMU's iWarp, and the Transputer IMS T9000 family.

## **3.4** Collective Communication

*Collective communication*, in contrast to point-to-point communication, involves several, potentially all, processors in the network. Whereas point-to-point communication has essentially one basic form (send-receive), there are several operations that are collective. We shall consider the following:

- Barrier synchronization: certain processes cannot complete until they have all reached the barrier.

- Multicasting: send the same message from one process to several others.

- Scatter: send different messages from one process to several others.

- Gather: send messages from several processes to one process.

- All-to-all: several processes send messages to every other process in the group.

- *Reduce*: operations such as global maximum. One variant leaves the result at a single process, whereas the other gives the result to all involved processes.

As with the point-to-point case, we will examine models that ignore network congestion. If more detail is required, a network simulator (such as those described in Section 2.2.2) can be used.

#### 3.4.1 Multicasting

There are three general techniques employed in parallel systems to send a message m from process 0 to processes 1 through n:

1. Obvious: process 0 issues n send operations, and the remaining processes issue receives. This technique is really only useful if the send operations are buffered, so that process i need not receive before the message even starts traveling to process i + 1.

Figure 3.3: An example of the smart multicasting approach: the hypercube broadcast algorithm [48]. During a phase, each processor that has the message (those in bold) sends in a particular direction (shown with arrows), which varies over time. (a-c) show time steps 1–3, respectively, for a three-dimensional hypercube.

- 2. Smart: in some prescribed manner depending on the network topology, the message propagates from process 0 to involved processes on the same or adjacent processors, eventually reaching all of the destinations (Figure 3.3).

- 3. Extra hardware: a bus, hierarchical bus, or other additional hardware is present to allow faster multicasting.

Analogous to the point-to-point case, the problem is much simpler when congestion is ignored. In fact, the obvious and smart approaches are nearly equivalent: the inefficiency of the obvious approach, that the multiple messages cause high congestion and may collide, is nullified.

The extra-hardware approach can be considered to be the obvious approach, except that a network other than the one for point-to-point communication is used. In the case of a bus, this network is completely connected (that is, processor distances are one). We can view a multi-level bus as a tree network (Figure 3.4) with

Figure 3.4: A complete binary tree multicast-network. This can be used as a multilevel bus, or (if the link speeds are doubled) as a smart approach using a recursive structure. Smaller circles denote dummy processors.

internal nodes that are *dummy processors*, that is, processors with no processes running on them.