# Power Characterization of a Digit-Online FPGA Implementation of a Low-Density Parity-Check Decoder for WiMAX Applications

by

Manpreet Singh

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Master of Applied Science in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2014

© Manpreet Singh 2014

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

## Abstract

Low-Density Parity-Check (LDPC) codes are a class of easily decodable error-correcting codes. Published parallel LDPC decoders demonstrate high throughput and low energy-per-bit but require a lot of silicon area. Decoders based on digit-online arithmetic (processing several bits per fundamental operation) process messages in a digit-serial fashion, reducing the area requirements, and can process multiple frames in frame-interlaced fashion. Implementations on Field-Programmable Gate Array (FPGA) are usually power- and area-hungry, but provide flexibility compared with application-specific integrated circuit implementations. With the penetration of mobile devices in the electronics industry the power considerations have become increasingly important. The power consumption of a digit-online decoder depends on various factors, like input log-likelihood ratio (LLR) bit precision, signal-to-noise ratio (SNR) and maximum number of iterations.

The design is implemented on an Altera Stratix IV GX EP4SGX230 FPGA, which comes on an Altera DE4 Development and Education Board. In this work, both parallel and digit-online block LDPC decoder implementations on FPGAs for WiMAX 576-bit, rate-3/4 codes are studied, and power measurements from the DE4 board are reported. Various components of the system include a random-data generator, WiMAX Encoder, shift-out register, additive white Gaussian noise (AWGN) generator, channel LLR buffer, WiMAX Decoder and bit-error rate (BER) Calculator. The random-data generator outputs pseudo-random bit patterns through an implemented linear-feedback shift register (LFSR).

Digit-online decoders with input LLR precisions ranging from 6 to 13 bits and parallel decoders with input LLR precisions ranging from 3 to 6 bits are synthesized in a Stratix IV FPGA. The digit-online decoders can be clocked at higher frequency for higher LLR precisions. A digit-online decoder can be used to decode two frames simultaneously in frame-interlaced mode. For the 6-bit implementation of digit-online decoder in single-frame mode, the minimum throughput achieved is 740 Mb/s at low SNRs. For the case of 11-bit LLR digit-online decoder in frame-interlaced mode, the minimum throughput achieved is 1363 Mb/s. Detailed analysis such as effect of SNR and LLR precision on decoder power is presented. Also, the effect of

changing LLR precision on max clock frequency and logic utilization on the parallel and the digit-online decoders is studied. Alongside, power per iteration for a 6-bit LLR input digit-online decoder is also reported.

## Acknowledgements

First of all, I would like to thank my supervisor Dr. Vincent Gaudet for his guidance, support, funding, and confidence in me and my work.

I am very thankful to Dr. Philip P. Marshall and Si-Yun Li for providing me with all the necessary help for making this work possible.

Many thanks to all the research group members including Brendan Crowley, Si-Yun Li, Bahareh Ebrahimi, Navid Bahrani, Rachna Srivastava, Chris Ceroici, Pierce Chuang for their valuable advice and feedback from time to time.

A bunch of thanks to Dr. Hiren Patel and Dr. Liang Liang Xie for accepting to act as readers for my thesis.

I also would like to mention how grateful I am to have worked alongside with some amazing people like Dr. Edgar Mateos Santillan, Dr. Bill Bishop, Dr. Wayne Loucks, Dr. Rodolfo Pellizzoni, Dr. Marcio Juliato, Dr. Carlos Moreno, Najma Jose, Bahaedinne Jlassi, Mortaja AlQassab, Peter Dawoud, Farhad Haghighizadeh, Alborz Rezazadeh Sereshkeh, Roger Sanderson, during my assignments as a Teaching Assistant at University of Waterloo. Many of these people I run into during my casual walks through University corridors and we have some good chats about future, past and sometimes present.

And, I am thankful to University of Waterloo for providing me with the coolest office ever; I really enjoyed partially jealous looks from anyone who visited my office for the first time. I am so glad to have had some great office mates at University of Waterloo, mostly they are great because they were away most (all) of the time, leaving me as the sole owner of the office. Saud Wasly, thank you very much for the support and guidance in times of need. You are among the most astute people I know.

I had the good fortune of meeting many people at University of Waterloo; sadly, I won't be able put down names of everyone. I would really like to thank you for being a part of my life, however small it was, for it contributed towards the kind of person I am today. Thanks.

# Dedication

Dedicated to all my dear ones whose love and support helped me make it through

# **Table of Contents**

| AUTHOR'S DECLARATIONii                           |

|--------------------------------------------------|

| Abstractiii                                      |

| Acknowledgementsv                                |

| Dedication                                       |

| Table of Contentsvii                             |

| List of Figuresix                                |

| List of Tablesxi                                 |

| Chapter 1 Introduction                           |

| Chapter 2 Background                             |

| 2.1 LDPC Codes                                   |

| 2.2 LDPC Decoding                                |

| 2.2.1 Sum-Product Decoding                       |

| 2.2.2 Min-Sum Decoding                           |

| 2.3 LDPC Decoder Implementations and Comparisons |

| 2.3.1 Parallel LDPC Decoding                     |

| 2.3.2 Serial LDPC Decoder Implementation         |

| 2.3.3 Stochastic LDPC Decoding11                 |

| 2.3.4 Analog LDPC Decoders                       |

| 2.4 LDPC Decoder Implementation on FPGA          |

| 2.5 Altera Stratix IV FPGAs                      |

| Chapter 3 Digit-Online Decoder                   |

| 3.1 Digit-Online Arithmetic                      |

| 3.2 LDPC Encoder                                 |

| 3.3 Digit-Online Decoder                         |

| 3.3.1 Variable Node Structure                    |

| 3.3.2 Check Node Structure                       |

| 3.3.3 Controller                                 |

| 3.3.4 Single Frame Decoding                      |

| 3.3.5 Frame-Interlaced Decoding                  |

| Chapter 4 Test Unit and Power Measurement Setup  |

| 4.1 Introduction                                      |    |

|-------------------------------------------------------|----|

| 4.1.1 FPGA Implementation                             |    |

| 4.2 FPGA Core Power Measurement                       |    |

| 4.3 FPGA Power Dissipation Discussion                 |    |

| Chapter 5 Results and Discussion                      | 40 |

| 5.1 WiMAX 576-bit, Rate-3/4 Bit-Parallel LDPC Decoder | 40 |

| 5.1.1 ModelSim <sup>®</sup> Simulation                | 41 |

| 5.1.2 FPGA Synthesis                                  |    |

| 5.2 WiMAX 576-bit, Rate-3/4 Digit-Online LDPC Decoder | 45 |

| 5.2.1 ModelSim <sup>®</sup> Simulation                | 46 |

| 5.2.2 FPGA synthesis                                  | 46 |

| 5.2.3 BER Performance                                 | 50 |

| 5.3 Power Characterization Experiment                 |    |

| 5.3.1 FPGA Core Power Consumption                     | 54 |

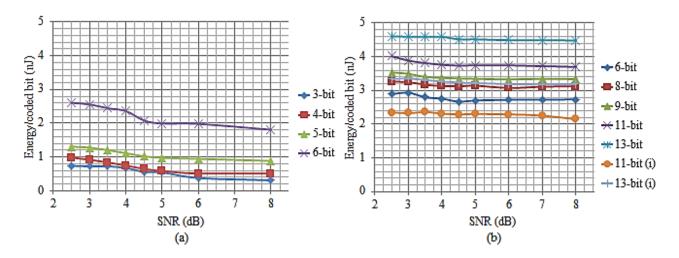

| 5.3.2 Energy-Per-Coded-Bit (E/b)                      | 57 |

| 5.3.3 Energy Per Iteration                            | 57 |

| Chapter 6 Summary and Future Work                     | 61 |

| 6.1 Thesis Summary                                    | 61 |

| 6.2 Future Work                                       | 63 |

| Bibliography                                          | 64 |

| Appendix A FPGA Resource Utilization Analysis         | 70 |

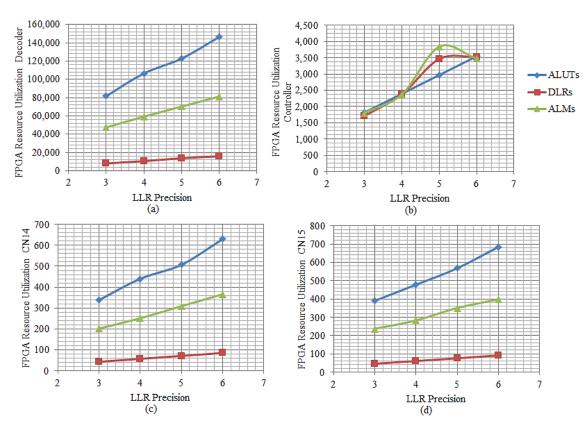

| A.1 Bit-Parallel Decoder                              | 70 |

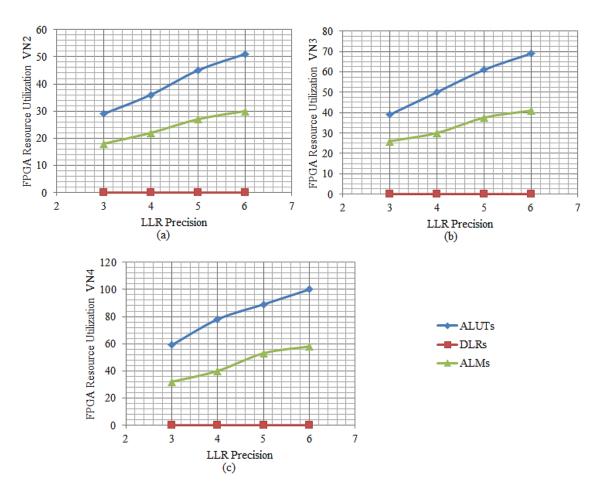

| A.2 Digit-Online Decoder                              | 72 |

# List of Figures

| Figure 2.1: An H matrix example of a $(3, 6)$ regular LDPC code with N = 16 and M = 8           | (3)        |

|-------------------------------------------------------------------------------------------------|------------|

| Figure 2.2: An example of a Tanner graph                                                        | (4)        |

| Figure 2.3: High level diagram of a Stratix IV ALM                                              | (16)       |

| Figure 2.4: Stratix IV ALM in Normal mode                                                       | (17)       |

| Figure 2.5: Stratix IV ALM in Arithmetic mode                                                   | (17)       |

| Figure 2.6: Carry, Arithmetic and Register chains in Stratix IV                                 | (18)       |

| Figure 3.1: A 576-b encoder frame output from the LDPC encoder frame                            | (21)       |

| Figure 3.2: Digit-online decoder system diagram                                                 | (22)       |

| Figure 3.3: Various components of digit-online decoder                                          | (22)       |

| Figure 3.4: An example degree-4 variable node                                                   | (24)       |

| Figure 3.5: Digit-online decoder - variable node structure                                      | (25)       |

| Figure 3.6: Digit-online decoder - check node structure                                         | (26)       |

| Figure 3.7: Beginning of decoding in single-frame mode -timing diagram                          | (29)       |

| Figure 3.8: Finishing decoding previous frame, hard-decision output in single frame mo          | de -timing |

| diagram                                                                                         | (30)       |

| Figure 3.9: Beginning of decoding in frame-interlaced mode -timing diagram                      | (31)       |

| Figure 3.10: Finishing decoding previous frame, hard-decision output in frame-interlac          | ed mode -  |

| timing diagram                                                                                  | (32)       |

| Figure 4.1: Block diagram of the FPGA implementation                                            | (35)       |

| Figure 4.2: Power measurement setup for measuring power in DE4 board                            | (37)       |

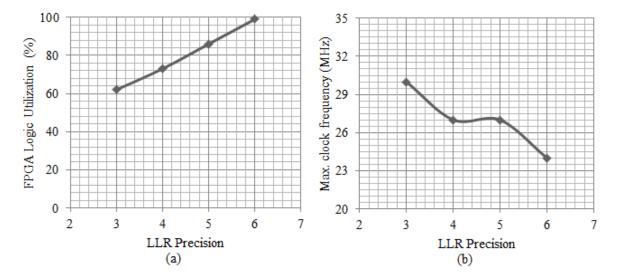

| Figure 5.1: (a) FPGA logic utilization, (b) $f_{max}$ versus LLR precision bit-parallel decoder | (42)       |

| Figure 5.2: ModelSim <sup>®</sup> simulation for 576 bit, rate-3/4 bit-parallel decoder         | (43)       |

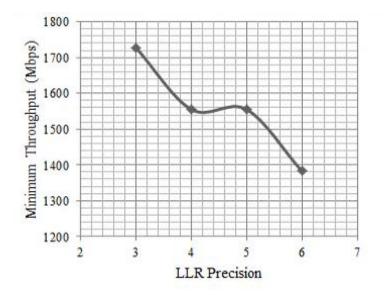

| Figure 5.3: Minimum throughput vs LLR precision for bit-parallel decoder                        | (44)       |

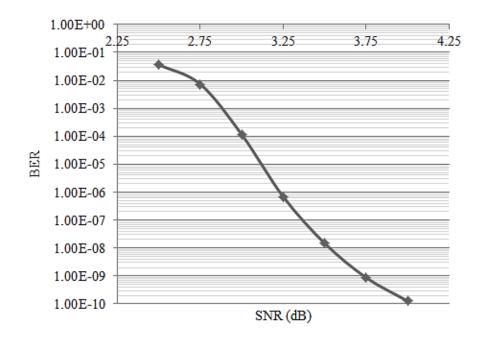

| Figure 5.4: Bit-parallel decoder BER curve                                                      |            |

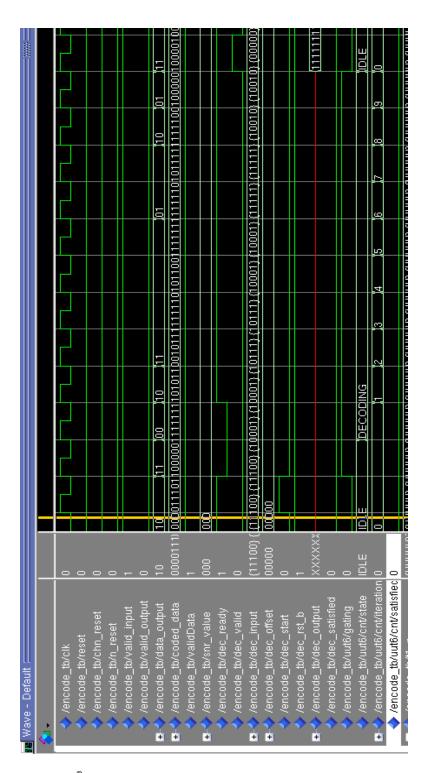

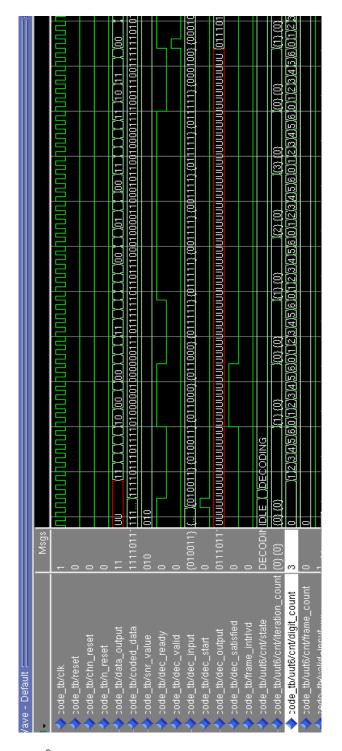

| Figure 5.5: ModelSim <sup>®</sup> simulation for 576 bit, rate-3/4 digit-online decoder         | (47)       |

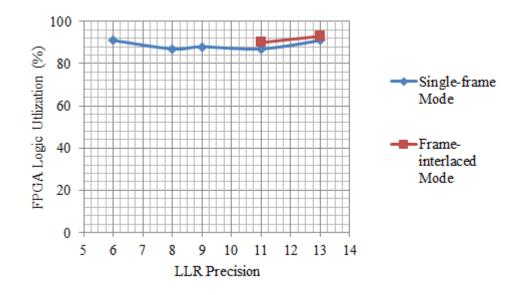

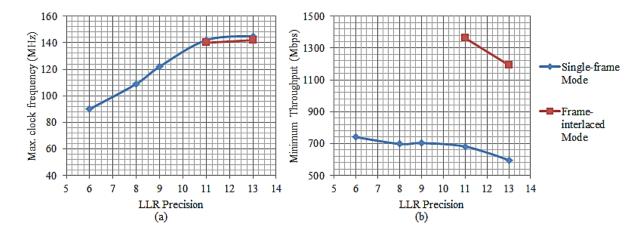

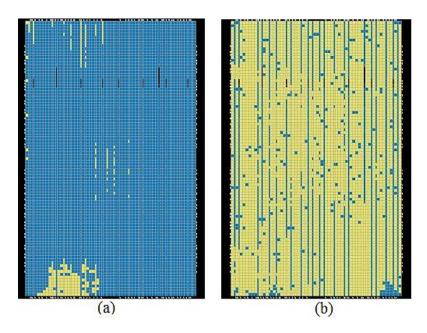

| Figure 5.6: FPGA logic utilization versus LLR precision for digit-online decoder                | (49)       |

| Figure 5.7: (a) f <sub>max</sub> , (b) minimum throughput versus LLR precision                  | (50)       |

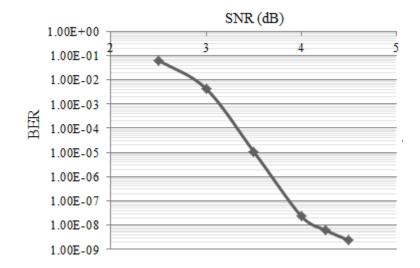

| Figure 5.8: Digit-online decoder BER curve                                                      | (51)       |

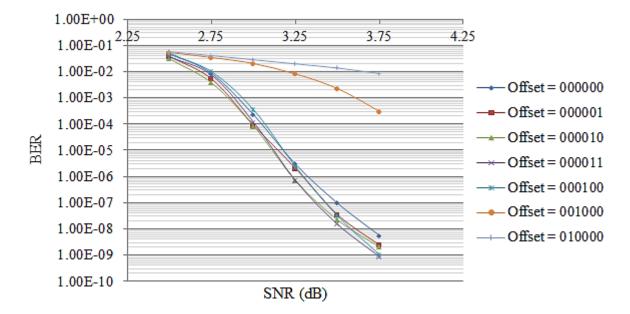

| Figure 5.9: Effect of offset value on BER of digit-online decoder                               | (52)       |

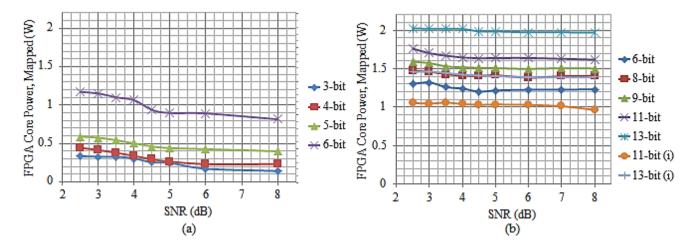

| Figure 5.10: FPGA core power vs SNR (a) bit-parallel decoder (b) digit-online decoder           | (54)       |

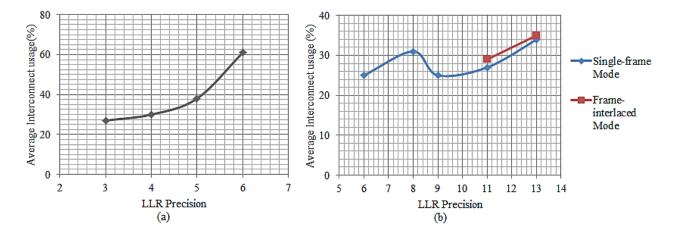

| Figure 5.11: Average interconnect usage vs LLR precision                               | (55) |

|----------------------------------------------------------------------------------------|------|

| Figure 5.12: FPGA chip planner screenshot showing low-power and high-performance tiles | (57) |

| Figure 5.13: E/b vs SNR for (a) bit-parallel decoder (b) digit-online decoder          | (58) |

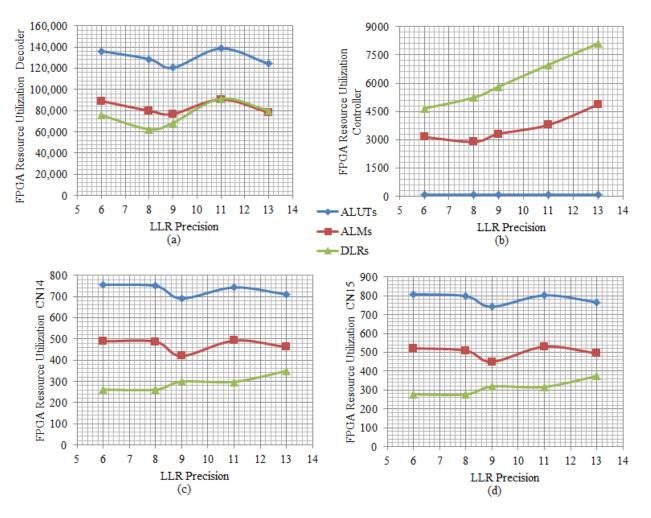

| Figure A.1: Entity resource utilization vs LLR precision (bit-parallel decoder) - 1 |

|-------------------------------------------------------------------------------------|

| Figure A.2: Entity resource utilization vs LLR precision (bit-parallel decoder) - 2 |

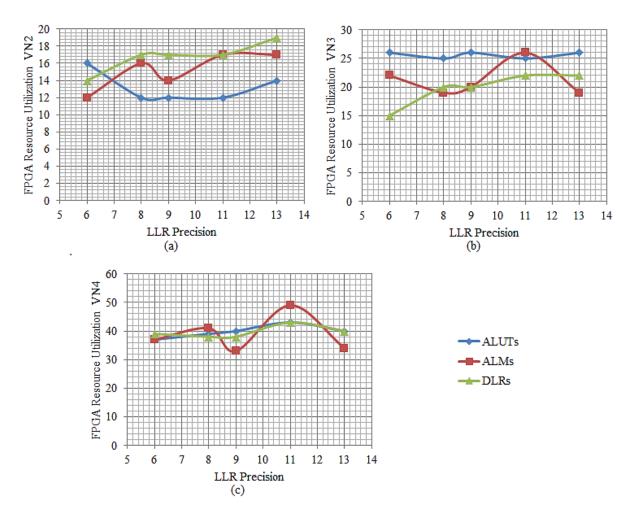

| Figure A.3: Entity resource utilization vs LLR precision (digit-online decoder) - 1 |

| Figure A.4: Entity resource utilization vs LLR precision (digit-online decoder) - 2 |

|                                                                                     |

## **List of Tables**

| Table 2.1: Summary of the discussed FPGA based decoders                                     | . (14) |

|---------------------------------------------------------------------------------------------|--------|

| Table 2.2: Summary of FPGA based decoders with reported power data                          | . (15) |

| Table 5.1: Digit-online decoder pipeline length for different LLR precision                 | . (49) |

| Table 5.2: Operating clock frequencies for a throughput of 450 Mb/s in digit-online decoder | . (53) |

| Table 5.3: Estimation of power consumption for 6-bit LLR digit-online decoder               | . (60) |

| Table 6.1: Average E/b values for different decoder configurations                          | . (62) |

| Table 6.2: Average entity resource utilization for digit-online decoder                     | . (62) |

•

# Chapter 1 Introduction

Forward error correction is a common technique used to control errors when transmitting data over noisy and unreliable channels. By adding controlled redundancy to a stream of data, enough information can be provided to a receiver so that it can detect or correct the occurrence of most errors. Low-Density Parity-Check Block Codes (LDPC-BC) are a class of forward error-correcting codes proposed by R.G. Gallager in 1962 [1]. These codes can communicate data at very low bit error rates (BER), asymptotically reaching a capacity limit given by Shannon's capacity Theorem [2]:

$$C = B \log_2 \left( 1 + \frac{S}{N} \right) \tag{1.1}$$

In the case of an Additive White Gaussian Noise (AWGN) channel, for a specific bandwidth B and signal-to-noise ratio (S/N), the maximum possible information capacity (C) is given by Equation (1.1). In practical applications, effective utilization of available capacity is required since signal bandwidth and transmission power are usually limited. LDPC decoding typically relies on Iterative Decoding Algorithms implemented on Very-Large-Scale integrated (VLSI) chips. Parallel implementations of such decoders can run at very high throughputs. The area of parallel LDPC decoders increases rapidly with an increase in message precision, with interconnect wiring possibly occupying more area than actual logic units [3], [4]. In a successful attempt to reduce wiring congestion with increased message precision, digit-online decoders based on digit-serial arithmetic were proposed in [5]. Previously proposed bit-serial decoders [4], [6], which although proving effective at reducing wiring congestion, suffered from a disadvantage of not being able to perform consistent and continuous serial processing (some nodes work on a most-significant-bit-first basis, and others least-significant-bit-first). In contrast, digit-online decoders employ techniques of digit-online arithmetic [7], [8] and are capable of processing all the data in a consistent most-significant-digit (MSD)-first order at all

computational nodes. This allows for increased pipelining and reductions in clock cycle requirements, and therefore, higher throughputs can possibly be achieved.

In this thesis the work in [5] is extended, by studying and comparing bit-parallel and digitonline decoder implementations of WiMAX 576-bit, rate-3/4 codes that were able to fit on an Altera Stratix IV field-programmable gate array (FPGA). Using a power measurement setup from [9], [18], various aspects of both decoders are characterized and power numbers are reported. In Chapter 2 discusses LDPC Decoding and various popular LDPC decoder implementation techniques, and provides a thorough literature review of FPGA-based LDPC decoders. Digit-online arithmetic and digit-online decoding algorithms are discussed in Chapter 3. Chapter 4 explains the FPGA implementations of the decoder systems and discusses DE4 power measurement setup along with a discussion of power dissipation factors in FPGA. In Chapter 5 reports and discusses the simulation and synthesis results for bit-parallel and digit-online decoders for a WiMAX 576-bit, rate-3/4 LDPC code. BER curves and power results for the FPGA implementation are also reported. Chapter 6 concludes the thesis along with a discussion of future work.

# Chapter 2 Background

## 2.1 LDPC Codes

Low-density parity-check (LDPC) codes are a class of linear error correcting codes defined by a sparse parity-check matrix **H** of dimensions M x N, such that all valid code words of size N (represented by vector **x**) satisfy the relation  $\mathbf{Hx}^{T} = \mathbf{0}$  [1]. For binary regular LDPC codes the number of 1's in **H** is fixed for each row and column, while for binary irregular LDPC codes the number of 1's is variable. The code rate of a block code is given by 1 - M/N. Lower code rates provide better error performance; however, with lower code rates the information content in a code word decreases and thus information throughput is reduced. There exists a trade-off where the designer chooses between the desired information throughput and code-rate. An example of a regular (3, 6) LDPC code H-matrix is shown in Figure 2.1. For a (3, 6) regular LDPC code, the number of 1's in a row of H-matrix is equal to 6 and number of 1's in each column is equal to 3. The distribution of 1's in H-matrix is random, and is required to keep the matrix sparse to guarantee a good-performance LDPC code. Tanner graphs [10] are bi-partite graphs that are popularly used to represent LDPC codes. Figure 2.2 shows the Tanner graph

Figure 2.1: An H-matrix example of a (3, 6) regular LDPC code with N = 16 and M = 8, the code.

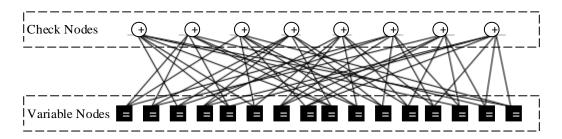

Figure 2.2: An example of a Tanner graph. Message passing occurs between the connected Variable and Check Nodes until all constraints are met or an early termination occurs after maximum allowed number of iterations

for the **H**-matrix represented in Figure 2.1. A Tanner graph consists of two sets of nodes: Variable nodes and Check nodes. The number of rows in the **H**-matrix corresponds to the number of check nodes in the Tanner graph while the number of **H**-matrix columns is equal to the number of variable nodes. Every element  $\mathbf{h}_{ij} = 1$  in the **H** matrix corresponds to an edge between a variable node *i* and check node *j*. Since this is an example of a regular code, all variable nodes have equal number of edges and thus a degree  $d_v = 3$  and all check nodes have a degree  $d_c = 6$ . To satisfy the constraint for a variable node, as represented by an equal sign, all the incoming symbols over the edges should carry equal values. For check nodes the constraints are satisfied if the XOR function calculated from all the input symbols results in a zero. The distribution of edges in the Tanner graph represents the LDPC decoder structure. Actual LDPC decoder designs are based on the Tanner graph design, with messages moving across the graph edges and nodes evaluating and iteratively trying to satisfy the constraints in the code.

## 2.2 LDPC Decoding

Given the size of the received block of data, if maximum-likelihood decoding is used to simultaneously satisfy all constraints, the algorithm required for finding the optimal solution will be NP-hard [11]. Therefore, for the purpose of decoding LDPC codes, iterative decoding

algorithms are suitable. Variable nodes are initialized with probabilistic information representing channel outputs, and messages are exchanged between the variable and check nodes until all the constraints are met. For the purpose of achieving higher throughput, the number of iterations is usually limited. The channel information entering the decoder is represented as log-likelihood ratios (LLRs), which is a relative probability specified on a logarithmic scale, and quantized to a desired bit precision. Mathematically, LLR can be expressed as:

$$\lambda(p_{0,}p_{1}) = \ln(\frac{p_{0}}{p_{1}})$$

(2.1)

where  $p_0$  is the probability that the transmitted bit could be a 0 and likewise  $p_1$  is the probability that the transmitted bit can be a 1. As a general rule, higher bit precision LLR inputs are better for decoding since they provide more accurate channel information and help the decoder to converge faster. Increasing the bit precisions above 6 bits offers marginal improvement in the error performance [12]; however, increasing LLR precision increases the decoder input buffer and decoder size requirements significantly. For the case of serial decoders, increasing LLR bit precision is not much of an issue for decoder size; however, the throughput is negatively affected, as higher number of clock cycles are required to decode a code word. In highly pipelined architectures like the digit-online decoder, increasing LLR precision allows for deeper pipelining, which allows it to be clocked at higher frequencies. Thus, the throughput of digit-online decoders remains relatively unaffected despite increase in LLR precisions [15]. The type of quantization scheme also affects the error performance of the decoder; in [12] it is shown that using a non-uniform quantization scheme results in better performance than a uniform quantization scheme. In [13], [14], it is shown that using an optimized quantization scheme for 4 bits of precision achieves BER performance similar to the design using uniform quantization using 6 bits per message.

#### 2.2.1 Sum-Product Decoding

As discussed previously, the data flow structure of LDPC decoders is based on bipartite graphs known as Tanner graphs; decoding uses iterative message-passing algorithms. One such algorithm is the sum-product (SP) algorithm, also referred to as belief-propagation (BP). The SP algorithm factors the complicated global function into a number of simpler local functions depending on a subset of the variables. The messages in each iteration of the SP algorithm are updated according to the SP update rule given in [16]. Variable node v outputs a message sent on edge e to check node c, which is the sum of the local function with all the messages received at v on all the edges other than e; this constitutes a half iteration. For the next half of the iteration, check node c outputs the product of the local function with all the messages received at c other than the ones received at e. The variable and the check node operations can be represented in form of following Equations (2.2), (2.3) and (2.4). The channel LLRs that are provided to the decoder variable nodes in the beginning of decoding are denoted as L<sub>c</sub>.

Variable Node :

$$\lambda_i = L_c + \sum_{\substack{j=1 \ j \neq i}}^{d_v} L_j$$

(2.2)

Varible Node, final iteration :

$$\lambda_{\text{Final}} = L_c + \sum_{j=1}^{d_v} L_j$$

(2.3)

Check Node :

$$L_p = 2 \tanh^{-1} \left( \prod_{\substack{p=1\\p \neq q}}^{d_c} \tanh\left(\frac{\lambda_q}{2}\right) \right)$$

(2.4)

$d_v$  and  $d_c$  denote the variable node and check node degrees respectively. Check node also monitors if the constraints for the code are satisfied, and can indicate the variable nodes to terminate the decoding early and perform a hard-decision of the results.

#### 2.2.2 Min-Sum Decoding

SP algorithm provides near-optimal decoding performance for LDPC codes [17], [19], but is inefficient to implement in silicon. The SP variable node implementation largely requires only summation operations, which is not very costly to implement; however, SP check node operations are relatively expensive to implement in hardware. For long low-rate codes, SP check nodes consume lot of silicon area and hence not considered a very area efficient choice. The min-sum (MS) algorithm provides a simpler implementation of check nodes. The check node update equation is modified to Equation (2.5) in MS algorithm:

$$L_{p} = |\lambda_{\min,p}| \left( \prod_{\substack{p=1\\p \neq q}}^{d_{c}} \operatorname{sign}(\lambda_{q}) \right)$$

(2.5)

where

sign (x) =

$$\begin{cases} +1 & \text{for all } x \ge 0 \\ -1 & \text{for all } x < 0 \end{cases}$$

(2.6)

The variable node update equation remains the same as Equation (2.2) and (2.3). Although MS provides easier implementation than SP, it comes at a slight performance loss. The MS decoder implementation typically requires a few tenths of a dB more transmitted power at same BER performance than the SP decoder implementation. It was found, as explained in [20], [21] using the density-evolution of the MS algorithm that the output LLRs from the check nodes tend to have a higher magnitude than LLRs output by SP check nodes. It was suggested that it is possible to regain most of the coding loss by introducing minor modifications in the algorithm to somehow reduce the magnitude of MS check node output LLRs to match those of SP check nodes. Most popular modifications in use include the use of correction factors, and are referred to as: 1) Offset correction, and 2) Normalization techniques. The offset correction

$$L_{p} = \max(\left|\lambda_{\min,p}\right| - \beta) \left(\prod_{\substack{p=1\\p \neq q}}^{d_{c}} \operatorname{sign}(\lambda_{q})\right)$$

(2.7)

$$L_{p} = \frac{|\lambda_{\min,p}|}{\alpha} \left( \prod_{\substack{p=1\\p\neq q}}^{d_{c}} \operatorname{sign}(\lambda_{q}) \right)$$

(2.8)

involves subtraction of an offset value ( $\beta$ ) from all the incoming LLRs in the check nodes. The normalization technique involves dividing the LLRs in check node by a factor  $\alpha$  ( $\alpha > 1$ ), such that the resulting LLRs are smaller. The check node update equations for the offset correction (offset-MS) and the normalization (normalized-MS) are shown in Equation (2.7) and (2.8), respectively. Both techniques provide very similar performance benefits [21]. However, [20] notes that the results of the offset-MS can be readily extended for the discretized density-evolution cases, and suggests that the offset-MS is a good choice for practical implementation since it can be extended easily to quantized values.

## 2.3 LDPC Decoder Implementations and Comparisons

#### 2.3.1 Parallel LDPC Decoding

Most straightforward implementations of parallel LDPC decoders instantiate a Tanner graph directly in hardware. The internal structure of the variable nodes and the check nodes depends on the decoding algorithm. Parallel LDPC decoder nodes process multi-bit LLR messages in parallel, so each edge in the Tanner graph corresponds to multiple interconnect wires.

One of the early parallel LDPC decoders was implemented in 160 nm technology [21], [22], decoding at a throughput of 1 Gb/s with 64 iterations per frame and clocked at a frequency of

64 MHz. Using parallel LDPC decoder implementations, high throughput and low power consumption per decoded frame can be achieved.

However, a parallel LDPC decoder architecture results in low logic-densities and high routing congestion. Most of the chip area is utilized for routing the connections between the variable and check nodes. While designing parallel LDPC decoders for long code sizes and high-precision input LLR messages, it becomes really hard to connect the nodes in the decoder. The number of parallel wires for each Tanner graph edge increases with increasing LLR precision. In the case of implementation of a parallel LDPC decoder on an FPGA where the routing resources are already limited, providing connections in the decoder places a lot of stress on the routing resources. A shared extrinsic memory is used between the variable node update units (VNUs) and the check node update units (VNUs) to achieve low routing congestion but highly parallel computations in [23]. Onizawa et al. report a variant of the parallel LDPC decoder in a new decoding algorithm referred to as a flooding-type update algorithm [24]. The longer wires between the nodes are divided appropriately in several subwires by insertion of flip flops; thus reducing the length of longer wires and enabling the decoder to be clocked at a higher frequency.

Apart from parallel decoder implementations, many "partially" parallel LDPC decoder implementations are presented in the literature. Zhang *et al.* implemented a partially parallel structured LDPC code decoder employing time-multiplexed routers to reduce parallelism and groups the highly connected check nodes and variable nodes in the decoder as local units [25], [26]. Zhong *et al.* present a partially parallel structured LDPC code decoder architecture with shared memory blocks for storing the iterative decoding messages and the channel messages [27], [28]. A clustering algorithm for partitioning a Tanner graph in clusters, such that the inter-cluster communications are minimized was proposed by Al-Rawi *et al.* [29]. To reduce the wiring congestion in the LDPC code decoders a message broadcasting technique is demonstrated in [30] which reduces the amount of information needed to be conveyed from the check nodes to the variable nodes. A half-broadcasting technique reduces average node-to-node wirelength by about 26%. Other techniques based on bit-flipping (BF), referred to as weighted-bit-flipping (WBF), modified-WBF (MWBF) and improved-MWBF have been

presented in [31], [32], [33] and [34] respectively. BF algorithm works in an iterative fashion and flips one or more bits per iteration until all the parity checksum are satisfied [34]. BF algorithm works well with LDPC codes, with performance losses of 1 dB or less in some cases as compared with sum-product algorithm [30].

#### 2.3.2 Serial LDPC Decoder Implementation

A bit-serial implementation of an LDPC decoder is able to reduce interconnect and routing complexity to a large extent and allows for longer code lengths. The multi-wire connections between nodes are replaced by single wires transmitting bits serially, resulting in significant reduction in the interleaver wiring. This implementation however, comes at a price of reduced throughput and higher switching activity in the decoder interconnects. With increase in LLR message precision, more number of clock cycles will be required for decoding each code word, as the number of bits to be transmitted serially across the decoder nodes increases.

Implementing satisfactory throughput in serial LDPC decoders is challenging. In [23], [35] and [36] a bit-serial message passing scheme is presented. The check node update units (CNUs) process the data bit-serially in MSB-first sign-magnitude format, while the variable node update units (VNUs) process the data serially in LSB-first 2's complement format. Therefore, the messages need to be stored and format conversions are required at the output of VNUs and CNUs. To maximize the utilization of decoder hardware two successive frames are simultaneously decoded in the block-interlaced mode; thus, doubling the throughput. The bit-serial LDPC decoder implementation presented by Darabiha *et al.* [4] employs variable nodes with parallel adders. The messages arriving from the check nodes are buffered and converted to parallel inputs and addition operations are performed in a single clock cycle. Processing two frames at once allows for double the throughput; however, the design of parallel adders is much complex than serial adders.

Digit-online decoding of LDPC block codes was proposed by Marshall *et al.*[5],[15], which involves deeply pipelined digit-serial processing in the decoder. Instead of using conventional sign-magnitude format, messages in digit-online decoder are expressed in the form of signed-

binary digit format. The variable nodes and the check nodes process signed-binary format LLR messages in a most-significant-digit (MSD)-first fashion without requiring any changes in message format or order of digits at the node inputs.

#### 2.3.3 Stochastic LDPC Decoding

Stochastic decoding is another method of reducing the interconnect complexity involved in LDPC decoders. Stochastic techniques were introduced in 1960s [37], and have been successfully used in implementation of neural networks [38] and are increasingly becoming popular in LDPC decoder implementations. Stochastic LDPC decoders are similar to bit-serial LDPC decoders in sense that extrinsic messages are communicated over single wires, thus interleaver wiring requirements are lower. The variable node and the check nodes operation can be implemented with simple architectures. For example, multiplication operation can be done as easy as ANDing two inputs together and a J-K flip flop can implement a division operation.

Therefore, stochastic LDPC decoders allow for low-complexity computational nodes and reduced routing congestion. Stochastic LDPC decoding uses a unique way of representing probabilistic messages as Bernoulli sequences indicating values in between 0.0 and 1.0 [39], [40], [41]. At the transmission side LLRs are turned into stochastic streams based on their probabilities, therefore, the encoding scheme is not unique and different sequences are possible for same probability values. For a message size of S bits, if r bits are 1 then the probability P represented by this message is given by:

$$\mathbf{P} = (\mathbf{r}/\mathbf{S}) \tag{1.9}$$

The frequency of 1s in the probabilistic message is equal to the probability P. Stochastic decoders, however do not get as large of a coding gain as sum-product decoders. Also, they are sensitive to the level of switching activity in the decoder and result in reduced decoding performance with reduction in switching activity. The lack of switching activity (latching)

worsens at high SNRs in which received LLR probabilities reach either 0 or 1. There are different techniques proposed in the literature like NDS (noise-dependent scaling), regenerative EMs (edge memories) and IMs (internal memories), which help to provide high switching activity in stochastic nodes [40], [41]. A parallel stochastic decoder capable of a maximum throughput of 61.3 Gb/s and very low error floor is presented in [42].

#### 2.3.4 Analog LDPC Decoders

Apart from digital LDPC decoders, an analog circuit for decoding LDPC codes was reported by Hemati *et al.* in 2006 [43]. The analog LDPC decoder employs iterative analog min-sum (MS) algorithm to decode a (32, 8) LDPC code. The node circuits in the analog decoder are based on current-mirrors and fabricated in 180-nm CMOS technology. The data throughput for the analog LDPC decoder is 6 Mb/s and power consumption is about 5 mW. However, designing analog LDPC decoders requires high process control to design accurate current mirror circuits. Analog LDPC decoders suffer from physical non-idealities such as component mismatch, thermal noise effects and short-channel effects; therefore, they have been only considered for small LDPC codes [44].

### 2.4 LDPC Decoder Implementation on FPGA

FPGAs provide reduced opportunities for parallelism but increased flexibility when compared with ASIC implementations of LDPC decoders. The routing requirements of the Tanner graph edges pose a lot of strain on the programmable interconnect fabric of an FPGA, especially for significantly longer routings. Since FPGAs are more suitable for datapath-intensive designs and have interconnects optimized for local routing [45], the implementation of less parallel and constrained LDPC decoders is more suitable for FPGAs. A parallel LDPC decoder synthesized on FPGA is reported by Zarubica *et al.* in [46] which is able to reach 12 Gb/s throughput. The biggest decoder in [46] to fit on the FPGA has a frame length of 1200 bits with 3-bit input channel LLR precision.

FPGAs also provide the benefit of already available extra hardware like block memories and DSP blocks. In [47] Zarubica *et al.* make use of the distributed memories available on the FPGA for storing the messages needed in the decoding iterations and suggests that use of memories can enable implementation of decoders for large code sizes. An implementation of 9984-bit block LDPC code decoder is reported in [47]. A partially parallel LDPC decoder architecture is synthesized on a Xilinx Virtex-5 FPGA for a rate-1/2 code of size 648 bits by Kim *et al.* [48]. A summary of the decoder along with reported power data for the decoder is shown in Table 2.1.

A bit-serial LDPC decoder presented in [4] is implemented on an Altera Stratix EP1S80 FPGA and occupies about 84% of logic resources. The maximum clock frequency of the decoder is 61 MHz and it can reach a throughput of 650 Mb/s with early termination. The use of FPGAs in implementation of stochastic decoders has been demonstrated by Tehrani *et al.* in [41] and [49], achieving throughputs upto 706 Mb/s and 1.66 Gb/s respectively.

Gunnam et al. present a multi-rate decoding architecture for irregular LDPC codes for WiMAX (IEEE 802.16) standard, resulting in significant savings in memory and routing requirements of the decoder [50]. Table 2.1 shows a summary of the decoders synthesized on the FPGA in [50]. A modified 2-bit min-sum LDPC decoding algorithm is proposed by Chandrasetty *et al.* resulting in a reduced implementation complexity of the decoder [51]. With a slight drop in the BER performance, the decoder can be implemented in about 18% less FPGA resources. An improvement on this implementation is presented in [52] by keeping different length intrinsic (LLR messages entering the decoder from channel) and extrinsic (LLR messages length reduces the interconnect complexity and also simplifies the check node operation. The LDPC decoder in [52] decodes rate-1/2 code words of size 1152 bits.

Two optimization techniques, vectorization and folding are presented by Chen *et al.* in [53] for effective utilization of block RAM resources available on the FPGA. Both these techniques build on the fact that the block RAMs available in FPGAs are of configurable aspect ratios and are dual-ported with very fast access times. Vectorization attempts to pack multiple messages

|                  |                          |                  |                        | I                        |            |                         |

|------------------|--------------------------|------------------|------------------------|--------------------------|------------|-------------------------|

| References       | ,                        | Zarubica et al., | Gunnam et al.          | Tehrani et al.           | Kim et al. | Sulek et al.            |

| References       | [4]                      | [46]             | [50]                   | [36]                     | [48]       | [54]                    |

| Year             | 2006                     | 2007             | 2007                   | 2008                     | 2010       | 2013                    |

| EDCA             | Altera Stratix           | Xilinx V4        | Xilinx V2              | Xilinx V4                | Xilinx V5  | Xilinx V6               |

| FPGA             | EP1S80                   | XC4VLX200        | XC2V8000               | XC4VLX200                | XC5VLX155T | XC6VLX240T              |

| LDPC             | RSbased                  | Parallel PEG     | OMS                    | Parallel                 | Partially  | GF(q) LDPC              |

| Code Type        | LDPC                     | based (6, 3)     | Algorithm              | Stochastic               | parallel   | Decoding                |

| Code Size        | (480, 355)               | (1200, 600)      | 576 b<br>(multi rates) | (1056, 528)              | (648, 324) | (480, 240)              |

| Throughput       | 650 Mb/s                 | 12 Gb/s          | 41-70 Mb/s             | 1.66 Gb/s                | 110 Mb/s   | 6 Mb/s                  |

| LLR              | 2 1.4                    | 2 1.4            | 5 1.14                 | (hit (in mut)            |            | 0 1.4                   |

| Message          | 3 bit                    | 3 bit            | 5 bit                  | 6 bit (input)            | -          | 8 bit                   |

| Max.             | 15                       | 10               |                        | 700 (DC <sub>max</sub> ) | 8          | 10                      |

| Iterations       | 15                       | 10               | -                      | (1DC/clk)                | 8          | 10                      |

| Reported         | 10 <sup>-5</sup> at 5dB* |                  |                        | $10^{-8}$ at             |            | 7 x 10 <sup>-6</sup> at |

| BER              | 10 at Sub*               | -                | -                      | 4.25 dB                  | -          | 2 dB*                   |

| f <sub>Max</sub> | 61 MHz                   | 100 MHz          | 110 MHz                | 222 MHz                  | 100 MHz    | 180 MHz                 |

| Logic            | 84 %                     | 450/             |                        |                          |            | 7 %                     |

| Utilization      | (66,588 LEs)             | 45%              | -                      |                          | -          | / %0                    |

| Slices           |                          | 40 (12           | 1 ( 40                 | 46.007                   | 7.001      |                         |

| (Xilinx)         | -                        | 40,613           | 1,640                  | 46,097                   | 7,081      |                         |

| LUTs             | -                        | 69,038           | 2,982                  | 68,112                   | 19,761     | 10,916                  |

| Block RAM        | -                        | -                | 38                     | -                        | 24         | 26                      |

| Decoder          |                          |                  |                        |                          |            |                         |

| Power            | -                        | -                | -                      | -                        |            |                         |

| E/b              | -                        | -                | -                      | -                        |            | -                       |

|                  |                          |                  |                        |                          |            |                         |

Table 2.1: Summary of some of the discussed FPGA based decoders

into the same word by utilizing configurable width of block RAM, while folding attempts to take advantage of configurable depth of block RAMs by allowing messages from different submatrices of the code to share the same physical block RAM. Li *et al.* present an FPGA implementation of 2.4 Gb/s, rate-1/2, (3, 6) convolutional encoder and decoder and discuss a detailed decoder power analysis for various aspects of the FPGA implementation [9]. In recent years, non-binary or higher-order Galois-field (GF) LDPC decoders implemented on FPGAs have been reported in literature. In case of Galois-field GF(q =  $2^{p}$ ) codes the decoding complexity grows exponentially [54] with  $2^{pd}_{c}$  (d<sub>c</sub> is the maximal nonzero entities in parity check matrix row). Non-binary decoders benefit from the extra available FPGA resources like configuration logic blocks, block RAMs and multipliers. [55] also presents non-binary decoders for different order implementations. Table 2.2 shows the important aspects of the works mentioned in this section which report the power data for the FPGA implementations.

| References           | Chen'11 [53]              | Chandrasetty'11<br>[52]      | Li'13 [9]                        | This work                         |                          |  |

|----------------------|---------------------------|------------------------------|----------------------------------|-----------------------------------|--------------------------|--|

| Year                 | 2011                      | 2012                         | 2013                             | 2014                              |                          |  |

| FPGA                 | Xilinx V4<br>XC4VLX200    | Xilinx V5<br>XC5VLX110T      | Altera<br>StratixIV<br>EP4SGX230 | Altera StratixIV<br>EP4SGX230     |                          |  |

| LDPC<br>Code Type    | Quasi-Cyclic<br>Irregular | (3, 6) Regular<br>MMS        | PN- LDPC-<br>CC<br>(3, 6)        | Digit-online LDPC decoding        |                          |  |

| Code Size            | (3969, 3213)              | (1152, 576)                  | $T_{s} = 192$                    | (576, 432)                        |                          |  |

| Max.Throughput       | 1.474 Gb/s                | 11.7 Gb/s                    | 2.4 Gb/s                         | 740 Mb/s                          | 1363 Mb/s                |  |

| LLR Message          | 6 –bit                    | 4 – bit (input)              | 4 –bit                           | 6-bit                             | 11-bit(interlaced)       |  |

| Max.<br>Iterations   | 15                        | 10                           | 9                                | 10                                | 10                       |  |

| Reported BER         | -                         | 3x10 <sup>-6</sup> at 3.9 dB | 10 <sup>-8</sup> at 4.25<br>dB   | 1.2x 10 <sup>-10</sup> at 4<br>dB | -                        |  |

| f <sub>Max</sub>     | 195.7 MHz                 | 138 MHz                      | 75 MHz                           | 90 MHz                            | 140 MHz                  |  |

| Logic<br>Utilization | -                         | -                            | 83 %                             | 91%                               | 90%                      |  |

| Slices (Xilinx)      | 62,362                    | 10,823                       | -                                | -                                 |                          |  |

| LUTs                 | 98,003                    | 39,024                       | -                                | -                                 |                          |  |

| Block RAM            | 330                       | -                            | -                                | -                                 |                          |  |

| Decoder<br>Power     | 7632 mW                   | 1130 mW                      | 4105 mW                          | 1248 mW (at<br>450 Mb/s)          | 1029 mW (at 450<br>Mb/s) |  |

| E/b                  | 5.18 nJ                   | -                            | 1.71 nJ                          | 2.77 nJ(avg.)                     | 2.29 nJ (avg.)           |  |

Table 2.2: Summary of FPGA based decoders with reported power data

## 2.5 Altera Stratix IV FPGAs

An FPGA is a semiconductor device consisting of programmable logic components, programmable interconnects and I/Os. Present-generation FPGAs also contain additional features such as configurable embedded SRAMs, DSP blocks and high-speed transceivers. FPGAs can be programmed to replicate the functionality of basic gates as well as complex logic functions.

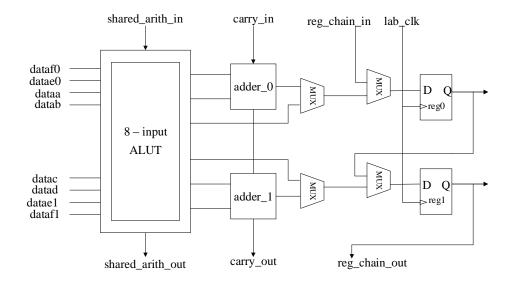

An Altera Stratix IV FPGA core is fabricated in 40nm technology and is made up of multiple LABs (Logic Array Blocks). Each LAB consists of 10 ALMs (Adaptive Logic Modules) along with interconnect and control circuitry. An ALM is the basic building block of Stratix IV FPGA and provides features for efficient logic usage. An ALM consists of a variety of resources consisting of one 8-input ALUT (Adaptive Look Up Table), two dedicated full

adders and two dedicated registers as shown in Figure 2.3. One ALM can implement variety of functions including all 2,3,4,5,6-input functions and certain 7-input functions [56].

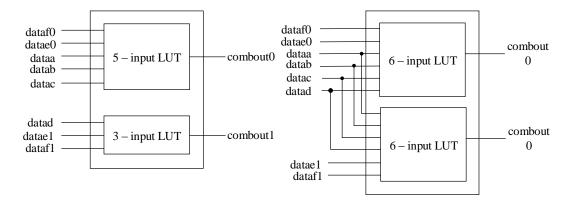

Figure 2.4 shows two examples from normal-mode of the ALMs, implementing 3-input, 5input and 6-input functions. This mode is suited for implementing general logic applications or combinatorial functions.

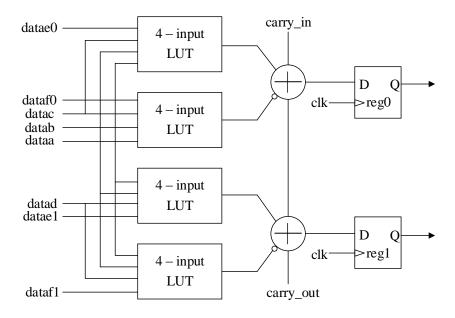

For implementation of addition circuits, comparators and counters, ALMs can be used in arithmetic-mode; shown in Figure 2.5. The adders can form large carry chains, the 4-input LUTs provide for pre-adder logic. ALM in arithmetic mode supports use of adder's carry output along with combinational logic outputs simultaneously. The carry chains in adders can run to very long lengths, from one ALM to next ALM and in between LABs.

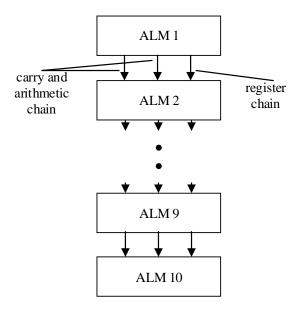

Quartus<sup>®</sup> II can allocate carry chains up to the length of a vertical column in FPGA fabric. Similarly, registers in ALMs can be cascaded together to form long register chains to implement large shift registers. Figure 2.6 shows example of data chains in a Stratix IV LAB.

Figure 2.3 : High level diagram of a Stratix IV ALM

Figure 2.4: Normal mode allows (a) two distinct functions a 5-input and a 3-input; (b) Two 6-input functions with shared inputs to be implemented in a single Stratix IV ALM

Figure 2.5 : Stratix IV ALM in Arithmetic mode

Figure 2.6: Carry, Arithmetic and Register chains in Stratix IV

# Chapter 3 Digit-Online Decoder

In this Chapter, a brief overview of the architecture of a digit-online LDPC decoder and its operation is discussed. This Chapter mainly builds on the works from [5], [15], [57].

#### **3.1 Digit-Online Arithmetic**

An online algorithm processes inputs piece-by-piece without needing a complete set of inputs to begin the calculations. For the processing to be digit-online [58], [59], [60] the operation should be able to produce  $i - \Delta$  most-significant digits of a result knowing only i digits out of the s digits of precision of input (s>i), with  $\Delta$  being the initial delay to produce first output. Thus, such a processing can achieve a very high level of pipelining, with a new set of outputs being produced every clock cycle.

The digit-online decoder in [57] employs the MS algorithm with offset correction. The variable nodes in a digit-online decoder perform an addition operation and the check nodes implement selection networks to select the minimum of the inputs. An offset correction operation is performed in the check nodes. The operations in a digit-online decoder are performed in a serial manner, with the most-significant digits (MSDs) processed first. It is not possible to perform MSD-first addition using the conventional notations without receiving all of the bits of the inputs being added, because carry values need to be propagated from the LSB. Thus a processing algorithm using conventional notations is not very advantageous from the point-of-view of serial processing. A pipelined digit-online process requires taking in new set of inputs and generating a new set of outputs every clock cycle.

To achieve highly pipelined continuous processing at the decoding nodes, the work in [5], [15], [57] uses redundant notation to represent numbers and represents them in form of generalized digits rather than bits. A class of number representations known as signed-digit

representation scheme is shown in [57], which allows for most-significant digit (MSD) to least-significant digit (LSD) addition of numbers.

Unlike conventional number representations where an integer radix r (r >1) each digit can only assume out of 0, 1,..., r-1 values, signed-digit representation allows for representations using negative integers as well. For a conventional number representation digits take values from set {0, 1} while for signed-binary the values from set { $\overline{1}$ , 0, 1} are allowed.  $\overline{1}$  represents -1, and borrows 1 from the digit before it. Thus, the representations of numbers are no longer unique. For example,  $11\overline{1} = 4 + 2 + (-1)$  and 101 = 4 + 0 + 1 represent same number in decimal format. Since the channel LLRs are provided to the decoder in conventional binary notation, they need to be converted in signed-binary digit format in the decoder.

Conversion of conventional sign-magnitude binary representation into signed-binary representation is shown in [57]. For conversion of positive numbers, the MSD of the resultant signed-binary number is set to zero and the remaining digits are left as is; however, now this number is stored with a greater number of bits. For the negative number conversion, the MSD is set to zero, and the remaining digits are stored as negative copies of the corresponding binary bits. The digit-online decoder in [5], [15], [57] converts channel LLRs into signed-binary representation from sign-magnitude representation in the first decoding iteration. The conversion from signed-binary representation to conventional binary representation becomes increasingly expensive to implement with increasing LLR precisions. After the decoding iterations are complete, a thresholding operation is performed to produce hard outputs. Performing this thresholding operation only requires the knowledge about the sign of final LLRs output from the variable nodes, which is relatively inexpensive and easy to implement.

When decoding LDPC codes with the MS algorithm using offset correction, the operations that need to be performed in the decoder are: addition, subtraction, compare-select and sign detection. All of these operations are explained in detail in [5], [15], [57] to work with redundant (signed-binary) notation with most-significant-digit (MSD)-first digit-online processing.

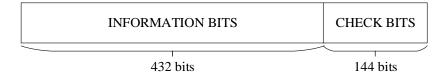

#### 3.2 LDPC Encoder

The VHDL files for the block LDPC encoder are generated using a C++ routine. The WiMAX standard supports frame sizes ranging from 576 bits to 2304 bits and supported code rates are 1/2, 2/3, 3/4, 5/6 with a minimum throughput requirement of 100 Mb/s. For this work, a 576-bit, rate-3/4 WiMAX Encoder is generated. The base matrix (.hbm) and half a- list (.alist) files provide information about the encoder structure to the C++ routine, while the size of the code word is decided through the expansion factor (Z) passed on to the routine. The encoder takes in a 432-bit input, generates and appends 144 check bits to generate a 576-bit frame as shown in Figure 3.1. The check bits of the frame are calculated as per the code constraint equations.

## 3.3 Digit-Online Decoder

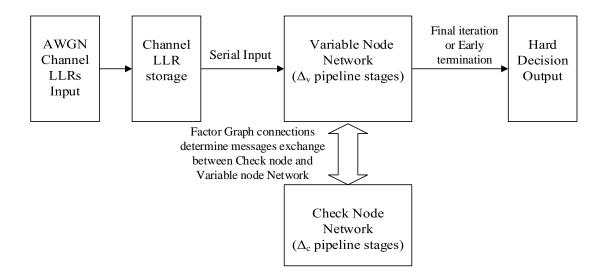

In an iterative LDPC decoder, each decoding iteration consists of messages flowing from the variable nodes to the check nodes and back. Thus, the total pipeline length (p) for one decoding iteration is equal to the sum of the variable node pipeline stages ( $\Delta_v$ ) and the check node pipeline stages ( $\Delta_c$ ) (Figure 3.2). Each pipeline stage stores and processes one digit, thus length of the input message should be less than  $\Delta_v + \Delta_c$  digits (total pipeline stages in one iteration), since guard digits need to be added into the message to prevent overflow in the variable nodes. The number of guard digits depends on the maximum variable node degree ( $d_{v,max}$ ) and the way values are being added in variable node [57]; however, an optimum number is given by [log2(dv,max)].

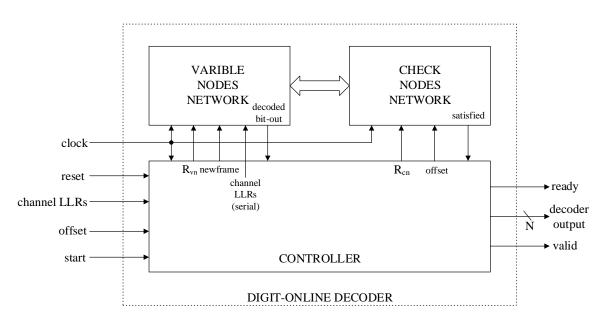

To distinguish the MSD of an LLR from other digits, each processing node in the decoder receives a globally synchronized control input (Figure 3.3). The vector version of this control

Figure 3.1 : A 576-b encoder frame output from the LDPC Encoder

Figure 3.2 : Digit-online decoder system diagram. Channel LLRs are sent serially to the variable nodes. The messages are passed between variable node array and check node array. Each iteration involves message going to check nodes and back to variable nodes for a total pipeline length of  $\Delta_v + \Delta_c$ .

Figure 3.3 : Various components of a digit-online decoder. Main signals are shown as well.

signal is called **R**, with  $\mathbf{r}_i$  being equal to 1 if the current i<sup>th</sup> input digit to a node is an MSD. This signal is required to reset the state machines in check nodes and break carry chains in adders in variable nodes for the new LLR messages [57].

**R** is expanded to the length of the pipeline, with multiple 1s in the R vector for decoding more than one frames simultaneously. The distance between 1s depends on the precision of LLRs. The processing nodes work on a continuous stream of data and need to know only where the LLR message starts and ends; thus, variable length LLR messages can be processed easily.

#### 3.3.1 Variable Node Structure

Variable nodes perform the addition operation on LLR messages as shown in equation below:

$$\lambda_i = L_{channel} + \sum_{\substack{j=1\\i\neq j}}^{\Delta_v} Lj \tag{3.1}$$

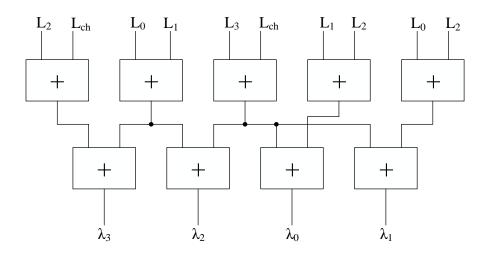

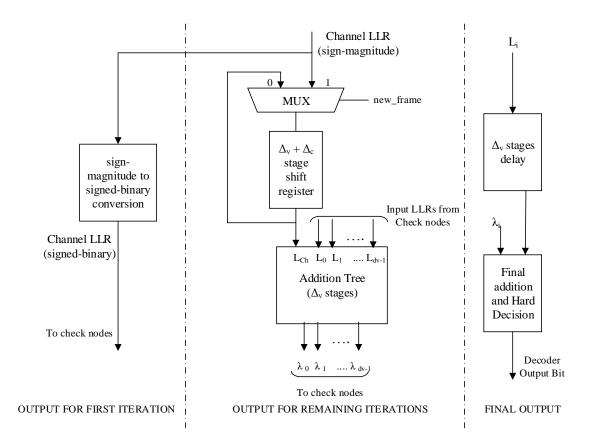

The addition trees in the variable nodes have been optimized for minimum  $\Delta_v$  and minimum required guard digits [57]. Optimization for small number of required guard digits also reduces overhead associated with their generation. An example structure of a degree-4 variable node is represented in Figure 3.4.

Figure 3.5 shows the variable node structure indicating the variable node outputs for various stages of decoding. In the first decoding iteration of a new frame, since the channel values are provided to the variable nodes in conventional sign-magnitude format, they are converted to signed-binary format and are output to the check nodes. A separate circuit is used for the conversion of sign-magnitude to signed-binary values. New channel values are loaded into the local channel memory in the variable nodes for use in future iterations. The local channel memory in the variable nodes is implemented as a circular shift register with output of the shift register connecting to the input when the new\_frame signal is 'low'. The local channel

Figure 3.4 : An example degree-4 variable node. The LLRs,  $L_{ch}$  (channel LLRs) and  $L_0$ ,  $L_1$ ,  $L_2$ ,  $L_3$  are added digit-serially in the adders represented by boxes with '+' sign

memory has a length equal to the pipeline length of  $(\Delta_c + \Delta_v)$  stages. Since new values in the local memory are only loaded in the first decoding iteration of a new frame, the local channel memory provides channel values in a digit-serial manner to the addition circuitry for the remaining decoding iterations of the frame. In the final iteration, new old channel values are shifted out to perform the final addition operation and the new frame channel values are loaded in the local channel memory. The final addition operation consists of adding  $\Delta_v + 1$  values (all incoming edge messages and local channel values). After final addition since the next step is hard-decision output, only the sign of the final output LLR ( $\lambda_{\text{final}}$ ) is of significance. So even if an overflow occurs in final addition, the sign of the result needs to be preserved while the magnitude can be incorrect [57].

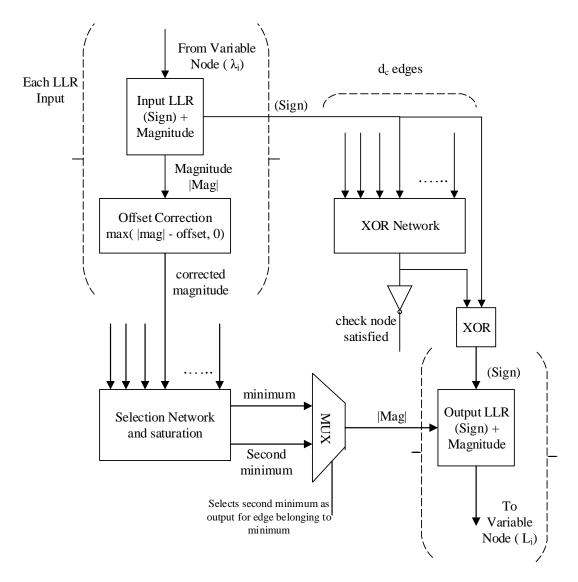

#### 3.3.2 Check Node Structure

The check nodes perform the minimum input selection operation through the use of selection networks. To compensate for the performance loss as compared with SP algorithm, an offset correction is performed in check nodes. If decoder constraints are met before the final iteration, check nodes output a 'satisfied' signal to indicate early termination of decoding to the controller. The architecture of a check node is shown in Figure 3.6. The sign of the incoming

Figure 3.5: Variable node structure. In the first iteration new channel LLRs are received serially and converted to signed-binary format and sent to check nodes. New channel values are also loaded in the shift register for use in later iterations. The process for final output is illustrated on the right hand side.

LLRs in the check nodes is determined and sent to the XOR network tree to check if the code constraints are meeting already and early termination can be performed.

The magnitude of the incoming LLRs undergoes offset correction. The offset value is stored in conventional binary format and is subtracted from the LLR magnitudes using digit-online subtraction circuits [57]. The resultant magnitudes if negative, are replaced with all zeroes otherwise kept as is. Offset correction applied on the inputs of the selection networks requires more subtraction circuits than offset correction applied at selection network outputs; however,

Figure 3.6: Digit-online check node structure. The sign of the incoming serial LLR is sent to an XOR network to identify if check node constraints are satisfied. Magnitude of LLR is sent for offset correction, preceding a selection network to calculate the minimum values. Appropriate magnitude is selected and then combined with sign to be sent to variable node edge.

[57] notes that performing offset correction at selection network outputs lead to incorrect results for digit-online processing. The selection network in the check nodes selects a minimum and a second-minimum magnitude. [61] provides an excellent online tool with various implementation options for generating selection networks up to 32 inputs. The WiMAX 576-bit, rate-3/4 LDPC decoder discussed in this thesis requires selection networks of 14 and 15 inputs; these selection network have been generated using "best" algorithm option in the online tool, giving the minimum number of comparisons required for implementation [57].

When processing MSD-first serially in redundant notation, the selection of minimum values is complicated. The numbers that appear smaller in the beginning may not be so when received completely. While comparing numbers the difference between the numbers is tracked as long as it is big enough and it is safe to make a decision on which number is smaller [57]. For the case of compared numbers being equal, a number is selected as the smaller one arbitrarily. Each comparator comparing two numbers A and B, issues a signal AIsSmaller, which is '1' if the number A is smaller of the two. This signal may change its value as the comparison progresses digit-by-digit, however this should occur only certain times to ensure correct results. The signal AIsSmaller from the individual comparators in the selection tree is used to track the minimum input magnitudes.

The minimum values at the outputs of the check nodes are checked for overflow, and if required they are saturated before sending to the variable nodes. The minimum number is output at all the check node edges except for the edge where this number came from, on which the second-minimum value is sent instead. The sign of the outputs is decided according to what other edges suggest the output sign should be. Thus, the sign of each output LLR is found by XORing the input sign for that edge to the output of the XOR network.

### 3.3.3 Controller

The controller is responsible for synchronizing the data flow between the variable and the check nodes. For irregular codes, the nodes are of varying degrees and there is a need to ensure that the pipeline path-length for all the node types is same and equal to  $\Delta_v + \Delta_c$ . If required,

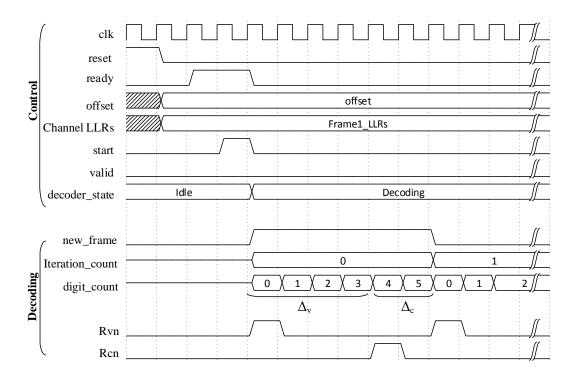

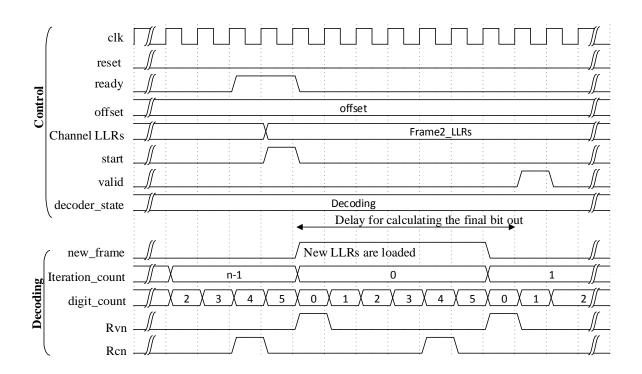

extra registers can be added in the nodes during synthesis to gain desired loop latency. The control signal R, as discussed before is generated by controller to keep track of the MSDs of the messages during serial processing. Controller issues  $R_{vn}$  signal for the variable nodes and  $R_{cn}$  signal for the check nodes. When the variable nodes are receiving the MSD of a message,  $R_{vn}$  signal is asserted '1'; while  $R_{cn}$  is '1' when the check nodes are receiving the MSD.  $R_{vn}$  and  $R_{cn}$  signals can be seen in the timing diagrams of the digit-online decoder as shown in Figure 3.7 and Figure 3.8.

Channel LLRs and offset values are loaded from the channel LLR buffer into the decoder in bit-parallel manner. Controller sends channel LLR values to the variable nodes and the offset value to the check nodes in bit-serial fashion in the beginning of decoding. new\_frame signal acts as a selection input for the MUX in the variable node structure shown in Figure 3.5, in the first decoding iteration, new\_frame signal is kept '1'. While new\_frame is 1, the MUX in the variable node loads the new channel values to the local channel memory. After first iteration, new\_frame signal is pulled to 0. This converts the local channel memory in a circular shift register, providing channel LLR values for future iterations.

The controller also monitors the number of decoding iterations performed. The maximum number of iterations allowed  $(i_{max})$  per code word is fixed at the time of design. After performing  $i_{max}$  iterations, the decoder signals the variable nodes to finish decoding current code word and perform a hard-decision (thresholding operation). Hard-decision output bits from individual variable nodes are appended together and output as a decoded code word. It is possible that the check node constraints are satisfied before the  $i_{max}$  iterations are reached (early termination criterion). Controller detects early termination from the satisfied signal generated at the check nodes. Each check node 'n' generates its satisfied signal CNsatisfied(n). The controller performs an AND operation on CNsatisfied from all the check nodes and if result is a '1' then it signals the next iteration to be final iteration.

### 3.3.4 Single Frame Decoding

Figure 3.7 shows timing diagrams of the various signals in the decoder when beginning decoding and loading a new frame. Figure 3.8 shows the timing diagram when finishing the decoding of current frame and starting with a new frame respectively in single-frame mode of decoding. The decoder is initialized by pulling reset 'low'. An offset value must be applied before initializing the decoder, since it is latched in with reset going 'low'. In an actual design, the offset is supplied in the HDL code, and its value is available to the decoder pre-initialization. After being initialized, the decoder asserts a ready = '1' signal indicating it is ready to take in channel LLR values. The channel LLRs are made available to the decoder and the decoder is signaled to start decoding by asserting start signal 'high'. The Start signal is

Figure 3.7 : Beginning of decoding a frame in single-frame mode. The decoder goes into Idle state when reset signal goes 0, and asserts 'ready' signal as 1. On receiving a 1 on 'start' pin, the decoder loads in the channel LLRs, pulls in 'ready' signal low and goes into DECODING state beginning with Iteration 0 for decoding the frame. In this example  $\Delta_v = 4$  and  $\Delta_c = 2$ , therefore the length of the pipeline is equal to  $\Delta_v + \Delta_c = 6$ .

pulled 'low' after one clock cycle; the decoder pulls ready signal 'low' as well. To keep the iterations going on continuously, the decoder asserts ready signal little before the last iteration finishes as shown in Figure 3.8. Thus, before the final iteration is over, the channel LLR buffer is able to respond with new frame LLRs. Next iteration is first iteration of the new frame, the old frame values are sent into the variable node pipeline for hard-decision decoding. The delay for the final decoded code word is represented in Figure 3.8. This delay is dependent on the pipeline depth in the decoder and is given by  $t_{delay,bitout}$  (= $\Delta_{v,sat} + \Delta_v + \Delta_c$ ) clock cycles. Thus after  $t_{delay,bitout}$  clock cycles, the resulting hard-decoded frame is output and the decoder is asserts valid signal 'high' for one clock cycle. The iteration count keeps incrementing from 0 to n-1 in a continuous circular fashion and decoder outputs a decoded frame every n iterations.

Figure 3.8: Finishing decoding previous frame, hard-decision output and loading next frame for single-frame decoding. The decoder hard-decision output of previous frame at beginning of iteration 1 of new frame. Iteration 0 is used up in hard-decision calculation of previous frame.

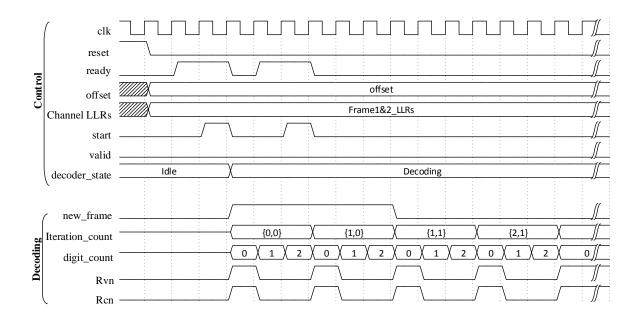

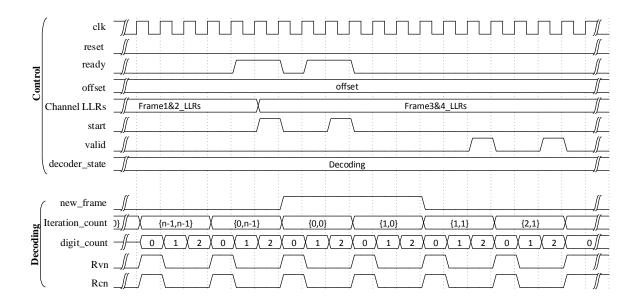

### 3.3.5 Frame-Interlaced Decoding

Frame-interlaced decoding enables the digit-online decoder to decode 2 frames simultaneously. However, the LLR precision of the frames being decoded is halved. The frame-interlaced mode does not require major changes in the decoder structure. Thus, for a slight change in implementation area, it is possible to achieve nearly twice the throughput [5], [15], [57]. Figure 3.9 illustrates the timing diagrams for various signals when beginning decoding and loading new frames. Figure 3.10 shows timing diagram when finishing decoding of previous frames and loading in new frames in frame-interlaced mode.

Pulling reset signal 'low' initializes the decoder. Upon initialization, the decoder asserts a ready signal 'high' when it is ready to start decoding. The channel LLR buffer responds by providing channel LLRs and asserting start bit 'high'. The input channel LLRs consist of LLRs

Figure 3.9 : The beginning of frame-interlaced decoding. Each iteration from single frame decoding is split in two iterations. Iteration number {1,0}, represents iteration 1 for frame 1 and iteration 0 for frame 2. There is a frame counter implemented as well to keep track of the frame number. The pipeline length for each frame is halved.

for both frame 1 and frame 2 LLRs in an interlaced manner. The total pipeline length of the decoder is distributed between the two frames. The new\_frame signal stays '1' for the duration of iteration  $\{0,0\}$  and  $\{1,0\}$ . The channel LLRs are loaded in variable nodes in this duration. The processing nodes in the digit-online decoders do not require information about which frame they are processing; they only need to know when MSDs for a frame appear. Thus, structurally frame-interlaced decoding is very similar to single-frame decoding. However the control signal differ, as shown in Figure 3.9 and Figure 3.10,  $R_{vn}$  and  $R_{cn}$  signals are asserted twice in each frame iteration.

When finishing decoding, a ready signal is asserted 'high' before the iteration counter resets to  $\{0,0\}$  to signal channel LLR buffer to send in new channel LLRs. The decoded frames are output after a delay similar to as explained in Single-frame decoding, the decoder output changes at each valid signal as shown in Figure 3.10.

Figure 3.10: Finishing decoding current frames and loading new frames in frame-interlaced decoding. The frames are output after a delay required for hard-decision decoding.  $\Delta_v$  and  $\Delta_c$  may not be equal and frames may not be in same decoding iteration.

The channel LLR values that are introduced to the decoder in conventional sign-magnitude format. The AWGN channel module generates channel LLRs and stores them in the channel LLR buffer module, until the decoder is ready to receive new LLRs. LLRs are converted in signed-binary format in the variable nodes only when the decoding begins, doing so reduces memory and fan-in requirements, since signed-binary format requires more number of bits to represent a number.

The hard-decision output of the frame being decoded is performed if either of the two events occur: 1) maximum number of iterations have taken place, or 2) all the check node equations are satisfied (early termination). The maximum number of iterations ( $i_{max}$ ) is estimated according to the throughput requirements and rate of code convergence. Minimum throughput of an LDPC decoder is inversely proportional to  $i_{max}$ .

# Chapter 4 Test Unit and Power Measurement Setup

## 4.1 Introduction

FPGA designs are considered more power and area hungry than their ASIC counterparts. However, FPGAs offer many advantages over ASICs such as fast prototyping abilities, allowing users to change and quickly verify idea in hardware rather than waiting for fabrication of a custom ASIC chip. This saves time and cost per FPGA chip if the quantity of product to be deployed is small. The reconfigurability associated with FPGAs increases product lifetime, and any incremental modifications occurring in future designs can be programmed into the FPGAs, as long as they fit in current FPGA, without the need to redesign the whole board.

### 4.1.1 FPGA Implementation

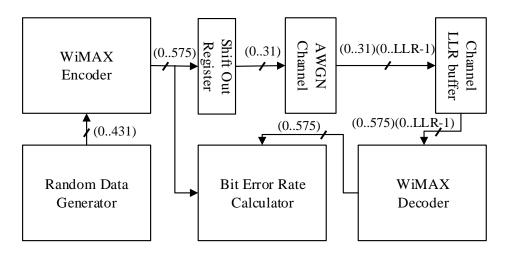

The design is implemented on an Altera Stratix IV GX EP4SGX230 FPGA, which comes on Altera DE4 development and education board. Most of the design is written in VHSIC (Very High Speed Integrated-Circuit) Hardware Description Language (VHDL), with the exception of AWGN Channel Module which is written in Verilog HDL. Figure 4.1 shows various functional blocks in the system.

A random data generator outputs pseudo-random bit patterns through a linear-feedback shift register (LFSR). The bit patterns from the random data generator are fed to WiMAX encoder as information bits (432 bits). Encoder generates check bits according to the code constraints, appends them to the information bits and outputs the resulting bit pattern as an encoded frame (576 bits). A shift-out register works in a parallel-in serial-out shift register manner. The shift-out register buffers the encoded frame of 576 bits and shifts out x bits per clock cycle. For x = 32 bits means that 576 bits of the frame are shifted out completely in 576/32 = 18 clock

cycles. The number of shift-out register output bits control the flow of channel LLRs to the decoder. Thus, for a 50 MHz clock source, shift-out register with x=32 bits allows for 2.77 million frames sent to the decoder in one second.

The shift-out register output bits are added with pseudo-random noise samples and scaled as per the assigned signal-to-noise ratio (SNR) in AWGN channel module and quantized to desired precision LLRs. The AWGN generator works on principal of Box-Muller transform, and generates LLRs for each input bit. Channel LLR buffer, stores the output LLRs from the AWGN module for each encoded bit, until all the LLRs for encoded frame are received. When all LLRs for a frame are received in channel LLR buffer, it waits for ready signal from the WiMAX decoder. On receiving '1' on ready signal, the channel LLR buffer provides the decoder with channel LLR values and signals the decoder to start decoding by asserting '1' on start signal. The start signal stays '1' for one clock cycle and goes back to '0'.

The final part of the system is a bit-error-rate (BER) calculation module. The BER module buffers the encoded and the decoded frames when the valid signal from appears from both the modules. Keeping track of the frame numbers is tricky; thus, to ensure proper operation three most recent frames from the encoder are buffered and compared with decoded frame. An XOR operation between the buffered encoder and decoder frames is performed, any bit errors

Figure 4.1: A block diagram of the FPGA implementation, showing all the component modules. The arrows indicated the flow of data, numbers on the arrows mention the bus-width

between the two frames results in 1s at that specific bit positions. Counting the number of 1s occurring in the output of XOR operation gives us the bit errors per frame. To calculate the BER, a variable keeps track of the number of frames processed until a set number of errors is reached. The decoder area forms the majority of the design's area on FPGA; an average decoder takes about 85-90% of the design area.

The initial approach in this work was to study WiMAX 1056-bit, rate-1/2 codes on FPGA, since a larger code provides better coding gain. Therefore, a bit-parallel LDPC decoder for code word size 1056 bits and rate-1/2 was synthesized on the FPGA. The size of a bit-parallel LDPC decoder increases with input LLR message precision. The biggest 1056-bit, rate-1/2 bit-parallel LDPC decoder that could fit in the FPGA had LLR message precision of 4 bits. The digit-online LDPC decoder for code word size 1056 bits, rate-1/2 was unable to fit on the FPGA for any LLR precision. A digit-online check node tends to occupy a lot more logic resources as compared with a digit-online variable node (see Appendix A). Going for a higher rate code like rate-3/4 reduces the check nodes in decoder by half in number, also a smaller code with size 576 bits was chosen. The biggest 576-bit, rate-3/4 bit-parallel LDPC decoder that can fit on the FPGA has LLR precision of 6 bits. For the 576-bit, rate-3/4 Digit-Online LDPC Decoder, up to an input LLR precision of 13 bits was successfully synthesized on the FPGA. Higher input precision cases might be able to fit as well, but they were not tested. Thus choosing a smaller size code with size 576 bits provides more test cases over a larger range of LLR precisions.

# 4.2 FPGA Core Power Measurement

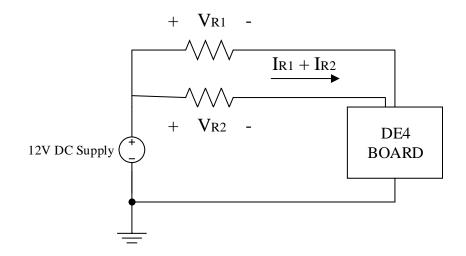

For the measurement of FPGA core power, the setup from [18] is used. A diagram showing the FPGA board power measurement setup is shown in Figure 4.2. The power characterization technique reported in [18] relates the power dissipated in the FPGA core to the actual measured power consumed by the Altera DE4 board. The power measurement setup consists of 0.01- $\Omega$  resistors connected to the power supply lines to DE4 board. There are two power supply lines onto the DE4 power supply: one being the 12V and, the other 3.3 V supply. The

power to the FPGA core is supplied through 12V supply, which is converted to 0.9V for FPGA core using three LTM4601 regulators on the Altera DE4 board [62]. Therefore, the power supplied to the board is calculated by measuring the current through the 12V supply lines.

The voltage drop across the  $0.01-\Omega$  resister connected in series with the supply lines is measured and current through the resistors is calculated by dividing the measured voltage with  $0.01-\Omega$ .

The current across the two 12 V supply lines are added to find out the total input current to the FPGA board.