### Design and Analysis of Agile Frequency Synthesizers for Mobile Communications

by

#### Amr Mohamed Fahim

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2000

© Amr Mohamed Fahim 2000

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada Bibliothèque nationale du Canada

Acquisitions et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

Your file Votre référence

Our file Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-60536-1

The University of Waterloo requires the signatures of all persons using or photocopying this thesis. Please sign below, and give address and date.

### Acknowledgements

After thanking God Almighty for giving me the strength and ability to complete this work, I would like to express my sincere thanks to my parents who have instilled in me the drive and encouragement to complete this work.

I would also like to express my appreciation and gratitude to my thesis supervisor, Professor M. I. Elmasry for his encouragement, guidance and support in my research. He gave me valuable insight and motivation for this work.

I would also like to acknowledge and thank all my colleagues in the VLSI Research Group for their support and useful discussion.

This work is supported in part by research funding from NSERC, Canadian Microelectronics Corporation (CMC) and Micronet. Their contributions are greatly appreciated.

#### **Abstract**

The wireless market has experienced an exponential growth over the past few years. To sustain this growth along with the increasing demands of new wireless standards, the cost, battery lifetime, and performance of wireless devices must all be enhanced.

With the advancement of radio frequency (RF) technology and requirement for more integration, new RF wireless architectures are needed. One of the most critical components in a wireless transceiver is the frequency synthesizer. It largely affects all three dimensions of a wireless transceiver design: cost, battery lifetime, and performance. In this thesis, new generations of RF synthesizer and transmitter architectures allowing low-power, high-performance and lower cost are presented.

The common approach to frequency synthesis design for wireless communication is to design an analog-compensated fractional-N phase-locked loop (PLL). However, this technique suffers from lock time limitations and lack of adequate fractional spur suppression for third generation wireless standards. In this work, two new fast lock PLL architectures are reported to overcome the above mentioned limitations with the aid of digital signal processing. One such scheme makes use of modified digital sigmadelta modulator to completely randomize fractional spurs present in fractional-N PLLs as well as to reduce the level of phase noise produced by the sigma-delta modulator. This aids in fully integrating a high-performance PLL frequency synthesizer, and hence reducing cost. The use of this architecture for closed loop modulation is also examined.

In another approach, a high frequency digital comparator aids in quickly acquiring frequency lock. Very fast lock times are achievable using this architecture. This architecture removes the PLL's frequency resolution dependence on the loop filter

parameters. This helps to drastically reduce the size of the loop filter components, and enables them to be integrated on-chip. Although more suitable for low frequency resolution applications, such as wireless LAN and cordless, this architecture may be modified to obtain higher frequency resolutions. The major advantages of this architecture include low-cost, low-power, and a fully monolithic solution.

Throughout this work, low-power has been achieved by both architectural techniques as well as circuit techniques. Architectural techniques enable tighter integration of the PLL's loop components on a single chip as well as faster lock time. Since the proposed techniques rely heavily on digital signal processing, low-power, high-performance digital logic families are reported. It is demonstrated how these logic families may be used in the frequency synthesizer architectures detailed above. Although differential in nature, it is demonstrated that the use of these logic families also helps to reduce area.

## **Contents**

| 1 | INTRO    | ODUCTION                                            | 1  |

|---|----------|-----------------------------------------------------|----|

| 2 | BACK     | GROUND                                              | 4  |

|   | 2.1 Fre  | quency Synthesizer Requirements in Wireless Systems | 4  |

|   | 2.2 Wi   | reless Transceiver Architectures                    | 7  |

|   | 2.3 Cla  | ssical Phase-Locked Loop                            | 8  |

|   | 2.3.1    | Basic Operation                                     | 8  |

|   | 2.3.2    | PLL Performance Measures                            | 10 |

|   | 2.3.3    | Charge-pump PLL                                     | 13 |

|   | 2.3.4    | Closed Loop PLL Analysis                            | 13 |

|   | 2.3.5    | Phase noise performance                             | 15 |

|   | 2.4 Fra  | ctional-N Phase-Locked Loop                         | 17 |

|   | 2.4.1    | Basic Operation                                     | 17 |

|   | 2.4.2    | Analog Compensated Fractional-N PLL                 | 18 |

|   | 2.4.3    | Sigma-Delta Compensated Fractional-N PLL            | 19 |

|   | 2.5 Fas  | t Lock Phase-Locked Loop Techniques                 | 20 |

| 3 | ANAL     | YSIS OF FRACTIONAL-N PLL                            | 27 |

|   | 3.1 Intr | oduction                                            | 27 |

|   | 3.2 Uno  | compensated Fractional-N PLLs                       | 28 |

|   |          | Time Domain Analysis                                |    |

|   | 3.2.2    | Frequency Domain Analysis                           | 31 |

|   | 3.2.3    | Model Verification                                  | 32 |

|   | 3.3 Ana  | alog Compensated Fractional-N PLLs                  | 35 |

|   |          | Time Domain Analysis                                |    |

|   | 3.3.2    | Frequency Domain Analysis                           | 36 |

|   | 3.3.3     | Model Verification                           | 37     |

|---|-----------|----------------------------------------------|--------|

|   | 3.4 Loc   | ck time characteristics of Fractional-N PLLs | 40     |

|   | 3.4.1     | General Locking characteristics              | 40     |

|   | 3.4.2     | Phase Locking Characteristics                | 42     |

|   | 3.5 Cor   | nclusions                                    | 47     |

| 4 | A MAS     | SH SIGMA-DELTA FRACTIONAL-N PLL              | 49     |

|   | 4.1 Intr  | oduction                                     | 49     |

|   | 4.2 MA    | ASH Sigma-Delta PLL Architecture             | 50     |

|   | 4.2.1     | Digital MASH Sigma-Delta Modulator           | 50     |

|   | 4.2.2     | Sigma-Delta Dithering                        | 54     |

|   | 4.2.3     | PLL Simulation Performance                   | 55     |

|   | 4.3 PLI   | Circuit Implementation                       | 56     |

|   | 4.3.1     | Frequency Divider Design                     | 57     |

|   | 4.3.2     | Other Loop Components                        | 61     |

|   | 4.3.      | 2.1 Charge Pump Design                       | 61     |

|   | 4.3.      | 2.2 Phase-Frequency Detector                 | 62     |

|   | 4.3.      | 2.3 Digital Circuit Implementation           | 64     |

|   | 4.3.3     | Experimental Results                         | 65     |

|   | 4.4 Cor   | nclusions                                    | 68     |

| 5 | A WID     | DEBAND SIGMA-DELTA PHASE-LOCKED LOOP MODULA  | TOR.69 |

|   | 5.1. Intr | oduction                                     | 69     |

|   | 5.2. Cor  | nventional Sigma-Delta PLL                   | 71     |

|   | 5.3. Pro  | posed Sigma-Delta PLL                        | 72     |

|   |           | olementation                                 |        |

|   |           | Digital ΣΔ Modulator                         |        |

|   |           | .1.1 Multiplier Reduction                    |        |

|   |           | .1.2 Multi-input Adder                       |        |

|   |           | Erectional Divider                           | 78     |

|   | 5          | .4.3    | Other Loop Components                           | 84  |

|---|------------|---------|-------------------------------------------------|-----|

|   |            | 5.4.3   | 1 Charge Pump Circuit                           | 84  |

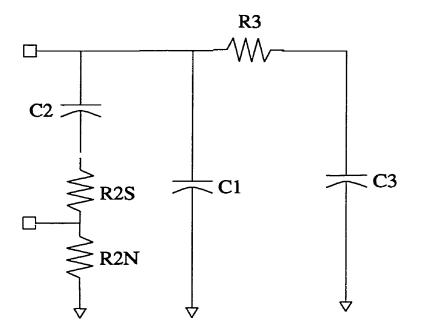

|   |            | 5.4.3.  | 2 Loop Filter Parameters                        | 85  |

|   | 5.5.       | Simu    | lation Results                                  | 86  |

|   | 5.6        | Perfo   | rmance Evaluation                               | 89  |

|   | 5.7        | Conc    | lusions                                         | 90  |

| 6 | <b>A</b> ] | DIGIT   | AL FAST LOCK PLL ARCHITECTURE                   | 92  |

|   | 6.1        | Introd  | luction                                         | 92  |

|   | 6.2        | Propo   | sed PLL Architecture                            | 93  |

|   | 6.         | .2.1 F  | Basic Architecture                              | 93  |

|   | 6.         | .2.2 F  | Resolution Enhanced Architecture                | 95  |

|   | 6.3        | Low     | Resolution Fast Lock Implementation             | 98  |

|   |            |         | Resolution Fast Lock Implementation             |     |

|   | 6.         | .4.1 I  | Direct Implementation                           | 101 |

|   | 6.         | .4.2 F  | High Resolution Fast Lock Architecture          | 102 |

|   | 6.5        | Perfo   | rmance Evaluation                               | 104 |

|   | 6.6        | Conc    | usions                                          | 105 |

| 7 | LC         | )W-P(   | OWER, HIGH-PERFORMANCE DIGITAL ARITHMETIC       | 106 |

|   | 7.1.       | Introd  | luction                                         | 106 |

|   | 7.         | .1.1 I  | ntroduction of Low-Power Design                 | 107 |

|   | 7.2        | Dyna    | mic Differential Logic Families                 | 107 |

|   | 7.         | .2.1 8  | Swing Limited Dynamic Differential logic        | 108 |

|   |            | 7.2.1.  | 1 Conventional Dynamic Logic                    | 108 |

|   |            | 7.2.1.  | 2 Noise Analysis of Swing Limited Dynamic Logic | 109 |

|   | 7.         | .2.2. 8 | Short-Circuit Current Logic                     | 111 |

|   |            | 7.2.2.  | 1 Basic Operation                               | 111 |

|   |            |         | 3 Modified SC <sup>2</sup> L Gate               |     |

|   |            | 722     | 4 SC <sup>2</sup> I Coto Dinelining             | 113 |

| 7.2.2.5 SC <sup>2</sup> L Simulation Results                                                                                                                                                                                                                                                                           | 114                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 7.2.2.6 SC <sup>2</sup> L Experimental Results                                                                                                                                                                                                                                                                         | 115                             |

| 7.2.3 CPCL Logic Family                                                                                                                                                                                                                                                                                                | 117                             |

| 7.2.3.1 Basic Operation                                                                                                                                                                                                                                                                                                | 117                             |

| 7.2.3.2 CPCL Characterization                                                                                                                                                                                                                                                                                          | 118                             |

| 7.3 Differential Static Logic Family                                                                                                                                                                                                                                                                                   | 119                             |

| 7.3.1 LVDSL Family Operating Principle                                                                                                                                                                                                                                                                                 | 119                             |

| 7.3.2 LVDSL Characterization                                                                                                                                                                                                                                                                                           | 121                             |

| 7.3.3 LVDSL Evaluation                                                                                                                                                                                                                                                                                                 | 124                             |

| 7.4 Low-Power Digital Logic in PLL Architectures                                                                                                                                                                                                                                                                       | 126                             |

| 7.4.1 Fast Lock ΣΔ PLL Implementation                                                                                                                                                                                                                                                                                  | 126                             |

| 7.4.2 Fast Lock Digital PLL Implementation                                                                                                                                                                                                                                                                             | 127                             |

| 7.6 Conclusions                                                                                                                                                                                                                                                                                                        | 128                             |

| SUMMARY AND CONCLUSIONS                                                                                                                                                                                                                                                                                                | 130                             |

|                                                                                                                                                                                                                                                                                                                        | •••••                           |

|                                                                                                                                                                                                                                                                                                                        |                                 |

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO                                                                                                                                                                                                                                                                    |                                 |

|                                                                                                                                                                                                                                                                                                                        | N133                            |

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO                                                                                                                                                                                                                                                                    | N133                            |

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction                                                                                                                                                                                                                                                 | N133<br>133                     |

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features                                                                                                                                                                                                                                  | 133<br>133<br>133               |

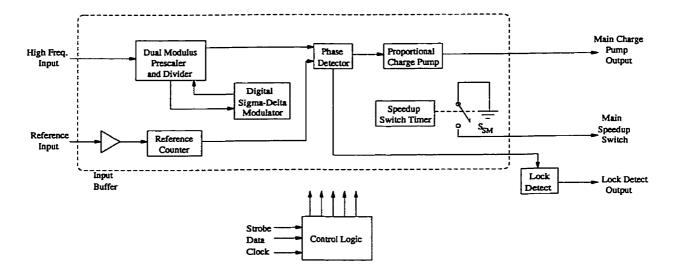

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram                                                                                                                                                                                                              | 133<br>133<br>134<br>135        |

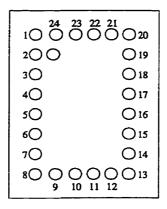

| A 1.2 GHZ \(\Sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments                                                                                                                                                    | 133<br>133<br>134<br>135        |

| A 1.2 GHZ ΣΔ FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface                                                                                                                                                                                   | 133<br>133<br>134<br>135<br>135 |

| A 1.2 GHZ \(\sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments  A.4.2 Terminal Functions  A.5. Specifications                                                                                                     | 133                             |

| A 1.2 GHZ \(\Sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments  A.4.2 Terminal Functions                                                                                                                          | 133                             |

| A 1.2 GHZ \(\Sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments  A.4.2 Terminal Functions  A.5. Specifications  A.5.1 Absolute Maximum Ratings  A.5.2 DC Electrical Characteristics                                | 133                             |

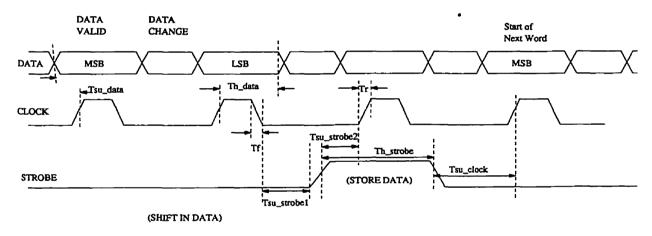

| A 1.2 GHZ \(\sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments  A.4.2 Terminal Functions  A.5. Specifications  A.5.1 Absolute Maximum Ratings  A.5.2 DC Electrical Characteristics  A.5.3 Digital Characteristics | 133                             |

| A 1.2 GHZ \(\Sigma\) FRAC-N SYNTHESIZER DESIGN SPECIFICATIO  A.1. Introduction  A.2. Features  A.3. Block Diagram  A.4. Electrical Interface  A.4.1 Pin Assignments  A.4.2 Terminal Functions  A.5. Specifications  A.5.1 Absolute Maximum Ratings  A.5.2 DC Electrical Characteristics                                | 133                             |

| A           | A.7.1 General                                                 | 144 |

|-------------|---------------------------------------------------------------|-----|

| A           | A.7.2 Operational                                             | 144 |

| A           | A.7.3 Specifications                                          | 145 |

| <b>A.8</b>  | Pyramid Test Modes                                            | 145 |

| <b>A</b> .9 | Test Configurations                                           | 148 |

| <b>A</b> .1 | 0 Fractional Channel Number                                   | 153 |

| <b>A</b> .1 | 1Frequency Plan of Pyramid                                    | 155 |

| <b>A</b> .1 | 2Operating Modes of the Digital ΣΔ Modulator                  | 156 |

| LIST        | OF CONTRIBUTIONS                                              | 158 |

| 1.          | Articles published/accepted/submitted to refereed journals    | 158 |

| 2.          | Articles published/accepted/submitted to refereed conferences | 159 |

| 3.          | Non-refereed contributions                                    | 159 |

| RIRI        | JOGRAPHY                                                      | 161 |

|             |                                                               |     |

# **List of Figures**

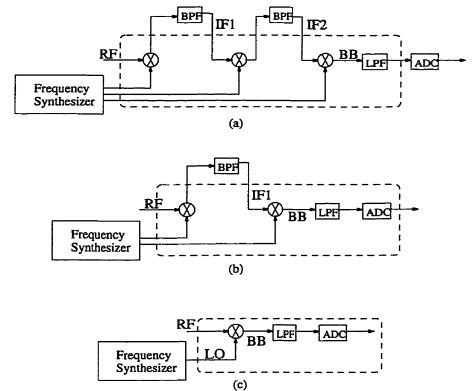

| Figure 2.1. | Wireless receiver architectures: (a) double IF, (b) single IF, and (c) di | irect |

|-------------|---------------------------------------------------------------------------|-------|

| conver      | rsion architecture                                                        | 8     |

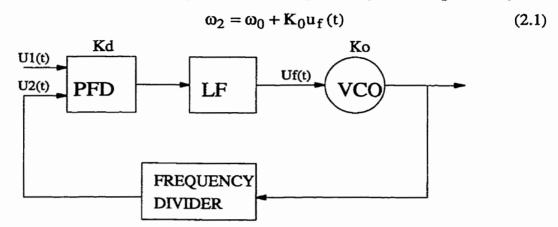

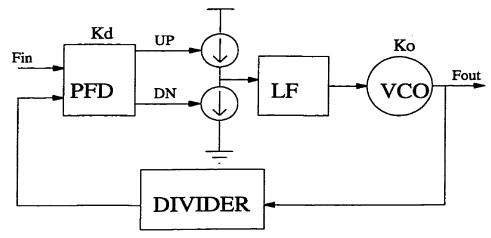

| Figure 2.2. | Classical PLL                                                             | 9     |

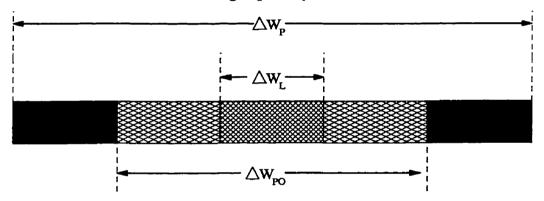

| Figure 2.3. | Relationship between various frequency ranges                             | 11    |

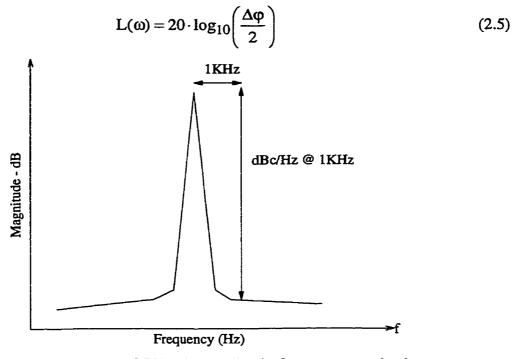

| Figure 2.4. | Measure of SSB phase noise in frequency synthesizers                      | 12    |

| Figure 2.5. | Charge pump based PLL                                                     | 13    |

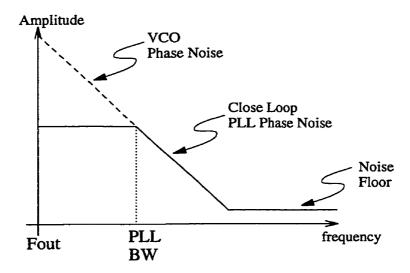

| Figure 2.6. | Phase noise in a closed loop PLL system                                   | 16    |

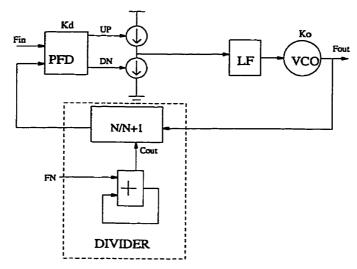

| Figure 2.7. | Fractional-N Phase-locked Loop                                            | 18    |

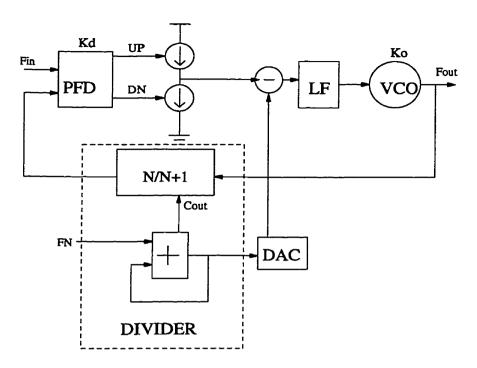

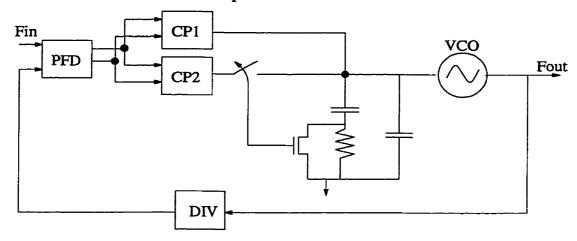

| Figure 2.8. | Analog compensated fractional-N PLL                                       | 19    |

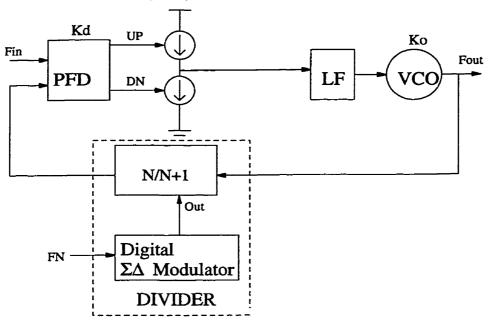

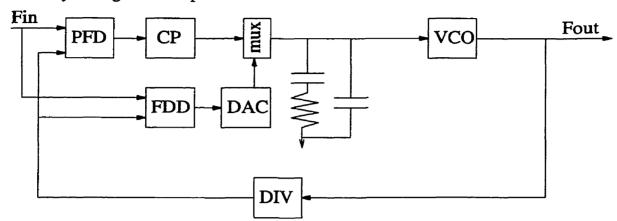

| Figure 2.9. | ΣΔ PLL Architecture                                                       | 20    |

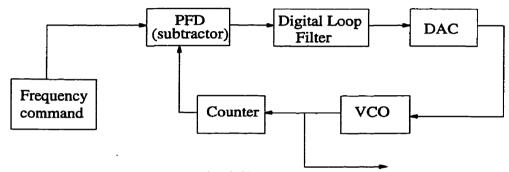

| Figure 2.10 | DSP PLL Architecture                                                      | 21    |

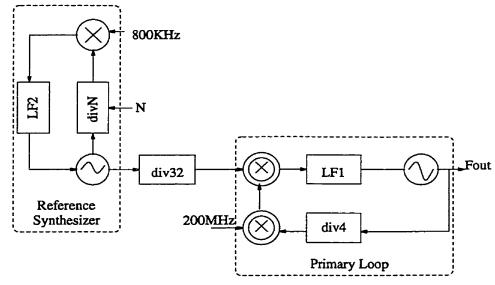

| Figure 2.11 | . Dual loop PLL architecture                                              | 22    |

| Figure 2.12 | Dual PLL architecture                                                     | 23    |

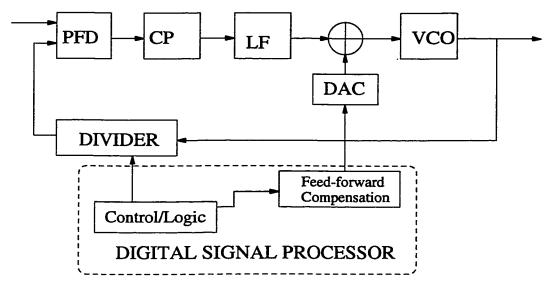

| Figure 2.13 | . Feedforward compensated PLL architecture                                | 24    |

| Figure 2.14 | . Two mode PLL architecture                                               | 25    |

| Figure 2.15 | . Fast lock PLL architecture employing FDD circuitry                      | 26    |

| Figure 3.1. | Model for uncompensated fractional-N PLL.                                 | 28    |

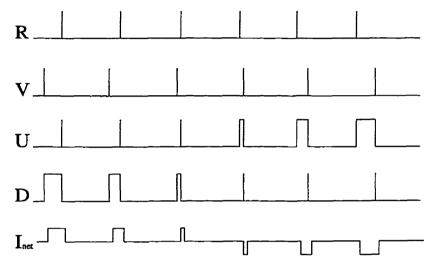

| Figure 3.2. | Ideal waveforms for uncompensated fractional-N PLL                        | 29    |

| Figure 3.3. | Waveforms for uncompensated fractional-N PLL with time shift              | 31    |

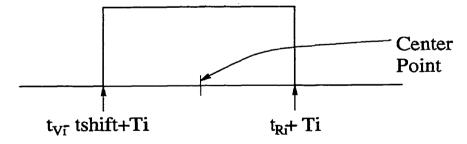

| Figure 3.4. | Ideal current pulse from charge pump                                      | 31    |

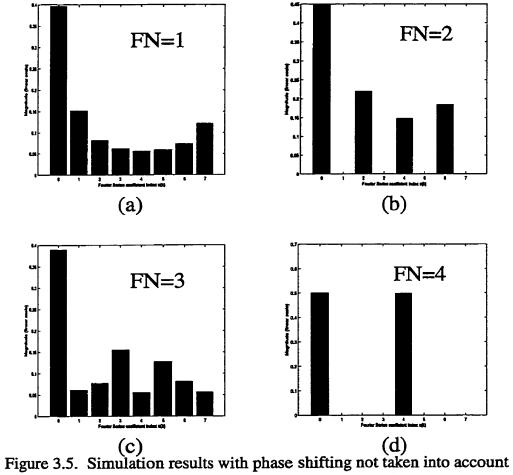

| Figure 3.5. | Simulation results with phase shifting not taken into account             | 33    |

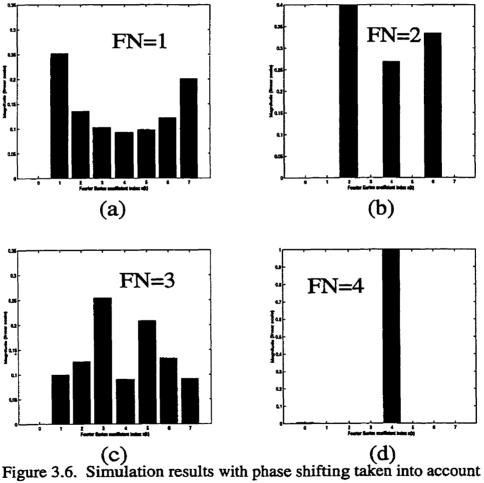

| Figure 3.6. | Simulation results with phase shifting taken into account                 | 34    |

| Figure 3.7. | Model for analog compensated fractional-N PLL                             | 35    |

|             | Waveforms for analog compensated fractional-N PLL                         |       |

| Figure 3.9. | Simulation results of the analog compensated Fractional-N PLL             | 38    |

| Figure 3.10. Typical locking behaviour of a charge pump based PLL40                       |

|-------------------------------------------------------------------------------------------|

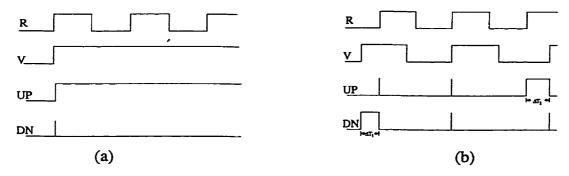

| Figure 3.11. Two cases during frequency lock (a) in phase signals and (b) out of phase    |

| signals41                                                                                 |

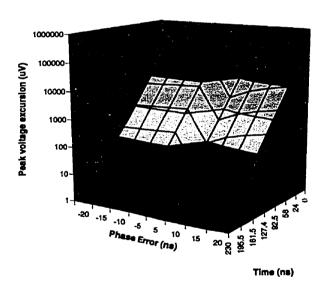

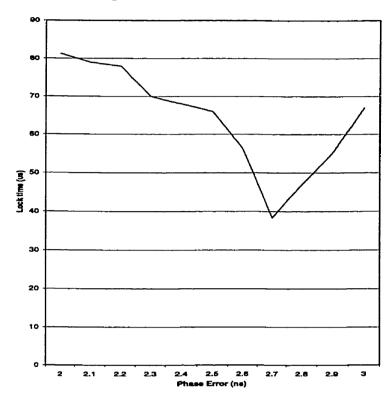

| Figure 3.12. Variation of lock time and peak voltage excursion with phase error 44        |

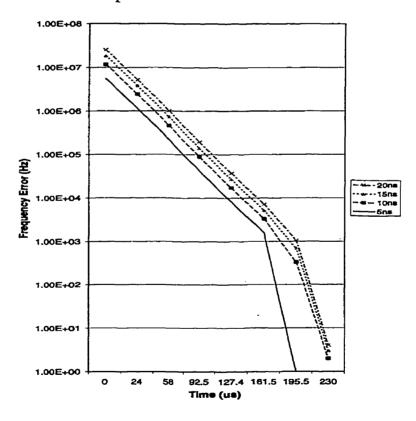

| Figure 3.13. Variation of frequency error with time for different phase error offsets 45  |

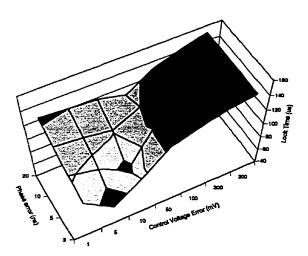

| Figure 3.14. Variation of lock time with phase error and initial frequency error46        |

| Figure 3.15. Variation of lock time with phase error for initial frequency error of       |

| 200KHz47                                                                                  |

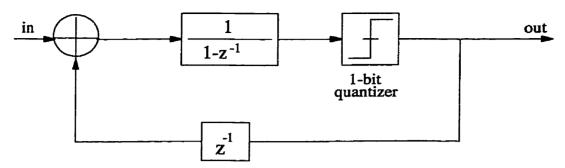

| Figure 4.1. Digital Sigma-Delta Modulator                                                 |

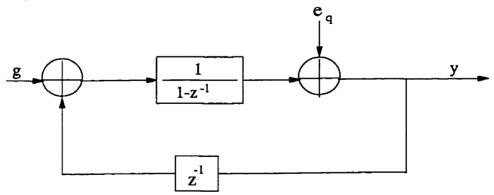

| Figure 4.2. First order ΣΔ modulator model                                                |

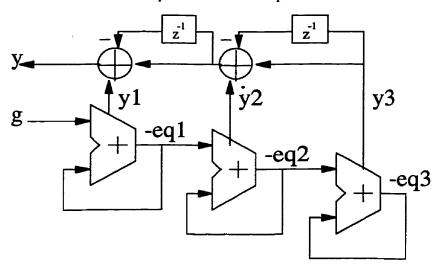

| Figure 4.3. Third order MASH ΣΔ digital modulator                                         |

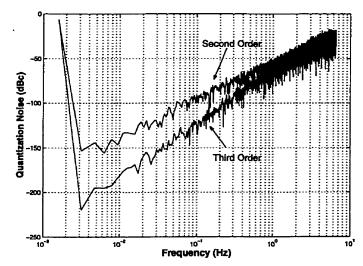

| Figure 4.4. Spectral densities of second and third order modulators53                     |

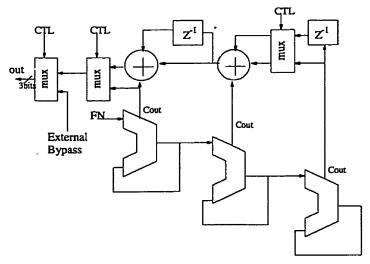

| Figure 4.5. A flexible 2 <sup>nd</sup> /3 <sup>rd</sup> Order MASH ΣΔ digital modulator54 |

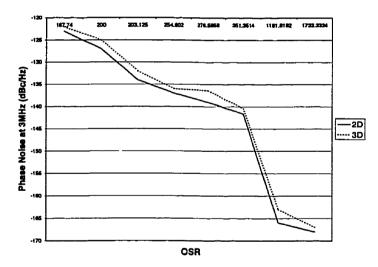

| Figure 4.6. Effect of OSR on quantization noise reduction                                 |

| Figure 4.7. Lock time simulation of ΣΔ PLL                                                |

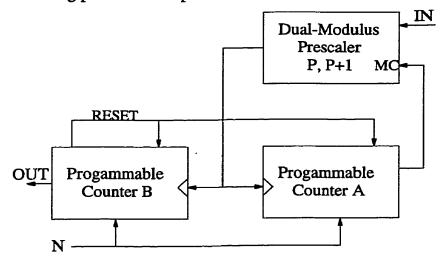

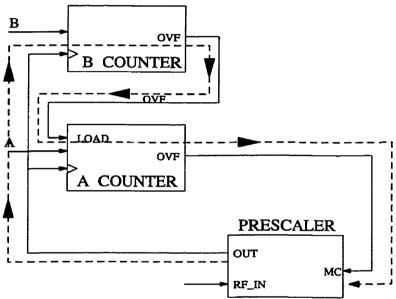

| Figure 4.8. Divider architecture used                                                     |

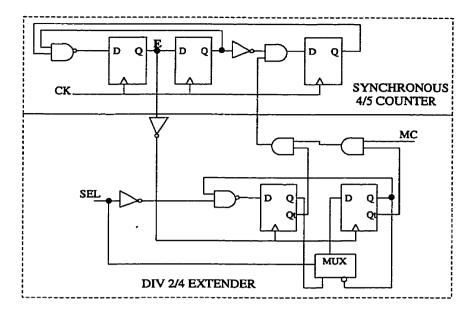

| Figure 4.9. Dual-modulus 8/9 and 16/17 prescaler59                                        |

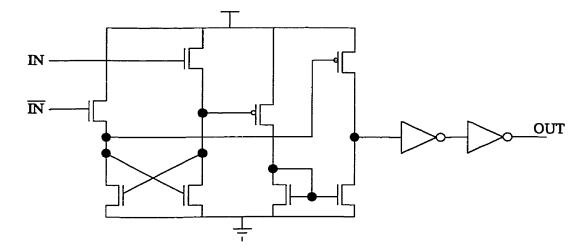

| Figure 4.10. Circuit schematic of level converter60                                       |

| Figure 4.11. Critical path delay in the divider61                                         |

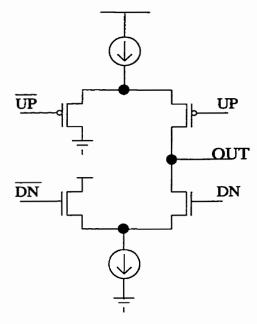

| Figure 4.12. Circuit schematic of charge pump62                                           |

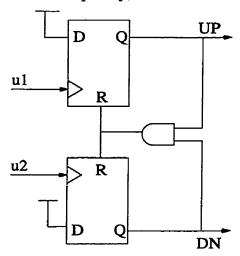

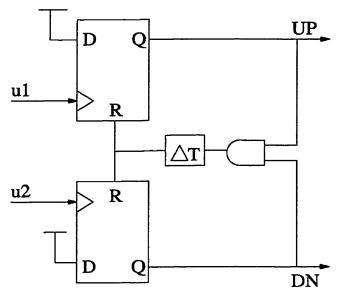

| Figure 4.13. Conceptual diagram of a PFD63                                                |

| Figure 4.14. PFD with a delayed reset signal                                              |

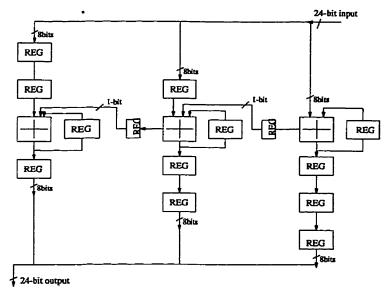

| Figure 4.15. Pipelined 24-bit accumulator65                                               |

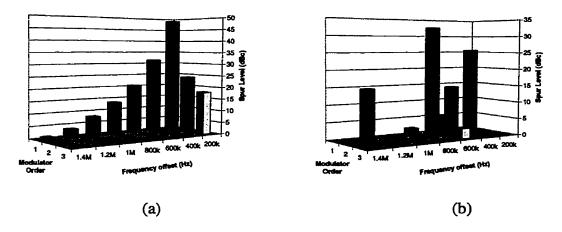

| Figure 4.16. Spurious performance for (a) 1/65 fractional channel and (b) 3/65            |

| fractional channel                                                                        |

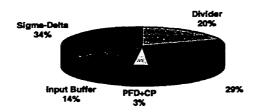

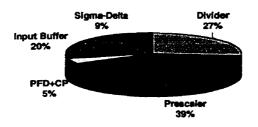

| Figure 4.17. Power breakdown of MASH $\Sigma\Delta$ PLL for $V_{DD,SD}$ =3.3 $V$          |

| Figure 4.18. Power breakdown of MASH $\Sigma\Delta$ PLL for $V_{DD,SD}=1.5V$              |

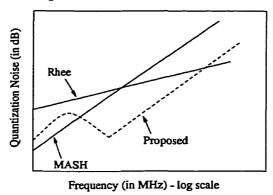

| Figure 5.1. Quantization noise shaping by different ΣΛ modulators                         |

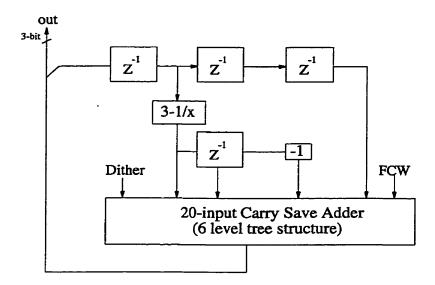

| Figure 5.2. High-level diagram of proposed $\Sigma\Delta$ modulator                   |

|---------------------------------------------------------------------------------------|

| Figure 5.3. ΣΔ modulator with optimized arithmetic structures                         |

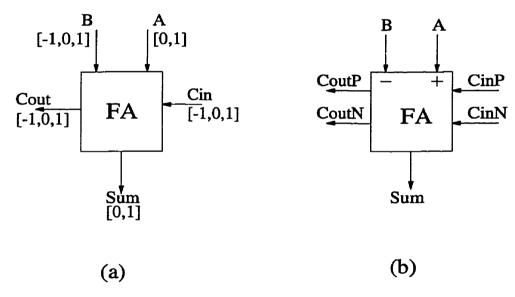

| Figure 5.4. Final Stage Full-adder (FA) cell. (a) input/output ranges and (b) block   |

| diagram of implemented circuit78                                                      |

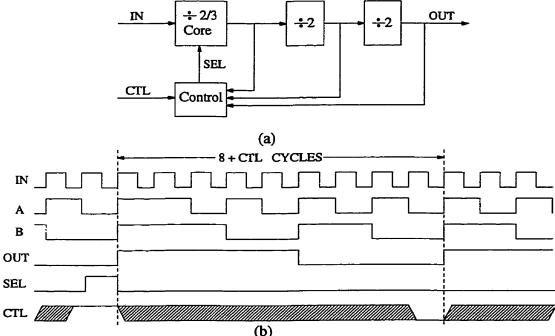

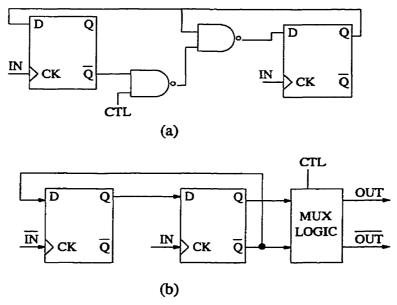

| Figure 5.5. (a) An 8/9 dual-modulus divider and (b) its timing waveform78             |

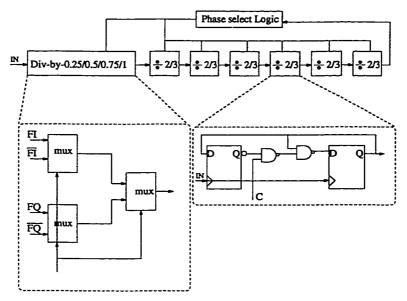

| Figure 5.6. A multi-modulus divider architecture                                      |

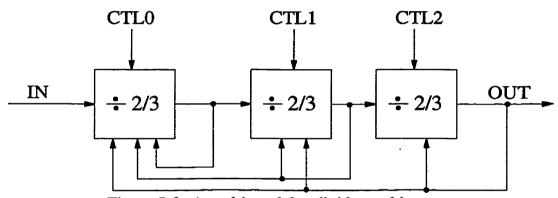

| Figure 5.7. A Johnson counter. (a) divide-by-2/3 using gating logic and (b) a divide  |

| by-2/3 using multiplexing80                                                           |

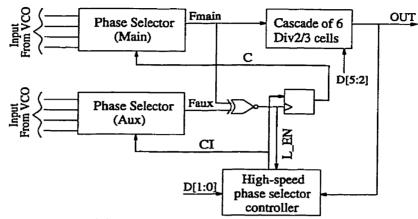

| Figure 5.8. Proposed fractional divider circuit                                       |

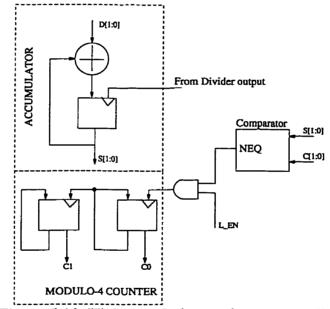

| Figure 5.9. Control logic for glitch free operation                                   |

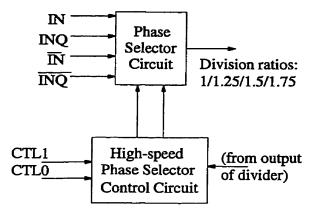

| Figure 5.10. High-speed phase selector controller                                     |

| Figure 5.11. Phase selection divider with quarter division ratios83                   |

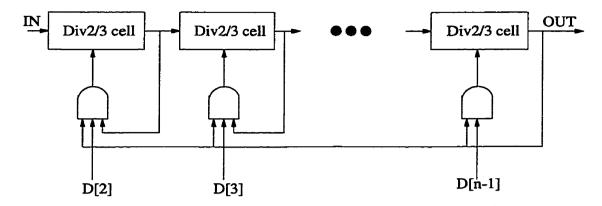

| Figure 5.12. Control logic for asynchronous divide-by-2/3 cells83                     |

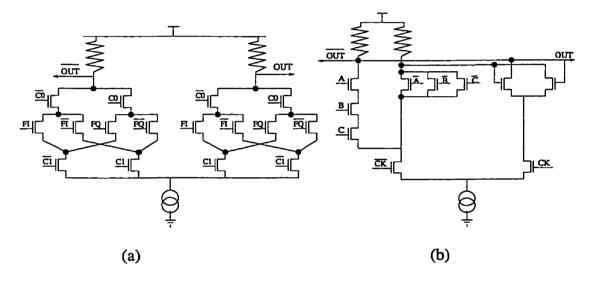

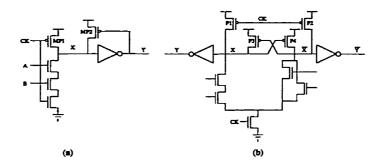

| Figure 5.13. Current mode logic cells for (a) phase selector and (b) merged 3-input   |

| AND/Latch gate82                                                                      |

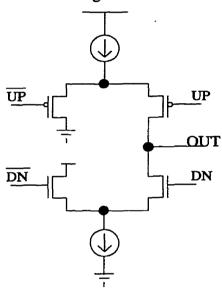

| Figure 5.14. Schematic diagram of charge pump current85                               |

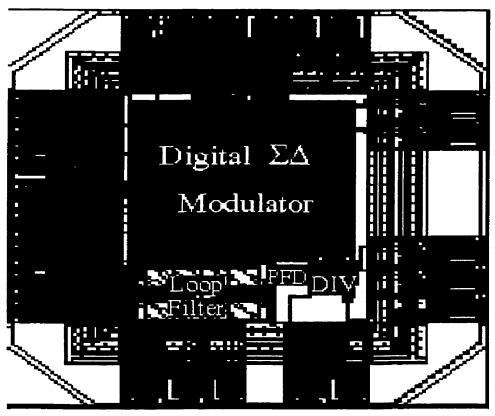

| Figure 5.15. Layout of ΣΔ PLL87                                                       |

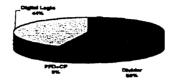

| Figure 5.16. Power consumption breakdown of the ΣΔ PLL                                |

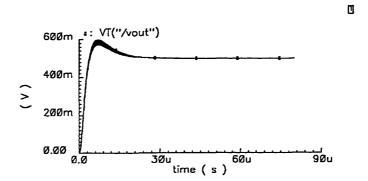

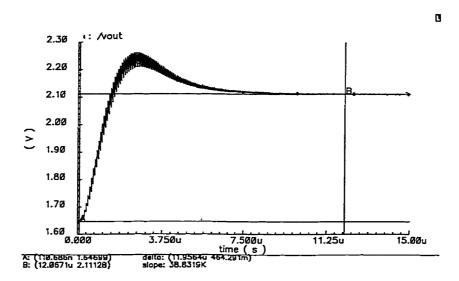

| Figure 5.17. Worst case lock time characteristics                                     |

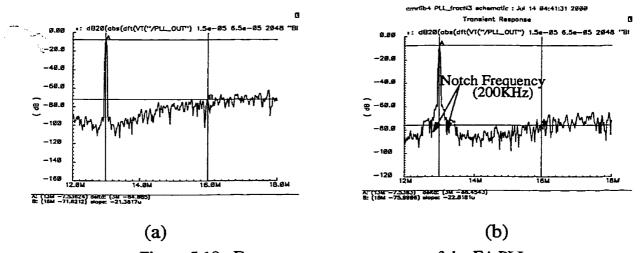

| Figure 5.18. Frequency spectrum output of the ΣΔ PLL                                  |

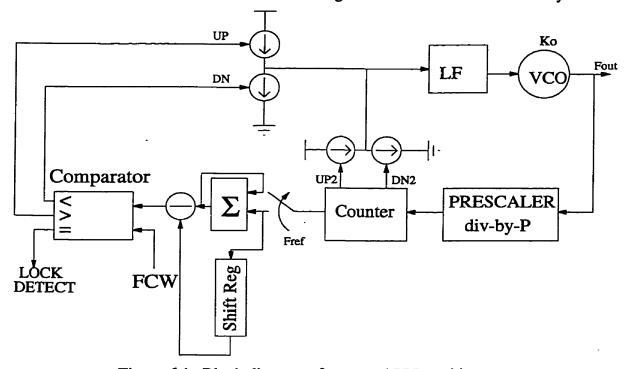

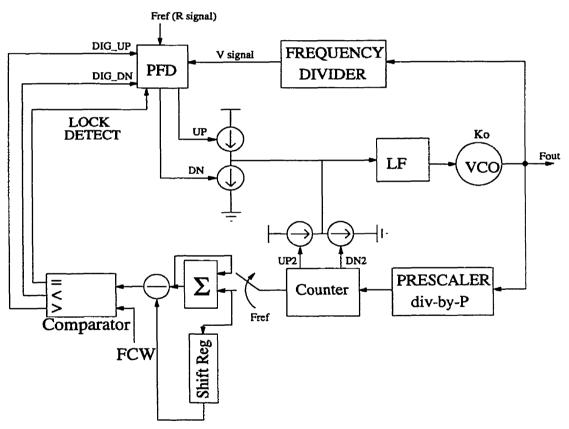

| Figure 6.1. Block diagram of proposed PLL architecture94                              |

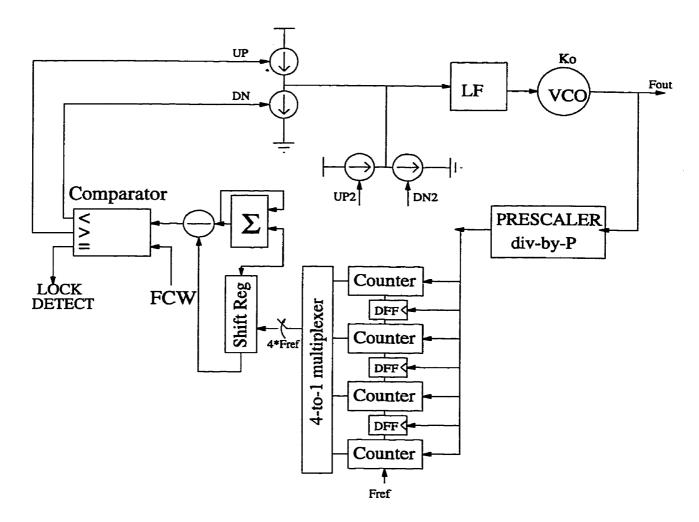

| Figure 6.2. Fast Lock Digital PLL with pipelined counters96                           |

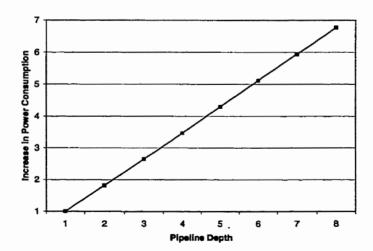

| Figure 6.3. PLL's relative power increase due to pipelining97                         |

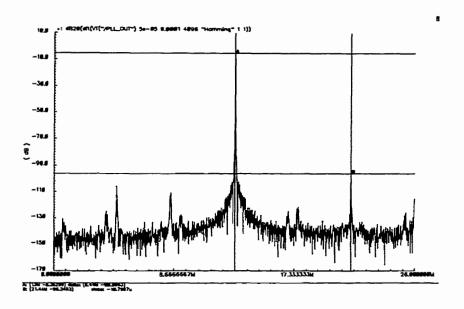

| Figure 6.4. Frequency spectrum of the digital PLL                                     |

| Figure 6.5. Proposed fast lock fine resolution PLL architecture103                    |

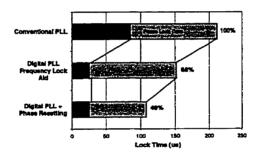

| Figure 6.6. Lock time speed-up using fast frequency and phase locking techniques. 104 |

| Figure 7.1. Dynamic Logic (a) single-ended, (b) differential108                       |

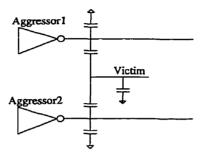

| Figure 7.2. Configuration for crosstalk model                                         |

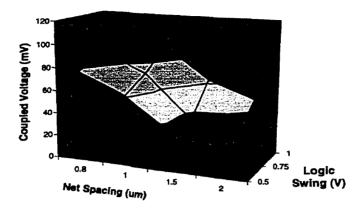

| Figure 7.3. Coupled voltage dependence on voltage swing and net spacing                    | 110    |

|--------------------------------------------------------------------------------------------|--------|

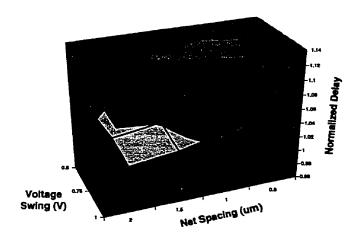

| Figure 7.4. Normalized delay dependence on voltage swing and net spacir                    | ıg of  |

| differential signals                                                                       | 111    |

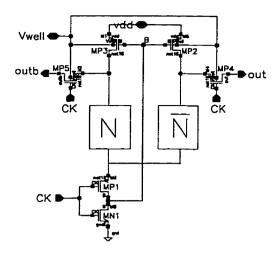

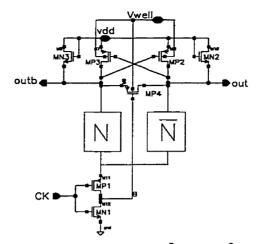

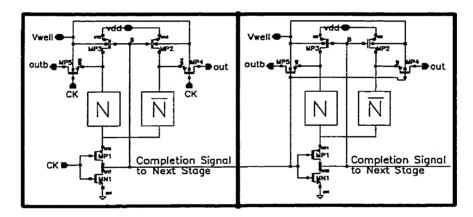

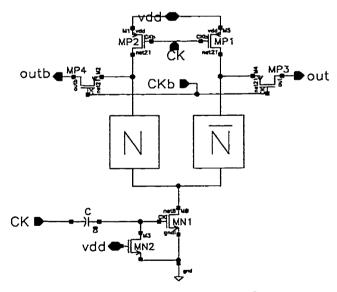

| Figure 7.5. Short-Circuit Current Logic (SC <sup>2</sup> L) Gate                           | 112    |

| Figure 7.6. Quasi-static SC <sup>2</sup> L (QSC <sup>2</sup> L) Gate                       | 113    |

| Figure 7.7. SC <sup>2</sup> L Asynchronous Pipelining Strategy                             | 113    |

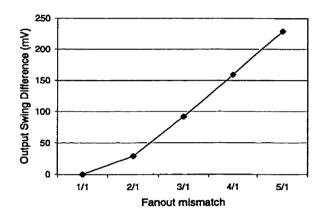

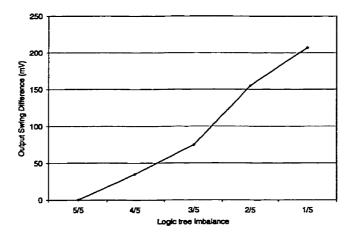

| Figure 7.8. Output voltage swing sensitivity to load mismatch                              | 114    |

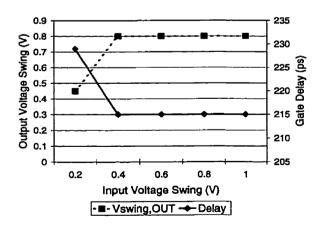

| Figure 7.9. Output voltage swing vs. input voltage swing                                   | 114    |

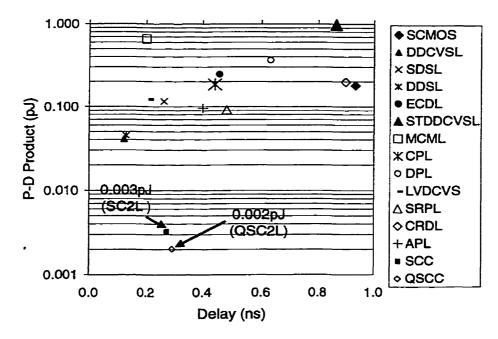

| Figure 7.10. Comparison of SC <sup>2</sup> L with other logic families [56]                | 116    |

| Figure 7.11. Chip micrograph of two SC <sup>2</sup> L carry ripple adders                  | 116    |

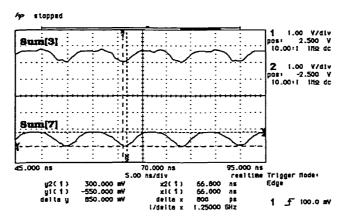

| Figure 7.12. Waveform output of test results from 8bit CRA (Sum[3] and Su                  | ım[7]  |

| output bits)                                                                               | 117    |

| Figure 7.13. Basic CPCL Gate                                                               | 118    |

| Figure 7.14. Output voltage swing sensitivity to load mismatch for CPCL logic              | 119    |

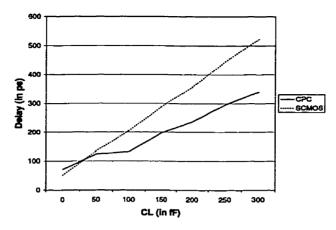

| Figure 7.15. Delay versus load capacitance for CPCL logic                                  | 119    |

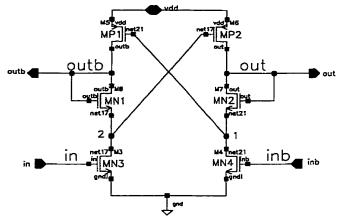

| Figure 7.16. A schematic of a LVDSL-1 inverter/buffer                                      | 120    |

| Figure 7.17. A Schematic of a LVDSL-2 inverter/buffer                                      | 121    |

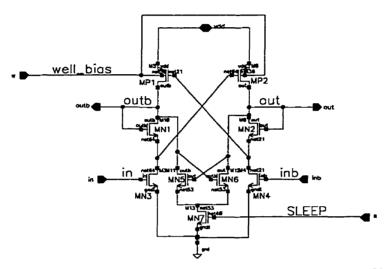

| Figure 7.18. Energy (power-delay product) of a LVDSL-1 inverter/buffer                     | 122    |

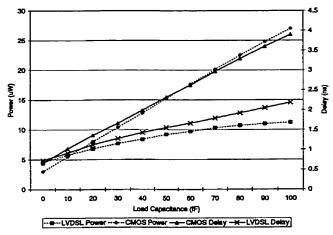

| Figure 7.19. Power and Delay of LVDSL-1 versus output capacitance                          | 123    |

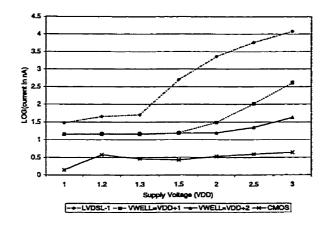

| Figure 7.20. Leakage current of LVDSL-1 inverter/buffer                                    | 123    |

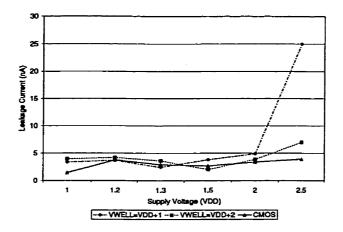

| Figure 7.21. Leakage current of LVDSL-2 inverter/buffer                                    | 124    |

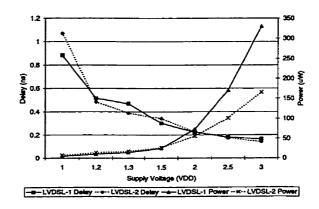

| Figure 7.22. Power and Delay of LVDSL-1 and LVDSL-2                                        | 124    |

| Figure 7.23. Full-adder differential logic tree                                            | 125    |

| Figure 7.24. D-type flip-flop implemented in (a) conventional CMOS and (b) LVI             | SL     |

|                                                                                            | 126    |

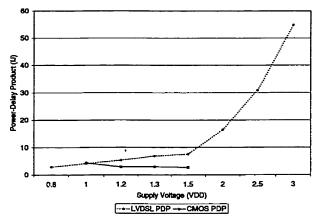

| Figure 7.25. Comparison of LVDSL and conventional CMOS for ΣΔ modulator                    | 127    |

| Figure 7.26. SC <sup>2</sup> L implementations of fast lock digital PLL for (a) IEEE 802.1 | 1, (b) |

| DECT handset, and (c) DECT base station                                                    | 128    |

| Figure A.1. | 24 Pin Chip Scale Packaging (top view) | 135 |

|-------------|----------------------------------------|-----|

| Figure A.2. | Digital Timing Specification           | 140 |

### **List of Tables**

| Table 2.1. Summary of 2G wireless communications standards [27]                              | 4       |

|----------------------------------------------------------------------------------------------|---------|

| Table 2.2. Spectral purity requirements of some 2 <sup>nd</sup> generation wireless standard | is7     |

| Table 3.1. Variation of time shift with fractional ratio                                     | 30      |

| Table 3.2. Effect of varying compensation pulse position on magnitudes                       | of F.S. |

| coefficients                                                                                 | 39      |

| Table 3.3. Effect of varying the compensation pulse width on magnitude                       | of F.S. |

| coefficients                                                                                 | 39      |

| Table 3.4. PLL parameters used for phase lock characterization                               |         |

| Table 4.1. Loop Filter component values                                                      | 56      |

| Table 4.2. Truth Table for division ratio for the prescaler                                  | 59      |

| Table 4.3. Frequency plan of the MASH $\Sigma\Delta$ PLL                                     | 59      |

| Table 4.4. Valid phase-frequency detector states                                             | 63      |

| Table 5.1. Effect of coefficient bit truncation on frequency accuracy                        | 75      |

| Table 5.2. Binary representations of carry signals                                           | 77      |

| Table 5.3. Loop parameters used for the proposed $\Sigma\Delta$ PLL                          | 85      |

| Table 5.4. Comparison of this work with other ΣΔ PLLs                                        | 90      |

| Table 6.1. Models for the digital portions of the PLL                                        | 96      |

| Table 6.2. Specifications of 802.11 wireless LAN                                             | 98      |

| Table 6.3. PLL parameters for the IEEE 802.11 wireless LAN standard                          | 99      |

| Table 6.4. Specifications of DECT cordless standard                                          |         |

| Table 6.5. PLL parameters for the DECT cordless standard                                     | 101     |

| Table 6.6. Specifications of GSM wireless standard                                           |         |

| Table 6.7. PLL parameters for the GSM wireless standard                                      | 101     |

| Table 6.8. Comparison of this work with other fast lock PLLs                                 |         |

| Table 7.1. Results of FA implementation in SC <sup>2</sup> L and QSC <sup>2</sup> L          |         |

| Table 7.2. Simulated & measured results of FA SC <sup>2</sup> L          | 117 |

|--------------------------------------------------------------------------|-----|

| Table 7.3. Full-adder Performance at $V_{DD}$ =1.2V Normalized to LVDSL2 | 125 |

| Table A.1. Chip pin list                                                 | 135 |

| Table A.2. Absolute Maximum Ratings                                      | 136 |

| Table A.3. Recommended DC Operating Conditions                           | 136 |

| Table A.4. DC Current Characteristics                                    | 136 |

| Table A.5. Reference Channel Characteristics                             | 137 |

| Table A.6. Reference Clock Buffered Output Description                   | 137 |

| Table A.7. Clock, data, and strobe signal level specifications           | 139 |

| Table A.8. Digital Timing specification                                  | 139 |

| Table A.9. Charage pump current ratio settings                           | 143 |

| Table A.10. PYRAMID Test Modes Table                                     | 145 |

| Table A.11 Operating modes of the Digital Sigma-Delta Modulator (DSDM)   | 156 |

| Table A.12. Output Range of the DSDM                                     | 157 |

| Table A.13. Binary Coding Scheme used in DSDM                            | 157 |

### Chapter 1

### Introduction

The past few years have seen an explosive growth in the wireless telecommunications market. Signs of this explosive growth are everywhere. It is estimated that approximately 20,000 people join the cellular phone market daily in the United States alone. It is now estimated that more that half of homes in the United States now have cordless phones. More than 280 million people currently subscribe to cellular phones. Just ten years ago, there were only 2 million subscribers. Currently, the wireless communications industry generates \$100 billion in revenue (in the year 2000). This revenue does not only come from cellular phones. It is estimated that 30% of the computer market revenue comes from portable computers (laptops and notebooks). These computers would require wireless access. Furthermore, dedicated e-mail wireless terminals are now available on the market. It is estimated that 10 million people are expected to use wireless networks to transmit data by the end of the year

2000.

The dream that anyone can communicate with anyone else "anytime, anywhere" and exchange "any kind" of information appears to be around the corner. Today, voice, data, and video can be transmitted over the wireless channel from one portable unit to another. The key to the success of the wireless market is affordability due to advances in semiconductor technology. As transistor dimensions shrink in size, more components are moved from the board to the chip. This not only helps to drastically reduce cost and area, but also helps in removing power consuming chip-to-chip communications. The present goal is to reduce both power consumption and the price of cellular phones by 30% each year. This cannot be achieved by relying on semiconductor technology alone. Circuit and architectural techniques must be investigated.

One pivotal block used in the wireless radio terminal is the frequency synthesizer. The frequency synthesizer is responsible for generating the carrier frequencies for both the transmitter and receiver. A wireless radio may have a shared frequency synthesizer for both transmit and receive, or two dedicated frequency synthesizers. The performance of the frequency synthesizer directly affects the performance of transceiver. The receiver sensitivity relies on how accurately the frequency synthesizer produces its output frequency.

The amount of time required for the synthesizer to generate a certain reference frequency (called lock time) also affects performance and power consumption. In many wireless standards, time division multiple access (TDMA) is used. In such standards, each user is given a time slice to transmit the data. After this time slice, the frequency synthesizer (of the base station) must tune to the transmission frequency of another user. If the frequency synthesizer lock time is reduced, the bandwidth allocated to each user can be increased. The frequency synthesizer is also the most active component in the wireless radio. Since the radio must periodically check for any incoming data, the synthesizer must be turned on for that amount of time. The

transceiver must also be on while the synthesizer is locking to the desired channel. In this time period, the transceiver is wasting power waiting for the synthesizer to lock.

Integrating the entire frequency synthesizer on a single chip is a challenging task. This is related to the stringent performance requirements put on the synthesizer. On-chip passive components used in the frequency synthesizer usually have much less quality than discrete components. Also, interference from one of the frequency synthesizer's components on another may cause performance degradation. This leads to extra board space, which entails higher cost, size, and power dissipation.

One approach to integrate the entire frequency synthesizer on a single chip is to use a specialized technology. This is regarded as an expensive solution and has not received widespread industrial acceptance. An alternative solution is to use a cheap technology, such as CMOS, and try to achieve integration through architectural innovations. This technique requires the redesign of the frequency synthesizer architecture to suit the current capabilities of the technology. Frequency synthesizers for wireless communications are usually implemented as phase locked loops (PLL). A PLL has both digital and analog components. In this study, digital solutions for improving the performance, integration, and lock time of PLLs are examined. In chapter 2, the basic operation of the PLL as well as a survey of current fast lock PLL architectures are given. In chapter 3, analytical solutions illustrating the performance of the most commonly used PLL architectures are given. In chapter 4, an implementation of a MASH sigma-delta PLL is given. This architecture attempts to provide a digital solution to eliminating the spurious noise produced by PLLs. It also offers high frequency resolution. In chapter 5, a novel wideband PLL architecture based on sigma-delta modulation is given. It is demonstrated that this architecture can also be used for closed loop modulation to directly transfer digital baseband data to radio frequency signals. In chapter 6, a new low-power fast lock PLL architecture is given. It is demonstrated that lock times much less than current PLL architectures may be achieved, while still meeting the performance requirements of wireless systems. Furthermore, it is demonstrated that the loop filter components in this architecture can be easily integrated on-chip. Finally, in chapter 7, digital logic families are detailed which may be used to further reduce the power consumption of the digital sections of the PLLs implemented. Such reductions may help to integrate both digital and analog components of the transceiver onto a single chip.

### **Chapter 2**

### **Background**

# 2.1 Frequency Synthesizer Requirements in Wireless Systems

Perhaps the most critical component in a wireless transceiver is the frequency synthesizer. The frequency synthesizer is used to generate an accurate local oscillator (LO) output frequency. The main frequency synthesizer parameters include frequency range, frequency resolution, switching speed, spurious output, phase noise, and power consumption. These parameters are specified by the specific standard being implemented. Table 2.1 summarizes some of the 2<sup>nd</sup> generation wireless communications standards that are currently used [27].

|                     | IS-95              | IS-54 /<br>IS-136  | GSM                | GPRS               | DCS-1800               | CT2             | DECT              | IEEE<br>802.11    |

|---------------------|--------------------|--------------------|--------------------|--------------------|------------------------|-----------------|-------------------|-------------------|

| F in MHz<br>(Rx/Tx) | 869-894<br>824-849 | 869-894<br>824-849 | 925-960<br>880-915 | 925-960<br>880-915 | 1805-1880<br>1710-1785 | 864/868         | 1880-<br>1900     | 2400-<br>2483     |

| Access<br>Method    | CDMA/<br>FDM       | TDMA/<br>FDM       | TDMA/<br>FDM       | Packet             | TDMA/<br>FDM           | TDMA/<br>FDM    | TDMA/F<br>DM      | CSMA              |

| Duplex<br>Method    | FDD                | FDD                | FDD                | FDD                | FDD                    | TDD             | TDD               | TDD               |

| # chan.             | 798                | 832                | 124                | 374                | 1600                   | 40              | 10                | FHSS:79<br>DSSS:7 |

| Chan.<br>spacing    | 1250<br>KHz        | 30KHz              | 200KHz             | 200KHz             | 200KHz                 | 100KHz          | 1.728<br>MHz      | FHSS:1<br>DSSS:11 |

| Modulati<br>on      | QPSK/<br>OQPSK     | π/4-<br>DQPSK      | GMSK<br>(0.3 GF)   | GSMK<br>(0.3 GF)   | GMSK<br>(0.3 GF)       | GFSK<br>(0.5GF) | GFSK<br>0.5GF     | GFSK,<br>DQPSK    |

| FS switching time   | Slow               | Slow               | 577us              | 200us              | 577us                  | 1ms             | 30usBS<br>450usHS | 300us             |

| Freq.<br>Accuracy   |                    | 200Hz<br>(0.2ppm)  | 50Hz<br>(0.1ppm)   | 50Hz<br>(0.1ppm)   | 100Hz<br>(0.1ppm)      | 10KHz<br>10ppm  | 50KHz<br>25ppm    | 75KHz<br>30ppm    |

Table 2.1. Summary of 2G wireless communications standards [27]

As shown in Table 2.1, all frequency standards demand switching speeds of at most one millisecond and frequency accuracies less than 30ppm. Note that all the cellular standards require the most frequency accuracy of less than 0.2ppm. Also note that the GSM (Global System for Mobile Communications) standard is the most widely used digital standard worldwide and it demands the most from frequency synthesizers. Both the frequency accuracy and switching speed of GSM are very aggressive.

In an effort to extend the use of wireless transmission from merely voice, new third generation standards are beginning to emerge. The objective of 3<sup>rd</sup> generation wireless standards can be summarized as:

- Full coverage and mobility for 144Kbps, preferable 384Kbps;

- Limited coverage and mobility for 2Mbps;

- High spectrum efficiency compared to existing systems;

- High flexibility to introduce new services.

The bit rates of 384Kbps and 2Mbps were set in order to meet current video transmission standards of H.263 [28] and MPEG-2 [29], respectively. There are two 3<sup>rd</sup>

generation standards that have emerged. One is called wideband CDMA [30] (or WCDMA). WCDMA standard has received wide acceptance in Europe, Japan, and North America. This standard was made backwards compatible with the GSM standard. Another version of WCDMA, called cdma2000 [31], was created to be backward compatible with the IS-95 standard.

Wideband CDMA has a nominal bandwidth of 5MHz. This has been done in order to incorporate data rates of 144Kbps, 384Kbps, and 2Mbps. In order to be compatible with GSM, different grades of data transmission have been created. The lowest grade being a 200KHz channel (which is the same as the GSM). Higher data rates can be achieved by combining several GSM channels.

Current TDMA-based technologies [32] (GSM, IS-136, IS-54) use a single voice channel for data per user, which delivers data at a rate of 9.6Kbps and 14.4Kbps. Today, new standards enabling high-speed wireless data transmission are emerging. These standards, which exhibit some features of 3<sup>rd</sup> generation standards, are extensions of current 2<sup>nd</sup> generation standards. Such standards are referred to as 2.5 generation or 2+ generation standards. The two most popular are the GPRS [33] (general-packet-radio service) and HSCSD [33] (high-speed circuit switched data) standards. HSCSD is a circuit switched data transmission that can offer as much as 76.8Kbps. This is done by dedicating more than one channel to a user. Circuit switched data transmission entails that a dedicated connection must be established and this connection cannot be broken until all transmission is complete. GPRS, on the other hand, is a packet switched data transmission that can offer data rates over 100Kbps. In packet switched transmission, a physical connection only exists during the transmission burst. This means that the channel is used more efficiently. This also means that in GPRS, users could be "virtually" connected for hours at a time and only incur connection charges during transmission bursts. GPRS is expected to be the main enabling technology for high-speed wireless internet access in the near future.

As shown in Table 2.1, GPRS requires fast switching from one channel to another. This is due to the fact that GPRS uses a combination of TDMA and FDMA. In this type of wireless transmission, each user is reserved a certain time slice (called a frame) to transmit the data. When the frame transmission is over, the next user transmits his own frame, which can be transmitted at a different frequency. In this case, a certain time period must be allocated for the frequency synthesizer to complete switching from one frequency to another. If less time is allocated for this frequency switching, more time can be allocated for data transmission, and hence data transmission rates can be increased. In the GPRS standard, the frequency synthesizer is given less than 200µs to switch from one frequency to another. Frequency synthesizer switching time is expected to be constrained even further as data rates increase.

Another important requirement in wireless standards that directly affect frequency synthesizers is spectral purity. Table 2.2 shows the spectral purity requirements of some of the 2<sup>nd</sup> generation wireless standards. The spectral purity requirements depend on several parameters, which include the data signal's dynamic range, channel spacing, and the modulation technique.

Table 2.2. Spectral purity requirements of some 2<sup>nd</sup> generation wireless standards

| Standard | Phase noise requirement |

|----------|-------------------------|

| GSM      | -141dBc/Hz @ 3MHz       |

| DECT     | -131dBc/Hz @ 4.7MHz     |

| PHS      | -96dBc/Hz @ 100KHz      |

| DCS-1800 | -123dBc/Hz @ 600KHz     |

| PDC      | -120dBc/Hz @ 50KHz      |

### 2.2 Wireless Transceiver Architectures

There are three main types of wireless receiver architectures, as shown in Fig. 2.1(a)-(c). The first one is the double-IF receive architecture in such an architecture, the input RF frequency is down mixed to two intermediate frequencies (IF) before it is converted to a baseband signal. Although this yields high spectral purity, this architecture

requires the most off-chip components. It also has the most demand from the frequency synthesizer, since three different frequencies must be generated. Another architecture, single-IF receiver, attempts to reduce the number of off-chip SAW filters by reducing the number of intermediate frequencies to one. The third architecture, the direct conversion architecture, no intermediate frequencies are used, which means that no SAW filters are used. This is the most suitable architecture for full integration, and it has the least demand from the frequency synthesizer.

Figure 2.1. Wireless receiver architectures: (a) double IF, (b) single IF, and (c) direct conversion architecture

### 2.3 Classical Phase-Locked Loop

#### 2.3.1 Basic Operation

The Phase-Locked Loop (PLL) is the most commonly used form of frequency

synthesizer used in wireless systems. The classical PLL consists of a voltage-controlled oscillator (VCO), a frequency divider, a phase frequency detector (PFD), and a loop filter (LF) as shown in Fig. 2.2. Now the operation of each component is described. The VCO produces a frequency proportional to its input voltage. More specifically,

Figure 2.2. Classical PLL

where  $\omega_0$  is the free oscillation frequency (frequency at which the VCO oscillates at when no input frequency is applied) measured in rad/s, and  $K_0$  is the VCO gain (measured in s<sup>-1</sup>V<sup>-1</sup>). The PFD compares the input signal,  $u_1(t)$ , and the feedback signal,  $u_2(t)$ , and produces an output which is proportional to the phase difference between the two signals. In terms of a mathematical description, the operation of the PFD may be expressed as

$$\mathbf{u_d}(\mathbf{t}) = \mathbf{K_d}\mathbf{\theta_e} \tag{2.2}$$

where  $K_d$  is the gain of the PFD and  $\theta_e$  is the difference in phase between  $u_1(t)$  and  $u_2(t)$  (measured in rads). The units of  $K_d$  is  $V \cdot rad^{-1}$ . The purpose of the loop filter is to control the bandwidth of the closed loop system. The loop bandwidth, in turn, controls the settling time, or lock-in time of the PLL. The loop filter, in most cases, is a second or third order low-pass filter. The frequency divider allows the input frequency to be lower than the output frequency by a factor of N. Note that if the value of N is

variable, then the PLL-based frequency synthesizer can be used to synthesize different frequencies.

The operation of the PLL is actually quite simple. If the input signal's phase is lagging behind the phase produced by the VCO, this means that the VCO frequency is too high and hence must be lowered. The phase detector handles this by producing an inhibiting signal to the loop filter, which in turn lowers the voltage input to the VCO,  $u_f(t)$ . As can be shown by Equation (2.1), lowering  $u_f(t)$  amounts to lowering  $\omega_2(t)$ , the output frequency of the VCO, which is what is desired. On the other hand, if the input signal's phase is leading that of the VCO, the PFD produces an excitatory signal to the loop filter, which increases the output voltage of the loop filter, and in turn, increases the output frequency of the VCO, as desired.

Frequency accuracy is ensured by the (1/s) term in the VCO, which acts as an integrator. Typically, another pole is contributed by the loop filter in order to ensure that the phase is also equalized to the input reference signal. This configuration would ensure both frequency and phase stability of the PLL's output.

#### 2.3.2 PLL Performance Measures

There are several figures of merit which objectively determine the PLL's performance. These figures of merit may be broken down into three categories[1]. One category of such figures describe the *acquisition characteristics* of the PLL. The four acquisition characteristics measures are:

- Pull-in range  $\Delta\omega_P$ : This is the maximum frequency deviation range which the PLL can tolerate without becoming unstable. If the frequency change in the input is smaller than this, then the PLL will eventually relock into the new frequency.

- Pull-in time T<sub>P</sub>: Time required for the pull-in process.

- Lock range  $\Delta\omega_L$ : This is the maximum frequency step that can be applied to the input of the PLL while still maintaining lock to within a single beat note (phase

difference of  $2\pi$ ) between the reference frequency and the output frequency.

• Lock-in time T<sub>L</sub>: Time required for the lock-in process.

Another category of performance measure determines the *tracking capability* of the PLL. The only performance measure belonging to this category, which is considered in this study, is:

• Pull-out range  $\Delta\omega_{PO}$ : This is the maximum frequency step that can be applied to the input of the PLL while still having the PLL to re-lock quickly. If the frequency step is greater than this quantity but less than the pull-in range, relocking will be a slow process.

Fig. 2.3 shows the relationship between the different frequency ranges of the acquisition characteristics and tracking capability characteristics of the PLLs.

Figure 2.3. Relationship between various frequency ranges

The third category is sometimes referred to in some texts [1,2] as the *noise immunity*, or the *noise rejection capability*, of the PLL. The total RMS phase error in a wireless transceiver can be contributed from several factors. The frequency synthesizer is one of them. When designing a PLL frequency synthesizer for wireless applications, the RMS phase error contribution of the frequency synthesizer should be no more than 2 degrees [33]. The PLL's RMS phase error, is also referred to as close-in phase noise, which is the phase noise within the closed loop bandwidth of the PLL. It should be noted that the close-in phase noise determines the bit error rate (BER) of the entire

system. The larger the bandwidth, the more phase noise is integrated. Noise within the closed loop bandwidth of the PLL can cause modulation on the VCO control voltage, which in turn causes phase excursions at the VCO's output. The peak excursion  $\Delta \phi$  can be described as

$$s_{VCO}(t) = A \cdot \cos(\omega_c t + \Delta \phi \sin \omega_m t)$$

$$= A \left[ \cos \omega_c t \cdot \cos(\Delta \phi \sin \omega_m t) - \sin \omega_c t \sin(\Delta \phi \sin \omega_m t) \right]$$

(2.3)

If  $\Delta \phi$  is small (which is the case for 2 degrees), then Equation 2.3 simplifies to

$$s_{VCO}(t) = A \left\{ \cos \omega_c t - \frac{\Delta \phi}{2} [\cos(\omega_c + \omega_m)t - \cos(\omega_c - \omega_m)t] \right\}$$

(2.4)

This equation shows that the noise spectrum is a sum of a large number of offset frequencies around the carrier due to phase modulation of the VCO. The level of noise sidebands on each side of the carrier is

Figure 2.4. Measure of SSB phase noise in frequency synthesizers

Integrating over the frequency range of interest (closed loop PLL bandwidth, BW) gives the final equation for the close-in phase noise as

$$\phi_{PLLRMS} = \sqrt{\int 2 \cdot L(\omega) d\omega}$$

(2.6)

Single sideband (SSB) phase noise outside the loop bandwidth is also important. It is defined as the distance (in dB) from the amplitude of the center frequency to the amplitude of the sidelobe at a specified frequency distance (as shown in Fig. 2.4). The unit of measure is dBc/Hz @ carrier offset frequency (in Hz).

It is important to note that phase noise is related to the noise of the semiconductor devices being used[73,74]. For metal oxide semiconductor (MOS) devices, the two main contributors of noise are flicker (or 1/f) noise and thermal noise. When implementing a VCO in MOS technology, the transfer function of the VCO becomes  $H(s)=s^{-2}$ , and the flicker noise is translated to  $f^3$  noise. Thermal noise is a form of amplitude noise. When applied to VCOs, the thermal noise modifies the zero crossings of the output of the VCO. This random modification of the zero crossings results in phase errors, or phase noise.

#### 2.3.3 Charge-pump PLL

In order to have an infinite capture range, an active filter must be used for the loop filter. Unfortunately, this is not a suitable structure for wireless applications since an active loop filter introduces a significant amount of noise (since active components are on whenever the PLL is turned on). Alternatively, wireless systems usually employ a charge-pump based PLL [37]. Fig. 2.5 shows a block level diagram of a charge-pump based PLL. The reasons for their popularity include extended lock range and low cost [37]. As its name implies, a charge pump is responsible for injecting a fixed amount of current to the loop filter. The charge pump is controlled by the PFD. If UP=1, then current is injected into the loop filter, and hence the voltage across the loop filter is increased. If DN=1, on the other hand, an equal amount of current is drawn out of the

loop filter, and thereby decreasing the voltage across the loop filter. Note that during locked condition the current sources of the charge pumps are on for a small fraction of the time, as opposed to being on all the time as in PLLs utilizing active filters. It is for this reason that charge pumps exhibit less in-band noise and are preferred when implementing PLLs fore wireless systems. Unless otherwise stated, all PLLs from this point forward are assumed to employ charge pumps.

Figure 2.5. Charge pump based PLL

### 2.3.4 Closed Loop PLL Analysis

For the classical PLL, shown in Fig. 2.6, it is instructive to obtain the various transfer functions of the PLL. Assuming that the closed loop bandwidth of the PLL is less than the reference frequency by at least an order of magnitude, the PLL may be thought of as a linear device. The transfer functions are given as

$$H_1(s) = \frac{K_d K_o F(s)}{s + K_d K_o F(s)/N}$$

from input to VCO output (2.7)

$$H_2(s) = \frac{sK_dF(s)}{s + K_dK_oF(s)/N}$$

from input to LF output (2.8)

$$H_3(s) = \frac{sK_d}{s + K_d K_o F(s)/N}$$

from input to PFD output (2.9)

$$H_4(s) = \frac{K_0 F(s)}{s + K_d K_0 F(s)/N}$$

from PFD to VCO output (2.10)

$$H_5(s) = \frac{K_o}{s + K_d K_o F(s)/N} \quad \text{from LF to VCO output}$$

(2.11)

These equations may be used to evaluate the effect of injecting noise at different points in the PLL on the output response of the PLL.

Equation (2.7) is the basic PLL transfer function. Assuming a charge pump PLL with a first order loop filter,  $H_I(s)$  may be rewritten as:

$$H_1(s) = \frac{\frac{I_p}{2\pi} K_o (R + \frac{1}{sC})}{s + \frac{I_p}{2\pi} K_o (R + \frac{1}{sC})/N}$$

(2.12)

Equation (2.12) is a second order system. The natural frequency and damping factor are then given as

$$\omega_{\rm n} = \sqrt{\frac{K_{\rm o}I_{\rm p}}{2\pi NC}} \tag{2.13}$$

$$\zeta = \frac{\omega_{\rm n} RC}{2} \tag{2.14}$$

The 3-dB bandwidth of the 2<sup>nd</sup> order PLL is given as

$$\omega_{3dB} = \frac{\omega_n}{2\pi} \sqrt{2\zeta^2 + 1 + \sqrt{(2\zeta^2 + 1)^2 + 1}} \text{ Hz}$$

(2.15)

Since the loop filter introduces one pole and the VCO acts as a second pole, both the frequency and phase are maintained at a constant value during locked conditions.

As long as the PLL is within the lock-in range, the PLL can lock to within one beat note. The lock-in range is given as

$$\Delta\omega_{L} = 4\pi\zeta\omega_{n} \tag{2.16}$$

Using equations (2.13) and (2.14), the lock-in range can also be expressed as

$$\Delta\omega_{L} = \frac{RK_{o}I_{p}}{N} \quad Hz \tag{2.17}$$

As long as the frequency deviation is less than the lock-in range, the PLL will lock within one beat note (i.e. within  $2\pi$  radians), which is given as

$$T_{\rm P} = \frac{(\Delta \omega)^2}{2\zeta \omega_{\rm n}^3} \tag{2.18}$$

where  $\Delta\omega$  is the step frequency change in rads/sec. Using equations (2.13) and (2.14), the lock-in time can also be expressed as

$$T_{\rm P} = \frac{(\Delta f)^2}{\frac{R}{C} \left(\frac{K_{\rm o} I_{\rm p}}{N}\right)^2} \quad \text{seconds}$$

(2.19)

where  $\Delta f$  is the step frequency change in hertz.

#### 2.3.5 Phase noise performance

As eluded in section 2.2.2, there are two types of phase noise in PLL frequency synthesizers. The first is close-in phase noise, usually caused by the external frequency reference source and noise in the charge pump circuitry, and the other is short term phase noise, usually contributed by the VCO [3]. Fig. 2.7 demonstrates the effect of the PLL loop on the phase noise of the VCO. It seems that the closed loop PLL effectively suppresses the phase noise of the VCO up to its bandwidth. To understand how this works, consider a simple PLL model with additive noise injected into the VCO input. If the input is taken to be from the input referred VCO noise source and the output from the VCO output, the transfer function becomes that of (2.11). Assuming a first order loop filter and a linear charge pump based PLL, (2.11) becomes

$$H_5(s) = \frac{K_0 s^2}{s^2 + \frac{K_0 I_p R}{2\pi NC} s + \frac{K_0 I_p}{2\pi NC}}$$

(2.20)

This is clearly a high pass filter. The denominator of  $H_5(s)$  is the same as  $H_1(s)$ . This means that the bandwidth of the high pass filter is equal to the bandwidth of the PLL, which is consistent with Fig. 2.6. The larger the PLL bandwidth, the more VCO generated phase noise is suppressed. This makes sense since the larger the PLL's bandwidth, the faster it can correct for any phase deviations that the VCO produces and hence the magnitude of the phase deviations are limited. This type of phase noise is referred to as short-term phase noise.

Another potential source of phase noise in phase locked-loops is from power supply bounces. For PLL-based clock generators used in microprocessor and digital signal processor (DSP) chips, this is a major source of phase noise, or jitter, since the PLL resides on the same chip with a large digital circuit block. In the design of front-end wireless systems, however, the phase locked-loop frequency synthesizer resides on an independent chip and its power supplies are well regulated. Therefore, this source of phase noise is not a major issue in the design of front-end phase locked-loops for wireless applications.

Figure 2.6. Phase noise in a closed loop PLL system

Long term phase noise (or more commonly referred to as close-in phase noise) results from the phase noise contributed by all other PLL components as well as the crystal oscillator driving the PLL. Noise generated by the crystal oscillator is shaped by the transfer function  $H_1(s)$ , which is a low pass filter. The other transfer functions  $H_2(s)$  to  $H_4(s)$  are all low pass filter transfer functions. This means that the larger the bandwidth, the more phase noise contributions are generated by all PLL components other than the VCO. Therefore, there is a trade-off in choice of the PLL bandwidth. Larger bandwidth leads to more phase noise suppression generated by the VCO, but allows more phase noise generated by the other PLL components. For a properly designed PLL, the close-in phase noise is dominated by the charge pump.

## 2.4 Fractional-N Phase-Locked Loop

#### 2.4.1 Basic Operation

Fractional-N PLLs [34] offer a cost effective method of achieving low phase noise and fast lock times. The frequency divider in fractional-N PLLs toggles between one of two division ratios to generate an average division ratio, N.f., that lies between these two division ratios, where N is the integer division ratio and f is the fractional division ratio. The division ratios are usually chosen such that they differ by a factor of one. For example, if a division ratio of 4 is chosen in four clock cycles and a division ratio of 5 is chosen in one clock cycle, an average division ratio of (4\*4+5\*1)/5=4.2 is achieved. A diagram of a fractional-N PLL is shown in Fig. 2.7.

Fractional-N PLLs have several advantages. Since fractions of the reference frequency can be achieved, the reference frequency can exceed the channel spacing. This enables a reduction of the size of the frequency divider, N. This helps in both reducing the close-in phase noise as well as reduce the lock time. The major disadvantage of fractional-N PLLs is that it produces fractional spurs, which are difficult to attenuate, even with a narrow loop bandwidth.

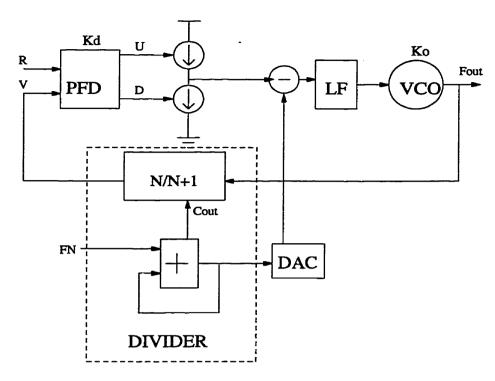

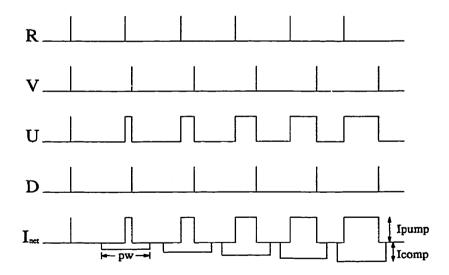

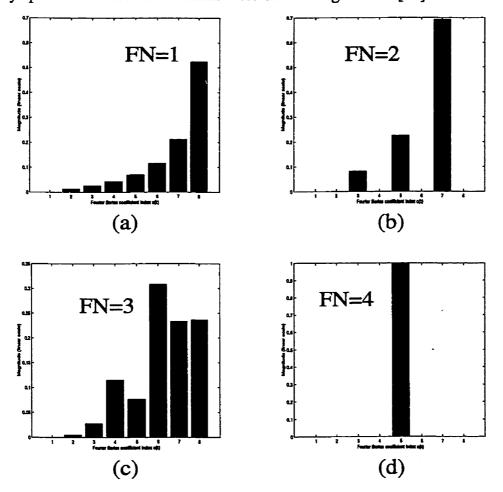

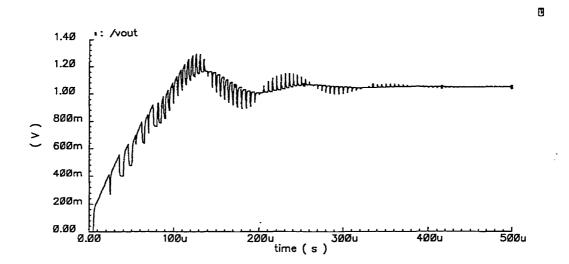

Figure 2.7. Fractional-N Phase-locked Loop

## 2.4.2 Analog Compensated Fractional-N PLL

One common solution to eliminate spurs generated by fractional-N PLLs is referred to as analog compensation [35]. A block diagram of a fractional-N PLL using this technique is shown in Fig. 2.8. This technique is based on the fact that the contents of the accumulator used in the fractional-N divider is proportional to the phase error at the output of the VCO. Therefore, the phase error can be eliminated by converting the digital contents of the accumulator into an analog signal and subtracting it from the control voltage, V<sub>c</sub>. This is accomplished by using a current-type digital-to-analog converter (DAC). A current-type DAC is nothing but a bank of current sources which are switched on and off by digital control signals. In this case, the digital control signals come from the accumulator output bits. The size of the DAC currents with respect to the charge pump currents depends on the fractionality used. If a fractionality of eight is used, 3 bits are taken from the accumulator, and the DAC current sources are sized to by one-eighth of the charge pump currents. The larger the fractionality used, the higher the reference frequency becomes, which reduces the PLL's lock time.

Figure 2.8. Analog compensated fractional-N PLL

Unfortunately, fractionality beyond 16 is hardly used since it is difficult to match the DAC current sources; furthermore, the DAC current sources start to occupy a significant portion of the overall PLL chip area. DAC nonlinearity errors are not an issue in this application since the DAC size is very small. Other limitations of this technique includes in the inability of the analog integrated circuits to accurately produce the error signal to be subtracted from the control voltage. This will be explained in more detail in chapter 3. Most commercial products implementing this technique report a spur reduction to nearly -70dBc [4,5,15]. The major advantage of this architecture is that it is a low-cost and low-power solution to frequency synthesis with reasonable frequency accuracy.

#### 2.4.3 Sigma-Delta Compensated Fractional-N PLL

Another method, which has recently gained popularity, is known as sigma-delta compensated fractional-N PLL, or simply  $\Delta\Sigma$  PLL [36]. Instead of attempting to

eliminate the phase errors in fractional-N PLLs, this technique noise shapes the phase errors to higher frequencies. This is done by using the output bits of a digital  $\Delta\Sigma$  modulator to change the frequency division ratio in a random manner. The closed loop bandwidth then acts as a low-pass filter, which eliminates the noise shaped error terms. Fig. 2.9 shows a block diagram of a  $\Delta\Sigma$  PLL. The major advantages of this technique include larger loop bandwidths (which result in faster lock times), less phase noise due to noise in the PFD and charge pumps. The two major disadvantages of this technique are increased circuit complexity (which entails larger power dissipation and area) and high phase noise at higher frequency offsets.

Figure 2.9. ΣΔ PLL Architecture

# 2.5 Fast Lock Phase-Locked Loop Techniques

The four key performance metrics in designing a frequency synthesizer for wireless systems are power dissipation, cost, spectral purity, and lock time. In this section,

techniques for reducing lock time in PLL for wireless systems are reviewed. Fast lock techniques used for PLLs can be divided into five categories:

- DSP/digital methods,

- Dual-loop/dual-PLL architectures,

- Feed-forward compensation methods,

- Variable loop bandwidth methods, and

- Frequency-to-voltage conversion.

Figure 2.10. DSP PLL Architecture

In the first method[6], digital signal processing techniques are used to control the VCO control voltage, as shown in Fig. 2.10. A digital word is used to represent the reference frequency and a digital word representing the divided frequency from the VCO are subtracted from each other to produce an error term. This subtractor replaces the PFD. The error term is then fed into a digital loop filter. The output of the loop filter is fed into a digital-to-analog converter (DAC). In this implementation, there are no reference spurs produced, which means that very large loop bandwidths can be produced. Large loop bandwidth translates to fast lock time. Three main limitations exist in this architecture. First the size of the DAC may be large. It was estimated that a 27-bit DAC was required to achieve the required accuracy for the GSM and GPRS wireless standards. Secondly, spurs are generated due to finite word length truncation. Furthermore, overflow in the subtractor (used in place of the PFD) or the loop filter causes additional spurs. The third main disadvantage of this architecture is that the

complexity DSP portion is quite large, which negatively affects the power consumption and area of the frequency synthesizer.

Figure 2.11. Dual loop PLL architecture

Dual-loop PLL architectures have also been reported in literature[7], which are capable of fast frequency lock times. A block diagram of the dual-loop PLL is shown in Fig. 2.11. The first loop is used for channel selection. It produces an RF output signal and is then frequency divided to achieve good phase noise. This signal is fed to the second loop, which contains a fixed divider (div 4), and an image rejection mixer with a fixed input reference frequency of 200MHz. The advantage of this approach is that there is no need for fractional-N divider (less spurs). The second PLL has a very high bandwidth and the close-in VCO noise is well suppressed. High bandwidth also translates to fast lock time. The major disadvantages of this architecture include integration difficulty (2 PLLs + mixer), large power consumption and area, and nonlinearities in the image rejection mixer may produce large spurs.

A dual-PLL architecture [8] may also be used to reduce lock time. A dual-PLL architecture is shown in Fig. 2.12. This architecture has been shown to have a 1µs lock

time when used for frequency hopping applications. The two PLLs work in parallel, but only one is active. While one PLL is producing the desired output frequency, the other is locking to a new frequency. A switch is used to select between the two. The lock time is set by the speed of the switch. The two disadvantages of this architecture are integration difficulties (2 separate PLLs), and the switch may produce nonlinear distortion when switching from one PLL to the other.

Figure 2.12. Dual PLL architecture

In a feed-forward compensated PLL [9], shown in Fig. 2.13, the knowledge of the desired frequency is used to pre-tune the VCO control voltage to near lock conditions. This is done by a DSP and a DAC. The DSP calculates the required control voltage and the DAC translates it to the pre-tuned control voltage. The DAC is implemented as either a standard DAC plus analog adder or a digitally controlled bank of charge pumps. Once pre-tuned, the regular PLL loop takes over to perform final lock. The lock time is limited by the accuracy of the DSP and DAC to produce the correct control voltage. Limitations of this architecture include the difficulty in implementing the DAC. For the standards such as the GSM and GPRS standards, a large DAC (>25 bit DAC) is required to cover the entire frequency range with reasonable accuracy. Another major difficulty with this architecture is that the accuracy of the feed-forward technique is undermined by the VCO inaccuracy, which significantly affects switching speed. VCO inaccuracy results from process variation (if the VCO is implemented on-chip) or from variation of VCO characteristics from one VCO chip to another.

Figure 2.13. Feedforward compensated PLL architecture

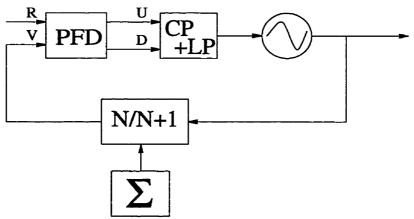

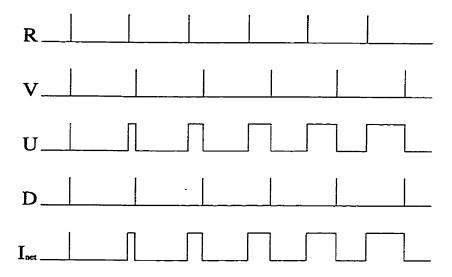

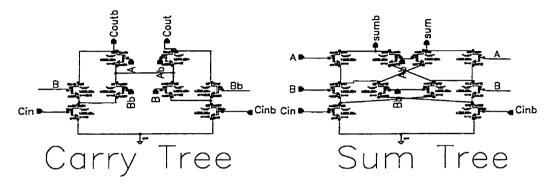

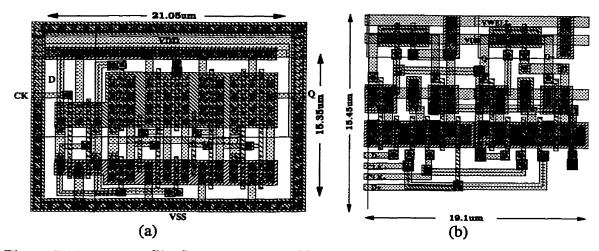

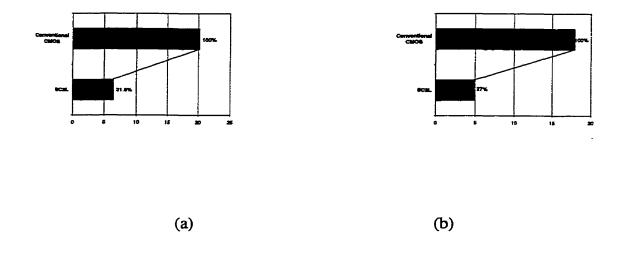

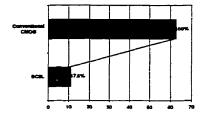

Variable loop bandwidths are the most common approach used in industry to achieve fast lock. This method typically achieves 2x to 5x reduction in lock time. In [10], a DFF-based lock-detection circuit is used to detect cycle slipping. If cycle slipping is detected, the charge pump current is multiplied by a certain factor. This increases the loop bandwidth of the PLL. Once cycle slipping stops, charge pump current is returned to its original value, and the closed loop bandwidth is returned to its original value. The charge pump current during cycle slipping is limited by PLL stability requirements.