# Timing Predictable and High-Performance Hardware Cache Coherence Mechanisms for Real-Time Multi-Core Platforms

by

Anirudh Mohan Kaushik

A thesis presented to the University of Waterloo in fulfillment of the thesis requirement for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Waterloo, Ontario, Canada, 2021

© Anirudh Mohan Kaushik 2021

#### **Examining Committee Membership**

The following served on the Examining Committee for this thesis. The decision of the Examining Committee is by majority vote.

| External Examiner: | Jörg Henkel<br>Professor, Karlsruhe Institute of Technology                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Supervisor(s):     | Hiren Patel<br>Professor, University of Waterloo                                                                                   |

| Internal Members:  | Rodolfo Pellizzoni<br>Associate Professor, University of Waterloo<br>Nachiket Kapre<br>Associate Professor, University of Waterloo |

Internal-External Member: Kenneth Salem Professor, University of Waterloo

#### **Author's Declaration**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### Abstract

Multi-core platforms are becoming primary compute platforms for real-time systems such as avionics and autonomous vehicles. This adoption is primarily driven by the increasing application demands deployed in real-time systems, and the cost and performance benefits of multicore platforms. For real-time applications, satisfying safety properties in the form of timing predictability, is the paramount consideration. Providing such guarantees on safety properties requires applying some timing analysis on the application executing on the compute platform. The timing analysis computes an upper bound on the application's execution time on the compute platform, which is referred to as the worst-case execution time (WCET).

However, multi-core platforms pose challenges that complicate the timing analysis. Among these challenges are timing challenges caused due to simultaneous accesses from multiple cores to shared hardware resources such as shared caches, interconnects, and off-chip memories. Supporting timing predictable shared data communication between real-time applications further compounds this challenge as a core's access to shared data is dependent on the simultaneous memory activity from other cores on the shared data. Although hardware cache coherence mechanisms are the primary high-performance data communication mechanisms in current multicore platforms, there has been very little use of these mechanisms to support timing predictable shared data communication in real-time multi-core platforms. Rather, current state-of-the-art approaches to timing predictable shared data communication sidestep hardware cache coherence. These approaches enforce memory and execution constraints on the shared data to simplify the timing analysis at the expense of application performance.

This thesis makes the case for timing predictable hardware cache coherence mechanisms as viable shared data communication mechanisms for real-time multi-core platforms. A key take-away from the contributions in this thesis is that timing predictable hardware cache coherence mechanisms offer significant application performance over prior state-of-the-art data communication approaches while guaranteeing timing predictability.

This thesis has three main contributions.

First, this thesis shows how a hardware cache coherence mechanism can be designed to be timing predictable by defining design invariants that guarantee timing predictability. We apply these design invariants and design timing predictable variants of existing conventional cache coherence mechanisms. Evaluation of these timing predictable cache coherence mechanisms show that they provide significant application performance over state-of-the-art approaches while delivering timing predictability.

Second, we observe that the large worst-case memory access latency under timing predictable hardware cache coherence mechanisms questions their applicability as a data communication mechanism in real-time multi-core platforms. To this end, we present a systematic framework to design better timing predictable cache coherence mechanisms that balance high application performance and low worst-case memory access latency. Our systematic framework concisely captures the design features of timing predictable cache coherence mechanisms that impacts their WCET, and identifies a spectrum of approaches to reduce the worst-case memory access latency. We describe one approach and show that this approach reduces the worst-case memory access latency of timing predictable cache coherence mechanisms to be the same as alternative approaches while trading away minimal performance in the original cache coherence mechanisms.

Third, we design a timing predictable hardware cache coherence mechanism for multi-core platforms used in mixed-critical real-time systems (MCS). Applications in MCS have varying performance and timing predictability requirements. We design a timing predictable cache coherence mechanism that considers these differing requirements and ensures that applications with no timing predictability requirements do not impact applications with strict predictability requirements.

#### Acknowledgements

This PhD thesis is a culmination of research work spanning over five years (2015-2021). The academic training and character building crucial to complete this thesis started much earlier under the guidance of several mentors who have guided and led me from naive beginnings to this moment. These mentors have taken different forms – teachers, professors, friends, and family. I have benefited from your collective wisdom and support, and I am immensely grateful for the positive impact you all have had on this thesis.

Let me begin by first thanking my adviser, Prof. Hiren Patel. I lucked out working with Hiren, and I consider myself even luckier to have been mentored by him for close to nine years (2012-2021)! I have benefited greatly from his supervision style that puts student training at the forefront. His training over these years have had a transformative effect on my technical thinking and skills. Hiren taught me how to understand and communicate technical challenges and observations at the right abstraction level that focuses on the essential details. In addition to my technical training, Hiren imparted several life lessons at crucial points in my PhD tenure that have shaped me into a better person. I am immensely grateful for his guidance and training, and look forward to many years of collaboration and friendship.

I am extremely grateful to the members of my thesis committee for their time and constructive feedback on my thesis: Prof. Jörg Henkel, Prof. Ken Salem, Prof. Rodolfo Pellizzoni, and Prof. Nachiket Kapre.

I feel extremely privileged and humbled to have interacted with some amazing instructors, academics, and students during my time at the UWaterloo. I sincerely thank you all for your wisdom and inspiration. Special thanks goes to Mohamed Hassan, with whom I wrote the first work that would lay the foundation for this thesis. Many thanks to the fantastic Zhuanhao Wu, with whom I had the pleasure of collaborating on a couple of works that are part of this thesis. I look forward to more collaborations with Zhuanhao. Special thanks to past and current members of the CAESR lab for their knowledge and support: Dan Wang, Zhuoran Yin, Yunling Cui, Nivedita Sritharan, Paulos Tegegn and Artem Klashtorny.

My time in Waterloo wouldn't have been nearly as rich without a wonderful set of friends: Hemant Saxena, Sharath Ibrahimpur, Jimit Mazmudar, Priya Soundararajan, Dhinakaran Vinayagamurthy, Abhinav Bommireddi, Retnika Devasher, Paulous Tegegn, Varuna Manivannan, and Karthik Velakur. From yearly camping trips, happy hours, and Friday night hangouts, you guys made Waterloo a special place for me and happily complimented the rigorous working hours of graduate school. I thank you all for your support and I consider myself blessed for your friendship. I want to especially thank Hemant for being a great friend and fellow companion on this PhD journey. Your levelheadedness and strong support helped me in this journey, and I cannot thank you enough. Many thanks to Srinivas Suryanarayan, Navnit Narayan Das, Akshay Shrivastava, and Sanket Jaiswal for being wonderful friends over many years despite geographical distances and different time-zones.

Finally and especially, I am immensely grateful to my parents Mandakolathur V. Mohan and Revathy Mohan for their support and love during this education journey. It is not possible for me to fully express my gratitude for their pure and unconditional love and support. They instilled in me the value of seeking good education and have sacrificed many luxuries so that I may receive a good education in India and Canada. My parents have been sources of strength during difficult times and celebrated every success, no matter how small, with great pomp. They are the sole reason for my success, happiness, and making my dreams come true.

#### Dedication

This thesis is dedicated to my parents for their love, support, and wisdom thoughout my life. I would never have made it here without you.

# **Table of Contents**

| Li | st of l | Figures       |                                                                                                                       | xiv  |

|----|---------|---------------|-----------------------------------------------------------------------------------------------------------------------|------|

| Li | st of [ | <b>Fables</b> |                                                                                                                       | xvii |

| Li | st of l | Publica       | tions                                                                                                                 | XX   |

| 1  | Intr    | oductio       | n                                                                                                                     | 1    |

|    | 1.1     | Multi-        | Core Real-Time Systems                                                                                                | 2    |

|    | 1.2     | Timing        | g Predictability of Multi-Core Real-Time Systems                                                                      | 3    |

|    | 1.3     |               | Focus: Achieving Predictable and High-Performance Shared Data Com-<br>ation Between Multiple Cores                    | 5    |

|    |         | 1.3.1         | Motivation: Existing Predictable Shared Data Communication Mecha-<br>nisms Constrain Application Performance          | 7    |

|    |         | 1.3.2         | Design Dilemma: Reconciling Predictability and High-Performance                                                       | 8    |

|    |         | 1.3.3         | Our Approach: Predictable and High-Performance Shared Data Com-<br>munication through <i>Hardware Cache Coherence</i> | 10   |

|    | 1.4     | Key B         | enefits of Proposed Approach                                                                                          | 10   |

|    | 1.5     | Thesis        | Contributions                                                                                                         | 12   |

|    | 1.6     | Structu       | are of Thesis                                                                                                         | 13   |

| 2  | Bac     | kground       | d and Related Works                                                                                                   | 14   |

|    | 2.1     | Multi-        | Core Platforms                                                                                                        | 14   |

|   | 2.2  | Hardw   | are Cache Coherence                                               | 16 |

|---|------|---------|-------------------------------------------------------------------|----|

|   | 2.3  | Related | d works                                                           | 24 |

|   |      | 2.3.1   | Predictable management of shared hardware resources               | 24 |

|   |      | 2.3.2   | Predictable shared data communication mechanisms                  | 25 |

|   |      | 2.3.3   | Hardware cache coherence mechanisms                               | 26 |

| 3 | Desi | gning P | redictable Cache Coherence Mechanisms for Hard Real-Time Systems  | 27 |

|   | 3.1  | Introdu | uction                                                            | 27 |

|   | 3.2  | Main c  | contributions                                                     | 29 |

|   | 3.3  | Related | d Work                                                            | 30 |

|   | 3.4  | System  | n Model                                                           | 31 |

|   | 3.5  | Design  | Invariants for Predictable Cache Coherence                        | 32 |

|   |      | 3.5.1   | Inter-core Coherence Interference                                 | 33 |

|   |      | 3.5.2   | Intra-core Coherence Interference                                 | 37 |

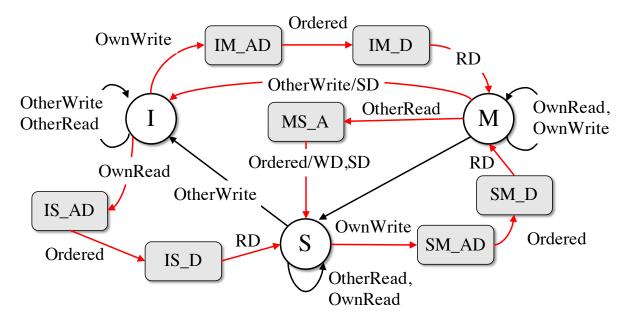

|   | 3.6  | Predict | table Cache Coherence Protocols                                   | 38 |

|   |      | 3.6.1   | Architectural Modifications                                       | 39 |

|   |      | 3.6.2   | Cache coherence protocol state machine modifications              | 42 |

|   | 3.7  | Latenc  | y Analysis                                                        | 47 |

|   | 3.8  | Evalua  | tion                                                              | 53 |

|   |      | 3.8.1   | Verification                                                      | 53 |

|   |      | 3.8.2   | Observed worst-case latencies                                     | 54 |

|   |      | 3.8.3   | Comparison against prior predictable approaches                   | 56 |

|   |      | 3.8.4   | Comparison of PMSI, PMESI, and Opt-PMESI protocols                | 58 |

|   | 3.9  | Conclu  | nsion                                                             | 59 |

| 4 | Bala | ncing P | Predictability and High-Performance in Cache Coherence Mechanisms | 60 |

|   | 4.1  | Introdu | action                                                            | 60 |

|   | 4.2  | Main c  | contributions                                                     | 62 |

|   | 4.3  | Relate          | d work                                                                  | 63  |

|---|------|-----------------|-------------------------------------------------------------------------|-----|

|   | 4.4  | Motiva          | ation                                                                   | 64  |

|   |      | 4.4.1           | High level understanding behind the WCL gap                             | 64  |

|   |      | 4.4.2           | Techniques to tighten the WCL                                           | 65  |

|   | 4.5  | System          | n model                                                                 | 67  |

|   | 4.6  | Analyz          | zing Predictable Cache Coherence Protocols                              | 68  |

|   |      | 4.6.1           | Formal model of coherence protocols                                     | 68  |

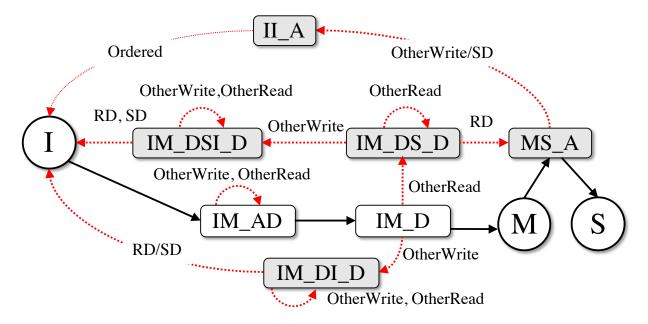

|   |      | 4.6.2           | Design principles of cache coherence protocols                          | 73  |

|   | 4.7  | Worst-          | case Asymptotic Latency Analysis (WCAL)                                 | 74  |

|   |      | 4.7.1           | Applying the formal model and analysis                                  | 79  |

|   | 4.8  | Tighte          | ning WCL bounds                                                         | 80  |

|   | 4.9  | Evalua          | ntion                                                                   | 86  |

|   |      | 4.9.1           | Observed WCL                                                            | 86  |

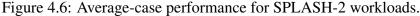

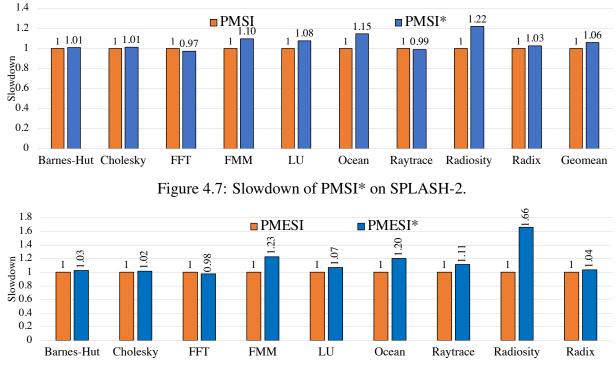

|   |      | 4.9.2           | Average-case performance                                                | 87  |

|   | 4.10 | Conclu          | usion                                                                   | 88  |

|   |      |                 |                                                                         |     |

| 5 |      | omatic<br>ocols | Construction of Predictable and High-Performance Cache Coherence        | 90  |

|   | 5.1  |                 | uction                                                                  | 91  |

|   | 5.2  |                 | contributions                                                           |     |

|   | 5.3  |                 | d works                                                                 |     |

|   |      | 5.3.1           | Predictable hardware cache coherence                                    |     |

|   |      | 5.3.2           | Cache coherence protocol synthesis                                      |     |

|   | 5.4  |                 | HIA implementation                                                      | 94  |

|   | 0    | 5.4.1           | Protocol specification in SYNTHIADSL                                    | 95  |

|   |      | 5.4.2           | Constructing t-states and transitions due to shared bus communication . | 97  |

|   |      | 5.4.3           | Constructing t-states and transitions due to interleaving memory oper-  | )   |

|   |      | 5.4.5           | ations                                                                  | 101 |

|   |       | 5.4.4   | Handling replacements, transition actions, and shared memory protocol construction       |

|---|-------|---------|------------------------------------------------------------------------------------------|

|   |       | 5.4.5   | Correctness of protocols constructed by SYNTHIA                                          |

|   |       | 5.4.6   | Limitations of SYNTHIA                                                                   |

|   | 5.5   | Case st | tudy: Predictable MESIF (PMESIF) cache coherence protocol                                |

|   | 5.6   | Results | s                                                                                        |

|   | 5.7   |         | nsion                                                                                    |

| 6 |       |         | ardware Cache Coherence Mechanism for Multi-Core Mixed-Criticality                       |

|   | Syste |         | 116                                                                                      |

|   | 6.1   |         | action                                                                                   |

|   | 6.2   |         | ntion                                                                                    |

|   | 6.3   |         | n Model                                                                                  |

|   | 6.4   | High le | evel overview of CARP                                                                    |

|   |       | 6.4.1   | Interference due to data responses from shared memory                                    |

|   |       | 6.4.2   | Interference due to write-back responses                                                 |

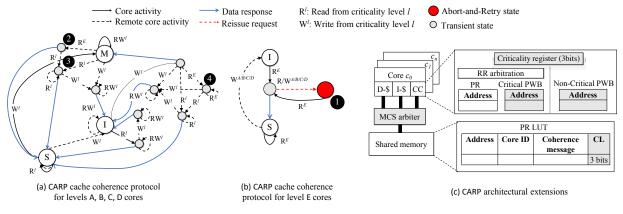

|   | 6.5   | CARP    | implementation                                                                           |

|   |       | 6.5.1   | Implementing abort-and-retry for level E cores                                           |

|   |       | 6.5.2   | Implementing PWB partitioning and slack scheduling for non-critical write-back responses |

|   |       | 6.5.3   | Hardware overhead                                                                        |

|   | 6.6   | Latenc  | y analysis                                                                               |

|   |       | 6.6.1   | Preliminaries                                                                            |

|   |       | 6.6.2   | Analysis                                                                                 |

|   |       | 6.6.3   | Discussion                                                                               |

|   | 6.7   | Metho   | dology                                                                                   |

|   | 6.8   | Results | s                                                                                        |

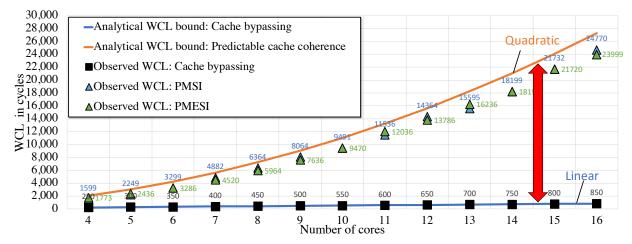

|   |       | 6.8.1   | Synthetic workloads                                                                      |

|   |       | 6.8.2   | SPLASH-2 workloads                                                                       |

|   |       |         |                                                                                          |

|   | 6.9   | Related | d works                                                                                  |

| 7  | End    | -to-End Predictable and High-Performance Real-Time Multi-Core Platforms                               | 142   |

|----|--------|-------------------------------------------------------------------------------------------------------|-------|

|    | 7.1    | POTPOURRI: A (hypothetical) timing predictable and high-performance real-<br>time multi-core platform | . 143 |

|    | 7.2    | Deriving WCET under predictable cache coherence                                                       | . 145 |

| 8  | Con    | clusion and Future Works                                                                              | 148   |

| Re | eferen | ices                                                                                                  | 151   |

# **List of Figures**

| 1.1 | MPSoCs with multi-core computing units (highlighted) used in real-time systems.                                                                                                                                                                                                                   | 2  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Illustrative example of impact of shared data accesses on timing behavior of real-<br>time applications.                                                                                                                                                                                          | 6  |

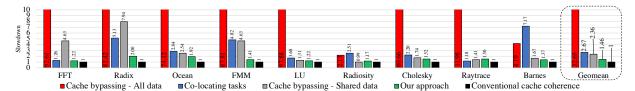

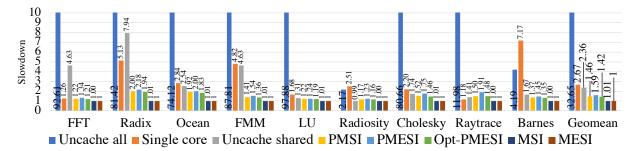

| 1.3 | Performance slowdown of state-of-the-art approaches to predictable shared data communication against a conventional multi-core communication mechanism for the SPLASH-2 workloads on a 4-core multi-core platform. These results are taken from [74]. Lower is better.                            | 8  |

| 1.4 | Performance slowdown of state-of-the-art approaches and one of our approaches to predictable shared data communication against a conventional hardware cache coherence mechanism for the SPLASH-2 workloads on a 4-core multi-core plat-form. These results are taken from [74]. Lower is better. | 11 |

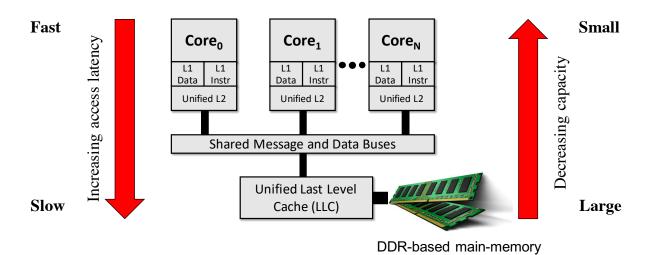

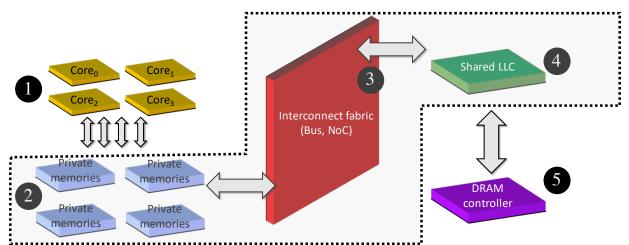

| 2.1 | Typical multi-core platform. Capacity and access latency trends of memory components in memory hierarchy highlighted.                                                                                                                                                                             | 15 |

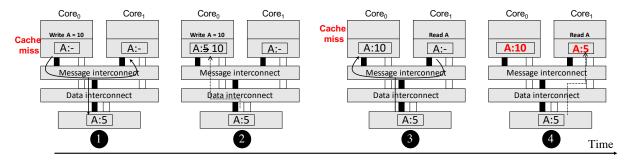

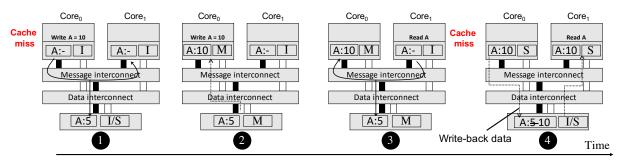

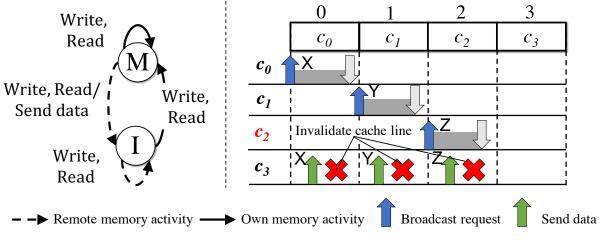

| 2.2 | Example of incoherent shared data communication.                                                                                                                                                                                                                                                  | 17 |

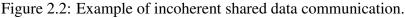

| 2.3 | Hardware cache coherence implementation of MSI cache coherence protocol                                                                                                                                                                                                                           | 17 |

| 2.4 | Coherent data sharing with MSI protocol.                                                                                                                                                                                                                                                          | 17 |

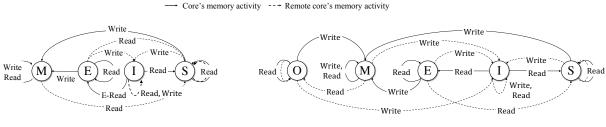

| 2.5 | MESI and MOESI cache coherence protocol state machines at the private cache level                                                                                                                                                                                                                 | 18 |

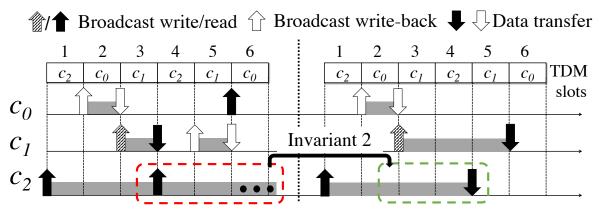

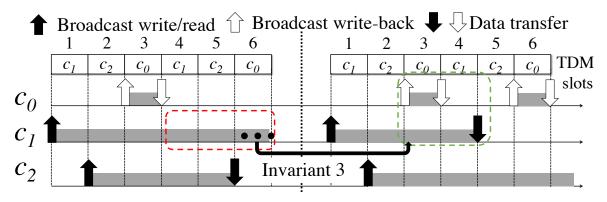

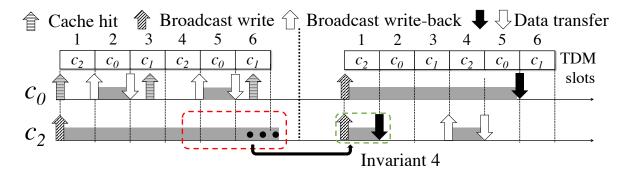

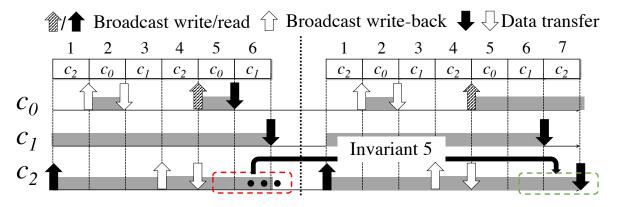

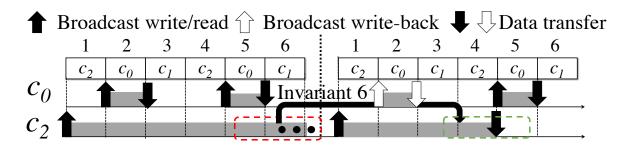

| 3.1 | Initially $c_0$ modified A. $c_2$ is core under analysis.                                                                                                                                                                                                                                         | 33 |

| 3.2 | Initially $c_0$ modified A and B. $c_1$ is core under analysis.                                                                                                                                                                                                                                   | 34 |

| 3.3 | Initially $c_0$ reads A. $c_2$ is core under analysis                                                                                                                                                                                                                                             | 35 |

| 3.4 | Initially $c_0$ modified A, $c_2$ modified B, and $c_1$ requested B. $c_2$ is core under analysis.                                                                                                                                                                                                | 36 |

| 3.5                                                                                      | Initially, $c_0$ has modified A. $c_2$ is under analysis.                                                                                                                                                                                                                                                                        | 37                               |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

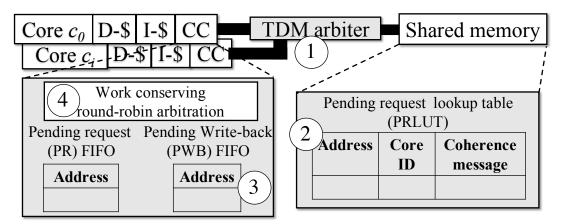

| 3.6                                                                                      | Architectural changes necessary for PMSI and PMESI.                                                                                                                                                                                                                                                                              | 39                               |

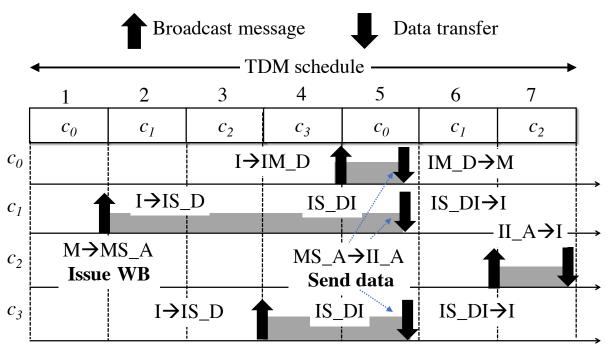

| 3.7                                                                                      | Execution with t-states. Initially, $c_0$ has A in S                                                                                                                                                                                                                                                                             | 45                               |

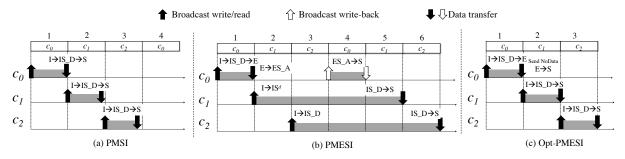

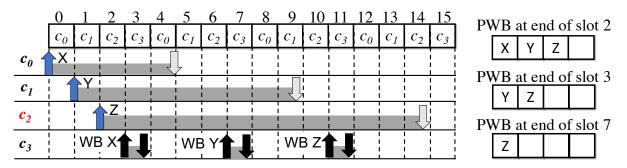

| 3.8                                                                                      | Execution example with PMSI and PMESI.                                                                                                                                                                                                                                                                                           | 45                               |

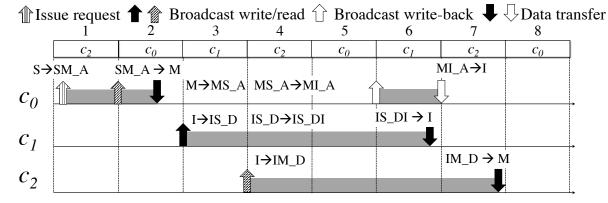

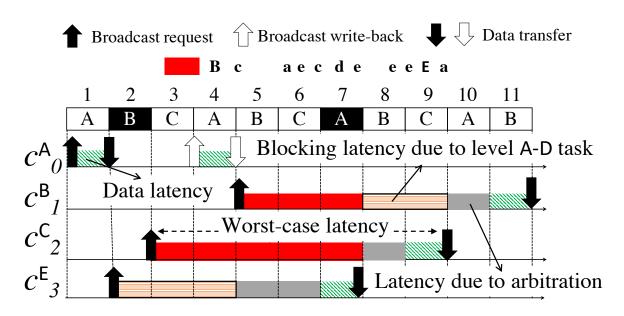

| 3.9                                                                                      | WC inter-core coherence latency. $c_1$ is $c_i$ .                                                                                                                                                                                                                                                                                | 48                               |

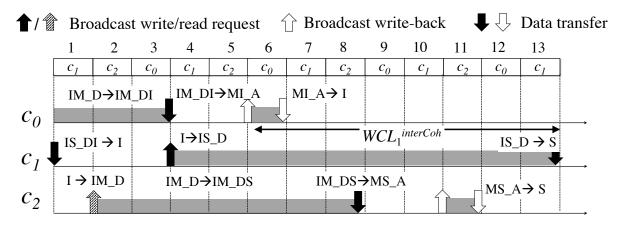

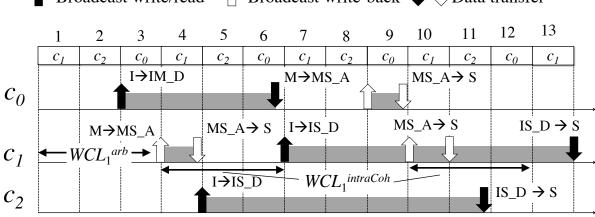

| 3.10                                                                                     | WC intra-core coherence latency. $c_1$ is $c_i$                                                                                                                                                                                                                                                                                  | 51                               |

| 3.11                                                                                     | WC latencies and the effect of unpredictability sources on them. Horizontal dotted line represents the analytical bound. Black bars are PMSI, PMESI, and Opt-PMESI protocols, orange bars denote violating design invariant 2, red bars denote violating design invariant 3, and green bars denote violating design invariant 4. | 55                               |

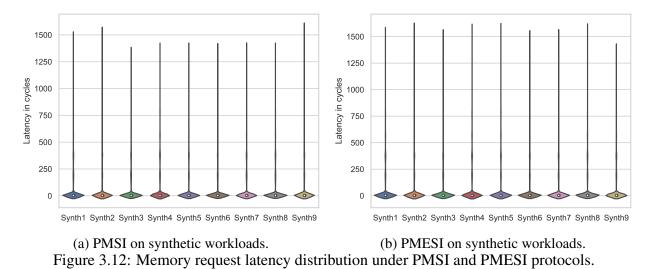

| 3.12                                                                                     | Memory request latency distribution under PMSI and PMESI protocols                                                                                                                                                                                                                                                               | 56                               |

| 3.13                                                                                     | Execution time slowdown compared to MESI protocol.                                                                                                                                                                                                                                                                               | 57                               |

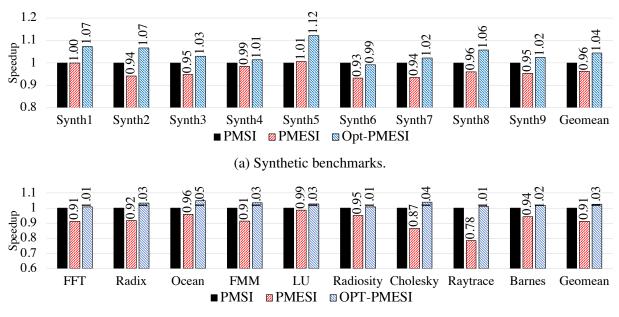

| 3.14                                                                                     | Average-case performance speedups of PMSI, PMESI, and Opt-PMESI for syn-<br>thetic and SPLASH-2 benchmarks.                                                                                                                                                                                                                      | 58                               |

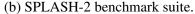

| 4.1                                                                                      | Variation of WCL for alternative and predictable cache coherence mechanisms with core count on synthetic workloads.                                                                                                                                                                                                              | 61                               |

| 4.2                                                                                      |                                                                                                                                                                                                                                                                                                                                  |                                  |

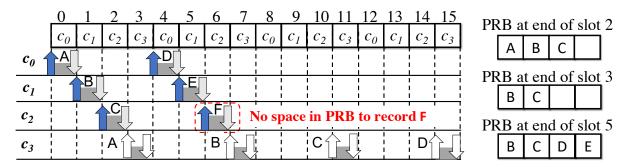

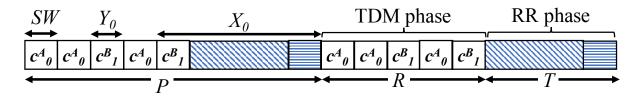

|                                                                                          | Example execution under PMSI protocol.                                                                                                                                                                                                                                                                                           | 64                               |

| 4.3                                                                                      | Example execution under PMSI protocolPMI protocol and execution example                                                                                                                                                                                                                                                          | 64<br>66                         |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                  | 66                               |

| 4.3                                                                                      | PMI protocol and execution example.                                                                                                                                                                                                                                                                                              |                                  |

| 4.3<br>4.4                                                                               | PMI protocol and execution example                                                                                                                                                                                                                                                                                               | 66<br>77<br>81                   |

| 4.3<br>4.4<br>4.5                                                                        | PMI protocol and execution example.       .         Visual aid for Lemma 9.       .         Transforming PMSI protocol to PMSI* protocol with $\mathcal{O}(N)$ WCAL. Transitions highlighted in red are offending transitions.                                                                                                   | 66<br>77<br>81<br>88             |

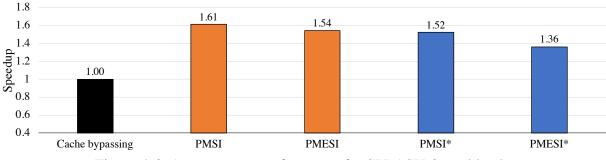

| <ul><li>4.3</li><li>4.4</li><li>4.5</li><li>4.6</li></ul>                                | PMI protocol and execution exampleVisual aid for Lemma 9Transforming PMSI protocol to PMSI* protocol with $\mathcal{O}(N)$ WCAL. Transitions<br>highlighted in red are offending transitions.Average-case performance for SPLASH-2 workloads                                                                                     | 66<br>77<br>81<br>88             |

| <ul> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> </ul>              | PMI protocol and execution exampleVisual aid for Lemma 9Transforming PMSI protocol to PMSI* protocol with $\mathcal{O}(N)$ WCAL. Transitions<br>highlighted in red are offending transitions.Average-case performance for SPLASH-2 workloadsSlowdown of PMSI* on SPLASH-2                                                        | 66<br>77<br>81<br>88<br>89<br>89 |

| <ul> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> </ul> | PMI protocol and execution example.Visual aid for Lemma 9.Transforming PMSI protocol to PMSI* protocol with $\mathcal{O}(N)$ WCAL. Transitionshighlighted in red are offending transitions.Average-case performance for SPLASH-2 workloads.Slowdown of PMSI* on SPLASH-2.Slowdown of PMESI* on SPLASH-2.                         | 66<br>77<br>81<br>88<br>89       |

| 5.4 | MSI protocol refinement for interleaving memory operations. Constructed t-    |

|-----|-------------------------------------------------------------------------------|

|     | states and transitions are highlighted                                        |

| 5.5 | MESIF protocol specification in SYNTHIADSL                                    |

| 5.6 | Execution example under PMESIF protocol                                       |

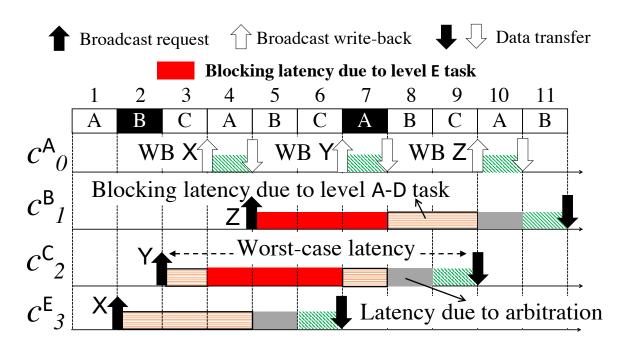

| 6.1 | Blocking communication due to shared memory responses                         |

| 6.2 | Blocking communication due to write-back responses                            |

| 6.3 | CARP protocol specification                                                   |

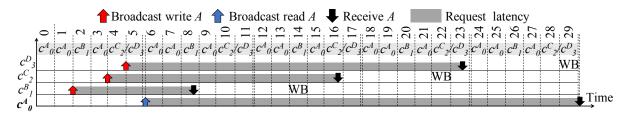

| 6.4 | Generalized MCS arbitration scheme [27]                                       |

| 6.5 | Worst-case instance for a 4-core system. $c_{ua}$ is $c_0^A$                  |

| 6.6 | Performance of design choices and CARP on synthetic workloads                 |

| 6.7 | Performance of CARP on SPLASH-2                                               |

| 7.1 | Hardware compute stack of a real-time multi-core platform. Research contribu- |

|     | tions in this thesis span across the highlighted layers                       |

# **List of Tables**

| 1.1 | Summary of prior research works on improving predictability of multi-core real-<br>time systems.                                                                                                                                                                                                                                                                                                                                                                                                                 | 5  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Capacity and access latency of different memory components in memory hierar-<br>chy of Intel's Xeon 5500 processors (Nehalem-EP) multi-core processors. Data<br>taken from [57].                                                                                                                                                                                                                                                                                                                                 | 15 |

| 2.2 | Private memory states for snooping bus-based MSI protocol. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . A core issues a <i>read/write</i> request. Once the cache line is available, the core <i>reads/writes</i> it. A replacement triggers a cache line eviction. Highlighted cells denote impossible scenarios, and cells marked with '—' denote no change in state.                                                                                  | 22 |

| 2.3 | Shared memory states for snooping bus-based MSI protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

| 3.1 | Hardware overheads with core count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40 |

| 3.2 | Private memory states for PMSI, PMESI, and Opt-PMESI. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . A core issues a <i>read/write</i> request. Once the cache line is available, the core <i>reads/writes</i> it. A core needs to issue a <i>replacement</i> to write back a dirty block before eviction. Changes to conventional MSI and MESI are in bold red. Differing transitions between PMESI and Opt-PMESI are marked as (A) and (B) respectively. | 41 |

| 3.3 | Shared memory states for PMSI protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

| 3.4 | Shared memory states for PMESI protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

| 3.5 | Shared memory states for Opt-PMESI protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

| 3.6 | Description of the proposed t-states in PMSI and PMESI to achieve a pre-<br>dictable behavior.                                                                                                                                                                                                                                                                                                                                                                                                                   | 43 |

| 4.1 | 2-core $(sv_A, ev_A^{c_{ua}}) \rightsquigarrow tv_A$ for PMSI protocol                                                                                                                                                                                                                                                                                                                                                     | 72   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.2 | Protocol changes to PMSI and PMESI protocols.                                                                                                                                                                                                                                                                                                                                                                              | 82   |

| 4.3 | Private memory states for PMSI* protocol. <i>issue msg/state</i> means the core issues<br>the message <i>msg</i> and move to state <i>state</i> . A core issues a <i>read/write</i> request.<br>Once the cache line is available, the core <i>reads/writes</i> it. A replacement triggers<br>a cache line eviction. Highlighted cells denote impossible scenarios, and cells<br>marked with '—' denote no change in state. | 84   |

| 4.4 | Private memory states for PMESI* protocol. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . A core issues a <i>read/write</i> request. Once the cache line is available, the core <i>reads/writes</i> it. A replacement triggers a cache line eviction. Highlighted cells denote impossible scenarios, and cells                                                       |      |

|     | marked with '—' denote no change in state                                                                                                                                                                                                                                                                                                                                                                                  |      |

| 4.5 | Simulation parameters                                                                                                                                                                                                                                                                                                                                                                                                      | 87   |

| 4.6 | Observed WCL (Obs) and analytical WCL bounds (Bound) in cycles for 4-core,<br>8-core, and 16-core configurations.                                                                                                                                                                                                                                                                                                          | 87   |

| 5.1 | Description of routines used for protocol construction.                                                                                                                                                                                                                                                                                                                                                                    | 95   |

| 5.2 | Private memory states for PMESIF cache coherence protocol generated by SYN-<br>THIA. <i>issue msg/state</i> means the core issues the message <i>msg</i> and move to state <i>state</i> . Changes to conventional MESIF are in <b>bold</b> red.                                                                                                                                                                            | 109  |

| 5.3 | Shared memory states and transitions of PMESIF cache coherence protocol                                                                                                                                                                                                                                                                                                                                                    | 110  |

| 5.4 | PMESIF t-states and transitions constructed by SYNTHIA.                                                                                                                                                                                                                                                                                                                                                                    | 110  |

| 5.5 | Evaluation of SYNTHIA on different protocols. SYNTHIA took less than a few seconds to construct the protocols.                                                                                                                                                                                                                                                                                                             | 113  |

| 5.6 | Predictability and performance evaluation                                                                                                                                                                                                                                                                                                                                                                                  | 113  |

| 6.1 | AUTOSAR guidelines satisfied and extended by CARP.                                                                                                                                                                                                                                                                                                                                                                         | 120  |

| 6.2 | Private memory states for CARP. <i>issue msg/state</i> means the core issues the mes-<br>sage <i>msg</i> and move to state <i>state</i> . A core issues a <i>read/write</i> request. Once the<br>cache line is available, the core <i>reads/writes</i> it. A core needs to issue a <i>replace-</i><br><i>ment</i> to write back a dirty block before eviction. Changes to PMSI are highlighted                             | .127 |

| 6.3 | Shared memory states for CARP protocol.                                                                                                                                                                                                                                                                                                                                                                                    |      |

| 6.4 | t-states and transitions introduced in CARP.                                                                                                                                                                                                                                                                                                                                                                               |      |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 6.5 | Symbols used in latency analysis                                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------------------|

| 6.6 | Hybrid arbitration policy parameters                                                                                  |

| 6.7 | Observed WCL for synthetic benchmarks                                                                                 |

| 7.1 | An instance of POTPOURRI using different related works that adopt predictable computer architecture design philosophy |

#### **List of Publications**

A large part of the contents of this thesis has been previously published in peer-reviewed conference and journal publications which I have co-authored. The use of the content, from the listed publications, in this thesis has been approved by all co-authors. For each publication, I present a list of my contributions.

- 1. Anirudh Mohan Kaushik, Mohamed Hassan, and Hiren Patel, "Designing Predictable Cache Coherence Protocols for Multi-Core Real-Time Systems" in IEEE Transactions on Computers (TC), 2020 [74]

- Developed, designed and implemented the cache coherence mechanisms

- Developed the timing analysis

- Execution of empirical evaluation

- Wrote portions of the article

- 2. Anirudh Mohan Kaushik and Hiren Patel, "A Systematic Approach to Achieving Tight Worst-Case Latency and High-Performance Under Predictable Cache Coherence" in IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS), 2021 [76]

- Deveopled, designed and implemented the cache coherence mechanisms

- Developed the timing analysis

- Execution of empirical evaluation

- Wrote significant portion of the article

- 3. Anirudh Mohan Kaushik and Hiren Patel, "Automated Synthesis of Predictable and High-Performance Cache Coherence Protocols" in IEEE Design Automation and Test in Europe (DATE), 2021 [75]

- Deveopled and designed the synthesis tool

- Execution of empirical evaluation

- Wrote significant portion of the article

- 4. Anirudh Mohan Kaushik, Paulos Tegegn, Zhuanhao Wu, and Hiren Patel, "CARP: A Data Communication Mechanism for Multi-Core Mixed-Criticality Systems", in IEEE Real-Time Systems Symposium (RTSS), 2019 [77]

- Deveopled and designed the cache coherence mechanism and contributed to implementation

- Developed the timing analysis

- Execution of empirical evaluation

- Wrote significant portion of the article

# **Chapter 1**

# Introduction

Today, computing systems are no longer limited to data-centers and supercomputers for delivering fast internet services and executing highly complex scientific computations respectively or desktop and laptop devices for personal use. In the last ten years, *embedded* computing systems that sense and interact with the physical world have become ubiquitous and pervasive in our daily lives. Examples of domains where embedded computing systems are used range from wearable and smart home technologies (smart watches, smart thermostats, video doorbells) to avionics, automotive, and robotic domains. Among these domains, computing systems used in avionics and automotive must not only compute correct results for correct functioning (logical correctness), but complete these computations within strict timing constraints (temporal correctness) for *correct and safe* operation. Failure to complete the computations within the timing constraints can result in dire catastrophic consequences such as loss of human lives. Such compute systems that depend on both logical correctness and temporal correctness are called *real-time systems*, and are the focus of this thesis.

As an example, consider an object avoidance application deployed in vehicles to realize semi/full autonomous driving capabilities [89]. This application detects the presence of objects on the current vehicle trajectory path, and informs the human driver of any detected objects. The human driver performs actions to safely steer the vehicle to avoid colliding with the detected object. Clearly, for safety of the human driver, this application must not only detect the object (functional correctness) but must do so in a timely manner (temporal correctness) so that the human driver can react to the detected object in a safe manner. Automatic braking system (ABS), airbag control systems, autopilot functions, and safety-critical radar applications are other examples of applications from the automotive and avionics domains that must satisfy functional and temporal correctness for safe and correct operation.

### **1.1 Multi-Core Real-Time Systems**

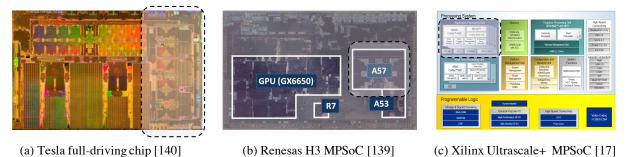

Figure 1.1: MPSoCs with multi-core computing units (highlighted) used in real-time systems.

There has been increasing attention and adoption of *multi-core computing platforms* to satisfy the demand for high computation capabilities in current real-time systems [28, 103, 106, 127, 144, 145]. For example, ARM projects a  $100 \times$  increase in computing performance between 2015-2024 in the automotive domain to enable future advanced driver assistance systems (ADAS) based on radar and computer vision technologies [146]. Multi-core computing platforms consolidate multiple processing units (referred to as cores or CPUs) onto a single component resulting in enhanced application performance and reduced power consumption. Furthermore, the consolidation of multiple processing units offers advantages with respect to the size, weight, and power (SWaP) constraints imposed by the embedded environment in which real-time systems are deployed.

The current trend in industry is to use commercially available off-the-shelf (COTS) multicore platforms in real-time systems. This trend in using COTS multi-core platforms in realtime systems is driven by the following reasons: (1) these platforms are readily available, (2) multi-core platform vendors spend considerable efforts in verifying their implementation before making them commercially available, and (3) availability of robust software ecosystems that enable designers to deploy their software applications with minimal effort. For these reasons, COTS multi-core platforms for real-time systems are preferred over custom in-house developed multi-core platforms as they shorten deployment time and minimize cost [12, 29, 148]. Embedded multi-processor system-on-chips (MPSoCs) developed for automotive and avionics domains such as Tesla's full self-driving computer [145], Renesas's R-Car SoC [144], Xilinx Ultrascale+ MPSoCs [18] feature COTS multi-core computing units alongside other compute accelerators such as as digital signal processing (DSP) units and graphics processing units (GPUs). We refer to real-time systems that use multi-core computing units as *multi-core real-time systems*. We refer the reader to [112] for a recent comprehensive survey of COTS multi-core computing units used in real-time systems. The memory hierarchy of current multi-core platforms feature multiple levels of *hardware caches*, which are small on-chip memory structures that are placed close to the core's execution execution pipeline. These caches store a subset of data in the shared main-memory that is frequently used, and provide fast data access to cores due to their proximity to the cores. Some of these cache levels are private to each core and some caches levels are shared across all cores, and they are essential for average-case performance. The multi-core platforms referred to in this thesis are *cached-based* multi-core platforms. Since hardware caches are primary performance features in multi-core platforms, there is a rich body of research work devoted towards leveraging their performance benefits for real-time systems [15, 23, 79, 94, 115, 131, 150].

### **1.2 Timing Predictability of Multi-Core Real-Time Systems**

Analyzing the temporal behavior of a real-time application prior to execution on the real-time system, which is referred to as *static timing analysis*, is crucial towards guaranteeing its temporal correctness. A real-time application comprises of multiple software routines or *tasks*, and each task must satisfy logical and temporal correctness. At a high level, this static timing analysis consists of two phases: (1) deriving an upper bound on the execution times of the tasks constituting the real-time application – *worst-case execution time (WCET) analysis* and (2) determining an execution schedule of the tasks such that the computed WCET of each task is not exceeded – *schedulability analysis*. Deriving the WCET of a task requires information about the task's software structure and the micro-architecture of the underlying compute platform. The derivation of the task's WCET must be *safe* in that it should be greater than or equal to any possible execution time of the task and *tight* in that it is the lowest WCET possible.

The micro-architecture of COTS multi-core platforms poses challenges to carry out precise WCET analysis resulting in the derivation of *loose* or *pessimistic* WCETs. The timing analysis challenges with multi-core platforms are primarily attributed to the presence of *shared hardware resources* that are shared between the multiple cores such as I/O interconnects, shared on-chip memories, and the shared main-memory [104, 116]. Multiple real-time tasks simultaneously executing on different cores *interfere* with each other for accesses to shared hardware resources thereby impacting their timing behavior and complicating the timing analysis. To put this into perspective, Nowotsch et al. [104] showed that a read operation to the shared main-memory (DRAM) on a multi-core platform used in real-time systems increased by more than  $14 \times$  when the number of concurrent cores executing tasks increased from one core (41 cycles) to eight cores (604 cycles). As a result, computing the WCET of a real-time task on a multi-core platform must take into account the timing interference caused due to shared hardware resources, which results in *pessimistic* WCET estimates. The risk of using such pessimistic WCET estimates is

that the schedulability analysis may deem a real-time application unschedulable on a compute platform (in other words, no feasible execution schedule such that all tasks of the application satisfy temporal correctness) even though it is safe to execute the real-time application on the compute platform. This prevents real-time applications from being deployed, which limits the functionality of the real-time system.

To this end, there is a large body of research devoted towards making multi-core real-time systems *timing predictable* or simply predictable in order to enable the timing analysis to compute precise WCET. Predictability is defined in Definition 1.

**Definition 1.** *Predictability is a property of a system that makes it easy for timing analysis to compute WCET of real-time tasks and guarantees that all possible execution times of tasks deployed on the system are within their WCET [55].*

Prior works in this research can be classified into four categories:

- (C1) New theories and analyses methodologies that improve the precision of the timing analysis on multi-core real-time systems [7,95,96,161,165]

- (C2) Empirical analysis of COTS multi-core platforms to capture the timing impact of shared hardware resources on WCET [29,41,103,116]

- (C3) Software techniques such as real-time operating system (RTOS) extensions and control of existing hardware features on multi-core platforms to limit timing interference [14,23,25,47,50,52,61,79,80,84,86,99,111,141]

- (C4) Novel computer architecture components that are designed with predictability in mind [15, 56, 63, 64, 78, 86, 91, 109, 118, 128, 131, 150]<sup>1</sup>.

Table 1.1 puts into perspective the impact of one recent prior work from each of these categories towards improving the predictability of multi-core real-time systems. We refer the reader to [40] for a comprehensive survey and critique of research efforts devoted towards addressing timing interference due to shared hardware resources in multi-core platforms.

<sup>&</sup>lt;sup>1</sup>Note that prior works under C4 propose hardware features not available in COTS multi-core platforms. The desired outcome of these works is to convince COTS multi-core manufacturers and vendors to implement them in future COTS multi-core platforms.

| Prior works             | Category | Brief description                                                                                                                                                                                                                                                      | Impact                                                                                                                                                                                                        |

|-------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mancuso et al. [96]     | C1       | A novel WCET analysis theory that reduces pes-<br>simism in the computed WCET of an application us-<br>ing knowledge about the application's execution in<br>isolation (no interference)                                                                               | Up to 60% reduction in the pessimism of es-<br>timated WCET compared to state-of-the-art<br>approaches                                                                                                        |

| Radojković et al. [116] | C2       | <i>Empirical analysis</i> of several COTS multi-core plat-<br>forms to identify impact of shared hardware resource<br>interference on application execution time                                                                                                       | Identifies COTS multi-core platforms <i>suit-able for real-time systems</i> and presents a methodology to identify computer architecture components in multi-core platforms that impact predictability        |

| Ward et al. [153]       | C3       | A software framework that provides fine grained con-<br>trol of shared hardware resources (cache and DRAM<br>partitioning, cache locking, cache scheduling) to<br><i>limit timing interference</i> between concurrent real-<br>time tasks on shared hardware resources | Fine grained control <i>reduced</i> the timing in-<br>terference on shared hardware resources re-<br>sulting in scheduling tasks that were pre-<br>viously unschedulable due to pessimistic<br>WCET estimates |

| Valsan et al. [150]     | C4       | New <i>predictable computer architecture components</i><br>in the form of per-core hardware control of outstand-<br>ing memory requests to the shared memory to limit<br>contention of shared hardware resources (miss status<br>handling registers)                   | <i>Up to 19% reduction in the WCET</i> compared to classic cache partitioning techniques.                                                                                                                     |

Table 1.1: Summary of prior research works on improving predictability of multi-core real-time systems.

## **1.3 Thesis Focus: Achieving Predictable and High-Performance Shared Data Communication Between Multiple Cores**

A common assumption underlying many of these prior works is that the real-time applications deployed on the multi-core platforms consist of *independent tasks*. It is our take that this means that real-time tasks do *not* communicate data with each other. This assumption is no longer representative of current and emerging practical real-time systems [43, 60, 72]. Furthermore, as demands for more integrated functionalities in real-time systems continue to rise shared data communication between multiple simultaneously executing real-time applications on different cores will be necessary to realize such functionalities. Examples of applications deployed in real-time domains that feature data communication include machine learning algorithms for training and classification [31, 85, 89, 172] and diagnostic real-time tasks that communicate frequently changing values from sensors and engines [43, 60]. As a concrete example, in state-of-the-art autonomous driving systems, multiple machine learning tasks execute in parallel and operate on the data captured by various sensors (shared data) to perform real-time object detection and vehicle localization computations [89].

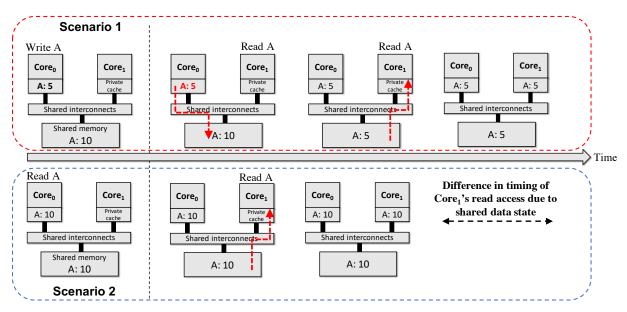

Shared data communication between real-time applications executing on different cores makes multi-core platforms even less amenable for timing analysis. This is because the timing behavior of a real-time application accessing shared data not only depends on the timing interference due to shared hardware resources but also on the *memory state* of the shared data due to past memory activity from other applications on the same shared data. As an example, consider the

Figure 1.2: Illustrative example of impact of shared data accesses on timing behavior of real-time applications.

scenarios shown in Figure 1.2 where two cores ( $Core_0$  and  $Core_1$ ) are accessing shared data with memory address A. In the first scenario,  $Core_0$  has modified A with a new value, and this is cached in  $Core_0$ 's private cache. In the second scenario,  $Core_0$  has an unmodified version of A in its private cache. Hence, the data state of A in  $Core_0$ 's private cache is different in both scenarios. This results in different timing behavior of  $Core_1$ 's access to A as shown. In the first scenario,  $Core_0$  has to respond by updating the shared memory version of A so that  $Core_1$ receives the most up-to-date version of A from the shared memory. On the other hand, in the second scenario,  $Core_1$  receives the correct data from the shared memory without any involvement of  $Core_0$ . Therefore, precise timing analysis of shared data communication involves accounting for timing interference due to shared hardware resources on two fronts – (1) a core's own access ( $Core_1$ 's read to A in both scenarios) and (2) other cores' responses based on the memory state of the shared data ( $Core_0$ 's update to shared memory in the first scenario). To handle the timing analysis challenges associated with shared data communication, recent research have focused on designing *predictable shared data communication mechanisms* [13, 14, 25, 52, 60, 79, 86, 87, 153].

#### **1.3.1** Motivation: Existing Predictable Shared Data Communication Mechanisms Constrain Application Performance

Designing for predictability entails designing components that are amenable to WCET analysis. As a result, designing for predictability is concerned with *worst-case scenarios* such that the computed WCET estimates are safe. On the other hand, designing for high-performance entails designing components that optimize for the *common case* or *average-case scenarios*. For example, speculative execution and deep cache hierarchies are high-performance micro-architectural optimizations common in COTS computing platforms that make computing WCET estimates difficult. Such architectural optimizations *threaten* predictability [11, 147]. As a result, predictability and high-performance are typically *conflicting* design goals where the former is concerned with optimizing worst-case scenarios and the latter is concerned with optimizing average-case scenarios [15, 24, 25].

Since predictability is a paramount consideration for real-time systems, state-of-the-art predictable shared data communication mechanisms trade away high-performance for enabling timing analysis. Examples of such mechanisms are:

- (M1) Private cache bypassing of shared data [13, 25, 86, 153],

- (M2) Co-locating real-time applications that communicate shared data to execute on the same core [14, 25, 52],

- (M3) software changes to real-time applications to eliminate shared data communication such as shared data duplication [25, 60, 79].

These mechanisms are adopted by industry as discussed in a recent survey on real-time systems industry practices [5]. To put this in context with the example in Figure 1.2, mechanisms in M1 prevent cores from caching A in their private caches, mechanisms in M2 force the application to execute on a single core, and mechanisms in M3 duplicate A into two versions where each version has a unique memory address. At a high level, these prior mechanisms place one of the following constraints: (1) how data is cached in the cores' cache hierarchy and (2) when and where real-time applications are executed to achieve predictable shared data communication. These data caching and application execution constraints in turn affect performance. Data caching constraints prevent cores from fully utilizing their private memory hierarchy (caches) that have been optimized for low latency access thereby incurring high compute latency. Application execution constraints prevents the usage of all available cores on the multi-core platform thereby throt-tling compute throughput. The consequences of such constraints (high compute latency and low compute throughput) goes against some of the key reasons for adopting multi-core platforms

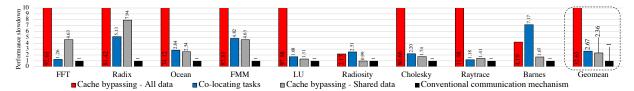

Figure 1.3: Performance slowdown of state-of-the-art approaches to predictable shared data communication against a conventional multi-core communication mechanism for the SPLASH-2 workloads on a 4-core multi-core platform. These results are taken from [74]. Lower is better.

(low compute latency and high compute throughput), and hence, prevent real-time systems that employ such predictable shared data communication mechanisms to take *full advantage* of the compute capabilities offered by multi-core platforms. Figure 1.3 highlights the performance slowdown of state-of-the-art predictable shared data communication mechanisms compared to the conventional multi-core communication mechanism deployed in multi-core platforms, which is hardware cache coherence [97]. A clear takeaway from Figure 1.3 is that state-of-the-art predictable shared data communication mechanisms exhibit up to  $97 \times$  performance slowdown ( $2.3 \times -32 \times$  average slowdown), which underscores the conflicting design trade-offs between predictability and performance.

#### **1.3.2** Design Dilemma: Reconciling Predictability and High-Performance

The conflicting design goals of predictability and high-performance puts real-time system designers and architects in a *dilemma* about the best way to reconcile them when designing a shared data communication mechanism. This dilemma is a recurring feature in real-time systems research, and features for different components of the real-time compute stack of which shared data communication mechanism is one component. Prior research works that addressed this dilemma for different components of the real-time compute stack espoused one of the following two design philosophies:

1. **Predictable Computer Architecture Design:** Research works that followed this design philosophy argued that the micro-architecture of compute platforms used in real-time systems must be designed with timing predictability as a first class design principle [15, 33, 56, 63, 65, 67, 78, 88, 91, 109, 118, 126, 128, 131, 150]. These works followed one of two approaches: (1) design the entire compute stack (micro-architecture, instruction set architecture, and associated compiler framework) from ground up with predictability in mind [33, 88, 109, 126, 128] (*complete approach*) or (2) analyze the predictability guarantees of a particular computer architecture component such as caches and memory con-

trollers present in COTS multi-core platforms and design extensions to improve their predictability [15, 56, 63, 65, 67, 78, 91, 131, 150] (*compositional approach*).

2. **Predictable Software Runtime Design:** Research works that followed this design philosophy argued that COTS multi-core platforms will continue to exhibit low predictability as compute platform vendors will most likely optimize for high-performance due to market factors. Therefore, it is the responsibility of the software (application or RTOS) to guarantee predictability [14, 23, 25, 47, 50, 52, 61, 79, 80, 84, 86, 99, 111, 141].

State-of-the-art predictable shared data communication mechanisms described in the previous section (Section 1.3.1) espoused the second design philosophy. In this thesis, we adopt the first design philosophy and propose *hardware-based* shared data communication mechanisms to achieve predictable and high-performance shared data communication. Therefore, the research contributions of this thesis fall under the *predictable computer architecture design philosophy*. Our motivation for choosing this design philosophy is based on the observation that software approaches to predictable shared data communication such as cache bypassing and task mapping have reached a *ceiling* on their performance returns. This is because, these approaches have *limited visibility* of the underlying micro-architecture and hence, wield *limited control* on the performance and predictability trade-offs. As a result, it is highly unlikely that newer communication mechanisms that follow the same design philosophy will observe significant performance returns above this performance ceiling.

On the other hand, predictable computer architecture design allows for *finer control* of the predictability and performance trade-offs through micro-architectural changes. Hence, a shared data communication mechanism designed by making *performance-preserving predictable* micro-architectural changes to an existing hardware-based shared data communication mechanism can achieve better performance compared to state-of-the-art approaches while guaranteeing predictability. This leads to the following research question that this thesis is concerned with:

Thesis question: Is it possible to design a hardware-based predictable shared data communication mechanism such that its average-case performance guarantees go beyond the performance ceiling of state-of-the-art predictable shared data communication mechanisms?

The approach taken in this thesis proposes micro-architectural changes to *hardware cache coherence mechanisms*, which are existing data communication mechanisms in COTS multi-core platforms. The research contributions presented in this thesis answer the above proposed research question in the affirmative.

#### **1.3.3** Our Approach: Predictable and High-Performance Shared Data Communication through *Hardware Cache Coherence*