# a-Si:H-Silicon Hybrid Low Energy X-ray Detector

by

Kyung-Wook Shin

A thesis

presented to the University of Waterloo

in fulfillment of the

thesis requirement for the degree of

Doctor of Philosophy

in

**Electrical and Computer Engineering**

Waterloo, Ontario, Canada, 2014

©Kyung-Wook Shin 2014

#### **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I understand that my thesis may be made electronically available to the public.

#### **Abstract**

Low energy X-ray (< 20 keV) detection is a key technological requirement in applications such as protein crystallography or diffraction imaging. Silicon based optical cameras based on CCDs or CMOS imaging chips coupled to X-ray conversion scintillators have become a mainstay in the field. They are attractive because of fast readout capability and ease of integrated circuit implementation due to modern semiconductor fabrication technology. More recently, hydrogenated amorphous silicon (a-Si:H) thin film technology, that had enabled a huge influx of large area display products into the commercial display market, has been introduced to digital imaging in the form of active matrix flat panel imagers (AMFPIs). Although thin film technology can enable large area X-ray imaging at a potentially lower cost, the existing technology lacks spatial resolution requirements for higher performance crystallography and diffraction imaging applications.

This work introduces a high resolution direct conversion silicon X-ray detector integrated with large area thin film silicon technology for sub-20 keV photon X-ray imagers. A prototype pixel was fabricated in-house using a fabrication facility (G2N) utilizing plasma enhanced chemical vapor deposition (PECVD), reactive ion etching (RIE), photo-lithography, and metal sputtering technologies. Unlike most active matrix display products, top-gate staggered a-Si:H thin film transistor (TFT) were implemented to take advantage of a novel thin film silicon pixel amplification device architecture.

The detector performance was evaluated with an iron 55 isotope gamma ray source to mimic low energy X-ray exposure. I-V and C-V measurement techniques indicate that the hybrid pixel functions as expected and is promising for low cost, high resolution, large area X-ray imaging (< 20 keV) applications. We also performed a noise spectrum investigation to estimate the lowest detection signal level limit and proposed a model rooted in device physics for the pixel output and gain.

# **Acknowledgements**

Prof. Kai Wang and Dr. Czang-Ho Lee's help was essential to the detector fabrication process and process optimization. Also, I would like to thank Dr. Umar Shafique for his support on wire bonding and setting up the noise test environment. I also extend thanks to Dr. Tasreen Charania for considerable assistance in proof-reading the thesis for grammatical correctness and consistency.

Lastly, I would like to thank Prof. Karim S. Karim as my supervisor and everlasting supporter since my roommate committed suicide in 2010.

# **Dedication**

To my mother and my sister.

# **Table of Contents**

| AUTHOR'S DECLARATION                                 | ii  |

|------------------------------------------------------|-----|

| Abstract                                             | iii |

| Acknowledgements                                     | iv  |

| Dedication                                           | v   |

| Table of Contents                                    | vi  |

| List of Figures                                      | ix  |

| List of Tables                                       | xii |

| Chapter 1 Introduction                               | 1   |

| 1.1 Digital X-ray Imaging                            | 1   |

| 1.2 Detector Technologies                            | 1   |

| 1.2.1 Direct Conversion X-ray Detectors              | 1   |

| 1.2.2 Indirect Conversion X-ray Detectors            | 3   |

| 1.2.3 Large Area Thin Film Silicon X-ray Detectors   | 4   |

| 1.3 Protein Crystallography                          | 5   |

| 1.3.1 Overview                                       | 5   |

| 1.3.2 Requirement of digital protein crystallography | 7   |

| 1.4 Motivation and Chapter Outlines                  | 8   |

| Chapter 2 Hybrid Detector Operation Schema           | 12  |

| 2.1 Thin Film Transistors                            | 12  |

| 2.1.1 Hydrogenated Amorphous Silicon (a-Si:H)        | 12  |

| 2.1.2 TFT Structures                                 | 14  |

| 2.1.3 a-Si:H TFT Operation Physics                   | 16  |

| 2.2 Direct Contact Detector                          | 20  |

| 2.2.1 Operation Principle                            | 20  |

| 2.3 Silicon Dioxide Passivated Detector              | 22  |

| 2.3.1 Energy Distribution Investigation with TCAD    | 24  |

| 2.3.2 Readout and In-pixel Amplification             | 25  |

| Chapter 3 Detector Fabrication                       | 29  |

| 3.1 Overview                                         |     |

| 3.2 Plasma Enhanced Chemical Vapor Deposition        | 31  |

| 3.3 Film Characterization                            | 34  |

| 3.3.1 Gate Dielectric                             | 34 |

|---------------------------------------------------|----|

| 3.3.2 n+ Contact Layer                            | 38 |

| 3.3.3 Thermal Oxide                               | 41 |

| 3.4 Direct Contact Detector Process               | 43 |

| 3.4.1 Mask 1                                      | 43 |

| 3.4.2 Mask 2                                      | 46 |

| 3.4.3 Bulk Electrode                              | 49 |

| 3.5 Silicon Dioxide Passivated Detector Process   | 49 |

| 3.5.1 Thermal Oxide Etch                          | 49 |

| 3.5.2 Mask 1                                      | 50 |

| 3.5.3 Mask 2                                      | 53 |

| Chapter 4 Detector Performance                    | 57 |

| 4.1 TFT Performance.                              | 57 |

| 4.1.1 Transfer and Output Characteristics         | 57 |

| 4.1.2 Metastability                               | 62 |

| 4.1.3 Time Domain Analysis                        | 63 |

| 4.2 Iron 55 Isotope Response                      | 65 |

| 4.3 Detector Noise Investigation                  | 69 |

| 4.3.1 Noise Test Set Up                           | 69 |

| 4.3.2 Flicker Noise Investigation (Detector Size) | 73 |

| 4.3.3 Shot Noise Investigation (Bulk Bias)        | 74 |

| 4.3.4 Total Noise Estimation                      |    |

| 4.4 X-ray Sensitivity                             | 79 |

| 4.4.1 X-ray Absorption Investigation              | 79 |

| 4.4.2 EHP Conversion and Signal Amplification     | 82 |

| 4.5 Closing The Loop                              | 87 |

| Chapter 5 Conclusions                             | 89 |

| 5.1 Summary and Conclusion                        | 89 |

| 5.2 Further Improvements                          | 90 |

| 5.3 Academic Contributions                        | 91 |

| Appendices                                        | 92 |

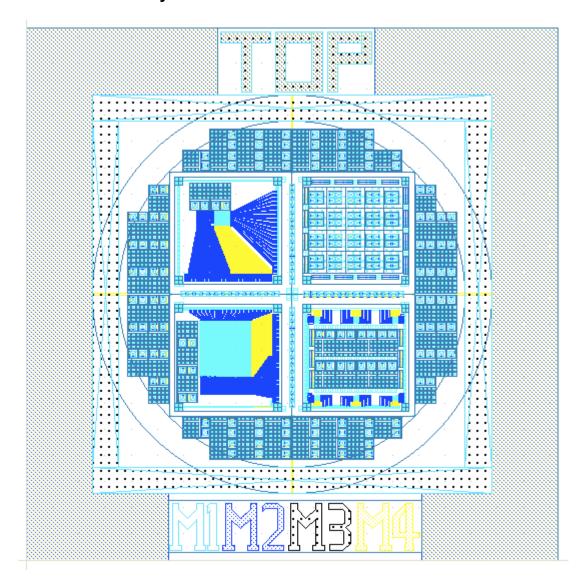

| Appendix A Hybrid Detector Mask Layout            | 93 |

| Appendix B TCAD Input Deck                                   | 96    |

|--------------------------------------------------------------|-------|

| Appendix C OpenGateCollabration Monte Carlo Simulation Macro | . 107 |

| Bibliography                                                 | .112  |

# **List of Figures**

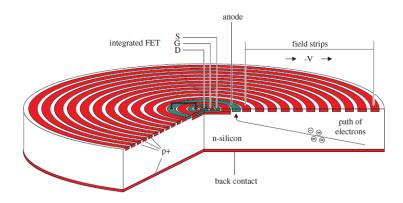

| Figure 1 A silicon drift detector example [10].                                                               | 2       |

|---------------------------------------------------------------------------------------------------------------|---------|

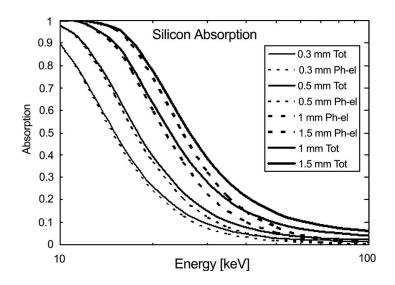

| Figure 2 X-ray absorption in silicon adopted from [11]                                                        | 2       |

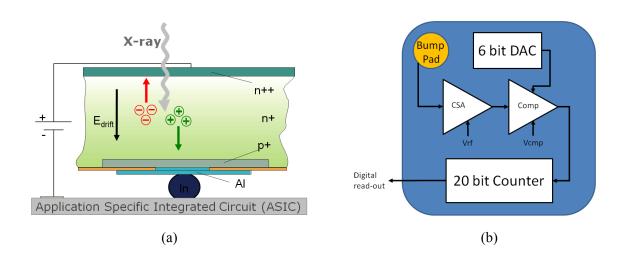

| Figure 3 Schematic of Pilatus from Dectris <sup>TM</sup> . (a) shows the hybrid pixel with silicon detector a | nd (b)  |

| shows photon counting circuit ASIC diagram attached to each pixel. Adopted from [12]                          | 3       |

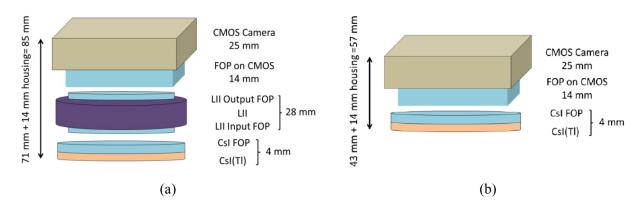

| Figure 4 (a) CCD detector and (b) CMOS detector schematics. Adopted from [15]                                 | 4       |

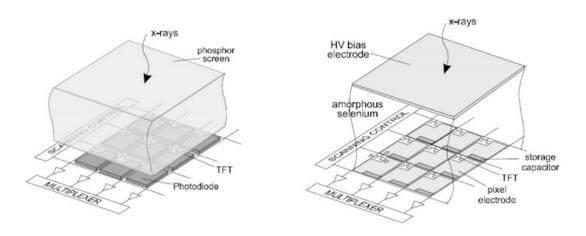

| Figure 5 Two types of AMFPI detectors. Indirect (Left) and Direct (Right.) Adopted from [17].                 | 5       |

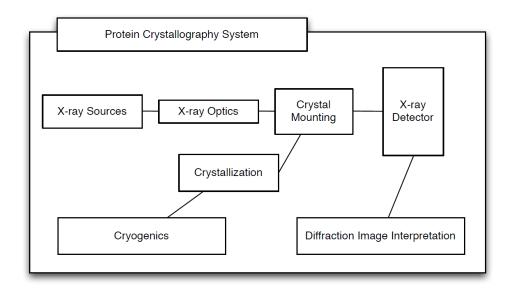

| Figure 6 Core components of protein crystallography.                                                          | 6       |

| Figure 7 Typical protein crystallography set up. Adopted from [20]                                            | 6       |

| Figure 8 Two dimensional illustrations on atomic bonding for (a) amorphous silicon and (b)                    |         |

| crystalline silicon.                                                                                          | 12      |

| Figure 9 Typical distribution of density of states in hydrogenated amorphous silicon                          | 13      |

| Figure 10 Four types of a-Si:H TFT structures.                                                                | 15      |

| Figure 11 Illustration of top gate staggered thin film transistor.                                            | 16      |

| Figure 12 One-dimensional illustration of electron conduction in a-Si:H.                                      | 17      |

| Figure 13 A typical I-V curve of an a-Si:H TFT.                                                               | 18      |

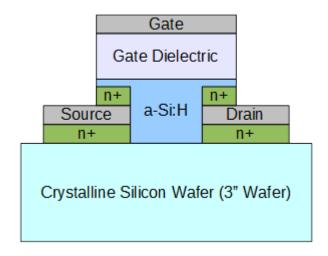

| Figure 14 Schematic of a-Si:H-silicon direct contact detector.                                                | 20      |

| Figure 15 Quasi-Fermi level distribution in the crystalline silicon substrate. The dotted line indi           | cates   |

| a-Si:H TFT-crystalline silicon interface.                                                                     | 21      |

| Figure 16 Revised hybrid detector with silicon dioxide blocking layer                                         | 22      |

| Figure 17 Quasi-Fermi level distribution in the silicon substrate.                                            | 23      |

| Figure 18 (a) Energy distribution in the direct contact detector (in the crystalline silicon substrates)      | te) and |

| (b) hole concentration under back to back bias condition.                                                     | 24      |

| Figure 19 (a) Energy distribution in the silicon dioxide passivated detector (in the crystalline sil          | icon    |

| substrate) and (b) hole concentration under back to back condition.                                           | 24      |

| Figure 20 Expected implementation of the hybrid detector readout.                                             | 26      |

| Figure 21 Array readout scheme of the 1T-APS pixel for the hybrid detector.                                   | 27      |

| Figure 22 Schematic of the MVSystems multi-chamber PECVD system.                                              | 29      |

| Figure 23 Temperature calibration data of the in-house cluster tool [39].                                     | 30      |

| Figure 24 Schematic diagram of a typical RF-PECVD reactor.                                                    | 32      |

| Figure 25 Static current-voltage (I-V) characteristics of a plasma (adopted from[40].)                        | 32      |

| Figure 26 Time-average potential distribution in a plasma reactor (modified from [40, 42].)                   | 33      |

| Figure 27 MIS a-SiN <sub>x</sub> :H characterization sample cross-section.                        | 35 |

|---------------------------------------------------------------------------------------------------|----|

| Figure 28 (a) I-V and (b) C-V characteristics of a-SiNx:H prepared by cluster tool PL4 chamber.   | 36 |

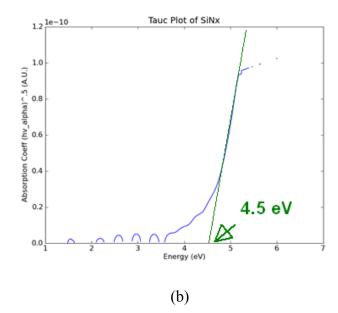

| Figure 29 (a) UV spectra and (b) bandgap estimation via Tauc plot method.                         | 38 |

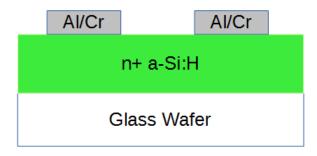

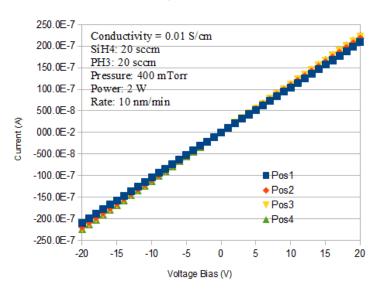

| Figure 30 Lateral sample for contact layer conductivity extraction.                               | 39 |

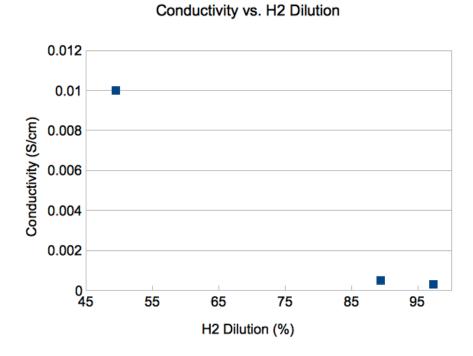

| Figure 31 Ohmic contact of n+ a-Si:H contact layer deposited with 49.5 % of hydrogen dilution     | 40 |

| Figure 32 Conductivity comparison of various hydrogen dilution conditions.                        | 41 |

| Figure 33 Passivation silicon dioxide I-V test set up. The MIS structure was biased with vertical |    |

| electric field                                                                                    | 42 |

| Figure 34 MIS test result of thermal silicon dioxide.                                             | 42 |

| Figure 35 Contact layers deposited on top of an RCA1 and RCA2 cleaned silicon wafer               | 43 |

| Figure 36 Patterned by mask 1 to form source and drain contacts.                                  | 44 |

| Figure 37 Bilayer deposition with sputtered gate electrode                                        | 47 |

| Figure 38 Patterned by mask 2, forming the gate electrode                                         | 47 |

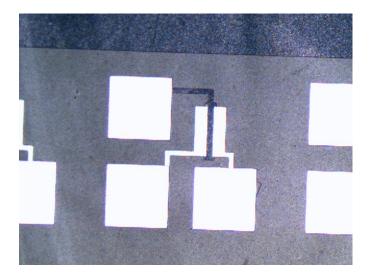

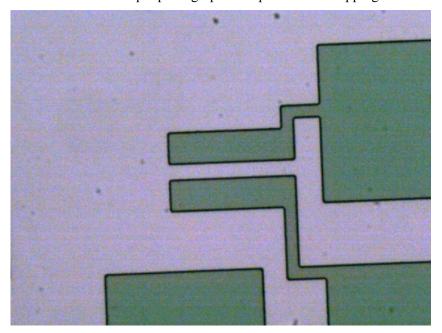

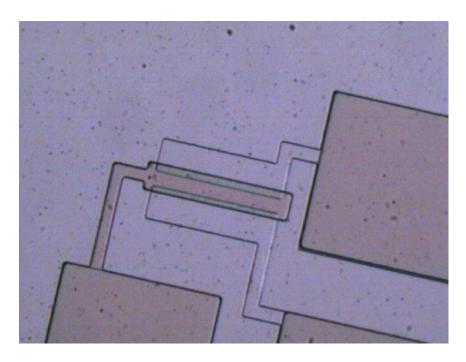

| Figure 39 Microscope snapshot of in-house fabricated direct contact detector                      | 48 |

| Figure 40 Completed hybrid detector device after bulk electrode deposition.                       | 49 |

| Figure 41 RCA1 cleaned and back side etched with AZ3312 photoresist protection at the top side    | 50 |

| Figure 42 Source-drain contact layer deposition.                                                  | 50 |

| Figure 43 Photoresist developed on top of the source-drain films.                                 | 51 |

| Figure 44 Patterned with source and drain pattern mask (mask 1.)                                  | 52 |

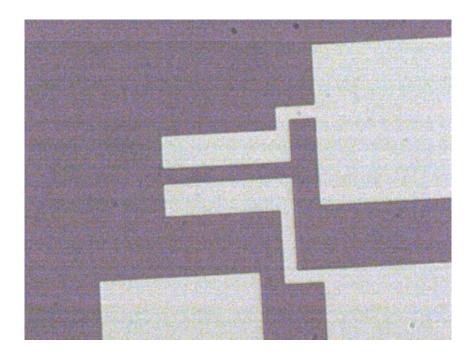

| Figure 45 Wafer snapshot after photoresist strip.                                                 | 52 |

| Figure 46 Bilayer and gate electrode deposition                                                   | 53 |

| Figure 47 Wafer snapshot of photoresist pattern for mask 2, before etch process.                  | 54 |

| Figure 48 Finished TFT on thermal oxide after Mask 2 etch.                                        | 54 |

| Figure 49 PR stripped after mask 2 etch processes.                                                | 55 |

| Figure 50 Bulk electrode deposition: finished device.                                             | 55 |

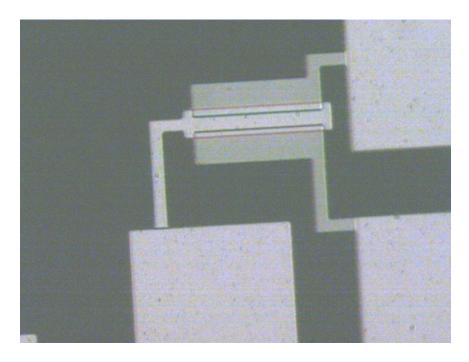

| Figure 51Thermal oxide passivated detector after bulk electrode deposition.                       | 56 |

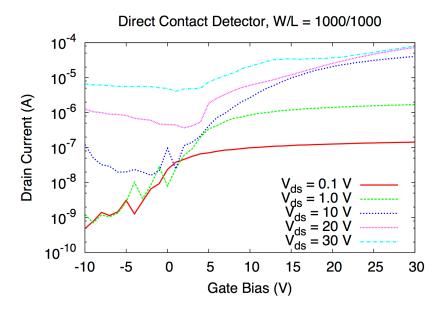

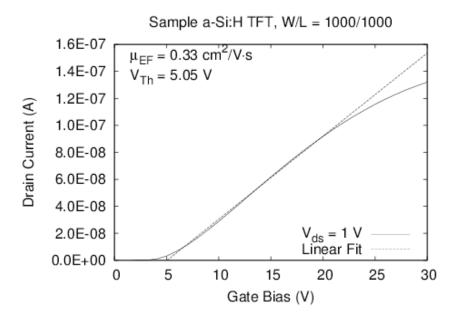

| Figure 52 Transfer characteristics of direct contact detector.                                    | 58 |

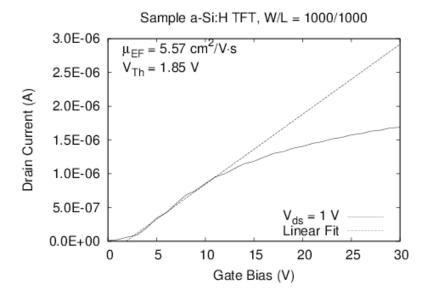

| Figure 53 Field effect mobility and threshold voltage extraction of direct contact detector       | 58 |

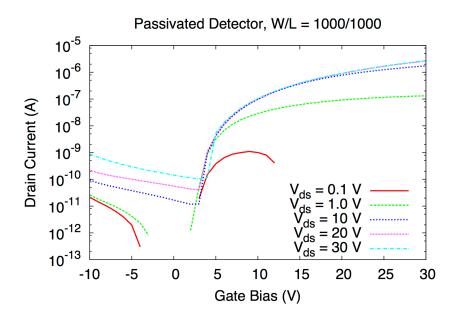

| Figure 54 Transfer characteristics of passivated detector.                                        | 59 |

| Figure 55 Field effect mobility and threshold voltage extraction of passivated detector           | 60 |

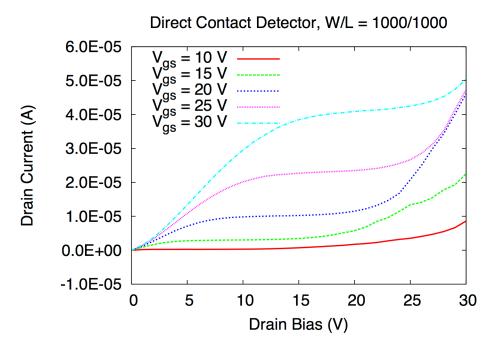

| Figure 56 Output characteristics of direct contact detector.                                      | 61 |

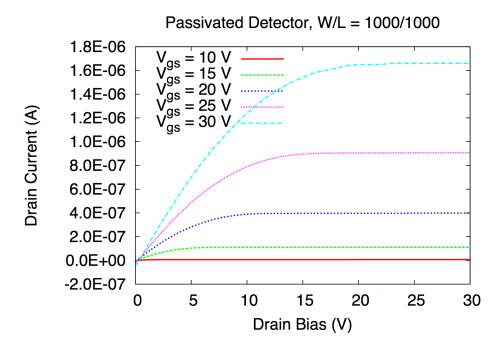

| Figure 57 Output characteristics of passivated detector.                                          | 61 |

|                                                                                                   |    |

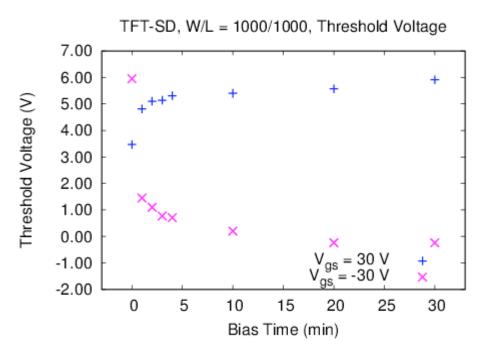

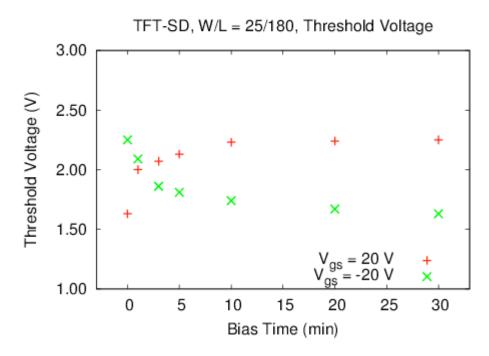

| Figure 58 Threshold voltage shift of direct contact detector with 10 V of drain bias                   | 62  |

|--------------------------------------------------------------------------------------------------------|-----|

| Figure 59 Threshold voltage shift of passivated detector, obtained with 1 V of drain bias              | 63  |

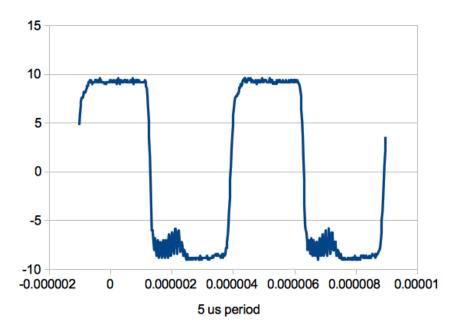

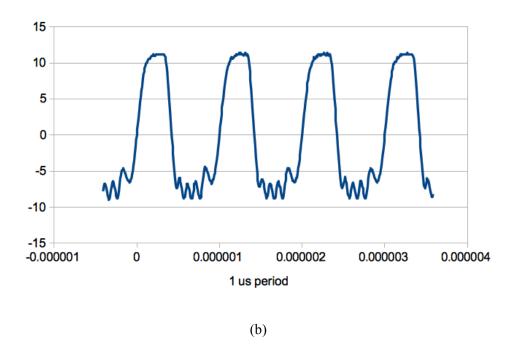

| Figure 60 Time domain measurement set up for readout TFTs in passivated detector. The bulk dic         | ode |

| bias was grounded.                                                                                     | 63  |

| Figure 61 Time domain response of a hybrid detector under the bias of 20 V square pulse gate bia       | .S  |

| and 1.35 V of drain bias.                                                                              | 65  |

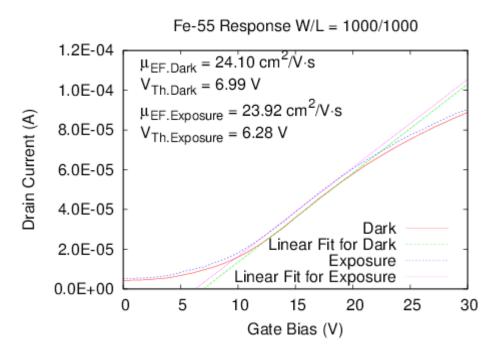

| Figure 62 Iron-55 isotope exposure set up for hybrid detectors.                                        | 66  |

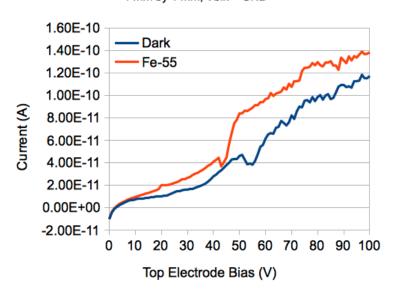

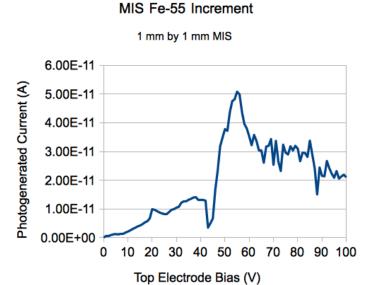

| Figure 63 Iron-55 isotope exposure comparison for direct contact detector.                             | 67  |

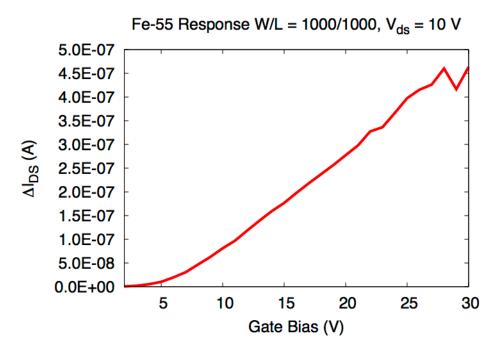

| Figure 64 Iron-55 isotope exposure result for 1 mm by 1 mm passivated hybrid detector                  | 67  |

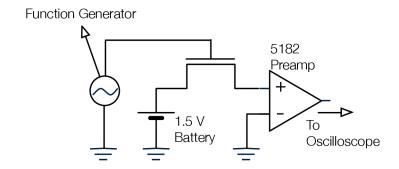

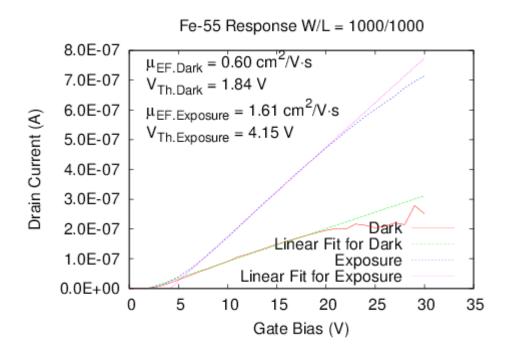

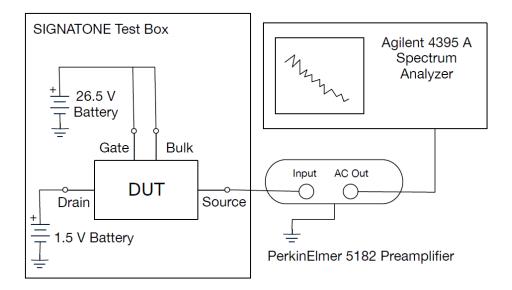

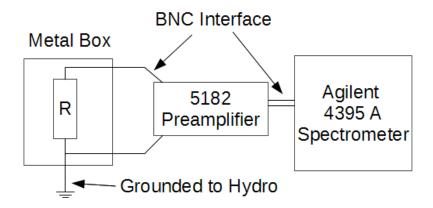

| Figure 65 Noise test set up diagram for hybrid detector. External biases for the detector and          |     |

| preamplifier were provided with battery.                                                               | 69  |

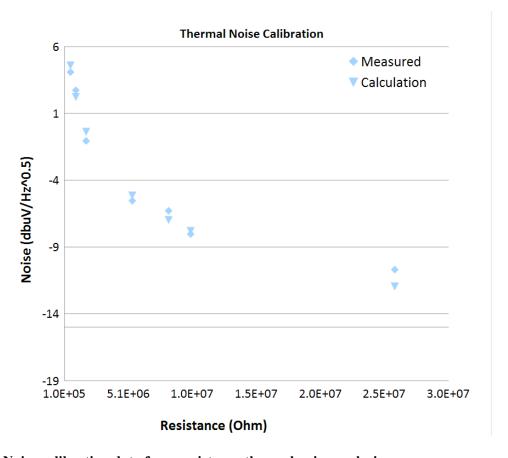

| Figure 66 Noise calibration data from resistance thermal noise analysis.                               | 70  |

| Figure 67 Noise measurement calibration set up. Thermal no                                             | 71  |

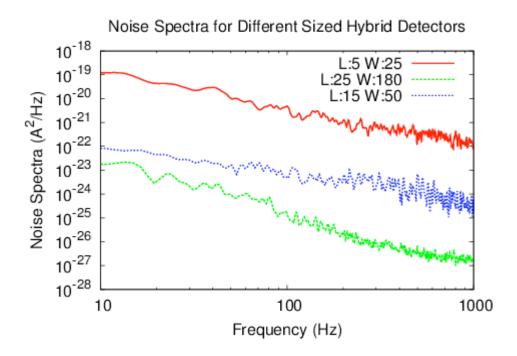

| Figure 68 Noise power density spectra for various sized passivated detectors. Bulk bias was            |     |

| maintained at 0 V                                                                                      | 73  |

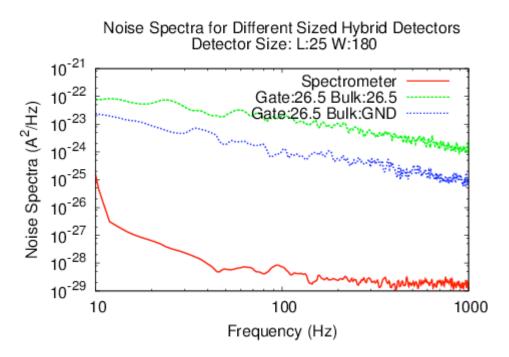

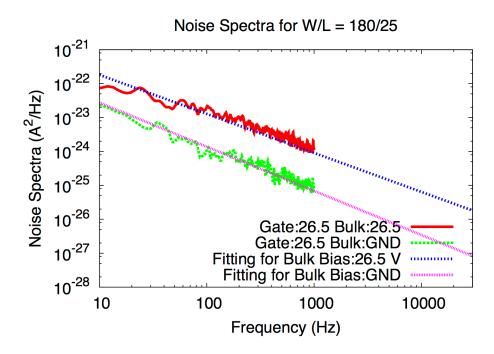

| Figure 69 Noise power density spectra for passivated detector on bulk bias and without bulk bias       |     |

| conditions.                                                                                            | 75  |

| Figure 70 Square root fitting for the noise spectra of 25 by 180 (μm/μm) pixel up to 30 kHz            | 76  |

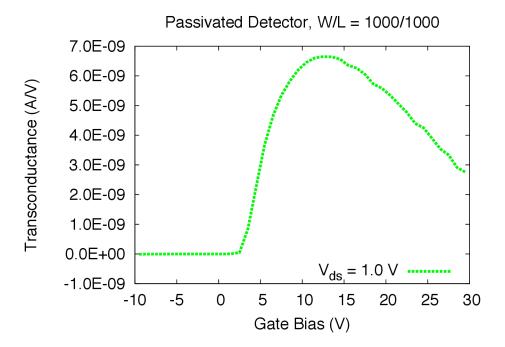

| Figure 71 Transconductance curve of 1 mm by 1 mm pixel at drain bias of 1.0 V.                         | 77  |

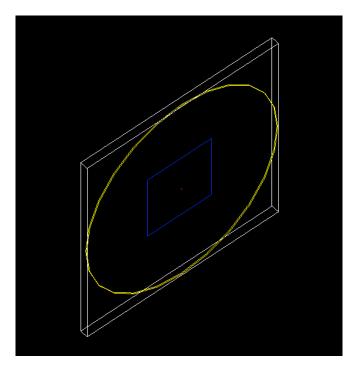

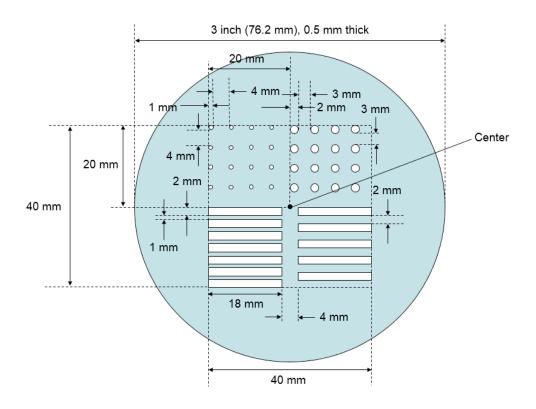

| Figure 72 Monte-Carlo simulation system set up to depict the X-ray exposure from iron-55 isotop        | e.  |

| The yellow ring is the 3" wafer, the blue square is the 1" by 1" isotope, and the small red dot is the | e   |

| detector pixel area                                                                                    | 80  |

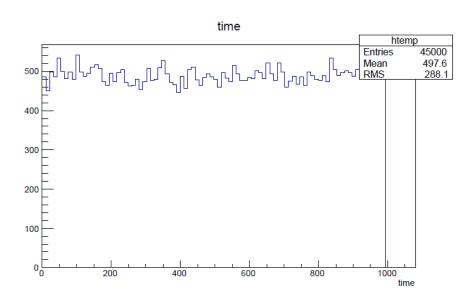

| Figure 73 X-ray photon absorption counts for 1000 seconds of operation.                                | 80  |

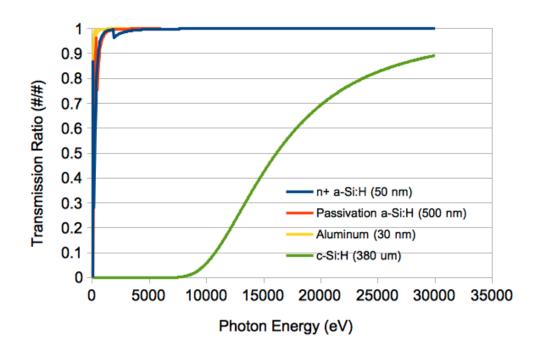

| Figure 74 Photon transmission ratio for various materials. Obtained from [77]                          | 81  |

| Figure 75 MIS structure setup for iron-55 isotope photo-generation evaluation.                         | 82  |

| Figure 76 MIS structure I-V test result.                                                               | 83  |

| Figure 77 Current increment from the MIS exposure results.                                             | 83  |

| Figure 78 Drain current increment from X-ray (iron-55) detection.                                      | 84  |

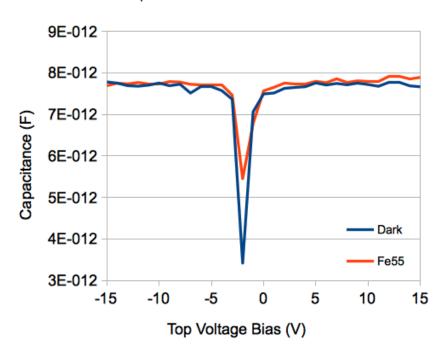

| Figure 79 Capacitance sweep of the passivated detector.                                                | 85  |

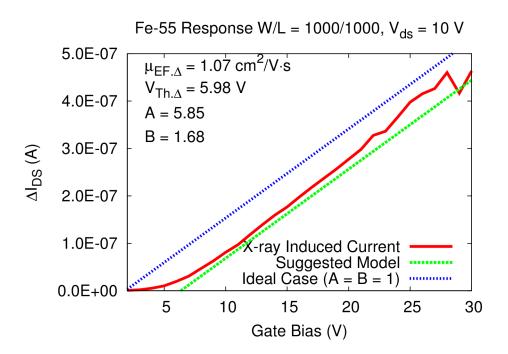

| Figure 80 Comparison of suggested model and extracted data.                                            | 86  |

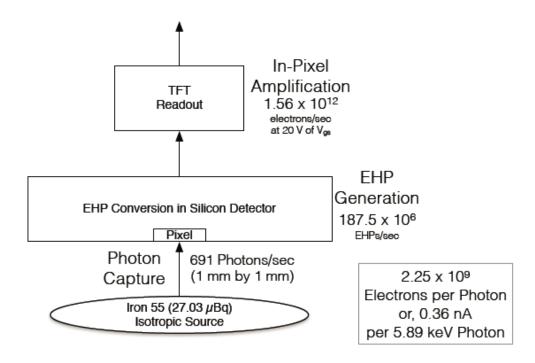

| Figure 81 Determining the number of electrons generated per absorbed photon.                           | 87  |

# **List of Tables**

| Table 1 Requirement of digital protein crystallography detectors                              | 8      |

|-----------------------------------------------------------------------------------------------|--------|

| Table 2 Comparison of various X-ray detectors for low energy (~ 6 keV) X-ray photon detection | ion 11 |

| Table 3 Hybrid detector readout schema.                                                       | 26     |

| Table 4 Chamber assignment of in-house cluster PECVD facility                                 | 30     |

| Table 5 Effect of PECVD parameters.                                                           | 34     |

| Table 6 Recipe table for a-SiNx:H gate dielectric, PL4.                                       | 36     |

| Table 7 PECVD condition for three different contact layer samples.                            | 39     |

| Table 8 Sputtering condition for Edwards sputtering system.                                   | 44     |

| Table 9 MA6 mask aligner UV exposure condition for AZ3312 photoresist                         | 45     |

| Table 10 AZ3312 spin coating and curing conditions for mask patterning.                       | 45     |

| Table 11 RIE process condition for contact layers.                                            | 45     |

| Table 12 a-Si:H channel layer PECVD condition for PL2 chamber.                                | 46     |

| Table 13 RIE process condition for bi-layer etch.                                             | 48     |

| Table 14 Spin coating condition for AZ3312 photoresist to withstand 10 % BHF solution         | 50     |

| Table 15 Thermal noise calibration table.                                                     | 71     |

| Table 16 Thermal noise of various sized detectors.                                            | 72     |

| Table 17 Detector performance comparison with the original expectation.                       | 78     |

| Table 18 5.89 keV X-ray transmission ratio information for bulk electrode penetration         | 81     |

### **Chapter 1**

#### Introduction

#### 1.1 Digital X-ray Imaging

Since the discovery of X-ray by German physicist, W. K. Roentgen in 1895-6, capturing X-ray intensity information has been performed by various types of phosphors including CsI:Ti, Gd<sub>2</sub>O<sub>2</sub>S, LaOBr, or Y<sub>2</sub>O<sub>2</sub>S:Tb and transferred to a photographic films with optical cameras. However, these methods suffered from the following difficulties:

- Lack of data storage and prompt retrieval

- Inability to perform image processing on raw data directly

- Captured images required a multi-step lossy process to transfer

- Chemical waste problems with film developing and associated environmental concerns

- Real-time imaging was not feasible with static images

To address these problems, X-rays went digital starting in the 1960s in the nondestructive testing equipment industry [1]. Later, digitization of X-ray imaging utilized charge-coupled devices (CCD) interfaced to scintillators where the scintillator converted the X-rays into optical signals that were subsequently imaged by a silicon CCD chip [2, 3].

#### 1.2 Detector Technologies

#### 1.2.1 Direct Conversion X-ray Detectors

Direct conversion semiconductor radiation (X-ray, gamma-ray, etc.) sensors saw widespread use in medical, scientific, and industrial systems due to their higher resolution, high sensitivity and fast readout speed. Direct conversion systems eliminated the X-ray to light conversion step enabling higher resolution than their indirect scintillator based X-ray imager counterparts. This enabled a manufacturing cost reduction as well because both expensive scintillators and fiber optics to couple the scintillator to the CCD chip were eliminated. One of the prominent examples of a direct conversion semiconductor X-ray detector is the silicon drift detector (SDD) [4-6] shown in Figure 1.

Due to the relatively low bandgap (1.1 eV) of silicon, X-ray absorption performance of silicon is limited to low energy photons (< 20 keV) as is the case for protein crystallography (as depicted in Figure

2), X-ray spectroscopy [7], medical imaging [8], and archeology [5]. SDD enabled such applications with lower cost, lack of liquid nitrogen cooling, small number of readout channels, low noise, and high readout energy resolution [9].

Figure 1 A silicon drift detector example [10].

Figure 2 X-ray absorption in silicon adopted from [11].

Another more recent example of the use of direct conversion silicon for X-ray imaging is the Pilatus detector from Dectris<sup>TM</sup>. This detector is composed of silicon X-ray detector components bump bonded to a very high performance ASIC photon counting circuit as depicted in Figure 3. The readout time for each pixel is reported to be as low as 7 ms (or alternately, a frame rate of 20 images per second) while the minimum capacitance of the photon detector silicon element is kept low to effectively reduce detector

noise. Since the silicon detector thickness defines the detector capacitance and also the maximum photon detection energy, Pilatus is sold with an option to obtain a silicon semiconductor thickness of 320, 450, or  $1000 \mu m$ . Its resolution is reported to reach 487 by 197 pixels with an active area of 83.8 by 33.5 mm<sup>2</sup> implying a pixel pitch of  $170 \times 170 \mu m^2$  while maintaining the dynamic range of 20 bits, or 1:1048573 [12]. The pixel pitch is presumably large due to the complex circuitry needed for photon counting.

Figure 3 Schematic of Pilatus from Dectris<sup>TM</sup>. (a) shows the hybrid pixel with silicon detector and (b) shows photon counting circuit ASIC diagram attached to each pixel. Adopted from [12].

#### 1.2.2 Indirect Conversion X-ray Detectors

In contrast to higher performance direct conversion detectors, the method by which X-rays are detected via scintillators is known as indirect conversion imaging since the conversion of X-ray signal to electronic charge involves an intermediate light conversion step in the scintillator. CCD or CMOS digital cameras are commonly used to interface to the scintillator to capture the light photons, however, it is not possible to efficiently capture small quantities of X-ray photons without the use of fiber optics, as depicted in Figure 4 (a) because of large optical losses (for example, if traditional lens based methods are used). A disadvantage of using a CCD camera for image capture is that CCDs can have a lower dynamic range due to the shallow well associated with the MOS capacitor in deep depletion [13, 14]. CMOS imagers, as depicted in Figure 4 (b), utilize silicon photodiodes which provides larger dynamic ranges up to 130,000 even for pixel sizes of  $25 \times 25 \,\mu m$  while maintaining a readout speed of 30 frames per second [15].

Detector sizes of up to 20 cm by 20 cm of area can be achieved using both CCDs with optical fiber enhancements as well as using their CMOS counterparts. However, the price range of a scintillator, fiber optic coupling and CMOS backplane is somewhat larger compared to the price of TFT flat panel arrays. More importantly, a scintillator emits the converted photons without any particular direction and causes image blurring. In other words, converted photons may travel to adjacent pixel to generate a false signal. Even if a structured scintillator is used, the image blurring is larger than when direct conversion X-ray imagers are employed.

Figure 4 (a) CCD detector and (b) CMOS detector schematics. Adopted from [15].

#### 1.2.3 Large Area Thin Film Silicon X-ray Detectors

The introduction of hydrogenated amorphous silicon (a-Si:H) thin film transistors (TFTs) opened up an opportunity for large area and low cost detectors driven by active matrix pixel driving technology [13]. The active matrix flat panel imager (AMFPI) was also introduced with a phosphor integrated detector, which reads out optically converted X-rays with photodiodes (indirect conversion) and a direct conversion method with amorphous selenium (a-Se), which converts the X-ray directly into electron-hole pairs to be read out by TFTs in the active matrix backplane as depicted in Figure 5.

Although TFT active matrix technology introduced a cost-effective readout for large area applications, AMFPI still requires pricy X-ray conversion layers: scintillators and fiber optic plates for the indirect conversion scheme, and a high quality a-Se layer for the direct conversion method. Also, integration of an additional photodiode in the indirect conversion scheme requires additional process steps, which amplifies production cost. On the other hand, the direct conversion method suffers from reliability issues primarily

the crystallization of the a-Se layer, which leads to an extreme dark current (noise), and extreme care is required to prevent exposure from excessive heat and photons [16].

Figure 5 Two types of AMFPI detectors. Indirect (Left) and Direct (Right.) Adopted from [17].

#### 1.3 Protein Crystallography

#### 1.3.1 Overview

One of prime example of low energy (sub 20 keV) X-ray applications is protein crystallography, which plays a great role in molecular biology and pharmaceutical research [18]. So-called molecular medicine research requires investigation of molecule structures (3D structures of protein molecules) because the structure defines the function and characteristic of the molecule and provides insight to negate the functionality of any disease protein.

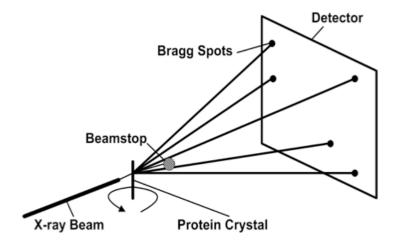

The basic set up of protein crystallography is shown in Figure 7. To prepare the crystallized sample, the protein must be frozen using cryogenics technology. Meanwhile the X-ray beam must be narrowed with optical elements and the direct path to the detector needs to be blocked to ensure only diffracted spots are detected. Thus, the crystallography system includes not only X-ray sources and detector elements, but also optics for X-ray, cryogenics, and crystal mounting apparatus, as depicted in Figure 6.

From a computational viewpoint, the X-ray beam must be monochromic to ensure protein structure reconstruction because diffracted spots (Bragg spots) change as a function of X-ray wavelength and protein structure. Typically, 6 to 20 keV photons (or a wavelength of 0.21 to 0.06 nm) are chosen which is close to the atomic distance of common protein target molecules. To obtain a complete 3D reconstructed image,

the Bragg spots must be obtained from various incident angles. So, the protein sample needs to be turned along the x, y, and z axes [19].

Figure 6 Core components of protein crystallography.

Figure 7 Typical protein crystallography set up. Adopted from [20].

#### 1.3.2 Requirement of digital protein crystallography

At first glance, the size of the detector appears a key requirement for protein crystallography since in the ideal case, the detector must be large enough to capture all Bragg spots effectively [19]. However, collecting the complete set of Bragg spots is not required because the first 100 orders of diffraction data are enough to rebuild the crystalline structure of sample protein. Usually, a detector size of 20 cm by 20 cm is sufficient to cover the first 100 orders [21]. Of course, the imager size depends on the distance from the crystallized protein proportionally. If the detector has sufficiently high resolution, the detector size can be shrunk by closing the gap between the protein sample and the detector itself reducing the requirement on the X-ray source power.

In some applications, the strongest Bragg spots can be as high as  $1.2 \times 10^5$  X-ray photons per pixel, while non-exposed pixels show almost zero counts as the Bragg spot distribution follows a Gaussian function [22]. Since only 0.1 % of the incident X-ray beam is scattered by the protein and prolonged exposure to X-ray is not preferable due to protein structure degradation, possible solutions are either reducing the intensity of the X-ray beam or to implement a fast readout. Because a fast readout was not feasible with image plate detectors, which required more than 2 to 3 seconds per exposure, the sensitivity of the detector became important to compensate for the reduced X-ray source intensity. However, digital X-ray detectors (scintillator based and direct conversion) could resolve such problems without sacrificing sensitivity because of fast readouts.

The readout time depends on the kind of X-ray source used. Generally, two kinds X-ray sources are relevant to protein crystallography: rotating anode lower power home sources, which usually operate in the 6 to 10 keV range, and much higher power synchrotron sources, which have variable energy, but operate mostly at around 12 keV. For rotating anodes, longer signal charge integration (typically a few minutes [23]) is required compared to synchrotrons (a couple of seconds [23]) because the X-ray intensity is limited. Synchrotron provides a high intensity homogeneous beam, which produces more diffraction spots in a short time interval. The readout time includes the X-ray photon detection time and the detector element to external circuitry transfer time for converted charge.

The sharpness of the X-ray diffraction pattern depends on the spatial resolution of the detector as well as the distance from the protein. Normally, 3 to 5 pixels can hold a single Bragg spot while at least five pixels are required to distinguish between two adjacent Bragg spots [19]. For example, if a 12 keV X-ray photon (wavelength around 0.1 nm) illuminates a protein crystal with a unit cell dimension of 20 nm while crystal-to-detector distance is 20 cm, a typical Bragg spot size would be 100 to 300 µm. Thus,

requiring pixel sizes of 50 to 200 μm [19]. Table 1 shows one set of design consideration factors as applied to the existing, primarily indirect detection detectors.

Table 1 Requirement of digital protein crystallography detectors.

| Parameter     | Values                                            |

|---------------|---------------------------------------------------|

| Detector area | Larger than 20 cm by 20 cm                        |

| Dynamic range | Larger than 10 <sup>4</sup>                       |

| Readout time  | Around 1 second but smaller the better.           |

| Pixel size    | Smaller than 200 μm                               |

| X-ray energy  | 20 kVp (rotating anode) or 12 keV (synchrotron)   |

| Object size   | Around 0.18 nm (Inter-atomic distance of protein) |

#### 1.4 Motivation and Chapter Outlines

Direct conversion crystalline silicon layers have the best sensitivity and spatial resolution performance with X-ray photons < 20 keV. Crystalline silicon is one of most widely produced materials due to the emergence of the high volume semiconductor industry since 1980s. Thus, they can be provided with at a lower cost than a comparable scintillator and with much higher reliability than a direct conversion a-Se layers. Silicon wafers currently processed can reach up to 12" (or 300-mm-diameter) in size. If a silicon X-ray conversion layer can be integrated with large area low cost thin film silicon readout, a low cost, high resolution and high sensitivity solution can be realized for low energy X-ray detection applications such as protein crystallography.

Today, large area direct conversion silicon X-ray detectors are already in production but require a process of tiling and bump bonding, which is both expensive and poses yield issues when performed over a large area. Photon counting detectors for protein crystallography such as the Pilatus by Dectris<sup>TM</sup> employ small four side buttable silicon photon counting pixel arrays bump bonded to high resistivity silicon detectors with a selling price ranging from \$150k for a modest sized 1" square imager to around \$1M for full-sized large area devices.

In addition, indirect detection thin film amorphous silicon based digital X-ray devices using scintillators suffer from degraded spatial resolution due to the indirect conversion process as well as lower signal levels due to the reduced conversion gains of the scintillator at low energies (as compared to direct conversion crystalline silicon). Amorphous selenium based direct conversion devices integrated with amorphous silicon TFTs offer yet a third alternative that can offer a credible challenge to the higher spatial resolution of direct conversion silicon, however, the selenium detectors have lower conversion gains and are temperature sensitive leading to a tradeoff between manufacturing cost and reliability.

This work implements high resistivity crystalline silicon as a direct conversion X-ray to electron-hole pair converter. The resulting signal is read out using a low-cost, large area capable device: a-Si:H TFTs. Because it is not economical to deposit thick high quality crystalline silicon (where sufficient thickness is required to absorb most of the impinging X-rays) on top of typical TFT devices which are deposited on glass, we propose a novel approach where the a-Si:H TFT readout element is deposited on top of the detector element (crystalline silicon) In Table 2, the benefits of the proposed approach are contrasted with the approaches taken currently by various imager manufacturers operating in the protein crystallography markets. Note that the key advantage of our approach is that it offers the best spatial resolution while maintaining the same signal to noise ratio as its indirect detection CMOS and CCD counterparts. Thus, in principle, our detector could (1) be moved closer to the protein sample, thus enabling a reduction in the Xray source power necessary to get a quality image which would enable home X-ray sources to complete tasks that are normally the domain of synchrotron sources and (2) investigate new materials that require the higher spatial resolution because of unique molecular structures not visible using traditional imagers. Although the dynamic range of our detector is considerably lower than its counterparts, the smaller pixel size would see a reduced number of photons as compared to a larger sized pixel (assuming the photon fluence is the same for both designs). Here, a 25um pixel would see 64X less incident photons than a 200um pixel counterpart. Moreover, real-time readout can enable an artificial increase in dynamic range, for example, by constantly reading out the detector and summing the frames to obtain the final image.

In Chapter 2, following a brief introduction to thin film silicon transistor operation physics, the novel pixel architecture integrating a crystalline silicon detector with an a-Si:H TFT readout circuit is introduced along with its operation principle, basic device physics and initial simulation results. Two pixel device designs are discussed: one adapted from previous work and a new higher performance design involving a passivation layer to isolate the silicon X-ray conversion layer from the TFT. In chapter 3, following a brief introduction to TFT fabrication processes, the fabrication process developed for the two

pixel designs is presented. The development and characterization steps for each layer employed in the pixel design are discussed along with each process step and condition. In Chapter 4, measurements and discussion on multiple aspects of the pixel designs are provided. These range from basic device operation via I-V sweeps, thin film silicon metastability, and electronic noise characterizations. In addition, measurements on the pixel architecture using an iron 55 isotope source which emits 5.89 keV of energy X-ray photons were taken to verify that the device functions adequately for its intended use with X-rays. In Chapter 5, concluding remarks and the contributions of this work are summarized. The appendices contain fabrication process mask layouts and Medici code for the semiconductor device simulator.

Table 2 Comparison of various X-ray detectors for low energy (~ 6 keV) X-ray photon detection.

| Parameters                            | Pilatus                                        | Indirect CMOS                                | AMFPI a-Se              | a-Si:H-c-Si Hybrid<br>(Estimated)                  |

|---------------------------------------|------------------------------------------------|----------------------------------------------|-------------------------|----------------------------------------------------|

| Pixel Size                            | 170 μm<br>(down to 75 μm)                      | 50 μm<br>(Indirect)                          | 70 μm                   | 25 μm<br>(direct)                                  |

| Detector Size                         | $83.8 \times 33.5 \ mm^2$ (four side tileable) | $75 \times 150 \ mm^2$ (three side tileable) | $430 \times 350 \ mm^2$ | $212 \times 212 \ mm^2$ (Square area of 12" Wafer) |

| EHP conversion $(6~keV/W_{\pm})$      | 1667<br>(c-Si)                                 | 167<br>(CsI:Ti)                              | 125<br>(a-Se)           | 1667<br>(c-Si)                                     |

| Readout<br>Noise                      | Negligible                                     | < 150 electrons                              | < 1500 electrons        | < 1500 electrons                                   |

| SNR                                   | Photon counting                                | ~1                                           | 0.08                    | ~ 1                                                |

| Dynamic<br>Range<br>(6keV<br>photons) | 1:1,048,573                                    | 1:61,750<br>(0.5 pF cap)                     | 1:120,000<br>(1 pF cap) | 1:3600<br>(0.03 pF cap)                            |

| Readout<br>Speed                      | 20 FPS at max                                  | 30 FPS at max                                | 30 FPS                  | 30 FPS                                             |

| Price per Detector Size (\$/mm^2)     | 51.96                                          | 2.00                                         | 0.66                    | 0.66                                               |

#### **Chapter 2**

## **Hybrid Detector Operation Schema**

#### 2.1 Thin Film Transistors

#### 2.1.1 Hydrogenated Amorphous Silicon (a-Si:H)

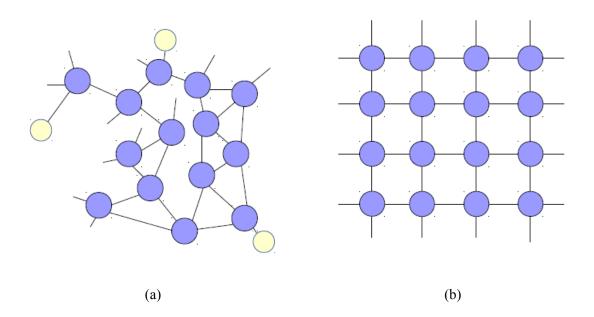

Figure 8 indicates the atomic bonding structure of a-Si:H in a two-dimensional illustration and is compared to a typical crystalline silicon structure. Figure 8 (a) illustrates the chaotic bonding structure of a-Si:H with a few dangling bonds filled up with hydrogen atoms (bright color.) Such bonding structure is generated from a low temperature (~ 300 °C) plasma enhanced chemical vapor deposition (PECVD) method where the atomic bonding cannot be controlled separately. However, such low temperature and the use of PECVD enables the fabrication of electronics in a large area format on cheaper alternate substrates, including glass, in an economical manner.

Figure 8 Two dimensional illustrations on atomic bonding for (a) amorphous silicon and (b) crystalline silicon.

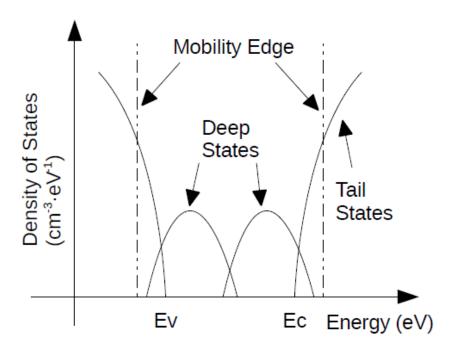

The disorder of the atomic structure illustrates a lot of additional trap states compared to the crystalline silicon layer. The missing atoms at dangling bonds can be interpreted as deep states, depicted in Figure 9,

and the disfigured and irregular atomic bonding leads to tail states where mobility edges need to be defined due to lack of distinct conduction and valence bands [24, 25]. The density of deep defect states in a-Si:H is in the range of  $10^{15} - 10^{18}$  cm<sup>-3</sup>eV<sup>-1</sup>, which is largely dependent on PECVD conditions. Meanwhile, atomic hydrogen (which can be supplied either from a SiH<sub>4</sub> precursor or additional hydrogen dilution) passivates a few dangling bonds to reduce the deep defect states [26].

Figure 9 Typical distribution of density of states in hydrogenated amorphous silicon.

Although decreased by hydrogen passivation, such a large deep defect density cannot be ignored in terms of transistor performance. A typical a-Si:H based transistor shows field effect mobility of  $0.1 - 1 \, cm^2/V \cdot s$ , which is dramatically lower than the typical field effect mobility of a crystalline silicon based MOSFETs ( $\sim 400 \, cm^2/V \cdot s$ ) or even polysilicon thin film transistors ( $\sim 200 \, cm^2/V \cdot s$ ). Such low field effect mobility also stems from massive distribution of the band tail states; thus, resulting in frequent trapping of electrons and holes during transport, which leads to extremely low field effect mobility. However, even faced with such challenges, a-Si:H TFTs are a proven technology capable of driving liquid crystal displays and commercially dominate the current flat panel display market [27].

The chaotic alignment of a-Si:H's atomic structure also leads to current drain over time due to threshold voltage increase over time. Carriers propagating through the a-Si:H constantly experience trapping and

de-trapping, inducing more deep states in the a-Si:H channel, resulting in Fermi energy distortion (pushing away from the conduction edge) on the process [26]. This constant creation of states especially under device operation leads to a well-known bias stress induced threshold voltage shift that was first modeled by M. J. Powell [28]:

#### **Equation 1**

$$\Delta V_{Thelec}(t) = A(V_{GS} - V_{Th0})^{\alpha}(t)^{\beta}$$

where,  $V_{GS}$  is a gate bias,  $V_{Th0}$  is the threshold voltage before metastability shift, and A,  $\propto$ , and  $\beta$  are temperature dependent fitting parameters (obtained empirically) when the electrical stress was applied for a time t.

However, the threshold voltage shift due to electrical bias stress can be reversed by simply applying a reverse bias (again, electrical stress) [29]. Thus, inserting a reverse bias cycle when the TFTs are operating in a constant cycle is usually sufficient to avoid long term performance degradation especially in display applications. However, if the application does not require a constant cycle of operation and mandates a constant bias stress, such as logic circuits, the feasibility of a-Si:H transistors remains questionable.

#### 2.1.2 TFT Structures

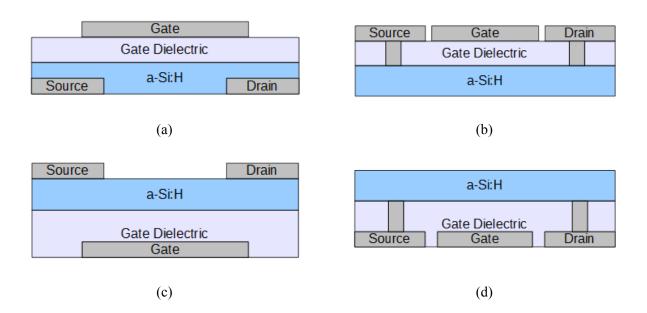

Thin film transistors can be manufactured in various configurations, which are determined by gate electrode and source-drain electrode arrangements. Generally, we assume four types of arrangements can be made as illustrated in Figure 10. Top gate structures can be found in Figure 10 (a) and (b) where the channel material is deposited prior to the gate dielectric, while the opposite deposition profile results in bottom gate structures as shown in Figure 10 (c) and (d).

On the other hand, gate electrode and source-drain electrodes are placed across the channel and dielectric layer, or staggered, as seen in Figure 10 (a) and (c). Such is a common structure for a-Si:H TFTs and nanocrystalline silicon TFTs because the channel layers provide additional space to decrease the electric field at the drain area, which prevents excessive off-state leakage. Furthermore, we can reduce process complexity with staggered structures because they only require two masks for TFT formation [30], while additional mask to open contact holes for source and drain electrodes are required for coplanar devices as depicted in Figure 10 (b) and (d).

In fact, a co-planar top gate structure is quite common in MOSFET and polycrystalline silicon TFTs because their contact layers can be prepared with ion implantation and the requirements of contact quality is higher than that of a-Si:H TFTs due to transconductance degradation issues. However, such processes require a post-annealing step to activate the dopants. This increases the production complexity even further beyond the additional contact hole mask. Therefore, to implement cost-effective large area applications, the staggered structure is preferred.

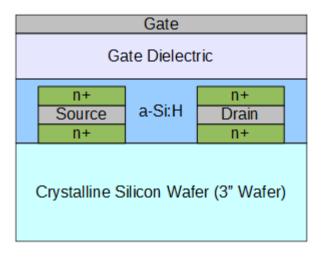

Figure 10 Four types of a-Si:H TFT structures.

In this work, we decided to implement our device readout of X-ray signals with a top-gate staggered structure (Figure 10 (a)) to reduce production complexity and subsequently cost. An inverted-staggered structure (or bottom gate staggered structure, Figure 10 (c)) was not selected because source and drain contact etch-selectivity is hard to control due to the contact layers being a-Si:H based materials. If the etch-selectivity problems are mitigated using a full wet etch process [31], the mask requirements and process complexity is still higher than that of a top-gate staggered TFT process. In contrast, a staggered-top gate structure can be fabricated with only two masks. It requires only one alignment step to finish the pixel and achieve a complete active-matrix TFT array, a remarkable achievement which simplifies the TFT fabrication process dramatically and improves reliability. Moreover, in contrast to a bottom gate

device, a top gate device is naturally suited to have a second gate on the bottom of the active semiconductor layer, a key requirement for operating the silicon X-ray sensitive layer which being the substrate, is naturally beneath the top gate TFT structure.

One drawback of the staggered-top gate structure is the crosstalk problem because the active layer (a-Si:H channel layer) spans through the entire array. However, we can avert this problem by allowing small gate overlaps for source and drain electrodes and etching the active layer and dielectric together, using the gate electrode as a mask. The process will be reviewed in detail in Chapter 3.

#### 2.1.3 a-Si:H TFT Operation Physics

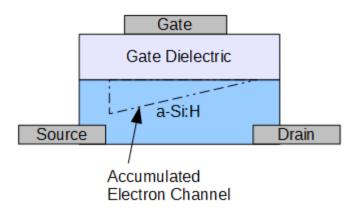

Figure 11 Illustration of top gate staggered thin film transistor.

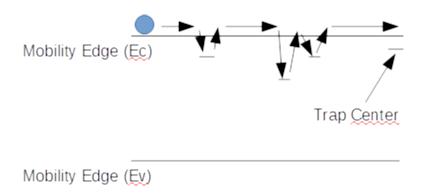

In short, the a-Si:H TFT operation and current-voltage (I-V) relationship is very similar to MOSFET's. The major difference is that we consider the mobility edges, depicted in Figure 9, to be the conduction and valence band edges, and the extreme amount of defect density of states in these tail states leads to a device best suited for accumulation mode operation. Due to the extreme amount of trap states, the threshold voltage required to cause inversion is much higher than that of MOSFETs, and the hole mobility is 1/10 the level of electrons in a-Si:H [26]. Thus, even though inversion can be theoretically achieved with high threshold voltage, the performance of TFT cannot reach that of electron accumulation channel and the large gate voltages necessary can cause stress on the gate dielectric.

Figure 11 illustrates the operation schema of a top gate staggered a-Si:H TFT. Because an intrinsic a-Si:H is slightly N-type [26], we can consider the device as an accumulation mode N-type MOSFET. Thus, gate and drain bias can be applied positive while source remains at ground. The positive bias at the gate attracts free electrons in the a-Si:H to induce an electron channel at the interface between the a-Si:H and the gate dielectric (mostly a-SiNx:H). When the drain is also biased positively, the electron channel conducts in the way illustrated in Figure 12.

Figure 12 One-dimensional illustration of electron conduction in a-Si:H.

The accumulated electron channel conduction is limited by massive amounts of deep trap states and band tail states, resulting in lower effective mobility than crystalline silicon MOSFETs. Here, electrons will confront a chain of trapping and detrapping mechanics constantly which can be modelled thusly:

#### Equation 2

$$\mu_{FE} = \mu_0 \frac{\tau_{free}}{\tau_{free} + \tau_{trapped}}$$

$\mu_0$  indicates the band mobility without trapping-detrapping mechanisms,  $\tau_{free}$  and  $\tau_{trapped}$  are the time intervals that electrons are free and trapped, respectively [26]. Because  $\tau_{trapped}$  is longer than free time and if the trapped location is a band tail state, then they are called band tail electrons.

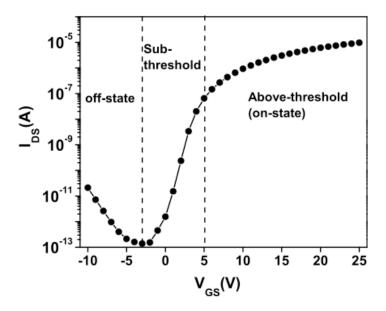

Figure 13 shows a typical transfer characteristic of an a-Si:H TFT. Three distinct operation regions can be distinguished: off-state, sub-threshold, and on-state. For small gate biases, the Fermi level lies in the deep defect states (refer to Figure 9) and the energy bands are close to the flat-band condition. As the gate bias increases (positive bias), band bending close to the gate dielectric interface occurs. In other words, the Fermi-level moves up through the deep defect states towards the band tail states [32, 33]. Thus, the threshold voltage of a-Si:H is a function of the density of deep defect states as derived in [24].

#### **Equation 3**

$$V_{Th} = qN_Tt_S(E_F - E_i)/C_{gate}$$

where  $E_F - E_i$  is the energy difference between the Fermi level and the intrinsic level at the threshold,  $N_T$  is the density of deep defect states,  $t_S$  and  $C_{gate}$  are the thicknesses of the channel layer and the gate capacitance per unit area, respectively. It should be noted that Equation 3 is derived with an assumption of uniformly distributed deep defect states in the energy gap.

Figure 13 A typical I-V curve of an a-Si:H TFT.

When the gate bias  $(V_{GS})$  exceeds the threshold voltage  $(V_{Th})$ , on-state, we can use FET equations to characterize the transfer characteristic. Thus, we can define linear and saturation with comparing  $V_{GS} - V_{Th}$  and drain bias  $(V_{DS})$ . Thus, if we take linear region,  $V_{DS} \leq V_{GS} - V_{Th}$ , the drain-source current  $(I_{DS})$  can be described as [27]:

#### **Equation 4**

$$I_{DS} = \mu_{FE} C_{gate} \frac{W}{L} \left[ (V_{GS} - V_{Th}) V_{DS} - \frac{{V_{DS}}^2}{2} \right]$$

W and L are TFT gate width and length, respectively.

When  $V_{DS} = V_{GS} - V_{Th}$ , the accumulation channel is pinched off near the drain terminal as depicted in Figure 11 and drain current saturates to be independent of drain bias  $(V_{DS})$ . For,  $V_{DS} > V_{GS} - V_{Th}$ , the TFT enters saturation regime and the output characteristic can be given by:

#### Equation 5

$$I_{DS} = \mu_{FE} C_{gate} \frac{W}{2L} (V_{GS} - V_{Th})^2$$

Therefore, field effect mobility ( $\mu_{FE}$ ) and threshold voltage ( $V_{Th}$ ) can be extracted from experimentally obtained I-V curves by using Equation 4 and Equation 5 depending on the regime of operation.

The off-state characteristic mainly depends on ohmic conductivity of the active layer [28] [33]. When negative gate bias is applied, the Fermi level is pushed down to the deep trap states, resulting in a depletion of the band tail states and the effective conductivity of the a-Si:H layer decreases.

However, Figure 13 depicts increasing drain current when the gate bias is negative. In other words, trap-assisted mechanisms may occur in the negatively biased a-Si:H region and intensify with increasing negative gate bias. Especially at the overlap region at the gate-drain electrodes, the gate bias and drain bias are applied additively leading to very high electric fields to encourage trapped electrons to travel by emission mechanisms, including Poole-Frenkel (thermionic emission) conduction [34, 35]:

#### **Equation 6**

$$I_{PF} = I_{PF0}e^{\left(\sqrt{E/E_0}\right)}$$

where  $E/E_0$  is the normalized electric field. Therefore, the Poole-Frenkel current ( $I_{PF}$ ) increases exponentially with the electric field in the gate-drain overlap region at the reverse gate bias condition. The off-state current is a combination of drain-source ohmic current and the Poole-Frenkel current due to excessive negative gate bias. In other words, the off-current is affected by the gate-drain voltage difference, preventing additional leakage routes between the drain-source.

#### 2.2 Direct Contact Detector

#### 2.2.1 Operation Principle

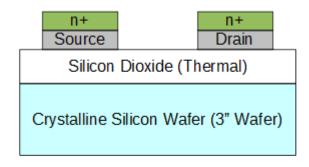

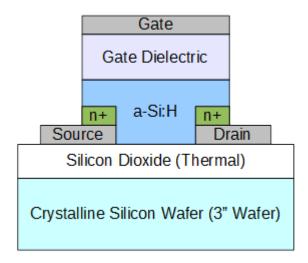

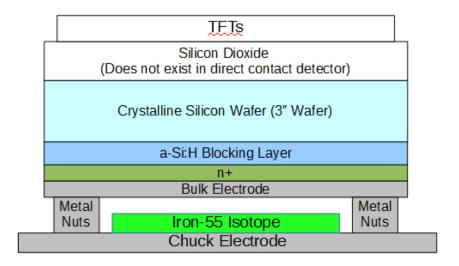

Figure 14 Schematic of a-Si:H-silicon direct contact detector.

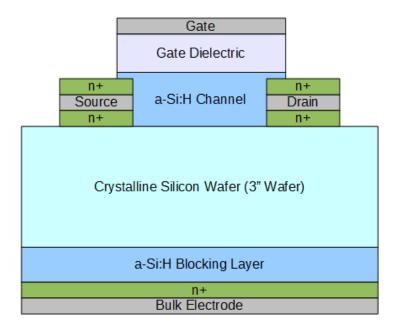

The direct contact detector is a combination of an intrinsic crystalline silicon bulk photodiode and a staggered top gate a-Si:H TFT. As depicted in Figure 14, the a-Si:H TFT is deposited on top of a crystalline silicon substrate that forms part of the photodiode. The bottom side of the crystalline silicon substrate is passivated with an additional a-Si:H layer to reduce dark current and a doped diode contact called the bulk electrode.

The crystalline silicon layer provides a direct conversion X-ray to electron-hole pair converter that operates normally under reverse bias (i.e. when a positive voltage is applied to the bulk electrode). The a-Si:H blocking layer is deposited to reduce leakage currents when the silicon diode is placed under reverse bias. Indeed, the TFT side will be positively biased (i.e. the gate and drain electrodes) while the source electrode is tied with ground; thus, resulting in a back to back bias for the entire system. The n+ contacts at the TFT source and drain contacts provide additional depletion regions to temporarily store the photogenerated carriers. For our device with positive bias voltages on the gate, drain and bulk electrodes and the source electrode grounded, holes will reside at the potential minimum of the depletion well created as depicted in Figure 15.

The stored carriers, holes, provide an additional gate bias from the bottom side, which alters the channel conductivity at the a-Si:H and crystalline silicon bulk interface. Thus, the TFT transfer characteristic equation can be adapted to include this effect as follows:

#### Equation 7

$$I_{DS} = \mu_{FE} C_{gate} \frac{W}{L} \left[ (V_{GS} + V_{IG} - V_{Th}) V_{DS} - \frac{{V_{DS}}^2}{2} \right]$$

where  $V_{IG}$  represents the induced gate bias resulting from the X-ray photon generated charge in the crystalline silicon substrate, also depicted in Figure 15 as the hole cloud.

# Figure 15 Quasi-Fermi level distribution in the crystalline silicon substrate. The dotted line indicates a-Si:H TFT-crystalline silicon interface.

The induced gate bias can be estimated as the following:

#### **Equation 8**

$$V_{IG} = \frac{Q_{X-Ray}}{C_D}$$

where  $Q_{X-Ray}$  is the X-ray photon-generated charge stored at the potential minimum and  $C_D$  is the capacitance per unit area of the intrinsic silicon substrate induced by the TFT gate bias:  $C_D = \epsilon_{si}/t_{si}$ .

Thus, the thicker the substrate, the larger induced voltage because the capacitance is smaller. Therefore, we can predict the induced current by absorbed X-ray photons using the following equation:

#### **Equation 9**

$$\Delta I_{DS} = \mu_{EF} C_{gate} \frac{W}{L} V_{IG} V_{DS}$$

Initial work on this pixel architecture using a bipolar TFT device with  $W/L = 1 \, mm/1 \, mm$  was first reported by Kai Wang and Karim S. Karim[36]. However, this device lacked n+ contacts to prevent off-state conduction at the top gate side and the direct contact for source and drain electrodes to the crystalline silicon bulk created an additional off-state current path through the silicon substrate, lowering the TFT's on/off current ratio dramatically. While functional at the pixel level, the high leakage makes the device unusable for a large area active matrix array application such as for protein crystallography. The performance of this direct contact detector will be elaborated on in a later chapter.

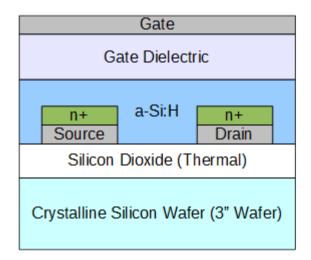

#### 2.3 Silicon Dioxide Passivated Detector

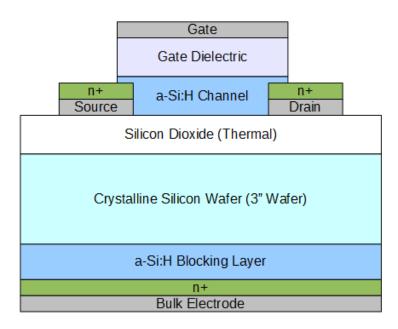

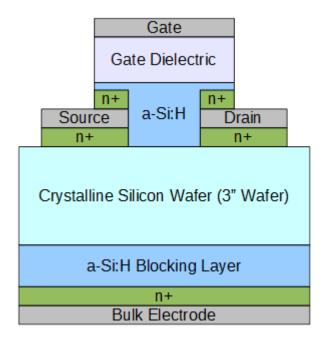

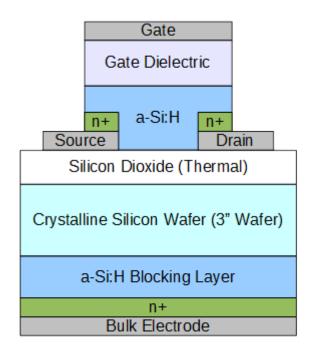

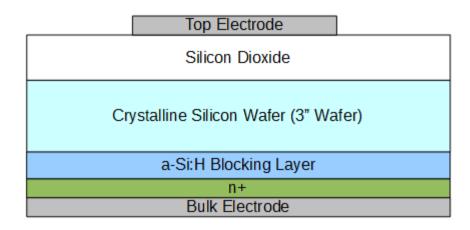

Figure 16 Revised hybrid detector with silicon dioxide blocking layer.

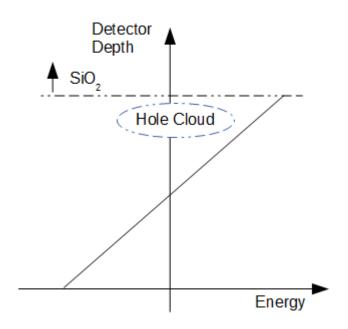

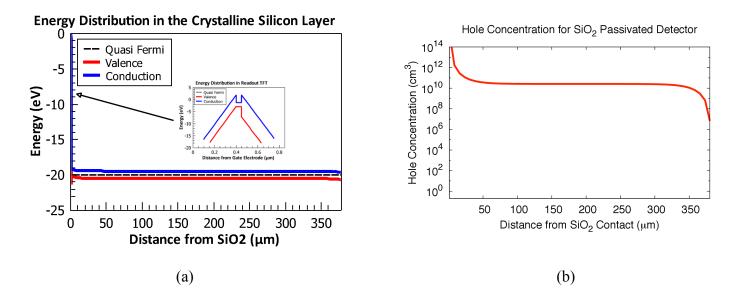

To prevent parasitic off-state current through the crystalline silicon bulk, a thermally grown silicon dioxide layer is implemented as a blocking layer and serve as the dielectric for secondary gate associated

with the X-ray photon-generated charge. The detector operation bias voltages stay similar to that of the direct contact detector. However, due to the passivation layer, the detector capacitance increases marginally. As seen in Figure 17, the energy increases throughout the crystalline silicon layer, resulting the X-ray generated holes concentrated at the silicon dioxide-crystalline silicon interface. Thus, the capacitance of a detector is simply determined by the silicon dioxide itself which is usually 1000 times thinner than the crystalline silicon detector itself. For in-house fabricated device, the silicon dioxide was 300-nm-thick, while the crystalline silicon was 380 µm-thick.

Figure 17 Quasi-Fermi level distribution in the silicon substrate.

Of course, the X-ray generated electrons will be extracted through the bulk diode contact since the electric field within the crystalline silicon detector is constant. Furthermore, the improved capacitance of the detector provides better in-pixel amplification since the larger capacitance provides more hole concentration in a given bulk diode bias voltage at the pixel area. In other words, the 'virtual gate' TFT in the silicon dioxide passivated detector has better performance than the direct contact detector. However, due to the cost to grow the silicon dioxide with thermal process, a slight increase in the price per unit area is inevitable. On the bright side, the silicon dioxide process is a common process in current industry standard. Thus, the increase in manufacture price will not affect as a critical factor for the overall unit price.

#### 2.3.1 Energy Distribution Investigation with TCAD

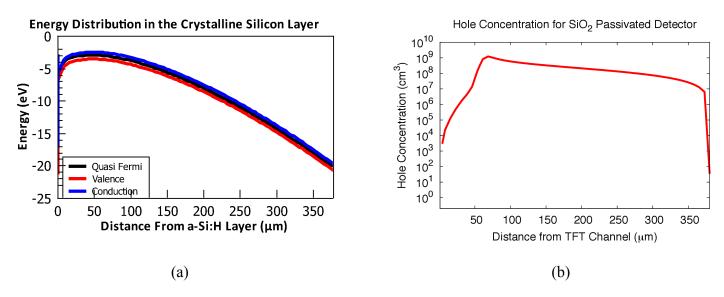

Figure 18 (a) Energy distribution in the direct contact detector (in the crystalline silicon substrate) and (b) hole concentration under back to back bias condition.

Figure 19 (a) Energy distribution in the silicon dioxide passivated detector (in the crystalline silicon substrate) and (b) hole concentration under back to back condition.

Energy distribution in the crystalline silicon detector under back-to-back bias was verified with a Synopsys MEDICI TCAD (Technology Computer Aided Design)<sup>1</sup> simulation tool. The simulation was performed to ensure the feasibility of operation principle which was discussed in previous chapter. As described in earlier sections, hole concentration in a direct contact detector is concentrated in the crystalline silicon bulk, away from the amorphous silicon TFT (Figure 18), while the majority of holes are concentrated in the vicinity of the silicon dioxide and crystalline silicon interface in the passivated detector (see Figure 19). Basically, Figure 18 and Figure 19 are transposed (rotated 90 degrees in counterclockwise direction) versions of Figure 15 and Figure 17, respectively.

However, simulation results cannot be trusted entirely because trap distribution of a-Si:H and a-Si $N_x$ :H layers was not accurately extracted from fabricated samples. In fact, the trap distribution used was that given in the simulator's default as provided by the MEDICI 2007 manual. These values are provided in the appendix section at the end of the thesis.

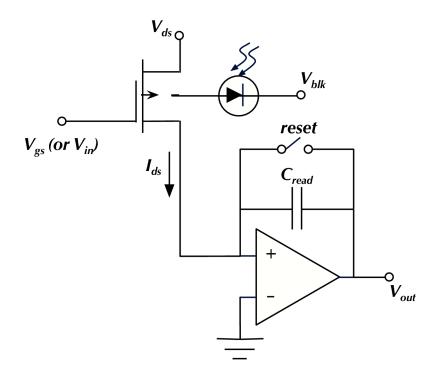

## 2.3.2 Readout and In-pixel Amplification

The pixel readout architecture is based on an active pixel sensor design, but it lacks a read transistor switch because the a-Si:H TFT itself is a switch and signal amplifier. Here, the switching function is controlled by the gate electrode bias while the X-ray photon-generated charge stored in the silicon substrate acts as additional gate bias resulting in an amplification effect in the transistor current. To the best of our knowledge, this is the first report of a single TFT active pixel sensor readout circuit as depicted in Figure 20.

The readout operation consists of three phases: reset, integration, and readout (as shown in Table 3). The reset phase is dedicated for clearing out accumulated photo-generated charges in the silicon substrate where a negative bias is applied to the bulk electrode while the source electrode remains at ground level. The photo-generated charge is evacuated through the forward biased P-N diode ( $V_{BLK}$ ) and the charge stored in the column amplifier's capacitance,  $C_{read}$ , is neutralized by closing the reset switch without reading out any signal from the pixel TFT.

<sup>&</sup>lt;sup>1</sup> TCAD is a computer aided design tool which simulates device characteristics and fabrication process.

Figure 20 Expected implementation of the hybrid detector readout.

Table 3 Hybrid detector readout schema.

| Signal           | Reset Phase   | Integration   | Readout       |

|------------------|---------------|---------------|---------------|

| V <sub>GS</sub>  | Low           | Low           | High          |

| V <sub>DS</sub>  | Low           | Low           | High          |

| V <sub>BLK</sub> | Negative Bias | Positive Bias | Positive Bias |

The integration phase is dedicated to accumulating and storing X-ray generated charge in the silicon detector capacitance. Thus,  $V_{BLK}$  must be such that the PN diode is under reverse bias and able to accumulate charge. The TFT's gate, drain and source electrodes are held at low potential to minimize metastability related changes.

In the Readout phase, both  $V_{GS}$  and  $V_{DS}$  are turned on and enable the TFT's  $I_{DS}$  to charge up the column amplifier's readout capacitance ( $C_{read}$ ). Note that the  $I_{DS}$  is a function of both the applied gate bias  $V_{GS}$  and the X-ray generated charge on the TFT's second gate. The amplification (pixel charge gain,  $G_p$ ) of the

single TFT active pixel can be described as a function of TFT transconductance  $(g_m)$  and the duration of Readout phase  $(T_s)$  [37]:

## **Equation 10**

$$G_p = \frac{g_m T_s}{C_{Pix}}$$

The pixel capacitance can be determined as  $C_{Pix} = WLC_D$ . Thus, the readout gain is dependent on the TFT performance  $(g_m)$ , the readout time  $(T_S)$  and, most importantly, the detector capacitance,  $C_{Pix}$ . Additionally, the TFT needs to be operated under linear bias to avoid detrimental effects from threshold voltage change and  $g_m$  dependence of the gate bias [38]. It is obvious that transconductance remains a constant when the transistor is operated in the linear region because the output current  $(I_{DS})$  increase is proportional to the input voltage  $(V_{GS})$ . Any effects of inadvertent threshold voltage shifts are minimal because the channel is connecting a source to drain path.

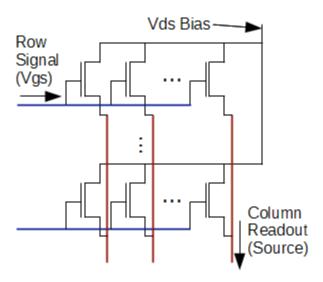

Figure 21 Array readout scheme of the 1T-APS pixel for the hybrid detector.

The detector can be laid out and operated as an active matrix array since only two ports are required for a pixel to operate. The drain electrode can be hooked at a common voltage source while gate bias was provided with a row and the readout at source electrode can be read out as a column. Only difference against a passive pixel sensor is the drain electrode which will be connected to a voltage source, instead of

a detector pixel capacitance. Of course, the bulk diode contact is provided by a single electrode which spans entire detector array at the other side of the wafer, isolated from the readout electronics. Figure 21 illustrates the active matrix array readout for the 1T-APS detector.

# **Chapter 3**

## **Detector Fabrication**

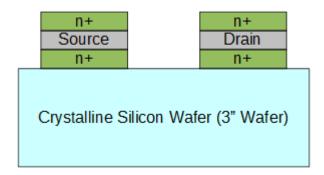

#### 3.1 Overview

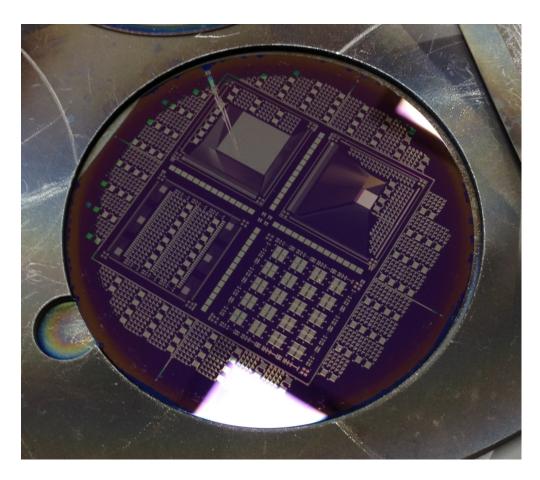

Both the direct contact and silicon dioxide passivated hybrid detectors were fabricated in-house using a process comprising only two lithography steps. The process is relatively simple and does not require a negative mask forvia openings as is typically used in TFT fabrication. The detector electrodes were deposited by a sputtering process using an Edwards sputtering system. The a-Si:H, hydrogenated amorphous silicon nitride (a-SiNx:H), and n+ doped a-Si:H films were deposited using a Plasma Enhanced Chemical Vapor Deposition (PECVD) process. These depositions were done using a PECVD cluster tool (multi-chamber system) developed by MVSystems Inc. (refer to Figure 22).

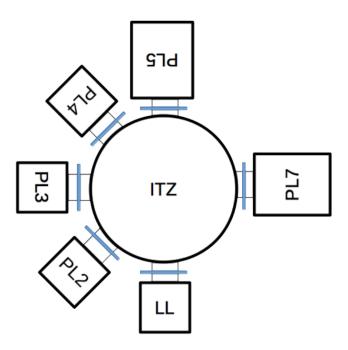

Figure 22 Schematic of the MVSystems multi-chamber PECVD system.

The multi-chamber system is advantageous in film quality and process control over single chamber systems, however their installation and maintenance budget requirements are much higher than simple systems. Because each chamber is dedicated to a certain type of film deposition, integrating different

process steps is easily accomplished with cluster tools. The in-house tool, depicted in Figure 22, has the chamber assignments shown in Table 4.

Table 4 Chamber assignment of in-house cluster PECVD facility.

| LL                        | PL2                               | PL3                           | PL4                             | PL5                               | PL7               | ITZ<br>(Robot arm)          |

|---------------------------|-----------------------------------|-------------------------------|---------------------------------|-----------------------------------|-------------------|-----------------------------|

| Load/Unload<br>Substrates | Intrinsic<br>silicon<br>materials | Doped<br>silicon<br>materials | Gate<br>dielectric<br>materials | ITO, metal<br>oxide<br>deposition | Laser<br>ablation | Junction for other chambers |

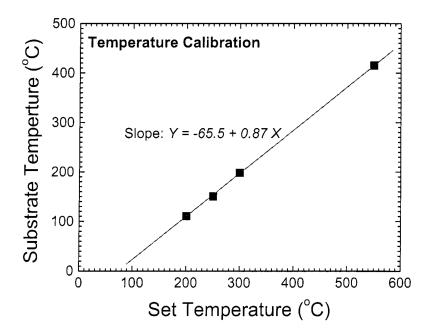

Figure 23 Temperature calibration data of the in-house cluster tool [39].

The substrates onto which the films are deposited are moved around by riding a robotic arm installed in the Interchamber Transfer Zone (ITZ). Therefore, direct contact with the heater element in each chamber is impossible. This leads to a difference between the heater element temperature setting at the control panel and the actual substrate temperature. A thermocouple is installed on top of each chamber for

detection of the chamber temperature. Figure 23 shows the thermal calibration data between the set temperature and the substrate temperature. The process temperature that appear in this thesis are the set values and can be converted to actual substrate temperature using the calibration curve in Figure 23.

## 3.2 Plasma Enhanced Chemical Vapor Deposition

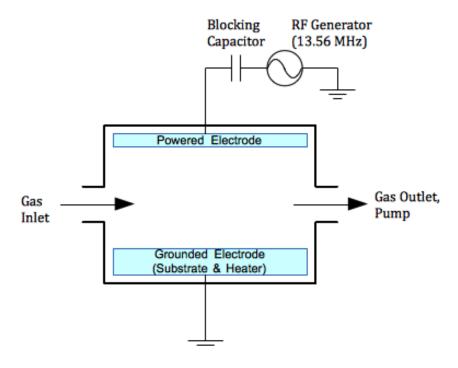

Various plasma-assisted deposition methods, including radio frequency PECVD, direct current PECVD, very-high frequency PECVD (VHF-PECVD), and electron cyclotron resonance (ECR)-CVD, for silicon-based thin films have been reported since the 1960s [40-42]. Among them, the 13.56 MHz RF PECVD process has been the industrial standard for thin film transistor (a-Si:H) fabrication.

A typical RF-PECVD reactor comprises of two parallel electrodes in a vacuum chamber with gas inlet and outlet ports, each connected toa mass flow controller and pump. The electrodes are biased with an RF generator with a frequency of 13.56 MHz in most cases (as illustrated in Figure 24). Additionally, PECVD chambers are typically equipped with a heating element to heat up the chamber. The deposition takes place inside the chamber where the plasma is ignited between the two parallel plates.

In the plasma state, the mobility of electrons is much higher than positive ions due to the smaller mass of electrons (an electron's mass is 5 times that of a proton[42]). Because the electrical force applied to both carriers is the same, the difference in mass of particles results in a difference in mobility. Such large differences generate unbalanced sinusoidal waves, as shown in Figure 25. The excess electrons result in a DC component in the plasma current, which is blocked by the capacitor shown in Figure 24. The voltage bias that appears across the blocking capacitor is known as the self-bias voltage.

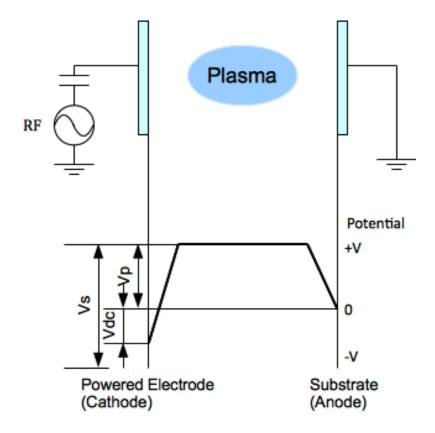

The space between the parallel electrodes consists of three major regions: the plasma itself (electrically neutral,) the RF electrode sheath, and the ground electrode sheath, as illustrated in Figure 26. Here,  $V_{dc}$ ,  $V_s$ , and  $V_p$  represent the self-bias voltage, sheath potential, and plasma potential, respectively. The plasma potential is always positive and considered as a reference potential, while the potential at the powered electrode ends up as the self-bias voltage. The sheath potential is the potential difference between the plasma and the powered electrode ( $V_p - V_{dc} = V_s$ ). Thus, ions tend to accelerate at the sheath region towards the electrodes, due to the high electric field at the sheath region, resulting in ion bombardment. Because the sheath region electric field (the slope of the potential distribution in Figure 26) is above the ground electrode, one can avoid ion bombardment by placing the substrate close to the ground electrode.

Figure 24 Schematic diagram of a typical RF-PECVD reactor.

Figure 25 Static current-voltage (I-V) characteristics of a plasma (adopted from [40].)

Figure 26 Time-average potential distribution in a plasma reactor (modified from [40, 42].)

The deposition process requires various gas precursors (such as SiH<sub>4</sub> for silicon based materials) to be physically disassembled by the electric bias of the RF plasma. The specific growth mechanism of any deposited film is very difficult to determine since the dominant reactions in a PECVD process can come from a large number of possibilities. For example, the plasma reactions for the SiH<sub>4</sub> precursor for a-Si:H deposition are [26]:

## **Equation 11**

$$e^- + SiH_4 \Rightarrow SiH_2 + H_2 + e^- \rightarrow 2.2 \ eV$$

$e^- + SiH_4 \Rightarrow SiH_3 + H + e^- \rightarrow 4.0 \ eV$

$e^- + SiH_4 \Rightarrow Si + 2H_2 + e^- \rightarrow 4.2 \ eV$ .

The electrons on the left hand side in Equation 11 indicate the electrons generated between the RF biased parallel plates. The radicals and ions collide with each other, or the precursor itself (SiH<sub>4</sub>), before reaching the substrate, causing additional reactions. Amongst various radicals, SiH<sub>3</sub> survives for the longest period and becomes a controlling factor in the a-Si:H deposition process. Meanwhile, they also combine themselves, resulting in the formation of large Si<sub>n</sub>H<sub>m</sub> molecules (or powders) in the reaction chamber, which can pull down the uniformity and mechanical integrity of the a-Si:H film.

Since the exact growth mechanisms for film growth are not known, the film growth parameters are described using the processing conditions, such as gas pressure, reactor temperature, dilution ratio, RF power density, and gas flow rate. The role of each deposition condition is summarized in Table 5.

Table 5 Effect of PECVD parameters.

| Parameters    | Effect in PECVD process                                                          |

|---------------|----------------------------------------------------------------------------------|

| Pressure      | Higher pressure ensures faster film growth speed. However, due to higher         |

|               | chance of collision of ions, powder generation also increases.                   |

| Gas flow rate | Provides more precursors in the reactor chamber in a given time. Thus, has a     |

|               | similar effect to the pressure. MFC (Mass Flow Controller) limited.              |

| RF power      | Increases the amount of plasma. Increases the deposition rate.                   |

| Temperature   | Determines chemical reaction rate on the growth surface. Decreases growth        |

|               | rate a bit due to fewer dangling bonds as a result of high mobility of radicals. |

|               | If SiH₄ was a precursor, hydrogen absorption rate increases.                     |

| Gas dilution  | Lowers deposition rate and prevents serious powder generation when inert         |

|               | gas is used. Improves interface states (decreases the number of surface          |

|               | states) if the dilution gas was hydrogen.                                        |

## 3.3 Film Characterization

## 3.3.1 Gate Dielectric

Silicon nitride has been used as a gate dielectric for a-Si:H TFT since the emergence of the LCD industry [26, 43, 44]. The gate dielectric plays a key role in any field effect transistor performance because its main

role is blocking the attracted charges that remain accumulated at the gate-active layer interface, and securing a clear path form source to drain. In this section, the electrical properties of the PECVD hydrogenated amorphous silicon nitride (a-SiN $_x$ :H) layer are presented.

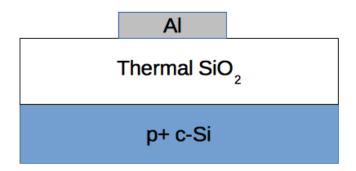

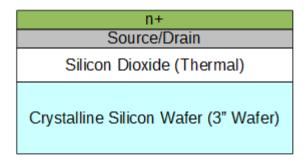

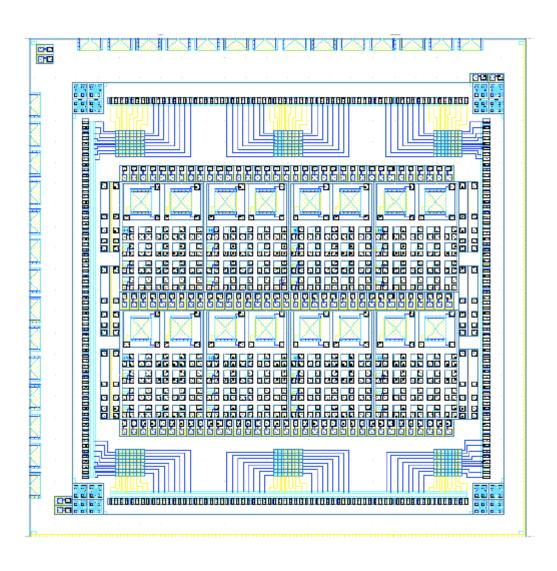

Figure 27 shows the metal-insulator-semiconductor structure used to characterize the silicon nitride film. The substrate was selected based on the purpose of the measurement. For current-voltage (I-V) tests, p+ crystalline silicon (surface resistance < 0.001  $\Omega \cdot$  cm) was used to ensure maximum conductivity, while a higher surface resistance (>0.01  $\Omega \cdot$  cm) was used in capacitance-voltage (C-V) tests. The dopant type remained as p-type because the main active carrier for a-Si:H TFT is electrons. The top metal electrode was sputtered with a shadow masks as shown in the appendix.

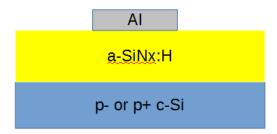

Figure 27 MIS a-SiN<sub>x</sub>:H characterization sample cross-section.

The a-SiN<sub>x</sub>:H was deposited in the PL4 chamber of the PECVD cluster tool. The chamber was pre-coated with 200 nm of a-Si:H to minimize contamination from silicon dioxide particles from other deposition processes. Table 6 shows the deposition conditions of the film with a gas flow to nitrogen dilution ratio of  $1:20 \text{ (SiH}_4:NH_3)$ . The nitrogen dilution ratio has been shown to give a high quality film for a-Si:H TFTs, with high field effect mobility and low gate leakage current [45-48]. Also, nitrogen rich a-SiN<sub>x</sub>:H films tend to sustain metastability effectively [49].

Table 6 Recipe table for a-SiNx:H gate dielectric, PL4.

| SiH <sub>4</sub> (sccm <sup>2</sup> ) | NH <sub>3</sub> (sccm) | N <sub>2</sub> (sccm) | Pressure<br>(mTorr) | Temp.<br>(°C) | RF Power<br>(W) | Growth<br>Rate<br>(nm/sec) |

|---------------------------------------|------------------------|-----------------------|---------------------|---------------|-----------------|----------------------------|

| 5                                     | 100                    | 50                    | 400                 | 350           | 2               | 0.1                        |

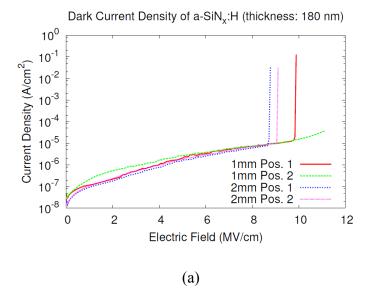

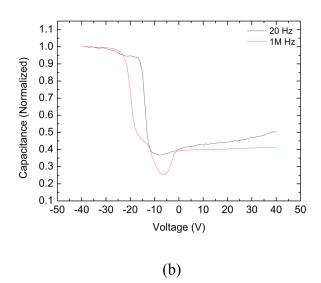

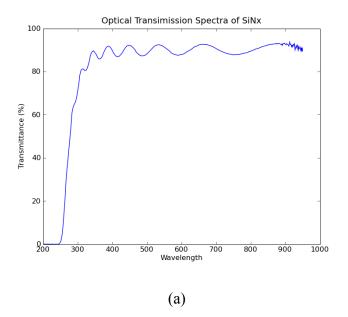

Figure 28 (a) I-V and (b) C-V characteristics of a-SiNx:H prepared by cluster tool PL4 chamber.

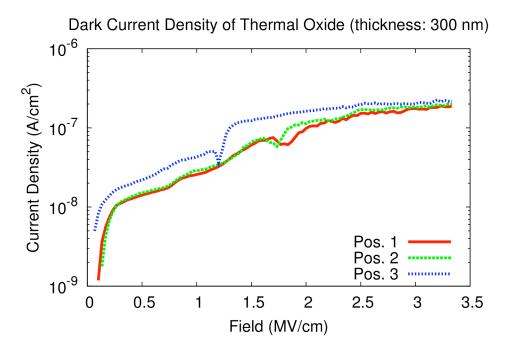

I-V characteristics were obtained with a Keithley 4200 system under dark conditions. The electric bias between the top electrode and the silicon bulk was applied via a sweeping profile from 0 to 200 V, and the result was normalized to the electric field, as depicted in Figure 28. The current increases through the continuous sweeping of voltage bias up to 8 MV/cm of electric field, where breakdown occurs and the current hits compliance value<sup>3</sup> of 1 mA.

The current-voltage characteristics (under dark conditions, Figure 28 (a)) provide a useful guide for TFT gate leakage estimation, at the current density around 2 MV/cm (36 V of gate bias for 180-nm-thick

<sup>&</sup>lt;sup>2</sup> Square Cubic Centimeters per Minute. Unit of precursor gas flow for PECVD deposition.